등록특허 10-2469160

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2022년11월22일

(11) 등록번호 10-2469160

(24) 등록일자 2022년11월16일

(51) 국제특허분류(Int. Cl.)

H01L 21/8238 (2006.01) H01L 27/02 (2006.01)

H01L 27/092 (2006.01) H01L 29/10 (2006.01)

(52) CPC특허분류

H01L 21/823892 (2013.01)

H01L 27/0248 (2013.01)

(21) 출원번호 10-2019-7004299

(22) 출원일자(국제) 2017년08월16일

심사청구일자 2020년08월12일

(85) 번역문제출일자 2019년02월13일

(65) 공개번호 10-2019-0039138

(43) 공개일자 2019년04월10일

(86) 국제출원번호 PCT/US2017/047148

(87) 국제공개번호 WO 2018/035226

국제공개일자 2018년02월22일

(30) 우선권주장

15/238,445 2016년08월16일 미국(US)

(56) 선행기술조사문현

US20080296675 A1

(뒷면에 계속)

전체 청구항 수 : 총 60 항

심사관 : 오순영

(54) 발명의 명칭 기판 상에 양면형 에피택셜을 사용한 공정 개선

**(57) 요 약**

반도체 웨이퍼를 및 집적 회로들을 제조하기 위한 반도체 디바이스들 및 제조 방법들의 설명된 예들에서, 방법(300)은 제1 전도형의 반도체 기판의 제1 면 상에 제1 전도형의 제1 에피택셜 반도체 층을 형성하는 단계(304), 제1 에피택셜 반도체 층의 상부 면 상에 질화물 또는 산화물 보호 층을 형성하는 단계(306), 반도체 기판의 제2 면 상에 제1 전도형의 제2 에피택셜 반도체 층을 형성하는 단계(310), 및 제1 에피택셜 반도체 층으로부터 보호 층을 제거하는 단계(314)를 포함한다. 웨이퍼는 제1 에피택셜 반도체 층 상에 적어도 부분적으로 트랜지스터들을 형성함으로써(316) 집적 회로를 제조하는 데 사용될 수 있다.

**대 표 도 - 도3**

(52) CPC특허분류

*H01L 27/0921* (2013.01)

*H01L 29/1083* (2013.01)

(56) 선행기술조사문헌

US20100075175 A1\*

US20110095358 A1

US20130264467 A1\*

WO2009001833 A1

\*는 심사관에 의하여 인용된 문헌

---

## 명세서

### 청구범위

#### 청구항 1

디바이스로서,

제1 전도형의 반도체 기판 - 상기 반도체 기판은 평탄한 제1 면 및 평탄한 제2 면을 포함함 -;

상기 반도체 기판의 제1 면 상에 형성된 상기 제1 전도형의 제1 반도체 층; 및

상기 반도체 기판의 제2 면 상에 형성된 상기 제1 전도형의 제2 반도체 층

을 포함하고,

제2 전도형의 영역들이 상기 제1 반도체 층 및 상기 제2 반도체 층 중 오직 하나에서 형성되고,

상기 제2 전도형의 영역들 중 어느 하나도, 상기 제1 반도체 층 및 상기 제2 반도체 층 중 다른 하나 및 상기 반도체 기판을 통과해 전기적으로 연결되지 않는, 디바이스.

#### 청구항 2

제1항에 있어서, 상기 제1 및 제2 반도체 층들은 상기 반도체 기판보다 더 저농도로 도핑된, 디바이스.

#### 청구항 3

제2항에 있어서, 상기 제1 전도형은 p-형이고, 상기 제2 전도형은 n-형인, 디바이스.

#### 청구항 4

제2항에 있어서, 상기 제1 전도형은 n-형이고, 상기 제2 전도형은 p-형인, 디바이스.

#### 청구항 5

제1항에 있어서, 상기 제2 전도형의 영역들 중 적어도 제1 영역과 제2 영역은 각각 트랜지스터의 소스 및 드레인을 형성하는, 디바이스.

#### 청구항 6

집적 회로(IC) 디바이스로서,

제1 전도형의 반도체 기판 - 상기 반도체 기판은 평탄한 제1 면 및 평탄한 제2 면을 포함함 -;

상기 반도체 기판의 제1 면 상에 형성된 제1 전도형의 제1 에피택셜 반도체 층;

상기 반도체 기판의 제2 면 상에 형성된 제1 전도형의 제2 에피택셜 반도체 층; 및

상기 제1 에피택셜 반도체 층의 표면에 적어도 부분적으로 형성된 복수의 트랜지스터들

을 포함하고,

어떠한 트랜지스터들도 상기 제2 에피택셜 반도체 층의 표면에 형성되지 않고,

상기 제1 에피택셜 반도체 층의 트랜지스터들 중 어느 하나도, 상기 반도체 기판 및 상기 제2 에피택셜 반도체 층을 통과해 전기적으로 연결되지 않는, 집적 회로(IC) 디바이스.

#### 청구항 7

제6항에 있어서, 상기 제1 및 제2 에피택셜 반도체 층들은 상기 반도체 기판보다 더 저농도로 도핑된, 집적 회로(IC) 디바이스.

#### 청구항 8

제7항에 있어서, 상기 제1 전도형은 p-형인, 집적 회로(IC) 디바이스.

#### 청구항 9

제7항에 있어서, 상기 제1 전도형은 n-형인, 집적 회로(IC) 디바이스.

#### 청구항 10

반도체 디바이스를 제조하는 방법으로서,

제1 전도형의 반도체 기판의 제1 면 상에 상기 제1 전도형의 제1 에피택셜 반도체 층을 형성하는 단계;

상기 반도체 기판의 제2 면 상에 상기 제1 전도형의 제2 에피택셜 반도체 층을 형성하는 단계; 및

제2 전도형의 영역들을 상기 제1 에피택셜 반도체 층에 적어도 부분적으로 형성하는 단계를 포함하고,

상기 제2 전도형의 어떠한 영역도 상기 제2 에피택셜 반도체 층에 형성되지 않고,

상기 반도체 기판은 상기 제1 에피택셜 반도체 층으로부터 상기 제2 에피택셜 반도체 층까지 통과해 연장되는 어떠한 전도성 통로도 갖지 않는, 반도체 디바이스를 제조하는 방법.

#### 청구항 11

제10항에 있어서,

상기 제2 에피택셜 반도체 층을 형성하기 전에 상기 제1 에피택셜 반도체 층의 상부 면 상에 보호 층을 형성하는 단계; 및

상기 제2 에피택셜 반도체 층을 형성한 후에 상기 제1 에피택셜 반도체 층으로부터 상기 보호 층을 제거하는 단계

를 더 포함하는, 반도체 디바이스를 제조하는 방법.

#### 청구항 12

제11항에 있어서, 상기 보호 층을 형성하는 단계는 상기 제2 에피택셜 반도체 층을 형성하기 전에 상기 제1 에피택셜 반도체 층의 상부 면 상에 질화물 재료를 형성하는 단계 또는 상기 제2 에피택셜 반도체 층을 형성하기 전에 상기 제1 에피택셜 반도체 층의 상부 면 상에 산화물 재료를 형성하는 단계를 포함하는, 반도체 디바이스를 제조하는 방법.

#### 청구항 13

제12항에 있어서, 상기 제1 및 제2 에피택셜 반도체 층들은 상기 반도체 기판보다 더 저농도로 도핑된, 반도체 디바이스를 제조하는 방법.

#### 청구항 14

제11항에 있어서, 상기 제2 전도형의 영역들을 상기 제1 에피택셜 반도체 층에 적어도 부분적으로 형성하는 단계는 상기 제1 에피택셜 반도체 층으로부터 상기 보호 층을 제거한 후에 수행되는, 반도체 디바이스를 제조하는 방법.

#### 청구항 15

제14항에 있어서, 상기 제1 및 제2 에피택셜 반도체 층들은 상기 반도체 기판보다 더 저농도로 도핑된, 반도체 디바이스를 제조하는 방법.

#### 청구항 16

제10항에 있어서, 상기 제1 및 제2 에피택셜 반도체 층들은 상기 반도체 기판보다 더 저농도로 도핑된, 반도체 디바이스를 제조하는 방법.

#### 청구항 17

제16항에 있어서, 상기 제1 전도형은 p-형이고 상기 제2 전도형은 n-형인, 반도체 디바이스를 제조하는 방법.

#### 청구항 18

제16항에 있어서, 상기 제1 전도형은 n-형이고 상기 제2 전도형은 p-형인, 반도체 디바이스를 제조하는 방법.

#### 청구항 19

제16항에 있어서,

상기 제2 에피택셜 반도체 층을 형성하기 전에 상기 제1 에피택셜 반도체 층의 상부 면 상에 질화물 또는 산화물 보호 층을 형성하는 단계; 및

상기 제2 에피택셜 반도체 층을 형성한 후에 상기 제1 에피택셜 반도체 층으로부터 상기 보호 층을 제거하는 단계

를 더 포함하는, 반도체 디바이스를 제조하는 방법.

#### 청구항 20

제10항에 있어서,

상기 제2 에피택셜 반도체 층이 아닌 상기 제1 에피택셜 반도체 층에 격리 구조물을 형성하는 단계를 포함하는, 반도체 디바이스를 제조하는 방법.

#### 청구항 21

집적 회로(IC) 디바이스로서,

제1 면 및 상기 제1 면에 대향하는 제2 면을 갖는 제1 전도형의 반도체 기판 - 상기 제1 면 및 제2 면은 상기 반도체 기판의 두께와 동일한 거리만큼 분리됨 -;

상기 반도체 기판의 상기 제1 면 상에 배치된 상기 제1 전도형의 제1 에피택셜 층 - 상기 제1 에피택셜 층은 제1 두께를 갖고 적어도 제2 전도형의 제1 영역을 포함함 -;

상기 제2 전도형의 상기 제1 영역 위의 상기 제1 에피택셜 층 상에 형성된 제1 트랜지스터;

상기 제2 전도형의 상기 제1 영역 외부에서 상기 제1 에피택셜 층 상에 형성된 제2 트랜지스터; 및

상기 반도체 기판의 상기 제2 면 상에 배치된 상기 제1 전도형의 제2 에피택셜 층 - 상기 제2 에피택셜 층은 제2 두께를 갖고, 상기 제2 에피택셜 층에는 상기 제2 전도형의 어떠한 영역도 없음 -

을 포함하는, 집적 회로 디바이스.

#### 청구항 22

제21항에 있어서,

상기 제2 에피택셜 층은 그 위에 어떠한 트랜지스터도 형성되지 않는, 집적 회로 디바이스.

#### 청구항 23

제21항에 있어서,

상기 제1 전도형은 p-형이고, 상기 제2 전도형은 n-형이고, 상기 제1 영역은 n-웰인, 집적 회로 디바이스.

#### 청구항 24

제21항에 있어서,

상기 제1 전도형은 n-형이고, 상기 제2 전도형은 p-형이고, 상기 제1 영역은 p-웰인, 집적 회로 디바이스.

#### 청구항 25

제21항에 있어서,

상기 제1 에피택셜 층은 상기 제1 트랜지스터와 상기 제2 트랜지스터 사이에 배치된 격리 구조물을 포함하고, 상기 제2 에피택셜 층에는 어떠한 격리 구조물도 없는, 집적 회로 디바이스.

### 청구항 26

제25항에 있어서,

상기 격리 구조물은 STI(shallow trench isolation) 구조물인, 집적 회로 디바이스.

### 청구항 27

제21항에 있어서,

상기 반도체 기판은 상기 제1 에피택셜 층 및 제2 에피택셜 층에 비해 더 고농도로 도핑된, 집적 회로 디바이스.

### 청구항 28

제21항에 있어서,

상기 반도체 기판의 두께는  $500\text{ }\mu\text{m}$  내지  $800\text{ }\mu\text{m}$  사이의 범위 내에 있고 상기 제1 두께 및 제2 두께보다 큰, 집적 회로 디바이스.

### 청구항 29

제21항에 있어서,

상기 제1 두께와 제2 두께는 동일한, 집적 회로 디바이스.

### 청구항 30

제21항에 있어서,

상기 제1 두께와 상기 제2 두께는 상이한, 집적 회로 디바이스.

### 청구항 31

제30항에 있어서,

상기 제1 두께는  $20\text{ }\mu\text{m}$ 보다 크고,

상기 제2 두께는  $2\text{ }\mu\text{m}$  내지  $20\text{ }\mu\text{m}$  사이의 범위 내에 있는, 집적 회로 디바이스.

### 청구항 32

제21항에 있어서,

상기 제1 에피택셜 층은 상기 제2 전도형의 제2 영역 및 상기 제2 전도형의 제3 영역을 포함하고, 상기 제2 영역 및 제3 영역은 각각 상기 제2 트랜지스터에 대한 소스 및 드레인인, 집적 회로 디바이스.

### 청구항 33

제21항에 있어서,

상기 제1 트랜지스터 및 제2 트랜지스터는 상기 반도체 기판 및 상기 제2 에피택셜 층을 통과해 전기적으로 연결되지 않는, 집적 회로 디바이스.

### 청구항 34

제21항에 있어서,

상기 반도체 기판의 시트 비저항은 상기 제1 에피택셜 층 및 제2 에피택셜 층의 시트 비저항보다 낮은, 집적 회로 디바이스.

**청구항 35**

반도체 디바이스로서,

제1 두께, 제1 면, 및 상기 제1 면에 대향하는 제2 면을 갖는 p-형 반도체 기판;

상기 반도체 기판의 상기 제1 면 상에 배치되고 제2 두께를 갖는 제1 p-형 에피택셜 층 - 상기 제1 p-형 에피택셜 층은 제1 n-형 영역, 제2 n-형 영역, 및 제3 n-형 영역을 포함함 -;

상기 제1 p-형 에피택셜 층 상에 형성되고 상기 제1 n-형 영역에 적어도 부분적으로 형성된 제1 트랜지스터 - 상기 제1 n-형 영역은 n-웰이고, 상기 제1 트랜지스터는 PMOS 트랜지스터임 -;

상기 제1 p-형 에피택셜 층 위에 그리고 상기 제2 n-형 영역 및 제3 n-형 영역 상에 형성된 제2 트랜지스터 - 상기 제2 트랜지스터는 NMOS 트랜지스터이고 상기 제2 n-형 영역 및 제3 n-형 영역은 각각 상기 NMOS 트랜지스터에 대한 소스 및 드레인을 제공함 -;

상기 제1 트랜지스터와 제2 트랜지스터 사이의 상기 제1 p-형 에피택셜 층에 형성된 격리 구조물; 및

제3 두께를 갖고 상기 반도체 기판의 상기 제2 면 상에 배치된 제2 p-형 에피택셜 층 - 상기 제2 p-형 에피택셜 층은 제2 두께를 갖고, 상기 제2 p-형 에피택셜 층에는 어떠한 n-형 영역도 없음 -

을 포함하고,

상기 제1 트랜지스터 및 제2 트랜지스터는 상기 p-형 반도체 기판을 통과해 상기 제2 p-형 에피택셜 층에 전기적으로 연결되지 않는, 반도체 디바이스.

**청구항 36**

제35항에 있어서,

상기 p-형 반도체 기판은 상기 제1 p-형 에피택셜 층 및 제2 p-형 에피택셜 층 중 어느 하나보다 높은 도핑 농도를 갖는, 반도체 디바이스.

**청구항 37**

제35항에 있어서,

상기 제1 두께는  $500\text{ }\mu\text{m}$  내지  $800\text{ }\mu\text{m}$  사이의 범위 내에 있고 상기 제2 두께 및 제3 두께 중 어느 하나보다 큰, 반도체 디바이스.

**청구항 38**

제35항에 있어서,

상기 제2 두께와 상기 제3 두께는 동일한, 반도체 디바이스.

**청구항 39**

제35항에 있어서,

상기 제2 두께와 상기 제3 두께는 상이한, 반도체 디바이스.

**청구항 40**

제39항에 있어서,

상기 제2 두께는  $20\text{ }\mu\text{m}$ 보다 크고,

상기 제3 두께는  $2\text{ }\mu\text{m}$  내지  $20\text{ }\mu\text{m}$  사이의 범위 내에 있는, 반도체 디바이스.

**청구항 41**

집적 회로(IC) 디바이스로서,

제1 면 및 상기 제1 면에 대향하는 제2 면을 갖고, 제1 전도형을 갖는 반도체 기판;

상기 반도체 기판의 상기 제1 면 상에 배치된 상기 제1 전도형의 제1 에피택셜 층 - 상기 제1 에피택셜 층은 적어도 제2 전도형의 제1 영역을 포함함 -;

상기 제2 전도형의 상기 제1 영역에 적어도 부분적으로 형성된 제1 트랜지스터;

상기 제2 전도형의 상기 제1 영역 외부에서 상기 제1 에피택셜 층에 적어도 부분적으로 형성된 제2 트랜지스터; 및

상기 반도체 기판의 상기 제2 면 상에 배치된 상기 제1 전도형의 제2 에피택셜 층 - 상기 제2 에피택셜 층에는 상기 제2 전도형의 어떠한 영역도 없음 -

을 포함하는, 집적 회로 디바이스.

#### 청구항 42

집적 회로(IC) 디바이스로서,

제1 전도형과 제1 도편트 농도를 갖고, 상기 제1 전도형과 제2 상이한 도편트 농도를 갖는 제1 표면 반도체 층과 제2 표면 반도체 층 사이에 위치한 반도체 기판;

상기 제1 표면 반도체 층 내에 배치된, 제2 반대 전도형을 갖는 도핑 영역; 및

상기 도핑 영역을 둘러싸면서 접촉하는 유전체 격리 구조물을 포함하고,

상기 제2 표면 반도체 층에는 상기 제2 반대 전도형의 어떠한 영역도 없는, 집적 회로 디바이스.

#### 청구항 43

제42항에 있어서,

상기 도핑 영역 내에 또는 그 위에 형성된 트랜지스터를 더 포함하는, 집적 회로 디바이스.

#### 청구항 44

제42항에 있어서,

상기 도핑 영역 외부에서 상기 제1 표면 반도체 층 내에 또는 그 위에 형성된 트랜지스터를 더 포함하는, 집적 회로 디바이스.

#### 청구항 45

제42항에 있어서,

상기 제1 전도형은 p-형이고, 상기 제2 반대 전도형은 n-형이고, 상기 도핑 영역은 n-웰을 포함하는, 집적 회로 디바이스.

#### 청구항 46

제42항에 있어서,

상기 격리 구조물은 STI(shallow trench isolation) 구조물인, 집적 회로 디바이스.

#### 청구항 47

제42항에 있어서,

상기 반도체 기판은 상기 제1 표면 반도체 층 및 제2 표면 반도체 층에 비해 더 고농도로 도핑된, 집적 회로 디바이스.

#### 청구항 48

제42항에 있어서,

상기 제1 표면 반도체 층 및 상기 제2 표면 반도체 층은 동일한 두께들을 갖는, 집적 회로 디바이스.

### 청구항 49

제42항에 있어서,

상기 제1 표면 반도체 층은 상기 제2 표면 반도체 층의 제2 두께보다 큰 제1 두께를 갖는, 집적 회로 디바이스.

### 청구항 50

제42항에 있어서,

상기 제1 표면 반도체 층은  $3\text{ }\mu\text{m}$ 와  $20\text{ }\mu\text{m}$  사이의 범위 내의 제1 두께를 갖고, 상기 제2 표면 반도체 층은  $2\text{ }\mu\text{m}$ 와  $20\text{ }\mu\text{m}$  사이의 범위 내의 제2 두께를 갖는, 집적 회로 디바이스.

### 청구항 51

제42항에 있어서,

상기 제1 표면 반도체 층 및 제2 표면 반도체 층은 p-형 에피택셜 성장된 층들인, 집적 회로 디바이스.

### 청구항 52

반도체 디바이스로서,

제1 전도형을 갖고, 제1 두께, 제1 면, 및 상기 제1 면에 대향하는 제2 면을 갖는 반도체 기판;

상기 반도체 기판의 상기 제1 면 상에 배치된 상기 제1 전도형을 갖는 제1 에피택셜 층 - 상기 제1 에피택셜 층은 제1 표면을 갖고, 제2 반대 전도형을 갖는 제1 도핑 영역, 제2 도핑 영역, 및 제3 도핑 영역을 포함함 -;

상기 반도체 기판의 상기 제2 면 상에 배치된 상기 제1 전도형을 갖는 제2 에피택셜 층 - 상기 제2 에피택셜 층은 상기 제1 표면에 대향하는 제2 표면을 가짐 -;

상기 제1 도핑 영역 내에 또는 그 위에 형성된 제1 트랜지스터;

상기 제1 도핑 영역 외부에서 상기 제1 에피택셜 층 내에 적어도 부분적으로 형성된 제2 트랜지스터 - 상기 제2 트랜지스터는 상기 제2 도핑 영역 및 제3 도핑 영역을 포함함 -; 및

상기 제1 트랜지스터와 상기 제2 트랜지스터 사이에서 상기 제1 에피택셜 층에 형성된 격리 구조물을 포함하고,

상기 제2 에피택셜 층은 상기 제2 표면 전체에 걸쳐 균일한 동질의 표면을 갖는, 반도체 디바이스.

### 청구항 53

제52항에 있어서,

상기 반도체 기판은 고농도로 도핑되고, 상기 제1 에피택셜 층 및 제2 에피택셜 층은 저농도로 도핑되는, 반도체 디바이스.

### 청구항 54

제52항에 있어서,

상기 반도체 기판은 상기 제1 에피택셜 층의 제2 두께 및 상기 제2 에피택셜 층의 제3 두께보다 큰  $500\text{ }\mu\text{m}$  내지  $800\text{ }\mu\text{m}$  사이의 범위인 제1 두께를 갖는, 반도체 디바이스.

### 청구항 55

제54항에 있어서,

상기 제2 두께와 상기 제3 두께는 동일한, 반도체 디바이스.

### 청구항 56

제54항에 있어서,

상기 제2 두께와 상기 제3 두께는 상이한, 반도체 디바이스.

**청구항 57**

제54항에 있어서,

상기 제2 두께는  $3\text{ }\mu\text{m}$ 와  $20\text{ }\mu\text{m}$  사이의 범위 내이고,

상기 제3 두께는  $2\text{ }\mu\text{m}$ 와  $20\text{ }\mu\text{m}$  사이의 범위 내인, 반도체 디바이스.

**청구항 58**

제52항에 있어서,

상기 반도체 기판, 제1 에피택셜 층, 및 제2 에피택셜 층은 p-형이고, 상기 제1 도핑 영역, 제2 도핑 영역, 및 제3 도핑 영역은 n-형이고, 상기 반도체 기판은 제1 p-형 에피택셜 층 및 제2 p-형 에피택셜 층보다 높은 도핑 농도를 갖는, 반도체 디바이스.

**청구항 59**

제52항에 있어서,

상기 제1 도핑 영역은 저농도로 도핑되고, 상기 제2 도핑 영역 및 제3 도핑 영역은 고농도로 도핑되는, 반도체 디바이스.

**청구항 60**

제52항에 있어서,

상기 제1 트랜지스터는 PMOS 트랜지스터이고, 상기 제2 트랜지스터는 NMOS 트랜지스터인, 반도체 디바이스.

**발명의 설명****기술 분야****배경 기술**

[0001]

방사선 경화(radiation hardened) 및 다른 고 신뢰성 전자 회로들은 시스템들 및 회로들이 방사선, 전자기적 간섭(EMI) 또는 다른 불리한 전기적 노이즈 조건들에 노출되는 다양한 응용들에 필요하다. 예시적인 응용들은 위성들 및 기타 우주선, 항공기, X-선 장비와 같은 의료 디바이스들, 원자력 발전소들에 사용되는 회로들, 프로세서 코어들, 및 다른 민감한 디지털 회로들을 포함한다. 이러한 응용들에서, 바이폴라 트랜지스터들로서 동작하는 웨들 및 도핑된 영역들로 인해 금속 산화물 반도체(MOS) 회로들에서 방사선이 래치업(latchup)을 일으킬 수 있다. 이러한 래치업 상태 동안, 이러한 기생 바이폴라 트랜지스터들은 MOS 회로 구성 요소들 아래의 전류 흐름에 의해 턴 온(turned on)될 수 있는데, 이는 집적 회로(IC) 내의 논리 회로들의 동작을 간섭하고 때때로 IC를 영구적으로 손상시킬 수 있는 잠재적으로 큰 전류들을 야기할 수 있다. 일반적으로, 래치업은 MOSFET 회로의 파워 서플라이(power supply) 레일들 사이에 낮은 임피던스 경로의 부주의한 생성을 수반하고, 서로 옆에 쌓여있는 PNP 및 NPN 트랜지스터로서 동작하는 기생 PNPN(실리콘 제어된 정류기 또는 SCR) 구조를 트리거한다. 래치업 동안 기생 바이폴라 트랜지스터들 중 하나가 전도할 때, 다른 하나도 전도하며 구조가 일부 영이 아닌 전류 흐름으로 순방향 바이어스로 유지되는 한 서로를 포화 상태로 유지한다. 단일 이벤트 래치업(SEL)은 일반적으로 우주 광선들 또는 태양 플레이들로부터의 중이온들 또는 양성자들로부터의 단일 이벤트 업셋으로 인한 래치업이다. 다양한 집적 회로 응용들은 이러한 방사선 환경들에서 동작하는 회로를 필요로 하며, MOS 회로 래치업은 재시작 또는 전력 순환을 필요로 하는 프로세서 회로들의 동결로 이어질 수 있다. 따라서, 개선된 반도체 디바이스들 및 제조 기술들은 디지털 회로 래치업 문제들을 해결하기 위해 방사선 노출을 수반하는 회로 응용들에 필요하다.

**발명의 내용**

[0002]

반도체 웨이퍼들 및 집적 회로들을 제조하기 위한 반도체 디바이스들 및 제조 방법들의 설명된 예들에서, 방법

은 제1 전도형의 반도체 기판의 제1 면 상에 제1 전도형의 제1 에피택셜 반도체 층을 형성하는 단계, 및 반도체 기판의 제2 면 상에 제1 전도형의 제2 에피택셜 반도체 층을 형성하는 단계를 포함한다. 설명된 반도체 디바이스의 예들은 제1 전도형의 반도체 기판, 반도체 기판의 제1 면 상에 형성된 제1 전도형의 제1 에피택셜 반도체 층, 및 반도체 기판의 제2 면 상에 형성된 제1 전도형의 제2 에피택셜 반도체 층을 포함한다. 디바이스는 트랜지스터들을 제1 에피택셜 반도체 층 상에 적어도 부분적으로 형성함으로써 집적 회로를 제조하는 데 사용될 수 있다. 일부 예들에서, 질화물 또는 산화물 보호 층은 제2 에피택셜 층을 형성하기 전에 제1 에피택셜 반도체 층의 상부 면 상에 형성되고, 보호 층은 제2 에피택셜 층이 형성된 후에 제거된다. 일부 예들에서, 제1 및 제2 에피택셜 반도체 층들은 반도체 기판보다 더 저농도로 도핑된다.

### 도면의 간단한 설명

[0003]

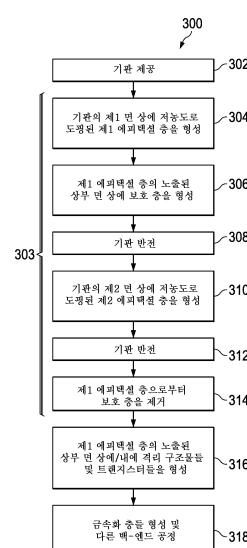

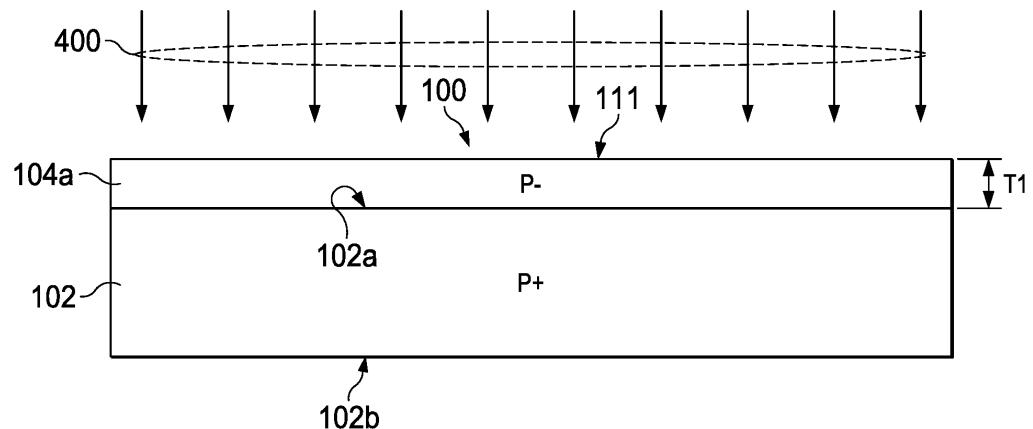

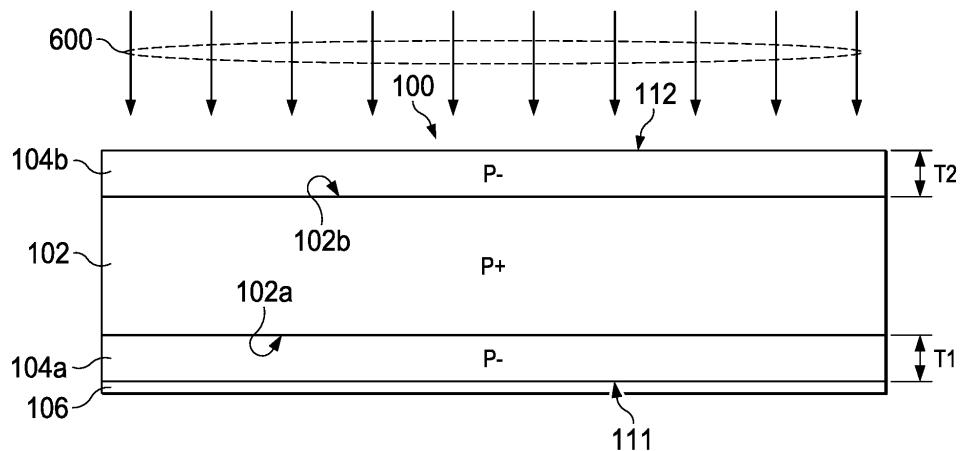

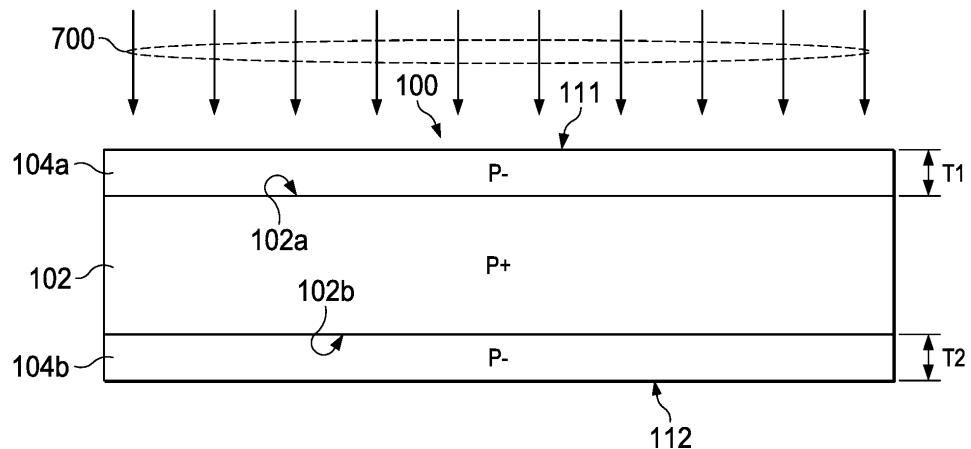

도 1은 더 고농도로 도핑된 p-형 기판의 반대의 상부 및 하부 면들 상에 제1 및 제2 저농도로 도핑된 p-형 에피택셜 층들을 갖는 반도체 웨이퍼 디바이스의 사시도이다.

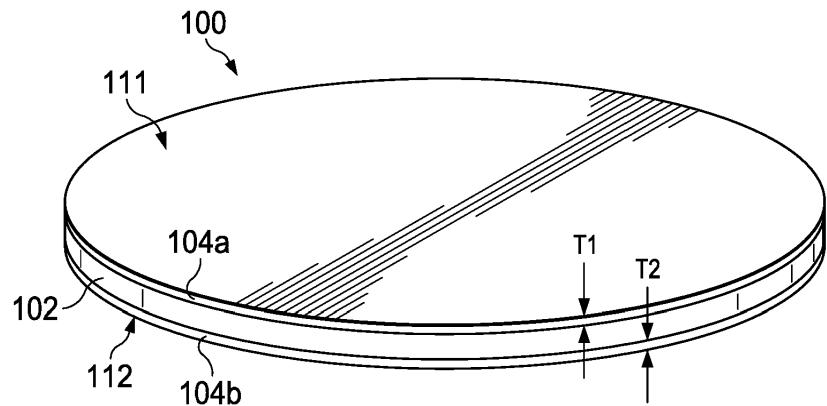

도 2는 도 1의 반도체 웨이퍼를 사용하여 제조된 집적 회로의 부분 측단면 정면도이다.

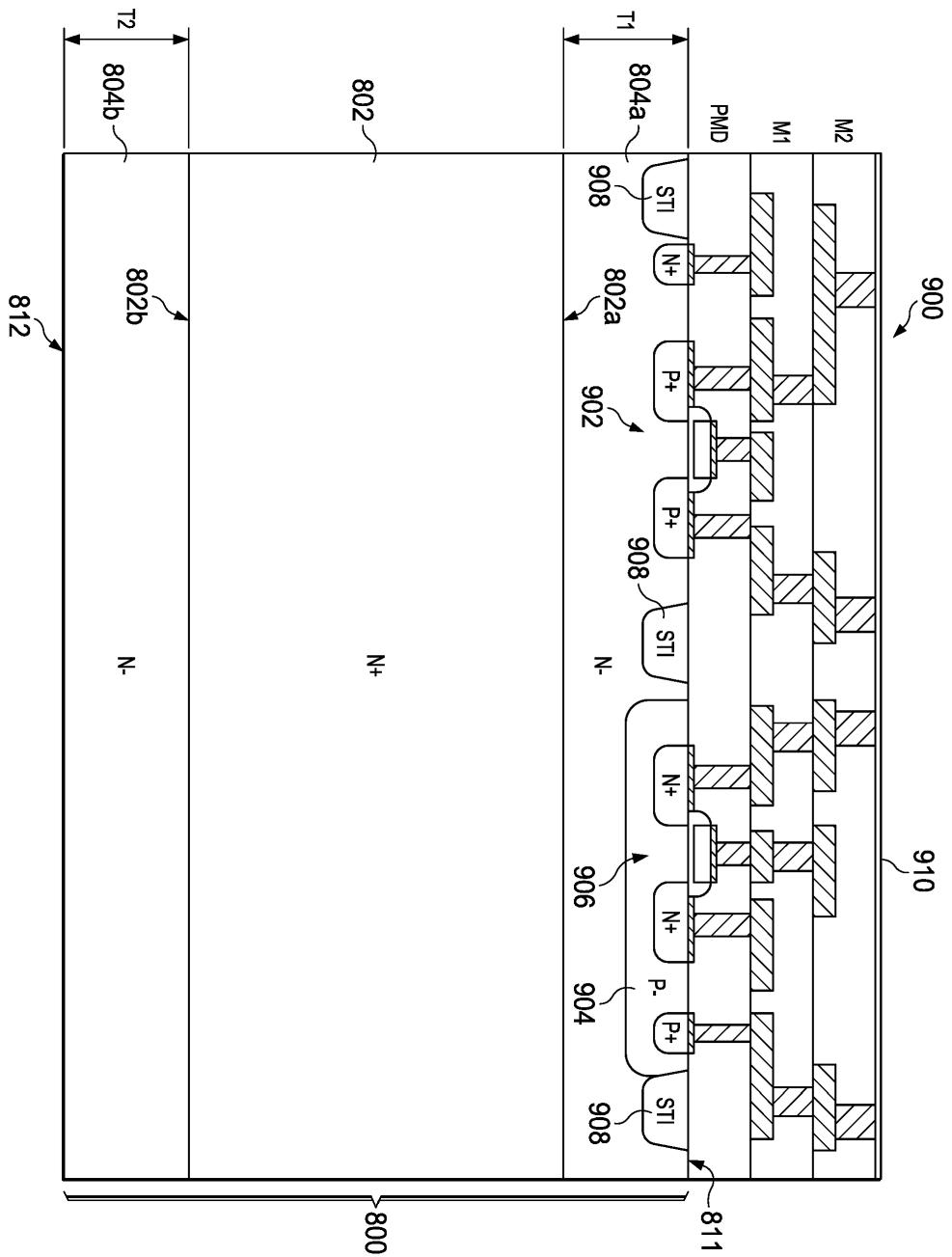

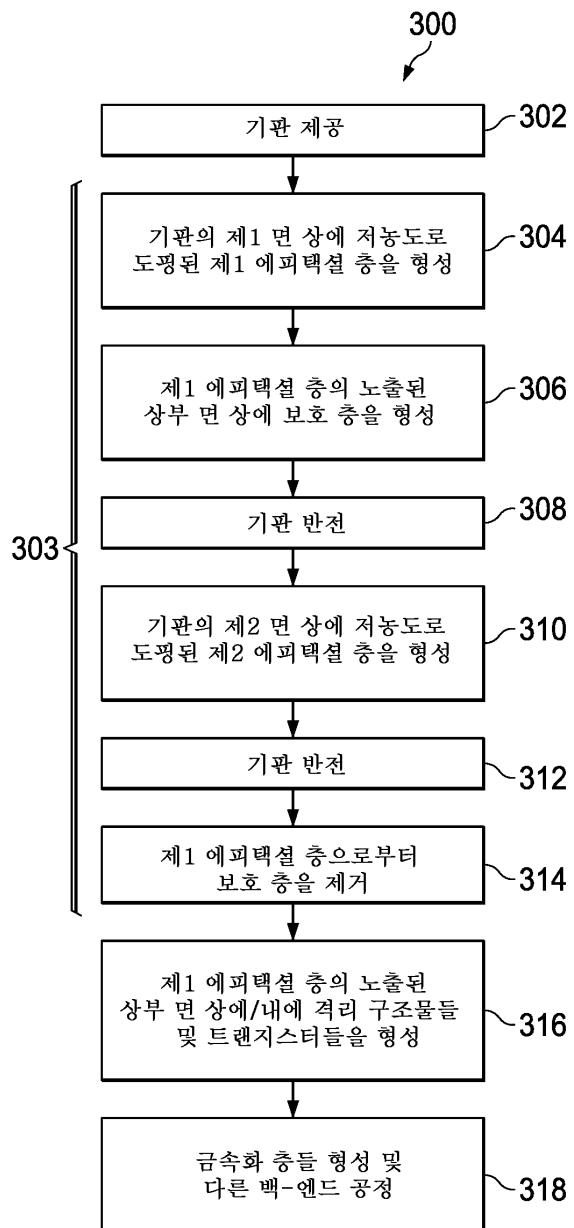

도 3은 반도체 웨이퍼를 제조하고 집적 회로를 제조하는 방법의 흐름도이다.

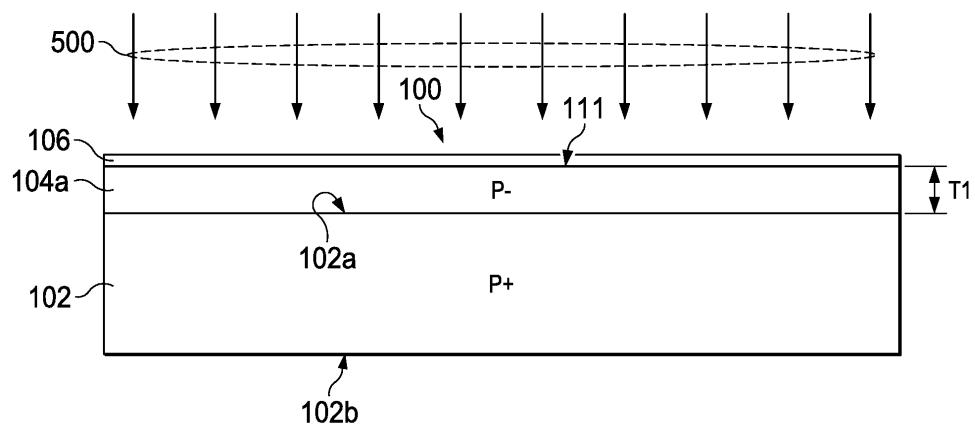

도 4 내지 도 7은 도 3의 방법에 따른 제조의 다양한 단계들에서의 도 1의 반도체 웨이퍼의 부분 측단면 정면도들이다.

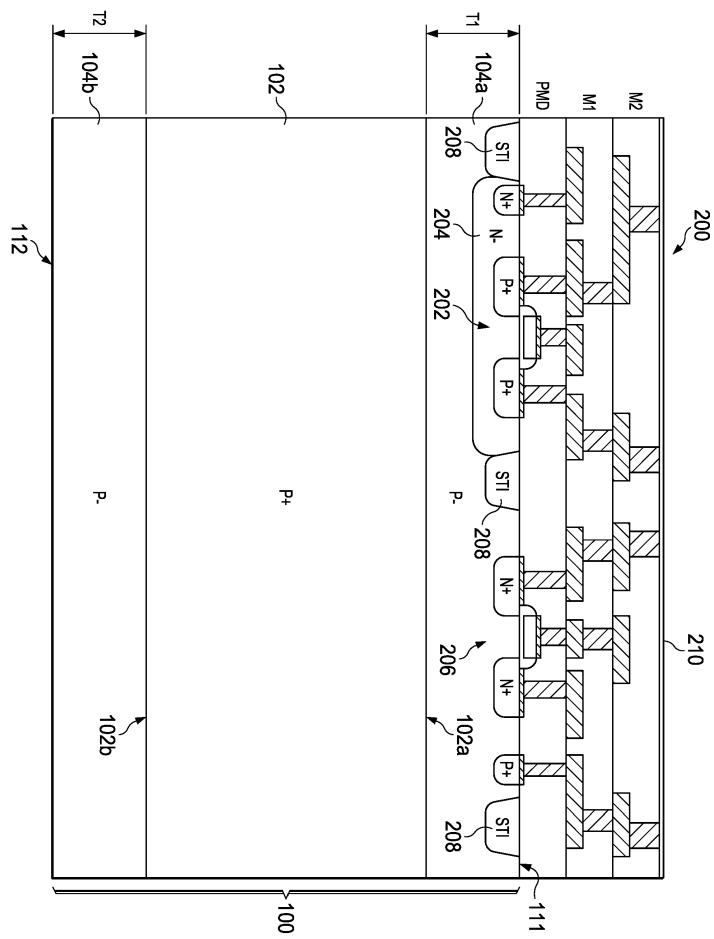

도 8은 더 고농도로 도핑된 n-형 기판의 반대의 상부 및 하부 면들 상에 제1 및 제2 저농도로 도핑된 n-형 에피택셜 층들을 갖는 반도체 웨이퍼의 사시도이다.

도 9는 도 8의 반도체 웨이퍼를 사용하여 제조된 집적 회로의 부분 측단면 정면도이다.

### 발명을 실시하기 위한 구체적인 내용

[0004]

도면들에서, 전체에 걸쳐서 유사한 참조 번호는 유사한 구성 요소를 지칭하며, 다양한 특징들은 필연적으로 실제 축척 대로 그려진 것은 아니다.

[0005]

도 1은 더 고농도로 도핑된 p-형 반도체 기판(102)의 반대의 상부 및 하부 면들 상에 각각 형성된, 제1 및 제2의 저농도로 도핑된 p-형 에피택셜 반도체 재료 층들(104a 및 104b)을 포함하는 반도체 웨이퍼 또는 디바이스(100)를 도시한다. 하나의 예시에서, 기판(102)은 집적 회로 제품들을 만들기 위한 반도체 제조 공정에 적합한 두께를 갖는 벌크 실리콘 재료고, 에피택셜 층들(104)은 에피택셜 실리콘 재료다. 다른 예들에서, 서로 다른 반도체 재료들이 기판(102) 및 에피택셜 층들(104)에 사용될 수 있으며, 전형적인 실시예들은 실리콘으로 제한되지 않는다. 하나의 예시에서, 기판(102)의 두께는 500 내지 800 $\mu\text{m}$ 의 범위 내에 있다. 하나의 예시에서 디바이스(100)는 일반적으로 150mm, 200mm, 300mm, 450mm 직경 등과 같은, 반도체 제조 공정들에 적합한 직경을 갖는 원통형이다. 제1 에피택셜 층(104a)은 노출된 상부 면(111)을 포함하며 두께(T1)를 갖는다. 하나의 예시에서, 두께(T1)는 3.0 $\mu\text{m}$  이상이다. 특정 예들에서, 두께(T1)는 3.0 내지 20 $\mu\text{m}$ 이다. 다른 예들에서, 20 $\mu\text{m}$ 보다 큰 두께(T1)가 사용될 수 있다. 특정 예들에서 두께(T1)는 트랜지스터들 및 다른 회로가 제1 에피택셜 층(104a) 상에 또는 내에 형성되도록, 주어진 회로 응용의 CMOS 공정 요건들에 의해 설정된다. 실제로, 에피택셜 층 두께(T1)는 주어진 집적 회로 설계에 대한 CMOS 트랜지스터 임계 전압(VT) 및 다른 파라미터들을 수용하도록 선택된다. 제2 에피택셜 층(104b)은 두께(T2)를 갖고, 노출된 하부 면(112)을 포함한다. 하나의 예시에서, 제2 에피택셜 층 두께(T2)는 두께(T1)와 대략 동일할 수 있다. 그러나, 두께(T2)는 CMOS 공정 요건들에 기초하여 결정될 필요는 없다. 하나의 예시에서, 제2 에피택셜 층(104b)의 두께(T2)는 2.0 내지 20 $\mu\text{m}$ 이다. 특정 예들에서, T2는 제조 중의 산화 공정 단계들 동안의 에피택셜 재료 소비를 포함하여, 집적 회로의 제조 중의 디바이스(100)의 열공정 동안의 오토 도핑을 완화시키기 위해 적절한 값으로 설정된다.

[0006]

도 1의 디바이스(100)는 고 신뢰성 및/또는 방사선 경화 집적 회로 디바이스들의 제조에서 시작 웨이퍼로서 사용하기에 특히 적합하다. 이와 관련하여, 정전기 방전(ESD), 과도적 전압, 빛 및 이온화하는 방사선에 의해 유도된 과도 전류들은 벌크 실리콘 웨이퍼들에서 형성된 CMOS 집적 회로들에서 기생 바이폴라 트랜지스터들 및 실리콘 제어된 정류기들(SCRs)을 트리거할 수 있다. 이는 래치업, 및 바이폴라 트랜지스터 이득 저하와 같은 다른 문제들로 이어진다. 특정 경우들에서의 래치업은 충분한 기생 바이폴라 트랜지스터 이득을 갖는 P+/n웰 접합의 순방향 바이어싱을 수반하고, 이는 기생 SCR의 래치된 상태를 야기하고, 전압 서플라이(voltage supply)와 기준 전압 노드들 사이에 잠재적으로 큰 전류 흐름으로 이어진다. 이러한 래치업 문제들은 특징부 크기들이 계

속 줄어들면서(90nm에서 28nm 등과 같이) 더 두드러진다. CMOS 래치업 메카니즘들은 더 낮은 비저항 시작 기판 위에 상대적으로 높은 비저항 에피택셜 층의 형성으로 어느 정도 완화될 수 있다. 트랜지스터들 및 다른 구성 요소들은 더 저농도로 도핑된, 더 높은 시트 비저항 P- 에피택셜 층 내에 형성되므로, 기생 바이폴라 및 SCR 디바이스들은 훨씬 더 낮은 이득을 가지며 래치업을 유발할 가능성이 적다. 하나의 예시에서, P+/P- 에피택셜 기판들은 항공 응용들에서의 우주 광선들(예를 들어, 지상 중성자 및 양성자 반응들)에 의해 야기되는 래치업에 대한 감도 및/또는 우주 응용들에서의 중이온들에 대한 감도를 완화시키기 위해 집적 회로들을 제조하는 데 사용된다.

[0007] 그러나, P+/P- 웨이퍼들의 사용은 열공정 동안의 오토 도핑의 문제점들로 이어진다. 예를 들어, 붕소 또는 다른 p-형 도편트들은 노 어닐링, 레이저 어닐링, 금속 열공정(RTP), 또는 집적 회로 제조 공정의 다른 열공정 단계들 동안 고농도로 도핑된 P+ 실리콘으로부터 인접한 웨이퍼들의 저농도로 도핑된 P- 에피택셜 층들로 이동할 수 있다. 오토 도핑을 제어하기 위해, P+/P- 웨이퍼들은 오토 도핑을 완화시키는 데 사용되는, 저온 산화(LTO) 질화물 층과 같은 후면 캐핑 층(backside capping layer)을 종종 포함한다. 그러나, P+/P- 시작 웨이퍼들은 고도로 및 저농도로 도핑된 층들 사이의 경계면에서의 열 응력에 의해 야기되는 뒤틀림(warping)의 대상이다. 이러한 뒤틀림 문제는 더 큰 웨이퍼 크기들에 대해 더 두드러지고, 오토 도핑 보호 층의 존재는 뒤틀림을 악화시킬 수 있다. 또한, 플라즈마 도구들 및 임플란트 도구들을 사용하는 제조 공정 동안에 LTO 캐핑 층에 전하가 축적될 수 있다.

[0008] 도 1의 디바이스(100) 내의 시작 기판(102)의 반대 면들 상의 제1 및 제2 에피택셜 층들(104)의 사용은 고 신뢰성 및/또는 방사선 경화 집적 회로 디바이스들의 제조 및 구성을 용이하게 하면서, 오토 도핑 및 뒤틀림 모두를 완화 또는 회피한다. 또한, 디바이스(100)는 또한 LTO 질화물 오토 도핑 캡 층들의 존재에 의해 이전에 야기된 아크 문제들 없이 표준 처리 도구들을 사용하여 제조를 용이하게 한다. 하나의 예시에서 시작 기판(102)은 상대적으로 낮은 시트 비저항을 갖는 벌크 실리콘이고, 에피택셜 층들(104a)은 상대적으로 더 높은 시트 비저항을 갖는다. 실제로, 디바이스(100)의 시트 비저항은 일반적으로 상부 및 하부 면들(111 및 112) 사이의 프로파일에 따라 변한다. 예를 들어, 하나의 예시에서 상부 및 하부 면들(111 및 112)에서의 에피택셜 층들(104a 및 104b)의 시트 비저항은 약 8-12 ohm-cm이고, 기판(102)의 제1 및 제2 면들과 대응하는 에피택셜 층들(104) 사이의 경계면들 근처의 시트 비저항은 약 1 ohm-cm이고, 기판(102)의 중간 근처의 시트 비저항은 0.025ohm-cm 정도이다. 전술한 바와 같이, 제1 에피택셜 층(104a)의 두께(T1)는 제1 에피택셜 층(104a) 상에 또는 내에 형성된 트랜지스터들 및 다른 구성 요소들의 임계 전압 및 다른 성능 파라미터들을 수용하도록 맞출 수 있다. 제2 에피택셜 층(104b)은 열공정 동안 고농도로 도핑된 기판(102)으로부터의 붕소 또는 다른 도편트들의 외부 이동에 대한 장벽으로서 동작하여, 집적 회로 제조 동안 오토 도핑을 완화시킨다. 게다가, 제2 에피택셜 층(104b)은 제1 에피택셜 층(104a)의 반대 면 상에서 기판(102)에 대한 제2 경계면을 제공함으로써 공정 중(in-process) 뒤틀림을 방지한다.

[0009] 또한 도 2를 참조하면, 도 1의 디바이스(100)를 사용하여 제조된, 집적 회로(IC)(200)가 도시되어 있다. IC(200)는 평탄한 제1(예를 들어, 상부) 면(102a) 및 평탄한 반대 제2(예를 들어, 하부) 면(102b)을 갖는 제1 전도형(예를 들어, p-형)의 반도체 기판(102)을 포함한다. 이 예시에서 또한 p-형인 제1 에피택셜 반도체 층(104a)은 기판(102)의 제1 면(102a) 상에 형성되고, p-형 제2 에피택셜 반도체 층(104b)은 기판(102)의 제2 면(102b) 상에 형성된다. IC(200)는 또한 제1 에피택셜 반도체 층(104a) 상에 적어도 부분적으로 형성된 하나 이상의 트랜지스터(202 및 206)를 포함한다. 많은 그러한 트랜지스터들 및 다른 전자 구성요소들(도시되지 않음)은 표준 제조 기술들을 사용하여 에피택셜 층(104a) 상에 적어도 부분적으로 형성될 수 있다. 도 2에서, PMOS 트랜지스터(202)는 저농도로 도핑된(예를 들어, N-) n-웰(204) 내에 형성된다. 상대적으로 고농도로 도핑된 P+ 소스/드레인 영역들은 채널 영역의 반대 측들 상에서 n-웰(204) 내에 형성되고, 게이트 구조물은 PMOS 채널 영역 위에 적어도 부분적으로 형성된다. 이 예시에서, N+ 웰 접촉부가 포함되고, PMOS 트랜지스터(202)는 하나 이상의 격리 구조물(208)(이 예시에서는 얇은 트렌치 격리 또는 STI 구조물들)에 의해 다른 주변 구성 요소들로부터 격리된다. 도 2의 제2 트랜지스터(206)는 저농도로 도핑된 P- 에피택셜 층 재료(104a) 내에 형성된 N+ 소스/드레인들 및 N+ 소스/드레인들 사이의 P- 채널 영역 위에 형성된 게이트 구조물을 포함하는 NMOS 트랜지스터이다. 이 예시에서 P+ 기판 접촉부는 또한 P+ 기판(102)에 전기 전도성을 제공하기 위해 NMOS 트랜지스터(206)에 인접하여 형성된다.

[0010] 트랜지스터 소스/드레인 영역들이 제1 에피택셜 층(104a)의 상부 면(111) 내에 형성되고, 게이트 구조물들 및 소스/드레인 접촉부들이 상부 면(111) 위에 형성되면, 트랜지스터들(202, 206)은 제1 에피택셜 반도체 층(104a) 상에 적어도 부분적으로 형성된다. 도 2의 IC(200)는 또한 상부 면(111) 위에 형성된 프리-금속 유전체(pre-

metal dielectric)(PMD) 구조물 층을 포함한다. PMD 층은 소스/드레인 영역들, 게이트들 및 웨/기판 접촉부들에 전기적 접촉들을 형성하는 하나 이상의 전도성 접촉 구조물을 포함한다. IC(200)는 하나 이상의 금속화 층(M1 및 M2) 및 상부 패시베이션 층(210)을 더 포함한다. 금속화 층(M1, M2) 각각은 트랜지스터들(202, 206)에 의해 형성된 전기 회로의 다양한 구성 요소들 및 구성 요소 단자들 및 IC(200)의 다른 전기 구성 요소들을 상호 접속하기 위한 층간 유전체(ILD) 재료 및 전도성 접촉 구조물들을 포함한다. 저농도로 도핑된 P- 에피택셜 층(104a)의 사용은 트랜지스터들(202, 206)의 방사선-유도 래치업 및 방사선 노출과 관련된 다른 문제점들을 유리하게 완화시킨다. 또한, 제2 또는 더 낮은 에피택셜 층(104b)은 제조 동안 오토 도핑을 완화 또는 방지하기 위한 장벽을 유리하게 제공하고, 또한 상부 제1 에피택셜 층(104a)의 존재와 연관된 임의의 뒤틀림 효과들에 대항한다. 더욱이, 제2 에피택셜 층(104b)은 플라즈마 또는 주입 공정 단계들 동안 전하 축적으로부터 어려움을 겪지 않으므로, 이전에 오토 도핑 방지(예를 들어, 질화물) 층들과 관련된 아크 문제들의 대상이 아니다.

[0011]

도 3 내지 도 7을 참조하면, 도 3은 도 1에 도시된 바와 같은 시작 웨이퍼 또는 디바이스(100)를 형성하는 공정 단계들(303), 및 도 2의 IC(200)와 같은 접적 회로를 형성하는 후속 공정 단계들을 포함하는, 반도체 디바이스를 제조하는 방법(300)을 도시한다. 도 4 내지 도 7은 도 3의 방법들(300 및 303)에 따른 제조의 다양한 단계들에서의 도 1의 반도체 웨이퍼 디바이스(100)를 도시한다. 방법들(300, 303)은 도 1 및 도 2에 도시된 P-/P+/-P- 디바이스들(100)과 연관하여 사용될 수 있고, 도 8 및 도 9와 관련하여 이하에 설명되고 도시된 바와 같은 N-/N+/N- 디바이스들과 함께 사용될 수 있다. 방법(300)은 시작 웨이퍼 또는 기판(102)과 함께 단계(302)에서 시작한다. 임의의 적합한 반도체 기판(102)이 방법(300)에서 사용될 수 있다. 하나의 예시에서 시작 기판은 제1 전도형(예를 들어, 하나의 예시에서 p-형)의 톱질되고 양면 연마된 실리콘 웨이퍼이다. 시작 기판(102)은 임의의 적합한 치수들(예를 들어, 150mm, 200mm, 300mm 또는 450mm 직경, 500 내지 800 $\mu$ m 두께를 갖는 원통형 웨이퍼)을 가질 수 있다.

[0012]

방법(300)은 단계(304)에서 기판의 제1 면(예를 들어, 전술한 도 2의 제1 면(102a)) 상에 제1 전도형의 제1 에피택셜 실리콘 층(104a)을 형성하는 것을 포함하는, 단계(303)에서의 디바이스(예를 들어, 전술한 디바이스(100))의 제조를 포함한다. 도 4는 단계(304)에서의 공정 예를 도시하며, 에피택셜 성장 공정 단계(400)가 P+ 기판(102)의 제1 면(102a) 상에 제1 두께(T1)로 p-형 제1 에피택셜 층(104a)을 형성하는 데 사용된다. 기판(102)의 제1 면(102a)의 결정 배향을 일반적으로 모방하는 결정 구조를 갖는 저농도로 도핑된 p-형 실리콘 재료를 제공하기 위해 임의의 적합한 에피택셜 성장 공정(400)이 단계(304)에서 사용될 수 있다.

[0013]

특정 예시들에서, 단계(306)에서 임의적(optional) 보호 층이 제1 에피택셜 층(104a)의 노출된 상부 면(111) 상에 형성된다. 하나의 구현에서, 제1 에피택셜 반도체 층(104a)의 상부 면(111) 상에 400 내지 2000Å와 같이, 약 400Å 이상의 두께로 산화물 및/또는 질화물 보호 층(106)을 형성하기 위하여 산화 공정(500)이 도 5에서 사용된다. 기판은 단계(308)에서 뒤집히거나 반전되어, 기판(102)의 노출된 제2 면(102a)을 구조물의 상부에 남긴다. 실제로, 도 2의 완성된 IC 디바이스(200)에서 트랜지스터들 및 다른 전자 구성 요소들의 후속 형성을 위해 설계된 제1 에피택셜 층(104a)과 함께, 보호 층(106)은 후속 제조 공정 동안 제1 에피택셜 층(104a)의 상부 면(111)에 대한 보호를 제공한다. 하나의 예시에서, 제2 에피택셜 실리콘 층(104b)을 형성하기 전에(310) 단계(306)에서 제1 에피택셜 실리콘 층(104a)의 상부 면(111) 상에 질화물 재료가 형성된다. 다른 예시에서, 제2 에피택셜 실리콘 층(104b)을 형성하기 전에(310) 단계(306)에서 제1 에피택셜 실리콘 층(104a)의 상부 면(111) 상에 산화물 재료가 형성된다.

[0014]

방법(303)은 단계(310)에서 실리콘 기판(102)의 제2 면(102b) 상에 제2 저농도로 도핑된 p-형 에피택셜 실리콘 층(104b)을 형성하는 것을 더 포함한다. 도 6에 도시된 바와 같이, 기판(102)의 제2 면(102b) 상에 두께(T2)의 제2 에피택셜 층(104b)을 형성하기 위해 제2 에피택셜 성장 공정(600)이 수행된다. 이것은 도 6에 도시된 바와 같이 제1 에피택셜 층(104a)의 상부 면(111) 위에 형성된 보호 층(106)이 있는 구조물을 남긴다. 제2 에피택셜 층 두께(T2)는 방법들(300, 303)의 모든 구현들에 대한 엄격한 요구 조건은 아니지만, 제1 에피택셜 층(104a)의 두께(T1)와 동일하거나 유사할 수 있다. 게다가, 제2 저농도로 도핑된 에피택셜 층(104b)을 형성하기 위해 임의의 적합한 제2 에피택셜 성장 공정(600)이 단계(310)에서 사용될 수 있다.

[0015]

단계(312)에서, 구조물은 다시 뒤집히거나 반전되며, 이전에 형성된 임의의 보호 층(106)은 단계(314)에서 제거된다. 도 7은 제1 에피택셜 층(104a)의 상부 면(111)이 노출된 채로 남긴, 보호 층(106)을 제거하는 데 사용되는 예시적인 예칭 또는 재료 제거 공정(700)을 도시한다. 도 3의 단계(303)에서의 공정은 p-형 반도체 재료들(102, 104)이 사용되는 도 1에서 도시된 디바이스(100)를 산출한다. 다른 예에서, 도 3의 공정 단계들(303)은 N+ 기판(802) 및 제1 및 제2 저농도로 도핑된 N- 에피택셜 층들(804a 및 804b)을 포함하는, 도 8에 도시된 디바

이스(802)를 제조하는 데 사용될 수 있다.

[0016] 하나의 예시에서의 IC 제조 방법(300)은 제1 에피택셜 실리콘 층(104a)으로부터 보호 층(106)을 제거한 후에 단계(316)에서 제1 에피택셜 실리콘 층(104a) 상에 적어도 부분적으로 복수의 트랜지스터들(202, 206)을 형성하는 단계를 더 포함한다. 하나 이상의 금속화 층 및 다른 백-앤드 공정이 전술한 도 2의 IC(200)와 같은 집적 회로 디바이스를 제공하기 위해 도 3의 단계(318)에서 수행된다.

[0017] 도 8 및 도 9를 또한 참조하면, 도 8은 N+ 기판(802), 기판(802)의 제1 면 상에 형성된 제1 저농도로 도핑된 N- 에피택셜 층(804a), 및 기판(802)의 반대의 제2 면 상에 형성된 제2 저농도로 도핑된 N- 에피택셜 층(804b)을 포함하는, N-/N+/N- 웨이퍼 또는 디바이스(800)를 도시한다. 도 8 및 도 9의 디바이스(800) 및 IC(900)는 p-형 도편트들 및 재료들이 n-형 도편트들 및 재료들로 대체되며, 그 반대도 마찬가지인 도 3의 공정들(300 및 303)을 사용하여 제조될 수 있다. 도 1의 P-/P+/P- 디바이스(100)와 관련하여 전술한 바와 같이, 디바이스(800)는 제1 및 제2 에피택셜 층들(804)이 공정 동안의 뒤틀림에 대한 상쇄, 및 공정 동안의 오토 도핑의 완화를 제공하는, 고 신뢰성 및/또는 방사선 경화 IC를 제조하기 위한 시작 웨이퍼로서 사용될 수 있다. 게다가, 제1 에피택셜 층(804a)은 생성된 IC에 대한 래치업 및 다른 방사선-기반 효과들을 완화시키기 위해 상대적으로 저농도로 도핑된 반도체 재료 내의 트랜지스터들 및 다른 전자 구성 요소들을 제조하는 데 사용될 수 있다. 도 3의 처리 단계들(303)은 기판(802) 및 에피택셜 층들(804)에 사용된 재료들이 n-형 도핑된 것인(예를 들어, 인 또는 다른 적절한 n- 도편트들을 사용하여), 도 8의 디바이스(800)를 제조하는 데 사용될 수 있다.

[0018] 도 9는 기판(802), 기판(802)의 제1 면(802a) 상에 형성된 제1 에피택셜 층(804a) 및 기판(802)의 반대의 제2 면(802b) 상의 제2 에피택셜 층(804b)을 포함하는 도 8의 디바이스(800)를 사용하여 제조된 예시적인 IC(900)를 도시한다. 이 예에서, 저농도로 도핑된 N- 에피택셜 층(804a) 내에 형성된 P+ 소스/드레인들을 포함하여, PMOS 트랜지스터(902)는 제1 에피택셜 반도체 층(804a)의 상부 면(811) 상에 형성된다. 이 예는 또한 한 쌍의 STI 구조물들(908) 사이의 PMOS 트랜지스터(902)로 형성된 N+ 기판 접촉부를 포함한다. IC(900)는 또한 NMOS 트랜지스터(906) 및 P+ 웨이퍼에 대한 접촉부가 제1 에피택셜 층(804a) 내에 형성된 저농도로 도핑된 P- p-웨이퍼(904)를 포함한다. 트랜지스터들(902 및 906)은 또한 대응하는 채널 영역들 위에 가로놓인 게이트 구조물들, PMD 구조물 층, 하나 이상의 금속화 층(M1 및 M2) 및 상부 패시베이션 층(910)을 포함한다.

[0019] 이것이 우리 기술이 하는 것이며, 이는 대전된 입자들, 중성자들, ESD 스트라이크들 및 광자(빛) 주입과 같은 주입된 에너지 소스들로부터 SEL을 제거한다. 대부분의 공정 장비는 고도로 도핑된 P+ 기판 상에 보호 후면 코팅을 필요로 한다. 이는 P+ 블록이 P+ 웨이퍼의 후면에서 외부로 확산되는 것을 방지하고 P+ 기판 바로 뒤의 장비 또는 웨이퍼에 대한 오염을 완화한다(오토 도핑 방지). P+ 기판에 단일 에피택셜 층을 사용하는 솔루션들은 보호 후면 층(들)을 필요로 하며 이 층들은 항상 비전도성이고, 이는 웨이퍼 공정 동안 웨이퍼가 충전되는 것을 야기하여 아크(arcing)를 유발할 수 있다. 설명된 예들은 도핑된 제2 에피택셜 층(104b, 804b)의 형성에 의한 차단 층을 제공한다. 도핑된 제2 에피택셜 층은 오토 도핑을 완화하기 위해 P-/P+/P- 예들에서 블록의 외부 확산을 차단한다. 제2 에피택셜 층(104b, 804b)은 또한 제조 동안 치킹 장치에 대해 기판의 후면 전도성을 제공하며, 따라서 추가적인 수정 또는 추가적인 차단 층들 없이 정규 제조 장비에서 사용될 수 있다.

[0020] 설명된 실시예들에서 수정이 가능하고, 청구범위의 범주 내에서 다른 실시예들이 가능하다.

## 도면

## 도면1

## 도면2

## 도면3

도면4

도면5

도면6

도면7

도면8

### 도면9