(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6056435号

(P6056435)

(45) 発行日 平成29年1月11日(2017.1.11)

(24) 登録日 平成28年12月16日(2016.12.16)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 21/338 | (2006.01) | HO1L 29/80 | H    |

| HO1L 29/778 | (2006.01) | HO1L 29/78 | 301B |

| HO1L 29/812 | (2006.01) | HO1L 29/44 | S    |

| HO1L 21/336 | (2006.01) | HO1L 29/58 | G    |

| HO1L 29/78  | (2006.01) |            |      |

請求項の数 6 (全 33 頁) 最終頁に続く

(21) 出願番号

特願2012-268315 (P2012-268315)

(22) 出願日

平成24年12月7日 (2012.12.7)

(65) 公開番号

特開2014-116401 (P2014-116401A)

(43) 公開日

平成26年6月26日 (2014.6.26)

審査請求日

平成27年2月26日 (2015.2.26)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 110000925

特許業務法人信友国際特許事務所

(72) 発明者 谷口 理

東京都港区港南1丁目7番1号 ソニー株式会社内

(72) 発明者 竹内 克彦

東京都港区港南1丁目7番1号 ソニー株式会社内

審査官 棚田 一也

最終頁に続く

(54) 【発明の名称】半導体装置

(57) 【特許請求の範囲】

【請求項 1】

チャネル層と、

前記チャネル層上に設けられ、前記チャネル層を構成する半導体よりも高い伝導帯位置を有する高抵抗の半導体からなる高抵抗層と、

前記高抵抗層の表面層に設けられ、第1導電型不純物を含む半導体からなる第1導電型の低抵抗領域と、

前記低抵抗領域を挟んだ位置において前記高抵抗層に接続されたソース電極及びドレイン電極と、

前記低抵抗領域上に設けられたゲート絶縁膜と、

10

前記ゲート絶縁膜を介して前記低抵抗領域上に設けられたゲート電極と、

前記低抵抗領域と前記ソース電極及び前記ドレイン電極との間において、前記高抵抗層と前記ゲート絶縁膜との界面準位によって生じた空乏層からなる電流ブロック領域と、を備え、

前記電流ブロック領域上の前記ゲート絶縁膜内に空隙を有する

半導体装置。

【請求項 2】

チャネル層と、

前記チャネル層上に設けられ、前記チャネル層を構成する半導体よりも高い伝導帯位置を有する高抵抗の半導体からなる高抵抗層と、

20

前記高抵抗層の表面層に設けられ、第1導電型不純物を含む半導体からなる第1導電型の低抵抗領域と、

前記低抵抗領域を挟んだ位置において前記高抵抗層に接続されたソース電極及びドレイン電極と、

前記低抵抗領域上に設けられたゲート絶縁膜と、

前記ゲート絶縁膜を介して前記低抵抗領域上に設けられたゲート電極と、

前記低抵抗領域と前記ソース電極及び前記ドレイン電極との間において、前記高抵抗層と前記ゲート絶縁膜との界面準位によって生じた空乏層からなる電流ブロック領域と、を備え、

前記電流ブロック領域上の前記ゲート絶縁膜内に、前記ゲート電極の側面に形成された、前記ゲート電極よりも仕事関数の大きい金属層からなる第2ゲート電極を有する半導体装置。

【請求項3】

チャネル層と、

前記チャネル層上に設けられ、前記チャネル層を構成する半導体よりも高い伝導帯位置を有する高抵抗の半導体からなる高抵抗層と、

前記高抵抗層の表面層に設けられ、第1導電型不純物を含む半導体からなる第1導電型の低抵抗領域と、

前記低抵抗領域を挟んだ位置において前記高抵抗層に接続されたソース電極及びドレイン電極と、

前記低抵抗領域上に設けられたゲート絶縁膜と、

前記ゲート絶縁膜を介して前記低抵抗領域上に設けられたゲート電極と、

前記低抵抗領域と前記ソース電極及び前記ドレイン電極との間において、前記高抵抗層と前記ゲート絶縁膜との界面準位によって生じた空乏層からなる電流ブロック領域と、を備え、

前記電流ブロック領域が、第1導電形不純物の拡散領域からなる半導体装置。

【請求項4】

チャネル層と、

前記チャネル層上に設けられ、前記チャネル層を構成する半導体よりも高い伝導帯位置を有する高抵抗の半導体からなる高抵抗層と、

前記高抵抗層の表面層に設けられ、第1導電型不純物を含む半導体からなる第1導電型の低抵抗領域と、

前記低抵抗領域を挟んだ位置において前記高抵抗層に接続されたソース電極及びドレイン電極と、

前記低抵抗領域上に設けられたゲート絶縁膜と、

前記ゲート絶縁膜を介して前記低抵抗領域上に設けられたゲート電極と、

前記低抵抗領域と前記ソース電極及び前記ドレイン電極との間において、前記高抵抗層と前記ゲート絶縁膜との界面準位によって生じた空乏層からなる電流ブロック領域と、を備え、

前記電流ブロック領域上に、前記ゲート絶縁膜と異なる絶縁膜が設けられている半導体装置。

【請求項5】

前記電流ブロック領域の表面層が、前記高抵抗層に適用する材料よりも前記ゲート絶縁膜との界面に形成される界面準位密度が大きい半導体層により形成されている請求項1から4のいずれかに記載の半導体装置。

【請求項6】

前記ゲート電極直下を除き、前記高抵抗層と前記ゲート絶縁膜との間に、前記高抵抗層に適用する材料よりも前記ゲート絶縁膜との界面に形成される界面準位密度が大きい材料からなるインターレイヤー層を有し、前記ゲート絶縁膜との界面の前記インターレイヤー

10

20

30

40

50

層の表面から前記電流プロック領域が形成されている請求項5に記載の半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本技術は半導体装置に関し、特にゲート電極とチャネル層との間の障壁層に低抵抗領域を備えた半導体装置に関する。

【背景技術】

【0002】

近年、携帯電話などの移動体通信システムにおいては、携帯通信端末の小型化及び低消費電力化が強く求められている。これらを実現するためには、例えばアンテナスイッチに 10 関し、オン抵抗 Ron の低減等が必要である。

このようなアンテナスイッチ用として実用化されている半導体装置の一つに、接合型電界効果トランジスタ (J P H E M T ; Junction Pseudo-morphic High Electron Mobility Transistor) がある(例えば、特許文献1参照)。

また、AlGaN/GaNやAlInN/GaNなどのIII族窒化物材料を用いて、MIS (MIS ; Metal Insulator Semiconductor) 反転層、及び、ヘテロ接合を利用して電流変調を行う、MISゲート構造型のHEMT素子がある(例えば、特許文献2参照)。

上記各半導体装置は、ソース電極とドレイン電極との間にゲート電極が設けられ、ソース電極 - ドレイン電極間に流れる電流の変調が可能な構造を有する。そして、各半導体装置では、ともにキャリアが走行するチャネルは1箇所のみであり、そのチャネルにおける輸送特性によりトランジスタ性能が決まっている。 20

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平11-150264号公報

【特許文献2】特開2009-71270号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、上記J P H E M Tでは、ゲート電極への順方向電圧印加に伴い、ゲート電流が増加するため、ゲート電極へ印加できる順方向電圧に制限がある。また、MISゲート構造型GaNHEMT素子では、上記J P H E M Tに比べて移動度が低く、高周波動作に向かない。このように、上記各半導体装置では、その構造上の問題点を有している。 30

【0005】

そこで、高い移動度を保ちつつ、かつ、ゲート電極に大きな正電圧を印加することが可能な半導体装置が求められている。さらに、この半導体装置では、スイッチ特性の向上が求められている。

【0006】

本技術においては、スイッチ特性に優れる半導体装置及び半導体装置の製造方法を提供するものである。 40

【課題を解決するための手段】

【0007】

本技術の半導体装置は、チャネル層と、チャネル層上に設けられ、チャネル層を構成する半導体よりも高い伝導帯位置を有する高抵抗の半導体からなる高抵抗層とを有する。また、高抵抗層の表面層に設けられ、第1導電型不純物を含む半導体からなる第1導電型の低抵抗領域を有する。そして、低抵抗領域を挟んだ位置において高抵抗層に接続されたソース電極及びドレイン電極と、低抵抗領域上に設けられたゲート絶縁膜と、ゲート絶縁膜を介して高抵抗層上に設けられたゲート電極とを有する。この半導体装置は、低抵抗領域とソース電極及びドレイン電極との間に電流プロック領域を有する。 50

## 【0008】

また、本技術の半導体装置は、チャネル層と、チャネル層上に設けられ、チャネル層を構成する半導体よりも高い伝導帯位置を有する高抵抗の半導体からなる高抵抗層とを有する。また、高抵抗層に接続されたソース電極及びドレイン電極と、高抵抗層上に設けられたゲート絶縁膜と、ゲート絶縁膜を介して、ソース電極とドレイン電極との間の高抵抗層上に設けられたゲート電極とを有する。この半導体装置は、ゲート電極直下を除く位置で、ソース電極とドレイン電極との間に電流ブロック領域を有する。

## 【0009】

また、本技術の半導体装置の製造方法は、チャネル層上に、チャネル層を構成する半導体よりも高い伝導帯位置を有する高抵抗の半導体からなる高抵抗層を形成し、高抵抗層の表面層に、第1導電型不純物を含む半導体からなる第1導電型の低抵抗領域を形成する。そして、低抵抗領域を挟んだ位置において高抵抗層に接続されたソース電極及びドレイン電極を形成し、低抵抗領域上にゲート絶縁膜を形成し、ゲート絶縁膜を介して低抵抗領域上にゲート電極を形成する。また、この半導体装置には、低抵抗領域とソース電極及びドレイン電極との間に電流ブロック領域を形成する。

10

## 【0010】

また、本技術の半導体装置の製造方法は、チャネル層上に、チャネル層を構成する半導体よりも高い伝導帯位置を有する高抵抗の半導体からなる高抵抗層を形成する。そして、高抵抗層に接続されたソース電極及びドレイン電極を形成し、高抵抗層上にゲート絶縁膜を形成し、ゲート絶縁膜を介して、ソース電極とドレイン電極との間の高抵抗層上にゲート電極を形成する。また、この半導体装置には、ゲート電極直下を除く、ソース電極とドレイン電極との間に電流ブロック領域を形成する。

20

## 【0011】

本技術の半導体装置及び半導体装置の製造方法によれば、ゲート電極と半導体層の間にゲート絶縁膜が、また、ソース電極及びドレイン電極とゲート電極の間に電流ブロック領域が形成される。このため、ゲート電極に電圧を印加したときのゲートリーク電流を抑制することができ、ゲート電極に大きな順方向電圧を印加することが可能となる。また、電流ブロック領域を備えることにより、ゲート電極下のMIS部に反転層が形成される場合にも、チャネル層よりも移動度が低い反転層に電流が流れないことから、不要な伝達コンダクタンスのゲート電圧依存性を回避することができ、半導体装置のスイッチ特性を向上させることができる。

30

## 【発明の効果】

## 【0012】

本技術によれば、ゲート絶縁膜と半導体層との界面での電流を抑制することにより、半導体装置のスイッチ特性を向上させることができる。

## 【図面の簡単な説明】

## 【0013】

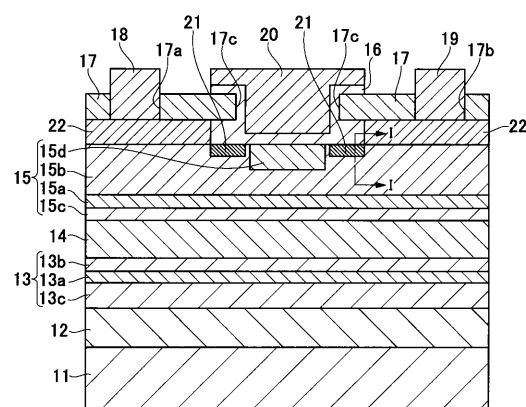

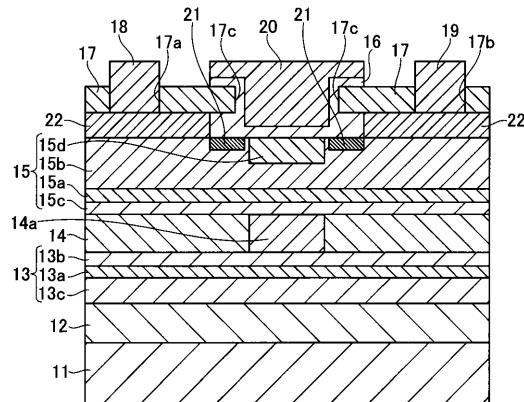

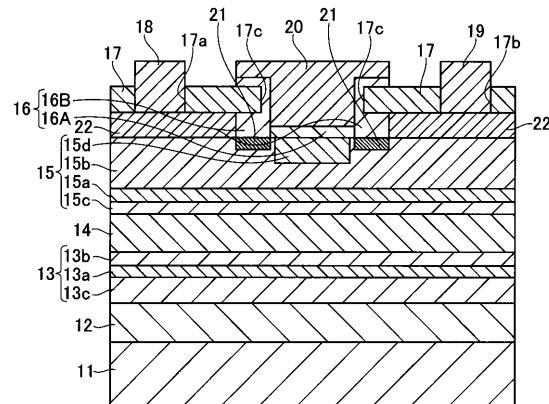

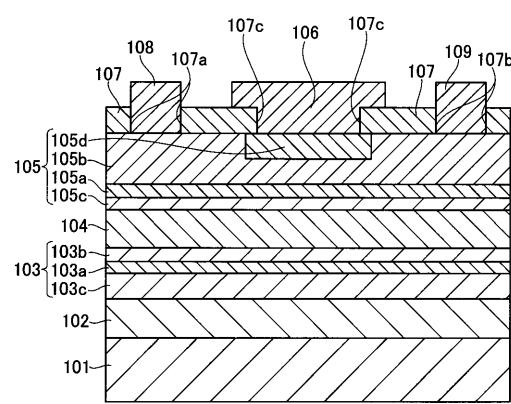

【図1】第1実施形態の半導体装置の概略構成を示す図である。

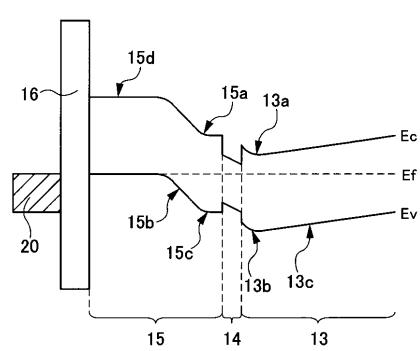

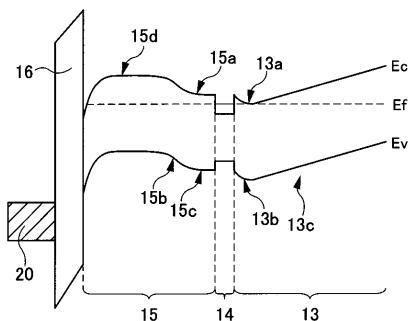

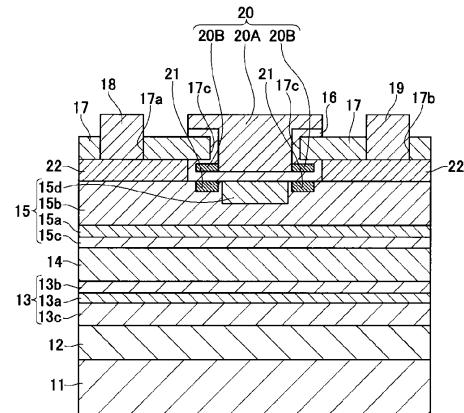

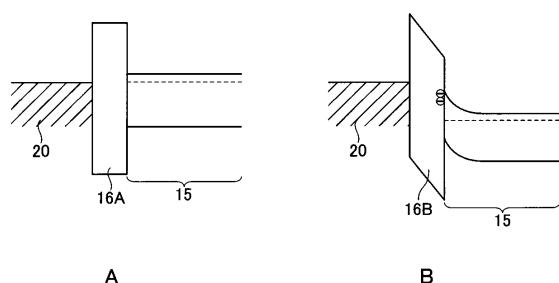

【図2】Aは、ゲート絶縁膜と上部障壁層とにおいて、界面準位密度が低い場合のエネルギー・バンド構成を示す図である。Bは、ゲート絶縁膜と上部障壁層とにおいて、界面準位密度が高い場合のエネルギー・バンド構成を示す図である。

40

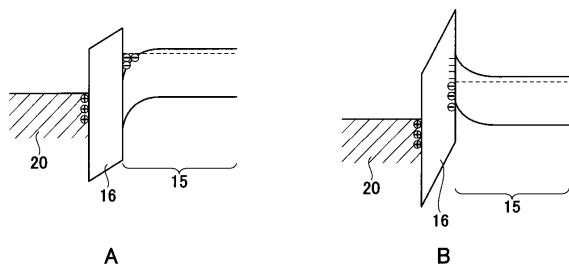

【図3】ゲート電極に0V程度のゲート電圧を印加した状態のエネルギー・バンド構成を示す図である。

【図4】ゲート電極に3V程度のゲート電圧を印加した状態のエネルギー・バンド構成を示す図である。

【図5】キャリア欠乏領域14aが形成された半導体装置の概略構成を示す図である。

【図6】ゲート電極に3V以上のゲート電圧を印加した状態のエネルギー・バンド構成を示す図である。

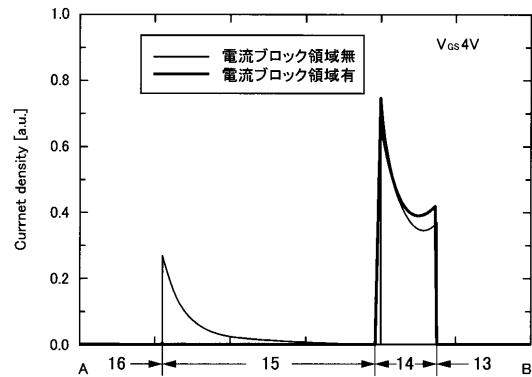

【図7】ゲート電圧印加時のキャリアの2次元分布と、ゲート電極脇の電流密度を示す図である。

50

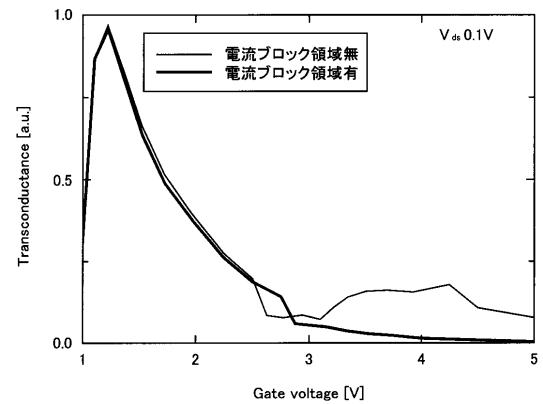

【図8】ゲート電極印加電圧変化に対する伝達コンダクタンスの変化量の関係を示す図である。

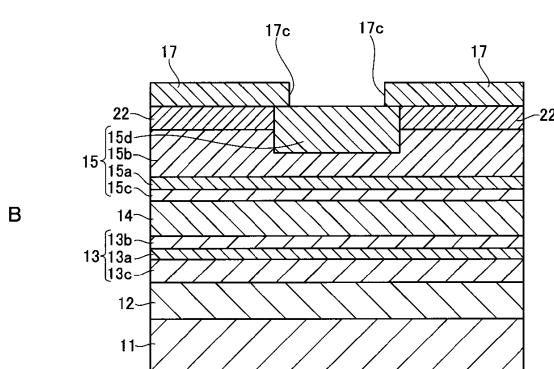

【図9】A及びBは、第1実施形態の半導体装置の製造工程図である。

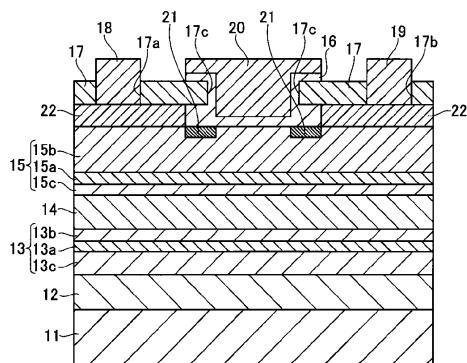

【図10】第2実施形態の半導体装置の概略構成を示す図である。

【図11】第3実施形態の半導体装置の概略構成を示す図である。

【図12】第4実施形態の半導体装置の概略構成を示す図である。

【図13】Aは、負の固定電荷を有していない絶縁膜を、ゲート電極下に用いる場合のエネルギー・バンド構成を示す図である。Bは、負の固定電荷を有している絶縁膜をゲート電極-ソース/ドレイン電極間の絶縁膜にもいる場合のエネルギー・バンド構成を示す図である。

10

【図14】第5実施形態の半導体装置の概略構成を示す図である。

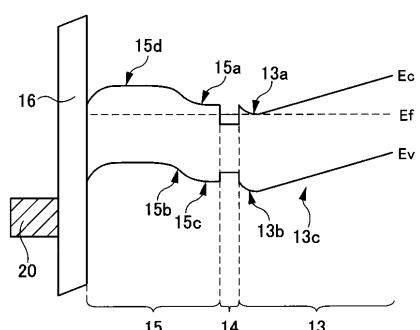

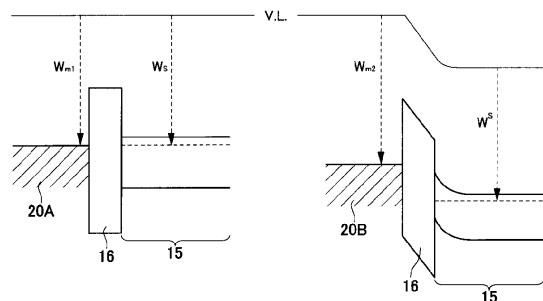

【図15】Aは、ゲート電極部におけるゲート金属とゲート絶縁膜と半導体層のエネルギー・バンド構成である。Bは、ゲート金属に対して大きな仕事関数を有する金属がゲート電極-ソース/ドレイン電極間の絶縁膜に接する場合のエネルギー・バンド構成である。

【図16】第6実施形態の半導体装置の概略構成を示す図である。

【図17】第7実施形態の半導体装置の概略構成を示す図である。

【図18】第8実施形態の半導体装置の概略構成を示す図である。

【図19】第9実施形態の半導体装置の概略構成を示す図である。

【図20】第10実施形態の半導体装置の概略構成を示す図である。

【図21】第11実施形態の半導体装置の概略構成を示す図である。

20

【図22】第12実施形態の半導体装置の概略構成を示す図である。

【図23】第13実施形態の半導体装置の概略構成を示す図である。

【図24】JPHEMT構造の半導体装置の構成を示す図である。

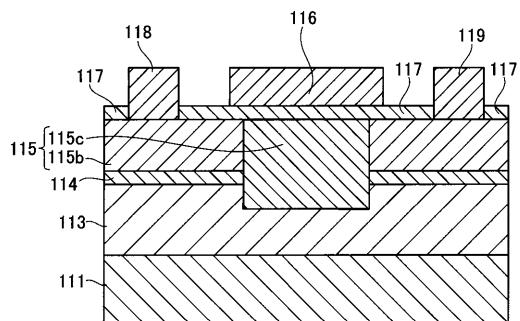

【図25】MISゲート構造型のHEMT素子の構成を示す図である。

【発明を実施するための形態】

【0014】

以下、本技術を実施するための最良の形態の例を説明するが、本技術は以下の例に限定されるものではない。

なお、説明は以下の順序で行う。

1. 半導体装置の概要

30

2. 第1実施形態(半導体装置)

3. 第1実施形態(半導体装置の製造方法)

4. 第2実施形態(半導体装置)

5. 第3実施形態(半導体装置)

6. 第4実施形態(半導体装置)

7. 第5実施形態(半導体装置)

8. 第6実施形態(半導体装置)

9. 第7実施形態(半導体装置)

10. 第8実施形態(半導体装置)

11. 第9実施形態(半導体装置)

40

12. 第10実施形態(半導体装置)

13. 第11実施形態(半導体装置)

14. 第12実施形態(半導体装置)

15. 第13実施形態(半導体装置)

【0015】

1. 半導体装置の概要

[JPHEMT]

上述の接合型電界効果トランジスタ(JPHEMT; Junction-gate Pseudomorphic High Electron Mobility Transistor)は、pn接合及びヘテロ接合を利用して電流変調を行う半導体装置である。図24に、JPHEMTの一構成例を示す。

50

## 【0016】

図24に示すJ P H E M Tは、例えば、半絶縁性単結晶G a A s基板101の上に、G a A sよりなるバッファ層102を介して、第2障壁層103と、チャネル層104と、第1障壁層105とが順次積層されている。

第2障壁層103は、2層の高抵抗層103b, 103cの間にキャリア供給層103aが挟まれた構造を有している。また、第1障壁層105は、2層の高抵抗層105b, 105cの間にキャリア供給層105aが挟まれた構造を有する。さらに、第1障壁層105内には上層の高抵抗層105bに、p型低抵抗領域105dが形成されている。

p型低抵抗領域105dの上にはゲート電極106が形成されている。p型低抵抗領域105d及びゲート電極106の両脇における障壁層105には、ソース電極108及びドレイン電極109が形成されている。 10

## 【0017】

このような構成の半導体装置は、例えば、I n G a A sからなるチャネル層104と、チャネル層104よりもバンドギャップの広いA 1 G a A sからなる各障壁層103, 105とのヘテロ接合を備えている。また、各障壁層103, 105は、ドナーとなる不純物を含むキャリア供給層103a, 105aを有している。

以上のような構成の半導体装置では、チャネル層104における障壁層103, 105の界面に、キャリアとなる電子が高濃度で閉じ込められた二次元電子ガス層が形成される。そして、ゲート電極106に電圧を印加し、p型低抵抗領域105dおよび高抵抗層105bからなるp n接合を利用して二次元電子ガス層の濃度を制御することにより、チャネル層104部分を介してソース電極108 - ドレイン電極109間に流れる電流が変調される。 20

## 【0018】

J P H E M Tは、不純物濃度が低い2次元電子ガス層をチャネルとしているため、移動度を高くできるという特徴を有している。しかしながら、p n接合を用いているので、ビルトイン電圧が高々1V程度であり、それ以上の正電圧を印加すると順方向電流が流れ、ゲートリーキ電流が高くなってしまうため、ゲート電極へ印加できる電圧に制限があるという問題がある。

## 【0019】

## [M I Sゲート構造型の素子]

30

M I Sゲート構造型のH E M T素子(M I S H E M T ; Metal Insulator Semiconductor High Electron Mobility Transistor)は、A 1 G a N / G a NやA 1 I n N / G a N等のI I I族窒化物材料を用いた高周波 / ハイパワーデバイスである。この半導体装置は、M I S(M I S ; Metal Insulator Semiconductor)反転層、及び、ヘテロ接合を利用して電流変調を行う。この半導体装置の一構成例を図25に示す。

## 【0020】

図25に示す半導体装置は、サファイア基板111の上に、G a Nからなるベース層113と、A 1 G a Nからなる障壁層115と、S i O<sub>2</sub>からなるゲート絶縁膜117が順次積層されている。そして、ゲート絶縁膜117の一部の領域の上にゲート電極116が形成されている。

40

障壁層115は、高抵抗層115bと、p型低抵抗領域115cとからなる。p型低抵抗領域115cは、ゲート絶縁膜117の直下であってゲート電極116を表面側から平面視した場合にゲート電極116に実質的に隠れる範囲内に形成されている。

ゲート電極116に電圧を印加すると、p型低抵抗領域115c内のゲート絶縁膜117との界面に反転層が形成され、ソース電極118とドレイン電極119との間を流れる電流が変調される。

## 【0021】

また、I I I族窒化物材料を用いたM I Sゲート構造型のH E M T素子は、ゲート電極116とp型低抵抗領域115cとの間にゲート絶縁膜117が形成されているため、ゲートリーキ電流が低く、ゲート電極116に大きな正電圧を印加することが可能である。

50

しかしながら、オン動作時、MIS動作により半導体表面に形成された反転層をチャネルとしているため、2次元電子ガス層をチャネルとする場合と比べて、移動度が低くなってしまうという問題がある。

I II - V族材料を用いたロッジックデバイス応用においても電子輸送特性に優れるInGaAsを用いて性能の向上が検討されているものの、反転層を利用したチャネルにおける移動度は今のところ本来の性能を実現できていない。

#### 【0022】

##### [MISPHEMT, MISJPHEMT]

上記FETが有する問題に対し、高い移動度を保ちつつ、ゲートリーク電流を低くし、ゲート電極に大きな正電圧を印加できるという両方の特性を備えるFETとしてMISPHEMT (Metal Insulator Semiconductor Pseudomorphic High Electron Mobility Transistor) やMISJPHEMT (Metal Insulator Semiconductor Junction-gate Pseudomorphic High Electron Mobility Transistor) が提案されている。10

#### 【0023】

MISJPHEMTでは、JPHEMTのゲート電極と半導体層の間にAl<sub>2</sub>O<sub>3</sub>等のゲート絶縁膜を挿入することで高移動度と低ゲートリーク電流の両立が期待されている。ゲートリーク電流を低く抑えることができるため、ゲート電極に大きな正電圧を印加することができ、オン抵抗Ronを小さくすることができる。加えて最大ドレイン電流Idma×を高くすることができる。これは、アンテナスイッチやパワーアンプ等の低消費電力化に寄与する。20

#### 【0024】

一方、このようなMISPHEMT、MISJPHEMTにおいては、キャリアが走行するチャネルとして、PHEMTの二次元電子ガス層と、MISのゲート絶縁膜 - 半導体界面の2つが存在する。

MISPHEMTを想定すると、ゲート印加電圧を大きくするに従い、MISの絶縁膜 - 半導体界面に蓄積する電子の輸送による電流が、PHEMTの二次元電子ガス層を走行する電子による電流に付加される。MISPHEMTの構造制約上、MIS部に用いられる半導体材料のキャリア輸送特性は、二次元電子ガス層に比べて劣る。このため、ソース - ドレイン電極間を流れるドレイン電流は絶対値としては増加するものの、伝達コンダクタンスのゲート印加電圧依存性の悪化を招く。アンテナスイッチやパワーアンプの歪特性はこの伝達コンダクタンス特性と正の相関を有し、伝達コンダクタンスの印加電圧依存性悪化は歪特性の悪化を招くことから、その依存性改善が課題となっている。30

#### 【0025】

##### 2. 第1実施形態（半導体装置）

##### [MISJPHEMT：構成]

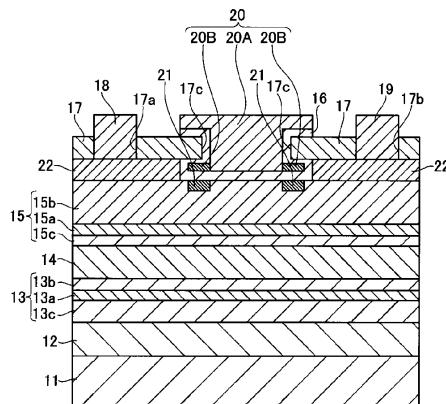

次に、本技術の第1実施形態について説明する。図1に第1実施形態の半導体装置の概略構成を示す。図1に示す半導体装置は、ゲート電極とチャネル層との間に障壁層を備え、さらに障壁層内に障壁層の導電型と異なる導電型の低抵抗領域を設け、また、この低抵抗領域の上に絶縁膜を介してゲート電極を設けたいわゆるMISJPHEMTである。

#### 【0026】

図1に示す半導体装置は、化合物半導体からなる基板11上に、各化合物半導体材料からなるバッファ層12、下部障壁層13、チャネル層14、上部障壁層15、及び、キャップ層22がこの順に積層されている。

下部障壁層13内にはキャリア供給層13aが設けられている。上部障壁層15内にはキャリア供給層15aと共にp型低抵抗領域15dが設けられている。

#### 【0027】

そして、以上のような化合物半導体材料からなる半導体層の積層体上には、絶縁層17が設けられている。この絶縁層17には、開口17a, bが設けられている。この開口17a, bには、キャップ層22を介して上部障壁層15に接続されたソース電極18、ドレイン電極19が形成されている。50

さらに、開口 17 a, b の間において、絶縁層 17 とキャップ層 22 には開口 17 c が設けられている。開口 17 c は、絶縁層 17 の開口幅よりもキャップ層 22 の開口幅の方が大きく形成されている。開口 17 c には、この底面及び側面に沿って、上部障壁層 15 上にゲート絶縁膜 16 が形成されている。

【0028】

ゲート絶縁膜 16 の上部にはゲート電極 20 が形成されている。p 型低抵抗領域 15 d はゲート絶縁膜 16 を介してゲート電極 20 直下に形成されている。さらに、上部障壁層 15 の表面であって、p 型低抵抗領域 15 d の両側のゲート絶縁膜 16 下に電流ブロック領域 21 を備える。

【0029】

(基板 11)

基板 11 は、半絶縁性の化合物半導体材料で構成されている。このような基板 11 は、例えば I II - V 族化合物半導体材料で構成され、半絶縁性の単結晶 GaAs 基板や、InP 基板が用いられる。

【0030】

(バッファ層 12)

バッファ層 12 は、例えば基板 11 上にエピタキシャル成長させた化合物半導体層で構成され、基板 11 および下部障壁層 13 に対して、良好に格子整合する化合物半導体を用いて構成される。例えば、基板 11 が単結晶 GaAs 基板からなる場合、このようなバッファ層 12 の一例として、不純物を添加しない  $u$ -GaAs ( $u$ - は不純物を添加していないことを表す；以下同様) のエピタキシャル成長層が用いられる。

【0031】

(下部障壁層)

下部障壁層 13 は、チャネル層 14 を構成する I II - V 族化合物半導体よりも高い伝導帯位置を有する、I II - V 族化合物半導体により構成されている。高い伝導帯位置を有する I II - V 族化合物半導体としては  $AlGaAs$  混晶などがあり、この下部障壁層 13 は、例えば、I II 族元素におけるアルミニウム ( $Al$ ) の組成比が 0.2 の  $Al_{0.2}Ga_{0.8}As$  混晶により構成されている。

【0032】

この下部障壁層 13 は、第 2 導電型不純物である n 型不純物を高濃度に含むキャリア供給層 13 a と、高抵抗の高抵抗層 13 b, c とを有している。この高抵抗層 13 b, c は、低濃度の n 型不純物、又は、第 1 導電型不純物である p 型不純物を含んでいてもよく、n 型不純物及び p 型不純物を含んでいなくてもよい。高抵抗層 13 b, c は、不純物濃度が  $1 \times 10^{17}$  個 /  $cm^3$  以下、比抵抗が  $1 \times 10^{12} \Omega \cdot cm$  以上であることが好ましい。

【0033】

下部障壁層 13 は、例えば、厚さが 4 nm であり n 型不純物としてシリコンを  $3 \times 10^{18} \Omega \cdot cm^{-3}$  程度添加したキャリア供給層 13 a を有する。そして、キャリア供給層 13 a の上下に、厚さが 200 nm の不純物を添加しない高抵抗層 13 c と、厚さが 2 nm の不純物を添加しない高抵抗層 13 b とが基板 11 上に積層された構造を有している。なお、下部障壁層 13 は、高抵抗層 13 b, c を有していなくてもよく、全領域がキャリア供給層 13 a とされていてもよい。

【0034】

(チャネル層)

チャネル層 14 は、ソース電極 18 とドレイン電極 19 との間の電流通路である。チャネル層 14 は、下部障壁層 13 及び上部障壁層 15 を構成する各 I II - V 族化合物半導体よりも低い伝導帯位置を有する I II - V 族化合物半導体により構成されている。伝導帯位置が低い I II - V 族化合物半導体としては  $InGaAs$  混晶等がある。チャネル層 14 は、例えば、I II 族元素におけるインジウム ( $In$ ) の組成比が 0.2 の不純物を添加しない  $u$ -In<sub>0.2</sub>Ga<sub>0.8</sub>As 混晶により構成されている。これにより、チャ

10

20

30

40

50

ネル層 1 4 には、下部障壁層 1 3 のキャリア供給層 1 3 a および後述する上部障壁層 1 5 のキャリア供給層 1 5 a から供給されたキャリアが蓄積されるようになっている。

【 0 0 3 5 】

例えば、チャネル層 1 4 を  $InGaAs$  混晶により構成する場合には、 $III$  族元素におけるインジウムの組成比を 0.1 以上とすることが好ましい。インジウムの組成比を高くするほどバンドギャップを狭くできる。インジウムの組成比を 0.1 以上とすれば、下部障壁層 1 3 とチャネル層 1 4 との間、及び、上部障壁層 1 5 とチャネル層 1 4 との間における各伝導帯位置の差をそれぞれ十分に大きくすることができる。また、チャネル層 1 4 の厚さは、15 nm 以下であることが好ましい。厚くすると、チャネル層 1 4 の結晶性が低下してしまうからである。

10

【 0 0 3 6 】

(上部障壁層)

上部障壁層 1 5 は、高濃度の n 型不純物を含むキャリア供給層 1 5 a と、高抵抗の高抵抗層 1 5 b, c とを有する。さらに、高抵抗層 1 5 c に、p 型低抵抗領域 1 5 d を有している。

【 0 0 3 7 】

上部障壁層 1 5 は、チャネル層 1 4 を構成する  $III-V$  族化合物半導体よりも高い伝導帯位置を有する  $III-V$  族化合物半導体により構成されている。例えば、この上部障壁層 1 5 は、 $III$  族元素におけるアルミニウムの組成比が 0.2 の  $Al_{0.2}Ga_{0.8}As$  混晶により構成されている。

20

上部障壁層 1 5 を  $AlGaAs$  混晶により構成する場合には、 $III$  族元素におけるアルミニウムの組成比を 0.25 以下とすることが好ましい。アルミニウムの組成比を 0.25 以下とすることにより、いわゆるソース抵抗の増加を抑制することができる。さらに、後述する p 型低抵抗領域 1 5 d を p 型不純物の拡散により形成する際に拡散速度を抑えることができ、制御性が向上する。

【 0 0 3 8 】

上部障壁層 1 5 は、キャリアを供給する不純物を含むキャリア供給層 1 5 a を有している。例えば、電子を供給する n 型不純物としてシリコン (Si) を含む n 型のキャリア供給層 1 5 a が、上部障壁層 1 5 の膜厚方向の中間部分に配置される。

高抵抗層 1 5 b, c は、低濃度の n 型不純物あるいは p 型不純物を含んでいてもよく、また n 型不純物及び p 型不純物を含んでいなくてもよい。

30

【 0 0 3 9 】

p 型低抵抗領域 1 5 d は、高濃度の p 型不純物の拡散領域である。p 型低抵抗領域 1 5 d は、ソース電極 1 8 とドレイン電極 1 9 との間の領域においてゲート電極 2 0 に対応して設けられた p 型低抵抗領域である。この p 型低抵抗領域 1 5 d は、ゲート絶縁膜 1 6 と高抵抗層 1 5 b との間に位置しており、例えば、p 型不純物である亜鉛 (Zn) が高抵抗層 1 5 b の一部に拡散することにより形成されている。p 型低抵抗領域 1 5 d における p 型不純物濃度は  $1 \times 10^{18} \text{ cm}^{-3}$  以上であることが好ましい。

【 0 0 4 0 】

例えば、上部障壁層 1 5 は、厚さが 4 nm であり n 型不純物としてシリコンを  $3 \times 10^{18} \text{ cm}^{-3}$  程度添加したキャリア供給層 1 5 a を有する。そして、キャリア供給層 1 5 a の上下に、厚さが 2 nm の不純物を添加しない高抵抗層 1 5 c と、厚さが 30 nm の不純物を添加しない高抵抗層 1 5 b とがチャネル層 1 4 側から積層された構成を有する。

40

さらに、 $1 \times 10^{19} \text{ cm}^{-3}$  程度の p 型不純物濃度を有する p 型低抵抗領域 1 5 d がゲート絶縁膜 1 6 に接して高抵抗層 1 5 b に埋め込まれた構造となっている。

【 0 0 4 1 】

なお、本例では、下部障壁層 1 3 と上部障壁層 1 5 とを同一組成の  $Al_{0.2}Ga_{0.8}As$  混晶で構成した例を説明するが、下部障壁層 1 3 と上部障壁層 1 5 とは、互いに異なった組成の  $AlGaAs$  混晶により構成されていれもよい。

上部障壁層 1 5 は  $III$  族元素におけるアルミニウムの組成比が 0.25 以下であるこ

50

とが好ましい。これに対して、下部障壁層 13 では p 型不純物の拡散により p 型低抵抗領域を形成する必要がない。このため、下部障壁層 13 では上部障壁層 15 に比べてアルミニウムの組成比を高い構成とすることもできる。

また、高抵抗層 13b, 15b における不純物濃度は  $1 \times 10^{17} \text{ cm}^{-3}$  以下であることが好ましく、比抵抗は  $1 \times 10^{-2} \text{ cm}$  以上であることが好ましい。

#### 【0042】

##### (キャップ層)

キャップ層 22 は、上部障壁層 15 と、ソース電極 18 及びドレイン電極 19 との間に設けられている。キャップ層 22 は、p 型低抵抗領域 15d と障壁層と異なる導電型の不純物を含有する層として形成される。また、キャップ層 22 は、上部障壁層 15 と同じ材料、或いは、ソース電極 18、ドレイン電極 19 の仕事関数と、上部障壁層 15 の伝導帯位置との間に伝導帯位置を有する半導体材料からなる。

#### 【0043】

キャップ層 22 は、チャネルまでのアクセス抵抗を低減することを目的として導入されている。アクセス抵抗は、半導体 - 電極の接触抵抗と電極からチャネル層 14 までの抵抗とから成る。このため、キャップ層 22 は、両抵抗を低減するために、高濃度に不純物が添加されている。

#### 【0044】

##### (絶縁層)

絶縁層 17 は、上部障壁層 15 を構成する化合物半導体に対して絶縁性を有し、かつ、イオンなどの不純物より下地（ここでは上部障壁層 15）の表面を保護する機能を持つ材料が用いられる。絶縁層 17 は、例えば、厚さが 200 nm の窒化珪素 ( $\text{Si}_3\text{N}_4$ ) により構成される。

#### 【0045】

##### (ソース電極 18 / ドレイン電極 19)

ソース電極 18 及びドレイン電極 19 は、p 型低抵抗領域 15d を挟む位置において、それぞれが開口 17a, b を介して上部障壁層 15 にオーミック接合されている。このようなソース電極 18 及びドレイン電極 19 は、上部障壁層 15 側から順に、金 - ゲルマニウム ( $\text{AuGe}$ )、ニッケル ( $\text{Ni}$ )、及び、金 ( $\text{Au}$ ) を順次積層して合金化したものにより構成されている。ソース電極 18 及びドレイン電極 19 の各膜厚は、例えばそれぞれ合計約 1000 nm である。

#### 【0046】

##### (ゲート絶縁膜)

ゲート絶縁膜 16 は、絶縁層 17 に形成された開口 17c の底部に設けられ、開口 17c を完全に塞ぐ状態で設けられている。そして、端縁が絶縁層 17 上まで設けられている。このようなゲート絶縁膜 16 は、酸化物または窒化物を用いて構成され、例えば、厚さが 10 nm の酸化アルミニウム ( $\text{Al}_2\text{O}_3$ ) により構成されている。

#### 【0047】

##### (ゲート電極)

ゲート電極 20 は、ゲート絶縁膜 16 を介して p 型低抵抗領域 15d の上部に設けられている。ゲート電極 20 は、開口 17c を埋め込む状態で設けられている。ゲート電極 20 は、例えば、基板 11 側からチタン ( $\text{Ti}$ )、白金 ( $\text{Pt}$ ) 及び金を順次積層した構成である。

#### 【0048】

##### (電流プロック領域)

また、図 1 に示すように p 型低抵抗領域 15d の両脇に電流プロック領域 21 が形成されている。図 1 に示す構成の半導体装置では、ゲート絶縁膜 16 と高抵抗層 15b との界面準位によってフェルミレベルピニングが生じる。つまり、ゲート絶縁膜 16 と上部障壁層 15 の高抵抗層 15b との界面準位によって高抵抗層 15b 中に空乏層が生じる。このように、ゲート電極 20 の両脇において半導体中に空乏層が広がる効果を、電流プロッ

10

20

30

40

50

ク領域 21 として用いている。

【0049】

界面準位により電流プロック領域 21 が形成される様子を、図 2A, B に示すエネルギー・バンド構成を用いて説明する。図 2A は、ゲート絶縁膜 16 と上部障壁層 15 とにおいて、界面準位密度が低い場合を示す。また、図 2B は、ゲート絶縁膜 16 と上部障壁層 15 とにおいて、界面準位密度が高い場合を示す。

図 2A に示すように、界面準位密度が低い場合、ゲート電極への電圧印加によって上部障壁層 15 側に電子が蓄積する。このため、ゲート絶縁膜 16 と上部障壁層 15 との界面に電流パスが生じる。これに対し、界面準位密度が高い場合、電圧印加によっても上部障壁層 15 側に電子が蓄積しにくい。このため、ゲート絶縁膜 16 と上部障壁層 15 との界面に電流パスが生じない。

【0050】

一般に p 型低抵抗領域 15d と高抵抗層 15b とを比べると、高抵抗層 15b とゲート絶縁膜 16 とにおいて、バンドギャップ中の深い位置に高密度の界面準位が形成されやすい。このため、ゲート絶縁膜 16 と高抵抗層 15b との界面から、高抵抗層 15b 中に電流プロック領域として寄与する空乏層が伸びやすい。

また、この領域にゲート電極 20 が接していないため、ゲート電圧印加の影響を受けにくいことから、正電圧が印加されても空乏層幅が変化しにくく、広いゲート電圧範囲で電流プロック領域の効果が期待できる。

【0051】

[MISJPHEMT：動作]

(エネルギー・バンド)

図 3 及び図 4 に、上述の構成の半導体装置のゲート電極 20 下におけるエネルギー・バンド構成を示す。図 3 は 0V 程度のゲート電圧  $V_g$  を印加した状態のものであり、図 4 は 3V 程度のゲート電圧  $V_g$  を印加した状態のものである。なお、図 3 及び図 4 では、下部障壁層 13 及び上部障壁層 15 が  $\text{Al}_{0.2}\text{Ga}_{0.8}\text{As}$  混晶によりそれぞれ構成され、チャネル層 14 が  $\text{In}_{0.2}\text{Ga}_{0.8}\text{As}$  混晶により構成された半導体装置について示している。

【0052】

図 3 に示すように、上述の半導体装置は、チャネル層 14 と上部障壁層 15 との伝導帯端の不連続量  $E_c$  が十分に大きく（ここでは 0.31eV）構成されている。また、上部障壁層 15 のポテンシャル極小点とチャネル層 14 内における電子のフェミル準位の差も十分に大きく（ここでは 0.20eV 以上）なるように構成されている。このため、上部障壁層 15 内に分布する電子数は、チャネル層 14 内に分布する電子数に比べて無視できる程度に少なくなっている。

【0053】

また、上述の半導体装置は、チャネル層 14 を、チャネル層 14 よりも高い伝導帯位置の下部障壁層 13 と上部障壁層 15 とで挟んだ構成である。このため、チャネル層 14 は、下部障壁層 13 及び上部障壁層 15 のキャリア供給層 13a, 15a からキャリアが供給された場合に、このキャリアが蓄積し二次電子ガス層となる。

【0054】

この半導体装置は、ゲート電極と第 1 導電型 p 型低抵抗領域との間にゲート絶縁膜が設けられており、pn 接合のように大きな順方向電流が流れることがない。このため、ゲートリーク電流を大幅に低減させることができ、ゲート電極 20 に大きな正電圧を印加することができる。

【0055】

さらに、図 1 に示すように p 型低抵抗領域 15d の両脇に電流プロック領域 21 を有する。これにより、ゲート電極 20 への正電圧印加によって、ゲート電極 20 とゲート絶縁膜 16、p 型低抵抗領域 15d とから成る MIS 構造が反転動作をし、ゲート絶縁膜 16 と p 型低抵抗領域 15d 界面にキャリアが発生する場合でも、ソース電極 18 とドレイン

10

20

30

40

50

電極 19 間を流れるドレイン電流に寄与しない。

【0056】

(動作)

上述の構成の半導体装置では、ゲート電極 20 に、ゲート電圧  $V_g = 0$  V 程度を印加した状態では、ゲート絶縁膜 16 下の p 型の p 型低抵抗領域 15d 内の価電子帯位置  $E_v$  は一定であり、フェルミレベル  $E_f$  とほぼ一致している。

【0057】

また、ゲート電圧  $V_g$  を閾電圧よりも低くした場合、図 5 に示すように、半導体装置における p 型低抵抗領域 15d の直下に位置するチャネル層 14 内の領域に、電子が空乏化したキャリア欠乏領域 14a が形成される。図 3 にこのときのエネルギー・バンド構成を示している。このように、キャリア欠乏領域 14a により、チャネル層 14 は高抵抗の状態になる。従って、ソース電極 18 とドレイン電極 19 との間には、チャネル層 14 を介してドレイン電流  $I_d$  が流れることはなく、オフ状態となる。

【0058】

一方、半導体装置のゲート電極 20 に、ゲート電圧  $V_g = 3.0$  V 程度の正のゲート電圧  $V_g$  を印加した状態では、ゲート絶縁膜 16 を介して p 型低抵抗領域 15d の伝導帯位置  $E_c$  が下がる。これにより、p 型低抵抗領域 15d 内の正孔が空乏化する。図 4 にこのときのエネルギー・バンド構成を示している。

また、このとき図 5 に示すチャネル層 14 内におけるキャリア欠乏領域 14a が消失する。このため、チャネル層 14 内における電子数が増大し、チャネル層 14 を介してソース電極 18 とドレイン電極 19 との間にドレイン電流  $I_d$  が流れる。このドレイン電流  $I_d$  は、ゲート電圧  $V_g$  によって変調される。

【0059】

従来の J PHEMT においてはゲート電極に印加する電圧を 1.0 V 以下としていたが、この半導体装置ではゲート電極に印加する電圧を 1.0 V 以下とする必要がない。つまり、J PHEMT と比較して、本例の半導体装置では、ゲート電極 20 に高い正電圧を印加することができる。このため、チャネル層 14 のオン抵抗  $R_{on}$  が低くなり、最大ドレイン電流  $I_{dmax}$  が大きくなる。さらに、素子サイズを縮小することができ、寄生容量を低減させることができる。

【0060】

(電流プロック領域)

ところで、上述の構成の半導体装置において、電流プロック領域を備えていない構成とした場合には、ゲート電極 20 に 3.0 V 以上の正のゲート電圧  $V_g$  を印加すると、以下の現象がおこる。

ゲート電極 20 に正のゲート電圧  $V_g$  を印加すると、ゲート絶縁膜 16 を介して p 型低抵抗領域 15d の伝導帯位置が下がり、ゲート絶縁膜 16 と p 型低抵抗領域 15d の領域で反転動作を起こし始める。このため、絶縁膜 - 半導体界面に存在する電子数が増大し、チャネル層 14 以外にドレイン電流  $I_d$  が流れるパスが形成される。その際、ドレイン電流  $I_d$  は反転動作部とチャネル層 14 を流れる電流の和となるため、ドレイン電流の総和は大きくなる。図 6 にこのときのエネルギー・バンド構成を示す。

【0061】

図 7 に、ゲート電圧印加時のゲート電極脇の電流密度分布を示す。図 7 には、電流プロック領域の有無による電流の違いを評価するため、図 1 に示す I - I 線断面図における電流密度を示している。ここで、電流プロック領域有りとは、上述の図 1 に示す構成の半導体装置である。また、電流プロック領域無しとは、上述の図 1 に示す半導体装置から、電流プロック領域 21 を除去した構成である。

【0062】

図 7 に示すように、電流プロック領域を有していない半導体装置では、チャネル層 14 と、ゲート絶縁膜 16 と高抵抗層 15b との界面 (ゲート絶縁膜 - 半導体界面) において、電流が発生している。

10

20

30

40

50

これに対して、電流プロック領域を有する半導体装置では、チャネル層14でのみ電流の発生があり、ゲート絶縁膜16と高抵抗層15bとの界面では電流の発生がない。このように、電流プロック領域21により、反転動作時にゲート絶縁膜・半導体界面を流れる電流が抑制されることがわかる。

#### 【0063】

絶縁膜・半導体界面に形成される反転層を走行する電子の移動度と、チャネル層14を走行する電子の移動度は同じではない。AlGaaS層に代表される上部障壁層15に用いられる半導体材料中を走行する電子の移動度は、 $1000 \sim 3000 \text{ cm}^2/\text{V}\cdot\text{s}$ であり、チャネル層14に比べて低い。従って、トランジスタの駆動能力の1つである伝達コンダクタンス( $g_m$ ；ゲート電極印加電圧変化に対するドレイン電流の変化量)は、電子が走行する箇所が1箇所から2箇所に増えることで、ゲート電極印加電圧に対して大きな依存性を示す。この様子を図8に示す。

10

#### 【0064】

図8に示すように、電流プロック領域を有していない半導体装置では、印加電圧を3V以上としたときに、伝達コンダクタンスの上昇が見られる。これに対して、電流プロック領域21を有する半導体装置では、印加電圧を3V以上とした場合にも伝達コンダクタンスの上昇がない。このように、電流プロック領域21を備えることにより、伝達コンダクタンス $g_m$ のゲート電圧依存性が小さいことがわかる。例えば、アンテナスイッチ応用を想定する場合、このような伝達コンダクタンス $g_m$ のゲート電圧依存性は、スイッチの歪特性に影響を与える。従って、電流プロック領域21を有するMISSJPHEMTでは、歪特性の悪化が少ない。

20

#### 【0065】

##### (効果)

このように本実施の形態に係る半導体装置によれば、ゲート電極20とp型低抵抗領域15dとの間(ゲート絶縁膜・半導体界面)にゲート絶縁膜16が形成されているので、この界面においてゲートリーケ電流がほとんど流れない。このため、ゲート電極20に大きな正電圧を印加することができ、オン抵抗 $R_{on}$ を小さくすることができる。さらに、最大ドレン電流 $I_{dmax}$ を高くすることができる。

さらに、電流プロック領域を有し、ゲート印加電圧を大きくしても伝達コンダクタンスのゲート電圧依存性が小さいことから、電流プロック領域を有しない構造に比べてオン時の高調波歪特性の悪化が抑えられる。

30

#### 【0066】

従って、この半導体装置を用いて無線通信装置を構成すれば、無線通信装置の大きさを小さくすることができると共に、その消費電力を少なくすることができる。すなわち、特に、携帯通信端末において、装置の小型化及び使用時間の延長が可能となり、携帯を更に容易とすることができます。

加えて、ゲート電極20とp型低抵抗領域15dとの間にゲート絶縁膜16が形成されているので、ゲート電極20とドレン電極19との間の耐圧を向上させることができる。

#### 【0067】

40

##### 3. 第1実施形態(半導体装置の製造方法)

次に、上述の第1実施形態の半導体装置の製造方法について説明する。

まず、図9Aに示すように、基板11上に半導体層を積層する。

例えばAlGaaSよりなる基板11上に、例えば不純物を添加しないu-AlGaaS層をエピタキシャル成長させてバッファ層12を形成する。その後、バッファ層12上に、例えばAl<sub>0.2</sub>Ga<sub>0.8</sub>As(Al<sub>0.2</sub>Ga<sub>0.8</sub>As混晶)層をエピタキシャル成長させて下部障壁層13を形成する。この際、例えば不純物を添加しないu-AlGaaS層からなる高抵抗層13c、シリコン(Si)を添加したn型AlGaaS層からなるキャリア供給層13a、および不純物を添加しないu-AlGaaS層からなる高抵抗層13bを順次エピタキシャル成長させる。これにより、膜厚方向の中央にn型のキャリア供給層13aを

50

備えた下部障壁層 13 を形成する。

【0068】

次に、下部障壁層 13 上に、例えば不純物を添加しない  $u$  - InGaAs 層をエピタキシャル成長させてチャネル層 14 を形成する。

その後、チャネル層 14 上に、例えば  $AlGaAs$  ( $Al_{0.2}Ga_{0.8}As$  混晶) 層をエピタキシャル成長させて上部障壁層 15 を形成する。この際、例えば不純物を添加しない  $u$  -  $AlGaAs$  層からなる高抵抗層 15c、シリコン (Si) を添加した  $n$  型の  $AlGaAs$  層からなるキャリア供給層 15a、不純物を添加しない  $u$  -  $AlGaAs$  層からなる高抵抗層 15b を順次エピタキシャル成長させる。これにより、膜厚方向の中央に  $n$  型のキャリア供給層 15a を備えた上部障壁層 15 を得る。

さらに、上部障壁層 15 上に、例えば  $n$  型不純物としてシリコンを添加した  $n$  型  $GaAs$  層を形成してキャップ層 22 とする。

この後、図示しないが、メサエッチングやアイソレーションインプラにより素子間分離を行う。

【0069】

次に、図 9B に示すように、キャップ層 22 上に、例えば PECVD (Plasma Enhanced Chemical Vapor Deposition) 法により窒化珪素膜を形成し絶縁層 17 を形成する。その後、絶縁層 17 をパターンエッチングし、ゲート電極形成領域に上部障壁層 15 の表面を露出する開口 17c を形成する。この状態で、開口 17c の底部に露出するキャップ層 22 の表面から  $p$  型不純物を導入し、上部障壁層 15 内に  $p$  型低抵抗領域 15d を形成する。例えば、600 度の温度で  $p$  型不純物である亜鉛をキャップ層 22 および高抵抗層 15b に拡散させて  $p$  型低抵抗領域 15d を形成する。ここでは、キャリア供給層 15a に達することのない位置、すなわち高抵抗層 15b 内の表面層のみに、 $p$  型不純物である亜鉛 (Zn) を拡散させて  $p$  型低抵抗領域 15d を形成する。亜鉛 (Zn) の拡散は、例えば 600 度の温度での亜鉛化合物気体を用いた気相拡散によって行う。これにより、開口 17c の底部にセルフアラインで  $p$  型低抵抗領域 15d を形成する。

【0070】

次に、 $p$  型低抵抗領域 15d を形成したのち、例えばクエン酸系エッチング溶液により、開口 17c から露出するキャップ層 22 のみを選択的に除去する。そして、絶縁層 17 が除去された上部障壁層 15 の高抵抗層 15b の上及び絶縁層 17 の上に、例えば ALD (Atomic Layer Deposition) 法によりアルミ酸化膜を成膜しゲート絶縁膜 16 を形成する。

【0071】

ゲート絶縁膜 16 を形成した後、その上に、例えばニッケル、及び金を順次蒸着してパターン形成を行い、ゲート電極 20 を形成する。

次に、ゲート絶縁膜 16 と絶縁層 17 をエッチングにより選択的に除去して  $p$  型低抵抗領域 15d を間に挟むソース電極形成領域及びドレイン電極形成領域に、開口 17a, 17b をそれぞれ形成する。そして、この開口 17a, 17b に、例えば  $Ag$ , ニッケル及び金を順次蒸着してパターン形成を行う。続いて、例えば 400 度の加熱処理により金系合金形成をして、ソース電極 18 及びドレイン電極 19 をそれぞれ形成し、図 1 に示す半導体装置を形成することができる。

【0072】

ゲート電極脇の空隙においては、ゲート絶縁膜 16 と上部障壁層 15 の高抵抗層 15b との界面準位によって高抵抗層 15b 中に空乏層がのびてあり、電流ブロック領域 21 として寄与する。一般に  $p$  型低抵抗領域 15d と高抵抗層 15b とを比べると、後者とゲート絶縁膜 16 においてバンドギャップ中の深い位置に高密度の界面準位が形成されやすい。このため、電流ブロック領域 21 として寄与する空乏層が伸びやすい。また、この領域にゲート電極 20 が接していないため、ゲート電圧印加の影響を受けにくいことから、正電圧が印加されても空乏層幅が変化しにくく、広いゲート電圧範囲で電流ブロック領域の効果が期待される。

## 【0073】

なお、この半導体装置は、例えば、移動体通信システム等における無線通信装置に好ましく用いられる。この無線通信装置としては、特に、通信周波数がUHF (ultra high frequency) 帯以上であるものが好ましい。

## 【0074】

このように本実施形態に係る半導体装置によれば、ゲート電極20とp型低抵抗領域15dとの間にゲート絶縁膜16が形成されているので、ゲート絶縁膜16と高抵抗層15bとの界面において、ゲートリーケ電流はほとんど流れない。このため、ゲート電極20に大きな正電圧を印加することができ、オン抵抗Ronを小さくすることができる。加えて、最大ドレイン電流Idmaxを高くすることができる。

10

## 【0075】

この半導体装置を用いて無線通信装置を構成すれば、無線通信装置を小型化することができると共に、その消費電力を少なくすることができる。すなわち、特に、携帯通信端末において、装置の小型化及び使用時間の延長が可能となり、携帯を更に容易とすることができます。

加えて、ゲート電極20とp型低抵抗領域15dとの間にゲート絶縁膜16が形成されているので、ゲート電極20とドレイン電極19との間の耐圧を向上させることができます。

## 【0076】

さらに、本実施の形態に係る半導体装置の製造方法によれば、チャネル層14とゲート絶縁膜16との間にチャネル層14を構成する半導体よりも広いバンドギャップを有する半導体からなる高抵抗層15bを形成する。そして、この高抵抗層15bに、ゲート電極20に対応してp型不純物を拡散してp型低抵抗領域15dを形成するため、本実施の形態に係る半導体装置を容易に製造することができる。

20

## 【0077】

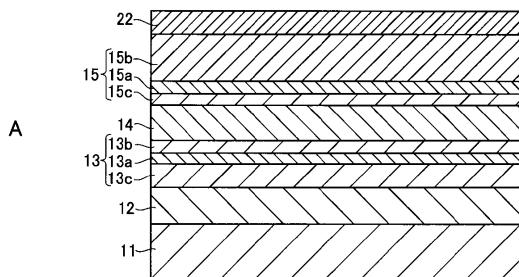

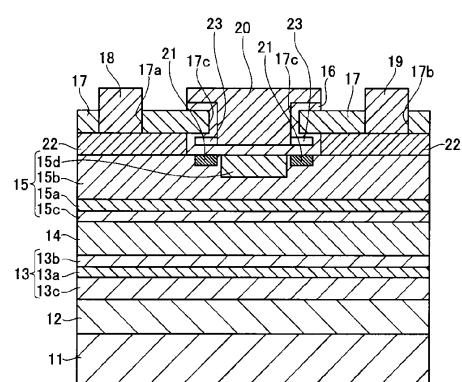

## 4. 第2実施形態（半導体装置）

次に、半導体装置の第2実施形態について説明する。第2実施形態は、上述の第1実施形態と同じく、ゲート電極とチャネル層との間に障壁層を備え、さらに障壁層内に障壁層と異なる導電型の低抵抗領域を設けた、いわゆるMISJPHEMTである。また、第2実施形態において、上述の第1実施形態と同様の構成には、同じ符号を付して詳細な説明を省略する。

30

## 【0078】

第2実施形態の半導体装置の構成を、図10に示す。図10に示すように、この半導体装置は、基板11上に、各化合物半導体材料からなるバッファ層12、下部障壁層13、チャネル層14、上部障壁層15、及び、キャップ層22がこの順に積層されている。

下部障壁層13内にはキャリア供給層13aが設けられている。上部障壁層15内にはキャリア供給層15aと共にp型低抵抗領域15dが設けられている。

## 【0079】

また、以上のような化合物半導体材料からなる各層の積層体上には、絶縁層17が設けられている。この絶縁層17には、開口17a, bが設けられている。この開口17a, bには、キャップ層22を介して上部障壁層15に接続されたソース電極18、ドレイン電極19が形成されている。

40

開口17a, bの間において、絶縁層17とキャップ層22とには開口17cが設けられている。開口17cは、絶縁層17と絶縁層17下のキャップ層22とに連続して形成され、絶縁層17の開口よりもキャップ層22の開口の方が大きく形成されている。

以上の構成については、上述の第1実施形態と同様の構成である。

## 【0080】

開口17cには、この底面及び側面に沿って、上部障壁層15上にゲート絶縁膜16が形成されている。開口17cにおいて、キャップ層22の側壁と上部障壁層15上のゲート絶縁膜16が、キャップ層22の厚さの半分未満の厚さで形成されている。このため、

50

ゲート絶縁膜 16 とゲート電極 20 の側面とに囲まれた空隙 23 が、キャップ層 22 と同じ層に設けられている。

空隙 23 を除くゲート絶縁膜 16 の上部にはゲート電極 20 が形成されている。p 型低抵抗領域 15d はゲート絶縁膜 16 を介してゲート電極 20 直下に形成されている。さらに、上部障壁層 15 の表面であって、p 型低抵抗領域 15d の両側のゲート絶縁膜 16 下に電流プロック領域 21 が形成される。

#### 【0081】

空隙 23 は、キャップ層 22 の側壁に設けられたゲート絶縁膜 16 と、ゲート電極 20 との間であり、電流プロック領域 21 の上方に形成されている。開口 17c では、絶縁層 17 よりもキャップ層 22 の開口幅が広いため、この開口幅の差分に空隙 23 が形成されている。10

このため、ゲート電極 20 の側面に空隙 23 が設けられている構成となる。ゲート電極 20 と、電流プロック領域 21 との間に空隙 23 が設けられるため、第 1 実施形態に比べて、ゲート印加電圧がゲート絶縁膜を介して電流プロック領域に与える影響をより抑えることができる。

#### 【0082】

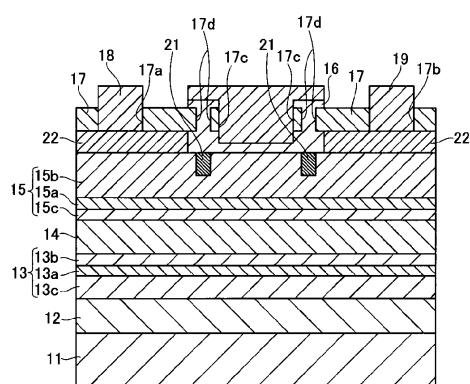

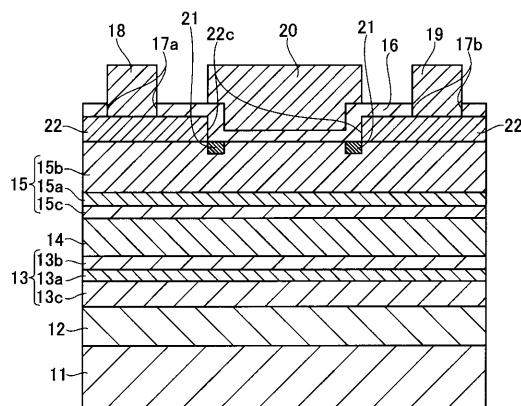

##### 5. 第 3 実施形態（半導体装置）

次に、半導体装置の第 3 実施形態について説明する。第 3 実施形態は、上述の第 1 実施形態と同じく、ゲート電極とチャネル層との間に障壁層を備え、さらに障壁層内に障壁層と異なる導電型の低抵抗領域を設けた、いわゆる MISJPHEMT である。また、第 3 実施形態において、上述の第 1 実施形態と同様の構成には、同じ符号を付して詳細な説明を省略する。20

#### 【0083】

第 3 実施形態の半導体装置の構成を、図 11 に示す。図 11 に示すように、この半導体装置は、基板 11 上に、各化合物半導体材料からなるバッファ層 12、下部障壁層 13、チャネル層 14、上部障壁層 15、及び、キャップ層 22 がこの順に積層されている。

下部障壁層 13 内にはキャリア供給層 13a が設けられている。上部障壁層 15 内にはキャリア供給層 15a と共に p 型低抵抗領域 15d が設けられている。

#### 【0084】

以上のような化合物半導体材料からなる各層の積層体上には、絶縁層 17 が設けられている。このゲート絶縁膜 17 には、開口 17a, b が設けられている。この開口 17a, b には、キャップ層 22 を介して上部障壁層 15 に接続されたソース電極 18、ドレイン電極 19 が形成されている。30

以上の構成については、上述の第 1 実施形態と同様の構成である。

#### 【0085】

また、開口 17a, b の間において、絶縁層 17 とキャップ層 22 とには開口 17c, d が設けられている。開口 17c は、絶縁層 17 及びキャップ層 22 のゲート電極 20 を形成する位置に設けられている。開口 17d は、所定の間隔をもつて開口 17c の両脇に設けられている。開口 17c と開口 17d とは、絶縁層 17 の下部において、キャップ層 22 と同じ層でつながるように、キャップ層 22 の開口が形成されている。そして、開口 17d から上部障壁層 15 上までに連続して、キャップ層 22 の開口内にゲート絶縁膜 16 が形成されている。さらに、開口 17c からゲート絶縁膜 16 の上部にゲート電極 20 が形成されている。p 型低抵抗領域 15d はゲート絶縁膜 16 を介してゲート電極 20 直下に形成されている。40

#### 【0086】

さらに、高抵抗層 15b の表面において、開口 17d の下方のゲート絶縁膜 16 下に電流プロック領域 21 を備える。

電流プロック領域 21 は、p 型低抵抗領域 15d の形成時、又は、後の工程において、開口 17d から高抵抗層 15b に不純物を導入することで形成される。例えば、絶縁層 17 を開口して、開口 17c と、開口 17c の両脇に開口 17d を設ける。そして、この開50

図 17 c, d から不純物を導入することにより、開口 17 c 下に p 型低抵抗領域 15 d を形成し、開口 17 d 下に電流プロック領域 21 を形成する。この領域は p n 接合からなり、高抵抗層 15 b 側に空乏層が伸びて電流プロック領域 21 として寄与する。ゲート電極 20 は電流プロック領域 21 直上ではなく、厚い絶縁膜を介して電圧が印加されるため、ゲート電圧印加時の電流プロック領域 21 の空乏層の変化は小さい。このため、p 型低抵抗領域 15 d とゲート絶縁膜 16 の間で反転動作により電子が存在する場合でも、電流プロック領域として寄与できる。

#### 【0087】

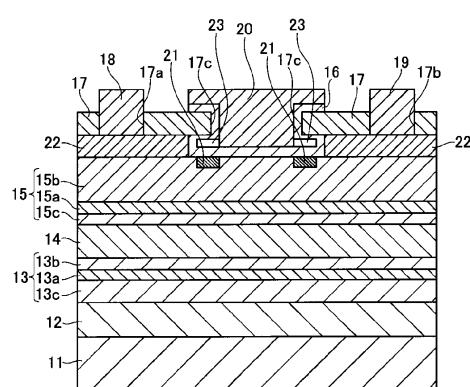

##### 6. 第4実施形態(半導体装置)

次に、半導体装置の第4実施形態について説明する。第4実施形態は、上述の第1実施形態と同じく、ゲート電極とチャネル層との間に障壁層を備え、さらに障壁層内に障壁層と異なる導電型の低抵抗領域を設けた、いわゆるMISJPHEMTである。また、第4実施形態において、上述の第1実施形態と同様の構成には、同じ符号を付して詳細な説明を省略する。

#### 【0088】

第4実施形態の半導体装置の構成を、図12に示す。図12に示すように、この半導体装置は、基板 11 上に、各化合物半導体材料からなるバッファ層 12、下部障壁層 13、チャネル層 14、上部障壁層 15、及び、キャップ層 22 がこの順に積層されている。

下部障壁層 13 内にはキャリア供給層 13 a が設けられている。上部障壁層 15 内にはキャリア供給層 15 a と共に p 型低抵抗領域 15 d が設けられている。

#### 【0089】

また、以上のような化合物半導体材料からなる各層の積層体上には、絶縁層 17 が設けられている。このゲート絶縁膜 16 には、開口 17 a, b が設けられている。この開口 17 a, b には、キャップ層 22 を介して上部障壁層 15 に接続されたソース電極 18、ドレイン電極 19 が形成されている。

開口 17 a, b の間において、絶縁層 17 とキャップ層 22 とには開口 17 c が設けられている。開口 17 c は、絶縁層 17 と絶縁層 17 下のキャップ層 22 とに連続して形成され、絶縁層 17 の開口よりもキャップ層 22 の開口の方が大きく形成されている。

以上の構成については、上述の第1実施形態と同様の構成である。

#### 【0090】

開口 17 c には、この底面及び側面に沿って、上部障壁層 15 上にゲート絶縁膜 16 が形成されている。ゲート絶縁膜 16 は、第1ゲート絶縁膜 16 A と、この第1ゲート絶縁膜 16 A とは異なる材料からなる第2ゲート絶縁膜 16 B と、から形成されている。

ゲート絶縁膜 16 上にはゲート電極 20 が形成されている。p 型低抵抗領域 15 d は第1ゲート絶縁膜 16 A を介してゲート電極 20 直下に形成されている。さらに、上部障壁層 15 の表面であって、p 型低抵抗領域 15 d の両側のゲート絶縁膜 16 下に電流プロック領域 21 が形成される。電流プロック領域 21 は、上部障壁層 15 の表面であって、第2ゲート絶縁膜 16 B と接する位置に設けられる。

#### 【0091】

第1ゲート絶縁膜 16 A は、ゲート電極 20 の直下にのみ設けられている。また、第2ゲート絶縁膜 16 B は、ゲート電極 20 の直下を除く開口 17 c の側面に設けられている。つまり、本例の半導体装置では、ゲート電極 20 直下と開口 17 c の側面等とで、2つの異なる材料からゲート絶縁膜 16 が構成されている。

#### 【0092】

第2ゲート絶縁膜 16 B と高抵抗層 15 b との界面に形成される界面準位は、第1ゲート絶縁膜 16 A と p 型低抵抗領域 15 d との間に形成される界面準位に比べて半導体中深い準位にあり密度も高く設定される。このため、第2ゲート絶縁膜 16 B と高抵抗層 15 b との界面に形成される界面準位は、ゲート電圧印加による空乏層の変化が小さくなっている。従って、p 型低抵抗領域 15 d と第2ゲート絶縁膜 16 B の間で反転動作により電子が存在する場合でも電流プロック領域 21 として寄与できる。

10

20

30

40

50

## 【0093】

このような第2ゲート絶縁膜16Bの機能を有する絶縁膜としては、例えばSiNやSiO<sub>2</sub>が挙げられる。一方、ゲート電極20直下のゲート絶縁膜16Aとしては、例えばAl<sub>2</sub>O<sub>3</sub>やHfO<sub>2</sub>を用いることができる。

## 【0094】

また、第2ゲート絶縁膜16Bとして、負の固定電荷量や界面ダイポールの量を変えることにより、電流ブロック領域21を形成してもよい。図13A、Bに、ゲート絶縁膜16に用いる材料の固定電荷量の違いによる、エネルギー・バンド構成の変化を示す。図13Aは、ゲート絶縁膜16に負の固定電荷を有していない場合のゲート電極20下におけるエネルギー・バンド構成を示す。また、図13Bは、ゲート絶縁膜16に負の固定電荷を有している場合のゲート電極20下におけるエネルギー・バンド構成を示す。

10

## 【0095】

図13Bに示すように、固定電荷量や界面ダイポールの量を変えることにより、MIS界面に蓄積層が形成される電圧をシフトさせることができる。このため、-Qf/Coxにより電子が蓄積されづらくなり、電流ブロック領域21として寄与できる。このように、第2ゲート絶縁膜16Bの、負の固定電荷量や、界面ダイポールの量を変えることにより、上部障壁層15の上部界面に電流ブロック領域21を形成することが可能である。固定電荷を導入する絶縁膜としては、例えば、Al<sub>2</sub>O<sub>3</sub>中にHを導入した材料などが報告されている。

## 【0096】

20

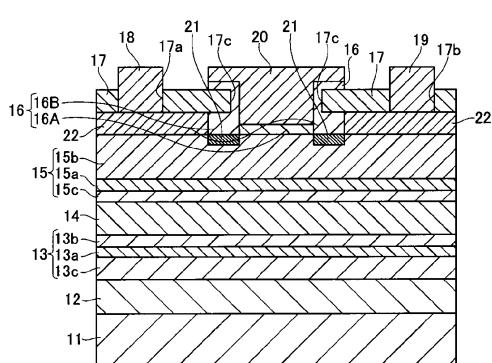

## 7. 第5実施形態(半導体装置)

次に、半導体装置の第5実施形態について説明する。第5実施形態は、上述の第1実施形態と同じく、ゲート電極とチャネル層との間に障壁層を備え、さらに障壁層内に障壁層と異なる導電型の低抵抗領域を設けた、いわゆるMISJPHEMTである。また、第5実施形態において、上述の第1実施形態と同様の構成には、同じ符号を付して詳細な説明を省略する。

## 【0097】

第5実施形態の半導体装置の構成を、図14に示す。図14に示すように、この半導体装置は、基板11上に、各化合物半導体材料からなるバッファ層12、下部障壁層13、チャネル層14、上部障壁層15、及び、キャップ層22がこの順に積層されている。

30

下部障壁層13内にはキャリア供給層13aが設けられている。上部障壁層15内にはキャリア供給層15aと共にp型低抵抗領域15dが設けられている。

## 【0098】

また、以上のような化合物半導体材料からなる各層の積層体上には、絶縁層17が設けられている。このゲート絶縁膜16には、開口17a, bが設けられている。この開口17a, bには、キャップ層22を介して上部障壁層15に接続されたソース電極18、ドレイン電極19が形成されている。

開口17a, bの間において、絶縁層17とキャップ層22とには開口17cが設けられている。開口17cは、絶縁層17と絶縁層17下のキャップ層22とに連続して形成され、絶縁層17の開口よりもキャップ層22の開口の方が大きく形成されている。

40

以上の構成については、上述の第1実施形態と同様の構成である。

## 【0099】

また、開口17cには、この底面及び側面に沿って、上部障壁層15上にゲート絶縁膜16が形成されている。開口17cにおいて、キャップ層22の側壁と上部障壁層15上のゲート絶縁膜16が、上述の第1実施形態よりも薄く形成されている。このゲート絶縁膜16の構成については、上述の第2実施形態と同様の構成である。

## 【0100】

本例では、ゲート絶縁膜16の上部にはゲート電極20が形成されている。また、ゲート電極20は、絶縁層17に設けられた開口17c開口よりも広い範囲において、キャップ層22に設けられた開口17cのゲート絶縁膜16上に形成されている。

50

ゲート電極 20 は、第1ゲート電極 20A と第2ゲート電極 20B とから構成されている。第1ゲート電極 20A は、開口 17c の中心において、開口 17c の開口幅及び p 型低抵抗領域 15d と同等の領域に形成されている。そして、この第1ゲート電極 20A の側面に第2ゲート電極 20B が形成されている。開口 17c では、キャップ層 22 の方が開口幅が広く、ゲート絶縁膜 16 が薄く形成されているため、この絶縁層 17 の開口幅とキャップ層 22 の開口幅の差分において、第2ゲート電極 20B が形成されている。そして、この第2ゲート電極 20B を除くゲート絶縁膜 16 上に第1ゲート電極 20A が形成されている。

#### 【0101】

また、p 型低抵抗領域 15d はゲート絶縁膜 16 を介して第1ゲート電極 20A 直下に形成されている。さらに、上部障壁層 15 の表面であって、p 型低抵抗領域 15d の両側のゲート絶縁膜 16 を介して第2ゲート電極 20B 直下に電流ブロック領域 21 が形成される。

#### 【0102】

この半導体装置は、第2ゲート電極 20B として、第1ゲート電極 20A よりも仕事関数が大きい金属を用いる。図 15 に、ゲート電極 20 に用いる金属の仕事関数の違いによる、エネルギー・バンド構成の変化を示す。図 15 は、ゲート電極 20 に小さい仕事関数 ( $W_{m1}$ ) を有する材料を適用した場合と、ゲート電極 20 に大きい仕事関数 ( $W_{m2}$ ) を有する材料を適用した場合とにおいて、ゲート電極 20 下におけるエネルギー・バンド構成を示す。

#### 【0103】

図 15 に示すように、仕事関数が大きい金属を用いることにより、 $V = W_{m2} - W_{m1}$  から、V 分界面に電子が蓄積されづらくなり、電流バスとなる蓄積層が形成される電圧は正バイアス方向にシフトする。これにより、第2ゲート電極 20B とゲート絶縁膜 16 と高抵抗層 15b からなる MIS 構造において、蓄積動作するゲート印加電圧は、第1ゲート電極 20A とゲート絶縁膜 16 と p 型低抵抗領域 15d からなる MIS 構造に対して、正方向にシフトしている。このため、後者 MIS 構造が反転動作しても前者 MIS 部分は電流ブロック領域として機能を維持できる。このように、第2ゲート電極 20B として、仕事関数の大きい材料を用いることにより、上部障壁層 15 の上部界面に電流ブロック領域 21 を形成することが可能である。

このような第2ゲート電極 20B としての機能を実現する仕事関数が大きい金属としては、例えば、Ni や Pd、Pt、Au 等を挙げることができる。

#### 【0104】

##### 8. 第6実施形態（半導体装置）

次に、半導体装置の第6実施形態について説明する。

上述の各実施形態では MISJPHEMT 構造を元に電流ブロック領域を導入した半導体装置とその製法について述べてきたが、この電流ブロック領域の寄与は MISJPHEMT のみならず MISPHEMT に対しても有効である。

以下、MISPHEMT 構造の半導体装置に電流ブロック領域を導入した構成について説明する。なお、第6実施形態に示す MISPHEMT 構造の半導体装置においても、上述の第1実施形態に示す MISJPHEMT 構造の半導体装置と同様の構成には、同じ符号を付して詳細な説明を省略する。

#### 【0105】

##### (MISPHEMT)

第6実施形態の半導体装置の構成を図 16 に示す。図 16 に示すように、この半導体装置は、基板 11 上に、各化合物半導体材料からなるバッファ層 12、下部障壁層 13、チャネル層 14、上部障壁層 15、及び、キャップ層 22 がこの順に積層されている。

下部障壁層 13 内にはキャリア供給層 13a が設けられている。上部障壁層 15 内には、キャリア供給層 15a が設けられている。

また、第1実施形態に示す MISJPHEMT 構造と異なり、上部障壁層 15 内には p

10

20

30

40

50

型低抵抗領域が設けられていない。

【0106】

そして、以上のような化合物半導体材料からなる各層の積層体上には、絶縁層17が設けられている。このゲート絶縁膜16には、開口17a, bが設けられている。この開口17a, bには、キャップ層22を介して上部障壁層15に接続されたソース電極18、ドレイン電極19が形成されている。

さらに、開口17a, bの間において、絶縁層17とキャップ層22とには開口17cが設けられている。開口17cは、絶縁層17と絶縁層17下のキャップ層22とに連続して形成されている。開口17cは、絶縁層17の開口幅よりもキャップ層22の開口幅の方が大きく形成されている。

10

【0107】

開口17cには、この底面及び側面に沿って、上部障壁層15上にゲート絶縁膜16が形成されている。ゲート絶縁膜16の上部にはゲート電極20が形成されている。p型低抵抗領域15dはゲート絶縁膜16を介してゲート電極20直下に形成されている。さらに、上部障壁層15の表面であって、ゲート電極20直下を除くゲート絶縁膜16下に電流ブロック領域21を備える。

【0108】

第6実施形態において、基板11、バッファ層12、下部障壁層13、チャネル層14、ゲート絶縁膜16、絶縁層17、ソース電極18、ドレイン電極19、ゲート電極20、及び、キャップ層22は、上述の第1実施形態と同様の構成である。また、上部障壁層15は、低抵抗領域を備えないことを除き、上述の第1実施形態と同様の構成である。

20

【0109】

(電流ブロック領域)

図16に示すように、ゲート絶縁膜16と高抵抗層15bとの界面には、ゲート電極20の直下を除き、ゲート電極20の直下の両脇に電流ブロック領域21が形成される。

図16に示す構成の半導体装置では、ゲート絶縁膜16と高抵抗層15bとの界面準位によってフェルミレベルピニングが生じる。つまり、ゲート絶縁膜16と上部障壁層15の高抵抗層15bとの界面準位によって高抵抗層15b中に空乏層が生じる。このように、ゲート電極20の両脇において、半導体中に空乏層が広がる効果を、電流ブロック領域21として用いている。

30

【0110】

本例において、界面準位により電流ブロック領域21が形成される様子は、上述の図2A, Bに示すエネルギー・バンド構成により、第1実施形態の構成と同様に説明することができる。図2Aに示すように界面準位密度が低い場合、ゲート電極への電圧印加によって上部障壁層15側に電子が蓄積する。このため、ゲート絶縁膜16と上部障壁層15との界面に電流パスが生じる。これに対し、図2Bに示すように界面準位密度が高い場合、電圧印加によっても上部障壁層15側に電子が蓄積しにくい。このため、ゲート絶縁膜16と上部障壁層15との界面に電流パスが生じない。

【0111】

電流ブロック領域21は、ゲート電極20が接していない領域であるため、ゲート電圧印加の影響を受けにくく、正電圧が印加されても空乏層幅が変化しにくい。このため、広いゲート電圧範囲で電流ブロック領域21の効果が期待できる。

40

一方、ゲート電極20直下では、電圧印加時に影響を大きく受けるため、正電圧が印加された際に空乏層幅が変化しやすく、電流ブロック領域の効果が期待しにくい。このため、この領域は、電流ブロック領域としての寄与は小さい。

【0112】

なお、第6実施形態に示すMISPHEMT構造の半導体装置の製造方法は、上述の第1実施形態の半導体装置の製造方法において、不純物導入による低抵抗領域の形成を行わないことを除き、同じ工程により製造することができる。

【0113】

50

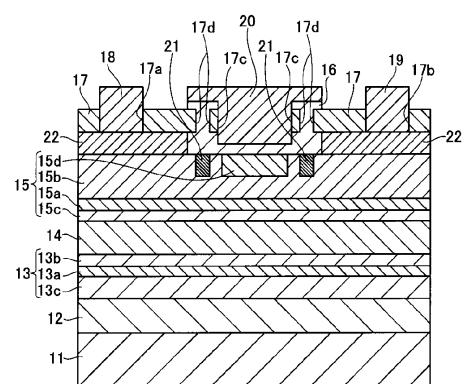

### 9. 第7実施形態(半導体装置)

次に、半導体装置の第7実施形態について説明する。第7実施形態は、上述の第6実施形態と同じく、ゲート電極とチャネル層との間に障壁層を備えた、いわゆるMISPEMTである。また、第7実施形態において、上述の第6実施形態と同様の構成には、同じ符号を付して詳細な説明を省略する。

#### 【0114】

第7実施形態の半導体装置の構成を、図17に示す。図17に示すように、この半導体装置は、基板11上に、各化合物半導体材料からなるバッファ層12、下部障壁層13、チャネル層14、上部障壁層15、及び、キャップ層22がこの順に積層されている。

下部障壁層13内にはキャリア供給層13aが設けられている。上部障壁層15内にはキャリア供給層15aが設けられている。

#### 【0115】

また、以上のような化合物半導体材料からなる各層の積層体上には、絶縁層17が設けられている。このゲート絶縁膜16には、開口17a, bが設けられている。この開口17a, bには、キャップ層22を介して上部障壁層15に接続されたソース電極18、ドレイン電極19が形成されている。

開口17a, bの間において、絶縁層17とキャップ層22とには開口17cが設けられている。開口17cは、絶縁層17と絶縁層17下のキャップ層22とに連続して形成され、絶縁層17の開口よりもキャップ層22の開口の方が大きく形成されている。

以上の構成については、上述の第6実施形態と同様の構成である。

#### 【0116】

開口17cには、この底面及び側面に沿って、上部障壁層15上にゲート絶縁膜16が形成されている。開口17cにおいて、キャップ層22の側壁と上部障壁層15上のゲート絶縁膜16が、キャップ層22の厚さの半分未満の厚さで形成されている。このため、ゲート絶縁膜16とゲート電極20の側面とに囲まれた空隙23が、キャップ層22と同じ層に設けられている。

空隙23を除くゲート絶縁膜16の上部にはゲート電極20が形成されている。さらに、上部障壁層15の表面であって、ゲート電極20の両側の空隙23及びゲート絶縁膜16下に電流ブロック領域21を備える。

#### 【0117】

空隙23は、キャップ層22の側壁に設けられたゲート絶縁膜16と、ゲート電極20との間であり、電流ブロック領域21の上方に形成されている。開口17cでは、絶縁層17よりもキャップ層22の開口幅が広いため、この開口幅の差分に空隙23が形成されている。

このため、ゲート電極20の側面に空隙23が設けられている構成となる。ゲート電極20と、電流ブロック領域21との間に空隙23が設けられるため、第1実施形態に比べて、ゲート印加電圧がゲート絶縁膜を介して電流ブロック領域に与える影響をより抑えることができる。

#### 【0118】

### 10. 第8実施形態(半導体装置)

次に、半導体装置の第8実施形態について説明する。第8実施形態は、上述の第6実施形態と同じく、ゲート電極とチャネル層との間に障壁層を備えた、いわゆるMISPEMTである。また、第8実施形態において、上述の第6実施形態と同様の構成には、同じ符号を付して詳細な説明を省略する。

#### 【0119】

第8実施形態の半導体装置の構成を、図18に示す。図18に示すように、この半導体装置は、基板11上に、各化合物半導体材料からなるバッファ層12、下部障壁層13、チャネル層14、上部障壁層15、及び、キャップ層22がこの順に積層されている。

下部障壁層13内にはキャリア供給層13aが設けられている。上部障壁層15内にはキャリア供給層15aが設けられている。

10

20

30

40

50

## 【0120】

以上のような化合物半導体材料からなる各層の積層体上には、絶縁層17が設けられている。この絶縁層17には、開口17a, bが設けられている。この開口17a, bには、キャップ層22を介して上部障壁層15に接続されたソース電極18、ドレイン電極19が形成されている。

以上の構成については、上述の第6実施形態と同様の構成である。

## 【0121】

また、開口17a, bの間ににおいて、絶縁層17とキャップ層22とには開口17c, dが設けられている。開口17cは、絶縁層17及びキャップ層22のゲート電極20を形成する位置に設けられている。開口17dは、開口17cから所定の間隔をあいて両脇に設けられている。開口17cと開口17dとは、絶縁層17の下部において、キャップ層22と同じ層でつながるように、キャップ層22の開口が形成されている。そして、開口17dから上部障壁層15上までに連続して、キャップ層22の開口内にゲート絶縁膜16が形成されている。さらに、開口17cからゲート絶縁膜16の上部にはゲート電極20が形成されている。

## 【0122】

さらに、高抵抗層15bの表面において、開口17dの下方のゲート絶縁膜16下に電流プロック領域21を備える。

電流プロック領域21は、開口17dから高抵抗層15bに不純物を導入することで形成される。例えば、絶縁層17を開口して、開口17cと、開口17cの両脇に開口17dを設ける。そして、この開口17dから不純物を導入することにより、開口17d下に電流プロック領域21を形成する。この領域はpn接合からなり、高抵抗層15b側に空乏層が伸びて電流プロック領域21として寄与する。ゲート電極20は電流プロック領域21直上になく、厚い絶縁膜を介して電圧が印加されるため、ゲート電圧印加時の電流プロック領域21の空乏層の変化は小さい。このため、ゲート電圧印加時でも、電流プロック領域として寄与できる。

## 【0123】

## 11. 第9実施形態(半導体装置)

次に、半導体装置の第9実施形態について説明する。第9実施形態は、上述の第6実施形態と同じく、ゲート電極とチャネル層との間に障壁層を備えた、いわゆるMISPEMTである。また、第9実施形態において、上述の第6実施形態と同様の構成には、同じ符号を付して詳細な説明を省略する。

## 【0124】

第9実施形態の半導体装置の構成を、図19に示す。図19に示すように、この半導体装置は、基板11上に、各化合物半導体材料からなるバッファ層12、下部障壁層13、チャネル層14、上部障壁層15、及び、キャップ層22がこの順に積層されている。

下部障壁層13内にはキャリア供給層13aが設けられている。上部障壁層15内にはキャリア供給層15aが設けられている。

## 【0125】

また、以上のような化合物半導体材料からなる各層の積層体上には、絶縁層17が設けられている。このゲート絶縁膜16には、開口17a, bが設けられている。この開口17a, bには、キャップ層22を介して上部障壁層15に接続されたソース電極18、ドレイン電極19が形成されている。

開口17a, bの間ににおいて、絶縁層17とキャップ層22とには開口17cが設けられている。開口17cは、絶縁層17と絶縁層17下のキャップ層22とに連続して形成され、絶縁層17の開口よりもキャップ層22の開口の方が大きく形成されている。

以上の構成については、上述の第6実施形態と同様の構成である。

## 【0126】

開口17cには、この底面及び側面に沿って、上部障壁層15上にゲート絶縁膜16が形成されている。ゲート絶縁膜16は、第1ゲート絶縁膜16Aと、この第1ゲート絶縁

10

20

30

40

50

膜 16 A とは異なる材料からなる第 2 ゲート絶縁膜 16 B と、から形成されている。

ゲート絶縁膜 16 上にはゲート電極 20 が形成されている。p 型低抵抗領域 15 d はゲート絶縁膜 16 A を介してゲート電極 20 直下に形成されている。さらに、上部障壁層 15 の表面であって、p 型低抵抗領域 15 d の両側のゲート絶縁膜 16 下に電流ブロック領域 21 を備える。電流ブロック領域 21 は、上部障壁層 15 の表面であって、第 2 ゲート絶縁膜 16 B と接する位置に設けられる。

#### 【 0 1 2 7 】

第 1 ゲート絶縁膜 16 A は、ゲート電極 20 の直下にのみ設けられている。また、第 2 ゲート絶縁膜 16 B は、ゲート電極 20 の直下を除く開口 17 c の側面に設けられている。つまり、本例の半導体装置では、ゲート電極 20 直下と開口 17 c の側面とで、2 つの異なる材料からゲート絶縁膜 16 が構成されている。

10

#### 【 0 1 2 8 】

第 2 ゲート絶縁膜 16 B と高抵抗層 15 b との界面に形成される界面準位は、第 1 ゲート絶縁膜 16 A と高抵抗層 15 b との間に形成される界面準位に比べて半導体中深い準位にあり、密度も高く設定される。このため、第 2 ゲート絶縁膜 16 B と高抵抗層 15 b との界面に形成される界面準位は、ゲート電圧印加による空乏層の変化が小さくなっている。従って、高抵抗層 15 b と第 2 ゲート絶縁膜 16 B の間で反転動作により電子が存在する場合でも電流ブロック領域 21 として寄与できる。

#### 【 0 1 2 9 】

このような第 2 ゲート絶縁膜 16 B の機能を有する絶縁膜としては、例えば SiN や SiO<sub>2</sub> が挙げられる。一方、ゲート電極 20 直下のゲート絶縁膜 16 A としては、例えば Al<sub>2</sub>O<sub>3</sub> や HfO<sub>2</sub> を用いることができる。

20

#### 【 0 1 3 0 】

また、第 2 ゲート絶縁膜 16 B として、負の固定電荷量や界面ダイポールの量を変えることにより、電流ブロック領域 21 を形成してもよい。ゲート絶縁膜 16 に用いる材料の固定電荷量の違いによる電流ブロック領域 21 の形成については、上述の図 13 A、B に示すエネルギー・バンド構成により、第 4 実施形態と同様に説明することができる。

図 13 B に示すように、固定電荷量や界面ダイポールの量を変えることにより、MIS 界面に蓄積層が形成される電圧をシフトさせることができる。このため、-Qf/Cox により電子が蓄積されづくなり、電流ブロック領域 21 として寄与できる。このように、第 2 ゲート絶縁膜 16 B の負の固定電荷量や、界面ダイポールの量を変えることにより、上部障壁層 15 の上部界面に電流ブロック領域 21 を形成することが可能である。固定電荷を導入する絶縁膜としては、例えば、Al<sub>2</sub>O<sub>3</sub> 中に H を導入した材料などが報告されている。

30

#### 【 0 1 3 1 】

##### 12. 第 10 実施形態（半導体装置）

次に、半導体装置の第 10 実施形態について説明する。第 10 実施形態は、上述の第 6 実施形態と同じく、ゲート電極とチャネル層との間に障壁層を備えた、いわゆるMISPHEMT である。また、第 10 実施形態において、上述の第 6 実施形態と同様の構成には、同じ符号を付して詳細な説明を省略する。

40

#### 【 0 1 3 2 】

第 10 実施形態の半導体装置の構成を、図 20 に示す。図 20 に示すように、この半導体装置は、基板 11 上に、各化合物半導体材料からなるバッファ層 12、下部障壁層 13、チャネル層 14、上部障壁層 15、及び、キャップ層 22 がこの順に積層されている。

下部障壁層 13 内にはキャリア供給層 13 a が設けられている。上部障壁層 15 内にはキャリア供給層 15 a が設けられている。

#### 【 0 1 3 3 】

また、以上のような化合物半導体材料からなる各層の積層体上には、絶縁層 17 が設けられている。この絶縁層 17 には、開口 17 a, b が設けられている。この開口 17 a, b には、キャップ層 22 を介して上部障壁層 15 に接続されたソース電極 18、ドレイン

50

電極 19 が形成されている。

開口 17a, b の間において、絶縁層 17 とキャップ層 22 とには開口 17c が設けられている。開口 17c は、絶縁層 17 と絶縁層 17 下のキャップ層 22 とに連続して形成され、絶縁層 17 の開口よりもキャップ層 22 の開口の方が大きく形成されている。

以上の構成については、上述の第 6 実施形態と同様の構成である。

#### 【0134】

また、開口 17c には、この底面及び側面に沿って、上部障壁層 15 上にゲート絶縁膜 16 が形成されている。開口 17c において、キャップ層 22 の側壁と上部障壁層 15 上のゲート絶縁膜 16 が、上述の第 6 実施形態よりも薄く形成されている。このゲート絶縁膜 16 の構成については、上述の第 7 実施形態と同様の構成である。

10

#### 【0135】

本例では、ゲート絶縁膜 16 上にゲート電極 20 が形成されている。また、ゲート電極 20 は、絶縁層 17 に設けられた開口 17c 開口よりも広い範囲において、キャップ層 22 に設けられた開口 17c のゲート絶縁膜 16 上に形成されている。

ゲート電極 20 は、第 1 ゲート電極 20A と第 2 ゲート電極 20B とから構成されている。第 1 ゲート電極 20A は、開口 17c の中心において、開口 17c の開口幅と同等の領域に形成されている。そして、この第 1 ゲート電極 20A の側面に第 2 ゲート電極 20B が形成されている。開口 17c では、キャップ層 22 の方が開口幅が広く、ゲート絶縁膜 16 が薄く形成されているため、この絶縁層 17 の開口幅とキャップ層 22 の開口幅の差分において、第 2 ゲート電極 20B が形成されている。そして、この第 2 ゲート電極 20B を除くゲート絶縁膜 16 上に第 1 ゲート電極 20A が形成されている。

20

また、上部障壁層 15 の表面であって、ゲート絶縁膜 16 を介して第 2 ゲート電極 20B 直下に電流プロック領域 21 を備える。

#### 【0136】

この半導体装置は、第 2 ゲート電極 20B として、第 1 ゲート電極 20A よりも仕事関数が大きい金属を用いる。ゲート電極 20 に用いる金属の仕事関数の違いによる電流プロック領域 21 の形成については、上述の図 15B に示すエネルギー・バンド構成により、第 5 実施形態と同様に説明することができる。

図 15 に示すように、仕事関数が大きい金属を用いることにより、 $V = W_{m2} - W_m$  から、V 分界面に電子が蓄積されづらくなり、電流パスとなる蓄積層が形成される電圧は正バイアス方向にシフトする。これにより、第 2 ゲート電極 20B とゲート絶縁膜 16 と高抵抗層 15b からなる MIS 構造において、蓄積動作するゲート印加電圧は、第 1 ゲート電極 20A とゲート絶縁膜 16 と高抵抗層 15b からなる MIS 構造に対して、正方向にシフトしている。このため、後者 MIS 構造が反転動作しても前者 MIS 部分は電流プロック領域として機能を維持できる。このように、第 2 ゲート電極 20B として、仕事関数の大きい材料を用いることにより、上部障壁層 15 の上部界面に電流プロック領域 21 を形成することが可能である。

30

このような第 2 ゲート電極 20B としての機能を実現する仕事関数が大きい金属としては、例えば、Ni や Pd、Pt、Au 等を挙げることができる。

#### 【0137】

##### 13. 第 11 実施形態(半導体装置)

次に、半導体装置の第 11 実施形態について説明する。

上述の第 6 ~ 10 実施形態では MISPHEMT 構造を元に電流プロック領域を導入した半導体装置について述べてきたが、この電流プロック領域の寄与はゲート絶縁膜が半導体表面の全面に接している構造においても有効である。

以下、電流プロック領域を有する MISPHEMT 構造の半導体装置において、ゲート絶縁膜が半導体表面と接している構成について説明する。なお、第 11 実施形態に示す MISPHEMT 構造の半導体装置においても、上述の第 6 実施形態に示す MISJPHEMT 構造の半導体装置と同様の構成には、同じ符号を付して詳細な説明を省略する。

#### 【0138】

40

50

## (MISPHMET)

第11実施形態の半導体装置の構成を図21に示す。図21に示すように、この半導体装置は、基板11上に、各化合物半導体材料からなるバッファ層12、下部障壁層13、チャネル層14、上部障壁層15、及び、キャップ層22がこの順に積層されている。

下部障壁層13内にはキャリア供給層13aが設けられている。上部障壁層15内には、キャリア供給層15aが設けられている。

また、キャップ層22に、ゲート電極20が形成される開口22cが設けられている。

## 【0139】

そして、以上のような化合物半導体材料からなる各層の積層体上には、キャップ層22上と、キャップ層22の開口22cから露出する高抵抗層15b上を覆って、ゲート絶縁膜16が設けられている。このゲート絶縁膜16には、開口17a, bが設けられている。この開口17a, bには、キャップ層22を介して上部障壁層15に接続されたソース電極18、ドレイン電極19が形成されている。開口22cは、開口17a, bの間に設けられている。開口22cにおいて、ゲート絶縁膜16上にゲート電極20が形成されている。さらに、上部障壁層15の表面であって、ゲート電極20直下を除くゲート絶縁膜16下に電流ブロック領域21が形成される。

## 【0140】

第11実施形態において、基板11、バッファ層12、下部障壁層13、チャネル層14、ソース電極18、ドレイン電極19、ゲート電極20、及び、キャップ層22は、上述の第1実施形態と同様の構成である。また、上部障壁層15は、上述の第6実施形態と同様の構成である。さらに、本例の半導体装置では、キャップ層22上に絶縁層を備えず、キャップ層22上とゲート電極20下とで共通するゲート絶縁膜16を備えていることを除き、上述の第6実施形態と同様の構成である。

## 【0141】

## (電流ブロック領域)

図21に示すように、ゲート絶縁膜16と高抵抗層15bとの界面には、ゲート電極20の直下を除き、ゲート電極20の直下の両脇に電流ブロック領域21が形成される。

図21に示す構成の半導体装置では、ゲート絶縁膜16と高抵抗層15bとの界面準位によってフェルミレベルピンニングが生じる。つまり、ゲート絶縁膜16と上部障壁層15の高抵抗層15bとの界面準位によって高抵抗層15b中に空乏層が生じる。このように、ゲート電極20の両脇において、半導体中に空乏層が広がる効果を、電流ブロック領域21として用いている。

## 【0142】

本例において、界面準位により電流ブロック領域21が形成される様子は、上述の図2A, Bに示すエネルギー・バンド構成により、第1実施形態の構成と同様に説明することができる。図2Aに示すように界面準位密度が低い場合、ゲート電極への電圧印加によって上部障壁層15側に電子が蓄積する。このため、ゲート絶縁膜16と上部障壁層15との界面に電流パスが生じる。これに対し、図2Bに示すように界面準位密度が高い場合、電圧印加によっても上部障壁層15側に電子が蓄積しにくい。このため、ゲート絶縁膜16と上部障壁層15との界面に電流パスが生じない。

## 【0143】

電流ブロック領域21は、ゲート電極20が接していない領域であるため、ゲート電圧印加の影響を受けにくく、正電圧が印加されても空乏層幅が変化しにくい。このため、広いゲート電圧範囲で電流ブロック領域21の効果が期待できる。

一方、ゲート電極20直下では、電圧印加時に影響を大きく受けるため、正電圧が印加された際に空乏層幅が変化しやすく、電流ブロック領域の効果が期待しにくい。このため、この領域は、電流ブロック領域としての寄与は小さい。

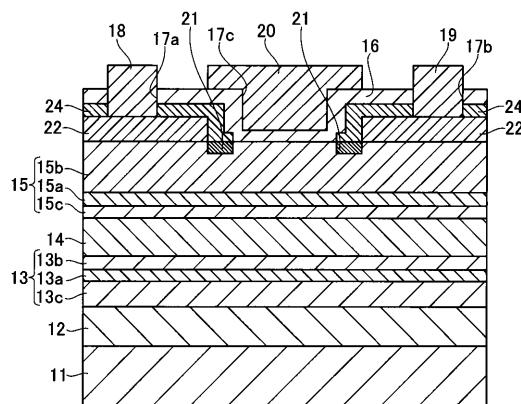

## 【0144】

## 14. 第12実施形態(半導体装置)

次に、半導体装置の第12実施形態について説明する。第12実施形態は、上述の第1

10

20

30

40

50

1 実施形態と同じく、ゲート絶縁膜が半導体表面の全面に接している構成の M I S P H E M T である。また、第 1 2 実施形態において、上述の第 1 1 実施形態と同様の構成には、同じ符号を付して詳細な説明を省略する。

【 0 1 4 5 】

第 1 2 実施形態の半導体装置の構成を、図 2 2 に示す。図 2 2 に示すように、この半導体装置は、基板 1 1 上に、各化合物半導体材料からなるバッファ層 1 2 、下部障壁層 1 3 、チャネル層 1 4 、上部障壁層 1 5 、及び、キャップ層 2 2 がこの順に積層されている。

下部障壁層 1 3 内にはキャリア供給層 1 3 a が設けられている。上部障壁層 1 5 内には、キャリア供給層 1 5 a が設けられている。

また、キャップ層 2 2 に、ゲート電極 2 0 が形成される開口 1 7 c が設けられている。

【 0 1 4 6 】

そして、以上のような化合物半導体材料からなる各層の積層体上には、キャップ層 2 2 上と、キャップ層 2 2 の開口 1 7 c から露出する高抵抗層 1 5 b 上を覆い、且つ、開口 1 7 c 内のゲート電極 2 0 の直下を除く領域に絶縁膜 2 4 が設けられている。さらに、絶縁膜 2 4 上と、開口 1 7 c の底面を覆ってゲート絶縁膜 1 6 が設けられている。

【 0 1 4 7 】

この絶縁膜 2 4 及びゲート絶縁膜 1 6 には、開口 1 7 a , b が設けられている。この開口 1 7 a , b には、キャップ層 2 2 を介して上部障壁層 1 5 に接続されたソース電極 1 8 、ドレイン電極 1 9 が形成されている。開口 1 7 c は、開口 1 7 a , b の間に設けられている。開口 1 7 c において、ゲート絶縁膜 1 6 上にゲート電極 2 0 が形成されている。さらに、上部障壁層 1 5 の表面であって、絶縁膜 2 4 下に電流ブロック領域 2 1 が形成される。

【 0 1 4 8 】

絶縁膜 2 4 と、ゲート絶縁膜 1 6 とは、それぞれ異なる材料から形成されている。絶縁膜 2 4 と高抵抗層 1 5 b との界面に形成される界面準位は、ゲート絶縁膜 1 6 と高抵抗層 1 5 b との間に形成される界面準位に比べて半導体中深い準位にあり、密度も高く設定される。このため、絶縁膜 2 4 と高抵抗層 1 5 b との界面に形成される界面準位は、ゲート電圧印加による空乏層の変化が小さくなっている。従って、高抵抗層 1 5 b と絶縁膜 2 4 の間で反転動作により電子が存在する場合でも電流ブロック領域 2 1 として寄与できる。

【 0 1 4 9 】

このような絶縁膜 2 4 の機能を有する絶縁膜としては、例えば SiN や SiO<sub>2</sub> が挙げられる。一方、ゲート電極 2 0 直下のゲート絶縁膜 1 6 としては、例えば Al<sub>2</sub>O<sub>3</sub> や HfO<sub>2</sub> を用いることができる。

【 0 1 5 0 】

また、絶縁膜 2 4 として、負の固定電荷量や界面ダイポールの量を変えることにより、電流ブロック領域 2 1 を形成してもよい。ゲート絶縁膜 1 6 に用いる材料の固定電荷量の違いによる電流ブロック領域 2 1 の形成については、上述の図 1 3 A 、 B に示すエネルギー・バンド構成により、第 4 実施形態と同様に説明することができる。

図 1 3 B に示すように、固定電荷量や界面ダイポールの量を変えることにより、M I S 界面に蓄積層が形成される電圧をシフトさせることができる。このため、 - Qf / Cox により電子が蓄積されづくなり、電流ブロック領域 2 1 として寄与できる。このように、第 2 ゲート絶縁膜 1 6 B の、負の固定電荷量や、界面ダイポールの量を変えることにより、上部障壁層 1 5 の上部界面に電流ブロック領域 2 1 を形成することが可能である。固定電荷を導入する絶縁膜としては、例えば、Al<sub>2</sub>O<sub>3</sub> 中に H を導入した材料などが報告されている。

【 0 1 5 1 】

本実施形態のように、ゲート絶縁膜が半導体表面の全面に接している構成は、キャップ層上の絶縁層とゲート絶縁膜を一体化させた構成とすることにより上述の第 1 ~ 1 0 実施形態に示す半導体装置にも適用可能である。

【 0 1 5 2 】

10

20

30

40

50

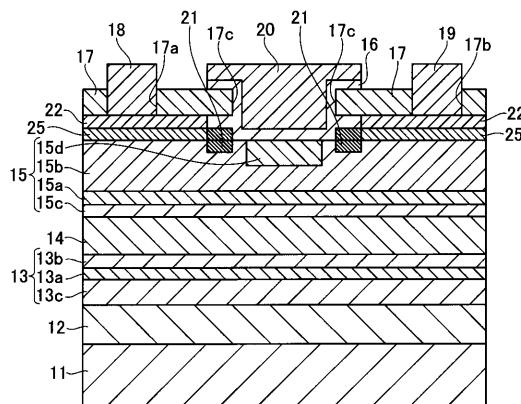

## 15. 第13実施形態(半導体装置)

次に、半導体装置の第13実施形態について説明する。

上述の各実施形態では、ゲート絶縁膜を介してゲート電極と対向する半導体層に、電流プロック領域の最表面が形成される構成について述べてきたが、電流プロック領域の最表面をゲート電極と対向する半導体層と異なる半導体層に形成することもできる。

以下、第1実施形態のMISJPHEMT構造の半導体装置において、電流プロック領域の最表面をゲート電極と対向する半導体層と異なる半導体層に形成する構成について説明する。なお、第13実施形態に示すMISJPHEMT構造の半導体装置においても、上述の第1実施形態に示すMISJPHEMT構造の半導体装置と同様の構成には、同じ符号を付して詳細な説明を省略する。

10

## 【0153】

第13施形態の半導体装置の構成を、図23に示す。図23に示すように、この半導体装置は、基板11上に、各化合物半導体材料からなるバッファ層12、下部障壁層13、チャネル層14、上部障壁層15、インターレイヤー層25、及び、キャップ層22がこの順に積層されている。

下部障壁層13内にはキャリア供給層13aが設けられている。上部障壁層15内にはキャリア供給層15aと共にp型低抵抗領域15dが設けられている。

## 【0154】

また、以上のような化合物半導体材料からなる各層の積層体上には、絶縁層17が設けられている。このゲート絶縁膜16には、開口17a, bが設けられている。この開口17a, bには、キャップ層22及びインターレイヤー層25を介して上部障壁層15に接続されたソース電極18、ドレイン電極19が形成されている。

20

さらに、開口17a, bの間ににおいて、絶縁層17、キャップ層22、及び、インターレイヤー層25には開口17cが設けられている。開口17cは、絶縁層17、キャップ層22、及び、インターレイヤー層25に連続して形成されている。開口17cは、絶縁層17の開口幅とインターレイヤー層25の開口幅とが同じ大きさに形成され、絶縁層17の開口幅よりもキャップ層22の開口幅の方が大きく形成されている。

## 【0155】

開口17cには、この底面及び側面に沿って、上部障壁層15上にゲート絶縁膜16が形成されている。ゲート絶縁膜16の上部にはゲート電極20が形成されている。p型低抵抗領域15dはゲート絶縁膜16を介してゲート電極20直下に形成されている。さらに、ゲート絶縁膜16と接するインターレイヤー層25の表面であって、ゲート電極20直下を除く位置に電流プロック領域21が形成される。電流プロック領域21は、インターレイヤー層25の表面から、高抵抗層15b内まで連続して形成されている。

30

## 【0156】

インターレイヤー層25は、高抵抗層15bに適用する材料よりも、ゲート絶縁膜16との界面に形成される界面準位密度が大きい材料を用いて構成される。例えばInGaP系材料は、絶縁膜との界面に形成される界面準位密度が、GaAs系材料よりも小さいことが、Appl. Phys. Lett., 63, (1993) p.379において報告されている。

従って、本例の半導体装置では、上部障壁層15の高抵抗層15bをInGaP系材料で形成し、インターレイヤー層25をAlGaAs系材料で構成する。この構成により、ゲート絶縁膜16とp型低抵抗領域15dの界面における界面準位密度を低くすることができ、さらに、ゲート絶縁膜16とインターレイヤー層25との界面における界面準位密度を高くすることができ、電流プロック領域を形成できる。

40

## 【0157】

上述のように、上部障壁層15とゲート絶縁膜16との間にインターレイヤー層25を介在させることにより、電流プロック領域が形成される最表面の半導体層と、ゲート絶縁膜16を介してゲート電極20と対向する半導体層とを、異なる層とすることができます。そして、電流プロック領域が形成される最表面の半導体層と、ゲート絶縁膜を介してゲート電極と対向する半導体層とを、それぞれ異なる材料で形成することにより、ゲート電極

50

下の界面準位密度の低減と、電流ブロック領域を両立することができる。

本実施形態では、インターレイヤー層25を介在させる構成を第1実施形態の半導体装置に適用した場合について説明しているが、このような構成は、上述の第2～12実施形態にも適用することができる。

【0158】

[障壁層と異なる導電型]

なお、上述の実施形態では、チャネル層のキャリアが電子である場合の構成について説明しているが、本技術の半導体装置はキャリアが正孔である場合にも適用できる。キャリアが正孔である場合には上述の実施形態において、不純物の導電型及びエネルギー・バンドの説明を障壁層と異なる導電型として、本技術を適用することができる。

10

【0159】

なお、本開示は以下のような構成も取ることができる。

(1) チャネル層と、前記チャネル層上に設けられ、前記チャネル層を構成する半導体よりも高い伝導帯位置を有する高抵抗の半導体からなる高抵抗層と、前記高抵抗層の表面層に設けられ、第1導電型不純物を含む半導体からなる第1導電型の低抵抗領域と、前記低抵抗領域を挟んだ位置において前記高抵抗層に接続されたソース電極及びドレイン電極と、前記低抵抗領域上に設けられたゲート絶縁膜と、前記ゲート絶縁膜を介して前記低抵抗領域上に設けられたゲート電極と、前記低抵抗領域と前記ソース電極及び前記ドレイン電極との間に形成された電流ブロック領域と、を備える半導体装置。

20

(2) 前記電流ブロック領域は、前記高抵抗層と前記ゲート絶縁膜とにおいて形成される界面準位によって、前記高抵抗層の表面に形成される空乏層からなる(1)に記載の半導体装置。

(3) 前記電流ブロック領域上の前記ゲート絶縁膜内に空隙を有する(2)に記載の半導体装置。

(4) 前記電流ブロック領域上の前記ゲート絶縁膜内に、前記ゲート電極よりも仕事関数の大きい金属層を有する(2)に記載の半導体装置。

(5) 前記電流ブロック領域が、第1導電形不純物の拡散領域からなる(1)に記載の半導体装置。

(6) 前記電流ブロック領域上に、前記ゲート絶縁膜と異なる絶縁膜が設けられている(1)に記載の半導体装置。

30

(7) 前記電流ブロック領域の表面層が、前記高抵抗層と異なる半導体層に形成されている(1)から(6)に記載の半導体装置。

(8) 前記ゲート電極直下を除き、前記高抵抗層と前記ゲート絶縁膜との間にインターレイヤー層を有し、前記ゲート絶縁膜との界面の前記インターレイヤー層の表面から前記電流ブロック領域が形成されている(7)に記載の半導体装置。

(9) チャネル層と、前記チャネル層上に設けられ、前記チャネル層を構成する半導体よりも高い伝導帯位置を有する高抵抗の半導体からなる高抵抗層と、前記高抵抗層に接続されたソース電極及びドレイン電極と、前記低抵抗領域上に設けられたゲート絶縁膜と、前記ゲート絶縁膜を介して、前記ソース電極と前記ドレイン電極との間に前記低抵抗領域上に設けられたゲート電極と、前記ゲート電極直下を除く位置で、前記ソース電極と前記ドレイン電極との間に形成された電流ブロック領域と、を備える半導体装置。

40

(10) チャネル層上に、前記チャネル層を構成する半導体よりも高い伝導帯位置を有する高抵抗の半導体からなる高抵抗層を形成し、前記高抵抗層の表面層に、第1導電型不純物を含む半導体からなる第1導電型の低抵抗領域を形成し、前記低抵抗領域を挟んだ位置において前記高抵抗層に接続されたソース電極及びドレイン電極を形成し、前記低抵抗領域上にゲート絶縁膜を形成し、前記ゲート絶縁膜を介して前記低抵抗領域上にゲート電極を形成し、前記低抵抗領域と前記ソース電極及び前記ドレイン電極との間に電流ブロック領域を形成する半導体装置の製造方法。

(11) チャネル層上に、前記チャネル層を構成する半導体よりも高い伝導帯位置を有する高抵抗の半導体からなる高抵抗層を形成し、前記高抵抗層に接続されたソース電極及び

50

ドレイン電極を形成し、前記低抵抗領域上にゲート絶縁膜を形成し、前記ゲート絶縁膜を介して、前記ソース電極と前記ドレイン電極との間の前記高抵抗層上にゲート電極を形成し、前記ゲート電極直下を除く、前記ソース電極と前記ドレイン電極との間に電流プロック領域を形成する半導体装置の製造方法。

## 【符号の説明】

## 【0160】

11, 101, 111 基板、12, 102 バッファ層、13 下部障壁層、13a, 15a, 14a, 103a, 105a キャリア供給層、13b, 13c, 15b, 15c, 103b, 103c, 105b, 105c, 115b 高抵抗層、14, 104 チャネル層、15 上部障壁層、15d, 105d, 1115c p型低抵抗領域、16, 16A, 117 ゲート絶縁膜、16A 第1ゲート絶縁膜、16B 第2ゲート絶縁膜、17 絶縁層、17a, 17b, 17c, 17d, 22c 開口、18, 108, 1118 ソース電極、19, 109, 1119 ドレイン電極、20, 106, 1116 ゲート電極、20A 第1ゲート電極、20B 第2ゲート電極、21 電流プロック領域、22 キャップ層、23 空隙、24, 1116 絶縁膜、25 インターレイヤー層、103 第2障壁層、105 第1障壁層、113 ベース層

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図9】

【図7】

【図8】

【図10】

【図11】

【図12】

【図14】

【図13】

【図15】

【図16】

【図18】

【図17】

【図19】

【図20】

### 【図21】

### 【図23】

【図22】

### 【図24】

【 図 25 】

---

フロントページの続き

(51)Int.Cl. F I

H 01L 29/41 (2006.01)

H 01L 29/423 (2006.01)

H 01L 29/49 (2006.01)

(56)参考文献 特開2004-273486 (JP, A)

特開平11-274175 (JP, A)

特開2010-186943 (JP, A)

特開2010-067816 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01L 21/336-338

H 01L 27/095-098

H 01L 29/41

H 01L 29/423

H 01L 29/49

H 01L 29/778

H 01L 29/78

H 01L 29/80-812