(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5272697号

(P5272697)

(45) 発行日 平成25年8月28日(2013.8.28)

(24) 登録日 平成25年5月24日(2013.5.24)

|              |                |

|--------------|----------------|

| (51) Int.Cl. | F 1            |

| G09G 3/30    | (2006.01)      |

| G09G 3/20    | (2006.01)      |

| HO4N 5/208   | (2006.01)      |

|              | GO9G 3/30 Z    |

|              | GO9G 3/20 611A |

|              | GO9G 3/20 612U |

|              | GO9G 3/20 632F |

|              | HO4N 5/208     |

請求項の数 9 (全 27 頁)

|           |                               |                                                  |

|-----------|-------------------------------|--------------------------------------------------|

| (21) 出願番号 | 特願2008-318216 (P2008-318216)  | (73) 特許権者 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号 |

| (22) 出願日  | 平成20年12月15日 (2008.12.15)      | (74) 代理人 100086841<br>弁理士 脇 篤夫                   |

| (65) 公開番号 | 特開2010-139944 (P2010-139944A) | (74) 代理人 100114122<br>弁理士 鈴木 伸夫                  |

| (43) 公開日  | 平成22年6月24日 (2010.6.24)        | (72) 発明者 小澤 淳史<br>東京都港区港南1丁目7番1号 ソニー株式会社内        |

| 審査請求日     | 平成23年10月28日 (2011.10.28)      | (72) 発明者 内野 勝秀<br>東京都港区港南1丁目7番1号 ソニー株式会社内        |

|           |                               | 審査官 小川 浩史                                        |

最終頁に続く

(54) 【発明の名称】表示装置、表示データ処理装置、表示データ処理方法

## (57) 【特許請求の範囲】

## 【請求項 1】

入力される表示データ信号に、エッジ成分を付加する処理を行うエッジ付加処理部と、上記エッジ付加処理部から出力される表示データ信号による発光消費電力が、上記エッジ付加処理部に入力される表示データ信号の発光消費電力以下となるようにするエッジ処理制御信号を生成するエッジ処理制御信号生成部と、

入力される表示データ信号のエッジ成分を抽出するエッジ抽出部と、

上記エッジ処理制御信号に基づいて、上記エッジ抽出部で抽出されたエッジ成分のプラス方向のエッジ強調量とマイナス方向のエッジ強調量を別々に設定してエッジ波形補正処理を行い、上記エッジ付加処理部に出力するエッジ補正部と、

上記エッジ付加処理部から出力される表示データ信号に基づいて表示動作を行う表示部と、

を備えた表示装置。

## 【請求項 2】

上記エッジ処理制御信号生成部は、上記エッジ付加処理部に入力される表示データ信号と、上記エッジ付加処理部から出力される表示データ信号のそれぞれについての発光消費電力を算出し、各発光消費電力の算出結果を用いて、上記エッジ処理制御信号を生成する請求項1に記載の表示装置。

## 【請求項 3】

上記エッジ処理制御信号は、上記エッジ補正部におけるエッジ成分のプラス方向のクリ

ップレベルとマイナス方向のクリップレベルの少なくとも一方を可変制御する信号であり、

上記エッジ補正部は、上記エッジ処理制御信号に基づく設定状態におけるプラス方向のクリップレベルとマイナス方向のクリップレベルにより決定されるプラスエッジ係数とマイナスエッジ係数を用いた係数演算で、エッジ波形補正処理を行う請求項2に記載の表示装置。

【請求項4】

上記エッジ処理制御信号生成部は、上記エッジ補正部におけるエッジ成分のマイナス方向のクリップレベルを低下させる方向に可変制御することを優先し、マイナス方向のクリップレベルを所定レベルまで低下させた後で必要がある場合に、上記エッジ補正部におけるエッジ成分のプラス方向のクリップレベルを低下させる方向に可変制御するように、上記エッジ処理制御信号を生成する請求項3に記載の表示装置。 10

【請求項5】

上記エッジ処理制御信号生成部は、上記エッジ補正部におけるエッジ成分のプラス方向のクリップレベルを低下させる方向に可変制御することを優先し、プラス方向のクリップレベルを所定レベルまで低下させた後で必要がある場合に、上記エッジ補正部におけるエッジ成分のマイナス方向のクリップレベルを低下させる方向に可変制御するように、上記エッジ処理制御信号を生成する請求項3に記載の表示装置。

【請求項6】

上記エッジ処理制御信号生成部は、上記エッジ補正部におけるエッジ成分のプラス方向のクリップレベルとマイナス方向のクリップレベルを同時に低下させる上記エッジ処理制御信号を生成する請求項3に記載の表示装置。 20

【請求項7】

上記エッジ処理制御信号生成部は、上記エッジ処理制御信号により、上記エッジ補正部におけるエッジ成分のプラス方向のクリップレベルと、マイナス方向のクリップレベルのうちの一方のみを可変制御する請求項3に記載の表示装置。

【請求項8】

入力される表示データ信号に、エッジ成分を付加する処理を行うエッジ付加処理部と、上記エッジ付加処理部から出力される表示データ信号による発光消費電力が、上記エッジ付加処理部に入力される表示データ信号の発光消費電力以下となるようにするエッジ処理制御信号を生成するエッジ処理制御信号生成部と、 30

入力される表示データ信号のエッジ成分を抽出するエッジ抽出部と、

上記エッジ処理制御信号に基づいて、上記エッジ抽出部で抽出されたエッジ成分のプラス方向のエッジ強調量とマイナス方向のエッジ強調量を別々に設定してエッジ波形補正処理を行い、上記エッジ付加処理部に出力するエッジ補正部と、

を備えた表示データ処理装置。

【請求項9】

入力される表示データ信号のエッジ成分を抽出するエッジ抽出ステップと、エッジ付加処理によって出力される表示データ信号による発光消費電力が、エッジ付加処理に供される表示データ信号の発光消費電力以下となるようにするエッジ処理制御信号を生成するエッジ処理制御信号生成ステップと、 40

上記エッジ処理制御信号に基づいて、上記エッジ抽出ステップで抽出されたエッジ成分のプラス方向のエッジ強調量とマイナス方向のエッジ強調量を別々に設定してエッジ波形補正処理を行うエッジ補正ステップと、

入力される表示データ信号に、上記エッジ補正ステップで得られたエッジ成分を付加する処理を行って出力するエッジ付加ステップと、

を備えた表示データ処理方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、例えば有機 E L (Electroluminescence) パネル等を用いた表示装置、又は表示装置に内蔵される表示データ処理装置、及び表示データ処理方法に関する。

【背景技術】

【0002】

【特許文献1】特開2007-221821号公報

【特許文献2】特開2007-249436号公報

【特許文献3】特開2006-236159号公報

【0003】

フラットパネルディスプレイは、コンピュータディスプレイ、携帯端末、テレビなどの製品で広く普及している。現在、主には液晶ディスプレイパネルが多く採用されているが、依然、視野角の狭さや、応答速度の遅さが指摘され続けている。

一方、自発光素子で形成された有機 E L ディスプレイは、前記の視野角や応答性の課題を克服できるのに加え、バックライト不要の薄い形態、高輝度、高コントラストを達成できるため、液晶ディスプレイに代わる次世代表示装置として期待されている。

但し有機 E L ディスプレイは、現在実用化されているものも存在する中でありながら、消費電力の高さがまだまだ問題視されている。

全ての表示装置にとっても共通して言えることでもあるが、消費電力を抑えることは、取組むべき大きな課題として捉えられている。

また、高画質化、高視認性ということも、各種の表示装置の課題とされている。

【0004】

高画質化、高視認性を実現する手段として、エッジ（輪郭）強調という画像処理手法がある。

この手法は画像の高周波成分を強調することによって画像全体を鮮鋭化し、画質向上を実現するものとして一般的なものである。この場合、一つはエッジ部分のコントラスト感が上がること、もう一つはプラス方向へ強調されるエッジの輝度が上がることによって、画質向上や視認性向上が実現されると考えられている。

【0005】

従来、エッジ強調並びに高画質化や、電力抑制という点で、上記特許文献1, 2, 3に開示された技術が提案されていた。

特許文献1の技術は、エッジ成分の一画面分のヒストグラムを抽出し、ヒストグラムの結果に応じてエッジ強調量をコントロールすることで、映像の状態に応じた適切なエッジ強調処理と可能とする。

また特許文献2の技術は、エッジ成分から、映像のダイナミックレンジを超えない範囲で有効的に使用されるエッジ強調量ゲインを動的に算出し、映像に適切なエッジ強調処理を実現する。

【0006】

また特許文献3では、アプリケーション使用状態によって、最適が映像処理機能のみを機能させ、不要な映像処理機能をオフすることで、電力抑制を実現することが記載されている。

【発明の開示】

【発明が解決しようとする課題】

【0007】

ここで、有機 E L ディスプレイ等の自発光ディスプレイについて考える。

自発光ディスプレイでは、画面内の平均表示輝度が高いほど、消費電力を多く必要とする。従って、明るく綺麗な表示を実現する、一般的な高画質化と低消費電力化を両立させることは今まで困難とされてきた。

【0008】

例えば L C D ディスプレイにおいては、バックライトの輝度が消費電力をほぼ決定しており、上記特許文献1, 2のようなエッジ強調の画像処理を行っても消費電力の増減が発生しない。ところがフラットパネルディスプレイの中でも有機 E L や P D P ( プラズマデ

10

20

30

40

50

イスプレイ)といった自発光デバイスは、消費電力増減の影響を受けるという問題が存在する。つまり有機ELディスプレイの場合、エッジ強調により画質は向上できるが、エッジ強調部分の輝度の上昇によって消費電力の大きくなり、消費電力抑制の要請と相反した状態となる。

#### 【0009】

また特許文献3では、不要な機能そのものの動作を止めてしまふことで、低電力化を実現することができるが、基本的に機能を動作させたまま低電力化を実現することはできない。即ち、低電力化を実現するために、エッジ強調などの機能そのものを止めてしまわなければならない。結局こののような技術も、有機ELディスプレイにおいて高画質化、高視認性と、消費電力低減を両立できない。

10

#### 【0010】

このように従来は、エッジ強調を画像の状態に応じて適切に行なうことは出来ていたが、自発光ディスプレイで採用する場合、電力の増加を抑制できるものは存在していなかった。また、電力抑制を実現するためには、高画質化する機能そのものを止めてしまうしかないという状況であった。つまり、消費電力を低減しながら、エッジ強調処理を実現させる手法は存在していなかった。

そこで本発明では、エッジ強調による視認性の維持又は向上を行いつつ、消費電力を増加させないようにすることができる手法を提案する。

#### 【課題を解決するための手段】

#### 【0011】

20

本発明の表示装置は、入力される表示データ信号にエッジ成分を付加する処理を行うエッジ付加処理部と、上記エッジ付加処理部から出力される表示データ信号による発光消費電力が、上記エッジ付加処理部に入力される表示データ信号の発光消費電力以下となるようにするエッジ処理制御信号を生成するエッジ処理制御信号生成部と、入力される表示データ信号のエッジ成分を抽出するエッジ抽出部と、上記エッジ処理制御信号に基づいて、上記エッジ抽出部で抽出されたエッジ成分のプラス方向のエッジ強調量とマイナス方向のエッジ強調量を別々に設定してエッジ波形補正処理を行い、上記エッジ付加処理部に出力するエッジ補正部と、上記エッジ付加処理部から出力される表示データ信号に基づいて表示動作を行う表示部とを備える。

#### 【0012】

30

また、上記エッジ処理制御信号生成部は、上記エッジ付加処理部に入力される表示データ信号と、上記エッジ付加処理部から出力される表示データ信号のそれぞれについての発光消費電力を算出し、各発光消費電力の算出結果を用いて、上記エッジ処理制御信号を生成する。

また上記エッジ処理制御信号は、上記エッジ補正部におけるエッジ成分のプラス方向のクリップレベルとマイナス方向のクリップレベルの少なくとも一方を可変制御する信号であり、上記エッジ補正部は、上記エッジ処理制御信号に基づく設定状態におけるプラス方向のクリップレベルとマイナス方向のクリップレベルにより決定されるプラスエッジ係数とマイナスエッジ係数を用いた係数演算で、エッジ波形補正処理を行う。

#### 【0013】

40

また上記エッジ処理制御信号生成部は、上記エッジ補正部におけるエッジ成分のマイナス方向のクリップレベルを低下させる方向に可変制御することを優先し、マイナス方向のクリップレベルを所定レベルまで低下させた後で必要がある場合に、上記エッジ補正部におけるエッジ成分のプラス方向のクリップレベルを低下させる方向に可変制御するよう、上記エッジ処理制御信号を生成する。

或いは上記エッジ処理制御信号生成部は、上記エッジ補正部におけるエッジ成分のプラス方向のクリップレベルを低下させる方向に可変制御することを優先し、プラス方向のクリップレベルを所定レベルまで低下させた後で必要がある場合に、上記エッジ補正部におけるエッジ成分のマイナス方向のクリップレベルを低下させる方向に可変制御するよう、上記エッジ処理制御信号を生成する。

50

或いは上記エッジ処理制御信号生成部は、上記エッジ補正部におけるエッジ成分のプラス方向のクリップレベルとマイナス方向のクリップレベルを同時に低下させる上記エッジ処理制御信号を生成する。

或いは上記エッジ処理制御信号生成部は、上記エッジ処理制御信号により、上記エッジ補正部におけるエッジ成分のプラス方向のクリップレベルと、マイナス方向のクリップレベルのうちの一方のみを可変制御する。

【0014】

本発明の表示データ処理装置は、入力される表示データ信号に、エッジ成分を付加する処理を行うエッジ付加処理部と、上記エッジ付加処理部から出力される表示データ信号による発光消費電力が、上記エッジ付加処理部に入力される表示データ信号の発光消費電力以下となるようにするエッジ処理制御信号を生成するエッジ処理制御信号生成部と、入力される表示データ信号のエッジ成分を抽出するエッジ抽出部と、上記エッジ処理制御信号に基づいて、上記エッジ抽出部で抽出されたエッジ成分のプラス方向のエッジ強調量とマイナス方向のエッジ強調量を別々に設定してエッジ波形補正処理を行い、上記エッジ付加処理部に出力するエッジ補正部とを備える。

【0015】

本発明の表示データ処理方法は、入力される表示データ信号のエッジ成分を抽出するエッジ抽出ステップと、エッジ付加処理によって出力される表示データ信号による発光消費電力が、エッジ付加処理に供される表示データ信号の発光消費電力以下となるようにするエッジ処理制御信号を生成するエッジ処理制御信号生成ステップと、上記エッジ処理制御信号に基づいて、上記エッジ抽出ステップで抽出されたエッジ成分のプラス方向のエッジ強調量とマイナス方向のエッジ強調量を別々に設定してエッジ波形補正処理を行うエッジ補正ステップと、入力される表示データ信号に、上記エッジ補正ステップで得られたエッジ成分を付加する処理を行って出力するエッジ付加ステップとを備える。

【0016】

このような本発明では、エッジ強調度、映像信号の内容によらず、入力表示データ信号から推定計算される発光消費電力に対し、出力表示データ信号から推定計算される発光消費電力が必ず低くなるように、プラス方向のエッジ強調量とマイナス方向のエッジ強調量を別々にコントロールするものである。これにより、エッジ強調処理の視認性改善効果を維持しつつ、自発光ディスプレイ独自の課題である消費電力の増大を確実に防止する。

【0017】

先に述べたように、自発光ディスプレイでは、エッジ強調を行うことで画質は向上するが、エッジ部分の輝度の上昇により消費電力は上昇する。

ここで、プラス方向へのエッジ成分は輝度を増大させ消費電力を増加させるが、マイナス方向へのエッジ成分は輝度を減少させ消費電力を減少することになる。

通常のエッジ強調であればプリエッジとオーバーエッジは、階調に対して均等につけられる。但し、通常ディスプレイパネルモジュールは、入力映像信号の階調に対する輝度の変化を表すガンマ特性が $2 \cdot 2$ 乗に近い特性をしていることが一般的であり、これはCRTの持っている特性に合わせて構築された撮像/受像のしくみがそのまま現在まで継承されていることによる。この結果、自発光ディスプレイデバイスにおいては、プラス方向のエッジ強調により増加する消費電力の方が、マイナス方向のエッジ強調により減少する消費電力より大きくなり、映像信号でプリエッジとオーバーエッジを同量強調しても、消費電力で考えると必ず増加が起こってしまうことが言える。

これに対して本発明では、プラス方向のエッジに対してマイナス方向のエッジをより大きくするように非対称強調をすることによって電力の増加を防止する。これによって電力増加を伴わないエッジ強調を実現する。

【発明の効果】

【0018】

本発明によれば、エッジ強調処理における画質/視認性改善効果を維持しながら、その際に伴ってしまう自発光ディスプレイ特有の課題である消費電力の上昇を、確実に防止す

10

20

30

40

50

することができるという効果がある。

【発明を実施するための最良の形態】

【0019】

以下、本発明の実施の形態を次の順序で説明する。

[1. 表示装置構成]

[2. 表示データ処理部の構成]

[3. 表示データ処理部による電力抑制エッジ強調]

[4. エッジ制御係数決定処理の他の例]

[5. 変形例]

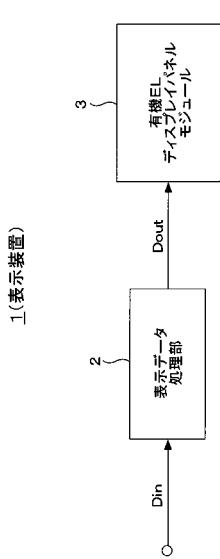

【0020】

[1. 表示装置構成]

10

図1に実施の形態の表示装置の要部の構成を示す。本例の表示装置1は、有機EL素子を発光素子として用いる有機ELディスプレイパネルモジュール3を有する。

そして有機ELディスプレイパネルモジュール3に対して供給する表示データ信号について処理を行う部位として、表示データ処理部2が設けられる。表示データ処理部2は、表示データ信号Dinに対して後述する処理を行い、処理後の表示データ信号Doutを有機ELディスプレイパネルモジュール3に供給する。

【0021】

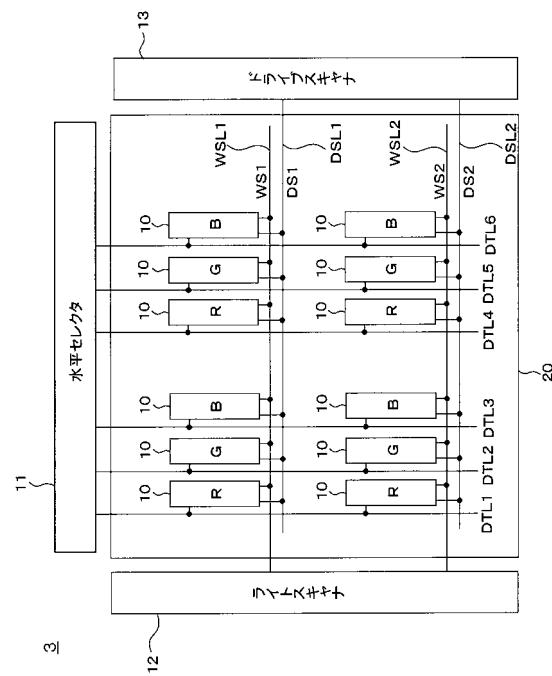

図2、図3を参照して有機ELディスプレイパネルモジュール3について述べる。

20

図2に有機ELディスプレイパネルモジュール3の構成の一例を示す。この有機ELディスプレイパネルモジュール3は、有機EL素子を発光素子とし、アクティブマトリクス方式で発光駆動を行う画素回路10を含むものである。

【0022】

図2に示すように、有機ELディスプレイパネルモジュール3は、画素回路10が列方向と行方向にマトリクス状に配列された画素アレイ部20を備える。なお、画素回路10には「R」「G」「B」を付しているが、これはR(赤)、G(緑)、B(青)の各色の発光画素であることを示している。

【0023】

そしてこの画素アレイ部20の各画素回路10を駆動するため、水平セレクタ(データドライバ)11と、ライトスキャナ(書き込みスキャナ)12と、ドライブスキャナ(駆動制御スキャナ)13を備える。

30

また水平セレクタ11により選択され、輝度情報に応じた映像信号を画素回路10に対する入力信号として供給する信号線DTL1、DTL2…が、画素アレイ部20に対して列方向に配されている。信号線DTL1、DTL2…は、画素アレイ部20においてマトリクス配置された画素回路10の列数分だけ配される。

【0024】

また画素アレイ部20に対して、行方向に書き込み制御線WSL1, WSL2…、電源制御線DSL1, DSL2…が配されている。これらの書き込み制御線WSL及び電源制御線DSLは、それぞれ、画素アレイ部20においてマトリクス配置された画素回路10の行数分だけ配される。

40

書き込み制御線WSL(WSL1, WSL2…)はライトスキャナ12により駆動される。ライトスキャナ12は、設定された所定のタイミングで、行状に配設された各書き込み制御線WSL1, WSL2…に順次、走査パルスWS(WS1, WS2…)を供給して、画素回路10を行単位で線順次走査する。

電源制御線DSL(DSL1, DSL2…)はドライブスキャナ13により駆動される。ドライブスキャナ13は、ライトスキャナ12による線順次走査に合わせて、行状に配設された各電源制御線DSL1, DSL2…に駆動電位(Vcc)、初期電位(Vini)の2値に切り替わる電源電圧としての電源パルスDS(DS1, DS2…)を供給する。

50

水平セレクタ 11 は、ライトスキャナ 12 による線順次走査に合わせて、列方向に配された信号線 DTL1、DTL2・・・に対して、画素回路 10 に対する入力信号としての信号電位 (Vsig) と基準電位 (Voff) を供給する。

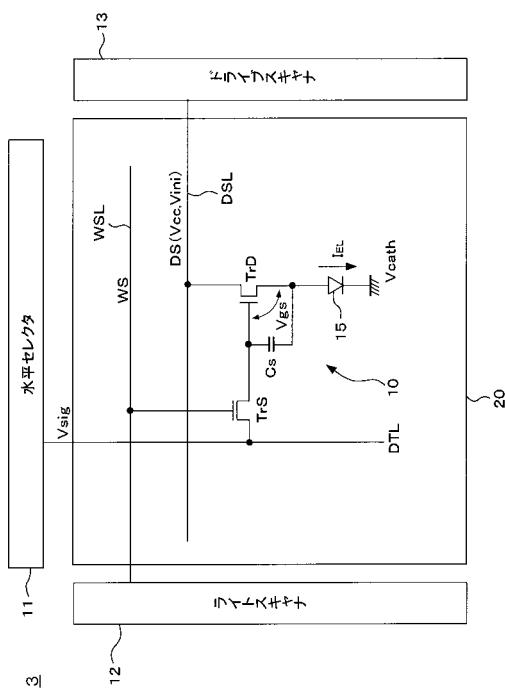

【0025】

図 3 に画素回路 10 の構成を示している。この画素回路 10 が、図 2 の構成における画素回路 10 のようにマトリクス配置される。なお、図 3 では簡略化のため、信号線 DTL と書込制御線 WSL 及び電源制御線 DSL が交差する部分に配される 1 つの画素回路 10 のみを示している。

【0026】

この画素回路 10 は、発光素子である有機 EL 素子 15 と、1 個の保持容量 Cs と、サンプリングトランジスタ TrS、駆動トランジスタ TrD としての 2 個の薄膜トランジスタ (TFT) とで構成されている。サンプリングトランジスタ TrS、駆動トランジスタ TrD は n チャネル TFT とされている。

【0027】

保持容量 Cs は、一方の端子が駆動トランジスタ TrD のソースに接続され、他方の端子が同じく駆動トランジスタ TrD のゲートに接続されている。

画素回路 10 の発光素子は例えばダイオード構造の有機 EL 素子 15 とされ、アノードとカソードを備えている。有機 EL 素子 15 のアノードは駆動トランジスタ TrD のソース s に接続され、カソードは所定の接地配線 (カソード電位 Vcath) に接続されている。

サンプリングトランジスタ TrS は、そのドレインとソースの一端が信号線 DTL に接続され、他端が駆動トランジスタ TrD のゲートに接続される。またサンプリングトランジスタ TrS のゲートは書込制御線 WSL に接続されている。

駆動トランジスタ TrD のドレインは電源制御線 DSL に接続されている。

【0028】

有機 EL 素子 15 の発光駆動は、基本的には次のようになる。

信号線 DTL に信号電位 Vsig が印加されたタイミングで、サンプリングトランジスタ TrS が書込制御線 WSL によってライトスキャナ 12 から与えられる走査パルス WS によって導通される。これにより信号線 DTL からの入力信号 Vsig が保持容量 Cs に書き込まれる。駆動トランジスタ TrD は、ドライブスキャナ 13 によって駆動電位 V1 が与えられている電源制御線 DSL からの電流供給により、保持容量 Cs に保持された信号電位に応じた電流 IEL を有機 EL 素子 15 に流し、有機 EL 素子 15 を発光させる。

【0029】

つまり、各フレーム期間において、画素信号値 (階調値) が保持容量 Cs に書き込まれる動作が行われるが、これにより、階調値によって駆動トランジスタ TrD のゲート - ソース間電圧 Vgs が決まる。駆動トランジスタ TrD は飽和領域で動作することで有機 EL 素子 15 に対して定電流源として機能し、ゲート - ソース間電圧 Vgs に応じた電流 IEL を有機 EL 素子 15 に流す。これによって有機 EL 素子 15 では、階調値に応じた輝度の発光が行われる。

【0030】

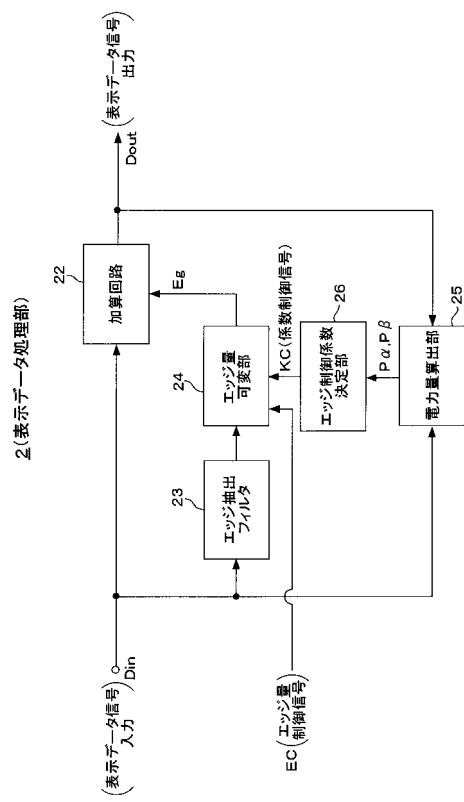

[ 2 . 表示データ処理部の構成 ]

表示データ処理部 2 の構成を説明する。

本実施の形態では、図 1 に示したように、表示データ信号 D in は、表示データ処理部 2 で必要な処理を施され、その処理後の表示データ信号 D out が有機 EL ディスプレイパネルモジュール 3 に供給される。

有機 EL ディスプレイパネルモジュール 3 においては、表示データ信号 D out が図 2 の水平セレクタ 11 に供給され、水平セレクタ 11 は、表示データ信号 D out に基づく各画素毎の信号値 Vsig を、各画素回路 10 に与えることになる。

10

20

30

40

50

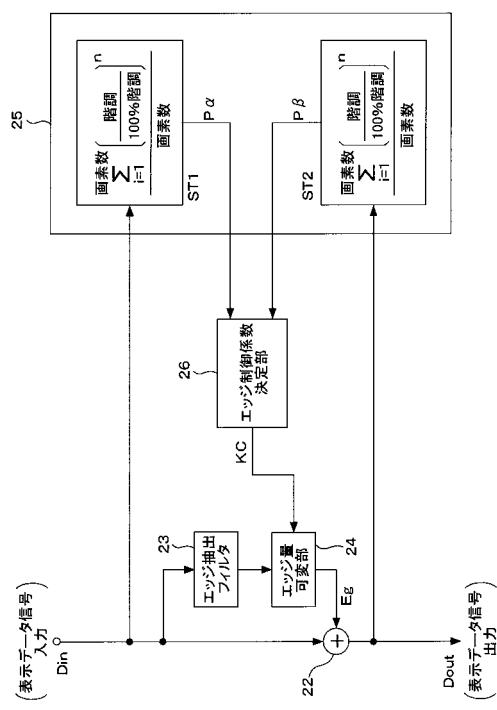

## 【0031】

ここで表示データ処理部2の処理は、特に表示データ信号に対するエッジ強調処理を行うことによる高画質化、視認性向上を図ると共に、そのエッジ強調の際のエッジ成分の波形について、プラス方向のエッジ強調量とマイナス方向のエッジ強調量を別々に設定してエッジ波形補正処理を行うことで、有機ELディスプレイパネルモジュール3における消費電力の削減を図るものである。

## 【0032】

図4に表示データ処理部2の構成例を示す。

表示データ処理部2は、加算回路22、エッジ抽出フィルタ23、エッジ量可変部24、電力量算出部25、エッジ制御係数決定部26を備える。

10

## 【0033】

表示データ信号Dinは、加算回路22、エッジ抽出フィルタ23、電力量算出部25にそれぞれ入力される。

## 【0034】

エッジ抽出フィルタ23は、表示データ信号Dinのエッジ成分（高周波成分）を抽出する。

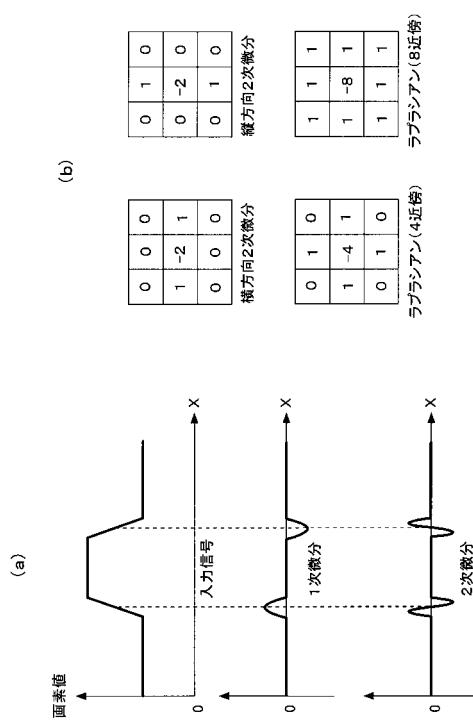

図5(a)にエッジ抽出フィルタ23によるエッジ抽出の例を示す。一般的にエッジ（高周波成分）を抽出するフィルタは、プリシート、オーバーシュートの双方の強調を行うため、2次微分フィルタ(HPF)が使用される。エッジ抽出フィルタ23は、図示するように入力信号（表示データ信号Din）のエッジについて、2次微分波形を取り出すものとなる。

20

2次微分フィルタの例としては図5(b)のように、対象画素に対し周囲の近傍データが使われるが、空間方向で考えて、横方向のみ：横方向2次微分、縦方向のみ：縦方向2次微分、縦横方向：ラプラシアン（4近傍）、縦横斜め方向：ラプラシアン（8近傍）のディジタルフィルタが使用されることが一般的となっている。

## 【0035】

エッジ量可変部24は、エッジ抽出フィルタ23から出力されるエッジ成分の補正処理を、エッジ制御係数決定部26からの係数制御信号KCに基づいて行う。またエッジ量のレベルを、図示しない制御系から供給されるエッジ量制御信号ECに基づいて可変する。

なお、エッジ量制御信号ECは、表示装置1に対するユーザの操作、或いはアプリケーションプログラムによる処理などに応じて、図示しない制御系によって所要の値として供給されるもので、エッジ強調の度合いを制御する信号である。

30

## 【0036】

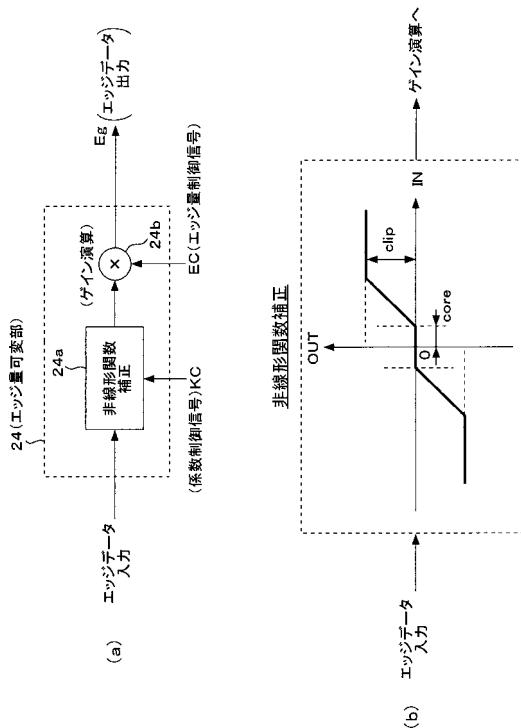

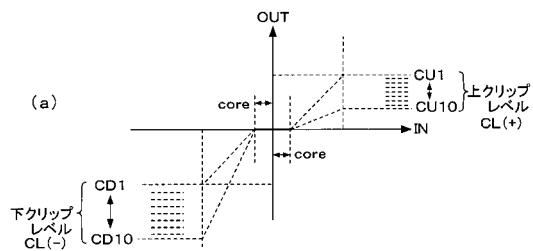

図6(a)はエッジ量可変部24の一例を示している。

エッジ量可変部24は、非線形関数補正回路24aとゲイン演算回路24bを有する。

非線形関数補正回路24aは、ノイズ強調の抑制とプリシート/オーバーシュート（大振幅エッジ強調）の抑制の2つが主な目的になっている。前者はコアリング、後者はクリッピングと呼ばれる。

図6(b)に一般的なコアリング及びクリッピングの様子を示す。

図示するように、抽出したエッジ量の大きさに応じて出力するエッジを「core」「clip」の2つのパラメータで制限する。

40

コアリングのパラメータ「core」は、ノイズ量に応じて決定される。

クリッピングのパラメータ「clip」は、大振幅エッジの強調を抑えるように決定される。

両パラメータは一般的には固定値として与えられ、エッジ強調による画質悪化を抑制する役目を担っており、画像を見て適値が決められる。

但し本実施の形態では、パラメータ「clip」によるクリップレベルが、エッジ制御係数決定部26からの係数制御信号KCによって可変制御される。これによって非線形関数補正回路24aが、エッジ成分の波形について、プラス方向のエッジ強調量とマイナス方向のエッジ強調量を別々に設定してエッジ波形補正処理を行う。詳しくは後述する。

50

## 【0037】

ゲイン演算回路24bは、非線形関数補正回路24aで補正されたエッジ成分と、入力されるエッジ量制御信号E\_Cの乗算を行う。エッジ量制御信号E\_Cの乗算によって表示データ信号に付加するエッジ量がコントロールされる。例えばユーザの好み等によってエッジ強調の度合いが調整されるようとするためのものである。

このゲイン演算回路24bの出力が、エッジデータE\_gとして図4の加算回路22に供給されることになる。

## 【0038】

加算回路22は、入力された表示データ信号にエッジデータE\_gを加算する処理を行う。

10

即ち、表示データ信号にエッジデータE\_gを付加し、エッジ強調された表示データ信号D\_outを得る。この表示データ信号D\_outが、有機ELディスプレイパネルモジュール3に供給される。

## 【0039】

電力量算出部25には、表示データ信号D\_inと、表示データ信号D\_outが供給される。そして電力量算出部25は、1フレーム毎に、入力される表示データ信号D\_in、D\_outのそれぞれについて、発光消費電力を推定算出する。そして算出した発光消費電力P<sub>+</sub>、P<sub>-</sub>をエッジ制御係数決定部26に出力する。

エッジ制御係数決定部26は、電力量算出部25から供給される表示データ信号D\_inでの推定発光消費電力P<sub>+</sub>と、表示データ信号D\_outでの推定発光消費電力P<sub>-</sub>とに基づいて、エッジ量可変部24に与える係数制御信号K\_Cを生成し、出力する。

20

例えばエッジ制御係数決定部26は、推定消費電力P<sub>+</sub>、P<sub>-</sub>の比較結果に基づいて係数制御信号K\_Cを生成する。

## 【0040】

電力量算出部25及びエッジ制御係数決定部26の具体的な処理例については後述するが、係数制御信号K\_Cは、図6の非線形関数補正回路24aにおいてクリップレベルをコントロールする信号となる。

そして、この非線形関数補正回路24aが、係数制御信号K\_Cに基づいてプラス方向のエッジ強調量とマイナス方向のエッジ強調量をそれぞれ設定してエッジ波形補正処理を行うことで、エッジ強調度、映像信号の内容によらず、入力表示データ信号から推定計算される発光消費電力に対し、出力表示データ信号から推定計算される発光消費電力が必ず低くなるようにコントロールされるものである。

30

## 【0041】

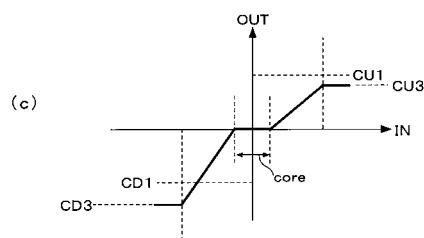

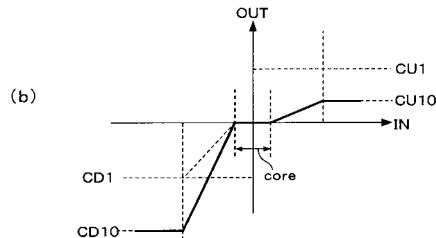

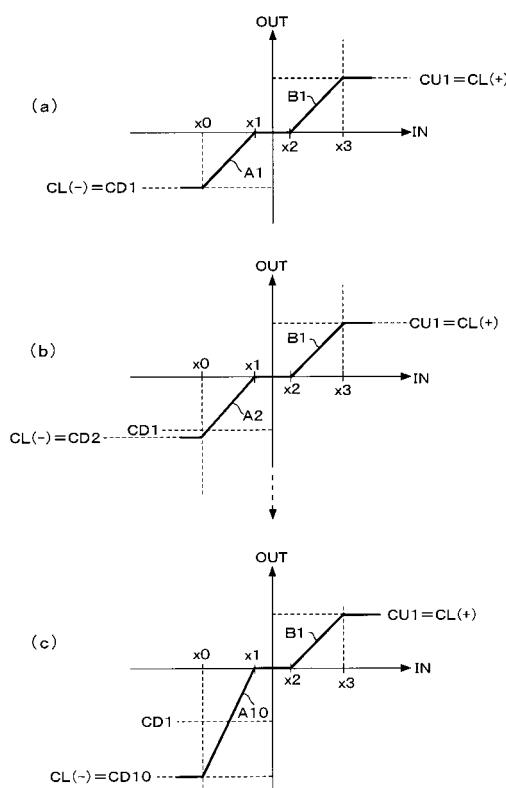

図7に非線形関数補正回路24aにおけるクリップレベルの可変制御の例を示す。

なお上述のようにクリップレベルはクリッピングのパラメータ「c1ip」として設定されるが、本例ではプラス側のクリップレベルとマイナス側のクリップレベルが個別に可変設定される。以下では、プラス側のクリップレベルを「上クリップレベルCL(+)」、マイナス側のクリップレベルを「下クリップレベルCL(-)」と呼ぶこととする。

## 【0042】

40

例えば非線形関数補正回路24aでの上下クリップレベルは、初期状態では図6(b)のように設定されている。

ここで本例では図7(a)に示すように、下クリップレベルCL(-)が「CD1」～「CD10」の10段階に可変設定されるものとし、上クリップレベルCL(+)が「CU1」～「CU10」の10段階に可変設定されるものとする。

なお、以下ではこのように上下クリップレベルCL(+)、CL(-)がそれぞれ10段階に可変設定可能とされた例で説明を続けるが、10段階というのは一例にすぎず、複数段階であれば何段階でも良い。また上クリップレベルCL(+)の可変段階数と下クリップレベルCL(-)の可変段階数が同数である必要もない。

また、1段階毎のレベル差は適切に設定されるものであるが、各段階で等レベル間隔で

50

ある必要もなく、さらに下クリップレベルCL(-)の各段階のレベル差と上クリップレベルCL(+)の各段階のレベル差が同様である必要もない。

#### 【0043】

図6(b)に示した初期状態とは、例えば図7(a)において下クリップレベルCL(-)としてCD1、上クリップレベルCL(+)としてCU1が設定されている状態である。絶対値レベルとしてCD1=CU1である。

本例では、この下クリップレベルCL(-)と上クリップレベルCL(+)が、係数制御信号KCによって可変制御される。

例えば図7(b)は、係数制御信号KCによって下クリップレベルCL(-)=CD10, 上クリップレベルCL(+) = CU10に制御された状態を示している。この場合、

10 非線形関数補正回路24aでは、太線で示す特性でエッジ成分に対する補正処理を行うことになる。

また例えば図7(c)は、係数制御信号KCによって下クリップレベルCL(-)=CD3, 上クリップレベルCL(+) = CU3に制御された状態を示している。この場合も、

20 非線形関数補正回路24aでは、太線で示す特性でエッジ成分に対する補正処理を行うことになる。

本例では、このようなクリップレベルの可変設定に応じたエッジ成分の補正が行われ、

そのエッジ成分が加算回路22で表示データ信号に加算されることで、エッジ強調による

視認性向上とともに、有機ELディスプレイパネルモジュール3における消費電力の増大

防止もしくは削減を図る。

#### 【0044】

なお図4、図5の構成の場合について言えば、加算回路22が、本発明請求項でいう「

エッジ付加処理部」に相当する。

またエッジ抽出フィルタ23が本発明請求項でいう「エッジ抽出部」に相当し、エッジ

量可変部24(特に非線形関数補正回路24a)が本発明請求項でいう「エッジ補正部」

に相当する。

また電力量算出部25とエッジ制御係数決定部26が、本発明請求項でいう「エッジ

処理制御信号生成部」に相当する。本発明請求項でいう「エッジ処理制御信号」は、係数制

御信号KCのこととなる。

#### 【0045】

##### 【3. 表示データ処理部による電力抑制エッジ強調】

以上のような表示データ処理部2では、プラス方向のエッジに対してマイナス方向のエッジをより大きくするように非対称強調をすることによって有機ELディスプレイパネルモジュール3における消費電力の増加を防止する。つまり電力増加を伴わないエッジ強調機能を実現する。

#### 【0046】

このための表示データ処理部2による電力抑制エッジ強調処理について説明する。

上述したように電力量算出部25は、表示データ信号Din及びDoutのそれぞれに

40 ついて、一画面の消費電力量(発光消費電力)を推定計算する。ここでいう、表示データ

信号Dinについての発光消費電力とは、表示データ信号Dinを有機ELディスプレイ

パネルモジュール3に与えて発光駆動した場合を想定した、1フレームでの消費電力である。

また表示データ信号Doutについての発光消費電力とは、表示データ信号Doutを有機ELディスプレイパネルモジュール3に与えて発光駆動した場合を想定した、1フレームでの消費電力である。

まず、この発光消費電力の推定計算の手法について説明する。

#### 【0047】

先に図3により説明したように、有機ELディスプレイパネルモジュール3の画素回路

10 では、有機EL素子15に電流を流すことによって発光が行われる。

発光電流と輝度との関係はI-L特性として表されるが、一般的に比例関係にある。そ

50

のため、必要輝度に対して流さなければならない電流は一意的に決まってしまう。

この発光に必要な電流  $I_{EL}$  を電圧源  $V_{c\,c}$  (図3の電源制御線  $D\,S\,L$  に与えられる駆動電位  $V_{c\,c}$ ) からカソード ( $V_{c\,a\,t\,h}$  のノード) に対し流すことで有機EL素子15は発光が行われる。このため、有機EL素子15の発光に関わる消費電力  $P_{EL}$  は、

$$P_{EL} = (V_{c\,c} - V_{c\,a\,t\,h}) \times I_{EL}$$

として表される。

#### 【0048】

駆動電位  $V_{c\,c}$  ならびにカソード電位  $V_{c\,a\,t\,h}$  は一般的に定値であるため、映像データ (階調値) に応じた電流  $I_{EL}$  が導出できれば、消費電力の推定計算は可能となる。

10

#### 【0049】

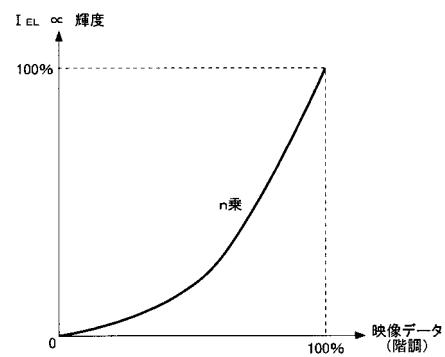

映像データに対する発光電流の関係は、ディスプレイデバイスの場合、一般的に図8のようにべき乗の関数になるように調整される。テレビジョンモニタでは2.2乗が一般的である。

即ち、このガンマ特性の情報 ( $n$ 乗) をあらかじめ入手しておけば、映像データから電流に相当するデータへの変換計算は可能になる。変換計算は演算で行うかテーブル変換で行うかのどちらかの手法が採択される。

#### 【0050】

またディスプレイの画素は一般的にRGBの3色のサブピクセル構成になっているため、基準ホワイトで発光させたときの必要電流比の情報を入手しておく必要もある。

20

(階調 / 100%階調)<sup>n</sup>の計算をしたそれぞれのサブピクセルでの算出結果を基準ホワイト電流比で足し合わせ、平均値を算出することで1画素の電力に相当する量を算出できる。これを全画素分行い、平均値を算出する。

この値を相対値比較計算することで電力量の増減率を算出することができる。

#### 【0051】

図9により、電力量算出部25での発光消費電力の算出の具体例を説明する。

この図9は、図4の構成について電力量算出部25の演算処理内容を具体的に示している。

電力量算出部25は、処理ST1として、表示データ信号  $D_{in}$  についての発光消費電力  $P$  の推定計算を行う。

30

また処理ST2として、表示データ信号  $D_{out}$  についての発光消費電力  $P$  の推定計算を行う。

ここでは発光消費電力  $P$  、  $P$  は、表示データ信号  $D_{in}$  、並びに表示データ信号  $D_{out}$  それぞれから、一画面分の電力パラメータの推定計算を行う。

具体的には、(階調 / 100%階調)<sup>n</sup>の全画素分の積算値 ( { (階調 / 100%階調)<sup>n</sup> } ) を画素数で割って平均値を算出する。つまり、

$$P = ( \{ (階調 / 100\%階調)^n \} ) / \text{画素数}$$

$$P = ( \{ (階調 / 100\%階調)^n \} ) / \text{画素数}$$

を計算する。

階調とは、各画素に対応する表示データ信号値、100%階調とは、最大輝度としての表示データ信号値である。nは、図8に示したn乗の値である。

40

#### 【0052】

従って、1フレーム内の各画素の信号値 (階調) について、(階調 / 100%階調)<sup>n</sup>により、1画素の消費電力を推定し、これを全画素について積算する。そして画素数で割って平均値をとることで、1画素あたりの発光消費電力を求めることになる。

#### 【0053】

ここで変換計算は上記式の演算を行っても良いし、べき乗計算の部分のみあらかじめ用意したテーブルを使用しての変換計算を行っても良い。

因みにここで、RGBサブピクセルの場合の計算は次のようなものになる。

仮に基準ホワイトを発光するためのRGBの電流比が1:2:3だったとすると、

50

$P = ( ( [ 1 \times \{ ( R \text{階調} / 100\% \text{階調} ) n \} + 2 \times \{ ( G \text{階調} / 100\% \text{階調} ) n \} + 3 \times \{ ( B \text{階調} / 100\% \text{階調} ) n \} ] / ( 1 + 2 + 3 ) ) ) / \text{画素数}$

となる。

#### 【0054】

このようにして発光消費電力  $P$  、  $P$  を算出したら、エッジ制御係数決定部 26 において、発光消費電力  $P$  、  $P$  に基づいて、係数制御信号  $K_C$  を発生させる。

#### 【0055】

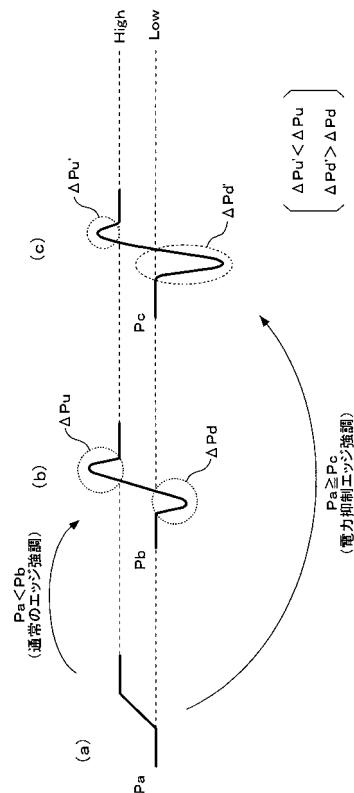

ここで、エッジ制御係数決定部 26 及びエッジ量可変部 24 における非線形関数補正回路 24a の具体的な処理例の説明の前に、理解を容易とするため、図 10 によりエッジ強調処理と電力の関係、及び本例による電力増加の防止効果を説明しておく。

#### 【0056】

例えば画面上のある箇所で、図 10 (a) のように Low レベルから High レベルへ移行するエッジが存在したとする。

これに対して通常のエッジ強調処理を行うと、図 10 (b) のように、Low レベルに対しプリシート、High レベルに対しオーバーシュート (プリシートとオーバーシュートのエッジ量は同量) が加わるような処理結果となる。

このような場合、前述したようにガンマ特性が 2.2 乗に近い (1 乗より大きい) 特性をしているため、マイナスエッジの 1 ステップの電力に対して、プラスエッジの 1 ステップの電力の方が必ず高くなってしまう。

つまり図示するように、マイナスエッジによる電力減少分を  $P_d$ 、プラスエッジの電力上昇分を  $P_u$  とすると、 $P_u > P_d$  であることは自明であり、通常エッジ強調処理を行うと消費電力の増加も伴っていることになる。

従って、エッジ強調前の消費電力を  $P_a$ 、エッジ強調後の消費電力を  $P_b$  とすると、 $P_a < P_b$  となる。

#### 【0057】

これに対して本実施の形態では、電力増加を抑制しつつエッジ強調を行うことになる。

即ち図 10 (c) のように、トータルのエッジ波形のピーク  $t_0$  ピークを同程度以上に維持することで、エッジ強調効果を維持しながら、プラス方向のエッジ量を低減、マイナス方向のエッジ量を増加させる方向にエッジ量を調整する。これにより消費電力の増加を確実に防止する。

図 10 (c) の場合、電力上昇分  $P_u'$  は、 $P_u' < P_u$  となるように抑制され、かつ電力減少分  $P_d'$  は、 $P_d' > P_d$  となるように制御される。ここで、 $P_u' = P_d'$  となるところまで調整すれば、 $P_a = P_c$  ( $P_c$  は電力抑制エッジ強調の処理後の消費電力) を実現することが可能になる。

#### 【0058】

つまりこの図 10 のように上下非対称のエッジ波形を非線形関数補正回路 24a での補正処理で生成し、これを加算回路 22 で表示データ信号に加算すれば、エッジ強調効果を維持したまま、消費電力の増大防止もしくは低減を実現できる。

そこで、このような非線形関数補正回路 24a でのエッジ成分波形の補正処理を実現するため、エッジ制御係数決定部 26 及び非線形関数補正回路 24a は以下に説明する処理を行うことになる。

#### 【0059】

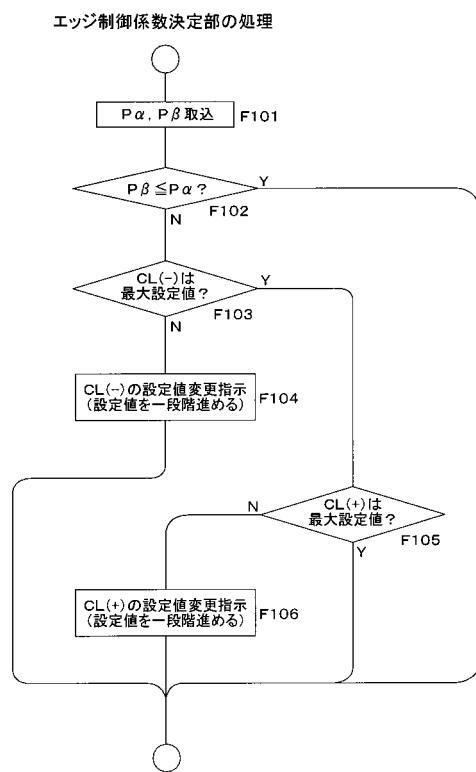

エッジ制御係数決定部 26 の処理を図 11 に示す。図 11 は例えば 1 フレーム期間毎にエッジ制御係数決定部 26 が実行する処理例である。

なお、エッジ制御係数決定部 26 は上述したように係数制御信号  $K_C$  によりエッジ量可変部 24 における非線形関数補正回路 24a の上クリップレベルと下クリップレベルを制御するものである。

#### 【0060】

エッジ制御係数決定部 26 では、まずステップ F101 として電力量算出部 25 で算出された発光消費電力  $P$  、  $P$  を取り込む。そしてステップ F102 で発光消費電力  $P$

10

20

30

40

50

、 $P_{out}$  の比較を行う。

ここで  $P_{in}$  と  $P_{out}$  ではない場合、即ち表示データ信号  $D_{in}$  による発光消費電力  $P_{in}$  より、表示データ信号  $D_{out}$  による発光消費電力  $P_{out}$  の方が高い場合は、エッジ制御係数決定部 26 の処理はステップ F102 から F103 に進む。このステップ F103 に進む場合とは、エッジ加算によって消費電力が増大している状況である。

エッジ制御係数決定部 26 は、ステップ F103 では、下クリップレベル  $CL(-)$  が図 7 (a) で述べた最大設定値  $CD10$  に達しているか否かを確認する。つまり、それ以上、下クリップレベル  $CL(-)$  を下げることができないか否かを確認する。

下クリップレベル  $CL(-)$  が最大設定値に達していないければ、エッジ制御係数決定部 26 は処理をステップ F104 に進める。そして下クリップレベル  $CL(-)$  の設定を 1 段階進めることを指示する係数制御信号  $KC$  を発生させ、エッジ量可変部 24 における非線形関数補正回路 24a に供給する。そして現フレーム期間での処理を終える。

10

#### 【0061】

一方、ステップ F103 で、下クリップレベル  $CL(-)$  が既に最大設定値に達していると判断した場合は、エッジ制御係数決定部 26 は処理をステップ F105 に進める。そしてエッジ制御係数決定部 26 は、ステップ F105 では、上クリップレベル  $CL(+)$  が図 7 (a) で述べた最大設定値  $CU10$  に達しているか否かを確認する。つまり、それ以上、上クリップレベル  $CL(+)$  を下げることができないか否かを確認する。

上クリップレベル  $CL(+)$  が最大設定値に達していないければ、エッジ制御係数決定部 26 は処理をステップ F106 に進める。そして上クリップレベル  $CL(+)$  の設定を 1 段階進めることを指示する係数制御信号  $KC$  を発生させ、エッジ量可変部 24 における非線形関数補正回路 24a に供給する。そして現フレーム期間での処理を終える。

20

ステップ F105 で、上クリップレベル  $CL(+)$  も最大設定値に達していると判断した場合は、それ以上は制御不能として可変制御は行わず、現フレーム期間での処理を終える。

#### 【0062】

また、ステップ F102 で  $P_{in} > P_{out}$  であると判定された場合、即ち表示データ信号  $D_{in}$  による発光消費電力  $P_{in}$  より、表示データ信号  $D_{out}$  による発光消費電力  $P_{out}$  の方が低い場合（もしくは同等の場合）は、既にエッジ加算によっても電力消費が増大していない状況である。その場合は、それ以上の制御は不要であるため、ステップ F102 から現フレーム期間での処理を終える。

30

#### 【0063】

このような図 11 の処理例は、表示データ信号  $D_{in}$  による発光消費電力  $P_{in}$  より表示データ信号  $D_{out}$  による発光消費電力  $P_{out}$  の方が高い場合に、表示データ信号  $D_{out}$  による発光消費電力  $P_{out}$  を低減させるように係数制御信号  $KC$  を発生する処理である。

そしてその場合、まず非線形関数補正回路 24a における下クリップレベル  $CL(-)$  を一段階づつ低下させていく。下クリップレベル  $CL(-)$  が最大設定値  $CD10$  とされても、なお表示データ信号  $D_{in}$  による発光消費電力  $P_{in}$  より表示データ信号  $D_{out}$  による発光消費電力  $P_{out}$  の方が高い場合には、さらに上クリップレベル  $CL(+)$  を一段階づつ低下させていく。このような処理によって、発光消費電力  $P_{out}$  が、発光消費電力  $P_{in}$  以下となるように追い込んでいく処理となる。

40

つまり、エッジ成分のマイナス方向のクリップレベルを低下させる方向に可変制御することを優先し、マイナス方向のクリップレベルを所定レベルまで低下させた後で必要がある場合に、プラス方向のクリップレベルを低下させる方向に可変制御するように係数制御信号  $KC$  を生成する。

#### 【0064】

図 12 に係数制御信号  $KC$  による設定制御の例を説明する。

図 12 (a) (b) は下クリップレベル  $CL(-)$  及び上クリップレベル  $CL(+)$  の設定値例である。例えばクリップレベルは 8 ビット値で設定されるとする。

図 7 で述べたように、下クリップレベル  $CL(-)$  の設定値として  $CD1 \sim CD10$  の

50

10段階が可変制御される。また上クリップレベルCL(+)の設定値としてCU1～CU10の10段階が可変制御される。

エッジ制御係数決定部26は、上記ステップF104では、係数制御信号KCによって、CD1～CD10のいずれかを指示することになる。またステップF106では係数制御信号KCによって、CU1～CU10のいずれかを指示する。

#### 【0065】

エッジ制御係数決定部26は、非線形関数補正回路24aの上クリップレベルCL(+)と下クリップレベルCL(-)について、デフォルト値として図13(a)に示すように、上クリップレベルCL(+) = CU1、下クリップレベルCL(-) = CD1を設定制御している。例えば図12に示すように、CD1 = CU1 = 「63」とする。

図12(a)のように、下クリップレベルCL(-)については、例えばこのデフォルト値CD1を示す値「63」に対して、CD2は1.25倍の値、CD3は1.50倍の値、・・・CD10は3.25倍の値として、それぞれレベルが設定されている。

また図12(b)のように、上クリップレベルCL(+)については、例えばデフォルト値CU1を示す値「63」に対して、CU2は0.9倍の値、CU3は0.8倍の値、・・・CU10は0.1倍の値として、それぞれレベルが設定されている。

#### 【0066】

例えば初期状態からステップF104に進んだ場合、エッジ制御係数決定部26は、下クリップレベルCL(-)を1段階進めるため、CD2を指示する係数制御信号KCを発生させることになる。例えば $63 \times 1.25 = 78.75$ の下クリップレベルCL(-)指示する。これにより、後述する非線形関数補正回路24a側の処理で、補正特性は図13(b)のようになる。このため補正処理によってマイナス側のエッジ量が増加し、図9で説明した原理で、表示データ信号Doutによる発光消費電力Pは抑制される方向にコントロールされることになる。

そして発光消費電力Pは抑制が十分な状態になるまで、1フレーム期間毎に、下クリップレベルCL(-)をCD3 CD4 CD5 ・・・と下げていくようとする。

#### 【0067】

また図13(c)のように下クリップレベルCL(-)をCD10まで下げても、まだ発光消費電力Pの抑制が十分でなければ、次のフレーム期間からは、上クリップレベルCL(+)を低下させていく。例えば上クリップレベルCL(+)をCD1からCD2への変更を指示する係数制御信号KCを発生させる。例えば $63 \times 0.9 = 56.7$ の上クリップレベルCL(+)指示する。これにより、非線形関数補正回路24a側の補正特性が図14(a)のようになり、補正処理でプラス側のエッジ量が低減する。これも図9で説明した原理で、表示データ信号Doutによる発光消費電力Pは抑制される方向にコントロールされることになる。

さらに発光消費電力Pの抑制が十分でなければ、1フレーム期間毎に、上クリップレベルCL(+)をCU3 CU4 CU5 ・・・と下げていくようとする。

例えば最高で図14(b)のように、上クリップレベルCL(+) = CD10となるまで制御を行う。もし、この状態まで制御しても、まだ発光消費電力Pの抑制が十分でない場合は、上述したように、図11のステップF105からF106には進まず、制御は打ち切られる。但し、図12のクリップレベル可変設定範囲が適切になされていれば、この制御打ち切りの状態に至ることは殆ど無いようにできると考えられる。

#### 【0068】

エッジ制御係数決定部26では、以上のようなクリップレベル設定制御を行うために係数制御信号KCを非線形関数補正回路24aに供給する。

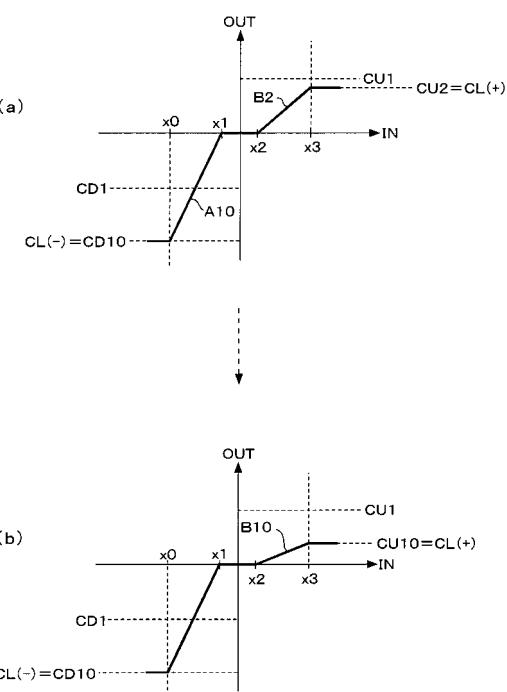

以下、非線形関数補正回路24a側の処理を説明する。

図15は、非線形関数補正回路24aが係数制御信号KCに応じて設定変更を行う処理を示している。

非線形関数補正回路24aは、エッジ制御係数決定部26が上記図11の処理で係数制御信号KCを発生させるたびに、図15の処理を行う。

10

20

30

40

50

## 【0069】

即ち非線形関数補正回路24aは、係数制御信号KCが入力されたら、図15の処理をステップF301からF302に進める。

非線形関数補正回路24aはステップF302では、係数制御信号KCによる設定指示が、下クリップレベルCL(-)の設定変更の指示であるか否かを確認する。

エッジ制御係数決定部26が図11のステップF104で係数制御信号KCを発生させた場合は、下クリップレベルCL(-)についての設定変更指示である。この場合非線形関数補正回路24aは、下クリップレベルCL(-)の設定変更指示であることを認識して処理をステップF303に進める。

## 【0070】

10

ステップF303では、非線形関数補正回路24aは下クリップレベルCL(-)の設定変更を行う。例えばそれまでが図13(a)のような初期設定状態であれば、図13(b)のように下クリップレベルCL(-)=CD2に変更する。

下クリップレベルCL(-)の設定変更を行ったら、非線形関数補正回路24aはステップF304で線形補間により下エッジ成分に与える係数を設定する。

## 【0071】

係数設定について説明する。

例えば図13(a)の初期状態においては、下クリップレベルCL(-)=CD1、上クリップレベルCL(+)=CU1である。

図中入力軸(横軸)でx1~x2の範囲は図6で説明したコアリング範囲である。

20

そしてマイナス側のエッジ波形は、x0~x1の範囲で傾きA1に相当するゲインを与え、x0以下は下クリップレベルCL(-)=CD1に固定して出力する。換言すれば、傾きA1に相当するゲインは、座標(x1, 0)と座標(x0, CD1)の間の直線補間によって求められるものである。

またプラス側のエッジ波形も同様の考え方であり、x2~x3の範囲で傾きB1に相当するゲインを与え、x3以上は上クリップレベルCL(+)=CU1に固定して出力する。つまり傾きB1に相当するゲインは、座標(x2, 0)と座標(x3, CU1)の間の直線補間によって求められるものである。

## 【0072】

そして下クリップレベルCL(-)又は上クリップレベルCL(+)の設定変更があった場合は、同様に直線補間で係数を設定する。

30

例えばステップF303で下クリップレベルCL(-)をCD1からCD2に変更した場合、ステップF304では、図13(b)の傾きA2に相当する係数を設定することになる。この場合、座標(x1, 0)と座標(x0, CD2)の間の直線補間によって傾きA2に相当する係数を求める。

## 【0073】

非線形関数補正回路24aは、このように下クリップレベルCL(-)の設定変更に伴う処理を行ったらステップF305に進む。

そして、非線形関数補正回路24aは、係数制御信号KCによる設定指示が、上クリップレベルCL(+)の設定変更の指示であるか否かを確認する。

40

なお、図11のように、エッジ制御係数決定部26が、下クリップレベルCL(-)を低下させることを優先し、下クリップレベルCL(-)を所定レベルまで低下させた後で必要がある場合に上クリップレベルCL(+)を低下させるような制御を行う場合、下クリップレベルCL(-)の設定変更指示と、上クリップレベルCL(+)の設定変更指示は同時には発生されない。

従って、例えば図13(c)のように下クリップレベルCL(-)=CD10となるまでは、非線形関数補正回路24aでのステップF305は、上クリップレベルCL(+)の変更指示ではないとして図15の処理を終えることになる。

## 【0074】

一方、図13(c)の状態に至った後において、エッジ制御係数決定部26が図11の

50

ステップ F 1 0 6 で係数制御信号 K C を発生させた場合は、非線形関数補正回路 2 4 a の処理は次のようになる。

この場合、上クリップレベル C L ( + ) の設定変更指示であることから、図 1 5 の処理はステップ F 3 0 1 F 3 0 2 F 3 0 5 F 3 0 6 と進む。

#### 【 0 0 7 5 】

ステップ F 3 0 6 では、非線形関数補正回路 2 4 a は上クリップレベル C L ( + ) の設定変更を行う。例えばそれまでが図 1 3 ( c ) のような初期設定状態であれば、図 1 4 ( a ) のように上クリップレベル C L ( + ) = C U 2 に変更する。

上クリップレベル C L ( + ) の設定変更を行ったら、非線形関数補正回路 2 4 a はステップ F 3 0 7 で線形補間により上エッジ成分に与える係数を設定する。即ち図 1 4 の傾き B 2 に相当する係数を設定する。 10

#### 【 0 0 7 6 】

非線形関数補正回路 2 4 a では、以上の図 1 5 のように、エッジ制御係数決定部 2 6 からの係数制御信号 K C に対応して設定変更を行う。そして各フレーム期間では、その時点の設定状態において、非線形補正処理を行う。

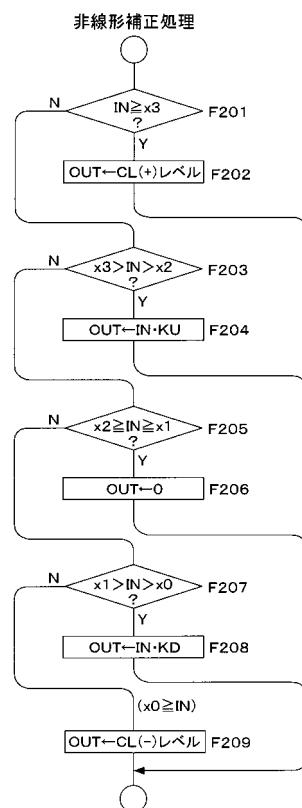

非線形関数補正処理は図 1 6 に示される。非線形関数補正回路 2 4 a はエッジ抽出フィルタ 2 3 から入力される二次微分によるエッジ成分波形（入力値 I N ）に対して、図 1 6 の処理で補正を行う。なお図 1 6 における  $\times 0 \sim \times 3$  は、図 1 3 , 図 1 4 の入力軸上の値を指す。 20

#### 【 0 0 7 7 】

入力値 I N が  $\times 3$  以上であるときは、出力値 O U T は、その時点で設定されている上クリップレベル C L ( + ) の値とする ( F 2 0 1 F 2 0 2 )

入力値 I N が  $\times 3 > I N > \times 2$  であるときは、出力値 O U T は、その時点で設定されているプラス側エッジ係数 K U を入力値 I N に乗算した値とする ( F 2 0 3 F 2 0 4 )。プラス側エッジ係数 K U とは、図 1 3 , 図 1 4 における傾き B 1 , B 2 . . . B 1 0 に相当する係数値であり、上記図 1 5 のステップ F 3 0 7 で設定される値である。 30

入力値 I N が  $\times 2 > I N > \times 1$  であるときは、コアリング範囲であるため、出力値 O U T = 0 とする ( F 2 0 5 F 2 0 6 )。

入力値 I N が  $\times 1 > I N > \times 0$  であるときは、出力値 O U T は、その時点で設定されているマイナス側エッジ係数 K D を入力値 I N に乗算した値とする ( F 2 0 7 F 2 0 8 )。マイナス側エッジ係数 K D とは、図 1 3 , 図 1 4 における傾き A 1 , A 2 . . . A 1 0 に相当する係数値であり、上記図 1 5 のステップ F 3 0 4 で設定される値である。 30

それ以外のばあい、つまり入力値 I N が  $\times 0$  以下であるときは、出力値 O U T は、その時点で設定されている下クリップレベル C L ( - ) の値とする ( F 2 0 7 F 2 0 9 )。

#### 【 0 0 7 8 】

このような補正処理を行うことで、加算回路 2 2 で表示データ信号に加算されることになるエッジ成分は、その時点での補正特性（図 1 3 ( a ) ~ 図 1 4 ( b ) の範囲で変化される補正特性）に応じて補正される。

すると例えば図 1 0 ( c ) で示したように上下非対称のエッジ波形となりながら、 P P となるまで追い込まれることになる。 40

これによって、エッジ強調を行うにもかかわらず、有機 E L ディスプレイパネルモジュール 3 における消費電力の上昇は必ず防止される。従って、コントラスト感向上効果が維持されることで視認性の低下を抑制しつつ電力消費増大を防止できる。

或いは、 P P ではなく、 P > P となるまで制御するようすれば、積極的に電力の低減を図ることも可能である。

また本例の場合、図 1 1 の処理で下クリップレベル C L ( - ) の設定変更を優先させている。つまりマイナス側エッジの波形レベルを下げるなどを、プラス側エッジの波形レベルを下げるよりも優先させる。これは、エッジ強調効果をなるべく低減させないという意味で有効である。これは、プラス側エッジのレベルが高いほど画像におけるコントラスト感が得られやすいからである。 50

## 【0079】

## [4. エッジ制御係数決定処理の他の例]

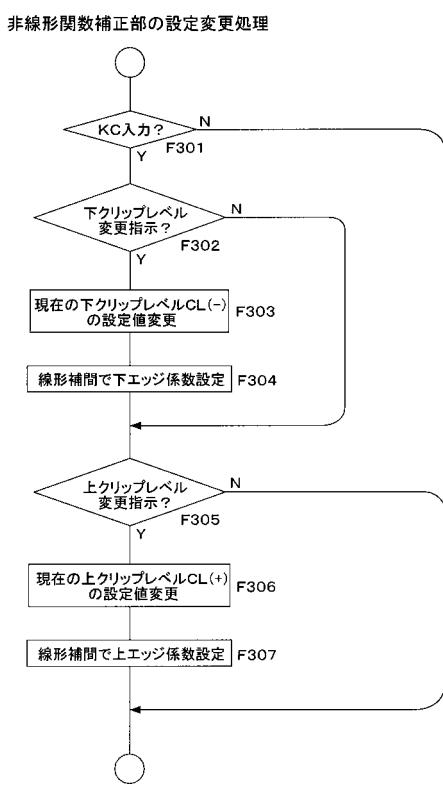

エッジ制御係数決定部26による係数制御信号KCの発生処理としては図11以外にも多様に考えられる。以下説明していく。

## 【0080】

図17は、図11とは逆に、エッジ成分のプラス方向のクリップレベルを低下させる方向に可変制御することを優先し、プラス方向のクリップレベルを所定レベルまで低下させた後で必要がある場合に、エッジ成分のマイナス方向のクリップレベルを低下させる方向に可変制御する例である。

上記のようにコントラスト感を優先させたい場合は図11の処理が好適であるが、消費電力の観点を重視すれば、図17のような手法も考えられる。

## 【0081】

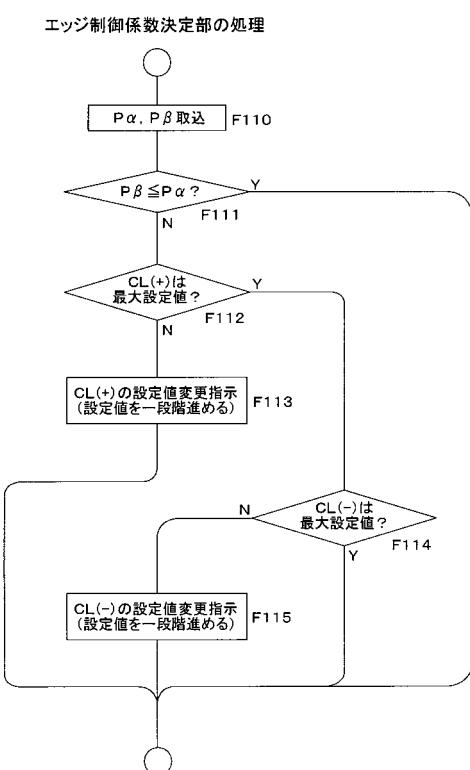

この図17の場合、エッジ制御係数決定部26では、まずステップF110として電力量算出部25で算出された発光消費電力P<sub>+</sub>、P<sub>-</sub>を取り込む。そしてステップF111で発光消費電力P<sub>+</sub>、P<sub>-</sub>の比較を行う。

ここでP<sub>+</sub>、P<sub>-</sub>ではない場合、即ち表示データ信号Dinによる発光消費電力P<sub>+</sub>より、表示データ信号Doutによる発光消費電力P<sub>-</sub>の方が高い場合は、エッジ制御係数決定部26の処理はステップF111からF112に進む。

エッジ制御係数決定部26は、ステップF103では、下クリップレベルCL(+)が図7(a)で述べた最大設定値CU10に達しているか否かを確認する。つまり、それ以上、上クリップレベルCL(+)を下げることができないか否かを確認する。

上クリップレベルCL(+)が最大設定値に達していなければ、エッジ制御係数決定部26は処理をステップF113に進める。そして上クリップレベルCL(+)の設定を1段階進めることを指示する係数制御信号KCを発生させ、エッジ量可変部24における非線形関数補正回路24aに供給する。そして現フレーム期間での処理を終える。

## 【0082】

一方、ステップF112で、上クリップレベルCL(+)が既に最大設定値に達していると判断した場合は、エッジ制御係数決定部26は処理をステップF114に進める。そしてエッジ制御係数決定部26は、ステップF114では、下クリップレベルCL(-)が図7(a)で述べた最大設定値CD10に達しているか否かを確認する。つまり、それ以上、下クリップレベルCL(-)を下げることができないか否かを確認する。

下クリップレベルCL(-)が最大設定値に達していなければ、エッジ制御係数決定部26は処理をステップF115に進める。そして下クリップレベルCL(-)の設定を1段階進めることを指示する係数制御信号KCを発生させ、エッジ量可変部24における非線形関数補正回路24aに供給する。そして現フレーム期間での処理を終える。

ステップF114で、下クリップレベルCL(-)も最大設定値に達していると判断した場合は、それ以上は制御不能として可変制御は行わず、現フレーム期間での処理を終える。

## 【0083】

また、ステップF111でP<sub>+</sub>、P<sub>-</sub>であると判定された場合、即ち表示データ信号Dinによる発光消費電力P<sub>+</sub>より、表示データ信号Doutによる発光消費電力P<sub>-</sub>の方が低い場合(もしくは同等の場合)は、既にエッジ加算によっても電力消費が増大していない状況である。その場合は、それ以上の制御は不要であるため、ステップF111から現フレーム期間での処理を終える。

## 【0084】

このような処理によっても、エッジ付加によるコントラスト感向上効果を維持しながら、電力消費増大を防止できる。

## 【0085】

次に図18は、下クリップレベルCL(-)と上クリップレベルCL(+)を同時に設

10

20

30

40

50

定変更させる処理である。

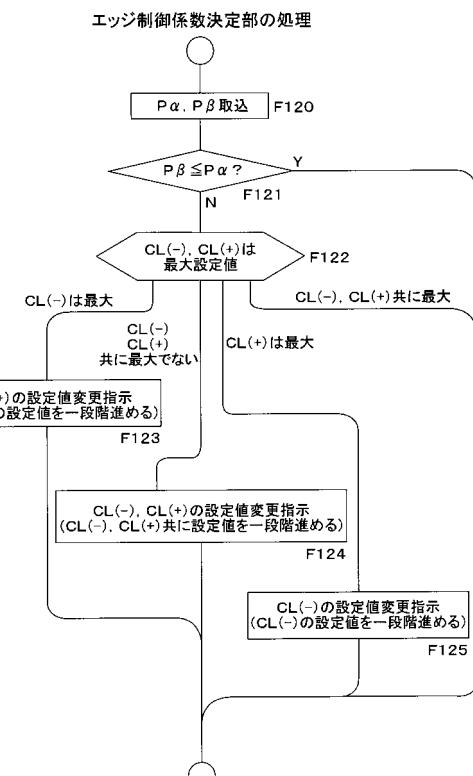

この図18の場合、エッジ制御係数決定部26では、まずステップF120として電力量算出部25で算出された発光消費電力P<sub>1</sub>、P<sub>2</sub>を取り込む。そしてステップF121で発光消費電力P<sub>1</sub>、P<sub>2</sub>の比較を行う。

P<sub>1</sub> = P<sub>2</sub> の場合は、既に設定変更不要の状態であるため処理を終える。

ここでP<sub>1</sub> ≠ P<sub>2</sub> ではない場合、即ち表示データ信号Dinによる発光消費電力P<sub>1</sub>より、表示データ信号Doutによる発光消費電力P<sub>2</sub>の方が高い場合は、エッジ制御係数決定部26の処理はステップF121からF122に進む。

エッジ制御係数決定部26は、ステップF122では、下クリップレベルCL(-)と上クリップレベルCL(+)のそれぞれについて、最大設定値CD10, CU10に達しているか否かを確認する。

#### 【0086】

下クリップレベルCL(-)と上クリップレベルCL(+)が共に最大設定値に達していなければ、ステップF124に進み、エッジ制御係数決定部26は下クリップレベルCL(-)及び上クリップレベルCL(+)の設定をそれぞれ1段階進めることを指示する係数制御信号KCを発生させ、エッジ量可変部24における非線形関数補正回路24aに供給する。そして現フレーム期間での処理を終える。

#### 【0087】

一方、下クリップレベルCL(-)と上クリップレベルCL(+)が共に最大設定値に達していれば、それ以上の設定変更はできないため、ステップF122から現フレーム期間での処理を終える。つまり消費電力低減制御しきれない状態である。但し上述もしたように、設定変更範囲が適切に設計されていれば、このような状態は殆ど生じないと考えられる。

#### 【0088】

なお、図7(a)の例のように、上クリップレベルCL(+)と下クリップレベルCL(-)の変更段階数が共に10段階などで同数であるときは、以上の場合しかない。ところが、上クリップレベルCL(+)の変更段階数が下クリップレベルCL(-)の変更段階数より多く設定されている場合は、ステップF122の判断において、下クリップレベルCL(-)のみが最大設定値に達していると判断される場合もある。

その場合は、エッジ制御係数決定部26はステップF123に進み、上クリップレベルCL(+)の設定を1段階進めることを指示する係数制御信号KCを発生させ、エッジ量可変部24における非線形関数補正回路24aに供給する。そして現フレーム期間での処理を終える。

#### 【0089】

また下クリップレベルCL(-)の変更段階数が上クリップレベルCL(+)の変更段階数より多く設定されている場合は、ステップF122の判断において、上クリップレベルCL(+)のみが最大設定値に達していると判断される場合もある。

その場合は、エッジ制御係数決定部26はステップF125に進み、下クリップレベルCL(-)の設定を1段階進めることを指示する係数制御信号KCを発生させ、エッジ量可変部24における非線形関数補正回路24aに供給する。そして現フレーム期間での処理を終える。

#### 【0090】

このような図18の処理では、ステップF124の処理により、1フレーム期間で上クリップレベルCL(+)と下クリップレベルCL(-)が同時に低下するよう制御される。これは、エッジ付加によるコントラスト感向上効果を維持しながら、電力消費増大を防止できるという効果と共に、ステップF121でP<sub>1</sub> ≠ P<sub>2</sub>と判断される状態にまで、迅速に追い込むことができるという利点があることになる。

#### 【0091】

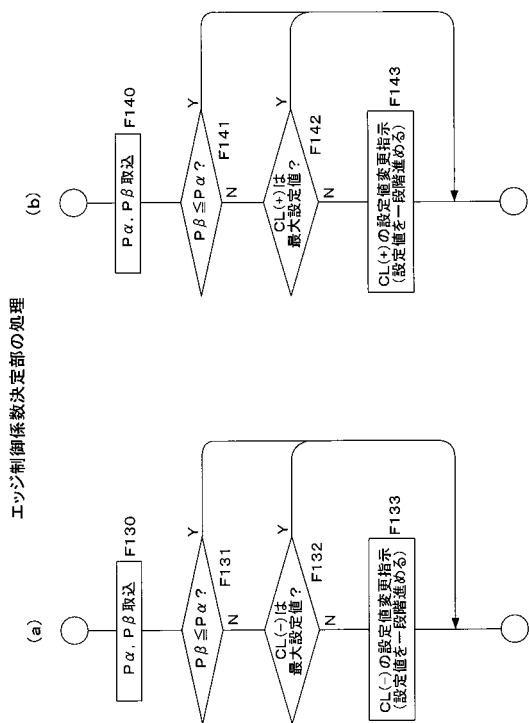

また、図19(a)(b)の処理例のように、設定可変とするのは下クリップレベルCL(-)のみ、もしくは上クリップレベルCL(+)のみとしてもよい。

10

20

30

40

50

## 【0092】

図19(a)の処理例では、エッジ制御係数決定部26では、まずステップF130で発光消費電力P<sub>+</sub>、P<sub>-</sub>を取り込む。そしてステップF131で発光消費電力P<sub>+</sub>、P<sub>-</sub>の比較を行う。

P<sub>+</sub> P<sub>-</sub>の場合は、既に設定変更不要の状態であるため処理を終える。

P<sub>+</sub> P<sub>-</sub>ではない場合は、エッジ制御係数決定部26はステップF132に進み、下クリップレベルCL(-)が最大設定値(例えばCD10)に達しているか否かを確認する。

## 【0093】

下クリップレベルCL(-)が最大設定値に達していなければ、ステップF133に進み、エッジ制御係数決定部26は下クリップレベルCL(-)の設定を1段階進めることを指示する係数制御信号KCを発生させ、エッジ量可変部24における非線形関数補正回路24aに供給する。そして現フレーム期間での処理を終える。

一方、下クリップレベルCL(-)が最大設定値に達していれば、それ以上の設定変更はできないため、ステップF132から現フレーム期間での処理を終える。

## 【0094】

また図19(b)の処理例では、エッジ制御係数決定部26では、まずステップF140で発光消費電力P<sub>+</sub>、P<sub>-</sub>を取り込む。そしてステップF141で発光消費電力P<sub>+</sub>、P<sub>-</sub>の比較を行う。

P<sub>+</sub> P<sub>-</sub>の場合は、既に設定変更不要の状態であるため処理を終える。

P<sub>+</sub> P<sub>-</sub>ではない場合は、エッジ制御係数決定部26はステップF142に進み、上クリップレベルCL(+)が最大設定値(例えばCU10)に達しているか否かを確認する。

## 【0095】

上クリップレベルCL(+)が最大設定値に達していなければ、ステップF143に進み、エッジ制御係数決定部26は上クリップレベルCL(+)の設定を1段階進めることを指示する係数制御信号KCを発生させ、エッジ量可変部24における非線形関数補正回路24aに供給する。そして現フレーム期間での処理を終える。

一方、上クリップレベルCL(+)が最大設定値に達していれば、それ以上の設定変更はできないため、ステップF132から現フレーム期間での処理を終える。

## 【0096】

この図19(a)又は図19(b)の処理は、マイナス側エッジ成分もしくはプラス側エッジ成分のいずれかを補正して、消費電力の増大防止を図るものであり、処理を簡易化したものと言える。

## 【0097】

## [5. 变形例]

以上、実施の形態について説明してきたが、本発明は実施の形態の例に限られず、多様な変形例が考えられる。

例えば、上記図11、図17、図18、図19で示した係数制御信号KCの発生処理では、下クリップレベルCL(-)又は上クリップレベルCL(+)を1段階づつ設定変更するようにしたが、1回の制御で複数段階の設定変更を指示するようにしてもよい。

またこの場合、単に発光消費電力P<sub>+</sub>、P<sub>-</sub>の比較だけでなく、その電力差又は電力比を求める。そして電力差又は電力比に基づいて、1回の制御で、表示データ信号Doutによる発光消費電力P<sub>+</sub>が、表示データ信号Dinによる発光消費電力P<sub>-</sub>以下となるようにするために必要な下クリップレベルCL(-)又は上クリップレベルCL(+)を求める。その結果により、当該求めた下クリップレベルCL(-)又は上クリップレベルCL(+)を指定するような係数制御信号KCを発生させてもよい。このようにすれば、1回の制御で、目的とする状態に達するようにすることが可能である。

## 【0098】

10

20

30

40

50

また上記図11, 図17, 図18, 図19で示した例では、常に下クリップレベルCL(-)又は上クリップレベルCL(+)を下げる方向に設定変更していく。基本的にはこのように制御するが、例えば或るフレームにおいて、発光消費電力P<sub>1</sub>が、発光消費電力P<sub>2</sub>より所定以上に低くなった場合は、下クリップレベルCL(-)又は上クリップレベルCL(+)を戻す方向(レベルを上げる方向)に設定変更するようにしてもよい。特にプラス側エッジ成分については、高い方がコントラスト感の向上という意味では良好となるため、必要以上に上クリップレベルCL(+)が下げられている場合は、これを戻す(レベルを上げる)ようにすると、画質的により好適である。

#### 【0099】

また、上記図11の例では下クリップレベルCL(-)の変更を優先し、図17の例では上クリップレベルCL(+)の変更を優先したが、例えば各フレーム期間において順番に交互に下クリップレベルCL(-)と上クリップレベルCL(+)の設定を変更する処理例も考えられる。

#### 【0100】

また図11のステップF102, 図17のステップF111, 図18のステップF121、図19のステップF131、F141では、それぞれP<sub>1</sub> < P<sub>2</sub>であるか否かの判断を行うようにしたが、P<sub>1</sub> < P<sub>2</sub>であるか否かの判断を行うようにしてもよい。

#### 【0101】

また、図6で述べたように、ゲイン演算部24bで非線形関数補正回路24aの出力についてエッジ量制御信号ECの乗算を行ってエッジ成分のレベルをコントロールする構成としたが、エッジ成分に対するゲインは固定値としてもよい。

#### 【0102】

また発光消費電力P<sub>1</sub>、P<sub>2</sub>として推定を行い、これに基づいてエッジ成分の補正特性を設定しているが、非線形関数補正回路24aは、固定の特性でエッジ成分波形の補正を行い、非対称なエッジ波形を生成して表示データ信号Dinに付加するようにしてもよい。

例えば図7(c)に示したような固定の補正特性を設定するなどである。

#### 【0103】

また、例えばユーザの使用状況や好みに応じて実施の形態でいう電力抑制エッジ強調処理と、通常のエッジ強調処理を切り替えることができるようになることも考えられる。

例えば電力抑制エッジ強調処理を行う場合は、上述のように発光消費電力P<sub>1</sub>、P<sub>2</sub>に基づいて非線形関数補正回路24aの補正特性を変更するが、ユーザがその機能を求めないときは、常に非線形関数補正回路24aでは図6(b)のデフォルト設定で処理を行うようになるなどである。

#### 【図面の簡単な説明】

#### 【0104】

【図1】本発明の実施の形態の表示装置の要部のブロック図である。

【図2】実施の形態の有機ELディスプレイパネルモジュールの説明図である。

【図3】実施の形態の有機ELディスプレイパネルモジュールの画素回路の説明図である。

【図4】実施の形態の表示データ処理部のブロック図である。

【図5】実施の形態のエッジ抽出フィルタの説明図である。

【図6】実施の形態のエッジ量可変部の説明図である。

【図7】実施の形態の非線形関数補正特性の設定変更の説明図である。

【図8】実施の形態の電力算出手法の説明図である。

【図9】実施の形態の発光消費電力の算出の説明図である。

【図10】実施の形態の電力抑制エッジ強調の効果の説明図である。

【図11】実施の形態のエッジ制御係数決定部の処理のフローチャートである。

【図12】実施の形態の係数制御信号の内容の説明図である。

【図13】実施の形態の非線形関数補正特性の設定変更の説明図である。

10

20

30

40

50

【図14】実施の形態の非線形関数補正特性の設定変更の説明図である。

【図15】実施の形態の非線形関数補正部の設定変更処理のフローチャートである。

【図16】実施の形態の非線形関数補正処理のフローチャートである。

【図17】実施の形態のエッジ制御係数決定部の他の例のフローチャートである。

【図18】実施の形態のエッジ制御係数決定部の他の例のフローチャートである。

【図19】実施の形態のエッジ制御係数決定部の他の例のフローチャートである。

【符号の説明】

【0105】

1 表示装置、2 表示データ処理部、3 有機ELディスプレイモジュール、

10 画素回路、15 有機EL素子、22 加算回路、23 エッジ抽出フィルタ、2 10

4 エッジ量可変部、24a 非線形関数補正回路、25 電力量算出部、26 エッジ

制御係数決定部

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

係数制御信号(CC)の内容例

(a)

| 設定No. | CL(-)    | CL(+) Default値 |

|-------|----------|----------------|

| CU1   | 63(8bit) |                |

| CU2   | x1.25    | x0.9           |

| CU3   | x1.50    | x0.8           |

| CU4   | x1.75    | x0.7           |

| CU5   | x2.00    | x0.6           |

| CU6   | x2.25    | x0.5           |

| CU7   | x2.50    | x0.4           |

| CU8   | x2.75    | x0.3           |

| CU9   | x3.00    | x0.2           |

| CU10  | x3.25    | x0.1           |

(b)

| 設定No. | CL(-)    | CL(+) Default値 |

|-------|----------|----------------|

| CD1   | 63(8bit) |                |

| CD2   | x1.25    |                |

| CD3   | x1.50    |                |

| CD4   | x1.75    |                |

| CD5   | x2.00    |                |

| CD6   | x2.25    |                |

| CD7   | x2.50    |                |

| CD8   | x2.75    |                |

| CD9   | x3.00    |                |

| CD10  | x3.25    |                |

【図 1 3】

【図 1 4】

【図15】

【図16】

【図17】

【図18】

【図 19】

---

フロントページの続き

(56)参考文献 特開平2 - 168776 (JP, A)

特開平4 - 340870 (JP, A)

特開平6 - 245104 (JP, A)

特開2004 - 120528 (JP, A)

特開2010 - 91719 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 09 G 3 / 20 - 3 / 38

H 04 N 5 / 208