(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

8 February 2007 (08.02.2007)

PCT

(10) International Publication Number

WO 2007/015209 A1

## (51) International Patent Classification:

*H03J 3/00* (2006.01)      *H03J 3/24* (2006.01)

*H03J 5/24* (2006.01)

## (21) International Application Number:

PCT/IB2006/052632

## (22) International Filing Date:

1 August 2006 (01.08.2006)

## (25) Filing Language:

English

## (26) Publication Language:

English

## (30) Priority Data:

|            |                            |    |

|------------|----------------------------|----|

| 60/595,749 | 2 August 2005 (02.08.2005) | US |

| 60/595,750 | 2 August 2005 (02.08.2005) | US |

| 60/595,754 | 2 August 2005 (02.08.2005) | US |

(71) Applicant (for all designated States except US): **RF MAGIC, INC.** [US/US]; 10182 Telesis Court, 4th Floor, San Diego, California 92121 (US).

## (72) Inventors; and

(75) Inventors/Applicants (for US only): **COPPOLA, Francesco** [IT/FR]; Villa Lilly, 48 Av De Lattre De Tassigny, F-06130 Grasse (FR). **CIPRIANI, Stefano** [IT/FR]; Res. Monteverdi, 662 Chemin de La Rampe, F-06220 Golfe Juan (FR). **CARPINETO, Lorenzo** [IT/FR]; 435 Chemin de Beauvert, Villa N4, F-06600 Antibes (FR).

**PUCCIO, Gianni** [BE/FR]; 500, Avenue Marcel Pagnol, F-06610 La Gaude (FR). **DUVIVIER, Eric** [BE/FR]; Res. Monceau Bat. A1, 212 Ave George Pompidou, F-06220 Golfe Juan (FR). **BISANTI, Biagio** [IT/FR]; Les Terrasses d'antibes Bat 1E, 357, Chemin de Fontmeries, F-06000 Antibes (FR). **ALDERTON, Martin** [US/US]; 12525 Montero Place, San Diego, Colorado 92128 (US).

(74) Agent: **PERRY, Clifford**; 132 N El Camino Real, No. 347, Encinitas, California 92024 (US).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LV, LY, MA, MD, MG, MK, MN, MW, MX, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM),

[Continued on next page]

## (54) Title: MULTIPLE FREQUENCY SOURCE SYSTEM AND METHOD OF OPERATION

(57) Abstract: A multiple frequency source system includes at least one frequency source tunable to a predefined target frequency, and at least one additional frequency source operable to generate a second signal at a frequency which is either higher or lower than the target frequency. A method for tuning the tunable frequency source to the target frequency during concurrent generation of the second signal includes (i) controlling the tunable frequency source to tune to at least one frequency point frequency lower than the target frequency, and thereafter controlling the oscillator to tune to the target frequency, when the second signal is higher in frequency than the target frequency, or (ii) controlling the tunable frequency source to tune to at least one frequency point higher than the target frequency, and thereafter controlling the tunable frequency source to tune to the target frequency, when the second signal is lower in frequency than the target frequency.

WO 2007/015209 A1

European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

— before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments

**Published:**

— with international search report

*For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.*

## Multiple Frequency Source System and Method of Operation

### Cross Reference to Related Applications

This patent application is related to, and concurrently filed with each of the following patent applications, the contents of which are herein incorporated by reference for all purposes:

“Offset Signal Phasing for a Multiple Frequency Source System,” Application Serial No. -----, Atty Dkt No. RFM-16-PCT; and

“System and Method for Mitigating Phase Pulling in a Multiple Frequency Source System,” Application Serial No. -----, Atty Dkt. No. RFM-17-PCT.

This patent application claims priority to, and incorporates in its entirety each of the following US patent applications:

“Multiple Frequency Source System and Method of Operation,” Application Serial No. 60/595,754, filed August 2, 2005;

“Offset Signal Phasing for a Multiple Frequency Source System,” Application Serial No. 60/595,749, filed August 2, 2005; and

“System and Method for Mitigating Phase Pulling in a Multiple Frequency Source System,” Application Serial No. 60/595,750, filed August 2, 2005.

### Background

[0001] The present invention relates to frequency source systems, and more particularly to a system employing multiple frequency sources operable to enable the generation of multiple signal frequencies concurrently.

[0002] Frequency sources are used in communication systems to perform a myriad of signal processing operations such as frequency translation, signal modulation/demodulation, system clock generation, as well as other processes. Frequency sources are used in other applications as well when the generation of a known reference signal is needed.

[0003] Frequency sources generally are of two types, fixed frequency sources operable to generate an output signal at one frequency, and tunable frequency sources which can be controlled to generate an output signal at multiple frequencies over a predefined frequency spectrum. L-C oscillators, crystal oscillators, and dielectric resonator oscillators are exemplary of conventional fixed frequency sources, and voltage controlled oscillators and phase locked loop circuits represent well-known tunable frequency sources.

[0004] Communication systems, as well as other systems could benefit from the use of multiple frequency signals, as multiple processes could be performed concurrently in such an instance, for example. However, the implementation of a system operable to generate concurrent, multiple frequency signals is difficult, as concurrently-generated signals will interact with each other if tuned too closely together. Interaction between the differing signals can results in degradation of each signal, possibly rendering the signal unusable for their intended purpose.

[0005] What is needed is a multiple frequency source system and method of operation which permits the concurrent generation of two or more frequencies while minimizing the interaction between the concurrently operating signals.

Summary

[0006] The present invention provides a multiple frequency source system and method for generating two or more frequency signals while minimizing the signal interaction therebetween. The presented system is tunable, having at least one frequency source which can be tuned proximate to a concurrently-operating frequency.

[0007] In one of various embodiments of the invention set forth herein, a multiple frequency source system is presented that includes at least one frequency source tunable to a predefined target frequency, and at least one additional frequency source operable to generate a second signal at a frequency which is either higher or lower than the target frequency. A method for tuning the tunable frequency source to the target frequency during concurrent generation of the second signal includes (i) controlling the tunable frequency source to tune to at least one frequency point lower than the target frequency, and thereafter controlling the tunable frequency source to tune to the target frequency, when the second signal is higher in frequency than the target frequency, or (ii) controlling the tunable frequency source to tune to at least one frequency higher than the target frequency, and thereafter controlling the tunable frequency source to tune to the target frequency, when the second signal is lower in frequency than the target frequency.

[0008] These and other features of the invention will be better understood when read in view of the following drawings and detailed description.

### Brief Description of the Drawings

[0009] Fig. 1A illustrates an exemplary system employing multiple frequency sources in accordance with the present invention.

Fig. 1B illustrates an exemplary frequency source in accordance with the present invention.

Fig. 2 illustrates an exemplary method for tuning one of the frequency sources to a target frequency in a multiple frequency source system in accordance with the invention.

Fig. 3A illustrates an exemplary embodiment of a start-up and calibration process in accordance with the present invention.

Fig. 3B illustrates an exemplary data structure operable to store operating frequency points for a plurality of oscillators within a phase locked loop frequency source in accordance with the present invention.

Fig. 3C illustrates an exemplary data structure operable to store presently-generated frequency information in accordance with the present invention.

Fig. 4 illustrates an exemplary embodiment of a tuning process in which the requested target frequency is the first generated frequency in accordance with the present invention.

Fig. 5A illustrates an exemplary embodiment of a tuning process in which the requested target frequency is lower than the lowest generated frequency in accordance with the present invention.

Fig. 5B illustrates an exemplary embodiment of a process in which a selected oscillator is activated and tuned to a target frequency lower than the lowest generated frequency in accordance with the present invention.

Fig. 5C illustrates an exemplary embodiment of a process illustrated in Fig. 5B in which a selected oscillator tunes to the target frequency in accordance with the present invention.

Fig. 6A illustrates an exemplary embodiment of a tuning process in which the requested target frequency is higher than the highest generated frequency in accordance with the present invention.

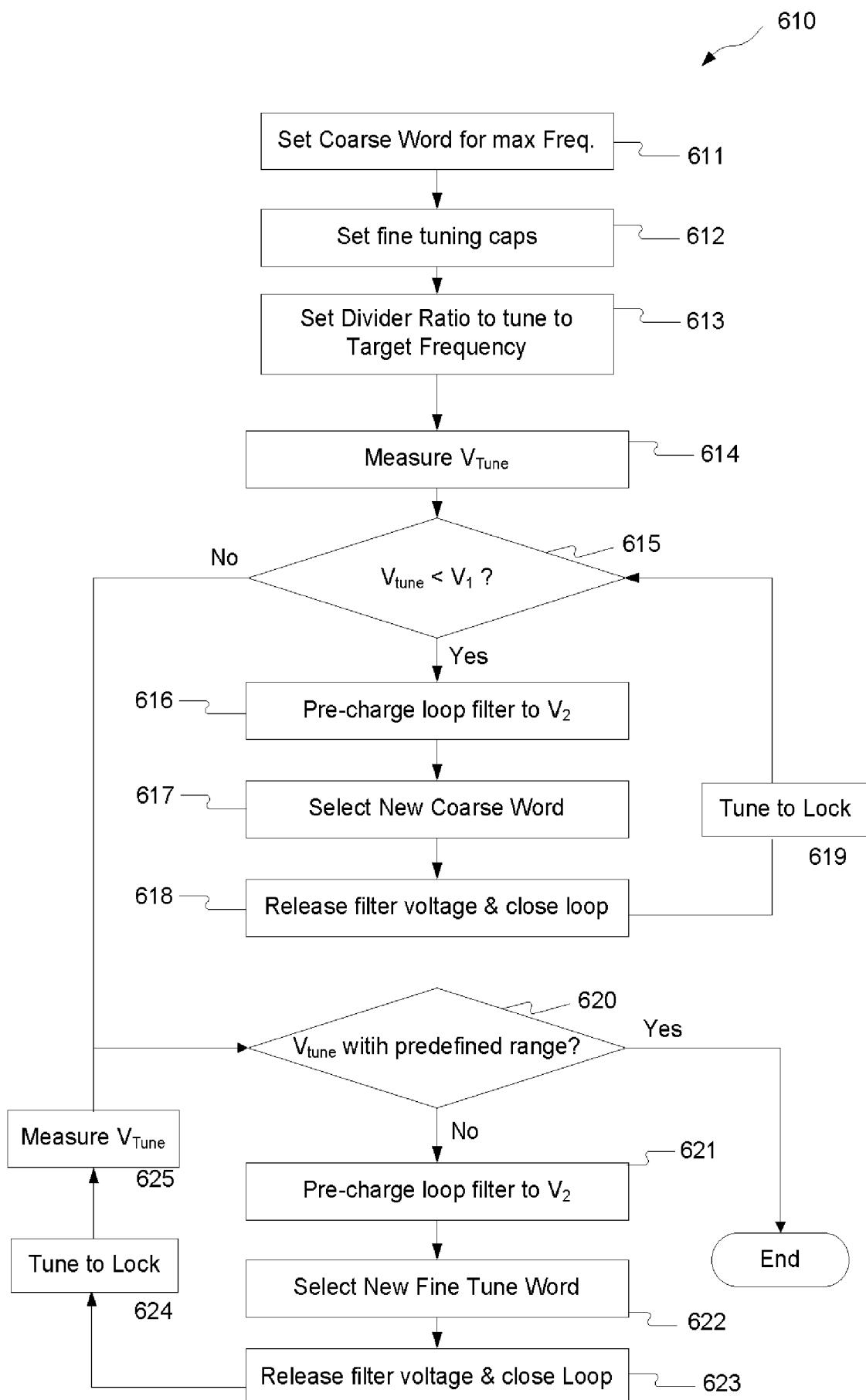

Fig. 6B illustrates an exemplary embodiment of a process in which a selected oscillator is activated and tuned to a target frequency higher than the highest generated frequency in accordance with the present invention.

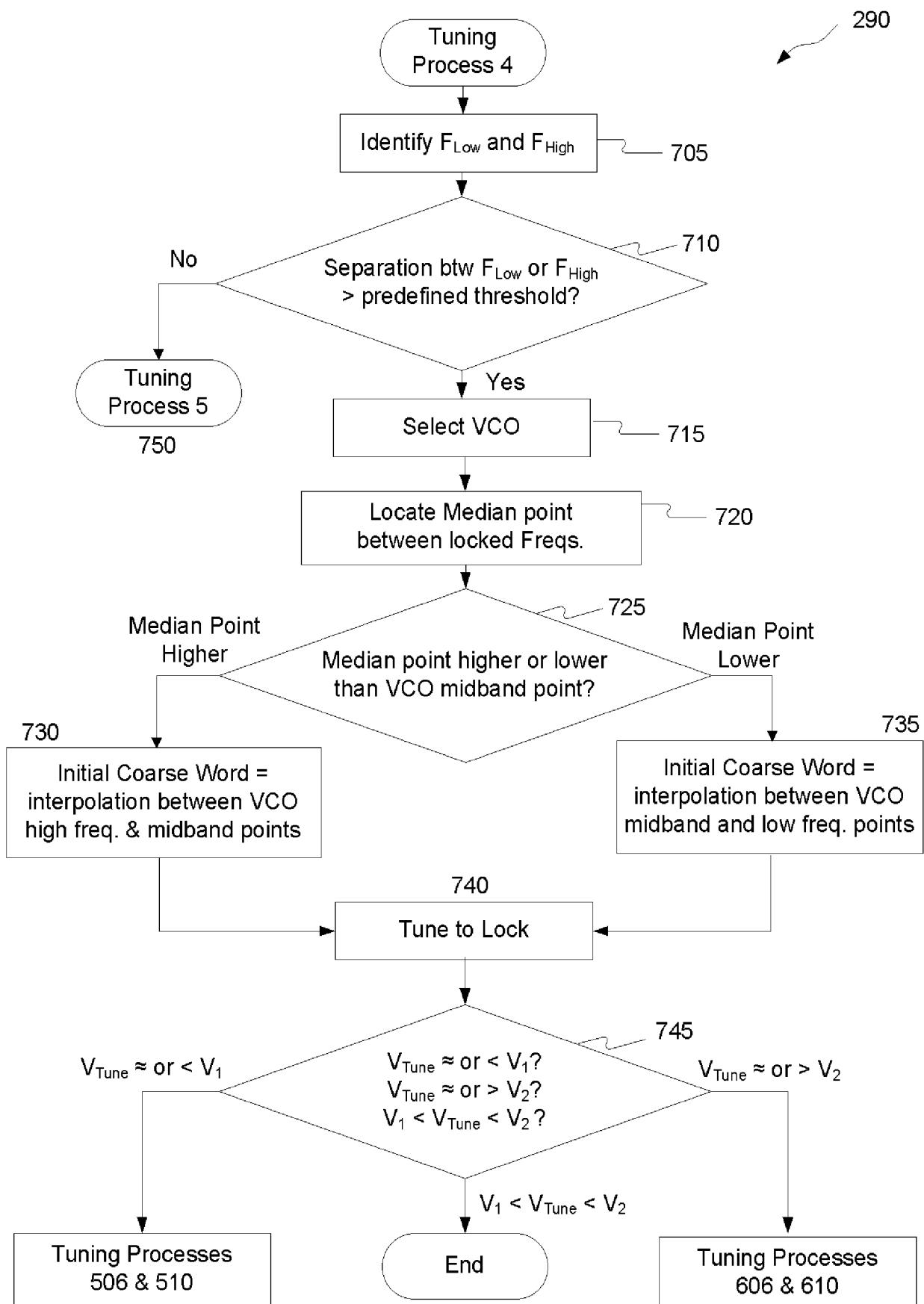

Fig. 7 illustrates an exemplary embodiment of a tuning process in which the requested target frequency is located between two existing frequencies in accordance with the present invention.

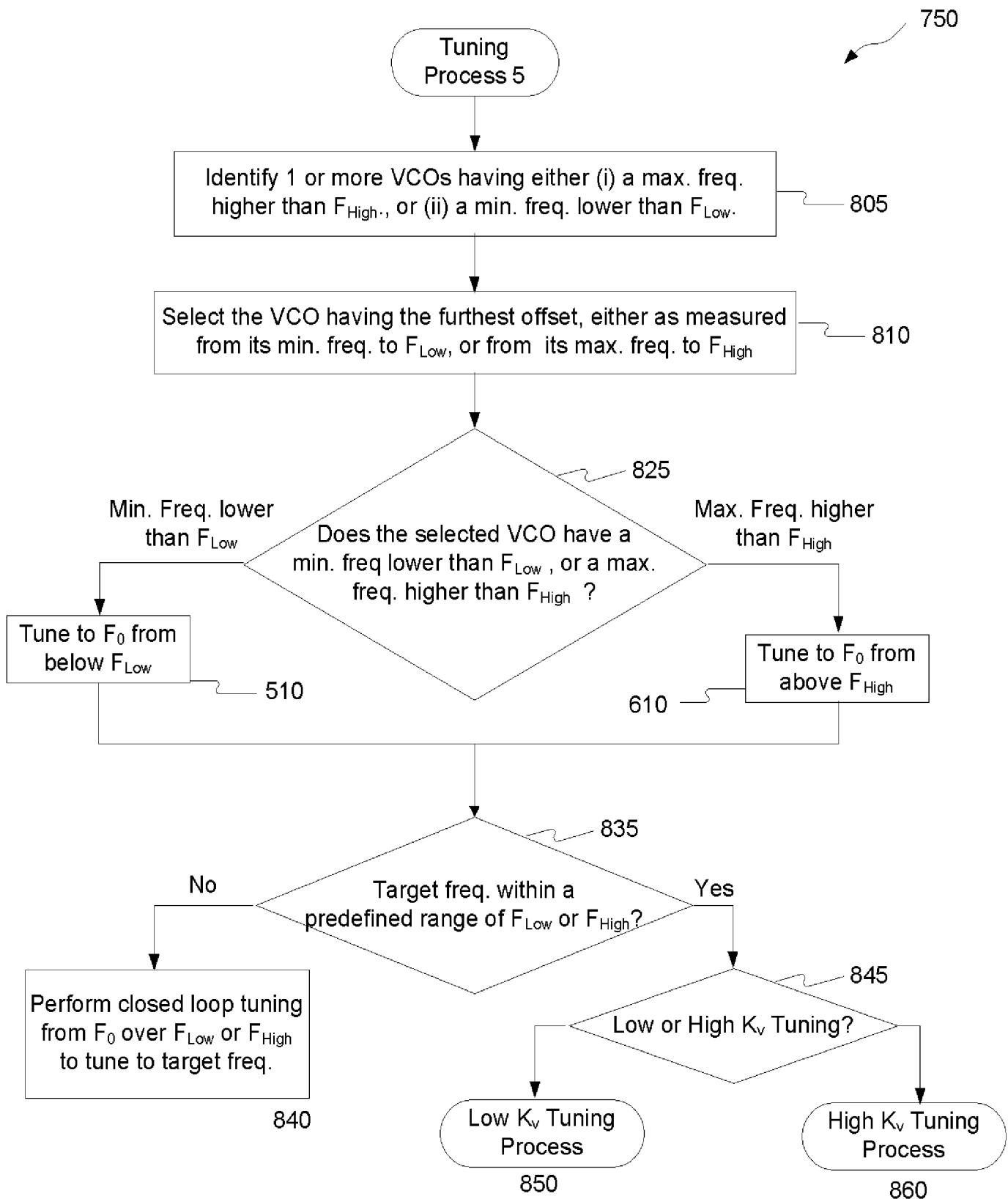

Fig. 8A illustrates an exemplary embodiment of a tuning process in which the requested target frequency is located between two closely spaced existing frequencies in accordance with the present invention.

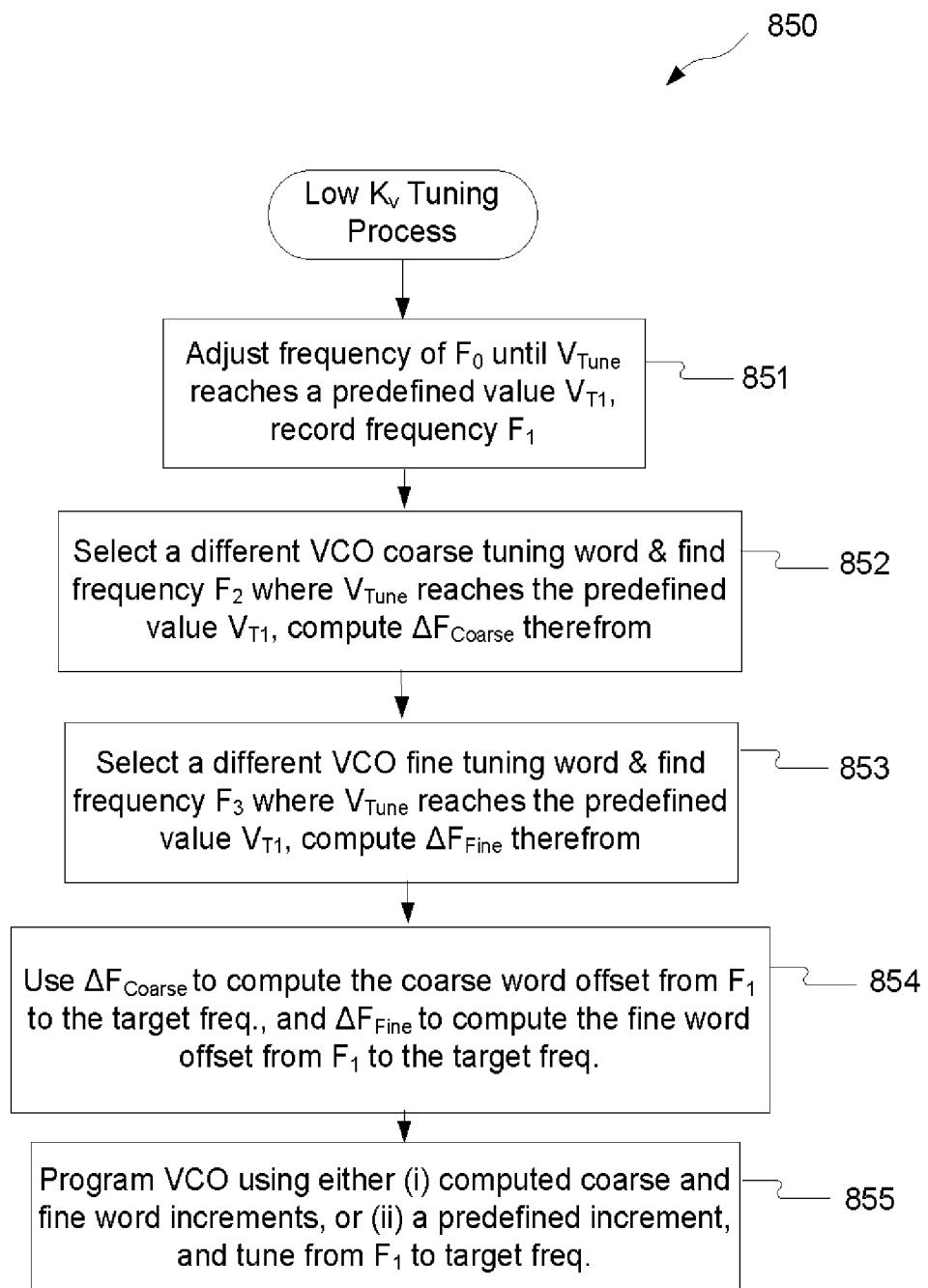

Fig. 8B illustrates an exemplary embodiment of process for tuning a low  $K_v$  voltage controlled oscillator to the requested target frequency residing between two closely spaced existing frequencies in accordance with the present invention.

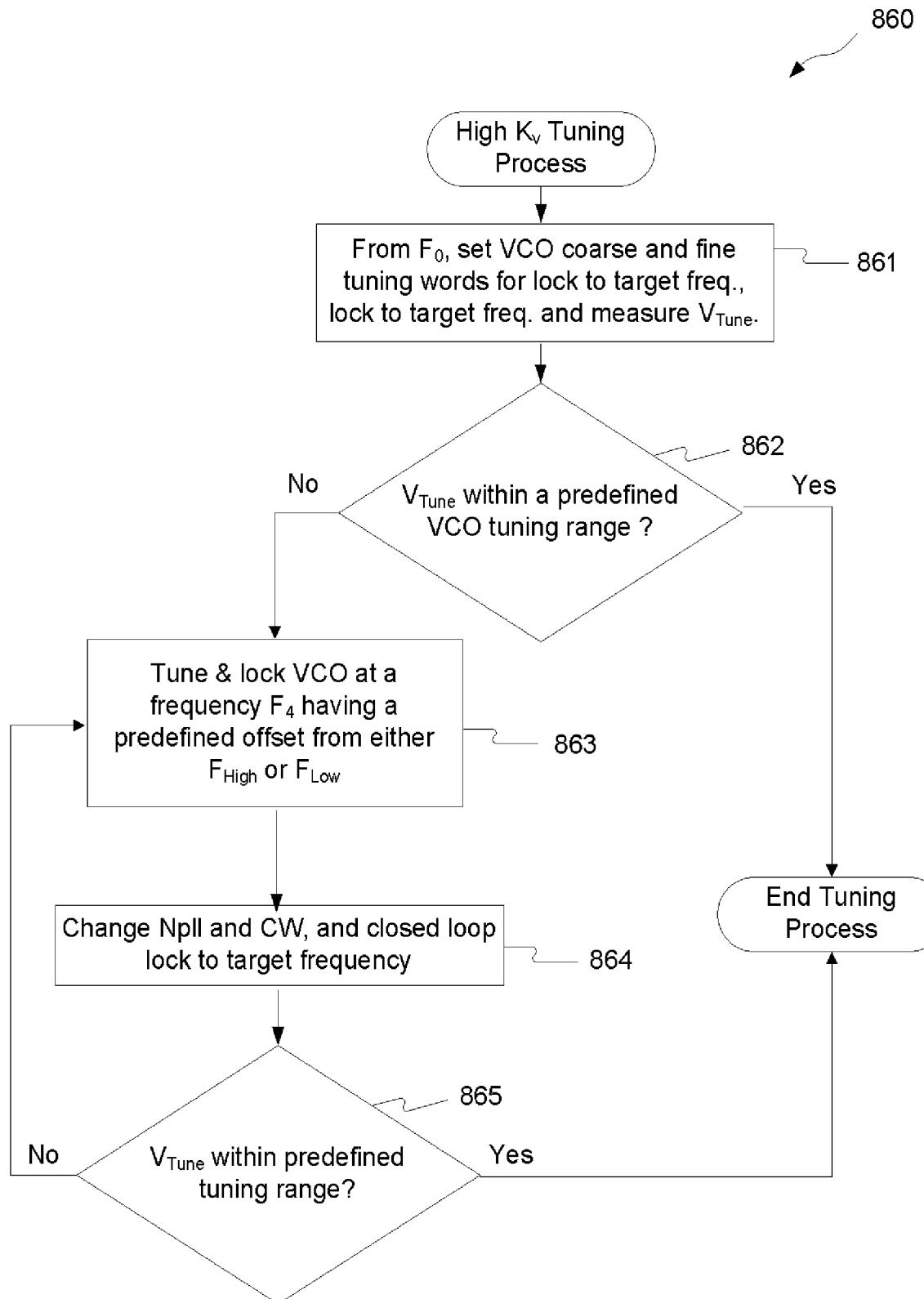

Fig. 8C illustrates an exemplary embodiment of a process for tuning a high  $K_v$  voltage controlled oscillator to the requested target frequency residing between two closely spaced existing frequencies in accordance with the present invention.

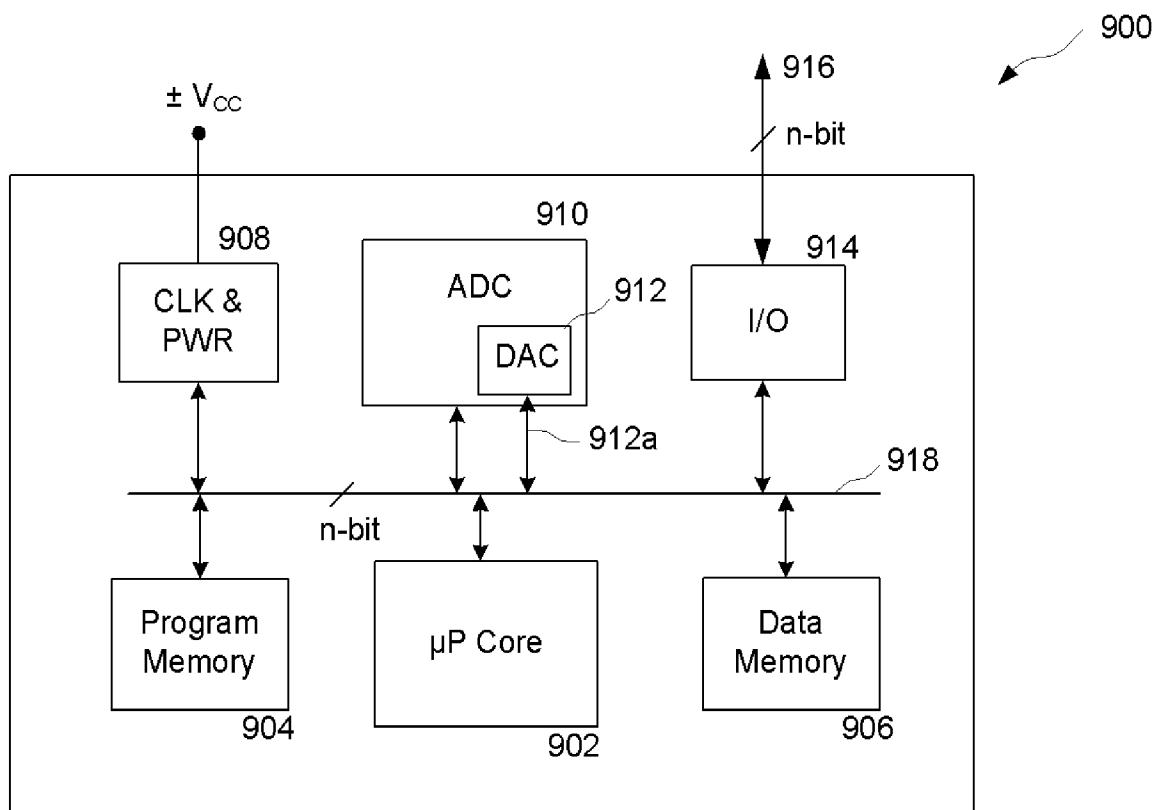

Fig. 9 illustrates a block diagram of an exemplary system microcontroller operable to control the multiple frequency source system in accordance with the present invention.

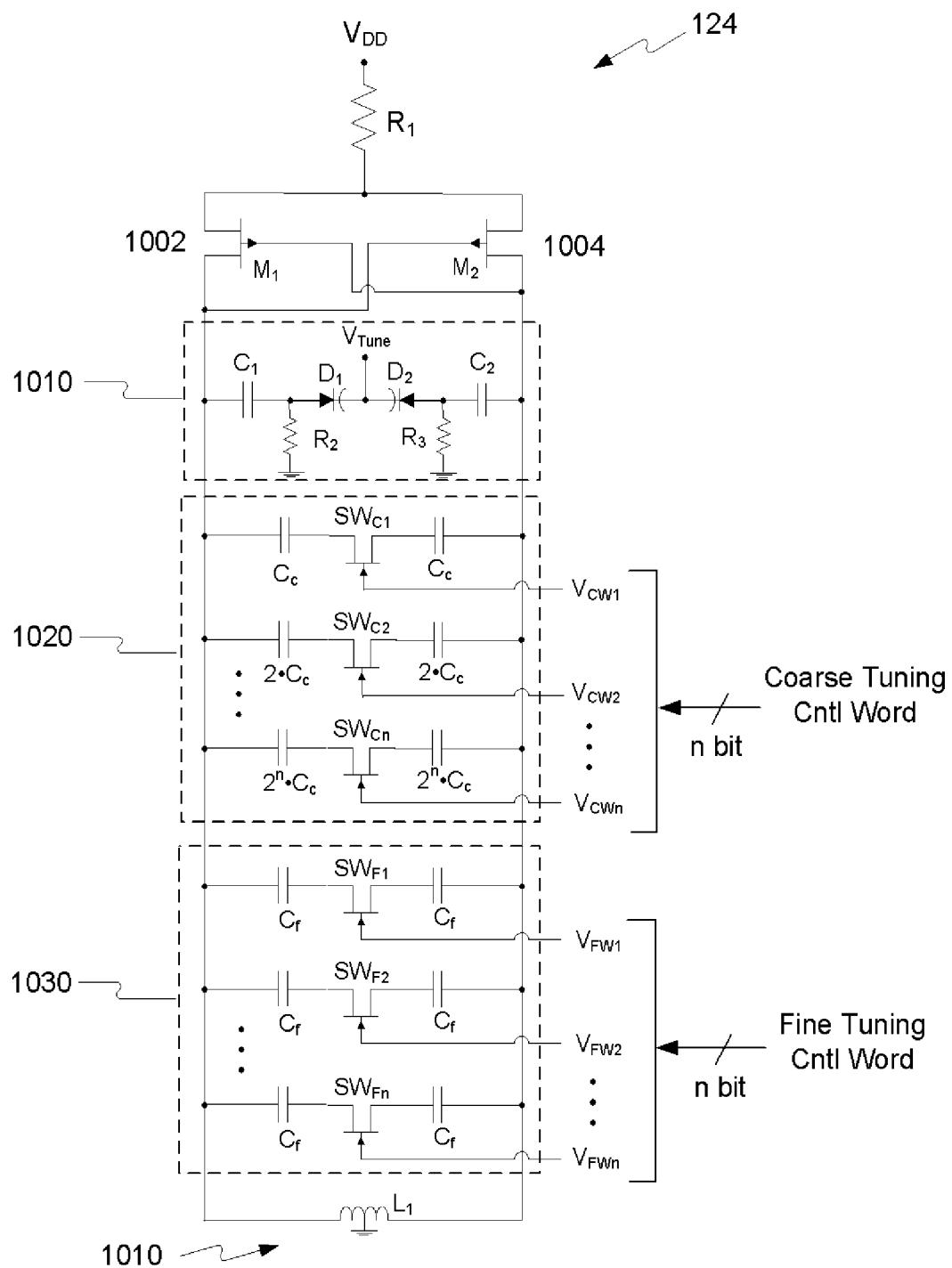

Fig. 10 illustrates an exemplary embodiment of an oscillator in accordance with the present invention.

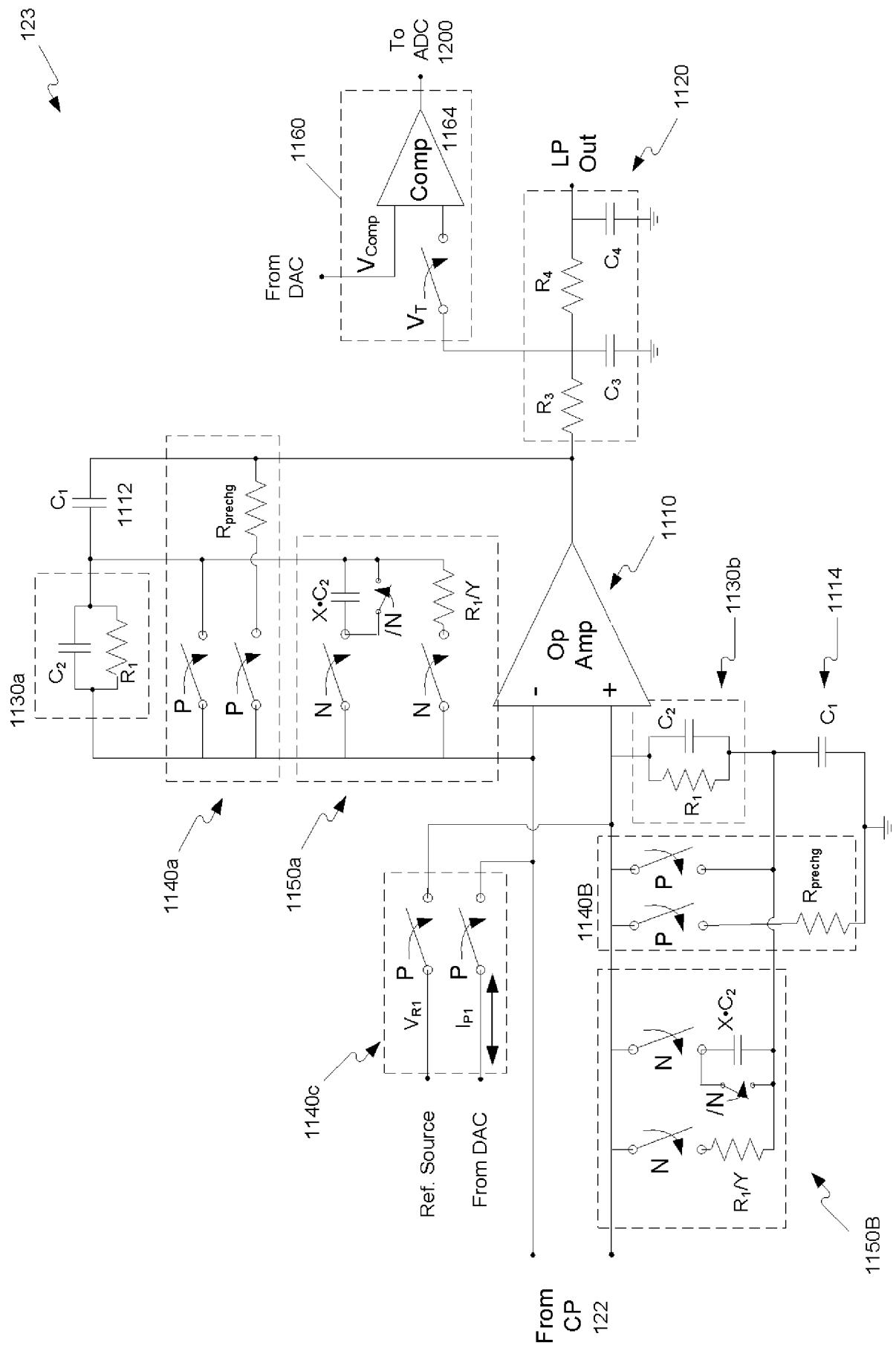

Fig. 11 illustrates an exemplary embodiment of a multi-mode loop filter in accordance with the present invention.

Fig. 12 illustrates an exemplary embodiment of an analog-to-digital converter employing a dual use digital-to-analog converter in accordance with the present invention.

Fig. 13A illustrates an exemplary embodiment of a direction control circuit for use with a phase-frequency detector in accordance with the present invention.

Fig. 13B illustrates the operation of the direction control circuit signals to avoid a transient frequency decrease when the oscillator is instructed to tune higher in frequency in accordance with the present invention.

Fig. 13C illustrates the operation of the direction control circuit signals in a normal mode to tune higher in frequency in accordance with the present invention.

[0010] For clarity, previously-identified features retain their reference indicia in subsequent drawings.

### Description of Exemplary Embodiments

[0011] The present invention provides systems and methods for operating multiple frequency sources within the same signal spectrum with the capability to tune to a desired (target) frequency without disturbing the operation of one or more existing frequencies generated within the spectrum. The required proximity between the target frequency and the existing signal(s) will depend upon system parameters, for example the required stability of the existing frequency, the range over which the source tuning to the target frequency must travel to reach the target frequency. The present invention is advantageously used in any system in which tuning to a target frequency is desired during the concurrent generation of another frequency within the operating frequency spectrum of the system.

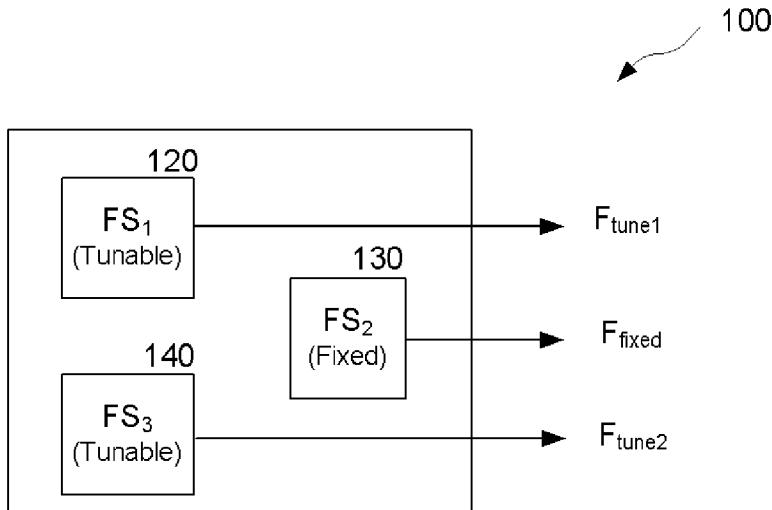

[0012] Fig. 1A illustrates an exemplary embodiment of a system employing currently operable frequency sources in accordance with the present invention. As shown, the tunable system 100 includes three frequency sources FS<sub>1</sub> 120, FS<sub>2</sub> 130 and FS<sub>3</sub> 140, at least one of which (e.g., FS<sub>1</sub> 120) is tunable. The remaining frequency sources may be operable to generate a fixed frequency or a tunable frequency, as required or desired by the system's design.

[0013] In an exemplary embodiment of the invention, a frequency source, e.g., 120, is tuned to a particular target frequency. As further described below, the process by which frequency source 120 tunes to the target frequency will depend upon the presence and proximity of any existing frequencies. In particular, tuning processes are described in which (i) the target frequency is presently the only generated frequency, (ii) the target frequency is located below the lowest existing frequency, (iii) the target frequency is located above the highest existing frequency, and (iv) the target frequency is located between two existing frequencies. Each of these tuning processes is described in detail below.

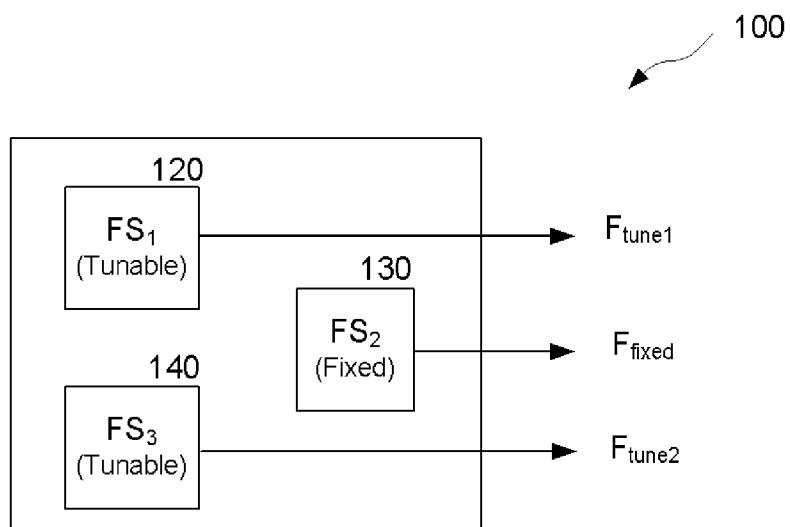

[0014] Fig. 1B illustrates an exemplary embodiment of the tunable frequency source 120 shown in Fig. 1A. As shown, the tunable source 120 is implemented as a phase

locked loop (PLL), which may be monolithically fabricated in a bipolar complementary metal oxide semiconductor (Bi-CMOS) process, although those of skill in the art will appreciate that the circuit may be formed using other processes or materials (e.g., CMOS, SiGe, GaAs) in monolithic, hybrid, or discrete form. In a particular embodiment of the invention, two or more (e.g., 3, 5, 10, 100 or more) PLLs are implemented in a system to provide a respective two or more tunable, synthesized frequencies within the same operating spectrum (e.g., a synthesized frequency spectrum covering 500 MHz - 10 GHz). The tunable source(s) may be implemented in other forms, such as a variable oscillator, a digitally controlled oscillator, and the like. Alternative to an all-tunable frequency source design, one or more fixed frequency source may be used, exemplary oscillators being in the form of L-C oscillators, crystal oscillators, dielectric resonator oscillators, and the like. In a similar vein, the tunable source(s) may be of another construction, such as a variable oscillator design, digitally controlled oscillator, and the like. Those skilled in the art will appreciate that the systems and methods of the present invention are not limited to any particular design or construction of the frequency source, tunable or fixed.

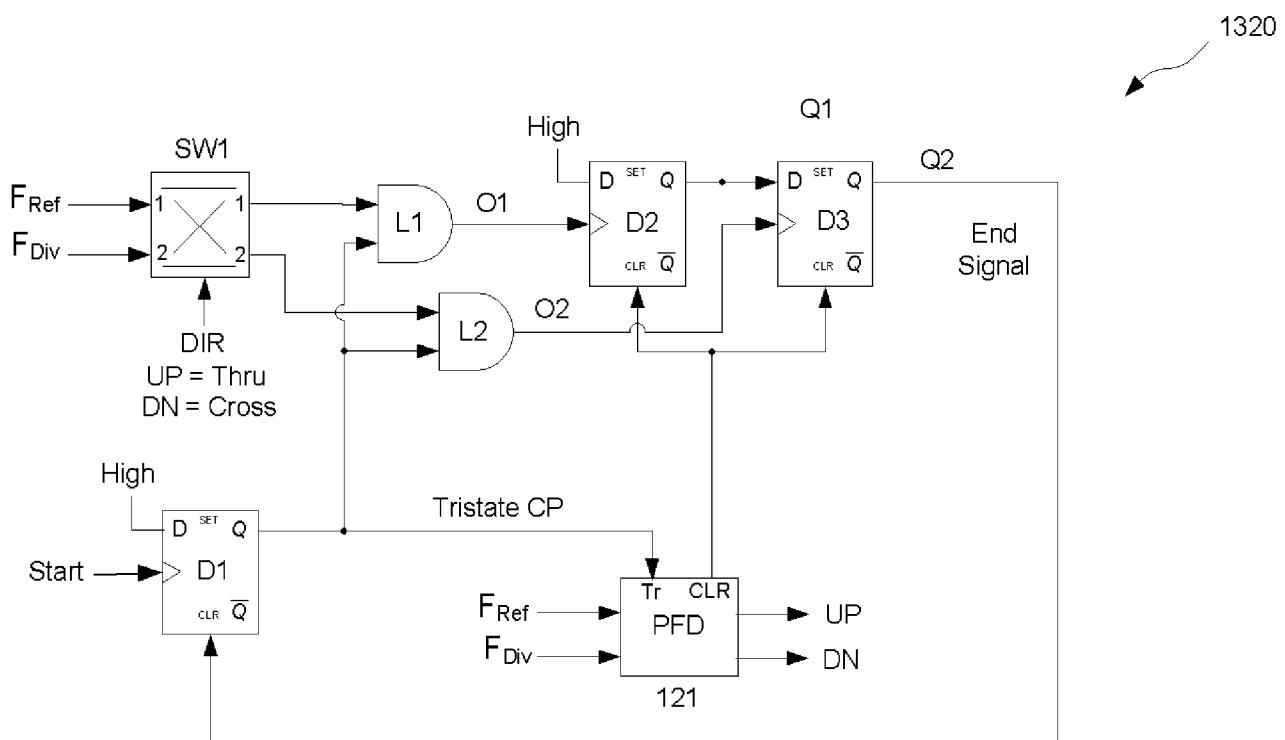

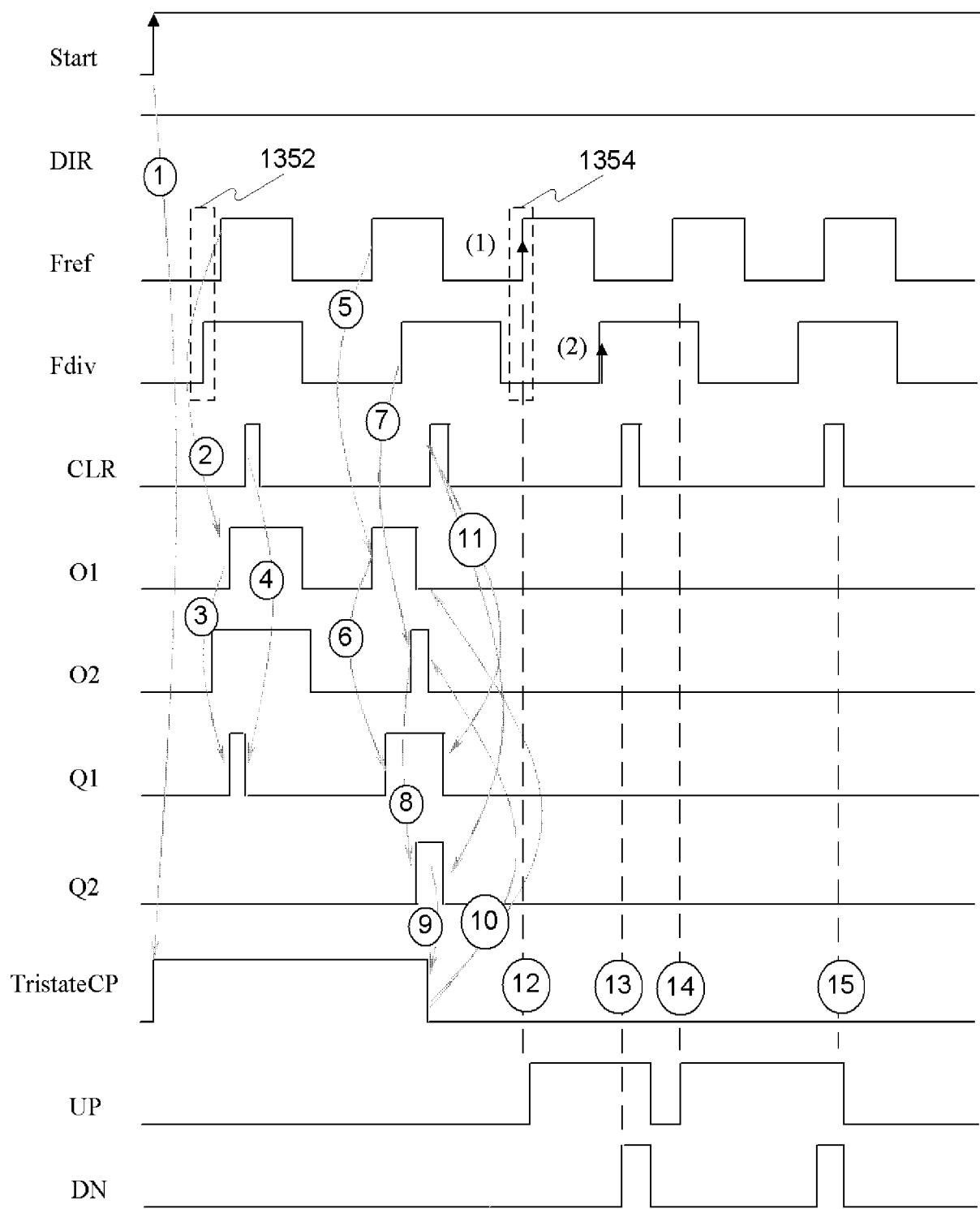

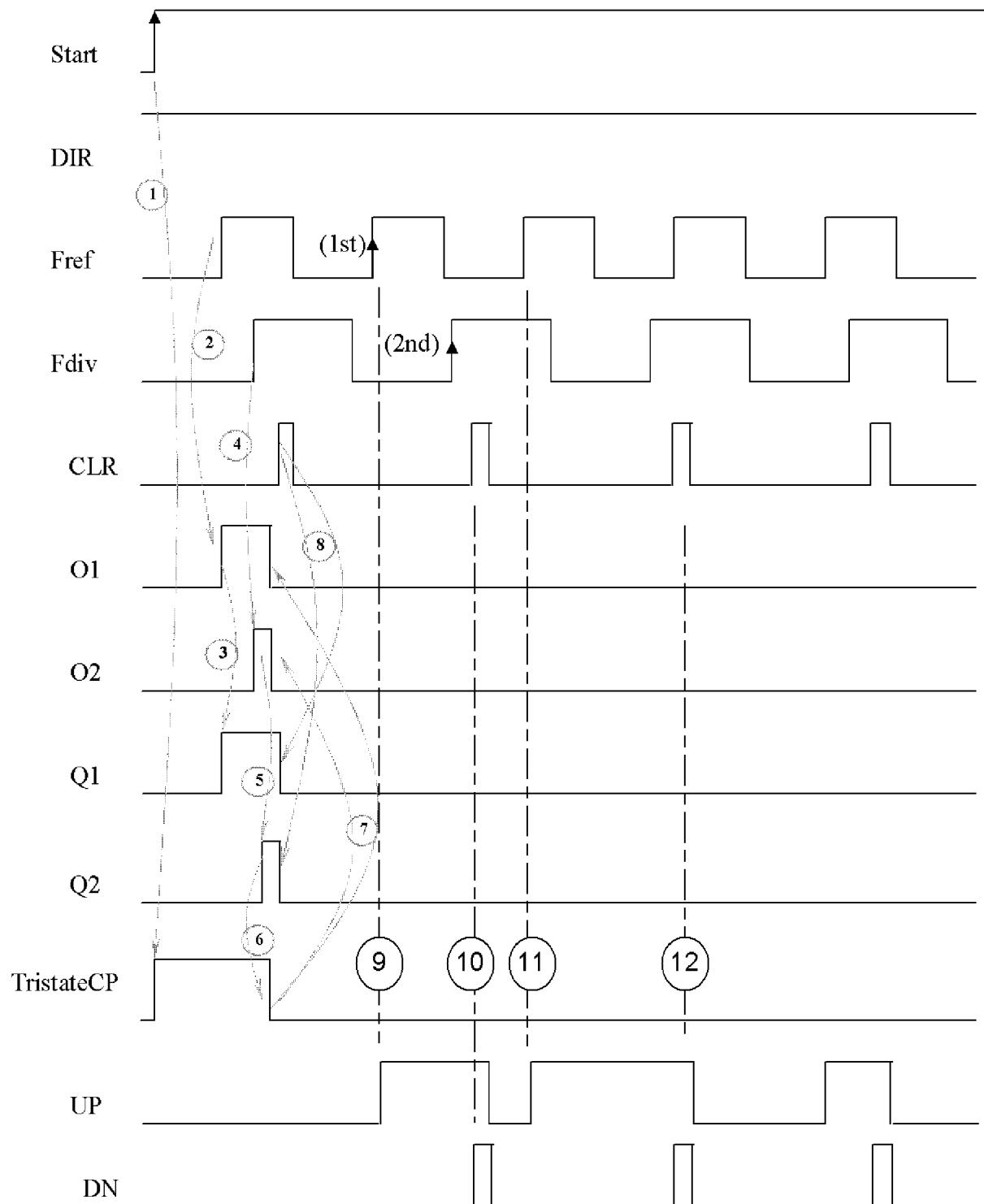

[0015] In the exemplary embodiment shown, the PLL 120 includes a phase-frequency detector 121 operable to compare the phase and frequency of a received reference signal  $F_{Ref}$  to a divided down version of the output frequency  $F_{Div}$ , the output of the phase-frequency detector being a signal (voltage or charge) representative of the difference between  $F_{Ref}$  and  $F_{Div}$ . In a particular embodiment of the invention, the phase-frequency detector 121 includes a direction control circuit to facilitate signal locking. An exemplary embodiment of the direction control circuit is illustrated in Fig. 13. As an alternative to the phase-frequency detector 121, a less complex phase detector may be employed as well.

[0016] In some embodiments, the PLL further includes a charge pump 122 operable to provide frequency control responsive to the output of the phase-frequency detector. Frequency control is provided by means of the charge pump either supplying current to or drawing current from the loop filter, these conditions providing a change in the voltage at

the input of a voltage-controlled oscillator (VCO) 124, the change in voltage resulting in a decrease or increase in the VCO's output frequency  $F_{Out}$ . When, for example, the UP signal is in a high state and the DN signal is in a low state, the oscillator is controlled to increase its output frequency. When the UP signal is in a low state and the DN signal is in a high state, the input voltage of the oscillator is controlled to decrease its output frequency. In an alternative embodiment, the charge pump 122 is omitted, and the UP/DN signals are generated from the phase-frequency detector 110 itself.

[0017] The PLL further includes a loop filter 123 operable to receive and filter the charge pump UP and DN signals, thereby reducing noise and spurious product content of the loop signal. The loop filter 123 may be passive or active, a typical embodiment of the latter employing an operational amplifier, or similar functional device. In a specific embodiment of the invention, the loop filter 123 is operable in several different modes, including a normal mode in which the oscillator is tuning freely, a pre-charge mode in which the filter's initial operating condition (e.g., voltage) is controllably set, a voltage read mode in which the tuning voltage of the oscillator is read, and a low frequency overshoot mode, in which the frequency overshoot of the phase locked loop is minimized. An exemplary embodiment of the multi-mode loop filter is presented below in Fig. 11. Alternative embodiments of the invention may employ a conventional loop filter known in the art.

[0018] The loop filter output signal is supplied to an oscillator 124, illustrated as a voltage controlled oscillator (VCO) in an exemplary embodiment. In a particular embodiment of the invention, oscillator 124 is included within a VCO bank, selection from which is defined by a particular oscillator selection process, which is further described below. In alternate embodiment of the invention, the oscillator 124 is a conventional VCO implemented either singly, or within a bank of VCOs as these features are known in the art. Other oscillators, such as digitally controlled oscillators may be employed alternatively in the present invention. Responsive to the supplied loop filter signal, the oscillator 124 generates a signal at frequency  $F_{Out}$ . An exemplary embodiment of the oscillator 124 is illustrated in Fig. 10 below. Of course, various types of oscillators

may be used. Those skilled in the art will appreciate that the invention is not limited to any particular oscillator design.

[0019] A portion of the output signal  $F_{Ref}$  is fed back to a divide-by-N counter 126, which is operable to divide down the output frequency by a particular amount N or fraction thereof. The divide-by-N counter 126 may be an integer or fractional N counter, as well as implement a sigma-delta modulator 127 to provide a sigma-delta PLL design to provide a smaller dividing ratio and greater tuning resolution. The divided down signal  $F_{Div}$  is subsequently provided to the phase-frequency detector which continues comparing the phase and frequency of the divided down signal and reference signals  $F_{Div}$  and  $F_{Ref}$  to generate an output signal. Furthermore, all or any portion of the loop's signal path may be of a single-ended or differential design.

### I. Exemplary Tuning and System Processes

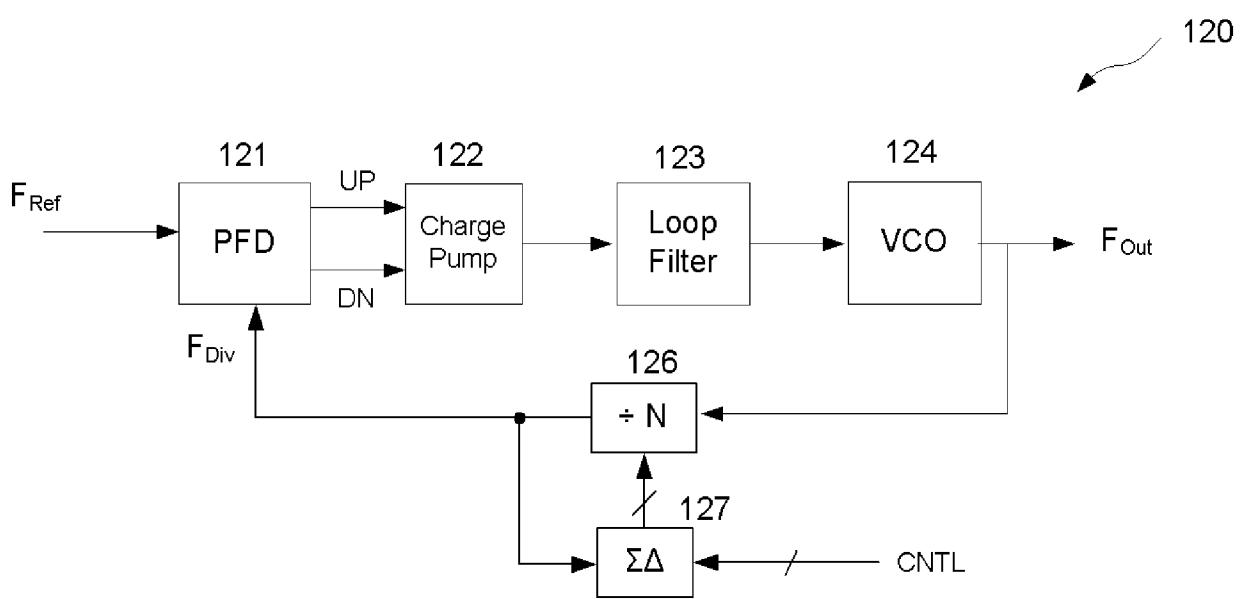

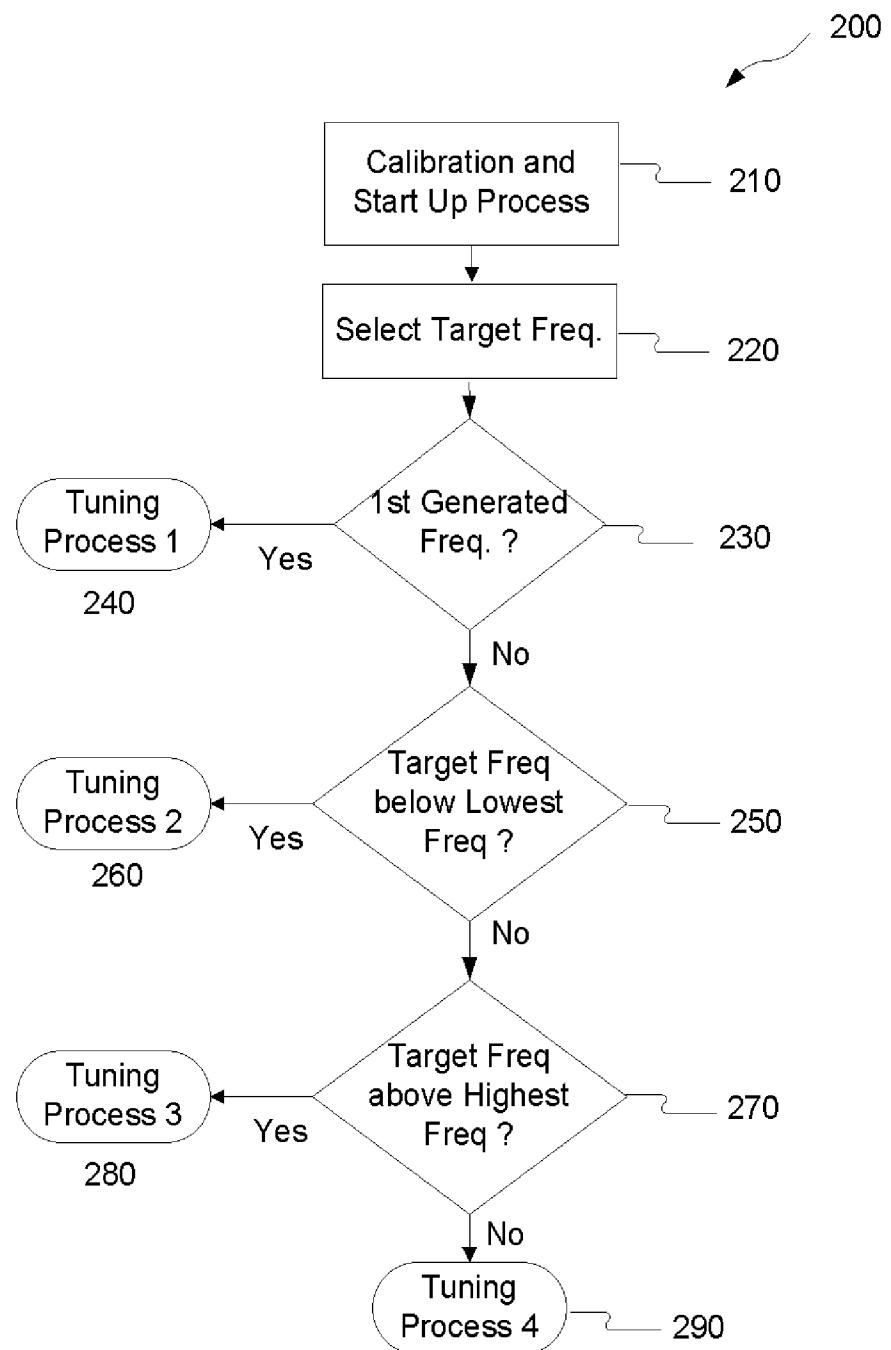

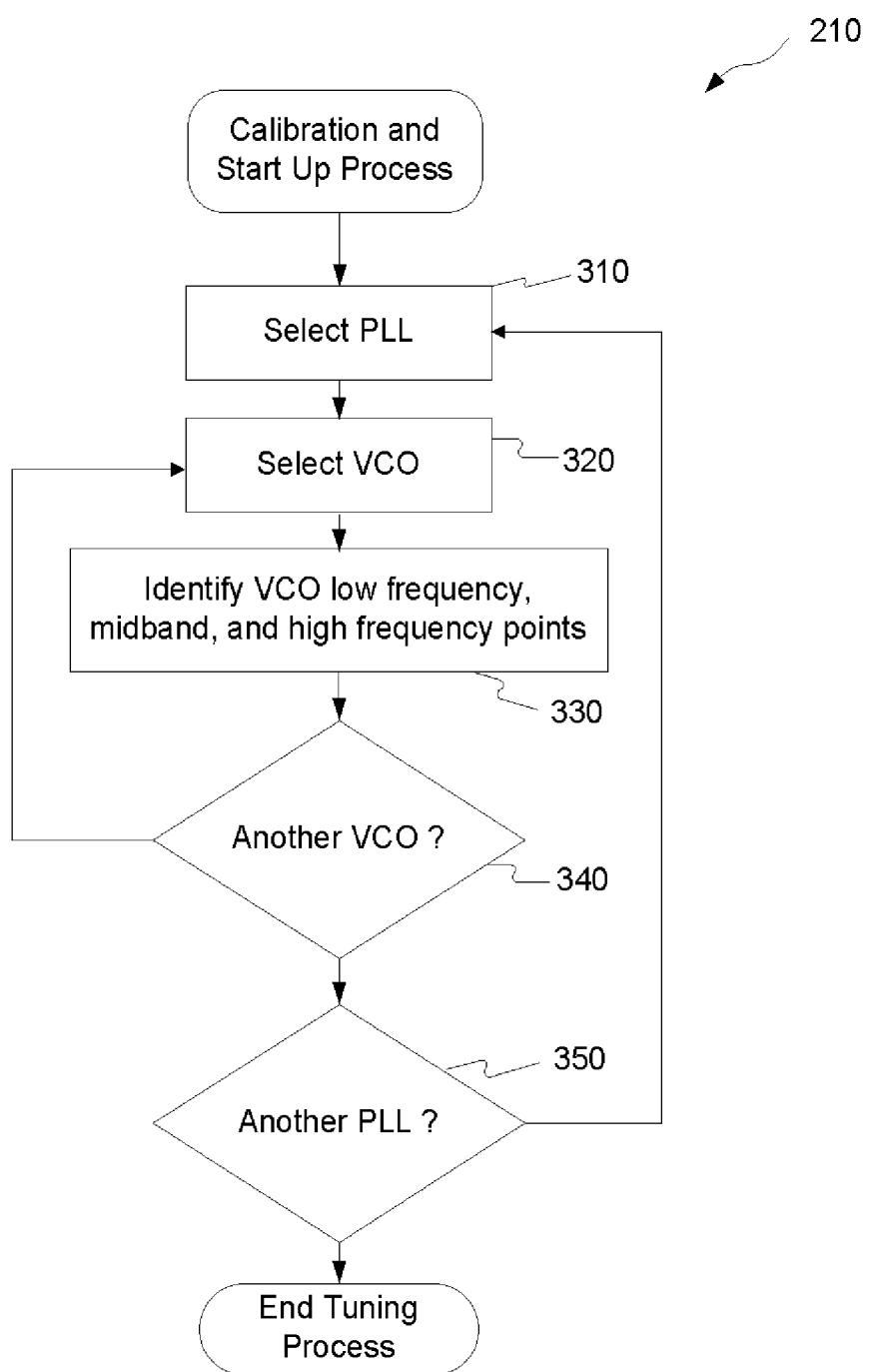

[0020] Fig. 2 illustrates an exemplary method for tuning one of the frequency sources to a target frequency in a multiple frequency source system in accordance with the invention. The method 200 includes a calibration and start-up process 210 operable to establish ranges for each of the oscillators employed within each of the frequency sources. In a particular embodiment of the invention, each frequency source is a tunable PLL frequency source, each PLL having multiple VCOs as its oscillators. In an alternative embodiment, the system may include a tunable source of a different construction, or having perhaps only one oscillator. In still a further embodiment, the system may include one or more fixed frequency sources, each having a single oscillator. An exemplary embodiment of the calibration and start-up process 210 is illustrated in Fig. 3A below.

[0021] Subsequent to calibration and start-up processes, a request to operate a signal at a particular target frequency is received at 220. At 230, a determination is made as to whether any other signals are being concurrently generated by the other frequency sources in the system. If no other signals are being produced, the process continues at

240 where an appropriate oscillator is selected and the signal generated at the requested target frequency. Fig. 4 further illustrates an exemplary embodiment of this process.

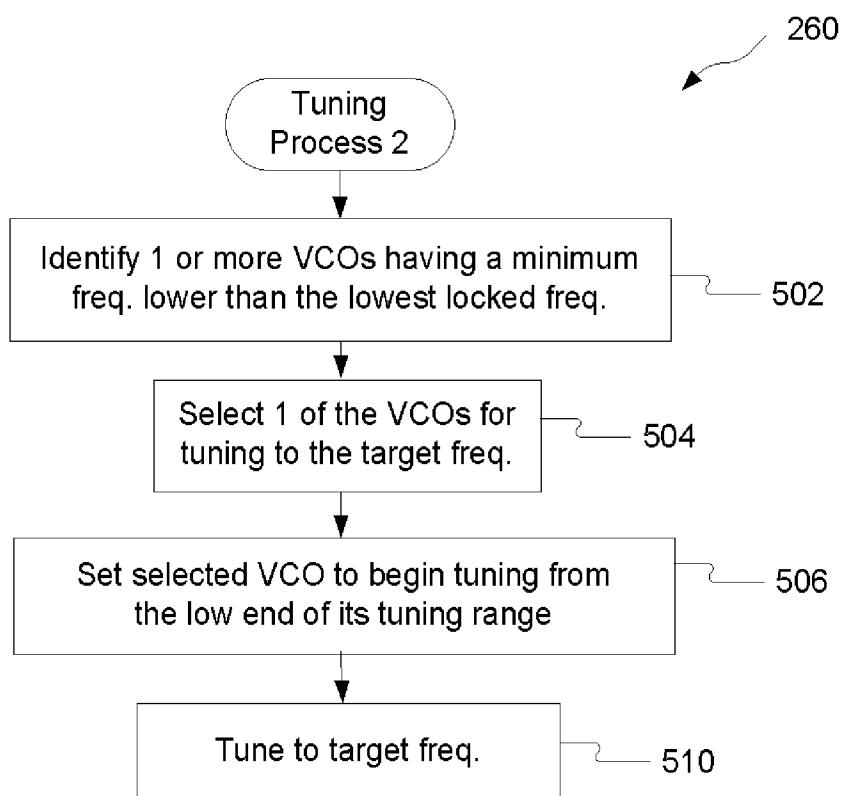

[0022] If one or more frequency sources are presently operating, the process continues at 250, where a determination is made as to whether the requested target frequency is below the lowest generated frequency. If so, the process continues at 260 in which an appropriate oscillator is selected and the signal generated at the target frequency. An exemplary embodiment of this process is further described in Fig. 5A below.

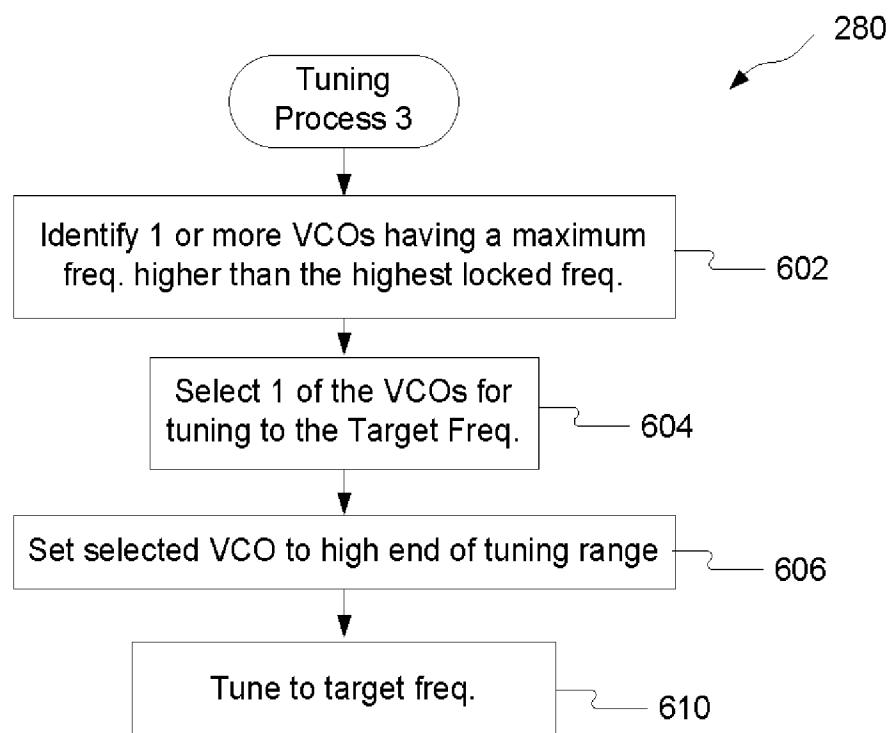

[0023] If the target frequency is not below the lowest generated frequencies, the process continues at 270 where a determination is made as to whether the target frequency is above the highest generated frequency. If so, the process continues at 280 whereby an appropriate oscillator is selected and a signal generated at the requested target frequency. An exemplary embodiment of this process is further illustrated in Fig. 6A below.

[0024] If the target frequency is not above the highest generated frequencies, the requested target frequency is located between two generated frequencies. The process continues at 290 where an appropriate oscillator is selected and a signal generated at the requested target frequency, an exemplary process of which is described in Fig. 7A below.

[0025] Fig. 3A illustrates an exemplary embodiment of a start-up and calibration process in accordance with the present invention. The exemplary embodiment shows each of the frequency sources as phase locked loop circuits (PLL), each PLL employing two or more voltage controlled oscillators (VCOs) to collectively provide a total tuning range over which the particular PLL generates its output frequency. Those skilled in the art will appreciate that only one of the frequency sources need be tunable, and that other tunable or fixed frequency sources may be used in alternative embodiments of the invention.

[0026] The process begins at 310 where one of the plurality of PLLs are selected, and at 320, one of its corresponding VCOs are activated. After selection, the VCO is tested at 330 to determine its lowest frequency operating point, a midband frequency point, and its highest frequency operating point. The process continues at 340 in which the next (if any) VCO is selected, and the processes of 320-330 are repeated therefor. When no further VCOs for the selected PLL remain, another PLL is selected at 350 and its corresponding VCO(s) are activated for determining their corresponding lowest, midband and highest operating frequency points. When no further PLLs remain, the start and calibration process concludes. Similar operations may be performed for other tunable frequency sources, as well as fixed frequency sources. For example in the latter, process 330 can be omitted, since the oscillator of the fixed frequency source would typically not include low, midband, and high frequency points. Further, the process of 340 can be omitted for fixed or tunable frequency sources employing a single oscillator. Other modifications will be apparent to the skilled person.

[0027] In a particular embodiment of the invention, the VCO's operating frequency is controlled digitally through the use of coarse and fine tuning words supplied to the VCO. In one exemplary embodiment, the coarse tuning word ranges from a value of 0 to 31, zero representing the highest operating VCO frequency, and thirty-one representing the lowest VCO operating frequency. In such an embodiment, the aforementioned process of 330 of identifying a VCO low frequency, midband and high frequency point is performed by supplying control words of values 31, 15, and 0, respectively, and recording the locked frequency at a predefined frequency, for instance at 1.5 V representing the center of the VCO's linear-most tuning range. Those skilled in the art will appreciate that the VCOs frequency may be set using analog voltages, or a digital word of shorter or longer length may be used in alternative embodiments under the present invention.

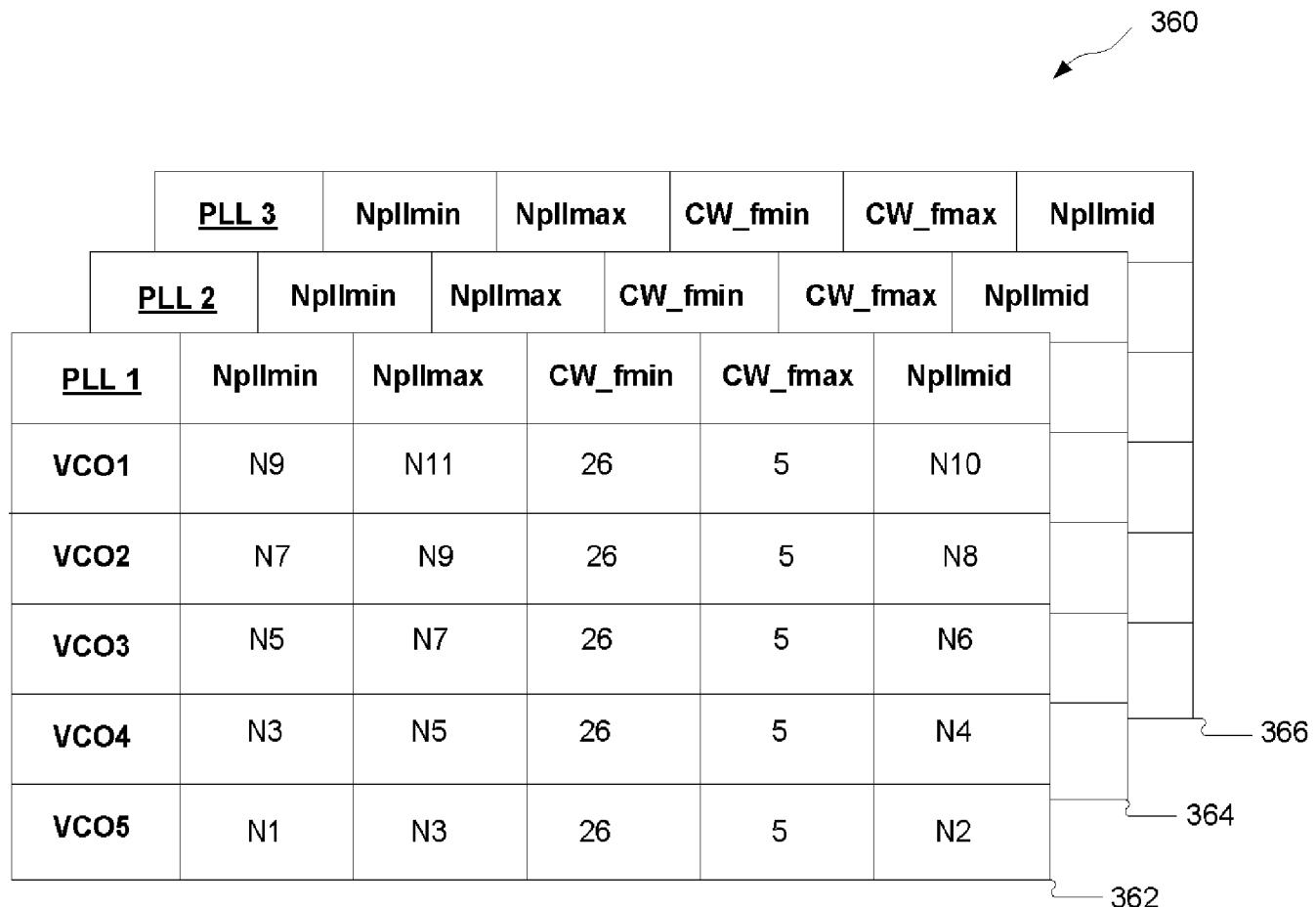

[0028] Fig. 3B illustrates an exemplary data structure operable to store operating frequency points for a plurality of oscillators within a PLL frequency source in accordance with the present invention. The described embodiment illustrates a total of three PLLs, each PLL having five VCOs. Of course, another arrangement as to the

number of PLLs and the number of VCOs per PLL may be used in alternative embodiments under the present invention. Further as mentioned above, frequency sources other than PLLs may be implemented in alternative embodiments under the present invention.

[0029] In the exemplary embodiment, the vco\_freq data structure 360 includes three pages 362, 364, and 366, each page corresponding to one PLL. Each data structure page lists a divider ratio Npll corresponding to the lowest, midband, and highest operating frequency points of each of the five VCOs, these quantities labeled as Npllmin, Npllmax, and Npllmid, respectively. Each VCO is operable to provide tuning over a particular frequency band, all collectively providing a total tuning range for the particular PLL.

[0030] In addition, each page includes digital coarse tuning words (“coarse words” or “CW” herein) CW\_fmin and CW\_max corresponding, respectively, to the lowest and highest operating frequency of the particular VCO. Coarse words CW\_fmin and CW\_fmax are digital control signals, which, when supplied to the VCO, control the VCO to tune to the lowest and highest frequency. Parameter Npllmid corresponds to the resulting divider ratio when the particular VCO is supplied coarse word representing the midband point, which is 15 in the illustrated embodiment.

[0031] In the data structure shown, the lowest VCO operating frequency is identified with a coarse word CW\_fmin of value 25 instead of 31, and the highest VCO operating frequency CW\_fmax is identified with a value 5 instead of 0, thereby providing some margin for overlap between adjacent VCOs. The actual highest and lowest tuning point of each VCO can be interpolated from the coarse words when the tuning range per coarse word increment is known; for example if it is known that CW\_fmin of VCO 1 is 25 and that coarse word corresponds to a frequency of 4,000 MHz, and it is further known that the VCO tunes over 400 MHz over 32 coarse word increments, then it can be determined that each coarse word increment will provide approximately 12.5 MHz of tuning range. Accordingly, although VCO1 is tuned to 4000 MHz at CW 25, it is able to tune to 6 x 12.5 MHz, or 75 MHz lower in frequency, thereby overlapping the high end of the tuning

range of VCO 2. In this manner, adjacent VCOs can be designed to provide overlap in their tuning frequency range to ensure gap-free tuning capability with process, temperature, operating or other variations.

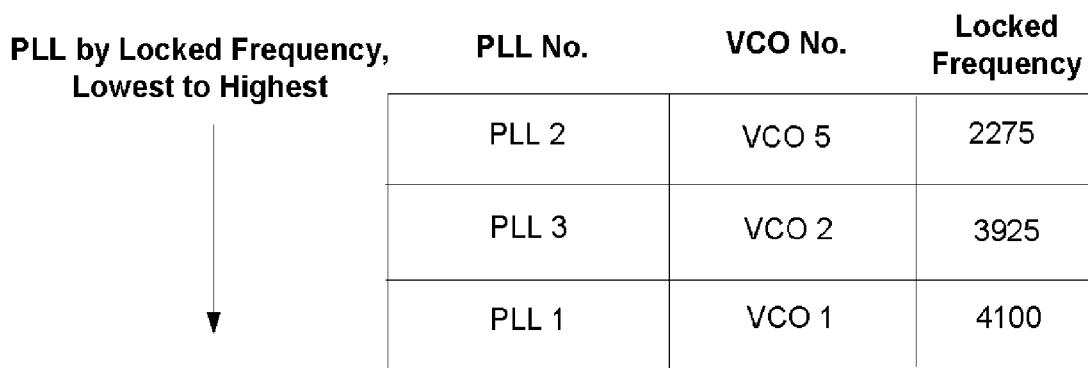

[0032] Fig. 3C illustrates an exemplary data structure operable to store presently generated frequency information in accordance with the present invention. The already\_generated data structure 370 includes information as to the presently generated or locked frequency (if any) of the PLLs, the PLL providing the locked frequency, and the VCO within the PLL employed to provide the locked frequency. In a particular embodiment, PLL and VCO information pertaining to the lowest generated frequency is listed first, and the highest generated frequency last. In a further exemplary embodiment, when a PLL does not produce an output frequency, it's generated frequency is displayed as a frequency outside of the stored frequency of operation, for example 0 or 5000 MHz, when no PLL is operable to produce a signal at this frequency. Further particularly, the data structure 370 is updated and re-ordered when a generated signal changes frequency, is activated, or de-activated.

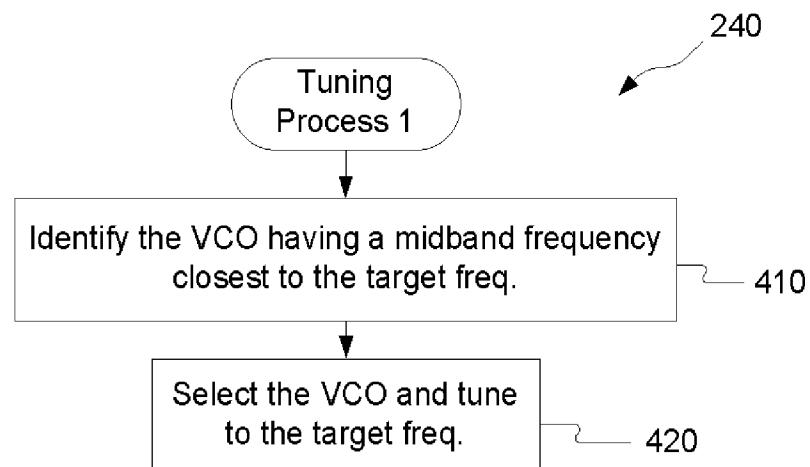

#### Target Frequency is First Locked Frequency

[0033] Fig. 4 illustrates an exemplary embodiment of the tuning process 240 in which the requested target frequency is the first generated frequency (or “locked” frequency in the case of a PLL-generated signal) in accordance with the present invention. When the multiple frequency source system presently generates no other signals, the oscillator selection process includes identifying an oscillator, e.g. a VCO, having a midband frequency point closest to the target frequency (410). The identified VCO is activated and permitted to tune and lock to the requested target frequency at 420.

#### Target Frequency Located Below Lowest Locked Frequency

[0034] Fig. 5A illustrates an exemplary embodiment of a tuning process 260 in which the requested target frequency is lower than the lowest generated frequency in accordance with the present invention. In a particular embodiment of the invention, VCO tuning to

the target frequency occurs by approaching the target frequency from the below the second (existing) frequency, without crossing the existing frequency.

[0035] The process begins at 502 whereby one or more oscillators (e.g., a VCO) having a minimum frequency lower than the lowest generated/locked frequency are identified. At 504, one of the identified VCOs is selected for tuning to the target frequency. The selection process may involve various factors, including which of the selected VCOs, when tuned to the target frequency, will be closest to, or within the linear-most tuning range, and which selected VCO can be activated at a frequency which is furthest from the locked frequency.

[0036] At 506, the selected VCO is set to begin tuning from a start frequency in the low end of its tuning range. In a particular embodiment, the selected VCO is supplied its corresponding coarse word CW\_fmin, setting the tuning frequency to its minimum frequency point. In an alternative embodiment, the VCO is configured to begin tuning from another point in the low end of its frequency range. At 510, the selected VCO is activated and permitted to tune and lock to the requested target frequency.

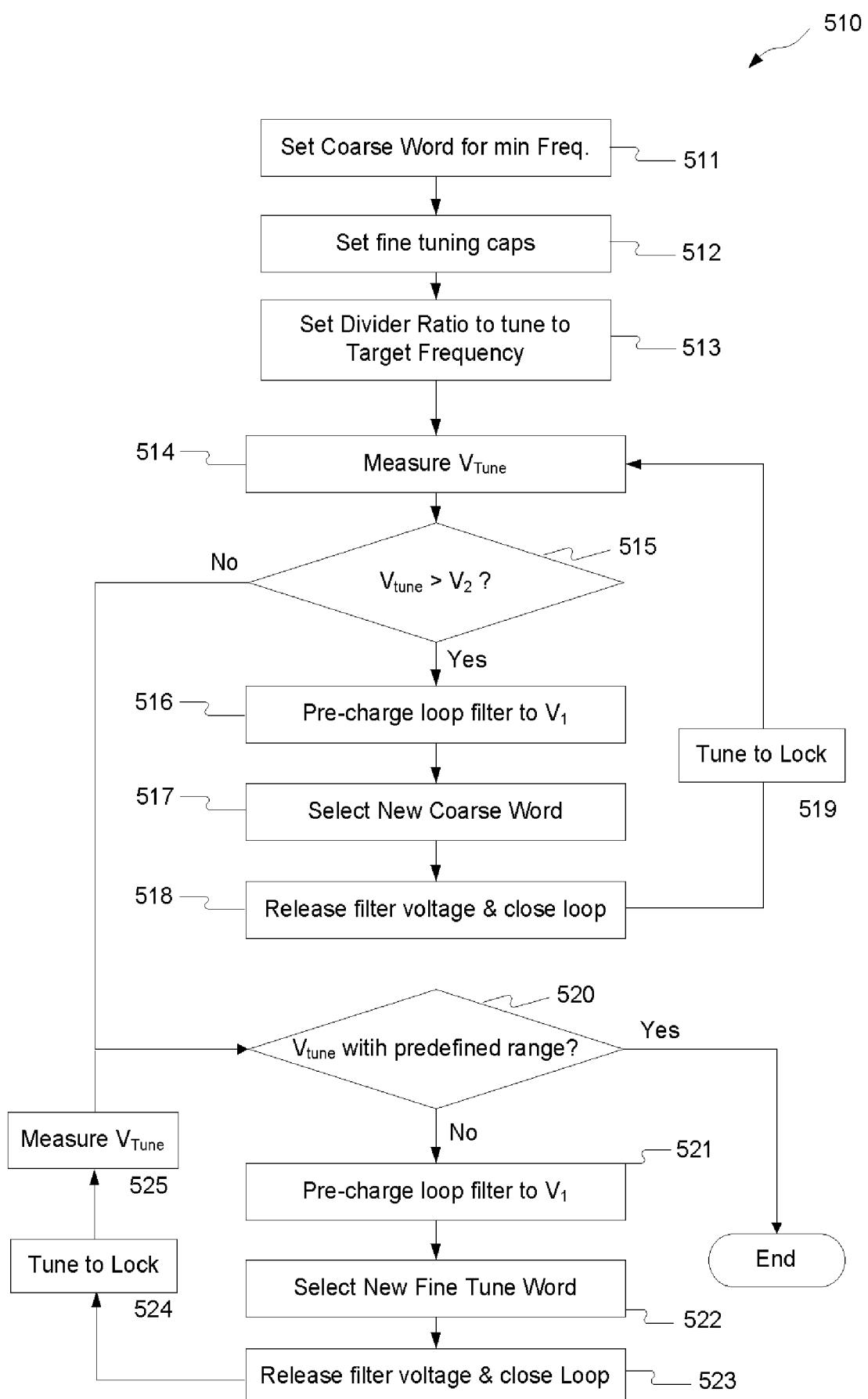

[0037] Fig. 5B illustrates an exemplary embodiment of a process 510 in which the selected oscillator is activated and tuned to a target frequency lower than the lowest generated frequency in accordance with the present invention. Initially at 511, the selected VCO is set to its lowest operating frequency point by supplying the VCO with the CW\_fmin coarse word. At 512, the fine tune setting of the VCO is set to its lowest frequency setting, in a particular embodiment by switching in all of the fine tuning capacitors. At 513, the PLL divider ratio N is set to tune to the target frequency, and at 514 the tuning voltage VTune of the VCO is measured.

[0038] At 515, a determination is made as to whether the tuning voltage is measured higher than the VCO's maximum voltage, V<sub>2</sub>. If it is, the VCO is not in the correct coarse tuning range, as the present coarse tuning range is too low in frequency. In this case, the processes of 516-519 are performed by which the loop filter is precharged at to

a predefined voltage (the lowest tuning voltage  $V_1$  in a particular embodiment), a coarse word corresponding to the next higher frequency range selected, the loop filter released from the pre-charge voltage, and the VCO activated with the new coarse word and attempts to tune to lock. An exemplary circuit for pre-charging the loop filter is described below in Fig 11.

[0039] If the tuning voltage  $V_{Tune}$  is lower than the VCO's maximum voltage  $V_2$ , the VCO is within a tunable coarse range, and the process continues at 520-525 in which a fine tuning process is performed. In a particular embodiment illustrated, a first determination is made at 520 as to whether the tuning voltage  $V_{Tune}$  is within a predefined range, for example 1.25V to 1.75V, where 1.5V represents the VCO midband frequency point. The predefined range may be any desired range, which, for example represents the most linear range of the oscillator.

[0040] If at 520, the tuning voltage  $V_{Tune}$  is not within the predefined range, the VCO is out of the correct fine tuning range, and is too low in frequency (as the fine tuning range was set to the lowest tuning range in 512). In this instance, the processes of 521-525 are performed, whereby the loop filter is pre-charged to a predefined voltage (e.g., the lowest tuning voltage  $V_1$ ), a fine tuning word corresponding to the next higher frequency range selected (which is operable to switch out one or more of the fine tuning capacitors), the loop filter released from the pre-charge voltage, and the VCO activated with the new fine word and attempts to tune to lock. The tuning voltage is again measured to determine if it is within the predefined range, and if not, the processes of 520-525 are repeated. Once the tuning voltage reaches a value within the predefined range, the tuning process concludes.

#### Computing Intermediate Frequency Points

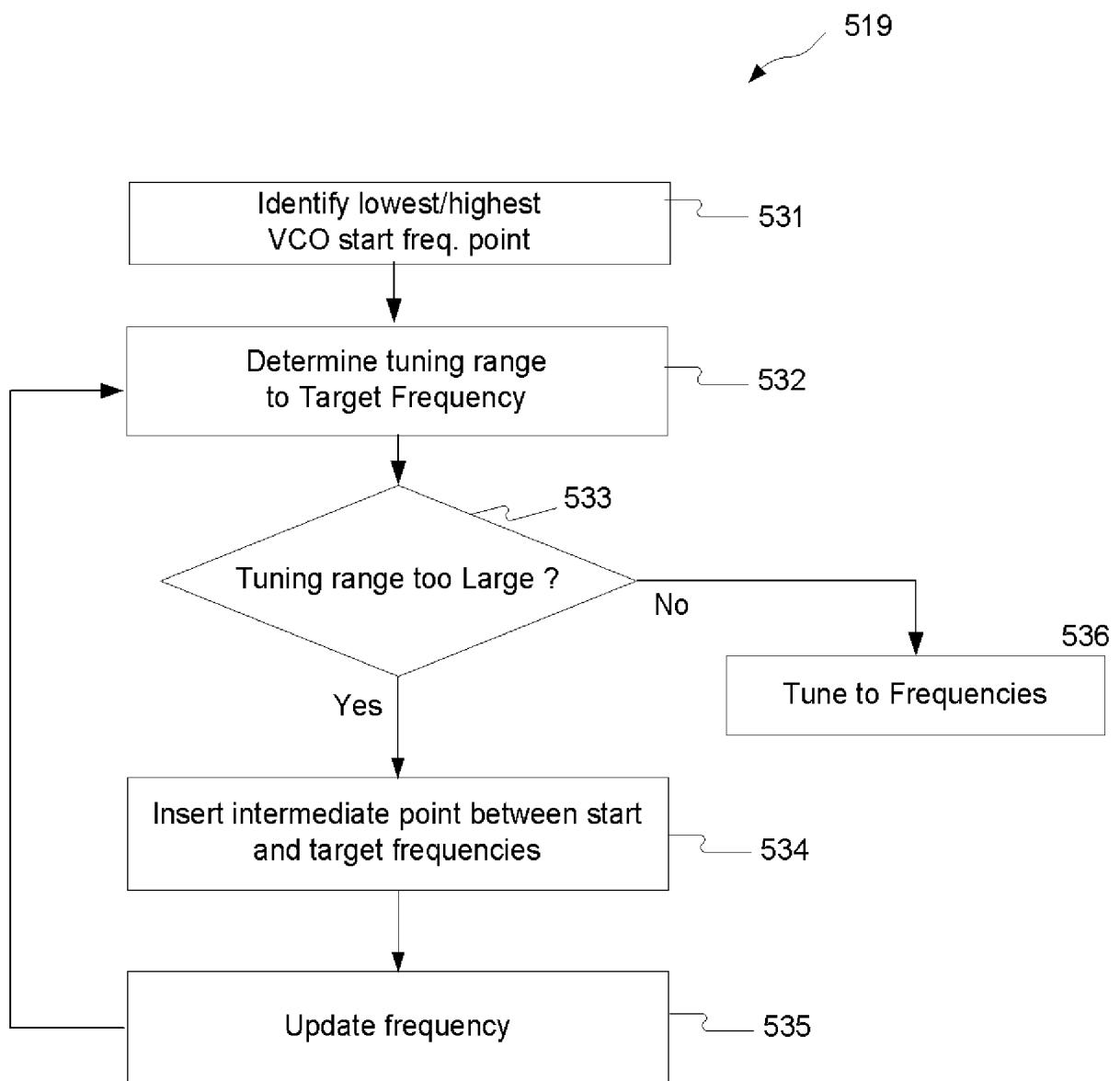

[0041] Fig. 5C illustrates an exemplary embodiment of the process 519 in which the selected oscillator tunes to the desired target frequency in accordance with the present invention. In this embodiment, the start frequency of the VCO is not known in advance,

but it is known that the VCO will start tuning from a frequency which is at or above the lowest VCO tuning frequency.

[0042] Initially at 531, the lowest VCO (or other oscillator type) frequency is identified. Next at 532, the tuning range between the lowest tuning frequency and the target frequency is determined. In the illustrated embodiment, the lowest VCO frequency is the frequency corresponding to the coarse word CW\_fmin, which can be ascertained from the data structure shown in Fig. 3B.

[0043] At 533, a determination is whether the tuning range moving from the lowest VCO frequency (or updated start frequency, further explained below) to the target frequency is too large. When the selected VCO tunes over too large of a frequency range, it can create effects which interfere with the operation of an existing frequency.

[0044] If at 533, a determination is made that the VCO tuning range to the target frequency would be to wide, the process continues at 534 where an intermediate frequency is defined between the start frequency (either the VCO lowest tuning frequency or a previously defined intermediate frequency point, as described below) and the target frequency. Next at 535, the previous start frequency used in 533 to determine whether the tuning range was too large is updated as being the intermediate frequency, and the process returns to 531, where a further calculation is made to determine whether the tuning range from the new starting frequency (i.e., the computed intermediate frequency point) to the target frequency is too wide. If the tuning range is again too large, the processes of 534 and 535 are repeated to identify a second intermediate tuning point between the first intermediate tuning point and the target frequency. If, at 533, the tuning range is determined to be within acceptable limits, the process continues at 536 where the VCO is controlled to tune to the target frequency via the intermediate points, if any.

[0045] Frequency overshoot is one exemplary interference mechanism which can occur when the oscillator tunes over a long frequency range to a target frequency located

relatively close to an existing frequency. In such an instance, it can be more advantageous to tune to intermediate frequency points between the start frequency and the final target frequency in order to reduce the amount of frequency overshoot. In such an instance, the total tuning range is reduced to two smaller ranges, a first extending between the lowest VCO frequency and the intermediate tuning point, and a second extending between the intermediate tuning point and the target frequency. Further iteratively, the frequency range between the intermediate tuning point and the target frequency, or the lowest VCO frequency and the intermediate point may prove to be also too large, in which case a further intermediate point may be defined therebetween.

[0046] In one embodiment, the determination process in 532 is based upon a computation of an intermediate tuning point  $F_{Int}$  and whether that intermediate tuning point  $F_{Int}$  satisfies a predefined condition. In a specific embodiment, the intermediate tuning point  $F_{Int}$  is calculated as follows:

$$F_{Int} = F_{Target} - \frac{1}{Overshoot} (F_{avoid} - F_{Target} - Mar) \quad \text{eq. (1)}$$

where  $F_{Int}$  is the intermediate frequency (Hz) which is to be determined;  $F_{avoid}$  is the existing or second frequency (Hz);  $F_{Target}$  is the Target VCO frequency (Hz) in the first iteration, and the previously computed intermediate tuning point  $F_{Int}$  in subsequent iterations;  $Mar$  is a predefined margin (Hz); and  $Overshoot$  is a predefined frequency overshoot quantity (dimensionless).

[0047] In the illustrated embodiment of Figs. 5A and 5B, the second frequency parameter  $F_{avoid}$  is the lowest locked frequency which is to be avoided, the parameter  $F_{Target}$  is the desired target frequency, the parameter  $Overshoot$  is a percentage of the last frequency step size to the target frequency, and  $Mar$  is a predefined margin optionally

allocated as a safety margin used to account for process variation, environmental factors and the like, an exemplary embodiment of which is 0.2% - 5% of the VCO tuning range.

[0048] Once the intermediate point  $F_{Int}$  is computed, a determination is made as to whether the intermediate point is higher in frequency than the VCO's lowest starting frequency:

$$F_{Int} > F_{VCO\_Low} \quad \text{eq. (2)}$$

wherein  $F_{VCO\_Low}$  is the lowest VCO start frequency. If the condition is satisfied (i.e., the computed intermediate point is higher than the lowest VCO starting frequency), VCO tuning to the intermediate point is deemed necessary.

[0049] As an example, given the following conditions: *Overshoot* is 50%, the selected VCO tunes from a lowest frequency of 1 GHz to a target frequency of 1.3 GHz, an existing frequency  $F_{avoid}$  resides at 1.6 GHz, and a guard margin of 0.03 GHz is used, eq. (1) yields the first intermediate point as being:

$$F_{Int,1st} = 1.3 - \frac{1}{0.5} (1.6 - 1.3 - 0.03) = 0.76 \text{ GHz.} \quad \text{eq. (3)}$$

[0050] In this case, the first intermediate point  $F_{Int,1st}$  (0.76 GHz)  $< F_{VCO\_Low}$  (1.0 GHz), and therefore tuning to this point is not needed (and is not possible, since the lowest VCO starting frequency is 1.0 GHz). In this case, tuning the VCO over the widest possible tuning range to the target frequency from 1.0 GHz to 1.3 GHz will not result in disturbing the existing frequency located at  $F_{avoid}$ .

[0051] Alternatively, if the existing frequency  $F_{avoid}$  is closer to the target frequency  $F_{Target}$ , e.g., 1.35 GHz, the first intermediate point would be computed as:

$$F_{Int,1st} = 1.3 - \frac{1}{0.5}(1.35 - 1.3 - 0.03) = 1.26 \text{ GHz} \quad \text{eq. (4)}$$

[0052] In this case, the condition  $F_{Int,1st}$  (1.26 GHz)  $> F_{VCO\_Low}$  (1.0 GHz) is true, and therefore the tuning range is needed to be too large at 532.

[0053] In such an instance, the process continues at 534 where the first intermediate point as computed in eq. (4) is defined as a tuning point which the VCO will tune to prior to tuning to the target frequency at 1.3 GHz.

[0054] At 535, the intermediate tuning point computed in eq (4) becomes the target frequency  $F_{Target_1}$ , and a second computation is made at 533 using eq. (1) to determine if a second intermediate point lies above the lowest VCO frequency:

$$F_{Int,2nd} = 1.26 - \frac{1}{0.5}(1.35 - 1.26 - 0.03) = 1.14 \text{ GHz} \quad \text{eq. (5)}$$

[0055] In this instance, the aforementioned condition also holds, as  $F_{Int,2nd}$  (1.14 GHz)  $> F_{VCO\_Low}$  (1.0 GHz), so tuning to the second intermediate point is needed, and a third iteration is performed, whereby the target frequency  $F_{Target_1}$  becomes the second intermediate point 1.14 GHz:

$$F_{Int,3rd} = 1.14 - \frac{1}{0.5}(1.35 - 1.14 - 0.03) = 0.78 \text{ GHz} \quad \text{eq. (6)}$$

[0056] In this instance, the aforementioned condition does not hold, since  $F_{Int,3rd}$  (0.78 GHz)  $< F_{VCO\_Low}$  (1.0 GHz), so tuning to the third intermediate point is not needed.

[0057] Once the intermediate tuning points are determined in this second example, the VCO is controlled to tune (or programmed to later tune) from its VCO start point (wherever between 1.0 GHz and 1.14 GHz that may be) to 1.14 GHz, then from 1.14

GHz to 1.26 GHz, and finally from 1.26 GHz to the final target frequency of 1.30 GHz (process 535). In this way, the frequency offset is reduced to ensure that it does not substantially impact the operation of the existing frequency at 1.35 GHz.

[0058] In a further alternative embodiment, the determination process in 533 as to whether the VCO tuning range is too wide is computed as:

$$|F_{Int} - F_{T\arg et}| * \text{Overshoot} \stackrel{?}{>} |F_{avoid} - F_{T\arg et} - Mar| \quad \text{eq. (7)}$$

[0059] The left side of the inequality represents the bandwidth between the target frequency and the computed intermediate frequency point, and the right side of the equation represents the bandwidth between the target frequency and the existing (avoid) frequency, offset by a predefined margin. Generally, if the left hand side is larger than the right, no intermediate point is deemed necessary. Alternatively, when the left and right hand sides become approximately of the same magnitude or when the right hand side becomes larger than the left hand side, tuning to one or more of the computed intermediate frequency points is deemed necessary.

[0060] The same process may be used to compute intermediate frequency points for process 619, except that eqs. (1) and (2) are expressed as:

$$F_{Int} = F_{T\arg et} + \frac{1}{\text{Overshoot}} (F_{T\arg et} - F_{avoid} - Mar) \quad \text{eq. (8)}$$

$$F_{Int} \stackrel{?}{<} F_{VCO\_High} \quad \text{eq. (9)}$$

$F_{VCO\_High}$  representing the VCO's highest start frequency. When the intermediate frequency point  $F_{Int}$  is located below the  $F_{VCO\_High}$ , VCO tuning to the computed intermediate frequency point is deemed necessary.

[0061] In a particular embodiment, the overshoot parameter ranges from 5 to 80 percent, and in a specific embodiment is 20 percent. The present invention provides a loop filter architecture which reduces frequency overshoot during the tuning process, and an exemplary embodiment of this structure is presented in detail below.

[0062] While the frequency overshoot effect is modeled in terms of a percentage of the tuning range covered, other models may be used as well in the present invention. Furthermore, as an alternative to the tuning processes described in 520-525 in which capacitors are systematically disconnected to obtain a tuning voltage within a predefined range, VCO fine tuning may involve the processes of 531-536.

#### Target Frequency Located Above Highest Locked Frequency

[0063] Fig. 6A illustrates an exemplary embodiment of a tuning process 280 in which the requested target frequency is higher than the highest generated frequency in accordance with the present invention. In a particular embodiment, the process is largely analogous to that described and shown in Fig. 5A, a difference being that the target frequency is approached from the high side of the highest generated frequency without crossing the highest generated frequency.

[0064] The process begins at 602 whereby one or more oscillators (e.g., a VCO) having a maximum frequency higher than the highest generated frequency are identified. At 604, one of the identified VCOs is selected for tuning to the target frequency. The selection process may involve various factors, including which of the selected VCOs, when tuned to the target frequency, will be closest to, or within the linear-most tuning range, and which selected VCO can be activated at a frequency which is furthest from the locked frequency.

[0065] At 606, the selected VCO is set to begin tuning from a start frequency in the high end of its tuning range. In a particular embodiment, the selected VCO is supplied its corresponding coarse word CW\_fmax, setting the tuning frequency to its maximum frequency point. In an alternative embodiment, the VCO is configured to begin tuning from another point in the high end of its frequency range. At 610, the selected VCO is activated and permitted to tune and lock to the requested target frequency.

[0066] Fig. 6B illustrates an exemplary embodiment of a process 610 in which the selected oscillator is activated and tuned to a target frequency higher than the highest generated frequency in accordance with the present invention. The process is largely analogous to that described and shown in Fig. 5B, a difference being that tuning is performed from the high side of the highest generated/locked frequency.

[0067] Initially at 611, the selected VCO is set to its highest operating frequency point by supplying the VCO with the CW\_fmax coarse word. At 612, the fine tune setting of the VCO is set to its highest frequency setting, in a particular embodiment by disconnecting all of the fine tuning capacitors. At 613, the PLL divider ratio N is set to tune to the target frequency, and at 614 the tuning voltage  $V_{Tune}$  of the VCO is measured.

[0068] At 615, a determination is made as to whether the tuning voltage is measured lower than the VCO's minimum voltage,  $V_1$ . If it is, the VCO is not in the correct coarse tuning range, as the present coarse tuning range is too high in frequency. In this case, the processes of 616-619 are performed by which the loop filter is pre-charged at to a predefined voltage (the highest tuning voltage  $V_2$  in a particular embodiment), a coarse word corresponding to the next lower frequency range selected, the loop filter released from the pre-charge voltage, and the VCO activated with the new coarse word and attempts to tune to lock. An exemplary circuit for pre-charging the loop filter is described below in Fig 11.

[0069] If the tuning voltage  $V_{Tune}$  is higher than the VCO's minimum voltage  $V_1$ , the VCO is within a tunable coarse range, and the process continues at 620-625 in which a fine tuning process is performed. In a particular embodiment illustrated, a first determination is made at 620 as to whether the tuning voltage  $V_{Tune}$  is within a predefined range, for example 1.25V to 1.75V, where 1.5V represents the VCO midband frequency point. The predefined range may be any desired range, which, for example represents the most linear range of the oscillator.

[0070] If at 620, the tuning voltage  $V_{Tune}$  is not within the predefined range, the VCO is out of the correct fine tuning range, and is too high in frequency (as the fine tuning range was set to the highest tuning range in 612). In this instance, the processes of 621-625 are performed, whereby the loop filter is pre-charged to a predefined voltage (e.g., the highest tuning voltage,  $V_2$ ), a fine tuning word corresponding to the next lower frequency range selected (which is operable to connect one or more of the fine tuning capacitors), the loop filter released from the pre-charge voltage, and the VCO activated with the new fine word and attempts to tune to lock. The tuning voltage is again measured to determine if it is within the predefined range, and if not, the processes of 620-625 are repeated. Once the tuning voltage reaches a value within the predefined range, the tuning process concludes.

[0071] The tuning process 619 of identifying and tuning to intermediate points is largely analogous to that described and shown in Fig. 5C. In one embodiment of the present invention, the determination as to whether a tuning range is too large is performed using the processes 531-536, and eqs. (8) and (9) outlined therefor.

[0072] For example, given the following condition: *Overshoot* is 50%, the VCO has a maximum start frequency  $F_{VCO\_High}$  of 1.60 GHz, the target frequency  $F_{Target}$  is 1.3 GHz, an existing frequency  $F_{avoid}$  resides at 1.25 GHz, and a guard margin *Mar* of 0.03 GHz, eq. (6) yields a first intermediate tuning point  $F_{Int}$  at:

$$F_{Int,1st} = 1.3 + \frac{1}{0.5}(1.3 - 1.25 - 0.03) = 1.34 \text{ GHz} \quad \text{eq. (10)}$$

[0073] As the condition  $F_{Int}$  (1.34 GHz)  $< F_{VCO\_High}$  (1.6 GHz) of eq. (14) is met, the tuning range is deemed to large, and tuning to the intermediate point is needed prior to tuning to the target frequency.

[0074] A second intermediate tuning point is computed in which  $F_{Target}$  (previously 1.3 GHz) becomes the previously-computed intermediate tuning point, 1.34 GHz:

$$F_{Int,2nd} = 1.34 + \frac{1}{0.5}(1.34 - 1.25 - 0.03) = 1.46 \text{ GHz} \quad \text{eq. (11)}$$

[0075] The iteration provides an intermediate tuning point at 1.46 GHz, which is below the highest tuning frequency of the VCO (1.6 GHz). Accordingly the condition in eq. (14) is met, and tuning to the second intermediate point is necessary. In the same manner, a third intermediate tuning point is further calculated:

$$F_{Int,3rd} = 1.46 + \frac{1}{0.5}(1.46 - 1.25 - 0.03) = 1.82 \text{ GHz} \quad \text{eq. (12)}$$

[0076] In this case, the third intermediate point is located above the target frequency of 1.6 GHz, and accordingly tuning to it is not needed.

[0077] As above, the overshoot parameter may comprise a range of values, an exemplary embodiment being from 5 to 80 percent, and in a specific embodiment 20 percent. Further, other linear or non-linear computations may be used to model frequency overshoot, as well as other effects. In addition, the fine tuning processes described in 620-625 in which capacitors are systematically connected to obtain a tuning voltage within a predefined range, may alternatively involve the tuning processes of 531-535.

Target Frequency Located Between Existing Locked Frequencies

[0078] Fig. 7 illustrates an exemplary embodiment of a tuning process 290 in which the requested target frequency is located between two existing frequencies  $F_{High}$  and  $F_{Low}$  in accordance with the present invention. The process begins at 705, whereby the frequencies  $F_{High}$  and  $F_{Low}$  located higher and lower than the requested target frequency are identified. In a particular embodiment, this process is performed by accessing the already\_generated data structure 370 illustrated in Fig. 3C.

[0079] At 710, a determination is made as to whether the separation between  $F_{High}$  and  $F_{Low}$  is greater than a predefined threshold. In a particular embodiment, the predefined threshold represents the tuning range, plus a predefined margin over which the selected VCO can tune whereby the accompanying frequency overshoot effect would not affect the existing  $F_{High}$  and  $F_{Low}$  frequencies. In a particular embodiment, the predefined margin includes interpolation error (or a factor thereof) that is introduced in the tuning process when the VCO attempts to tune to the target frequency using coarse and/or fine tuning words, as that tuning process is further defined below.

[0080] If, at 710, a determination is made that the separation between  $F_{High}$  and  $F_{Low}$  is greater than the predefined threshold, an oscillator is selected at 715. The selection process may involve various factors, including which of the selected VCOs, when tuned to the target frequency, will be closest to, or within the linear-most tuning range. If the high and low frequencies  $F_{High}$  and  $F_{Low}$  are spaced apart less than the predefined threshold, the process continues at 750, which is further illustrated in Fig. 8A.

[0081] At 720, the median point between  $F_{High}$  and  $F_{Low}$  is determined at 720. In a particular embodiment, this process is performed using the already\_generated data structure 370 shown in Fig. 3C. At 725, a determination is made as to whether the median frequency point is above or below the midband frequency point of the selected VCO. If the median frequency point is located higher, a start frequency for the selected VCO is computed as an interpolated value between the high and midband frequencies (730). Alternatively, if the median frequency is located lower than the midband

frequency of the selected VCO, the start frequency for the selected VCO is set as an interpolated value between the midband and low frequency points (735). In this manner, the start frequency is located closer to the median frequency point, and thus initial activation of the VCO is less likely to disturb either of the existing high or low frequencies  $F_{High}$  and  $F_{Low}$ .

[0082] The start frequency is computed as described above, and the corresponding coarse word supplied to the selected VCO. The divider ratio is set to tune to the target frequency, and one half of the fine tuning capacitors is switched in. The selected VCO is then activated and begins tuning from the start frequency toward the target frequency (740). The VCO is permitted sufficient time to achieve lock, and subsequently the tuning voltage  $V_{Tune}$  is measured, and a determination is made at 745 as to whether  $V_{Tune}$  is: (i) at or near the VCO's lowest tuning voltage  $V_1$ , (ii) at or near to the VCO's highest tuning voltage  $V_2$ , or (iii) generally in the center of voltage range between  $V_1$  and  $V_2$ . If  $V_{Tune}$  is measured as being at or near to the lowest tuning voltage  $V_1$ , the VCO may be operating in too high of a frequency range. In such an instance, the coarse and fine tuning processes of 506 and 510 illustrated in Figs. 5A and 5B are executed to search for a better VCO tuning range. If  $V_{Tune}$  is measured as being at or near to the highest tuning voltage  $V_2$ , the VCO may be in too low of a frequency range. In such an instance, the coarse and fine tuning processes of 606 and 610 illustrated in Figs. 6A and 6B are executed to search for a better VCO tuning range. The tuning processes of both 260 and 280 may include the operations of computing and tuning to intermediate frequency points in the direction toward the target frequency. Alternatively, if the VCO achieves lock to the target frequency, and  $V_{Tune}$  is measured between the  $V_1$  and  $V_2$ , VCO operation is determined to be within acceptable limits and the tuning process concludes. While  $V_1$  and  $V_2$  are described above in terms of the VCO's minimum and maximum tuning voltages, e.g., 0.5V-3.5V, they may equally correspond to a more narrow voltage range which more tightly defines the VCO's optimal region of operation, e.g., 1.25V-1.75V. In the latter embodiment, a tuning voltage less than 1.25V would result in a tuning operation as defined by 260 in Fig. 5A, and similarly for a tuning voltage greater than 1.75V resulting in the tuning operation defined by 280 in Fig. 6A.

Target Frequency Located Between Closely Spaced Frequencies

[0083] Fig. 8A illustrates an exemplary embodiment of a tuning selection process 750 in which the requested target frequency is located between two closely spaced existing frequencies  $F_{High}$  and  $F_{Low}$  in accordance with the present invention. The term “closely spaced” refers to the separation between the existing frequencies as being insufficient to permit a oscillator, such as a VCO, from tuning over a large portion of its tuning range between the two frequencies  $F_{High}$  and  $F_{Low}$  without disturbing one or both the frequencies. In such an instance, effects created by the VCO’s tuning operations (e.g., frequency overshoot) are likely to impact the operation of one or both of the existing frequencies due to their proximity in frequency to the oscillator. As noted in the exemplary embodiment above, the spacing may be on the order of 175 MHz, although the frequency spacing may be narrower or wider than this in other embodiments, for example, frequency spacings less than or equal to 10 MHz, 20 MHz, 50 MHz, 75 MHz, 100 MHz, 150 MHz, 200 MHz, 250 MHz, 500 MHz or wider frequency spacings.

[0084] The exemplary process begins at 805, where one or more VCOs having either (i) a maximum frequency higher than  $F_{High}$ , or (ii) a minimum frequency lower than  $F_{Low}$  are identified. This process may be performed by accessing the `vco_freq` data structure 360 shown in Fig. 3B. Subsequently at 810, one of the identified VCOs is selected, the selected VCO preferably having the furthest offset, either as measured from its minimum frequency to  $F_{Low}$ , or from its maximum frequency to  $F_{High}$ . In this manner, the VCO having the largest frequency offset from either  $F_{High}$  or  $F_{Low}$  is selected.

[0085] The process continues at 825, whereby a determination is made as to whether a VCO having a frequency lower than  $F_{Low}$  is selected, or whether a VCO having a frequency higher than  $F_{High}$  is selected. As noted above, the VCO which provides the greatest offset from its respective neighboring frequency  $F_{Low}$  or  $F_{High}$  is the VCO preferably chosen. If a VCO neighboring  $F_{Low}$  is selected, the tuning procedure of 510 illustrated in Fig. 5B is performed to tune to an approach frequency  $F_0$  which is proximate to, but does not cross the existing frequency  $F_{Low}$ . The computation and

intermediate tuning process 519 illustrated in Fig. 5C may be employed in the coarse or fine tuning procedures included therein.

[0086] The approach frequency  $F_0$  is located a predefined distance away (below) from the existing frequency  $F_{Low}$ , the predefined distance operable to place the approach frequency close to the existing frequency so as to provide a relative small frequency jump from this point to a close approximation of the target frequency located between existing frequencies  $F_{Low}$  and  $F_{High}$ . However, the approach frequency  $F_0$  is preferably not located too close to the existing frequency  $F_{Low}$ , as a large number of intermediate frequencies would be needed to tune to this point from the VCO start frequency. Accordingly, a balancing of the two requirements will determine the most appropriate offset for the approach frequency  $F_0$ , and in an exemplary embodiment, an offset of between 1-10 percent of the VCO tuning range is used. In the illustrated embodiment in which the VCO tuning range is approximately 200 MHz, the approach frequency  $F_0$  is defined at 2.5 MHZ below the existing frequency  $F_{Low}$ .

[0087] In a particular embodiment of this process when the selected VCO has a minimum frequency lower than  $F_{Low}$ , tuning at the approach frequency  $F_0$  is locked using a tuning voltage near the low end of the  $V_{Tune}$  range, e.g., 0.5 V. This establishes a condition, such that when the VCO tunes higher to the target frequency, the VCO will be in/near its linear most region (e.g., 1.5 V).

[0088] Alternatively, if a VCO neighboring  $F_{High}$  is selected, the tuning procedure of 610 illustrated in Fig. 6B is performed to tune to an approach frequency  $F_0$  which is proximate to, but does not cross the existing frequency  $F_{High}$ . In a particular embodiment of this process, tuning at the approach frequency  $F_0$  is locked using a tuning voltage near the high end of the  $V_{Tune}$  range, e.g., 2.5 V. This establishes a condition such that when the VCO tunes lower to the target frequency, the VCO will be in/near its linear most region (e.g., 1.5 V). The intermediate tuning process 619 illustrated in Fig. 5C may be employed in the coarse or fine tuning procedures included therein.

[0089] Next at 835, a determination is made as to whether the requested target frequency, located between the existing frequencies,  $F_{Low}$  and  $F_{High}$ , is within a predefined range of the approach frequency  $F_0$ . The predefined range within which the approach and target frequencies lie is based upon several factors, including the linear bandwidth of the VCO tuning range. In one embodiment, the predefined range is generally between 1-10% of the VCO tuning range, and in a particular exemplary embodiment is 10 MHz for a VCO having a tuning range of approximately 200 MHz.

[0090] If the requested target frequency is within the predefined range of the approach frequency  $F_0$ , process 840 is performed, whereby, the VCO is closed loop locked from the approach frequency  $F_0$ , across the existing frequency (either  $F_{Low}$  or  $F_{High}$ ) to the target frequency. In a closed loop VCO tuning operation, the VCO is programmed with appropriate coarse and fine tuning words for tuning to a frequency according to the PLL dynamics.

[0091] As noted above, the tuning process may involve tuning to the approach frequency  $F_0$  at a  $V_{Tune}$  voltage which is on the low or high end of the  $V_{Tune}$  range, thus resulting in the VCO being tuned nearer or within its linear most  $V_{Tune}$  range once tuned to the target frequency.

[0092] Once the VCO has been tuned to what is believed the target frequency, its tuning voltage is measured. If the tuning voltage is not within an acceptable range (e.g.,  $1.25 \text{ V} < V_{Tune} < 1.75 \text{ V}$ ) when tuned to the target frequency, then the VCO is programmed with a new coarse and/or fine tune word, and activated to perform another closed locked loop tuning operation. The process repeats until the aforementioned conditions are met. In an alternative embodiment, the fine tuning process is performed in an open loop operation in which the VCO is permitted to freely tune between a starting and locked frequency if the frequency excursion in such an operation is not expected to be too great that resulting frequency overshoot would affect one or more neighboring frequencies.

[0093] If, at 835, the target frequency is located further than the predefined range from the approach frequency  $F_0$ , the process continues at 845 where a determination is made as to whether a low or a high  $K_v$  tuning procedure is to be made (processes 850 or 860). As known in the art, the parameter  $K_v$  refers to VCO gain or tuning sensitivity, and describes the frequency shift per volt applied. VCOs employing high  $K_v$  exhibit wider tuning ranges and greater linearity per Hz over their ranges, low  $K_v$  VCOs exhibit lower sensitivity to  $V_{Tune}$  noise. Accordingly, PLL systems of either type may be used, depending the application and design requirements, and the present invention further presents a VCO tuning regime for each. While high and low  $K_v$  values are relative, generally high  $K_v$  refers to an oscillator sensitivity on the order of 25-70 MHz/V and above, while low  $K_v$  VCOs are generally in the range of 10-30 MHz/V.

[0094] Fig. 8B illustrates an exemplary embodiment of process 850 for tuning a low  $K_v$  VCO to the requested target frequency residing between two closely spaced existing frequencies  $F_{Low}$  or  $F_{High}$  in accordance with the present invention. Initially at 851, the frequency of the VCO, which has been tuned at the approach frequency  $F_0$  in process 825 or 830 previously in Fig. 8B, is varied until the tuning voltage  $V_{Tune}$  reaches a predefined value  $V_{T1}$ , the VCO being tune to frequency  $F_1$  at this point. The coarse and fine tuning words used to tune to  $F_1$  (CW1 and FW1) are then recorded.

[0095] In a particular embodiment, the value  $V_{T1}$  is a tuning voltage which is at/near the center of the VCO's linear most tuning range. In the illustrated embodiment described herein, this voltage is 1.5V, although those skilled in the art will appreciate that another voltage may be used as well. The tuning voltage is varied so as to move to  $F_1$  without crossing the proximate existing frequency (either  $F_{Low}$  or  $F_{High}$ ). If it is determined that adjusting the VCO's tuning voltage towards  $V_{T1}$  results in moving the VCO tuned frequency closer to the existing proximate frequency than  $F_0$ , a new coarse and/or fine tuning word is selected and used to tune the VCO further away from the approach frequency  $F_0$  until the voltage  $V_{T1}$  is measured at a frequency  $F_1$  which is no closer to the existing proximate frequency than the approach frequency  $F_0$ .

[0096] At 852, a second VCO coarse tuning word (CW2) is supplied to the VCO which tunes the VCO frequency even further away from the proximate existing frequency, and a frequency is found where the tuning voltage is substantially  $V_{T1}$ . The differences in tuning frequencies  $F_1$  and  $F_2$  and corresponding coarse words CW1 and CW2 are used to generate a quantity  $\Delta F_{coarse}$  which describes the frequency shift per coarse word at the voltage  $V_{T1}$ . For example, following the exemplary embodiment in which the approach frequency  $F_0$  is proximate to and below the lowest existing frequency  $F_{Low}$ , a frequency  $F_1$  is tuned at substantially 1.5V further below  $F_0$  in accordance with process 851. Subsequently, a new coarse word, e.g., CW2 = CW1-2 (two coarse words lower than the first coarse word, CW1), is used to tune the VCO to a frequency  $F_2$ , and a ratio  $\Delta F_{coarse}$  is derived from  $(F_1-F_2)/(CW1-CW2)$  which describes the frequency shift per coarse tuning word. As readily apparent, a different coarse word offset may be used in alternative embodiments as well.

[0097] A similar operation is performed at 853 to obtain a ratio  $\Delta F_{fine}$  to describe the VCO's frequency shift per fine tuning word. In an exemplary embodiment of this process, the VCO is fine tuned from  $F_2$  to a new frequency,  $F_3$ , where the tuning voltage reaches substantially  $V_{T1}$ , and the corresponding fine tuning word FW3 is recorded. A ratio  $\Delta F_{fine}$  is derived from  $(F_2-F_3)/(FW2-FW3)$  which describes the frequency shift per fine tuning word.

[0098] With knowledge of the frequency difference between  $F_1$  and the requested target frequency, the quantities  $\Delta F_{coarse}$  and  $\Delta F_{fine}$  can be applied to CW1 and FW1 to compute the corresponding coarse and fine word increments needed therefrom to tune the VCO substantially to the requested target frequency. In a particular embodiment, the coarse word increment added to CW1 to tune from  $F_1$  to the target frequency is computed as the truncated integer value of the quantity:

$$\Delta_{CW} = \left[ \frac{F_{Target} - F_1}{\Delta F_{Coarse}} \right]_{Integer, Truncated} \quad \text{eq. (13)}$$

Thus, for example, if the coarse word increment is 2.9, the output value of eq. (13) would be 2.0.

Further, the fine word increment added to FW1 is computed as the rounded integer value of the quantity:

$$\Delta_{FW} = \left[ \frac{F_{Target} - F_1 - (\Delta_{CW} * \Delta F_{Coarse})}{\Delta F_{fine}} \right]_{Integer, Rounded} \quad \text{eq. (14)}$$

Thus, for example, if the coarse word increment is 2.9, the output value of eq. (14) would be 3.0. The numerator of the quantity represents the residual coarse word.

[0099] In a particular embodiment, the computations are performed as a part of process 854, in which the VCO is re-tuned to  $F_1$ , the new coarse and fine tuning words corresponding to the target frequency computed as shown in eqs. (13) and (14), and the VCO closed looped tuned to substantially the target frequency using the computed coarse and fine tuning coarse words.

[0100] Subsequent to close loop tuning to substantially the target frequency, the VCO tuning voltage is optionally measured to determine if it lies within an acceptable range of  $V_{T1}$ . Variance of the VCO's operation from the linear approximation of the above coarse and fine words may result in the actual VCO frequency being offset from the desired target frequency. In this case, one or more fine tuning capacitors may be connected or disconnected (to achieve a lower or higher tuning frequency, respectively), and the tuning voltage and locked frequency re-measured to determine if each lies within an acceptable range. In a particular embodiment, the fine tuning process is performed as an open loop process in which the VCO is allowed to vary between frequencies to achieve lock, as the fine tuning operation occurs over a small frequency range which may not produce a significant frequency overshoot effect to disturb neighboring frequencies. However, if

such a condition is found or would be expected, the fine tuning procedure could be carried out as a closed loop lock operation in the same manner as the coarse tuning.

[0101] Fig. 8C illustrates an exemplary embodiment of process 860 for tuning a high  $K_v$  VCO to the requested target frequency residing between two closely spaced existing frequencies  $F_{Low}$  or  $F_{High}$  in accordance with the present invention. The process begins at 861, whereby the selected VCO is provided coarse and fine tuning words for performing a closed loop lock to the target frequency. As noted above, the closed loop lock tuning operation across the pre-existing frequency provides the least disturbance to the existing frequency. The process by which the coarse and fine tuning words corresponding to the target frequency are selected may be as described in processes 851-855 in Fig. 8C.

[0102] At 862, a determination is made as to whether the VCO tuning voltage is within an acceptable range, 1.25V to 1.75V in an exemplary embodiment. If not, a new frequency  $F_4$  within the present VCO tuning band (i.e., same CW) is tuned to (process 863). In an exemplary embodiment,  $F_4$  is chosen at predefined offset from either  $F_{Low}$  or  $F_{High}$ , an exemplary offset being in the range from 500 KHz- 5 MHz.

[0103] At 864, a CW and frequency (divider ratio Npll) for tuning to the target frequency is supplied to the VCO, and the VCO performs a closed loop jump from  $F_4$  to the target frequency using the new CW. In a particular embodiment of this process, the coarse and fine tuning words are latched substantially concurrently with the value of the dividing ratio Npll, in a closed loop environment. At 865, the VCO tuning voltage is measured to determine if it is within an acceptable ranges, e.g.,  $1.25 \text{ V} < V_{Tune} < 1.75 \text{ V}$ . If the condition is not met, the process returns to 863, in which the VCO is close loop tuned back to frequency  $F_4$  using intermediate frequency tuning process. The process repeats as shown until the conditions are met, at which point the process concludes.

## II. Exemplary System Components

### System Microcontroller

[0104] Fig. 9 illustrates a block diagram of an exemplary system microcontroller operable to control the multiple frequency source system in accordance with the present invention. The microcontroller 900 includes a microprocessor core 902 operable to run one or more programs to execute the tuning operations and processes described herein, a program memory 904 (typically non-volatile or programmable ROM) operable to store, for example, the data structures of 360 and 370 shown in Figs. 3A and 3B and programs for performing the tuning procedures as set forth herein, and a data memory 906 (typically RAM) operable to store, for example, the data values of data structures 360 and 370.

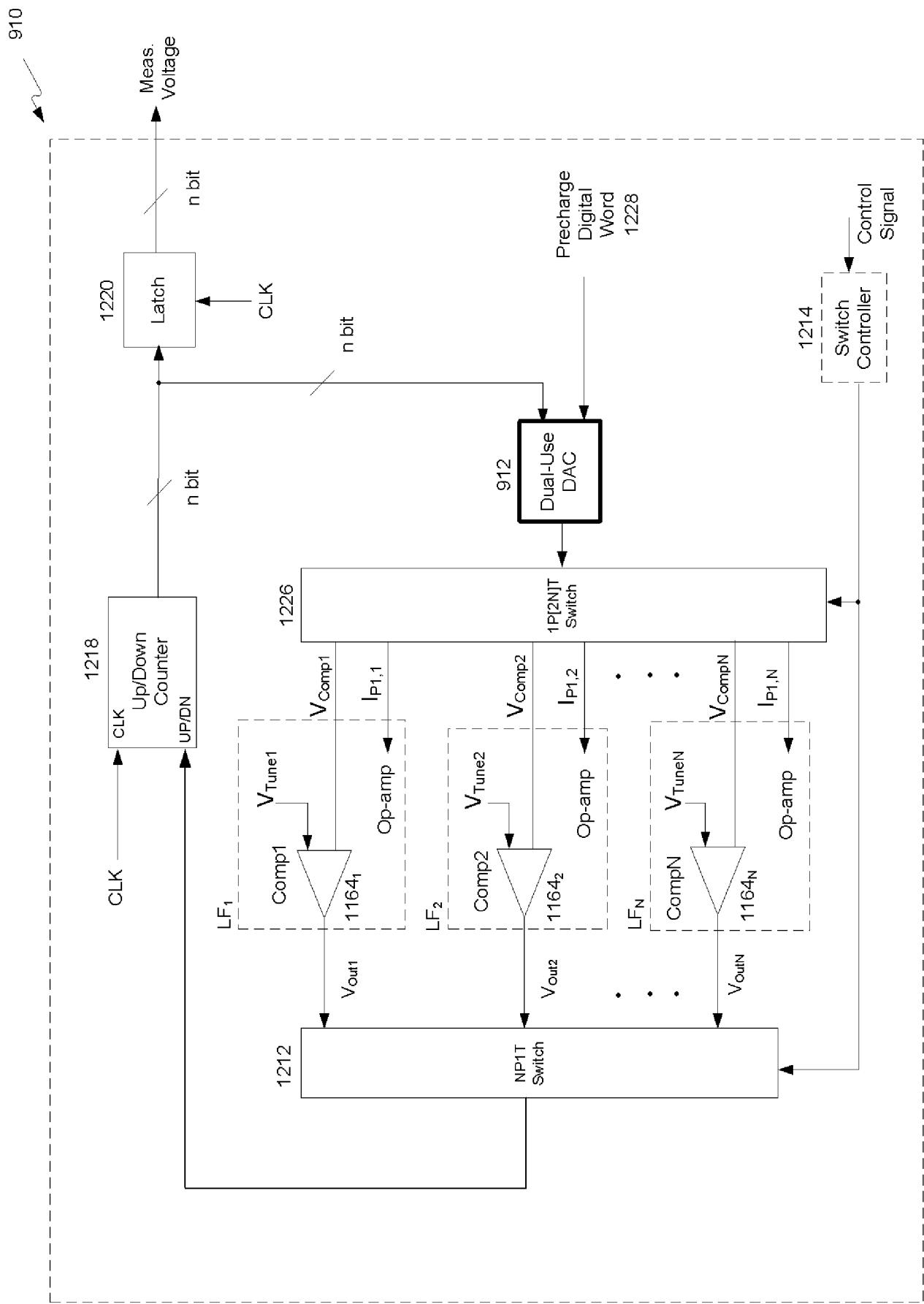

[0105] The microcontroller 900 further includes a system clock and power management unit 908 for controlling the system clock and power consumption, an analog-to-digital converter unit 910 for providing digital conversion of supplied analog signals, the ADC 910 further including an embedded digital-to-analog converter (DAC) unit 912 used to pre-charge the loop filter to a desired level, further described below, and an input/output module 914 for receiving and transmitting data, power, control, and other information and signals to the system of the present invention via an n-bit I/O bus line 916. The microcontroller itself includes an internal n-bit bus line which interconnects the microprocessor core 902, program and data memory units 904 and 906, the clock and power management module 908, the ADC 910 and DAC 912, and the I/O unit 914. In a specific embodiment of the invention further described below, the DAC 912 is operable both as a part of the ADC unit 910, and as a separate DAC unit, the later functionality being provided by a DAC bus line 912a coupled to the internal microcontroller bus 918.

[0106] The microcontroller 900 may be fabricated integrally with one or more of the frequency sources, or separately therefrom, for example as an application specific integrated circuit (ASIC). Still further alternatively, one or more functions of the

microcontroller 900 may be integrated within or proximate to one or more frequency sources, the other functions residing on a remotely-accessible circuit or integrated circuit. Those skilled in the art will appreciate that the illustrated microcontroller is only exemplary and can be modified in a variety of ways to provide the desired system functionality and control. Alternatively, the microcontroller 900 may be omitted in those designs in which the functionality and control of the multiple frequency source system is provided using other means.

#### Voltage Controlled Oscillator

[0107] Fig. 10 illustrates an exemplary embodiment of an oscillator 124 in accordance with the present invention. The oscillator, illustrated as a VCO, includes oscillator transistors 1002 and 1004 arranged in a differential configuration, a tank circuit 1010, and a bank of fine tune capacitors 1030. In one embodiment, each of these components are monolithically fabricated in a bipolar-complementary metal oxide semiconductor (Bi-CMOS) process, although those of skill in the art will appreciate that the circuit may be formed in other materials and processes (e.g., CMOS, SiGe, GaAs), as well as in monolithic, hybrid, or discrete form. Furthermore, the oscillator 124 may be integrated with one or more of the phase-frequency detector 121, the charge pump circuit 122, the loop filter 123, the divide-by-N counter 126, and/or the sigma delta modulator 127.

[0108] Oscillator transistors 1002 and 1004 provide negative resistance to compensate for the losses of the tank circuit 1010, thereby allowing the VCO 114 to oscillate. In the illustrated embodiment, oscillator transistors 1002 and 1004 are p-type metal oxide semiconductor (PMOS) transistors having their respective source terminals coupled together and to the power supply through supply resistor R1. Drain terminals are coupled to respective ports of the tank circuit, the gate terminals of opposing transistors coupled to the other's drain terminal. While oscillator transistors 1002 and 1004 are illustrated as PMOS transistors, other FET transistor embodiments such as NMOS, as well as bipolar transistor architectures may be used in alternative embodiments under the present invention.

[0109] VCO tank circuit 1010 includes varactor diodes D1 and D2, capacitors C1 and C2, and inductor L1, operable to provide the desired resonant frequency over a range of frequencies as assisted by the variable capacitor of the varactor diodes D1 and D2. A tuning voltage  $V_{Tune}$  is supplied to the varactor diodes D1 and D2 to set the capacitance of the tank circuit, thereby setting the resonant frequency of the oscillator 124. While the illustrated embodiment illustrates a variable reactance tank circuit commonly used in voltage controlled oscillator circuits, the oscillator 124 is not limited thereto, and a tank circuit having a fixed resonant frequency may be used in an alternative embodiment of the invention. Moreover, the invention is not limited to any particular tank circuit configuration, as any resonant circuit, active or passive, parallel or series-coupled, can be used with the present invention. In embodiments in which n-type FETs (field effect transistors) or BJTs (bipolar junction transistors) are employed,  $V_{DD}$  and ground potentials are reversed, e.g., inductor L1 is coupled to  $V_{DD}$  and resistor R1 coupled to ground.