(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6501514号

(P6501514)

(45) 発行日 平成31年4月17日(2019.4.17)

(24) 登録日 平成31年3月29日(2019.3.29)

(51) Int.Cl.

F 1

H01L 29/786 (2006.01)

H01L 29/78 616T

H01L 21/336 (2006.01)

H01L 29/78 612C

G02F 1/1368 (2006.01)

H01L 29/78 612D

G09F 9/30 (2006.01)

H01L 29/78 616K

H01L 29/78 618B

請求項の数 10 (全 16 頁) 最終頁に続く

(21) 出願番号

特願2014-260230 (P2014-260230)

(22) 出願日

平成26年12月24日(2014.12.24)

(65) 公開番号

特開2016-122683 (P2016-122683A)

(43) 公開日

平成28年7月7日(2016.7.7)

審査請求日

平成29年12月12日(2017.12.12)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100088672

弁理士 吉竹 英俊

(74) 代理人 100088845

弁理士 有田 貴弘

(72) 発明者 今村 謙

熊本県合志市御代志997番地 メルコ・

ディスプレイ・テクノロジー株式会社内

(72) 発明者 山吉 一司

熊本県合志市御代志997番地 メルコ・

ディスプレイ・テクノロジー株式会社内

最終頁に続く

(54) 【発明の名称】薄膜トランジスタ基板およびその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に形成された薄膜トランジスタと、

前記薄膜トランジスタのゲート電極に接続されたゲート配線と、

前記薄膜トランジスタのドレイン電極に接続された画素電極と、

前記薄膜トランジスタのソース電極に接続されたソース配線と、

を備え、

前記薄膜トランジスタは、

前記基板上に形成された前記ゲート電極と、

前記ゲート電極を覆うように形成された第1の絶縁膜と、

前記第1の絶縁膜上の前記ゲート電極と重なる位置に形成された酸化物半導体から成る

チャネル層と、

前記チャネル層上に形成された第2の絶縁膜と、

前記第2の絶縁膜を覆うように形成された第3の絶縁膜と、

前記第3の絶縁膜上に形成されたソース電極、ドレイン電極とを備え、

前記ソース電極および前記ドレイン電極は、それぞれ前記第2の絶縁膜および前記第3

の絶縁膜を貫通するコンタクトホールを通して、前記チャネル層に接続しており、

前記ソース配線の下の全体には、前記チャネル層と同層において当該チャネル層と離間

して設けられた酸化物半導体膜、および、前記第2の絶縁膜と同層において当該第2の絶

縁膜と離間して設けられた絶縁膜が配置されている

10

20

ことを特徴とする薄膜トランジスタ基板。

**【請求項 2】**

前記第 2 の絶縁膜と同層の前記絶縁膜は、前記ソース配線と接している

請求項 1 に記載の薄膜トランジスタ基板。

**【請求項 3】**

前記ソース電極および前記ドレイン電極は、前記画素電極と同層の透明導電膜を用いて形成されている

請求項 1 または請求項 2 に記載の薄膜トランジスタ基板。

**【請求項 4】**

前記ソース配線は、前記第 2 の絶縁膜と同層の絶縁膜上に形成されており、

10

前記ソース電極は、前記第 3 の絶縁膜を貫通するコンタクトホールを通して、前記ソース配線に接続している

請求項 1 から請求項 3 のいずれか一項に記載の薄膜トランジスタ基板。

**【請求項 5】**

前記ソース配線の幅は、その下の前記酸化物半導体膜および前記第 2 の絶縁膜と同層の絶縁膜の幅よりも狭い

請求項 1 から請求項 4 のいずれか一項に記載の薄膜トランジスタ基板。

**【請求項 6】**

前記ゲート電極と同層の導電膜で形成された共通配線と、

20

前記画素電極を覆うように形成された第 4 の絶縁膜と、

前記第 4 の絶縁膜上の前記画素電極と重なる位置に形成された共通電極とを備え、

前記共通電極は、前記第 1 の絶縁膜および前記第 3 の絶縁膜および第 4 の絶縁膜を貫通するコンタクトホールを通して前記共通配線に接続している

請求項 1 から請求項 5 のいずれか一項に記載の薄膜トランジスタ基板。

**【請求項 7】**

薄膜トランジスタ基板の製造方法であって、

第 1 の導電膜より形成されたゲート電極を覆うように第 1 の絶縁膜からなるゲート絶縁膜が形成された基板を用意する工程と、

前記基板の前記ゲート絶縁膜上に、半導体膜、第 2 の絶縁膜および第 2 の導電膜をこの順に積層した積層膜を形成する工程と、

30

薄膜トランジスタのチャネル層の形成領域である第 1 領域およびソース配線の形成領域である第 2 領域の前記積層膜の上に、フォトレジストパターンを形成する工程と、

前記フォトレジストパターンにより前記半導体膜をパターニングし、前記ゲート絶縁膜上に前記チャネル層を形成するとともに、前記第 2 領域の前記積層膜をパターニングし、前記第 2 の導電膜よりなる前記ソース配線と、前記ソース配線の下に配置され前記第 2 の絶縁膜および前記半導体膜よりなる積層パターンとを形成する工程と、

前記チャネル層に接続されるソース電極およびドレイン電極と、前記ドレイン電極に接続される画素電極とを形成する工程と、

を備える

ことを特徴とする薄膜トランジスタ基板の製造方法。

40

**【請求項 8】**

前記フォトレジストパターンを形成する工程は、

ハーフ露光を用いて、前記第 2 領域の方が前記第 1 領域よりも厚いフォトレジストパターンを形成する工程、

を含み、

前記チャネル層、前記ソース配線および前記積層パターンを形成する工程は、

前記フォトレジストパターンをマスクにするエッチングにより、前記積層膜をパターニングする工程と、

前記フォトレジストパターンを薄膜化して前記第 1 領域の前記フォトレジストパターンを除去し、前記第 2 領域に残存する前記フォトレジストパターンをマスクにするエッチ

50

グにより前記第2の導電膜をパターニングして前記ソース配線を形成する工程と、

を含む、

請求項7に記載の薄膜トランジスタ基板の製造方法。

【請求項9】

前記ゲート電極の形成と同時に、基板上に前記第1の導電膜を用いて共通配線を形成する工程と、

前記ソース電極および前記ドレイン電極の形成と同時に前記画素電極を形成する工程と、

前記画素電極を覆うように第3の絶縁膜を形成する工程と、

前記第1の絶縁膜および前記第3の絶縁膜を貫通して前記共通配線に達するコンタクトホールを形成する工程と、

前記第3の絶縁膜の上に、前記コンタクトホールを通して前記共通配線に接続し、スリットを有する共通電極を、前記画素電極と重なる位置に形成する工程と、

をさらに備える

請求項7または請求項8に記載の薄膜トランジスタ基板の製造方法。

【請求項10】

前記画素電極および前記共通電極は、透明導電膜である

請求項9に記載の薄膜トランジスタ基板の製造方法。

【発明の詳細な説明】

【技術分野】

20

【0001】

本発明は、酸化物半導体を用いた薄膜トランジスタを備えた薄膜トランジスタ基板、並びに薄膜トランジスタ基板の製造方法に関するものである。

【背景技術】

【0002】

薄膜トランジスタ(Thin Film Transistor; 以下「TFT」)をスイッチング素子として用いたTFTアクティブマトリクス基板(薄膜トランジスタ基板; 以下「TFT基板」)は、例えば液晶を利用した表示装置(液晶表示装置)等の電気光学装置に利用される。TFT等の半導体装置は、低消費電力で薄型という特徴があり、この特徴を活かして、CRT(Cathode Ray Tube)に変わるフラットパネルディスプレイへの応用が盛んになされている。

30

【0003】

液晶表示装置(LCD)用の電気光学素子には、単純マトリックス型LCDと、TFTをスイッチング素子として用いるTFT-LCDがある。特にTFT-LCDは、携帯性および表示品位の点でCRTや単純マトリックス型LCDより優れており、ノート型パソコンやテレビジョンなどのディスプレイ製品に広く実用化されている。

【0004】

一般に、TFT-LCDは、アレイ状に配設された複数のTFTを備えたTFT基板と、カラーフィルタ等を備えた対向基板との間に、液晶層が挟持された構造の液晶表示パネルを有している。液晶表示パネルの前面側と背面側のそれぞれに偏光板が設けられ、さらにそのうちの一方側にはバックライトが設けられる。この構造によって良好なカラー表示が得られる。

40

【0005】

液晶表示装置における液晶の駆動方式としては、TN(Twisted Nematic)モード、VA(Vertical Alignment)モードなどの縦電界方式と、IPS(In Plane Switching)モード(「IPS」は登録商標)、FFS(Fringe Field Switching)モードなどの横電界方式がある。一般に、横電界方式の液晶表示装置は、縦電界方式のものに比べて、広視野角や高精細度、高輝度化に有利であり、スマートフォンやタブレットなどの中小型パネルでは主流になりつつある。

【0006】

50

縦電界方式の液晶表示パネルでは、画像信号に応じた電圧が印加される画素電極がTFT基板に配設され、一定の電位（共通電位）に固定される共通電極が対向基板に配設される。従って、液晶層の液晶は、液晶表示パネルの表面に対してほぼ垂直な電界によって駆動される。

#### 【0007】

一方、横電界方式の液晶表示パネルでは、画素電極と共通電極の両方がTFT基板に配設され、液晶層の液晶は、液晶表示パネルの表面に対してほぼ水平な電界によって駆動される。特に、FFSモードのTFT基板では、画素電極と共通電極とが絶縁膜を介して上下に対向するように配設される。画素電極と共通電極はどちらを下にしてもよいが、下側に配設される方は平板状に形成され、上側に配設される方はスリットを有する格子状または櫛歯状に形成される。10

#### 【0008】

従来、液晶表示装置用のTFT基板のスイッチング素子には、TFTの活性層（チャネル層）を形成するための半導体膜にアモルファスシリコン（a-Si）が用いられていた。近年では、活性層に酸化物半導体を用いたTFTの開発が盛んになされている。酸化物半導体は、従来のアモルファスシリコンよりも高い移動度を有している。酸化物半導体としては、酸化亜鉛（ZnO）系材料や、酸化亜鉛に酸化ガリウム（Ga<sub>2</sub>O<sub>3</sub>）および酸化インジウム（In<sub>2</sub>O<sub>3</sub>）を添加した非晶質のInGaZnO系材料が主に用いられている。この技術は、特許文献1, 2および非特許文献1等に開示されている。20

#### 【0009】

酸化物半導体材料は、透明導電体である非晶質ITO（酸化インジウム（In<sub>2</sub>O<sub>3</sub>）+酸化すず（SnO<sub>2</sub>））や非晶質InZnO（酸化インジウム（In<sub>2</sub>O<sub>3</sub>）+酸化亜鉛（ZnO））のような酸化物導電体と同様に、シュウ酸やカルボン酸のような弱酸系溶液でエッティングすることが可能であり、パターン加工が容易であるという利点がある。20

#### 【0010】

しかし、酸化物半導体材料は、TFTのソース電極やドレイン電極に用いられる一般的な金属膜（Cr、Ti、Mo、Ta、Al、Cuおよびこれらの合金）のエッティング加工に用いられる酸系溶液に対してもエッティングダメージを受け、特性を劣化させてしまうことがある。あるいは、酸化物半導体材料の種類によっては、これらの酸系溶液に溶けてしまうことがある。従って、例えば特許文献2の図11（b）のように酸化物半導体から成るチャネル層の上にソース電極やドレイン電極を配設したTFT（一般的に、バックチャネルエッティング（BCE）型TFTと呼ばれる）を形成する場合は、ソース電極およびドレイン電極の加工に用いる酸系溶液によってチャネル層がダメージを受け、TFT特性を劣化させてしまうことがあった。さらには、ソース電極およびドレイン電極となる金属膜を酸化物半導体膜（チャネル層）の上に成膜するときに、その界面での酸化還元反応によりチャネル層がダメージを受け、TFTの特性を劣化させてしまうことがあった。30

#### 【0011】

この問題を解決するために、特許文献3に示すような、半導体膜の上層に保護絶縁層を形成したTFT構造を応用することが考えられる。このTFT構造では、金属膜をソース電極およびドレイン電極に加工するためのエッティングによって、酸化物半導体膜がダメージを受けたり消失したりすることを防止できる。この構造のTFTは、一般的に、エッティングストップまたはエッチストップ（ES）型TFTと呼ばれる。40

#### 【0012】

また、例えば、特許文献1の図1や図2には、金属酸化物からなる半導体膜（チャネル層）上に、酸化シリコンや窒化シリコンからなるチャネル保護膜（チャネル保護層）が設けられたTNモードのES型TFT基板が開示されている。

#### 【0013】

また、例えば特許文献5の図1や図2のような、a-Si半導体膜をチャネル層とするバックチャネルエッティング型TFTを備えるTNモードのTFT基板を作製する場合、一般的には、（1）ゲート電極の形成工程、（2）ゲート絶縁膜およびチャネル層の形成工50

程、(3)ソース電極およびドレイン電極の形成工程、(4)保護絶縁膜へのコンタクトホール形成工程、(5)画素電極の形成工程、という計5回の写真製版工程を経て製造することができる。

#### 【0014】

また、例えば特許文献6の図2や図3に示すように、バックチャネルエッチング型TFTを備えるFFS-TFT基板を作製する場合は、(1)ゲート電極の形成工程、(2)ゲート絶縁膜およびチャネル層の形成工程、(3)ソース電極およびドレイン電極の形成工程、(4)保護絶縁膜へのコンタクトホール形成工程、(5)画素電極の形成工程、(6)層間絶縁膜へのコンタクトホール形成工程、(7)共通電極の形成工程、という計7回の写真製版工程を経て製造することができる。

10

#### 【0015】

しかしながら、酸化物半導体をチャネル層とする一般的なエッチストップ型TFTを備えるTFT基板を作成するためには、酸化物半導体膜の上に保護絶縁層を形成するために、少なくとも写真製版工程を1回加する必要がある。従って、生産能力を低下させ、製造コストの増加を招くといった問題があった。

#### 【先行技術文献】

#### 【特許文献】

#### 【0016】

【特許文献1】特開2005-77822号公報

20

【特許文献2】特開2007-281409号公報

【特許文献3】特開昭62-235784号公報

【特許文献4】再表2011/077607号公報

【特許文献5】特開平10-268353号公報

【特許文献6】特開2009-151285号公報

#### 【非特許文献】

#### 【0017】

【非特許文献1】Kenji Nomura等著、「Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors」、Nature 2004年、第432巻、第488頁～第492頁

30

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0018】

例えば特許文献4には、(1)ゲート電極の形成工程、(2)酸化物半導体を用いたチャネル層の形成工程、(3)保護絶縁膜へのコンタクトホール形成工程、(4)画素電極、ソース電極およびドレイン電極の形成工程、という計4回の写真製版工程を用いて、TNモードのエッチストップ型TFT基板を作製する方法が提案されている(上記(2)と(3)との間に、ソース電極に接続するソース配線を形成するための写真製版工程が行われる場合もある)。

#### 【0019】

特許文献4に開示された方法でTFT基板を作製した場合、TFTのソース電極が接続するソース配線の下には、ゲート絶縁膜と同層の第1の絶縁膜と、保護絶縁膜と同層の第2の絶縁膜とが存在することになる。また、第1の絶縁膜の成膜工程と第2の絶縁膜の成膜工程との間に、酸化物半導体膜のエッチング工程が行われる。そのため、第1の絶縁膜の表面が、酸化物半導体膜のエッチング工程でダメージを受け、第1の絶縁膜と第2の絶縁膜との密着力が悪くなる場合があった。その結果、液晶表示装置の長期使用時に、第1の絶縁膜と第2の絶縁膜との密着力が悪い箇所でソース配線の断線が生じやすくなり、信頼性が低下するという問題があった。

40

#### 【0020】

なお、特許文献4には、エッチストップ型TFTを用いたLCDの写真製版工程の回数を減らす方法が記載されているものの、横電界方式のLCD(特にFFS-LCD)の製

50

造において写真製版工程の回数および製造コストを削減するための方法についての記載はない。

#### 【0021】

本発明は以上のような課題を解決するためになされたものであり、TFTのチャネル層に酸化物半導体を用いたエッチストップ型TFTを有するTFT基板において、写真製版工程の回数の増加を抑制しながら、各層の密着力の低下を防止することを目的とする。

#### 【課題を解決するための手段】

#### 【0022】

本発明に係る薄膜トランジスタ基板は、基板上に形成された薄膜トランジスタと、薄膜トランジスタのゲート電極に接続されたゲート配線と、前記薄膜トランジスタのドレイン電極に接続された画素電極と、薄膜トランジスタのソース電極に接続されたソース配線と、を備え、前記薄膜トランジスタは、前記基板上に形成された前記ゲート電極と、前記ゲート電極を覆うように形成された第1の絶縁膜と、前記第1の絶縁膜上の前記ゲート電極と重なる位置に形成された酸化物半導体から成るチャネル層と、前記チャネル層上に形成された第2の絶縁膜と、前記第2の絶縁膜を覆うように形成された第3の絶縁膜と、前記第3の絶縁膜上に形成されたソース電極、ドレイン電極とを備え、前記ソース電極および前記ドレイン電極は、それぞれ前記第2の絶縁膜および前記第3の絶縁膜を貫通するコンタクトホールを通して、前記チャネル層に接続しており、前記ソース配線の下の全体には、前記チャネル層と同層において当該チャネル層と離間して設けられた酸化物半導体膜、および、前記第2の絶縁膜と同層において当該第2の絶縁膜と離間して設けられた絶縁膜が配置されている。10 20

#### 【発明の効果】

#### 【0023】

本発明に係るTFT基板によれば、液晶表示装置の長期使用時においても、TFT部の膜剥がれやソース配線の断線などが抑制されるため、液晶表示装置の信頼性が向上する。また、移動度の高い酸化物半導体を高性能な特性を維持した状態でチャネル層として用いることができるため、高性能のTFT基板、およびこれを用いた液晶表示装置を生産性良く製造することができる。30

#### 【図面の簡単な説明】

#### 【0024】

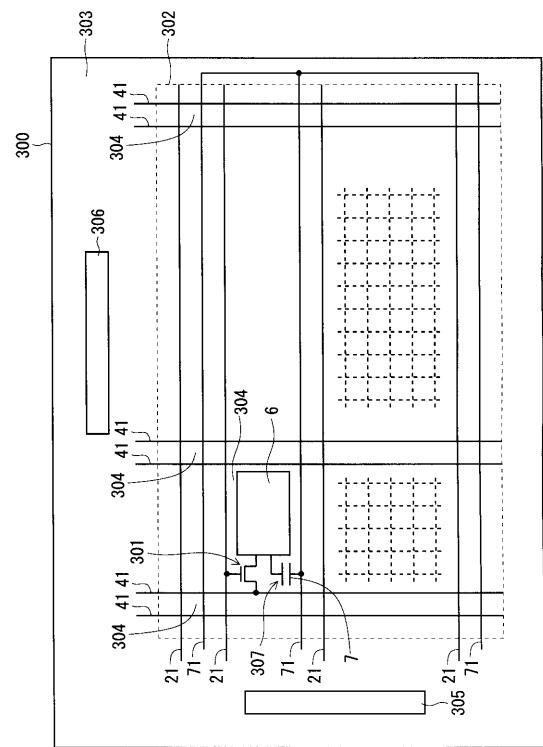

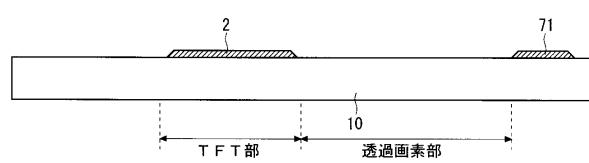

【図1】一般的なTFT基板の構成を模式的に示す平面図である。

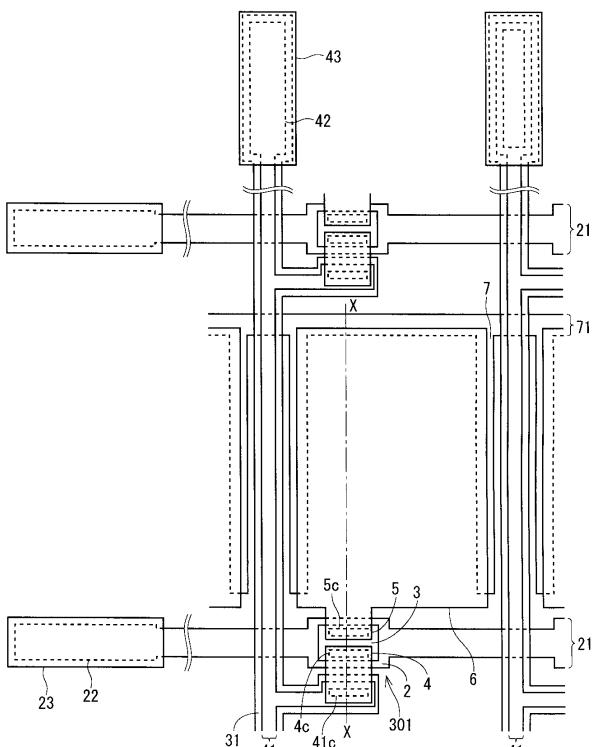

【図2】実施の形態1に係るTFT基板の構成を示す平面図である。

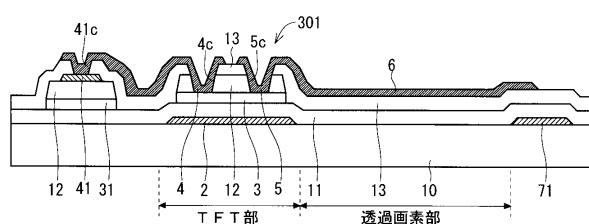

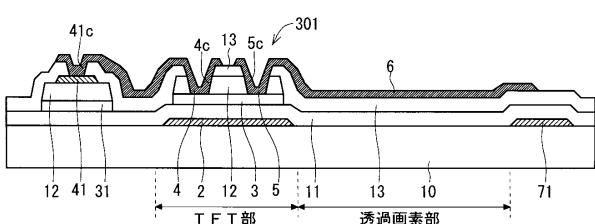

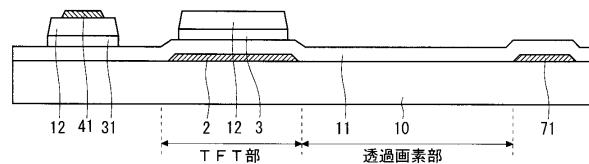

【図3】実施の形態1に係るTFT基板の構成を示す断面図である。

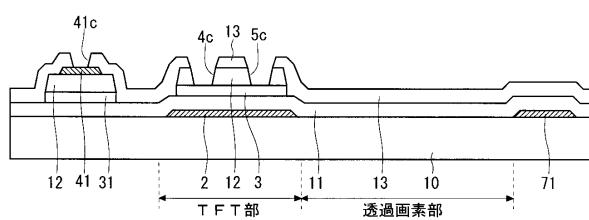

【図4】実施の形態1に係るTFT基板の製造工程を示す断面図である。

【図5】実施の形態1に係るTFT基板の製造工程を示す断面図である。

【図6】実施の形態1に係るTFT基板の製造工程を示す断面図である。

【図7】実施の形態1に係るTFT基板の製造工程を示す断面図である。

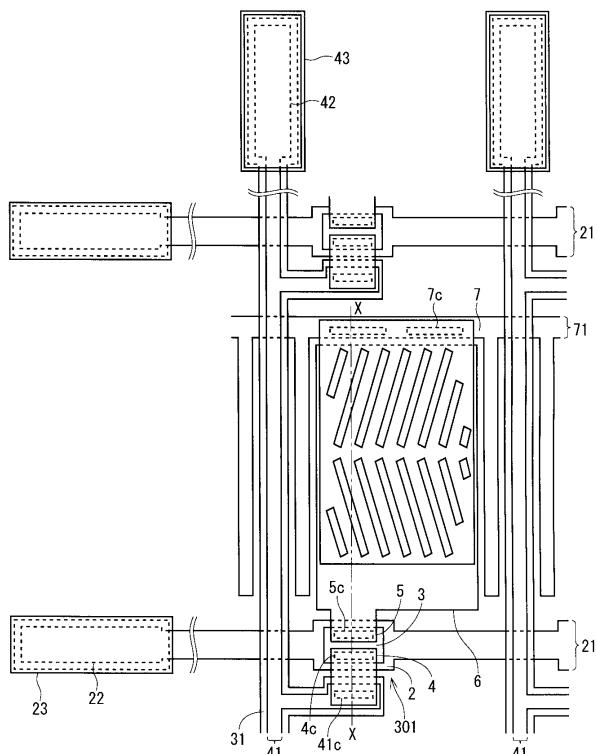

【図8】実施の形態2に係るTFT基板の構成を示す平面図である。

【図9】実施の形態2に係るTFT基板の構成を示す断面図である。40

【図10】実施の形態2に係るTFT基板の製造工程を示す断面図である。

【図11】実施の形態2に係るTFT基板の製造工程を示す断面図である。

【図12】実施の形態2に係るTFT基板の製造工程を示す断面図である。

【図13】実施の形態2に係るTFT基板の製造工程を示す断面図である。

【図14】実施の形態2に係るTFT基板の製造工程を示す断面図である。

【図15】実施の形態2に係るTFT基板の製造工程を示す断面図である。

#### 【発明を実施するための形態】

#### 【0025】

<実施の形態1>

図1は、一般的なTFT基板の構成を示す平面図である。TFT基板は、スイッチング50

素子としての薄膜トランジスタ（TFT）がマトリックス状に複数個配置されたアクティブマトリックス基板である。また、ここでは、平面型表示装置（フラットパネルディスプレイ）である液晶表示装置（LCD）用のTFT基板を例に挙げて説明する。

#### 【0026】

TFT基板300は、TFT301を有する画素304がマトリックス状に配列される表示領域302と、表示領域302の外側を囲む額縁領域303とに分けられる。

#### 【0027】

表示領域302には、複数のゲート配線21（走査信号線）および複数のソース配線41（表示信号線）が配設される。複数のゲート配線21は互いに平行に配設され、複数のソース配線41も互いに平行に配設される。複数のゲート配線21と複数のソース配線41は交差する。図1では、ゲート配線21が横方向に延在し、ソース配線41が縦方向に延在している。隣接するゲート配線21と隣接するソース配線41で囲まれた領域が画素304となるので、表示領域302には、画素304がマトリックス状に配列されることになる。

#### 【0028】

図1においては、代表的に1つの画素304の構成を図示している。画素304には、少なくとも1つのTFT301が配設される。TFT301は、ソース配線41とゲート配線21の交差点近傍に配置され、ゲート配線21に接続されるゲート電極と、ソース配線41に接続されるソース電極と、画素電極6に接続されるドレイン電極とを有している。また、画素電極6は補助容量電極7との間に補助容量307を形成しており、補助容量電極7は予め定められた電位（共通電位）が供給される共通配線71に接続されている。共通配線71は、ゲート配線21に平行に（ソース配線41に直交するように）延在し、ゲート配線21と共に共通配線71とは交互に配設される。

#### 【0029】

一方、TFT基板300の額縁領域303には、走査信号駆動回路305および表示信号駆動回路306が設けられている。図示は省略するが、ゲート配線21は、表示領域302から走査信号駆動回路305が設けられた側の額縁領域303へと引き出され、走査信号駆動回路305に接続されている。同様に、ソース配線41は、表示領域302から表示信号駆動回路306が設けられた側の額縁領域303へと引き出され、表示信号駆動回路306に接続されている。また、走査信号駆動回路305および表示信号駆動回路306には、外部接続の接続基板（不図示）が接続されている。

#### 【0030】

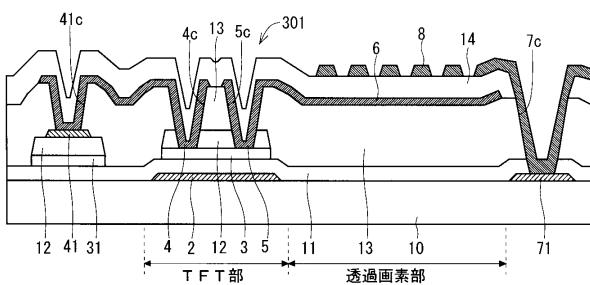

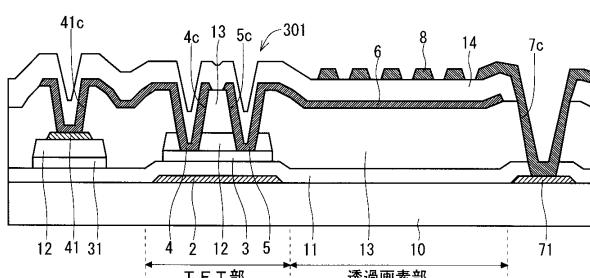

次に、図2および図3を参照して、本実施の形態に係るTFT基板の構成について説明する。図2は、TNモードの液晶表示装置に用いるTFT基板の構成を示す平面図であり、画素の形成領域（画素部）と、ゲート配線端部のゲート端子の形成領域と、ソース配線端部のソース端子の形成領域とが示されている。図3は、画素部の断面構成を示しており、図2に示すX-X線に沿った断面に対応している。X-Xに沿った断面は、図3に示すように、TFT301の形成領域である「TFT部」と、画素電極の形成領域である「透過画素部」とを含んでいる。

#### 【0031】

図3のように、TFT基板は、例えばガラス等の透明性絶縁基板である基板10を用いて形成される。基板10上には、第1の導電膜を用いて形成された、ゲート電極2、ゲート配線21、補助容量電極7、共通配線71およびゲート端子22が配設されている。

#### 【0032】

図2において、ゲート配線21は横方向に延在している。TFT301のゲート電極2は、ゲート配線21の一部分である。すなわち、ゲート配線21におけるTFT部の部分がゲート電極2となっている。本実施の形態では、ゲート電極2となる部分の幅を、ゲート配線21の他の部分よりも広くしている。また、ゲート端子22は、ゲート配線21の一方の端部に形成されている。共通配線71は、ゲート配線21と平行に延在している。

#### 【0033】

10

20

30

40

50

そして、ゲート電極2、ゲート配線21、補助容量電極7、共通配線71およびゲート端子22を覆うように、第1の絶縁膜11が形成されている。第1の絶縁膜11は、TFT部ではゲート絶縁膜として機能する。

#### 【0034】

第1の絶縁膜11の上には、ゲート電極2に重なる位置に、酸化物半導体からなるTFT301のチャネル層3が配設されている。なお、チャネル層3と同層の酸化物半導体膜31は、TFT部だけでなく、第2の導電膜で形成されるソース配線41およびソース端子42の下に残存する。チャネル層3および酸化物半導体膜31の上には、第2の絶縁膜12が形成され、ソース配線41およびソース端子42は、第2の絶縁膜12の上に形成される。よって、ソース配線41およびソース端子42の下には、第1の絶縁膜11、酸化物半導体膜31および第2の絶縁膜12からなる積層構造が存在することとなる。10

#### 【0035】

第2の絶縁膜12、ソース配線41およびソース端子42を覆うように、第3の絶縁膜13が形成されている。第2の絶縁膜12および第3の絶縁膜13には、それらを貫通するようにコンタクトホール4c, 5c, 41cが形成されている。コンタクトホール4cおよびコンタクトホール5cは、チャネル層3に達している。コンタクトホール4cに露出したチャネル層3の部分がTFT301のソース領域となり、コンタクトホール5cに露出したチャネル層3の部分がTFT301のドレイン領域となる。コンタクトホール41cはソース配線41に達している。20

#### 【0036】

そして第3の絶縁膜13の上に、透明導電膜（透光性導電膜）で形成された、ソース電極4、ドレイン電極5および画素電極6が形成されている。ソース電極4とドレイン電極5とは互いに離間しており、ソース電極4はコンタクトホール4cを通してチャネル層3に接続し、ドレイン電極5はコンタクトホール5cを通してチャネル層3に接続している。20

#### 【0037】

また、ソース電極4は、コンタクトホール41cが形成された領域まで延在しており、当該コンタクトホール41cを通してソース配線41に接続している。ドレイン電極5は画素電極6と一体的に形成されている。このような構成により、ソース電極4はソース配線41に電気的に接続され、ドレイン電極5は画素電極6に電気的に接続される。30

#### 【0038】

本実施の形態では、チャネル層3となる酸化物半導体膜として、例えば、酸化亜鉛（ZnO）系の酸化物半導体や、酸化亜鉛（ZnO）に酸化インジウム（In<sub>2</sub>O<sub>3</sub>）および酸化すず（SnO<sub>2</sub>）を添加したIn-Zn-SnO系の酸化物半導体、あるいは、酸化亜鉛（ZnO）系の酸化物半導体や、酸化亜鉛（ZnO）に酸化ガリウム（Ga<sub>2</sub>O<sub>3</sub>）と酸化インジウム（In<sub>2</sub>O<sub>3</sub>）を添加したIn-Ga-ZnO系の酸化物半導体などを用いることができる。好ましくは、ソース電極4およびドレイン電極5の加工時（第2の導電膜のエッチング時）にエッチングされない、もしくは、エッチングによるダメージを受けない材料が良い。30

#### 【0039】

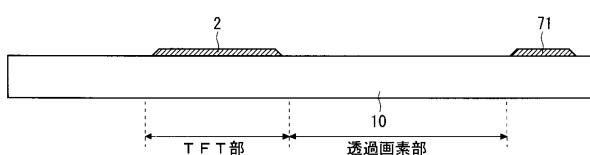

次に、実施の形態1に係るTFT基板の製造方法について、図4～図7を参照しつつ説明する。なお、図4～図7においては、図2および図3で示したものと同一の要素には、同一符号を付している。40

#### 【0040】

まず、基板10を洗浄液または純水を用いて洗浄する。本実施の形態では、厚さ0.5mmのガラス基板を基板10として用いた。そして、洗浄された基板10の一方の主面全面に、ゲート電極2、ゲート配線21等の材料である第1の導電膜を成膜する。

#### 【0041】

第1の導電膜としては、例えばクロム（Cr）、モリブデン（Mo）、チタン（Ti）、銅（Cu）、タンタル（Ta）、タングステン（W）、アルミニウム（Al）などの金50

属やこれらの金属元素を主成分として他の元素を1種類以上添加した合金等を用いることができる。ここで、主成分の元素とは、合金を構成する元素のうち、含有量が最も多い元素のことを示すものとする。また、これらの金属または合金からなる層を2以上含む積層構造としてもよい。これらの金属または合金を用いることによって、比抵抗値が $50\ \mu\text{cm}$ 以下の低抵抗な導電膜を得ることができる。本実施の形態では、第1の導電膜としてアルミニウム(A1)合金膜を用い、アルゴン(Ar)ガスを用いたスパッタリング法で、A1合金膜を200nmの厚さに成膜した。

#### 【0042】

その後、第1の導電膜上にフォトレジスト材を塗布し、1回目の写真製版工程でフォトレジストパターンを形成し、当該フォトレジストパターンをマスクにして、第1の導電膜をエッチングによりパターニングする。ここでは、リン酸、酢酸および硝酸を含む溶液(PAN薬液)によるウエットエッチングを用いた。その後、フォトレジストパターンを除去すると、基板10上に、ゲート電極2、ゲート配線21、補助容量電極7、共通配線71およびゲート端子22が形成される(図4)。

#### 【0043】

次に、基板10の上面全体に第1の絶縁膜11を成膜する。本実施形態では、化学的気相成膜(Chemical Vapor Deposition: CVD)法を用いて、酸化シリコン膜(SiO)と窒化シリコン膜(SiN)を成膜することで、第1の絶縁膜11を形成した。酸化シリコン膜は、水分(H<sub>2</sub>O)や水素(H<sub>2</sub>)、ナトリウム(Na)、カリウム(K)のようなTFT特性に悪影響を及ぼす不純物元素に対するバリア性(遮断性)が弱いため、本実施形態では、酸化シリコン膜の下にバリア性に優れる窒化シリコン膜を設けた。ここでは、第1の絶縁膜11を、厚さ50nmの酸化シリコン膜と厚さ400nmの窒化シリコン膜との積層構造とした。この第1の絶縁膜11は、TFT301のゲート絶縁膜として機能する。

#### 【0044】

その後、第1の絶縁膜11の上に、チャネル層3の材料である酸化物半導体膜を成膜する。本実施形態では、酸化物半導体として、InとGaとZnを含む酸化物(例: InGaZnO)を用いる。具体的にはIn:Ga:Zn:Oの原子組成比が1:1:1:4であるIn-Ga-Zn-Oターゲット[In<sub>2</sub>O<sub>3</sub>·Ga<sub>2</sub>O<sub>3</sub>·(ZnO)<sub>2</sub>]を用いたスパッタリング法により、InGaZnO膜を成膜した。

#### 【0045】

次に、第2の絶縁膜12を成膜する。本実施形態では、第2の絶縁膜12として、CVD法を用いて、SiO膜を形成した。ここでは、厚さ100nmのSiO膜を成膜した。

#### 【0046】

そして、第2の絶縁膜12の上に、ソース電極4、ドレイン電極5、画素電極6などの材料としての第2の導電膜を成膜する。本実施形態では、第2の導電膜としてモリブデン(Mo)とアルミニウム(A1)との積層膜を、第2の導電膜として用いた。MoおよびA1のそれぞれに他の元素を微量に添加した合金を用いてもよい。

#### 【0047】

その結果、第1の絶縁膜11上に、酸化物半導体膜、第2の絶縁膜12および第2の導電膜をこの順に積層した積層膜が形成される。そして、2回目の写真製版工程でフォトレジストパターンを形成し、これをマスクにして、その積層膜をエッチングしてパターニングする。このフォトレジストパターンは、チャネル層3の形成領域およびソース配線41およびソース端子42の形成領域に形成する。ただし、フォトレジストパターンを形成する際、「グレートーンマスク」あるいは「ハーフトーンマスク」と呼ばれるハーフ露光マスクを用いる露光(ハーフ露光)を行うことで、ソース配線41およびソース端子42の形成領域上のフォトレジストパターンが他の部分よりも厚くなるように、フォトレジストパターンを形成する(フォトレジストパターンの厚い部分の幅は、実際のソース配線41およびソース端子42の形成領域よりも若干広くする)。

#### 【0048】

10

20

30

40

50

第2の導電膜(MoとAlとの積層膜)のエッティングは、リン酸、酢酸および硝酸を含む溶液(PAN薬液)によるウエットエッティング法を用いることができる。ここでは、リン酸70wt%+酢酸7wt%+硝酸5wt%+水のPAN薬液を用いてエッティングを行った。チャネル層3となる酸化物半導体膜は第2の絶縁膜12で覆われているため、エッティングの薬液によるダメージを受けない。

#### 【0049】

第2の導電膜をエッティングした後、続けてその下の第2の絶縁膜12(SiO膜)をエッティングする。このエッティングは、フッ素を含むガスを用いたドライエッティング法を用いることができる。ここでは、六フッ化硫黄(SF<sub>6</sub>)に酸素(O<sub>2</sub>)を加えたガスを用いたドライエッティングを行った。O<sub>2</sub>ガスを添加することで、エッティング時に第2の絶縁膜12の下の酸化物半導体膜に還元反応によるダメージが生じることを抑制できる。

10

#### 【0050】

その後、酸化物半導体膜をエッティングする。このエッティングには、カルボン酸を含む薬液によるウエットエッティングを用いることができる。カルボン酸を含む薬液としては、シウ酸を1~10wt%の範囲で含むものが好ましい。本実施の形態では、シウ酸5wt%+水のシウ酸系薬液を用いて、酸化物半導体膜をエッティングした。

#### 【0051】

その後、酸素アッシングによって、フォトレジストパターンを薄膜化する。ソース配線41およびソース端子42の形成領域上のフォトレジストパターンを予め厚く形成しているため、酸素アッシング後には、ソース配線41およびソース端子42の形成領域上にのみ、フォトレジストパターンが残ることになる。

20

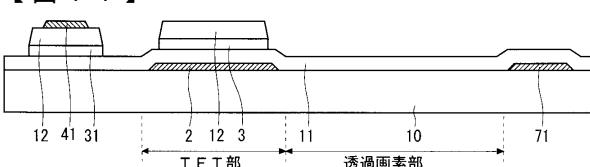

#### 【0052】

そして、残存するフォトレジストパターンをマスクとして、第2の導電膜をエッティングする。それにより、第2の導電膜が、ソース配線41およびソース端子42のパターンに加工される。このエッティングは、上記と同様のPAN薬液を用いて行うことができる。その後、フォトレジストパターンを除去する。すると、TFT領域には、第1の絶縁膜11上に、チャネル層3および第2の絶縁膜12の積層構造が形成される。また、ソース配線41およびソース端子42の形成領域には、第1の絶縁膜11上に、酸化物半導体膜31と第2の絶縁膜12の積層構造の上に配置されたソース配線41およびソース端子42が形成される(図5)。

30

#### 【0053】

つまり、本実施の形態のTFT基板では、ソース配線41およびソース端子42の下に、酸化物半導体膜31と第2の絶縁膜12が残存する構造となる。なお、ソース配線41およびソース端子42をバーニングしたときのフォトレジストパターンは、上記の酸素アッシングによって、酸化物半導体膜31と第2の絶縁膜12をバーニングしたときのフォトレジストパターンよりも幅が狭くなるため、図5のように、ソース配線41の幅は、その下の酸化物半導体膜31および第2の絶縁膜12の幅よりも狭くなる。

#### 【0054】

その後、基板10の上面全体に第3の絶縁膜13を成膜する。本実施形態では、CVD法を用いて、厚さ200nmのSiO膜を成膜し、その上に厚さ100nmのSiN膜を成膜することで、第3の絶縁膜13を形成した。

40

#### 【0055】

そして、3回目の写真製版工程でフォトレジストパターンを形成し、それをマスクにして、第3の絶縁膜13および第2の絶縁膜12をエッティングする。このエッティングには、フッ素を含むガスを用いたドライエッティング法を用いることができる。本実施例では六フッ化硫黄(SF<sub>6</sub>)に酸素(O<sub>2</sub>)を加えたガスを用いてドライエッティングした。その後、フォトレジストパターンを除去すると、コンタクトホール41c, 4c, 5cが形成される(図6)。なお、図示は省略するが、この工程では、ゲート端子22およびソース端子42およびその周辺部の第3の絶縁膜13も除去される。

#### 【0056】

10

20

30

40

50

その後、第3の導電膜を成膜する。本実施形態では、第3の導電膜として透明導電膜(透光性導電膜)を用いる。透明導電膜としては、ITO(酸化インジウム( $In_2O_3$ ))と酸化すず( $SnO_2$ )の混合比は、例えば90:10(重量%)を用いる。ここではスパッタリング法で、アルゴン(Ar)に水素(H)を含むガス、例えば、水素( $H_2$ )ガスまたは水蒸気( $H_2O$ )などを混合したガスを用い、厚さ100nmのITO膜を非晶質状態で成膜する。

#### 【0057】

そして、4回目の写真製版工程でフォトレジストパターンを形成し、これをマスクにして第3の導電膜(非晶質ITO膜)をエッチングする。このエッチングは、シュウ酸5wt%+水のシュウ酸系薬液を用いたウエットエッチング法で行った。その後、フォトレジストパターンを除去すると、ソース電極4、ドレイン電極5および画素電極6が形成される(図7)。このとき、ソース電極4は、コンタクトホール4cを通してチャネル層3に接続されると共に、コンタクトホール41cを介してソース配線41に接続される。また、ドレイン電極5は、コンタクトホール5cを通してチャネル層3に接続される。

#### 【0058】

図示は省略するが、ゲート端子22およびソース端子42の上には、コンタクトホールを介してそれらに接続するパッド23, 43が、第3の導電膜を用いて形成される。以上により、図2および図3に示したTFT基板が完成する。

#### 【0059】

液晶表示パネルの組み立ての際は、完成したTFT基板の表面に配向膜やスペーサーを形成する。配向膜は、液晶を配列させるための膜であり、ポリイミド等で構成される。また、別途作製したカラーフィルタや配向膜を備えた対向基板を、本実施の形態のTFT基板と貼り合わせる。このときスペーサーによってTFT基板と対向基板との間に隙間が形成され、その隙間に液晶層を形成して封止することによって、TNモードの液晶表示パネルが形成される。最後に、液晶表示パネルの外側に偏光板、位相差板およびバックライトユニット等を配設することによって液晶表示装置が完成する。

#### 【0060】

以上のように、本実施の形態では、チャネル層に酸化物半導体膜を用いたエッチストップ型TFTの形成において、ソース電極4およびドレイン電極5を形成するための第2の導電膜のエッチングを行うとき、チャネル層3の表面はそのエッチングに曝されない。そのため、当該エッチングによってチャネル層3が消滅したり、ダメージを受けたりすることが防止される。また、エッチストップ型TFTを用いたTFT基板を4回の写真製版工程を用いて形成することができる。よって、写真製版工程の回数を増やすずに、良好な特性のTFT301を備えるTFT基板を生産性よく製造することができる。

#### 【0061】

さらに、第1の絶縁膜11、酸化物半導体膜、第2の絶縁膜12、第3の絶縁膜13の積層構造を形成する際、各層を形成する間に、ウエットエッチング処理やドライエッチング処理が行われないため、各層の表面にダメージが生じず、各層間の密着力の低下を防止できる。そのため、長期使用時においても、TFT部の膜剥がれやソース配線41の断線などが抑制され、信頼性が向上するという効果も得られる。

#### 【0062】

##### <実施の形態2>

実施の形態1では、本発明をTNモードの液晶表示装置に使用されるTFT基板に適用した例を示したが、実施の形態2では、本発明をFFSモードの液晶表示装置に使用されるTFT基板に適用した例を示す。

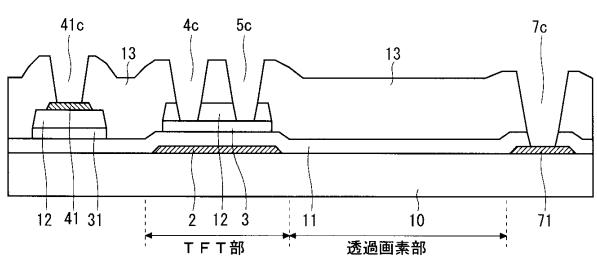

#### 【0063】

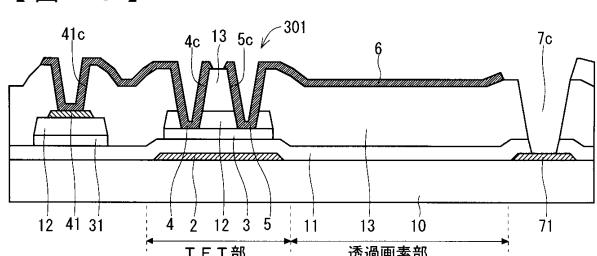

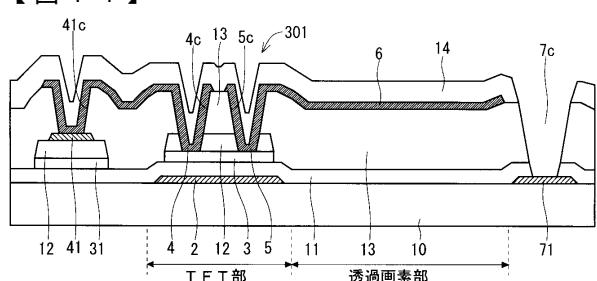

図8および図9を参照して、本実施の形態に係るTFT基板の構成について説明する。図8は、FFSモードの液晶表示装置に用いるTFT基板の構成を示す平面図であり、画素の形成領域(画素部)と、ゲート配線端部のゲート端子の形成領域と、ソース配線端部

10

20

30

40

50

のソース端子の形成領域とが示されている。図9は、画素部の断面構成を示しており、図8に示すX-X線に沿った断面に対応している。各図において、実施の形態1で説明したものと同様の機能を有する要素にはそれと同一符号を付しているため、ここではそれらの詳細な説明は省略する。

#### 【0064】

図8および図9に示すように、FFSモードのTFT基板には、画素電極6に対向するように共通電極8が設けられる。本実施の形態では、実施の形態1と同様に第3の導電膜(第1の透明導電膜)で形成した画素電極6の上に、第4の絶縁膜14を介して、第4の導電膜(第2の透明導電膜)で形成した共通電極8を配設している。共通電極8は、スリットを有する格子状または櫛歯状であり、第4の絶縁膜14、第3の絶縁膜13、第1の絶縁膜11を貫通するコンタクトホール7cを通して、共通配線71に電気的に接続している。10

#### 【0065】

また、本実施の形態では、第4の絶縁膜14を有機樹脂膜を用いて厚く形成し、TFT基板の上面の平坦性を向上させている(以下、有機樹脂膜を「平坦化膜」ともいう)。

#### 【0066】

次に、実施の形態2に係るTFT基板の製造方法について、図10～図15を参照しつつ説明する。なお、図10～図15においては、図8および図9で示したものと同一の要素には、同一符号を付している。

#### 【0067】

まず、実施の形態1と同様に、1回目の写真製版工程を経て、基板10上に、ゲート電極2、ゲート配線21、補助容量電極7、共通配線71およびゲート端子22が形成する(図10)。さらに、第1の絶縁膜11を形成した後、ハーフ露光マスクを使用する2回目の写真製版工程を経て、第1の絶縁膜11上に、チャネル層3および第2の絶縁膜12の積層構造と、ソース配線41およびソース端子42を形成する(ソース配線41およびソース端子42の下には、酸化物半導体膜31と第2の絶縁膜12が残存する)(図11)20。

#### 【0068】

次に、平坦化膜となる第3の絶縁膜13を形成する。ここでは、感光性を有する有機樹脂をスピンドル等によって膜厚2～4μmを塗布する。その後、3回目の写真製版工程で第3の絶縁膜13を露光、現像することで、コンタクトホール4c, 5c, 7c, 41cを形成する(図12)。図示は省略するが、このときゲート配線21およびソース端子42の形成領域でも、第3の絶縁膜13を除去しておく。30

#### 【0069】

次に、基板10上の全面に、第3の導電膜(第1の透明導電膜)をスパッタ法等で成膜し、4回目の写真製版工程でフォトレジストパターンを形成し、これをマスクにして第3の導電膜をエッチングする。その後、フォトレジストパターンを除去すると、ソース電極4、ドレイン電極5および画素電極6が形成される(図13)。このとき、ソース電極4は、コンタクトホール4cを通してチャネル層3に接続されると共に、コンタクトホール41cを介してソース配線41に接続される。また、ドレイン電極5は、コンタクトホール5cを通してチャネル層3に接続される。40

#### 【0070】

次に、基板10上の全面に第4の絶縁膜14をCVD法などにより成膜する。第4の絶縁膜14は、先に形成したコンタクトホール7cの内部にも形成されるため、5回目の写真製版工程でコンタクトホール7cを再度形成する(コンタクトホール7c内の第4の絶縁膜14を除去する)(図14)。図示は省略するが、このときゲート端子22およびソース端子42の形成領域およびその外周部の第4の絶縁膜14も除去する。

#### 【0071】

その後、共通電極8の材料である第4導電膜(第2の透明導電膜)を、コンタクトホール7c内を含む基板10上の全面に成膜する。ここでは、ITOを用い、スパッタ法で形50

成する。その後、6回目の写真製版工程で、第4導電膜をパターニングすることで、スリットを有する共通電極8を形成する(図15)。共通電極8は、コンタクトホール7cを介して、補助容量電極7と電気的に接続される。

#### 【0072】

また、図示は省略するが、ゲート端子22およびソース端子42の上には、それらに接続するパッド23, 43が、第4の導電膜を用いて形成される。以上により、図8および図9に示したTFT基板が完成する。

#### 【0073】

なお、本実施の形態では、感光性の有機樹脂膜を用いて第3の絶縁膜13を形成したが、第3の絶縁膜13の構成はこれに限らず、例えば、有機樹脂膜の下層にCVD法を用いて形成したSiO膜やSiN膜あるいはこれらの積層膜を設けたものを第3の絶縁膜13としてもよい。この場合は、有機樹脂膜のコンタクトホール4c, 5c, 7c, 41cのパターンを形成した後に、有機樹脂膜をマスクとして下層のSiO膜やSiN膜をエッチングしてコンタクトホール4c, 5c, 7c, 41cを形成することができる。10

#### 【0074】

第3の絶縁膜13は、また有機樹脂膜を用いずに、SiO膜やSiN膜、あるいはこれらの積層膜のみとしてもよい。この場合は、SiO膜やSiN膜を成膜した後、フォトレジストパターンを形成し、これをマスクとしてSiO膜やSiN膜をエッチングする。その後、フォトレジストパターンを除去して、コンタクトホール4c, 5c, 7c, 41cを形成することができる。20

#### 【0075】

以上のように、実施の形態2においても、チャネル層に酸化物半導体膜を用いたエッチストップ型TFTの形成において、ソース電極4およびドレイン電極5を形成するための第2の導電膜のエッチングを行うとき、チャネル層3の表面はそのエッチングに曝されない。そのため、当該エッチングによってチャネル層3が消滅したり、ダメージを受けたりすることが防止される。また、エッチストップ型TFTを用いたFFSモードのTFT基板を6回の写真製版工程を用いて形成することができる。よって、良好な特性のTFT301を備えるTFT基板を生産性よく製造することができる。

#### 【0076】

なお、本発明は、その発明の範囲内において、各実施の形態を自由に組み合わせたり、各実施の形態を適宜、変形、省略することが可能である。30

#### 【符号の説明】

#### 【0077】

2 ゲート電極、3 チャネル層、31 酸化物半導体膜、10 基板、11 第1の絶縁膜、12 第2の絶縁膜、13 第3の絶縁膜、14 第4の絶縁膜、2 ゲート電極、21 ゲート配線、22 ゲート端子、4 ソース電極、41 ソース配線、42 ソース端子、5 ドレイン電極、6 画素電極、7 補助容量電極、71 共通配線、8 共通電極、4c, 5c, 7c, 41c コンタクトホール、300 TFT基板、301 TFT、302 表示領域、303 額縁領域、304 画素、305 走査信号駆動回路、306 表示信号駆動回路、307 補助容量。40

【図1】

【図2】

【図3】

【図7】

【図4】

【図5】

【図6】

【図 8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 15】

【図 13】

【図 14】

---

フロントページの続き

(51)Int.Cl.

F I

G 0 2 F 1/1368

G 0 9 F 9/30 3 3 8

(72)発明者 井上 和式

熊本県合志市御代志 9 9 7 番地 メルコ・ディスプレイ・テクノロジー株式会社内

審査官 綿引 隆

(56)参考文献 特開2012-164976 (JP, A)

特開2014-215485 (JP, A)

特開2007-157916 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 0 2 F 1 / 1 3 6 8

G 0 9 F 9 / 3 0

H 0 1 L 2 1 / 3 3 6

H 0 1 L 2 9 / 7 8 6