# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

**H01G 4/12** (2006.01) **H01G 4/30** (2006.01)

(21) 출원번호 **10-2013-0008029**

(22) 출원일자 **2013년01월24일** 심사청구일자 **2013년01월24일**

(65) 공개번호10-2014-0095270(43) 공개일자2014년08월01일

(56) 선행기술조사문헌 JP2000124057 A\* KR100586954 B1\* KR1020110074259 A

\*는 심사관에 의하여 인용된 문헌

(24) 등록일자 (73) 특허권자

(45) 공고일자

(11) 등록번호

# 삼성전기주식회사

경기도 수워시 영통구 매영로 150 (매탄동)

2014년11월17일

2014년11월11일

10-1462753

(72) 발명자

#### 임진형

경기 수원시 영통구 매영로 150, (매탄동, 삼성 전기)

# 우석균

경기 수원시 영통구 매영로 150, (매탄동, 삼성 전기)

(뒷면에 계속)

(74) 대리인

특허법인씨엔에스

전체 청구항 수 : 총 16 항

심사관: 전한철

#### \_\_\_\_\_ (54) 발명의 명칭 **적충 세라믹 전자부품 및 이의 제조방법**

### (57) 요 약

본 발명은 적층 세라믹 전자부품 및 이의 제조방법에 관한 것으로, 본 발명은 유전체층을 포함하는 세라믹 본체; 및 상기 세라믹 본체 내에서 상기 유전체층을 사이에 두고 서로 대향하도록 배치되며, 폭 방향으로 인쇄폭이 차이가 나도록 교차 적층되는 제1 및 제2 내부전극;을 포함하며, 상기 제1 및 제2 내부전극의 최대폭을 W라 하고, 상기 제1 및 제2 내부전극의 최소폭을 w라고 정의하면, 하기식으로 표현되는 상기 최대폭과 최소폭의 폭 차이율 (D)이 20 내지 80%인 적층 세라믹 전자부품,

#### [식] D=(W-w)/W×100

을 제공한다.

# 대 표 도 - 도2

(72) 발명자

이충은

경기 수원시 영통구 매영로 150, (매탄동, 삼성 전기) 김두영

경기 수원시 영통구 매영로 150, (매탄동, 삼성 전기)

# 특허청구의 범위

### 청구항 1

유전체층을 포함하는 세라믹 본체; 및

상기 세라믹 본체 내에서 상기 유전체층을 사이에 두고 서로 대향하도록 배치되며, 폭 방향으로 인쇄폭이 차이가 나도록 교차 적층되는 제1 및 제2 내부전극;을 포함하며,

상기 제1 및 제2 내부전극의 최대폭을 W라 하고, 상기 제1 및 제2 내부전극의 최소폭을 w라고 정의하면,

하기식으로 표현되는 상기 최대폭과 최소폭의 폭 차이율(D)이 20 내지 80%이며, 상기 제1 및 제2 내부전극 중 인쇄폭이 더 넓은 전극의 인쇄폭이 200 내지 250 μm에서 상기 제1 내부전극과 제2 내부전극의 폭 차이율이 20 내지 40%인 적층 세라믹 전자부품,

[식] D=(W-w)/W×100.

### 청구항 2

제1항에 있어서,

상기 제1 내부전극과 제2 내부전극의 인쇄폭 차이는 100 μm 이하인 적층 세라믹 전자부품.

#### 청구항 3

제1항에 있어서,

상기 유전체층의 평균 두께는 0.6 µm 이하인 적층 세라믹 전자부품.

### 청구항 4

제1항에 있어서.

상기 제1 및 제2 내부전극의 평균 두께는 0.6 μm 이하인 적층 세라믹 전자부품.

#### 청구항 5

삭제

# 청구항 6

유전체층을 포함하는 세라믹 본체; 및

상기 세라믹 본체 내에서 상기 유전체층을 사이에 두고 서로 대향하도록 배치되며, 폭 방향으로 인쇄폭이 차이가 나도록 교차 적층되는 제1 및 제2 내부전극;을 포함하며,

상기 제1 및 제2 내부전극의 최대폭을 W라 하고, 상기 제1 및 제2 내부전극의 최소폭을 w라고 정의하면,

하기식으로 표현되는 상기 최대폭과 최소폭의 폭 차이율(D)이 20 내지 80%이며, 상기 제1 및 제2 내부전극 중 인쇄폭이 더 넓은 전극의 인쇄폭이 300 내지 400 μm에서 상기 제1 내부전극과 제2 내부전극의 폭 차이율이 40 내지 70%인 적층 세라믹 전자부품,

[식] D=(W-w)/W×100.

## 청구항 7

유전체층을 포함하는 세라믹 본체; 및

상기 세라믹 본체 내에서 상기 유전체층을 사이에 두고 서로 대향하도록 배치되며, 폭 방향으로 인쇄폭이 차이가 나도록 교차 적층되는 제1 및 제2 내부전극;을 포함하며,

상기 제1 및 제2 내부전극의 최대폭을 W라 하고, 상기 제1 및 제2 내부전극의 최소폭을 w라고 정의하면,

하기식으로 표현되는 상기 최대폭과 최소폭의 폭 차이율(D)이 20 내지 80%이며, 상기 제1 및 제2 내부전극 중인쇄폭이 더 넓은 전극의 인쇄폭이 500 μm 이상에서 상기 제1 내부전극과 제2 내부전극의 폭 차이율이 20 내지 80%인 적층 세라믹 전자부품.

[식] D=(W-w)/W×100.

## 청구항 8

제1항에 있어서,

상기 제1 또는 제2 내부전극의 연결성은 90% 이상인 적층 세라믹 전자부품.

#### 청구항 9

세라믹 분말을 포함하는 슬러리를 이용하여 세라믹 그린시트를 마련하는 단계;

도전성 금속 페이스트를 이용하여 상기 세라믹 그린시트 상에 내부전극 패턴을 형성하는 단계; 및

상기 세라믹 그린시트를 적층하고 소결하여, 유전체층 및 상기 유전체층을 사이에 두고 서로 대향하도록 배치되며, 폭 방향으로 인쇄폭이 차이가 나도록 교차 적층되는 제1 및 제2 내부 전극을 포함하는 세라믹 본체를 형성하는 단계;를 포함하며,

상기 제1 및 제2 내부전극의 최대폭을 W라 하고, 상기 제1 및 제2 내부전극의 최소폭을 w라고 정의하면,

하기식으로 표현되는 상기 최대폭과 최소폭의 폭 차이율(D)이 20 내지 80%이며, 상기 제1 및 제2 내부전극 중 인쇄폭이 더 넓은 전극의 인쇄폭이 200 내지 250 μm에서 상기 제1 내부전극과 제2 내부전극의 폭 차이율이 20 내지 40%인 적층 세라믹 전자부품의 제조 방법,

[식] D=(W-w)/W×100.

## 청구항 10

제9항에 있어서,

상기 제1 내부전극과 제2 내부전극의 인쇄폭 차이는 100 μm 이하인 적층 세라믹 전자부품의 제조 방법.

#### 청구항 11

제9항에 있어서,

상기 유전체층의 평균 두께는 0.6 μm 이하인 적층 세라믹 전자부품의 제조 방법.

# 청구항 12

제9항에 있어서,

상기 제1 및 제2 내부전극의 평균 두께는 0.6 μm 이하인 적층 세라믹 전자부품의 제조 방법.

#### 청구항 13

삭제

#### 청구항 14

세라믹 분말을 포함하는 슬러리를 이용하여 세라믹 그린시트를 마련하는 단계;

도전성 금속 페이스트를 이용하여 상기 세라믹 그린시트 상에 내부전극 패턴을 형성하는 단계; 및

상기 세라믹 그린시트를 적충하고 소결하여, 유전체충 및 상기 유전체충을 사이에 두고 서로 대향하도록 배치되며, 폭 방향으로 인쇄폭이 차이가 나도록 교차 적충되는 제1 및 제2 내부 전극을 포함하는 세라믹 본체를 형성하는 단계;를 포함하며,

상기 제1 및 제2 내부전극의 최대폭을 W라 하고, 상기 제1 및 제2 내부전극의 최소폭을 w라고 정의하면,

하기식으로 표현되는 상기 최대폭과 최소폭의 폭 차이율(D)이 20 내지 80%이며, 상기 제1 및 제2 내부전극 중 인쇄폭이 더 넓은 전극의 인쇄폭이 300 내지 400 μm에서 상기 제1 내부전극과 제2 내부전극의 폭 차이율이 40 내지 70%인 적층 세라믹 전자부품의 제조 방법,

[식] D=(W-w)/W×100.

#### 청구항 15

세라믹 분말을 포함하는 슬러리를 이용하여 세라믹 그린시트를 마련하는 단계;

도전성 금속 페이스트를 이용하여 상기 세라믹 그린시트 상에 내부전극 패턴을 형성하는 단계; 및

상기 세라믹 그린시트를 적충하고 소결하여, 유전체충 및 상기 유전체충을 사이에 두고 서로 대향하도록 배치되며, 폭 방향으로 인쇄폭이 차이가 나도록 교차 적충되는 제1 및 제2 내부 전극을 포함하는 세라믹 본체를 형성하는 단계;를 포함하며,

상기 제1 및 제2 내부전극의 최대폭을 W라 하고, 상기 제1 및 제2 내부전극의 최소폭을 w라고 정의하면,

하기식으로 표현되는 상기 최대폭과 최소폭의 폭 차이율(D)이 20 내지 80%이며, 상기 제1 및 제2 내부전극 중인쇄폭이 더 넓은 전극의 인쇄폭이 500 μm 이상에서 상기 제1 내부전극과 제2 내부전극의 폭 차이율이 20 내지 80%인 적층 세라믹 전자부품의 제조 방법,

[식] D=(W-w)/W×100.

# 청구항 16

제9항에 있어서.

상기 제1 또는 제2 내부전극의 연결성은 90% 이상인 적층 세라믹 전자부품의 제조 방법.

## 청구항 17

제9항에 있어서.

상기 세라믹 그린 시트의 적층수는 400층 이상인 적층 세라믹 전자부품의 제조 방법.

#### 청구항 18

제9항에 있어서,

상기 도전성 금속은 니켈(Ni), 구리(Cu), 팔라듐(Pd) 및 팔라듐-은(Pd-Ag) 합금으로 이루어진 군으로부터 선택된 하나 이상인 적층 세라믹 전자부품의 제조 방법.

## 명 세 서

# 기술분야

[0001] 본 발명은 단차 영향성을 개선하여 신뢰성이 우수한 대용량 적층 세라믹 전자부품 및 이의 제조방법에 관한 것이다.

# 배경기술

- [0002] 최근, 전자 제품들의 소형화 추세에 따라, 적층 세라믹 전자 부품 역시 소형화되고, 대용량화될 것이 요구되고 있다.

- [0003] 이에 따라 유전체와 내부전극의 박막화, 다층화가 다양한 방법으로 시도되고 있으며, 근래에는 유전체층의 두께는 얇아지면서 적층수가 증가하는 적층 세라믹 전자 부품들이 제조되고 있다.

- [0004] 이러한 대용량화를 구현하기 위해서 유전체층 두께와 내부 전극 층 두께가 얇아질수록 내부전극 도포 두께에 의한 단차 영향성이 커지고 있다.

- [0005] 단차값이 커질수록 내부전극 단차부분의 밀도가 저하되어 크랙 불량이 발생할 수 있다.

- [0006] 또한, 비어있는 단차부를 채워주기 위해 내부전극이 늘어나면서 내부전극의 끊김이 심화 되어 신뢰성이 저하될 수 있다.

- [0007] 한편, 내부 전극 층 두께가 얇아질수록 내부전극층의 두께가 불균일해지고 전극 층이 연속적으로 두께가 유지되면서 연결되지 못하고 부분적으로 끊겨서 연결성이 저하된다.

- [0008] 또한 전극이 끊어지면서 유전체층의 평균 두께는 같지만 부분적으로 두꺼워지거나 얇아지는 부분이 발생되어 유전체층이 얇아진 부분에서 절연특성이 저하되어 신뢰성이 저하되는 문제점이 있었다.

## 선행기술문헌

# 특허문헌

(특허문헌 0001) 한국공개공보 제2011-0074259호

# 발명의 내용

### 해결하려는 과제

[0009] 본 발명은 단차 영향성을 개선하여 신뢰성이 우수한 대용량 적층 세라믹 전자부품 및 이의 제조방법에 관한 것

이다.

# 과제의 해결 수단

- [0010] 본 발명의 일 실시형태는 유전체층을 포함하는 세라믹 본체; 및 상기 세라믹 본체 내에서 상기 유전체층을 사이에 두고 서로 대향하도록 배치되며, 폭 방향으로 인쇄폭이 차이가 나도록 교차 적층되는 제1 및 제2 내부전극; 을 포함하며, 상기 제1 및 제2 내부전극의 최대폭을 W라 하고, 상기 제1 및 제2 내부전극의 최소폭을 w라고 정의하면, 하기식으로 표현되는 상기 최대폭과 최소폭의 폭 차이율(D)이 20 내지 80%인 적층 세라믹 전자부품,

- [0011] [식] D=(W-w)/W×100

- [0012] 을 제공한다.

- [0013] 상기 제1 내부전극과 제2 내부전극의 인쇄폭 차이는 100 μm 이하일 수 있다.

- [0014] 상기 유전체층의 평균 두께는 0.6 µm 이하일 수 있다.

- [0015] 상기 제1 및 제2 내부전극의 평균 두께는 0.6 µm 이하일 수 있다.

- [0016] 상기 제1 및 제2 내부전극 중 인쇄폭이 더 넓은 전극의 인쇄폭이 200 내지 250 µm에서 상기 제1 내부전극과 제 2 내부전극의 폭 차이율이 20 내지 40%일 수 있다.

- [0017] 상기 제1 및 제2 내부전극 중 인쇄폭이 더 넓은 전극의 인쇄폭이 300 내지 400 μm에서 상기 제1 내부전극과 제 2 내부전극의 폭 차이율이 40 내지 70%일 수 있다.

- [0018] 상기 제1 및 제2 내부전극 중 인쇄폭이 더 넓은 전극의 인쇄폭이 500 µm 이상에서 상기 제1 내부전극과 제2 내 부전극의 폭 차이율이 20 내지 80%일 수 있다.

- [0019] 또한, 상기 제1 또는 제2 내부전극의 연결성은 90% 이상일 수 있다.

- [0020] 본 발명의 다른 실시형태는 세라믹 분말을 포함하는 슬러리를 이용하여 세라믹 그린시트를 마련하는 단계; 도전 성 금속 페이스트를 이용하여 상기 세라믹 그린시트 상에 내부전극 패턴을 형성하는 단계; 및 상기 세라믹 그린시트를 적충하고 소결하여, 유전체충 및 상기 유전체충을 사이에 두고 서로 대향하도록 배치되며, 폭 방향으로 인쇄폭이 차이가 나도록 교차 적충되는 제1 및 제2 내부 전극을 포함하는 세라믹 본체를 형성하는 단계;를 포함하며, 상기 제1 및 제2 내부전극의 최대폭을 W라 하고, 상기 제1 및 제2 내부전극의 최소폭을 w라고 정의하면, 하기식으로 표현되는 상기 최대폭과 최소폭의 폭 차이율(D)이 20 내지 80%인 적충 세라믹 전자부품의 제조 방법,

- [0021] [식] D=(W-w)/W×100

- [0022] 을 제공한다.

- [0023] 상기 제1 내부전극과 제2 내부전극의 인쇄폭 차이는 100 μm 이하일 수 있다.

- [0024] 상기 유전체층의 평균 두께는 0.6 µm 이하일 수 있다.

- [0025] 상기 제1 및 제2 내부전극의 평균 두께는 0.6 μm 이하일 수 있다.

- [0026] 상기 제1 및 제2 내부전극 중 인쇄폭이 더 넓은 전극의 인쇄폭이 200 내지 250 µm에서 상기 제1 내부전극과 제 2 내부전극의 폭 차이율이 20 내지 40%일 수 있다.

- [0027] 상기 제1 및 제2 내부전극 중 인쇄폭이 더 넓은 전극의 인쇄폭이 300 내지 400 μm에서 상기 제1 내부전극과 제 2 내부전극의 폭 차이율이 40 내지 70%일 수 있다.

- [0028] 상기 제1 및 제2 내부전극 중 인쇄폭이 더 넓은 전극의 인쇄폭이 500 μm 이상에서 상기 제1 내부전극과 제2 내 부전극의 폭 차이율이 20 내지 80%일 수 있다.

- [0029] 또한, 상기 제1 또는 제2 내부전극의 연결성은 90% 이상일 수 있다.

- [0030] 상기 세라믹 그린 시트의 적층수는 400층 이상일 수 있다.

- [0031] 상기 도전성 금속 페이스트는 금속 분말 40 내지 50 중량부를 포함할 수 있으며, 상기 금속은 니켈(Ni), 구리 (Cu), 팔라듐(Pd) 및 팔라듐-은(Pd-Ag) 합금으로 이루어진 군으로부터 선택된 하나 이상일 수 있다.

# 발명의 효과

[0032] 본 발명에 따르면 정전용량의 대용량화를 구현하면서 단차에 의한 영향성을 줄여 크랙 불량을 감소시키고, 내전 압 특성과 신뢰성이 우수한 대용량 적층 세라믹 전자부품의 구현이 가능하다.

# 도면의 간단한 설명

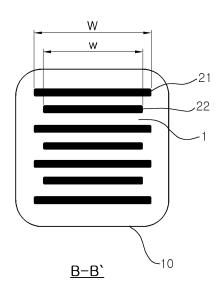

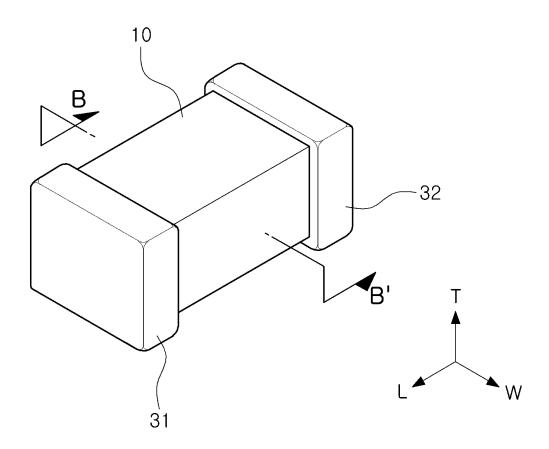

- [0033] 도 1은 본 발명의 일 실시형태에 따른 적층 세라믹 캐패시터를 개략적으로 나타내는 사시도이다.

- 도 2는 본 발명의 일 실시형태에 따른 도 1의 B-B' 단면도이다.

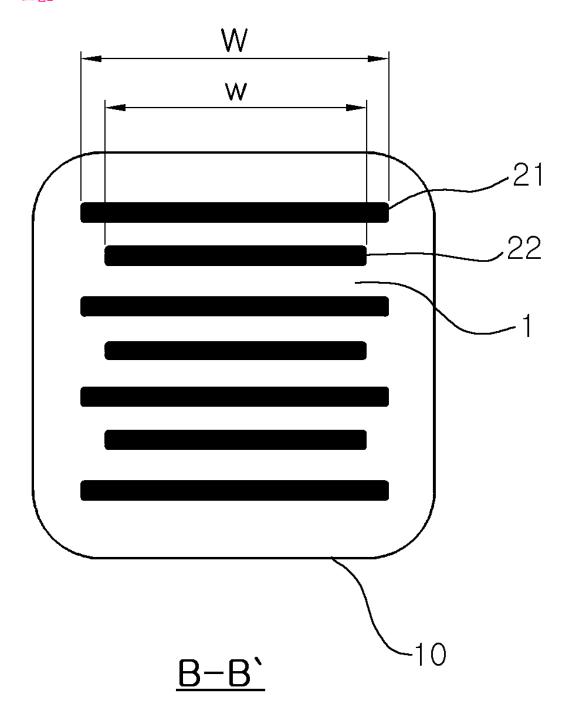

- 도 3은 본 발명의 다른 실시형태에 따른 도 1의 B-B' 단면도이다.

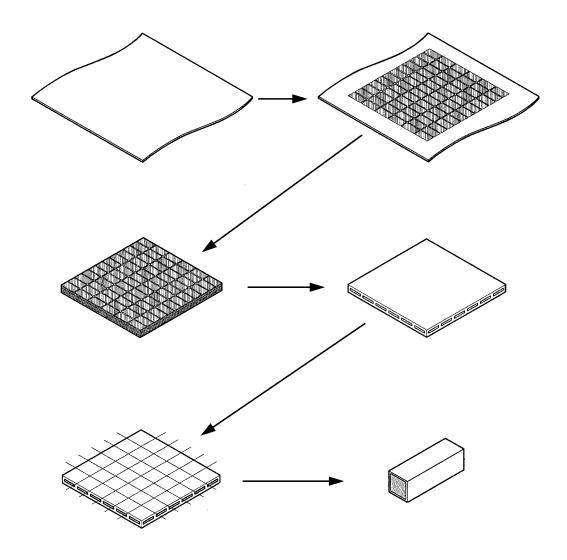

- 도 4는 본 발명의 다른 실시형태에 따른 적층 세라믹 캐패시터의 제조 공정도이다.

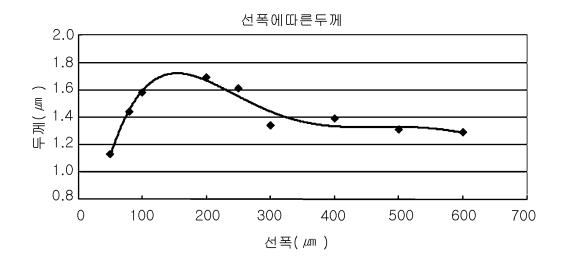

- 도 5는 내부전극의 인쇄폭에 따른 두께를 나타내는 그래프이다.

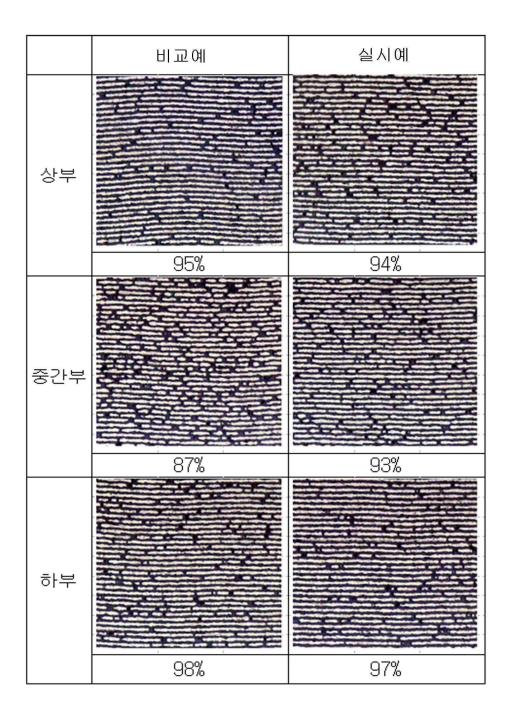

- 도 6은 본 발명의 일 실시예 및 비교예의 내부전극의 영역별 연결성을 나타내는 SEM(Scanning Electron Microscope) 사진이다.

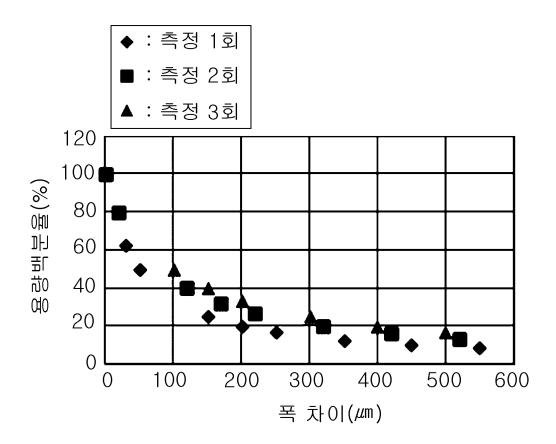

- 도 7은 제1 내부전극과 제2 내부전극의 인쇄폭 차이에 따른 적층 세라믹 커페시터의 정전 용량 백분율을 나타내는 그래프이다.

## 발명을 실시하기 위한 구체적인 내용

[0034] 본 발명의 실시형태는 여러 가지 다른 형태로 변형될 수 있으며, 본 발명의 범위가 이하 설명하는 실시형태로 한정되는 것은 아니다. 또한, 본 발명의 실시형태는 당업계에서 평균적인 지식을 가진 자에게 본 발명을 더욱 완전하게 설명하기 위해서 제공되는 것이다. 따라서, 도면에서의 요소들의 형상 및 크기 등은 보다 명확한 설

명을 위해 과장될 수 있으며, 도면상의 동일한 부호로 표시되는 요소는 동일한 요소이다.

- [0035] 이하, 첨부된 도면을 참조하여 본 발명의 바람직한 실시형태를 설명한다.

- [0036] 도 1은 본 발명의 일 실시형태에 따른 적층 세라믹 캐패시터를 개략적으로 나타내는 사시도이다.

- [0037] 도 2는 본 발명의 일 실시형태에 따른 도 1의 B-B' 단면도이다.

- [0038] 도 3은 본 발명의 다른 실시형태에 따른 도 1의 B-B' 단면도이다.

- [0039] 도 1 및 도 2를 참조하면, 본 발명의 일 실시형태에 따른 적층 세라믹 전자부품은 유전체층(1)을 포함하는 세라 믹 본체(10); 및 상기 세라믹 본체(10) 내에서 상기 유전체층(1)을 사이에 두고 서로 대향하도록 배치되며, 폭 방향으로 인쇄폭이 차이가 나도록 교차 적층되는 제1 및 제2 내부전극(21, 22);을 포함하며, 상기 제1 및 제2 내부전극(21, 22)의 최대폭을 W라 하고, 상기 제1 및 제2 내부전극(21, 22)의 최소폭을 w라고 정의하면, 하기식으로 표현되는 상기 최대폭과 최소폭의 폭 차이율(D)이 20 내지 80%일 수 있다

- [0040] [식] D=(W-w)/W×100.

- [0041] 이하에서는 본 발명의 일 실시형태에 따른 적층 세라믹 전자부품을 설명하되, 특히 적층 세라믹 커패시터로 설명하지만 이에 제한되는 것은 아니다.

- [0042] 상기 세라믹 본체(10)는 특별히 제한되지 않으며, 예를 들어 육면체 형상을 가질 수 있다.

- [0043] 한편, 본 실시 형태의 적층 세라믹 커패시터에 있어서, '길이 방향'은 도 1의 'L' 방향, '폭 방향'은 'W' 방향, '두께 방향'은 'T' 방향으로 정의하기로 한다. 여기서 '두께 방향'은 유전체층를 쌓아 올리는 방향 즉 '적층 방향'과 동일한 개념으로 사용할 수 있다.

- [0044] 본 발명의 일 실시형태에 따른 적층 세라믹 커패시터는 유전체층(1)을 포함하는 세라믹 본체(10); 및 상기 세라 믹 본체(10) 내에서 상기 유전체층(1)을 사이에 두고 서로 대향하도록 배치되며, 폭 방향으로 인쇄폭이 차이가 나도록 교차 적층되는 제1 및 제2 내부전극(21, 22);을 포함할 수 있다.

- [0045] 상기 제1 및 제2 내부전극(21, 22)은 특별히 제한되지 않으며, 예를 들어, 팔라듐(Pd), 팔라듐-은(Pd-Ag) 합금 등의 귀금속 재료 및 니켈(Ni), 구리(Cu) 중 하나 이상의 물질로 이루어진 도전성 페이스트를 사용하여 형성될 수 있다.

- [0046] 정전 용량 형성을 위해 제1 및 제2 외부전극(31, 32)이 상기 세라믹 본체(10)의 외측에 형성될 수 있으며, 상기 제1 및 제2 내부전극(21, 22)과 전기적으로 연결될 수 있다.

- [0047] 상기 제1 및 제2 외부전극(31, 32)은 내부전극과 동일한 재질의 도전성 물질로 형성될 수 있으나 이에 제한되지는 않으며, 예를 들어, 구리(Cu), 은(Ag), 니켈(Ni) 등으로 형성될 수 있다.

- [0048] 상기 제1 및 제2 외부전극(31, 32)은 상기 금속 분말에 글라스 프릿을 첨가하여 마련된 도전성 페이스트를 도포한 후 소성함으로써 형성될 수 있다.

- [0049] 본 발명의 일 실시형태에 따르면, 상기 제1 및 제2 내부전극(21, 22)은 상기 세라믹 본체(10) 내에서 폭 방향으로 인쇄폭이 차이가 나도록 교차 적충될 수 있다.

- [0050] 상기 제1 및 제2 내부전극(21, 22)이 폭(W) 방향으로 인쇄폭이 차이가 나도록 교차 적충함으로써, 단차에 영향을 미치는 내부전극 간의 거리를 길게 함으로써, 단차 영향을 개선할 수 있다.

- [0051] 즉, 적층 세라믹 커패시터의 대용량화를 구현하기 위해서 유전체층 두께와 내부 전극 층 두께가 얇아질수록 내부전극 도포 두께에 의한 단차값이 크게 되며, 상기 단차값이 커질수록 내부전극 단차부분의 밀도가 저하되어 크랙 불량이 발생할 수 있다.

- [0052] 또한, 비어있는 단차부를 채워주기 위해 내부전극이 늘어나면서 내부전극의 끊김이 심화 되어 신뢰성이 저하될 수 있다.

- [0053] 본 발명의 일 실시형태에 따르면, 상기 제1 및 제2 내부전극(21, 22)이 폭(W) 방향으로 인쇄폭이 차이가 나도록 교차 적층함으로써 상기의 문제점을 해결할 수 있어, 크랙 불량을 감소시킬 수 있다.

- [0054] 본 발명의 일 실시형태에 따르면, 상기 제1 및 제2 내부전극(21, 22)의 최대폭을 W라 하고, 상기 제1 및 제2 내부전극(21, 22)의 최소폭을 w라고 정의하면, 하기식으로 표현되는 상기 최대폭과 최소폭의 폭 차이율(D=(W-w)/W ×100)이 20 내지 80%일 수 있다.

- [0055] 상기 제1 내부전극(21)과 제2 내부전극(22)의 최대폭과 최소폭의 폭 차이율(D)은 최대폭에 대한 최대폭과 최소폭의 차이의 백분율로 정의될 수 있다.

- [0056] 즉, 최대폭을 W라 하고, 최소폭을 w라 할면, 폭 차이율(D)= (W-w)/W×100의 식으로 정의될 수 있다.

- [0057] 상기 제1 내부전극(21)과 제2 내부전극(22)의 폭 차이율(D)은 단차 영향을 최소화시키기 위한 본 발명의 목적에 따라 다양하게 변화시킬 수 있으며, 예를 들어 20 내지 80%일 수 있다.

- [0058] 상기 제1 및 제2 내부전극(21, 22) 중 인쇄폭이 더 넓은 전극은 제1 전극일 수도 있고, 제2 전극일 수도 있다.

- [0059] 인쇄폭이 더 넓은 전극이 제1 전극일 경우가 도 2에 도시되어 있으며, 인쇄폭이 더 넓은 전극이 제2 전극일 경우가 도 3에 도시되어 있다.

- [0060] 도 2를 참조하면, 본 발명의 일 실시형태에 따른 적충 세라믹 커패시터의 내부전극에 있어서, 제1 내부전극(2 1)의 인쇄폭이 더 넓을 수 있으며, 도 3을 참조하면, 본 발명의 다른 실시형태에 따른 적충 세라믹 커패시터의 내부전극은 제2 내부전극(22)의 인쇄폭이 더 넓을 수 있다.

- [0061] 구체적으로, 상기 제1 및 제2 내부전극(21, 22) 중 인쇄폭이 더 넓은 전극의 인쇄폭이 200 내지 250 µm일 경우에 상기 제1 내부전극(21)과 제2 내부전극(22)의 폭 차이율은 20 내지 40%일 수 있다.

- [0062] 상기와 같이 폭 차이율이 20 내지 40%일 경우에 정전 용량을 유지하면서도 단차에 의한 영향이 줄어들어 크랙 불량을 감소시킬 수 있으며, 전극 늘어남이 억제되어 내전압 향상 및 신뢰성도 우수한 적층 세라믹 커패시터를 구현할 수 있다.

- [0063] 상기 인쇄폭이 더 넓은 전극의 인쇄폭이 200 내지 250 µm일 경우에 상기 폭 차이율이 20% 미만의 경우에는 단 차 영향의 감소 효과가 적어 크랙 불량 발생의 문제가 발생할 수 있다.

- [0064] 또한, 상기 인쇄폭이 더 넓은 전극의 인쇄폭이 200 내지 250 μm일 경우에 상기 폭 차이율이 40%를 초과하는 경 우에는 정전 용량 감소의 문제가 발생할 수 있다.

- [0065] 한편, 상기 제1 및 제2 내부전극(21, 22) 중 인쇄폭이 더 넓은 전극의 인쇄폭이 300 내지 400 µm일 경우에 상기 제1 내부전극(21)과 제2 내부전극(22)의 폭 차이율은 40 내지 70%일 수 있다.

- [0066] 상기와 같이 폭 차이율이 40 내지 70%일 경우에 정전 용량을 유지하면서도 단차에 의한 영향이 줄어들어 크랙 불량을 감소시킬 수 있으며, 전극 늘어남이 억제되어 내전압 향상 및 신뢰성도 우수한 적층 세라믹 커패시터를 구현할 수 있다.

- [0067] 상기 인쇄폭이 더 넓은 전극의 인쇄폭이 300 내지 400 µm일 경우에 상기 폭 차이율이 40% 미만의 경우에는 단 차 영향의 감소 효과가 적어 크랙 불량 발생의 문제가 발생할 수 있다.

- [0068] 또한, 상기 인쇄폭이 더 넓은 전극의 인쇄폭이 300 내지 400 µm일 경우에 상기 폭 차이율이 70%를 초과하는 경우에는 정전 용량 감소의 문제가 발생할 수 있다.

- [0069] 상기 제1 및 제2 내부전극(21, 22) 중 인쇄폭이 더 넓은 전극의 인쇄폭이 500 μm 이상일 경우, 상기 제1 내부 전극(21)과 제2 내부전극(22)의 폭 차이율은 20 내지 80%일 수 있다.

- [0070] 상기와 같이 폭 차이율이 20 내지 80%일 경우에 정전 용량을 유지하면서도 단차에 의한 영향이 줄어들어 크랙 불량을 감소시킬 수 있으며, 전극 늘어남이 억제되어 내전압 향상 및 신뢰성도 우수한 적층 세라믹 커패시터를 구현할 수 있다.

- [0071] 상기 인쇄폭이 더 넓은 전극의 인쇄폭이 500 µm 이상일 경우에 상기 폭 차이율이 20% 미만의 경우에는 단차 영향의 감소 효과가 적어 크랙 불량 발생의 문제가 발생할 수 있다.

- [0072] 또한, 상기 인쇄폭이 더 넓은 전극의 인쇄폭이 500 µm 이상일 경우에 상기 폭 차이율이 80%를 초과하는 경우에는 정전 용량 감소의 문제가 발생할 수 있다.

- [0073] 또한, 상기 제1 내부전극(21)과 제2 내부전극(22)의 인쇄폭 차이는 특별히 제한되는 것은 아니나, 예를 들어 100 µm 이하일 수 있다.

- [0074] 상기 인쇄폭 차이가 100 µm 이하인 경우에 크랙 불량을 감소 및 내전압 특성과 신뢰성이 우수한 효과뿐만 아니라, 적층 세라믹 커패시터의 정전 용량 구현도 가능하다.

- [0075] 즉, 상기 인쇄폭 차이가 100 μm를 초과하는 경우에는 적층 세라믹 커패시터의 정전 용량이 50% 이상 저하되는 문제가 발생할 수 있다.

- [0076] 따라서, 본 발명의 일 실시형태에 따른 적층 세라믹 커패시터는 상기 제1 내부전극(21)과 제2 내부전극(22)의 인쇄폭 차이가 100 μm 이하일 수 있다.

- [0077] 본 발명의 일 실시형태에 따르면, 상기 유전체층(1)의 평균 두께는 0.6 µm 이하일 수 있다.

- [0078] 본 발명의 일 실시형태에서, 상기 유전체층(1)의 두께는 내부 전극층(21, 22) 사이에 배치되는 유전체층(1)의 평균 두께를 의미할 수 있다.

- [0079] 상기 유전체층(1)의 평균 두께는 도 2와 같이 세라믹 본체(10)의 폭 방향 단면을 주사전자현미경(SEM, Scanning Eletron Microscope)으로 이미지를 스캔하여 측정할 수 있다.

- [0080] 예를 들어, 도 2와 같이 세라믹 본체(10)의 길이(L) 방향의 중앙부에서 절단한 폭 및 두께 방향(W-T) 단면을 주 사전자현미경(SEM, Scanning Eletron Microscope)로 스캔한 이미지에서 추출된 임의의 유전체층에 대해서, 폭 방향으로 등간격인 30개의 지점에서 그 두께를 측정하여 평균값을 측정할 수 있다.

- [0081] 상기 등간격인 30개의 지점은 제1 및 제2 내부전극(21, 22)이 중첩되는 영역을 의미하는 용량 형성부에서 측정될 수 있다.

- [0082] 또한, 이러한 평균값 측정을 10개 이상의 유전체층으로 확장하여 평균값을 측정하면, 유전체층의 평균 두께를 더욱 일반화할 수 있다.

- [0083] 상기 유전체층(1)의 평균 두께가 0.6 μm 이하인 경우에는 상기 제1 및 제2 내부전극(21, 22)의 연결성이 저하될 수 있으나, 본 발명의 일 실시형태에 따르면 폭(W) 방향으로 인쇄폭이 차이가 나도록 교차 적층함으로써, 단차 영향을 최소화하여 내부전극의 연결성을 높일 수 있다.

- [0084] 또한, 상기 유전체층(1)의 평균 두께가 0.6 μm 이하인 경우에는 전극이 끊어지면서 유전체층의 평균 두께는 같지만 부분적으로 두꺼워지거나 얇아지는 부분이 발생되어 유전체층이 얇아진 부분에서 내전압특성이 저하되어 신뢰성이 저하될 수 있으나, 본 발명의 일 실시형태에 따르면 내부전극의 연결성을 높임으로써 내전압특성이 향상될 수 있다.

- [0085] 한편, 상기 유전체층(1)의 평균 두께가 0.6 µm를 초과하는 경우에는 유전체층의 평균 두께가 두꺼워서 상기와 같은 내전압특성 및 신뢰성에 문제가 없을 수 있다.

- [0086] 상기 제1 및 제2 내부전극(21, 22)의 소성후 평균 두께는 정전용량을 형성할 수 있다면 특별히 제한은 없으며, 예를 들어, 0.6  $\mu$ m 이하일 수 있다.

- [0087] 본 발명의 일 실시형태에 따른 적층 세라믹 전자부품에 있어서 상기 제1 또는 제2 내부전국(21, 22)의 연결성은 90% 이상일 수 있다.

- [0088] 상기 내부전극의 연결성이란, 상기 제1 또는 제2 내부전극(21, 22)의 전체 전극 길이 대비 실제 전극이 형성된 부분의 길이로 정의될 수 있다.

- [0089] 예를 들어, 상기 내부전극의 연결성은 도 2와 같이 적충 본체(10)의 폭 방향 단면을 주사전자현미경(SEM, Scanning Eletron Microscope)로 이미지를 스캔하여 측정할 수 있다.

- [0090] 구체적으로, 도 2와 같이 적층 본체(10)의 길이(L) 방향의 중앙부에서 절단한 폭 및 두께 방향(W-T) 단면을 주 사전자현미경(SEM, Scanning Eletron Microscope)으로 스캔한 이미지에서 추출된 임의의 내부전극층에 대해서, 내부전극 단면의 전체 길이 대비 실제 내부 전극이 형성된 부분의 총 길이를 측정하여 구할 수 있다.

- [0091] 상기 제1 및 제2 내부전극의 연결성 측정은 제1 및 제2 내부전극(21, 22)이 중첩되는 영역을 의미하는 용량 형성부에서 측정될 수 있다.

- [0092] 또한, 이러한 내부전극층의 연결성 측정을 상기 길이 및 두께 방향(L-T) 단면의 중앙부의 10개 이상의 내부전극 층으로 확장하여 평균값을 측정하면, 내부전극층의 연결성을 더욱 일반화할 수 있다.

- [0093] 구체적으로, 제1 및 제2 내부전극(21, 22)의 어느 한 지점에서 측정된 전체 전극 길이를 A 및 실제 전극이 형성된 부분의 길이를 c1, c2, c3, · cn으로 규정하면, 상기 제1 및 제2 내부전극의 연결성은 (c1 + c2 + c3 + · + cn) / A로 표현될 수 있다.

- [0094] 또한, 이는 내부 전극의 도포 비율을 의미하는 것으로서, 상기 임의의 한 지점에서의 내부 전극의 전체 면적 대비 실제 내부 전극이 형성된 면적의 비율로도 정의할 수 있다.

- [0095] 상기 제1 또는 제2 내부전극(21, 22)의 연결성은 후술하는 방법들에 따라 다양하게 구현될 수 있으며, 본 발명의 일 실시형태에 따른 적층 세라믹 전자부품의 제1 또는 제2 내부전극의 연결성은 90% 이상이다.

- [0096] 제1 또는 제2 내부전극(21, 22)의 연결성을 90% 이상 구현하기 위한 방법으로는 내부전극을 형성하는 도전성 페이스트에서 메탈 파우더의 입자 크기를 변화시키거나 첨가하는 유기물과 세라믹의 양을 조절하는 방법 등이 있다.

- [0097] 그리고, 소성 공정에서 승온 속도와 소성 분위기를 조절하여 전극 연결성을 제어하는 것이 가능하다.

- [0098] 본 발명의 일 실시형태에 따르면, 상기 내부전극 층의 연결성을 구현하기 위하여, 상기 용량 형성부의 제1 및 제2 내부전극에 대하여 폭(W) 방향으로 인쇄폭이 차이가 나도록 교차 적층함으로써, 단차 영향을 최소화하는 방법을 사용할 수 있다.

- [0099] 본 발명의 일 실시형태에 따르면, 상기 제1 또는 제2 내부전극(21, 22)의 연결성을 90% 이상 구현함으로써, 정전 용량이 증가하고 신뢰성이 우수한 고용량 적층 세라믹 커패시터의 제조가 가능하다.

- [0100] 도 4는 본 발명의 다른 실시형태에 따른 적층 세라믹 커패시터의 제조 공정도이다.

- [0101] 도 4를 참조하면, 본 발명의 다른 실시형태에 따른 적층 세라믹 전자부품의 제조방법은 세라믹 분말을 포함하는 슬러리를 이용하여 세라믹 그린시트를 마련하는 단계; 도전성 금속 페이스트를 이용하여 상기 세라믹 그린시트 상에 내부전극 패턴을 형성하는 단계; 및 상기 세라믹 그린시트를 적층하고 소결하여, 유전체층 및 상기 유전체 층을 사이에 두고 서로 대향하도록 배치되며, 폭 방향으로 인쇄폭이 차이가 나도록 교차 적층되는 제1 및 제2 내부 전극을 포함하는 세라믹 본체를 형성하는 단계;를 포함하며, 상기 제1 및 제2 내부전극의 최대폭을 W라 하고, 상기 제1 및 제2 내부전극의 최소폭을 w라고 정의하면,

- [0102] 하기식으로 표현되는 상기 최대폭과 최소폭의 폭 차이율(D)이 20 내지 80%일 수 있다

- [0103] [식] D=(W-w)/W×100.

- [0104] 상기 유전체층의 평균 두께는 0.6 μm 이하일 수 있으며, 상기 제1 및 제2 내부전극의 평균 두께는 0.6 μm 이하일 수 있다.

- [0105] 상기 제1 및 제2 내부전극 중 인쇄폭이 더 넓은 전극의 인쇄폭이 200 내지 250 µm에서 상기 제1 내부전극과 제 2 내부전극의 폭 차이율이 20 내지 40%일 수 있다.

- [0106] 상기 제1 및 제2 내부전극 중 인쇄폭이 더 넓은 전극의 인쇄폭이 300 내지 400 μm에서 상기 제1 내부전극과 제 2 내부전극의 폭 차이율이 40 내지 70%일 수 있다.

- [0107] 상기 제1 및 제2 내부전극 중 인쇄폭이 더 넓은 전극의 인쇄폭이 500 μm 이상에서 상기 제1 내부전극과 제2 내 부전극의 폭 차이율이 20 내지 80%일 수 있다.

- [0108] 또한, 상기 제1 또는 제2 내부전극의 연결성은 90% 이상일 수 있다.

- [0109] 상기 세라믹 그린 시트의 적층수는 특별히 제한되지 않으며, 고용량 적층 세라믹 전자부품의 제조를 위하여 예를 들어 400층 이상일 수 있다.

- [0110] 상기 적층수가 400층 미만일 경우에는 유전체층 및 내부전극층의 두께가 두꺼워 내부전극의 연결성의 문제 및 내전압 특성의 문제가 발생하지 않을 수 있다.

- [0111] 즉, 상기 적충수가 400충 이상일 경우에만 유전체충의 두께가 얇아져서 내부전극의 연결성이 문제되고 이로 인하여 내전압 특성이 저하되는 문제가 있을 수 있으며, 본 발명의 일 실시형태에 따르면, 상기 제1 및 제2 내부전극(21, 22)이 폭(W) 방향으로 인쇄폭이 차이가 나도록 교차 적충함으로써, 크랙 발생 감소, 내부전극의 연결성 및 내전압 특성을 향상시킬 수 있다.

- [0112] 상기 도전성 금속 페이스트는 특별히 제한되지 않으며, 예를 들어 금속 분말 40 내지 50 중량부를 포함할 수 있으며, 상기 금속은 니켈(Ni), 구리(Cu), 팔라듐(Pd) 및 팔라듐-은(Pd-Ag) 합금으로 이루어진 군으로부터 선택된하나 이상일 수 있다.

- [0113] 상기의 실시형태에 따른 적층 세라믹 전자부품의 제조방법은 상기 제1 내부전극과 제2 내부전극의 폭 차이율이 20 내지 80%가 되도록, 상기 제1 내부전극과 제2 내부전극을 폭 방향으로 인쇄폭이 차이가 나게 교차 적층한 것을 제외하고는 일반적인 방법과 동일하다.

- [0114] 상기 제조방법에 의해 제조된 적층 세라믹 전자부품은 내부전극 간의 단차 영향이 최소화되어 크랙 발생이 감소하고, 내부전극의 연결성이 높아지므로, 내전압 특성과 신뢰성이 우수한 적층 세라믹 전자부품을 구현할 수있다.

- [0115] 이하, 실시예를 들어 본 발명을 더욱 상세히 설명하지만, 본 발명이 이에 의해 제한되는 것은 아니다.

- [0116] 본 실시예는 0.6 μm 이하의 평균 두께를 갖는 유전체층(1)을 적용한 적층 세라믹 캐패시터에 대해, 제1 내부전 극과 제2 내부전극의 폭 차이율이 20 내지 80%가 되도록 교차 적층함으로써, 크랙 발생, 내전압 및 신뢰성 향상 여부를 시험하기 위해 수행되었다.

- [0117] 본 실시예에 따른 적층 세라믹 캐패시터는 하기와 같은 단계로 제작되었다.

- [0118] 우선, 평균 입경이 0.1μm인 티탄산바륨(BaTiO<sub>3</sub>) 등의 파우더를 포함하여 형성된 슬러리를 캐리어 필름(carrier film)상에 도포 및 건조하여 1.05μm 및 0.95μm의 두께로 제조된 복수 개의 세라믹 그린 시트를 마련하며, 이로써 유전체층(1)을 형성하게 된다.

- [0119] 다음으로, 니켈 입자 평균 크기가 0.1 내지 0.2 µm이며, 40 내지 50 중량부의 니켈 분말을 포함하는 내부전극용 도전성 페이스트를 마련하였다.

- [0120] 상기 그린시트 상에 상기 내부전극용 도전성 페이스트를 스크린 인쇄공법으로 도포하여 내부전극을 형성한 후 400 내지 500층 적층하여 적층체를 만들었다.

- [0121] 이후 압착, 절단하여 1005 규격의 Size의 칩을 만들며, 상기 칩을 H₂ 0.1%이하의 환원 분위기의 온도 1050~1200 ℃에서 소성하였다.

- [0122] 다음으로, 외부전극, 도금 등의 공정을 거쳐 적층 세라믹 캐패시터로 제작하였다.

- [0123] 비교예는 제1 및 제2 내부전극 간의 인쇄폭에 있어서, 차이가 없도록 제작한 것을 제외하고는 상기 실시예에 의한 방법과 동일하게 제작하였다.

- [0124] 아래의 표 1은 세라믹 그런 시트의 두께 및 적층수에 따른 단차율을 비교한 표이다.

丑 1

[0125]

|     | 시트 두께(μm) | 적층수 | 단차율(%) | 비고(내부전극 도포<br>두께, µm) |

|-----|-----------|-----|--------|-----------------------|

|     | 0.5       | 500 | 50.0   |                       |

| 비교예 | 0.7       | 400 | 41.7   |                       |

|     | 1.0       | 300 | 33.3   | 0.5                   |

|     | 0.5       | 500 | 25.0   |                       |

| 실시예 | 0.7       | 400 | 20.8   |                       |

|     | 1.0       | 300 | 16.7   |                       |

- [0126] 상기 [표 1]을 참조하면, 비교예는 동일한 그린 시트 두께 및 적충수에 대하여 실시예에 비하여 단차율이 큰 것을 알 수 있다.

- [0127] 즉, 본 발명의 일 실시형태에 따른 적충 세라믹 커패시터의 경우 제1 내부전극과 제2 내부전극의 폭 차이율이 20 내지 80%가 되도록 교차 적충함으로써, 단차율이 감소하였음을 알 수 있다.

- [0128] 상기 단차율(%)은 (내부전극의 두께 × 적층수) / {(그린시트의 두께 + 내부전극의 두께) × 적층수}에 의하여 구할 수 있다.

- [0129] 도 5는 내부전극의 인쇄폭에 따른 두께를 나타내는 그래프이다.

- [0130] 도 5를 참조하면, 내부전극의 인쇄폭과 인쇄 두께 사이에는 인쇄폭이 작아질수록 인쇄 두께가 증가하는 경향이 있을 수 있으며, 인쇄폭은 정전 용량과도 관련이 있으므로, 용량 및 두께비를 고려하여 인쇄폭이 차이가 나도록 교차 적층할 수 있다.

- [0131] 아래의 표 2는 내부전극의 인쇄폭이 차이가 나도록 교차 적층할 경우 두께비를 비교한 표이다.

[0132]

| <u>#</u> 2    |          |      |      |       |       |       |       |       |      |      |

|---------------|----------|------|------|-------|-------|-------|-------|-------|------|------|

|               | 좁은 폭(µm) |      |      |       |       |       |       |       |      |      |

|               |          | 50   | 80   | 100   | 200   | 250   | 300   | 400   | 500  | 600  |

| 넓은 폭.<br>(µm) | 50       | 0.00 | -    | -     | -     | -     | -     | -     | _    | -    |

|               | 80       | 0.11 | 0.00 | _     | _     | _     | _     | _     | _    | _    |

|               | 100      | 0.14 | 0.04 | 0.00  | -     | -     | -     | _     | _    | -    |

|               | 200      | 0.17 | 0.07 | 0.03  | 0.00  | _     | _     | _     | _    | _    |

|               | 250      | 0.15 | 0.05 | 0.01  | -0.02 | 0.00  | -     | _     | _    | -    |

|               | 300      | 0.08 | 0.04 | -0.09 | -0.13 | -0.10 | 0.00  | _     | _    | -    |

|               | 400      | 0.09 | 0.05 | 0.01  | -0.11 | -0.08 | 0.02  | 0.00  | _    | -    |

|               | 500      | 0.07 | 0.02 | -0.10 | -0.15 | -0.11 | -0.01 | -0.03 | 0.00 | -    |

|               | 600      | 0.06 | 0.04 | 0.01  | -0.16 | -0.12 | -0.02 | -0.04 | 0.01 | 0.00 |

$\mathbf{E} \circ$

- [0133] 상기 [표 2]를 참조하면 두께비가 음(-)의 값을 가질 때가 단차 영향을 최소화할 수 있는 경우이며, 이에 따라 단차 영향을 최소화할 수 있는 폭 변화율을 나타낼 수 있다.

- [0134] 즉, 상기 제1 및 제2 내부전극 중 인쇄폭이 더 넓은 전극의 인쇄폭이 200 내지 250 µm에서 상기 제1 내부전극 과 제2 내부전극의 폭 차이율이 20 내지 40%일 수 있다.

- [0135] 상기 제1 및 제2 내부전극 중 인쇄폭이 더 넓은 전극의 인쇄폭이 300 내지 400 μm에서 상기 제1 내부전극과 제 2 내부전극의 폭 차이율이 40 내지 70%일 수 있다.

- [0136] 상기 제1 및 제2 내부전극 중 인쇄폭이 더 넓은 전극의 인쇄폭이 500 μm 이상에서 상기 제1 내부전극과 제2 내 부전극의 폭 차이율이 20 내지 80%일 수 있다.

- [0137] 아래의 표 3은 본 발명의 실시예 및 비교예에 따른 크랙 불량 발생율, 정전용량, 내전압 및 고온 가속수명 고장

률을 비교한 표이다.

丑 3

| 구분  | 크랙불량율(%) | 정전용량(μF) | 내전압(V)     | 고온 가속 수명      |

|-----|----------|----------|------------|---------------|

|     |          |          |            | 고장률(Fit)      |

| 비교예 | 5        | 12.7     | 40         | 14            |

| 실시예 | 2        | 11.8     | 43         | 6             |

|     | 비교예      | 비교예 5    | 비교예 5 12.7 | 비교예 5 12.7 40 |

- [0139] 상기 [표 3]을 참조하면, 본 발명의 일 실시예에 따른 적충 세라믹 커패시터의 경우가 비교예에 비하여 정전 용량은 다소 감소하나, 크랙 발생율이 5%에서 2%로 감소하였으며, 내전압이 향상되고 신뢰성도 우수함을 알 수 있다.

- [0140] 도 6은 본 발명의 일 실시예 및 비교예의 내부전극의 영역별 연결성을 나타내는 SEM(Scanning Electron Microscope) 사진이다.

- [0141] 도 6을 참조하면, 본 발명의 일 실시형태에 따른 적층 세라믹 커패시터의 경우가 비교예에 비하여 내부전극의 연결성이 90% 이상으로서, 전극 연결성이 전체 영역에서 고른 것을 알 수 있다.

- [0142] 도 7은 제1 내부전극과 제2 내부전극의 인쇄폭 차이에 따른 적충 세라믹 커패시터의 정전 용량 백분율을 나타내는 그래프이다.

- [0143] 도 7을 참조하면, 상기 인쇄폭 차이가 100 µm를 초과하는 경우에는 적충 세라믹 커패시터의 정전 용량이 50% 이상 저하되어 문제가 있음을 알 수 있다.

- [0144] 따라서, 본 발명의 일 실시형태에 따르면, 제1 내부전극과 제2 내부전극의 인쇄폭 차이는 100 µm이하일 수 있다.

- [0145] 결론적으로, 본 발명의 일 실시형태에 따른 적층 세라믹 전자부품은 내부전극 간의 단차 영향이 최소화되어 크 랙 발생이 감소하고, 내부전극의 연결성이 높아지므로, 내전압 특성과 신뢰성이 우수한 적층 세라믹 전자부품을 구현할 수 있다.

- [0146] 본 발명은 상술한 실시형태 및 첨부된 도면에 의해 한정되는 것이 아니며, 첨부된 청구범위에 의해 한정하고자한다. 따라서, 청구범위에 기재된 본 발명의 기술적 사상을 벗어나지 않는 범위 내에서 당 기술분야의 통상의지식을 가진 자에 의해 다양한 형태의 치환, 변형 및 변경이 가능할 것이며, 이 또한 본 발명의 범위에 속한다고 할 것이다.

#### 부호의 설명

[0147] 1: 유전체 층 10: 세라믹 본체

21, 22: 제1 및 제2 내부전극

31, 32: 외부 전극

도면4