(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5295507号

(P5295507)

(45) 発行日 平成25年9月18日(2013.9.18)

(24) 登録日 平成25年6月21日(2013.6.21)

(51) Int.Cl.

H01L 31/10 (2006.01)

G02F 1/1335 (2006.01)

F 1

H01L 31/10

G02F 1/1335

A

請求項の数 6 (全 24 頁)

(21) 出願番号 特願2007-45052 (P2007-45052)

(22) 出願日 平成19年2月26日 (2007.2.26)

(65) 公開番号 特開2008-209559 (P2008-209559A)

(43) 公開日 平成20年9月11日 (2008.9.11)

審査請求日 平成22年1月26日 (2010.1.26)

(73) 特許権者 598172398

株式会社ジャパンディスプレイウェスト

愛知県知多郡東浦町大字緒川字上舟木50

番地

(74) 代理人 100092152

弁理士 服部 肇

(72) 発明者 小橋 裕

長野県安曇野市豊科田沢6925 エプソ

ンイメージングデバイス株式会社内

審査官 濱田 聖司

最終頁に続く

(54) 【発明の名称】半導体装置、表示装置および電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の基板上に形成され、複数の受光部と複数のアノード領域と複数のカソード領域を含む光センサーと、前記光センサーに外光を取り入れるために前記第1の基板に対向配置される第2の基板上に設けられた遮光層の一部を除去する形で前記光センサーと重なる位置に形成された長方形の受光開口部と、前記複数のアノード領域に共通して接続されるアノード配線と、前記複数のカソード領域に共通して接続されるカソード配線と、を備えた半導体装置であって、

前記光センサーは、前記受光部が前記アノード領域と前記カソード領域に平面的に挟まれて構成され、前記受光部と前記アノード領域との接合面および前記受光部と前記カソード領域との接合面を有した複数のフォトダイオードからなり、

前記受光部と前記アノード領域との接合面および前記受光部と前記カソード領域との接合面は、平面的に前記受光開口部の短手方向に対して平行になるように形成され、

前記アノード配線および前記カソード配線は、前記受光開口部とは平面視で重ならないように配置され、前記複数の受光部、前記複数のアノード領域、および前記複数のカソード領域の周囲に形成される

ことを特徴とする半導体装置。

## 【請求項 2】

前記受光部、前記アノード領域および前記カソード領域は、同一のポリシリコン薄膜か

10

20

ら構成され、

前記アノード領域は、高濃度のボロンイオンをドープして形成され、

前記カソード領域は、高濃度のリンイオンをドープして形成される

ことを特徴とする請求項 1 に記載の半導体装置。

【請求項 3】

前記アノード配線および前記カソード配線は遮光性の金属を含む

ことを特徴とする請求項 1 又は 2 に記載の半導体装置。

【請求項 4】

前記光センサーは、前記複数のフォトダイオードが並列に接続されてなる

ことを特徴とする請求項 1 に記載の半導体装置。

10

【請求項 5】

請求項 1 ~ 4 のいずれか一項に記載の半導体装置を用いた表示装置。

【請求項 6】

請求項 5 に記載の表示装置を用いた電子機器。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、例えば、光センサーを備えた半導体装置、この半導体装置を用いた表示装置

およびこの表示装置を備える電子機器に関する。

【背景技術】

20

【0002】

近年、表示装置上、特に薄膜トランジスターを用いた液晶表示装置において光センサー機能を搭載する技術の開発が進んでいる（例えば特許文献 1）。光センサーを搭載する目的は（1）外光を測定して輝度等を調整することで消費電力低減・画質向上を図る、（2）バックライトを測定し輝度あるいは色度を調整する、（3）指やライトペンの位置を認識しタッチキーとして使用する、の 3 つがあげられる。光センサーとしては PIN ダイオード、PN ダイオードなどがあげられる。いずれの場合も受光部はシリコン薄膜であって、製造上のコストを増大させないため、表示のスイッチング素子を構成するシリコン薄膜と同一製造工程で製造されることが望ましい。このように製造されたフォトセンサーは感度が低いため、面積あたりの素子サイズをなるべく大きくする必要がある。

30

【0003】

また、光センサーの角度依存性は重要な性能要素である。理想的な状態では平面的な構造をもつこれらの光センサーの角度依存性は  $\cos \theta$  で表される。ここで  $\theta$  は表示装置を構成する基板の法線方向を 0 度とした角度である。この角度依存性が理想状態より狭いと、拡散光条件下では光センサーの感度が低下する。また平行光線下で（1）の目的で使用する場合、特に斜め方向から光が当たる時に本来ある状態より周囲が暗いと判定され、輝度を本来の最適値より暗く設定してしまうのである。

【0004】

【特許文献 1】米国特許第 5 831693 号明細書

40

【発明の開示】

【発明が解決しようとする課題】

【0005】

本発明は面積あたりの素子サイズを向上させて光電流の S / N 比を向上させるとともに、光センサーの角度依存性を向上させる構成を提案するものである。

【課題を解決するための手段】

【0006】

本発明の半導体装置は、基板上に形成され、複数の受光部と複数のアノード領域と複数のカソード領域を含む光センサーと、前記光センサーに前記基板周辺の外光を取り入れるための受光開口部を備えた半導体装置であって、前記光センサーは、前記受光部が前記アノード領域と前記カソード領域に平面的に挟まれて構成され、前記受光部と前記アノード

50

領域との接合面および前記受光部と前記カソード領域との接合面を有したフォトダイオードからなることを特徴とする。このように構成すると、フォトダイオードを櫛歯状に形成して面積あたりの接合面面積を増やすことが出来るので光電流量を増大させることができ、受光部に挟まれたアノード領域・カソード領域に金属配線がないために角度依存性がないフォトダイオードを備えた光センサーを実現できる。また、上記の半導体装置は、前記複数のアノード領域に共通して接続されるアノード配線と、前記複数のカソード領域に共通して接続されるカソード配線と、をさらに備えていてもよい。さらに、前記アノード配線および前記カソード配線は、前記光センサーの受光面に対向配置された前記受光開口部とは平面視で対向せず、前記複数の受光部、前記複数のアノード領域、および前記複数のカソード領域の周囲に形成されていてもよい。

10

#### 【0007】

また、前記受光部、前記アノード領域および前記カソード領域は、同一のポリシリコン薄膜から構成され、それぞれ、ドープ濃度の違いにより分離されることを特徴とする。なお、前記アノード領域は、高濃度のボロンイオンをドープして形成されてもよいし、前記カソード領域は、高濃度のリンイオンをドープして形成されてもよい。この構成により、容易に、フォトダイオードを櫛歯状に形成して面積あたりの接合面面積を増やすことができ光電流量を増大させることができ、角度依存性がないフォトダイオードを備えた光センサーを実現できる。また、本発明の半導体装置は、前記受光部と前記アノード領域との接合面および前記受光部と前記カソード領域との接合面は、平面的に前記受光開口部の短軸方向に対して平行になるように形成されることを特徴とする。このように構成すると、金属を使わぬことでアノード領域・カソード領域の比抵抗が上がっても、抵抗による電位変化が無視できる程度に影響を抑えることができる。また、前記アノード配線および前記カソード配線は遮光性の金属を含んでいてもよい。

20

#### 【0008】

また、前記光センサーは、前記複数のフォトダイオードが並列に接続されてなることを特徴とする。この構成により、光センサーの光電流量を増大させることができ、さらに角度依存性に優れる。

#### 【0009】

また、本発明はこれらの半導体装置を用いた表示装置を提案する。これにより、製造コストの上昇無く、表示装置上に設けられたフォトセンサーの角度依存性を向上させ、十分な光電流量を低照度で得ることが可能となるため、消費電力を抑えつつ画質を外光にあわせて最適化できる。

30

#### 【0010】

また、本発明ではこれらの表示装置を用いた電子機器を提案する。低消費電力で高品位な表示装置をコスト上昇無しに備えることができる。

#### 【発明を実施するための最良の形態】

#### 【0011】

以下、本発明に係る光センサー、半導体装置、表示装置およびこれを備える電子機器の実施の形態について、図面に基づいて説明する。

#### 【0012】

40

##### [第1の実施の形態]

以下、本発明に係る光センサー、半導体装置、表示装置およびこれを備える電子機器の実施の形態について、図面に基づいて説明する。

#### 【0013】

##### [第1の実施の形態]

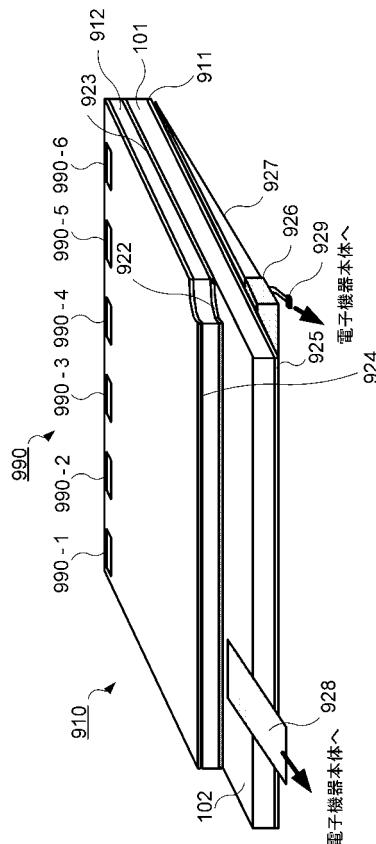

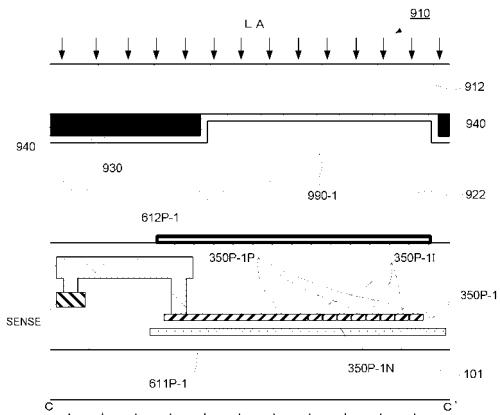

図1は本実施例に係る液晶表示装置910の斜視構成図（一部断面図）である。液晶表示装置910は、アクティブマトリクス基板101（半導体装置）と対向基板912とをシール材923により一定の間隔で貼り合わせ、ネマティック相液晶材料922を挟持した液晶パネル911を備える。アクティブマトリクス基板101上には図示しないがポリイミドなどからなる配向材料が塗布されラビング処理されて配向膜が形成されている。ま

50

た、対向基板 912 は、図示しないが画素に対応したカラーフィルタと、光抜けを防止し、コントラストを向上させるための低反射・低透過率樹脂よりなるブラックマトリクス 940 と、アクティブマトリクス基板 101 上の対向導通部 330-1 ~ 330-2 と短絡される共通電位が供給される ITO 膜である対向電極 930 が形成される。ネマティック相液晶材料 922 と接触する面にはポリイミドなどからなる配向材料が塗布され、アクティブマトリクス基板 101 の配向膜のラビング処理の方向とは直交する方向にラビング処理されている。

#### 【0014】

さらに対向基板 912 の外側には、上偏光板 924 を、アクティブマトリクス基板 101 の外側には、下偏光板 925 を各々配置し、互いの偏光方向が直交するよう（クロスニコル状）に配置する。さらに下偏光板 925 下には、バックライトユニット 926 と導光板 927 が配置され、バックライトユニット 926 から導光板 927 に向かって光が照射され、導光板 927 はバックライトユニット 926 からの光をアクティブマトリクス基板 101 に向かって垂直かつ均一な面光源となるように光を反射屈折させることで液晶表示装置 910 の光源として機能する。バックライトユニット 926 は、本実施例では LED ユニットであるが、冷陰極管（CCFL）であってもよい。バックライトユニット 926 はコネクタ 929 を通じて電子機器本体に接続され、電源を供給されるが、本実施例では電源が適宜適切な電流・電圧に調整されることでバックライトユニット 926 からの光量が調整される機能を有する。

#### 【0015】

図示しないが、さらに必要に応じて、周囲を外殻で覆っても良いし、あるいは上偏光板 924 のさらに上に保護用のガラスやアクリル板を取り付けても良いし、視野角改善のため光学補償フィルムを貼っても良い。

#### 【0016】

また、液晶表示装置 910 の外周部には光センサー受光開口部 990 が設けられる。また、アクティブマトリクス基板 101 は、対向基板 912 から張り出す張り出し部 102 が設けられ、その張り出し部 102 にある信号入力端子 320 には、FPC（可撓性基板）928 が実装され電気的に接続されている。FPC（可撓性基板）928 は電子機器本体に接続され、必要な電源、制御信号等を供給される。

#### 【0017】

さらに液晶表示装置 910 上には 6 個の光センサーの受光開口部 990-1 ~ 990-6 が設けられる。この受光開口部 990-1 ~ 990-6 は対向電極 930 上のブラックマトリクス 940 を部分的に除去することで形成されており、外部の光がアクティブマトリクス基板 101 上に到達するようになっている。各受光開口部 990-1 ~ 990-6 の周囲は対向電極 930 上のブラックマトリクス 940 は除去されておらず、外光はアクティブマトリクス基板 101 上に到達しないようになっている。

#### 【0018】

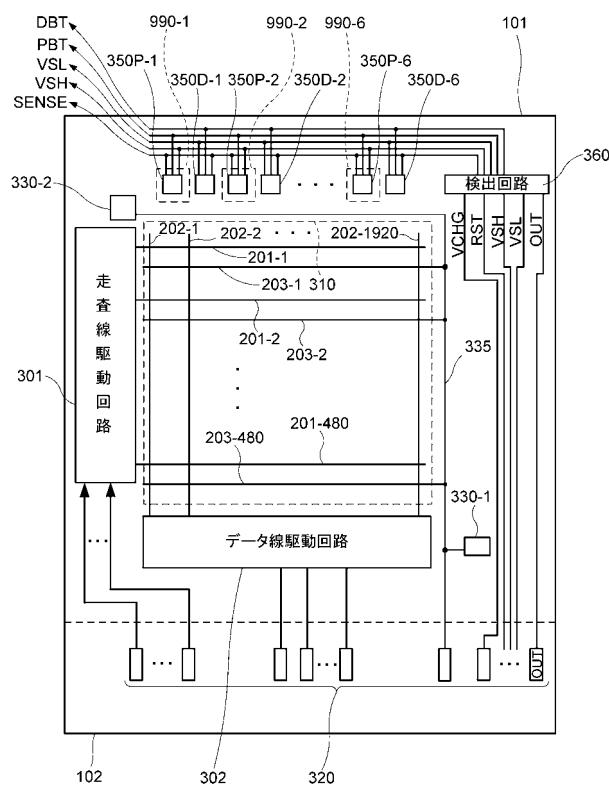

図 2 はアクティブマトリクス基板 101 のブロック図である。アクティブマトリクス基板 101 上には、480 本の走査線 201-1 ~ 201-480 と 1920 本のデータ線 202-1 ~ 202-1920 が直交して形成されており、480 本の容量線 203-1 ~ 203-480 は走査線 201-1 ~ 201-480 と並行に配置されている。容量線 203-1 ~ 203-480 は相互に短絡され、共通電位配線 335 と接続され、さらに 2 個の対向導通部 330-1 ~ 330-2 と接続されて信号入力端子 320 より 0V-5V の反転信号、反転時間は 35 μ 秒である共通電位を与えられる。走査線 201-1 ~ 201-480 は走査線駆動回路 301 に接続され、またデータ線 202-1 ~ 202-1920 はデータ線駆動回路 302 に接続され、それぞれ適切に駆動される。また走査線駆動回路 301、データ線駆動回路 302 は信号入力端子 320 から駆動に必要な信号を供給される。信号入力端子 320 は張り出し部 102 上に配置される。一方、走査線駆動回路 301、データ線駆動回路 302 は対向基板 912 と重なる領域、すなわち張り出し部 102 外に配置される。走査線駆動回路 301、データ線駆動回路 302 は、低温ポリシ

10

20

30

40

50

リコン TFT プロセスによりアクティブマトリクス基板上に駆動に必要な回路機能をに集積するシステム・オン・グラス (SOG) 技術により、アクティブマトリクス基板上にポリシリコン薄膜トランジスターを集積することで形成されており、後述する画素スイッチング素子 401-n-m と同一工程で製造される、いわゆる駆動回路内蔵型の液晶表示装置となっている。

#### 【0019】

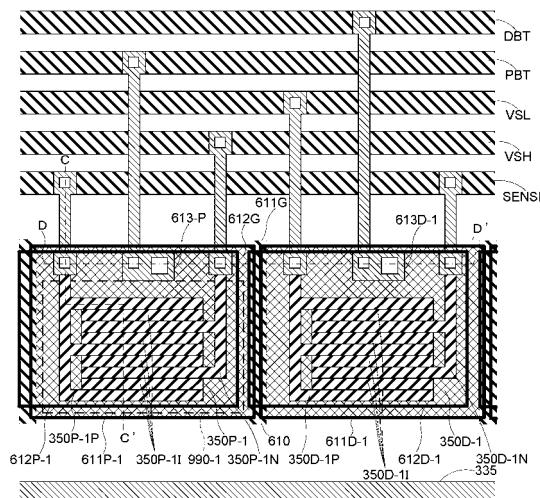

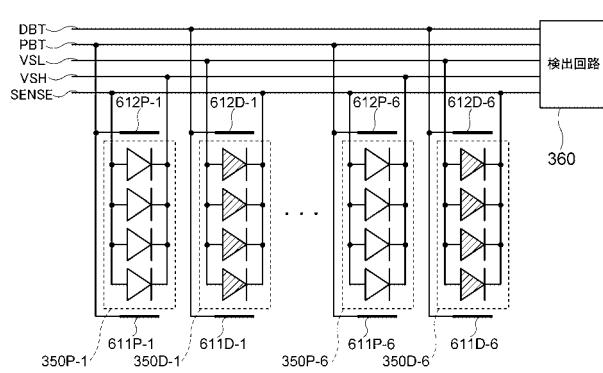

また 6 個の受光開口部 990-1~990-6 と平面的に重なる領域にそれぞれ 6 個の受光センサー 350P-1~350P-6 が形成され、それと交互になるよう 6 個の遮光センサー 350D-1~350D-6 が形成される。この受光センサー 350P-1~350P-6 と遮光センサー 350D-1~350D-6 もシステム・オン・グラス (SOG) 技術により、アクティブマトリクス基板上に形成される。このようにガラス基板上に画素スイッチング素子 401-n-m と同一工程で製造することで、製造コストを下げることができる。10

#### 【0020】

受光センサー 350P-1~350P-6 は受光開口部 990-1~990-6 と平面的に重なっており外光がセンサーに到達するが、遮光センサー 350D-1~350D-6 は受光開口部 990-1~990-6 と平面的に重なっておらず、外光は対向電極 930 上のブラックマトリクス 940 で吸収されほとんど到達しない。受光センサー 350P-1~350P-6 は配線 PBT、配線 VSH、配線 SENSE と、遮光センサー 350D-1~350D-6 は配線 DBT、配線 VSL、配線 SENSE と接続される。これらの配線 PBT、配線 VSH、配線 SENSE、配線 DBT、配線 VSL は検出回路 360 に接続される。検出回路 360 は受光センサー 350P-1~350P-6 と遮光センサー 350D-1~350D-6 からの外光照度と相関を持つ出力アナログ電流に対応したパルス長の二値出力信号 OUT に変換し、信号入力端子 320 へ出力する。また、配線 VCHG、配線 RST、配線 VSL、配線 VSH も信号入力端子 320 を介して検出回路 360 に供給される。20

#### 【0021】

詳細は後述するが、受光センサー 350P-1~350P-6 はバックライト遮光電極 611P-1~611P-6、遮光センサー 350D-1~350D-6 はバックライト遮光電極 611D-1~611D-6 とそれぞれ平面的に重なり、それぞれバックライトからの光は遮蔽されているので、バックライトからの光によって外光の検出精度が低下することができないように構成されている。また、受光センサー 350P-1~350P-6 は透明電極 612P-1~612P-6、遮光センサー 350D-1~350D-6 は透明電極 612D-1~612D-6 とも重なっており、表示領域 310 を駆動する際に発生した電磁ノイズによって検出精度が低下することもない。これらの構成によって、受光センサー 350P-1~350P-6 および遮光センサー 350D-1~350D-6 は表示領域 310 近くに配置しても検出精度が低下しないので、従来の製品よりデザイン的な自由度が向上している。本実施例では受光開口部 990-1~990-6 のサイズ、すなわち各受光センサー 350P-1~350P-6 上のブラックマトリクス 940 の開口サイズは 10mm × 0.3mm に設定し、受光開口部 990-1~990-6 の端部から表示領域 310 までの距離は 0.5mm とした。30

#### 【0022】

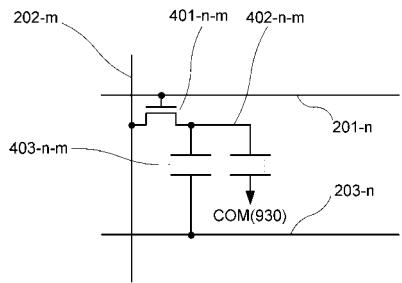

図 3 は図 2 の点線 310 部で示す表示領域の m 番目のデータ線 202-m と n 番目の走査線 201-n の交差部付近の回路図である。走査線 201-n とデータ線 202-m の各交点には N チャネル型電界効果ポリシリコン薄膜トランジスターによりなる画素スイッチング素子 401-n-m が形成されており、そのゲート電極は走査線 201-n に、ソース・ドレイン電極はそれぞれデータ線 202-m と画素電極 402-n-m に接続されている。画素電極 402-n-m 及び同一電位に短絡される電極は容量線 203-n と補助容量コンデンサー 403-n-m を形成し、また液晶表示装置として組み立てられた際には液晶材料をはさんで対向電極 930 (コモン電極) とやはりコンデンサーを形成する。40

## 【0023】

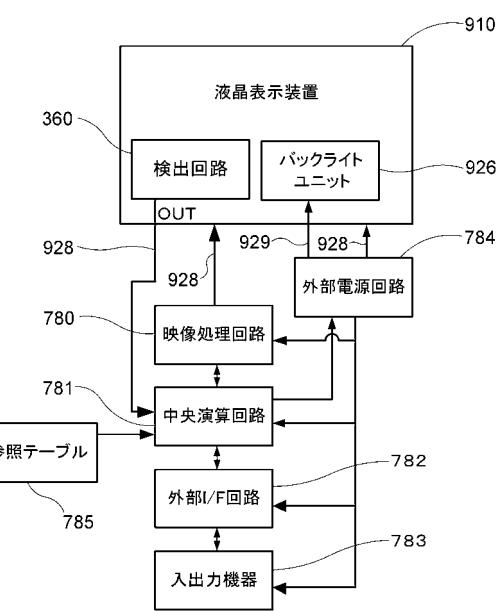

図4は本実施例での電子機器の具体的な構成を示すブロック図である。液晶表示装置910は図1で説明した液晶表示装置であって、外部電源回路784、映像処理回路780がFPC(可撓性基板)928およびコネクタ929を通じて必要な信号と電源を液晶表示装置910に供給する。中央演算回路781は外部I/F回路782を通して入出力機器783からの入力データを取得する。ここで入出力機器783とは例えばキーボード、マウス、トラックボール、LED、スピーカー、アンテナなどである。中央演算回路781は外部からのデータをもとに各種演算処理を行い、結果をコマンドとして映像処理回路780あるいは外部I/F回路782へ転送する。映像処理回路780は中央演算回路781からのコマンドに基づき映像情報を更新し、液晶表示装置910への信号を変更することで、液晶表示装置910の表示映像が変化する。また、液晶表示装置910上の検出回路360からの二値出力信号OUTがFPC(可撓性基板)928を通じて中央演算回路781に入力され、中央演算回路781は二値出力信号OUTのパルス長を対応する離散値に変換する。次に中央演算回路781はEEPROM(Electronically Erasable and Programmable Read Only Memory)よりなる参照テーブル785にアクセスし、変換した離散値を適切なバックライトユニット926の電圧に対応する値に再変換し、外部電源回路784に送信する。外部電源回路784はこの送信された値に対応した電圧の電位電源を液晶表示装置910内のバックライトユニット926にコネクタ929を通じて供給する。バックライトユニット926の輝度は外部電源回路784より供給される電圧によって変化するので、液晶表示装置910の全白表示時輝度も変化することになる。ここで電子機器とは具体的にはモニター、TV、ノートパソコン、PDA、デジタルカメラ、ビデオカメラ、携帯電話、携帯フォトビューワー、携帯ビデオプレイヤー、携帯DVDプレイヤー、携帯オーディオプレイヤーなどである。

## 【0024】

なお、本実施例では電子機器上の中央演算回路781によってバックライトユニット926の輝度を制御したが、例えば液晶表示装置910内にドライバーIC及びEEPROMを備えた構成とし、このドライバーICに二値出力信号OUTから離散値への変換機能、EEPROMを参照しての再変換機能、バックライトユニット926への出力電圧の調整機能を持たせても良い。また、参照テーブルを用いず、数値計算によって離散値からバックライトユニット926の電圧に対応する値に再変換するように構成しても良い。

## 【0025】

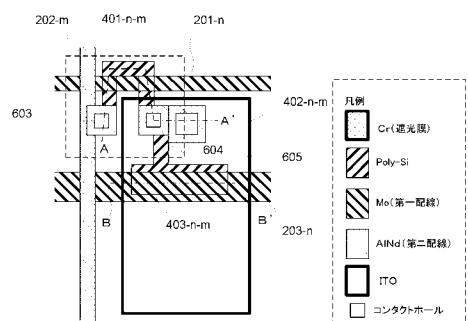

図5は図3で示した画素表示領域の回路図の実際の構成を示す平面図である。図5の凡例に示す通り、各網掛けの異なる部位はそれぞれ異なる材料配線であることを示し、同じ網掛けで示した部位は同じ材料配線であることを示す。クロム薄膜(Cr)、ポリシリコン薄膜(Poly-Si)、モリブデン薄膜(Mo)、アルミ・ネオジウム合金薄膜(AlNd)、酸化インディウム・錫薄膜(Indium Tin Oxide=ITO)の5層薄膜より構成されており、それぞれの層間には酸化シリコン、窒化シリコン、有機絶縁膜のいずれかあるいはそれらを積層した絶縁膜が形成される。具体的にはクロム薄膜(Cr)は膜厚100nm、ポリシリコン薄膜(Poly-Si)は膜厚50nm、モリブデン薄膜(Mo)は膜厚200nm、アルミ・ネオジウム合金薄膜(AlNd)は膜厚500nm、酸化インディウム・錫薄膜(ITO)は膜厚100nmとする。また、クロム薄膜(Cr)とポリシリコン薄膜(Poly-Si)の間に100nmの窒化シリコン膜と100nmの酸化シリコン膜を積層した下地絶縁膜が形成され、ポリシリコン薄膜(Poly-Si)とモリブデン薄膜(Mo)の間に100nmの酸化シリコン膜からなるゲート絶縁膜が形成され、モリブデン薄膜(Mo)とアルミ・ネオジウム合金薄膜(AlNd)の間に200nmの窒化シリコン膜と500nmの酸化シリコン膜を積層した層間絶縁膜が形成され、アルミ・ネオジウム合金薄膜(AlNd)と酸化インディウム・錫薄膜(ITO)の間に200nmの窒化シリコン膜と平均1μmの有機平坦化膜を積層した保護絶縁膜が形成され、互いの配線間を絶縁しており、適切な位置にコンタクトホールを開口して互いに接続される。なお、図5中にはクロム薄膜(Cr)パターンは

存在しない。

**【0026】**

図5で示すように、データ線202-mはアルミニウム合金薄膜(AlNd)により形成され、コンタクトホールを介して画素スイッチング素子401-n-mのソース電極に接続される。走査線201-nはモリブデン薄膜(Mo)で構成され、画素スイッチング素子401-n-mのゲート電極を兼用する。容量線203-nは走査線201-nと同じ配線材料から構成され、画素電極402-n-mは酸化インディウム・錫薄膜よりなり、画素スイッチング素子401-n-mのドレイン電極にコンタクトホールを通じて接続される。また、画素スイッチング素子401-n-mのドレイン電極はリンを高濃度ドープされたn+型ポリシリコン薄膜よりなる容量部電極605にも接続され、容量線203-nと平面的に重なって補助容量コンデンサー403-n-mを構成する。

10

**【0027】**

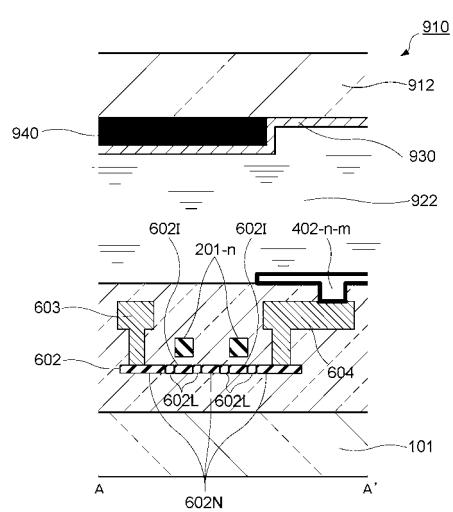

図6は画素スイッチング素子401-n-mの構造を説明するための図5のA-A'線部に対応する液晶表示装置910の一部の断面構造を示す図である。なお、図を見やすくするために縮尺は一定でない。アクティブラトリクス基板101は無アルカリガラスよりなる厚さ0.6mmの絶縁基板であって、その上に200nmの窒化シリコン膜と300nmの酸化シリコン膜を積層した下地絶縁膜を介してポリシリコン薄膜よりなるシリコンアイランド602が配置され、走査線201-nはシリコンアイランド602と前述のゲート絶縁膜を挟んで上方に配置される。走査線201-nとオーバーラップする領域ではシリコンアイランド602はリンイオンが全く、あるいはごく低濃度しかドープされていない真性半導体領域602Iであり、その左右にリンイオンが低濃度にドープされたシート抵抗20k程度のn-領域602Lが存在し、さらにその左右にリンイオンが高濃度にドープされたシート抵抗1k程度のn+領域602Nが存在する、LD (Lightly Doped Drain)構造である。左右のn+領域602Nは層間絶縁膜にそれぞれ形成したコンタクトホールを介してソース電極603、ドレイン電極604と接続しており、ソース電極603はデータ線202-mと、ドレイン電極604は平坦化絶縁膜上に形成された画素電極402-n-mとそれぞれ接続している。画素電極402-n-mと対向基板912上の対向電極930との間にはネマティック相液晶材料922が存在する。また、画素電極402-n-mと一部重なるようにしてブラックマトリクス940が対向基板912上に形成されている。なお、画素スイッチング素子401-n-mの光リーク電流が問題になる場合はシリコンアイランド602下にCr膜よりなる遮光層を形成しても良い。本実施例では光リーク電流はほとんど問題ではなく、かつこのような構造をとると、画素スイッチング素子401-n-mの移動度が下がるため、シリコンアイランド602下のCr膜は除去する構成を選択した。

20

30

**【0028】**

図7は補助容量コンデンサー403-n-mの構造を説明するための図5のB-B'線部に対応する液晶表示装置910の一部の断面構造を示す図であり、ドレイン電極604と繋がる容量部電極605と容量線203-nがゲート絶縁膜をはさんで重なることで蓄積容量を形成している。

40

**【0029】**

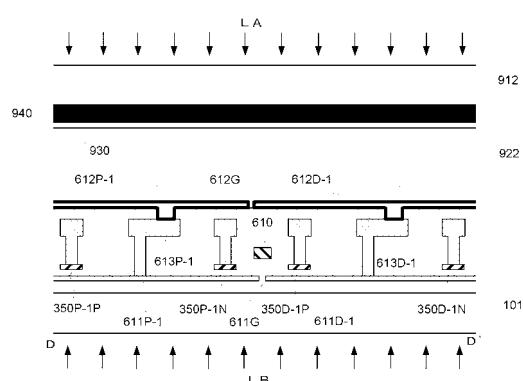

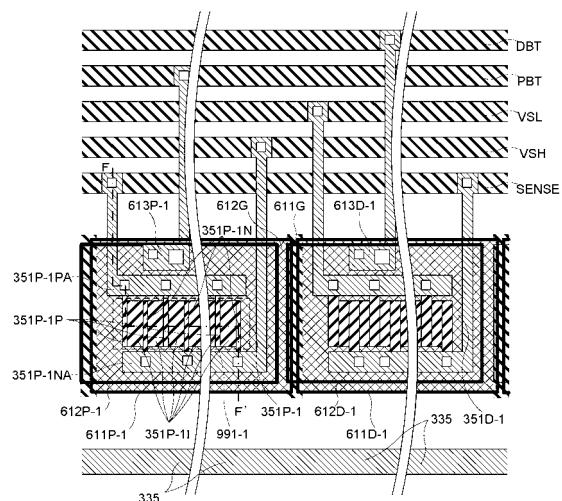

図8は受光センサー350P-1(第1の光センサー)と遮光センサー350D-1(第2の光センサー)付近の拡大平面図である。なお、図を見やすくするために縦と横の縮尺は一定でない。また、凡例は図5と同様である。受光センサー350P-1は太点線で示す受光開口部990-1と平面的に重なっており、外光が照射されるようになっている。受光センサー350P-1は4箇所の孤立した受光部350P-1Iとそれに隣り合う配線SENSEに接続されるアノード領域350P-1Pと、配線VSHに接続されるカソード領域350P-1Nとによって構成される。受光部350P-1I、アノード領域350P-1P、カソード領域350P-1Nはいずれも同一のポリシリコン薄膜アイランドがドープ濃度の違いによって分離されることで構成され、アノード領域350P-1Pは比較的高濃度のボロンイオンがドープされ、カソード領域350P-1Nは比較的高

50

濃度のリンイオンがドープされ、受光部 350P-1I はごく低濃度でしかボロンイオン・リンイオンを含まない。また、アノード領域 350P-1P、カソード領域 350P-1N、受光部 350P-1I はそれぞれ幅 10 μm であって、受光部 350P-1I の長さはそれぞれ 1000 μm である。このように受光センサー 350P-1 は複数の並列接続された PIN 接合ダイオードからなるフォトダイオードを構成している。受光センサー 350P-1 及び遮光センサー 350D-1 の表示領域 310 に近い側には共通電位配線 335 が配置されるが、本実施例では受光センサー 350P-1 及び遮光センサー 350D-1 には接続されず、電磁ノイズの影響を避けるため 100 μm 離して配置している。

#### 【0030】

遮光センサー 350D-1 は 4箇所の孤立した受光部 350D-1I とそれに隣り合う配線 VSL に接続されるアノード領域 350D-1P と、配線 SENSE に接続されるカソード領域 350D-1N によって構成される。カソードとアノードが接続される配線が異なることと、受光開口部 990-1 と平面的に重なっていないこと以外は受光センサー 350P-1 と遮光センサー 350D-1 は同一の構成であるので、これ以上の説明は省略する。また、受光センサー 350P-2 ~ 350P-5 は受光センサー 350P-1 と、遮光センサー 350D-2 ~ 350D-5 は遮光センサー 350D-1 と、それぞれ配置位置を除いて同様の構成であるので説明は省略する。

#### 【0031】

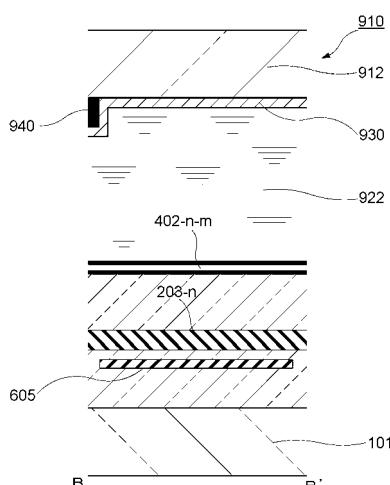

図 9 は受光センサー 350P-1 の構造を説明するための図 8 の線 C-C' 線部に対応する液晶表示装置 910 の一部の断面構造を示す図である。アクティブマトリクス基板 101 上には下地絶縁膜を介してバックライト遮光電極 611P-1 ( 第 1 の遮光電極 ) が配置され、その上に薄膜ポリシリコンよりなる受光センサー 350P-1 がゲート絶縁膜を挟んで形成される。受光センサー 350P-1 が 4箇所の受光部 350P-1I とそれに隣り合う配線 VSL に接続されるアノード領域 350P-1P と、配線 SENSE に接続されるカソード領域 350P-1N によって構成されるのは前述の通りである。受光センサー 350P-1 の上方には層間絶縁膜、平坦化絶縁膜を介して酸化インディウム・錫薄膜 ( ITO ) よりなる透明電極 612P-1 ( 第 1 の透明電極 ) が配置され、受光部 350P-1I に対する電界シールドとして機能する。透明電極 612P-1 の上方はネマティック相液晶材料 922 が封入され、対向基板 912 上の対向電極 930 が配置される。なお、受光センサー 350P-1 配置位置によってはネマティック相液晶材料 922 のかわりにシール材 923 が配置されることもある。受光開口部 990-1 は対向基板 912 上のブラックマトリクス 940 を部分的に除去することで形成されてなる。図示しないが、遮光センサー 350D-1 上には受光開口部は存在しないので、ブラックマトリクス 940 は除去されない。

#### 【0032】

対向基板 912 の上方からは外光 LA が照射され、他方、アクティブマトリクス基板 101 の下方からはバックライトユニット 926 からの光 ( バックライト光 LB ) が照射される構成となっている。

#### 【0033】

なお、本実施例では実施していないが、受光開口部 990-1 部に光学的な補正層を入れてもよい。例えば対向基板 912 に形成される画素に対応したカラーフィルタを構成する色材のうちの一つあるいは複数を受光開口部 990-1 と重ねて形成して、視感度分光特性と受光センサー 350P-1 をより一致させるようにしてもよい。例えばグリーンの画素に対応する色材を受光開口部 990-1 上に重ねて形成すれば、短波長と長波長側をカットするため、受光センサー 350P-1 の分光特性が視感度分光特性より短波長あるいは長波長にずれていても補正できる。その他、反射防止膜や干渉層、偏光層等と目的に応じて受光開口部 990-1 部を重ねればよい。また、本図では図示していないが、上偏光板 924 は受光開口部 990-1 と重ねてもよいし、除去しても良い。重ねた方が受光開口部 990-1 は目立たなくなるが、除去すると光感度が向上する。

#### 【0034】

10

20

30

40

50

本実施例では液晶表示装置 910 は低消費電力化のため、共通電位配線 335 に反転信号を印加する共通電極反転駆動（コモン A C 駆動）を行っているので、対向電極 930 には振幅 0 V ~ 5 V、周波数 14 K H z の A C 信号が印加される。しかしながら対向電極 930 より生じる電磁波は透明電極 612P - 1 によってシールドされるため、対向電極 930 反転時に受光センサー 350P - 1 にノイズがほとんどのことがない。同様に下方からの電磁ノイズに対してはバックライト遮光電極 611P - 1 がシールドとして機能する。

#### 【 0035 】

図 10 は図 8 の線 D - D' 線部に対応する液晶表示装置 910 の一部の断面構造を示す図である。下地絶縁膜上に形成されるバックライト遮光電極 611P - 1（第 1 の遮光電極）とバックライト遮光電極 611D - 1（第 2 の遮光電極）は遮光電極間隙 611G によって互いに離間しており、別々の電位を与えられる。また平坦化絶縁膜上に形成される透明電極 612P - 1（第 1 の透明電極）と透明電極 612D - 1（第 2 の透明電極）も透明電極間隙 612G によって互いに離間しており、別々の電位を与えられる。バックライト遮光電極 611P - 1 と透明電極 612P - 1 は互いに中間電極 613P - 1 とゲート絶縁膜、層間絶縁膜および平坦化絶縁膜に形成されたコンタクトホールを介して接続されており、最終的に配線 PBT に接続される。バックライト遮光電極 611D - 1 と透明電極 612D - 1 は互いに中間電極 613D - 1 とコンタクトホールを介して接続されており、最終的に配線 DBT に接続される。

#### 【 0036 】

ここで遮光電極間隙 611G と透明電極間隙 612G はアクティブマトリクス基板 101 および対向基板 912 の鉛直方向において互いに重ならない。このように構成すると、平面的に上下ともにシールドされていない領域がなくなるので、間隙から進入する電磁ノイズが左右に広がりにくくなり、間隙によるシールド性能の低下を軽減できる。

#### 【 0037 】

また、遮光電極間隙 611G と重なるようにモリブデン薄膜（M o）よりなる間隙遮光体 610 が形成される。これにより、遮光電極間隙 611G より進入するバックライト光が各種絶縁膜やガラスの界面等で多重反射され、迷光となって受光センサー 350P - 1 や遮光センサー 350D - 1 に到達する割合を飛躍的に軽減できる。

#### 【 0038 】

本実施例では受光部 350P - 1I に隣接したアノード領域 350P - 1P、カソード領域 350P - 1N はドープされたポリシリコン薄膜のみで構成し、金属配線を引き回さない。このように構成すると、受光開口部 990 - 1 と平面的に重なる領域にほとんど（あるいは全く）金属配線が受光部 350P - 1I より上層には存在しない。このため、より光の利用効率が良くなり、また広角度の光が入射するため、角度依存性が少なくなるのである。これについてアノード領域 350P - 1P、カソード領域 350P - 1N に金属配線を用いる従来の事例と比較しながら説明する。

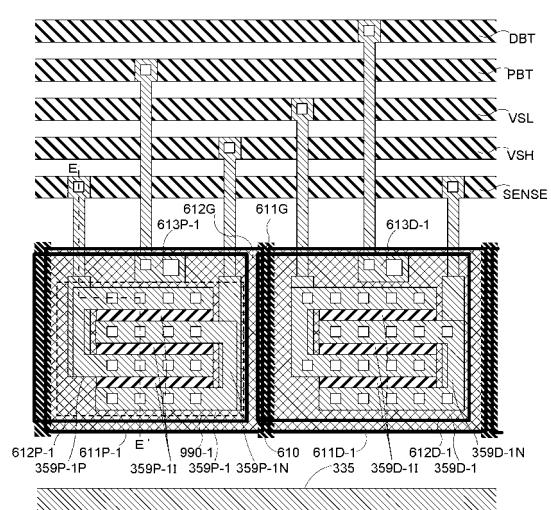

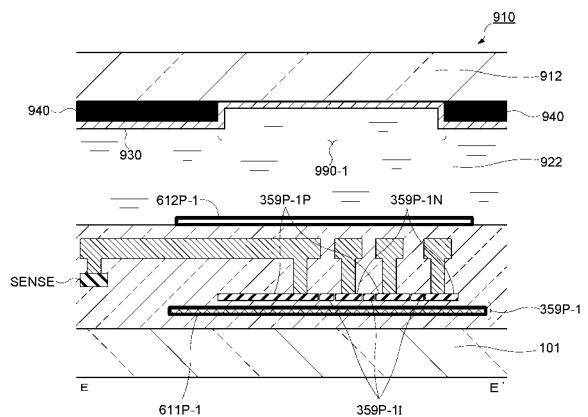

#### 【 0039 】

図 19 は第 1 の実施例の受光センサー 350P - 1 と遮光センサー 350D - 1 にかわり、従来の構成である受光センサー 359P - 1 と遮光センサー 359D - 1 を適用した場合の拡大平面図であって、図 20 はその E - E' 断面の図である。図 19 は本実施例の図 8 に対応し、図 20 は図 9 に対応する。受光センサー 359P - 1 はアノード領域 359P - 1P と、カソード領域 359P - 1N と、これらに挟まれた受光部 359P - 1I とによって構成される。以下、受光センサー 350P - 1 との違いを説明する。本従来例ではアノード領域 359P - 1P と、カソード領域 359P - 1N はデータ線 202 - m を構成するアルミ・ネオジウム合金薄膜（A1Nd）と同一の膜で形成される金属配線と、ポリシリコン薄膜を積層してコンタクトホールで接続することによって形成している。コンタクトホールのサイズと合わせズレマージンの問題から、アノード領域 359P - 1P とカソード領域 359P - 1N の幅は第 1 の実施例のアノード領域 350P - 1P とカソード領域 350P - 1N の幅よりも大きく、15 μm となっている。受光部 359P -

10

20

30

40

50

1 I の各領域の幅は受光部 350P - 1 I と同じ  $10\text{ }\mu\text{m}$  であり、長さも受光部 350P - 1 I と同じ  $1000\text{ }\mu\text{m}$  である。受光開口部 990 - 1 のサイズは本実施例と同じであり、この中に入るよう受光センサー 359P - 1 のサイズを調整した結果、受光部 359P - 1 I は 3 つの領域からなっており、第 1 の実施例の受光部 350P - 1 I より領域の数が少なくなっている。

#### 【0040】

遮光センサー 359D - 1 の構成は受光センサー 359P - 1 と基本的に同一であるので説明を省略する。また、受光センサー 350P - 1 と遮光センサー 350D - 1 にかわって受光センサー 359P - 1 と遮光センサー 359D - 1 を用いている以外は図 19 は図 8 と、図 20 は図 9 と全く同一の構成であるので、これらの詳細な説明は同じ記号を付与することで省略する。10

#### 【0041】

図 20 によると、受光部 359P - 1 I の外光入射方向側にアノード領域 359P - 1 P と、カソード領域 359P - 1 N を構成するアルミ・ネオジウム合金薄膜 (AlNd) の配線が存在する。このようなパターンが存在すると、斜め方向から光が入射した際に光の効率が低下するため、受光センサー 359P - 1 の光感度依存性は狭くなる。また、受光開口部 990 - 1 の中に金属配線があるため、液晶表示装置 910 上で受光開口部 990 - 1 がより目立ち、デザイン性が良くない。これを避けるためにはアノード領域 359P - 1 P とカソード領域 359P - 1 N を構成するアルミ・ネオジウム合金薄膜 (AlNd) の配線と受光部 359P - 1 I の距離を長くすればよいが、そうすると受光開口部 990 - 1 の面積あたりの受光部 359P - 1 I の割合が低下し、光利用効率が低下してしまう。20

#### 【0042】

本実施例の図 8、図 9 のような構成の受光センサー 350P - 1 であれば、受光開口部 990 - 1 内にバックライト遮光電極 611P - 1 以外の金属が存在せず、角度依存性が低下することがない。しかも、従来例に比べ、受光開口部 990 - 1 における受光部 350P - 1 I の面積の占める密度が高く、より大きな光電流を得ることができる。

#### 【0043】

一方で従来例のアノード領域 359P - 1 P、カソード領域 359P - 1 N に比べ、本実施例のアノード領域 350P - 1 P、カソード領域 350P - 1 N の抵抗値は数 100 ~ 数 1000 倍上昇してしまうが、本実施例では受光部 350P - 1 I に流れる電流は幅  $1\text{ }\mu\text{m}$ あたり上限は使用温度範囲・保証光強度領域内では 1 ナノアンペア以下であるので、これによるアノード・カソード電極電位の変動は  $1\text{ mV}$  を超えることはなく、精度上問題にはならない。30

#### 【0044】

なお、光感度の良いセンサー素子を用いる場合は光電流が増大し、高い照度領域でアノード領域・カソード領域の抵抗による電位変動が問題となる場合がある。このような場合は、受光開口部 990 - 1 及び光センサーのサイズを縮めるか、アノード領域・カソード領域の幅を広げるなどしてもよい。また、受光部からはなれた箇所のアノード領域・カソード領域でのみ、金属配線を併用するなどしてもよい。40

#### 【0045】

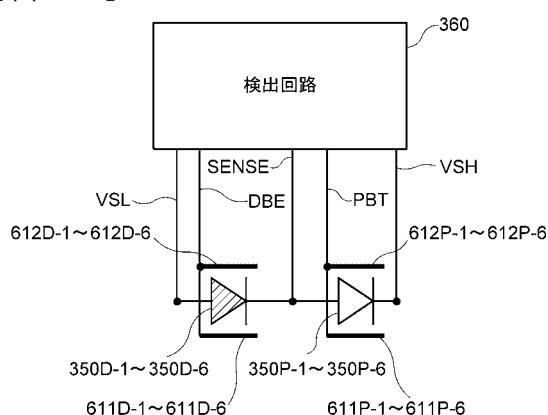

受光センサー 350P - 1 ~ 350P - 6、遮光センサー 350D - 1 ~ 350D - 6 の等価回路が図 11 である。各受光センサー 350P - 1 ~ 350P - 6、遮光センサー 350D - 1 ~ 350D - 6 はそれぞれ、4 つの PIN ダイオードが並列に接続されている。また、各受光センサー 350P - 1 ~ 350P - 6 も互いに並列に接続されており、遮光センサー 350D - 1 ~ 350D - 6 も互いに並列に接続されている。ゆえに最終的に図 11 は図 12 の回路図と等価である。すなわち、遮光センサー 350D - 1 ~ 350D - 6 はチャネル幅  $24000\text{ }\mu\text{m}$ 、チャネル長  $10\text{ }\mu\text{m}$  の PIN ダイオードであり、そのアノードは配線 VSL に接続され、そのカソードは配線 SENSE に接続される。また、遮光センサー 350D - 1 ~ 350D - 6 と平面的に重なるバックライト遮光電極 61

1 D - 1 ~ 6 1 1 D - 6 及び透明電極 6 1 2 D - 1 ~ 6 1 2 D - 6 は配線 D B T に接続される。受光センサー 3 5 0 P - 1 ~ 3 5 0 P - 6 はチャネル幅 2 4 0 0 0  $\mu\text{m}$ 、チャネル長 1 0  $\mu\text{m}$  の P I N ダイオードであり、そのアノードは配線 S E N S E に接続され、そのカソードは配線 V S H に接続される。また、受光センサー 3 5 0 P - 1 ~ 3 5 0 P - 6 と平面的に重なるバックライト遮光電極 6 1 1 P - 1 ~ 6 1 1 P - 6 及び透明電極 6 1 2 P - 1 ~ 6 1 2 P - 6 は配線 P B T に接続される。

#### 【 0 0 4 6 】

ここで受光センサー 3 5 0 P - 1 ~ 3 5 0 P - 6、遮光センサー 3 5 0 D - 1 ~ 3 5 0 D - 6 を図 1 5 及び図 1 6 で説明したような従来構成の受光センサー 3 5 9 P - 1、遮光センサー 3 5 9 D - 1 のような構成にそれぞれ置き換えると、受光センサー・遮光センサーのチャネル幅は 1 8 0 0 0  $\mu\text{m}$  になる。すなわち、本実施例の構成では従来構成と比べて 4 / 3 倍の素子サイズが設定可能であって、光電流も 4 / 3 倍得ることができるので、より低照度での照度検出が可能になっているのである。10

#### 【 0 0 4 7 】

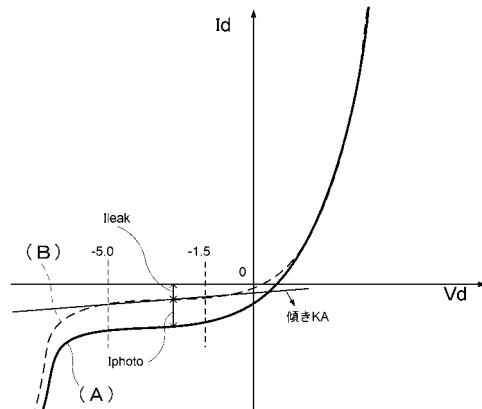

図 1 3 は一定の外光照射度 L X が液晶表示装置 9 1 0 に照射された時の受光センサー 3 5 0 P - 1 ~ 3 5 0 P - 6 と遮光センサー 3 5 0 D - 1 ~ 3 5 0 D - 6 を構成する P I N ダイオードの特性を示したグラフである。横軸はバイアス電位 V d (= アノード電位 - カソード電位) であり、縦軸はアノード - カソード間に流れる電流量 I d である。実線で示したグラフ ( A ) は受光センサー 3 5 0 P - 1 ~ 3 5 0 P - 6 の特性であり、破線で示したグラフ ( B ) は遮光センサー 3 5 0 D - 1 ~ 3 5 0 D - 6 の特性である。このように順バイアス領域 ( I d > 0 ) ではほぼ両者は一致するが、逆バイアス領域 ( I d < 0 ) では受光センサー 3 5 0 P - 1 ~ 3 5 0 P - 6 のグラフ ( B ) 方が電流の絶対値が大きくなる。これは遮光センサー 3 5 0 D - 1 ~ 3 5 0 D - 6 には外光が照射されないため、温度に起因する熱電流量 I l e a k のみが流れるが、受光センサー 3 5 0 P - 1 ~ 3 5 0 P - 6 を構成する P I N ダイオードの受光部 3 5 0 P - 1 I ~ 3 5 0 P - 6 I に光が照射されるとキャリア対が生成され、光電流量 I p h o t o が流れるため、受光センサー 3 5 0 P - 1 ~ 3 5 0 P - 6 では光電流量と熱電流量の和、I p h o t o + I l e a k が流れるためである。熱電流量 I l e a k は V d (= アノード電位 - カソード電位) 依存性を示し、- 5 . 0 V d - 1 . 5 の領域では傾き K A ( K A > 0 ) の直線として近似できる。ここで K A は温度に対する関数であって、温度が上昇すると指数関数的に上昇する。この V d 領域 ( V d = - 5 . 0 V d - 1 . 5 ) では受光センサー 3 5 0 P - 1 ~ 3 5 0 P - 6 に流れる光電流量 I p h o t o はほぼ一定の値を有し、外光照射度 L X に比例する (以下、I p h o t o = L X × k とする)。ゆえに、受光センサー 3 5 0 P - 1 ~ 3 5 0 P - 6 に流れる電流 (グラフ ( A ))、遮光センサー 3 5 0 D - 1 ~ 3 5 0 D - 6 に流れる電流 (グラフ ( B )) ともに - 5 . 0 V d - 1 . 5 の領域では傾き K A ( K A > 0 ) の直線である。20

#### 【 0 0 4 8 】

ここで遮光センサー 3 5 0 D - 1 ~ 3 5 0 D - 6 と受光センサー 3 5 0 P - 1 ~ 3 5 0 P - 6 の V d を同じになるようにバイアスを設定する、すなわち配線 S E N S E の電位 V S E N S E を配線 V S H の電位 V V S H と配線 V S L の電位 V V S L のちょうど中間である ( V V S H + V V S L ) ÷ 2 に設定すると、受光センサー 3 5 0 P - 1 ~ 3 5 0 P - 6 と遮光センサー 3 5 0 D - 1 ~ 3 5 0 D - 6 に流れる熱電流量 ( I l e a k ) は全く一致する。このとき、配線 V S H に流れる電流量 (= 受光センサー 3 5 0 P - 1 ~ 3 5 0 P - 6 に流れる電流量) は I p h o t o + I l e a k であり、配線 V S L にながれる電流量 (= 遮光センサー 3 5 0 D - 1 ~ 3 5 0 D - 6 に流れる電流量) は I l e a k であるので、キルヒホッフ第 1 法則から配線 S E N S E に流れる電流量は I p h o t o = L X × k となって、外光照射度 L X に比例する。なお実施例では受光センサーを高電位側に、遮光センサーを低電位側に接続したが、もちろん別でも差し支えないし、結論は同じである。30

#### 【 0 0 4 9 】

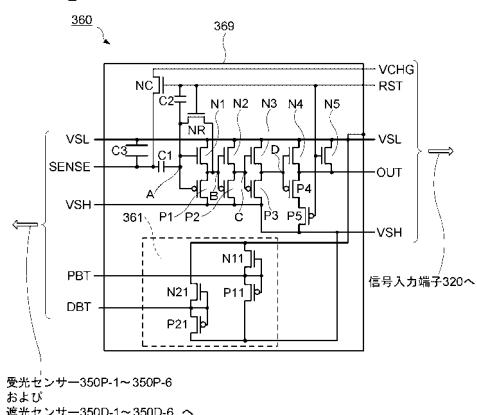

図 1 4 は検出回路 3 6 0 の回路図である。配線 V C H G、配線 R S T、配線 V S L、配40

線 V S H、配線 O U T は信号入力端子 3 2 0 と接続され、また配線 V S L、配線 V S H、配線 S E N S E、配線 P B T、配線 D B T 配線は受光センサー 3 5 0 P - 1 ~ 3 5 0 P - 6 及び遮光センサー 3 5 0 D - 1 ~ 3 5 0 D - 6 に接続される。ここで配線 V C H G、配線 V S L、配線 V S H は外部電源回路 7 8 4 より供給される DC 電源に接続され、V C H G 配線は電位 V V C H G (= 2 . 0 V)、V S L 配線は電位 V V S L (= 0 . 0 V)、V S H 配線は電位 V V S H (= 5 . 0 V) を供給される。なお、ここで V S L 配線の電位 V V S L は液晶表示装置 9 1 0 の G N D である。

#### 【 0 0 5 0 】

配線 S E N S E は第 1 のコンデンサー C 1 と、第 3 のコンデンサー C 3 の各一端に接続される。また、初期充電トランジスター N C のドレイン電極に接続される。第 3 のコンデンサー C 3 の他端は配線 V S L に接続される。第 1 のコンデンサー C 1 の他端はノード A に接続される。初期充電トランジスター N C のソース電極は配線 V C H G に接続され、電位 V V C H G (= 2 . 0 V) 電源を供給される。初期充電トランジスター N C のゲート電極は配線 R S T に接続される。ノード A はさらに第 1 の N 型トランジスター N 1 のゲート電極と第 1 の P 型トランジスター P 1 のゲート電極とリセットトランジスター N R のドレイン電極に接続され、さらに第 2 のコンデンサー C 2 の一端に接続される。第 2 のコンデンサー C 2 の他端は配線 R S T に接続される。第 1 の N 型トランジスター N 1 のドレイン電極と第 1 の P 型トランジスター P 1 のドレイン電極とリセットトランジスター N R のソース電極はノード B に接続され、ノード B はさらに第 2 の N 型トランジスター N 2 のゲート電極と第 2 の P 型トランジスター P 2 のゲート電極に接続される。第 2 の N 型トランジスター N 2 のドレイン電極と第 2 の P 型トランジスター P 2 のドレイン電極はノード C に接続され、ノード C はさらに第 3 の N 型トランジスター N 3 のゲート電極と第 3 の P 型トランジスター P 3 のゲート電極に接続される。第 3 の N 型トランジスター N 3 のドレイン電極と第 3 の P 型トランジスター P 3 のドレイン電極はノード D に接続され、ノード D はさらに第 4 の N 型トランジスター N 4 のゲート電極と第 4 の P 型トランジスター P 4 のゲート電極に接続される。第 4 の N 型トランジスター N 4 のドレイン電極と第 4 の P 型トランジスター P 4 のドレイン電極は配線 O U T に接続され、配線 O U T はさらに第 5 の N 型トランジスター N 5 のゲート電極と第 5 の P 型トランジスター P 5 のゲート電極は配線 R S T に接続され、第 5 の P 型トランジスター P 5 のドレイン電極は第 4 の P 型トランジスター P 4 のソース電極に接続される。第 1 ~ 第 5 の N 型トランジスター N 1 ~ N 5 のソース電極は配線 V S L に接続され、電位 V V S L (= 0 V) を供給されてなる。また第 1 ~ 第 3 の P 型トランジスター P 1 ~ P 3 及び第 5 の P 型トランジスター P 5 のソース電極は配線 V S H に接続され、電位 V V S H (= + 5 V) を供給されてなる。

#### 【 0 0 5 1 】

また、検出回路 3 6 0 には配線 P B T と配線 D B T に印加する電位をトランジスターの閾値電圧 ( V t h ) から自動的に補正する自己補正電圧回路 3 6 1 も備えてなる。自己補正電圧回路 3 6 1 は第 6 の N 型トランジスター N 1 1 と、第 6 の P 型トランジスター P 1 1 のドレイン電極及びゲート電極がそれぞれ配線 P B T に接続され、第 7 の N 型トランジスター N 2 1 と、第 7 の P 型トランジスター P 2 1 のドレイン電極及びゲート電極がそれぞれ配線 D B T に接続され、第 6 の N 型トランジスター N 1 1 と、第 7 の N 型トランジスター N 2 1 のソース電極は配線 V S L に接続されて電位 V V S L (= 0 V) を供給され、第 6 の P 型トランジスター P 1 1 と、第 7 の P 型トランジスター P 2 1 のソース電極は配線 V S H に接続され、電位 V V S H (= + 5 V) を供給されて構成される。

#### 【 0 0 5 2 】

また、検出回路 3 6 0 は画素電極 4 0 2 - n - m を構成する酸化インディウム・錫薄膜 ( I T O ) と同一の膜で形成されたシールド電極 3 6 9 によって全面を覆われる。シールド電極 3 6 9 は配線 V S L を通じて液晶表示装置 9 1 0 の G N D 電位に接続され、電磁ノイズに対するシールドとして機能する。

#### 【 0 0 5 3 】

10

20

30

40

50

ここで本実施例では第1のN型トランジスターN1のチャネル幅は10μmであり、第2のN型トランジスターN2のチャネル幅は35μmであり、第3のN型トランジスターN3のチャネル幅は100μmであり、第4のN型トランジスターN4のチャネル幅は150μmであり、第5のN型トランジスターN5のチャネル幅は150μmであり、第6のN型トランジスターN11のチャネル幅は4μmであり、第7のN型トランジスターN21のチャネル幅は200μmであり、第1のP型トランジスターP1のチャネル幅は10μmであり、第2のP型トランジスターP2のチャネル幅は35μmであり、第3のP型トランジスターP3のチャネル幅は100μmであり、第4のP型トランジスターP4のチャネル幅は300μmであり、第5のP型トランジスターP5のチャネル幅は300μmであり、第6のP型トランジスターP11のチャネル幅は200μmであり、第7のP型トランジスターP21のチャネル幅は4μmであり、リセットトランジスターNRのチャネル幅は2μmであり、初期充電トランジスターNCのチャネル幅は50μmであり、全てのN型トランジスターのチャネル長は8μmであり、全てのP型トランジスターのチャネル長は6μmであり、全てのN型トランジスターの移動度は80cm<sup>2</sup>/Vsecであり、全てのP型トランジスターの移動度は60cm<sup>2</sup>/Vsecであり、全てのN型トランジスターの閾値電圧(Vth)は+1.0Vであり、全てのP型トランジスターの閾値電圧(Vth)は-1.0Vであり、第1のコンデンサーC1の容量は1pFであり、第2のコンデンサーC2の容量は100fFであり、第3のコンデンサーC3の容量は100pFである。

## 【0054】

配線RSTは電位振幅0-5Vのパルス波であって、周期510m秒毎にパルス長100μ秒の間High電位(5V)に保持され、残りの509.9m秒間はLow電位(0V)に保持される。RST配線が510m秒毎にHigh(5V)になると、初期充電トランジスターNCとリセットトランジスターNRがONし、配線SENSEにはVCHG配線の電位(2.0V)がチャージされ、ノードAとノードBは短絡する。第1のN型トランジスターN1と第1のP型トランジスターP1はインバーター回路を構成するから、インバーター回路のIN/OUTが短絡される。このとき、ノードAとノードBの電位は最終的に以下の式で表される電位VSに到達する(詳細なる計算は例えばKang Leblebic著"CMOS Digital Integrated Circuits" Third Edition P206などを参照)。

## 【0055】

## 【数1】

$$VS = \frac{Vthn + \sqrt{\frac{WpLn\mu_p}{WnLp\mu_n}} \times (VVSH - VVSL + Vthp)}{(1 + \sqrt{\frac{WpLn\mu_p}{WnLp\mu_n}})}$$

## 【0056】

ここで、Wn:第1のN型トランジスターN1のチャネル幅、Ln:第1のN型トランジスターN1のチャネル長、μn:第1のN型トランジスターN1の移動度、Vthn:第1のN型トランジスターN1の閾値電圧、Wp:第1のP型トランジスターP1のチャネル幅、Lp:第1のP型トランジスターP1のチャネル長、μp:第1のP型トランジスターP1の移動度、Vthp:第1のP型トランジスターP1の閾値電圧であるので、本実施例においてはVS=2.5(V)と計算される。なお、配線RSTがHigh(5V)である間は第5のN型トランジスターN5がONし、第5のP型トランジスターP5がOFFしているのでOUT配線は0Vである。

10

20

30

40

50

## 【0057】

R S T配線が $100\mu\text{s}$ 後にL o w(0V)になると、リセットトランジスターN RがOFFし、ノードAとノードBは電気的に切り離される。この時、第1のN型トランジスターN 1と第1のP型トランジスターP 1で構成されるインバーター回路はノードAの電位がV Sより低ければノードBにV Sより高い電位を出力し、ノードAの電位がV Sより高ければノードBにV Sより低い電位を出力する。第2のN型トランジスターN 2と第2のP型トランジスターP 2および第3のN型トランジスターN 3と第3のP型トランジスターP 3もそれぞれインバーター回路を構成するが、同様に入力段の電位がV Sより低ければV Sより高い電位を、入力段の電位がV Sより高ければV Sより低い電位を、それぞれ出力する。この時、入力段の電位のV Sとの差より出力段の電位のV Sとの差はより大きくなり、配線V S Hの電位V V S H( $= + 5\text{V}$ )もしくは配線V S Lの電位V V S L( $= 0\text{V}$ )へと近づく。結果、ノードAの電位がV Sより低ければノードDはほぼV S H配線の電位V V S H( $= + 5\text{V}$ )となり、ノードAの電位がV Sより高ければノードDはほぼV S L配線の電位V V S L( $= 0\text{V}$ )となる。第4のN型トランジスターN 4及び第5のN型トランジスターN 5、第4のP型トランジスターP 4及び第5のP型トランジスターP 5はN O R回路を構成してなるので、R S T配線の電位がL o w(0V)である期間ではノードDがH i g h(+ 5V)であればL o w(0V)を、ノードDがL o w(0V)であればH i g h(+ 5V)を、それぞれO U T配線へ出力する。すなわち、R S T配線の電位がL o w(0V)である期間ではノードAの電位がV Sより低ければO U T配線への出力はL o w(0V)であり、ノードAの電位がV Sより高ければO U T配線への出力はH i g h(+ 5V)となる。10

## 【0058】

ノードAは前述の通り、配線R S TがL o w(0V)になってリセットトランジスターN RがOFFし、ノードAとノードBは電気的に切り離されるが、これと同時に第2のコンデンサーC 2の結合によって配線R S Tと同時に電位が下がる。ここで第1のコンデンサーC 1の容量C C 1( $= 1\text{pF}$ )が第2のコンデンサーC 2の容量C C 2( $= 100\text{fF}$ )及び第1のN型トランジスターN 1、第1のP型トランジスターP 1、リセットトランジスターN Rのゲート、ドレイン間容量(本実施例ではいずれも $10\text{fF}$ 以下)より十分大きければ、またリセットトランジスターN Rの書き込みインピーダンスと第1のコンデンサーC 1の容量の積(本実施例では約 $1\mu\text{s}$ )が配線R S Tの電位の立ち下げ期間(本実施例では $100\text{n}\mu\text{s}$ )より十分大きければ配線R S TがL o w(0V)になったとき(以下、これを時間 $t = 0$ )とするのノードAの電位(以下、V A(t)とする)は以下の式で表される。20

## 【0059】

## 【数2】

$$VA(t=0) = VS - \frac{CC2}{CC1} \times (VVSH - VVSL)$$

## 【0060】

本実施例ではV A( $t = 0$ ) = 2.0Vとなる。このとき、受光センサー350 P - 1にかかるバイアスはV d = -3.0Vであり、遮光センサー350 D - 1にかかるバイアスはV d = -2.0Vである。図13の説明から明らかなように、このとき、受光センサー350 P - 1と遮光センサー350 D - 1を構成するP I Nダイオードの熱電流量I 1 e a kの差はK A × 1.0で表される。従って、配線S E N S Eには受光センサー350 P - 1に照射される外光に応じた光電流量I p h o t oに電流量K A × 1.0を加えた電流が流れる。ここで、K A < I p h o t oであれば配線S E N S Eに流れる電流量はI p h o t oのみと近似でき、熱電流の寄与を除去できることになる。本実施例では動作保証温度上限の70℃におけるK Aと照度10ルクスにおけるI p h o t oが等しくなった。このことから、外光照度100ルクス以上であれば動作保証温度範囲内において効果的4050

に熱リークを除去できる。

【0061】

ここで外光と  $I_{photo}$  の関係は前述の通り、このバイアス条件では外光が受光センサー 350P-1 を照らす外光強度  $LX$  に比例して  $Vd$  には依存せず  $I_{photo} = LX \cdot k$  となる ( $k$  は一定の係数)。RST配線が Low (0V) になると、ノードAはフローティング状態であるので、第2のコンデンサー C2 の容量 CC2 及び第1のN型トランジスター N1、第1のP型トランジスター P1 のゲート・ソース間容量を無視すればほぼ実効的な容量は第3のコンデンサー C3 の容量 CC3 のみとなって、配線 SENSE の電位 VSENSE は以下の式で示すように変化する。

【0062】

【数3】

$$VSENSE(t) = VVCHG + \frac{LX \times k}{CC3} \times t$$

【0063】

なお、ここでは説明のために受光センサー 350P-1 及び遮光センサー 350D-1、及び引き回し配線での付加容量を無視して説明をしている。これらの付加容量分は上記の CC3 に加算すればよい。また、受光センサー 350P-1 及び遮光センサー 350D-1、及び引き回し配線での付加容量が十分大きい場合は第3のコンデンサー C3 は無くても良い。従って、CC3 の値は受光センサー 350P-1 及び遮光センサー 350D-1、及び引き回し配線の付加容量から下限が決定される。

【0064】

$VA(t)$  は  $VSENSE(t)$  が変化すると容量結合で同じ電位分変化する。従って、ノードAの電位  $VA$  は以下のような式で表される。

【0065】

【数4】

$$VA(t) = VS - \frac{CC2}{CC1} \times (VVSH - VVSL) + \frac{LX \times k}{CC3} \times t$$

【0066】

ここで  $VA(t) = VS$  となる時間  $t_0$  は、以下のような式で表される。

【0067】

【数5】

$$t_0 = \frac{CC2 \times CC3}{CC1 \times LX \times k} \times (VVSH - VVSL)$$

【0068】

すなわち、時間  $t_0$  で OUT 出力は Low (0V) → High (5V) へと反転することになり、この時間  $t_0$  から外光強度  $LX$  は容易にもとまる。

【0069】

検出回路 360 は RST配線が Low (0V) である間、ノードAがフローティング状態となり、ここに電磁ノイズが進入してノードAの電位が変化すると誤動作する。従って、電磁ノイズの防止が極めて重要であり、このためにシールド電極 369 を配置している。

【0070】

さて本構成のようなラテラル構造の PIN 型ダイオードや PN 型ダイオードは垂直方向の電界に対して光電流量  $I_{photo}$  が変化するという問題がある。本実施例にあわせて

10

20

30

40

50

具体的に言うと、配線 PBT に接続される透明電極 612P-1 ~ 612P-6 とバックライト遮光電極 611P-1 ~ 611P-6 の電位（以下、VPBT）が受光センサー 350P-1 ~ 350P-6 の特性に、配線 DBT に接続される透明電極 612D-1 ~ 612D-6 とバックライト遮光電極 611P-1 ~ 611P-6 の電位（以下、VDBT）が遮光センサー 350D-1 ~ 350D-6 の特性に、それぞれ影響する。VPBT 及び VDBT の最適電位は製造ばらつきによって製品毎に異なるが、これらは薄膜トランジスターの閾値（Vth）と強い相関を持つ。本実施例では薄膜トランジスターの閾値（Vth）をもとに電圧を自己補正した電位 VPBT と電位 VDBT をそれぞれ配線 PBT と配線 DBT に印加する自己補正電圧回路 361 を用いている。本実施例での製造ばらつき中の平均的な値では、 $V_{thN} = +1.0$ 、 $V_{thP} = -1.0$  であって、このとき自己補正電圧回路 361 は配線 PBT には 3.6V が、配線 DBT には 1.4V を印加する。受光センサー 350P-1 ~ 350P-6 ではカソードは配線 VSH と接続され 5.0V であるから、バックライト遮光電極 611P-1 ~ 611P-6 及び透明電極 612P-1 とカソードの電位差は -1.4V となり、これが光電流を得られる最適電位となる。製造ばらつきでトランジスターの特性が変動し、例えば  $V_{thN} = +1.5$ 、 $V_{thP} = -0.5$  であれば配線 PBT には 4.1V が、配線 DBT には 1.9V が印加される。同様に例えば  $V_{thN} = +0.5$ 、 $V_{thP} = -1.5$  であれば配線 PBT には 3.1V が、配線 DBT には 0.9V がそれぞれ印加される。いずれの場合もトランジスターのしきい値が変動するとそれにあわせて配線 PBT と配線 DBT に印加される電位 VPBT、VDBT も変動するので、常に光電流がほぼ最大に得られるのである。

#### 【0071】

本実施例では、中央演算回路 781 が端子 OUT の信号を監視し、反転した時間 t0 から離散値 V10 をまず得る。離散値 V1 は任意の回数サンプリングされ、この平均値 V10\_を得る。この V10\_ から参照テーブル 785 を参照し、V10\_ に対応する適切なバックライトユニット 926 の電圧設定値 V20 を得る。中央演算回路 781 はこの V20 値を外部電源回路 784 に送ることでバックライトユニット 926 の輝度が変更される。これにより液晶表示装置 910 の全白表示時輝度が変化し、ユーザーにとって過剰な輝度を抑えることで視認性を向上させるとともに消費電力の増大を抑えることができるのである。

#### 【0072】

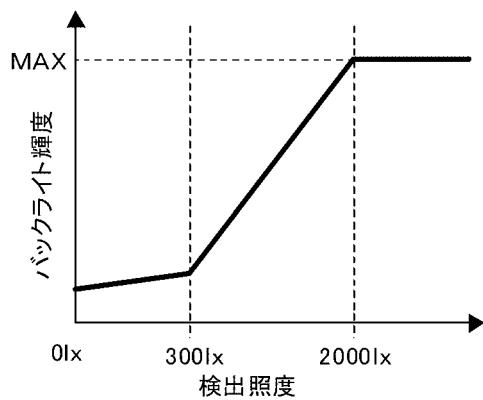

本実施例では外部光の検出照度とバックライト輝度の関係は図 15 のように設定した。検出照度 300（ルクス）まではバックライトの照度を緩やかに上げ、300 ルクス以上では比較的傾きを大きくして照度を上げる。検出照度 2000 ルクスで輝度は MAX となって以降は同じ状態となる。このように設定すると、外光が 300 ルクス以下で周囲がごく暗く、ユーザーの瞳孔が開いている時にはまぶしくない程度にバックライトを抑え、300 ルクス ~ 2000 ルクスまでの外光が液晶パネルに映り込む領域では周囲の明るさに合わせて輝度を急速に上げて視認性を低下させないことが出来る。

#### 【0073】

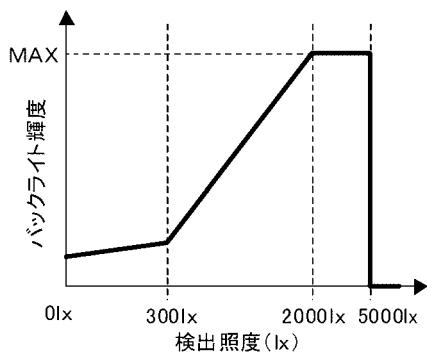

一方、本実施例のように透過型ではなく、半透過型液晶を使う場合は図 16 のようにすればよい。外光照度 5000 ルクスまでは同様であるが、それ以上では反射部分だけで十分な視認性になるため、バックライトを完全に OFF し、消費電力を節約できるようになっているため、特に屋外で使用すると搭載する電子機器のバッテリー駆動時間が飛躍的に延びる。

#### 【0074】

もちろん、この制御カーブは一例であって、用途に応じ、どのようなカーブの設定にしてもよいし、ちらつきを抑えるためにカーブにヒステリシスを持たせるなどしてもよい。また、測定毎に輝度調整するのではなく、複数回数を測定し、平均や中央値をとって輝度を調整するなどしてもよい。

#### 【0075】

[ 第 2 の実施の形態 ]

10

20

30

40

50

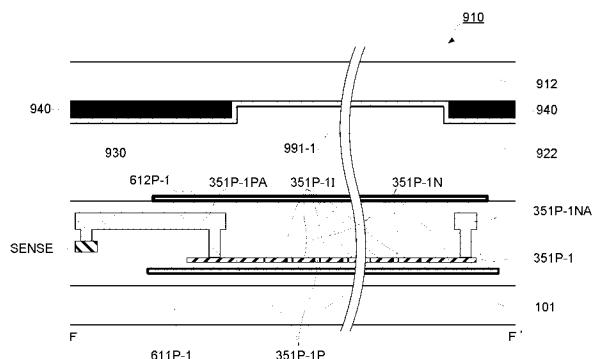

図17は第2の実施例に係る受光センサー351P-1(第1の光センサー)と遮光センサー351D-1(第2の光センサー)付近の拡大平面図であって、第1の実施例の図8にかわる図面である。図18は図17のF-F'に沿った断面図であり、第1の実施例の図9にかわる図面である。以下、第1の実施例での受光センサー350P-1と遮光センサー350D-1との差異について説明する。

#### 【0076】

受光センサー351P-1は70個のアノード領域351P-1Pと、70個のカソード領域351P-1Nと、これらに挟まれた70個の受光部351P-1Iとによって構成される。なお、図17、図18においては図面の見易さを優先し、70個全てを図示していない。アノード領域351P-1Pを構成する各領域は幅4μm・長さ70μmであり、カソード領域351P-1Nを構成する各領域は幅4μm・長さ70μmであり、受光部351P-1Iを構成する各領域は幅10μm・長さ70μmである。これらの各領域が形成するPIN接合面は第1の実施例とは90度異なり、受光開口部991-1の短手方向に配置されている。アノード領域351P-1Pの各領域はアノード主配線351P-1PAに接続され、カソード領域351P-1Nの各領域はカソード主配線351P-1NAに接続され、アノード主配線351P-1PA及びカソード主配線351P-1NAはデータ線202-mを構成するアルミニウム合金薄膜(ALNd)と同一の膜で形成される金属配線と、ポリシリコン薄膜を積層してコンタクトホールで接続することによって形成することで比抵抗を下げている。一方、アノード領域351P-1Pとカソード領域351P-1Nはポリシリコン薄膜によってのみ形成され、アノード領域351P-1Pは高濃度のボロンイオン、カソード領域351P-1Nは高濃度のリンイオンをそれぞれドープされて形成されている。受光部351P-1Iもポリシリコン薄膜で形成されるが、ボロンイオン及びリンイオンは殆ど含まれていない。アノード主配線351P-1PAは配線SENSEに、カソード主配線351P-1NAは配線VSHにそれぞれ接続され、適切な電位を印加される。受光センサー351P-1は受光開口部991-1と重なってなり、受光開口部991-1の開口サイズは10mm×0.1mmとなっている。遮光センサー351D-1は受光開口部991-1と重ならない点を除いて受光センサー351P-1と同様の構成であるので説明を省略する。

#### 【0077】

この他の点については第1の実施例の図8、図9と何らかわりはないので、同じ記号を付与することで説明は省略する。また受光センサー351P-2～351P-6は受光センサー351P-1に、遮光センサー351D-2～351D-6は遮光センサー351D-1に、受光開口部991-2～991-6は受光開口部991-1に配置場所を除いて同一であるので説明は省略する。

#### 【0078】

また、本実施例のフォトセンサーを搭載したアクティブマトリクス基板の例は第1の実施例でのアクティブマトリクス基板101において、受光開口部990-1～990-6を受光開口部991-1～991-6に、受光センサー350P-1～350P-6を受光センサー351P-1～351P-6に、遮光センサー350D-1～350D-6を遮光センサー351D-1～351D-6に、それぞれ置き換えるだけであり、液晶表示装置910及び電子機器の構成も第1の実施例と同様であるのでそれぞれの説明は省略する。

#### 【0079】

このように構成すると、受光センサー351P-1～351P-6、遮光センサー351D-1～351D-6のチャネル幅はそれぞれ総計29400μmであって、開口部の面積が小さいにも係らず、第1の実施例のさらに1.4倍の光電流が得られる。これは各アノード領域351P-1P、カソード領域351-1Nを金属配線と重ねないためにコンタクトホールが不要であり、幅を4ミクロンと狭く設定しているためである。各アノード領域351P-1P、カソード領域351-1Nは開口部の短軸方向に配置されてごく短いため、幅が狭いにも係らず抵抗は第1の実施例の1/5以下と低いので光センサーの

能力が高く、電流が大きく流れても抵抗による電位変動は第1の実施例以上に問題にならない。一方、長軸方向に引き回すアノード主配線351P-1PAおよびカソード領域351P-1Nは金属配線と重ねているため、これも抵抗は問題ない。また、受光開口部991-1の短軸方向の幅は狭くすることでアノード主配線351P-1PAおよびカソード領域351P-1Nの金属は受光開口部991-1にからず、従って受光開口部991-1が目立つことが無く、デザイン性を損なわない。なお、受光効率や角度依存性を優先する場合は受光開口部991-1の幅をより広くとり、アノード主配線351P-1PAおよびカソード主配線351P-1NAを受光開口部991-1と重ねても構わない。

## 【0080】

10

このように構成することで、本実施例では角度依存性に優れ、かつ配線の抵抗による電位変動が無く、光電流が十分確保できるフォトダイオードを提供できるものである。

## 【0081】

なお、今回開示された実施形態は、すべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は、上記した実施形態の説明ではなく特許請求の範囲によって示され、さらに特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれる。

## 【0082】

20

## [産業上の利用可能性]

本発明は実施例の形態に限定されるものではなく、TNモードではなく垂直配向モード(VAモード)、横電界を利用したIPSモード、フリンジ電界を利用したFFSモードなどの液晶表示装置に利用しても構わない。また、全透過型のみならず全反射型、反射透過兼用型であっても構わない。また、液晶表示装置ではなく、有機ELディスプレイ、フィールドエミッショントransistor型ディスプレイに用いても良いし、液晶表示装置以外の半導体装置に用いても良い。

## 【0083】

また、本実施例で示したような外光にあわせた表示輝度の制御だけでなく、表示装置の輝度や色度を測定してこれをフィードバックし、ムラや経年変化のない表示装置に用いても構わない。

## 【図面の簡単な説明】

30

## 【0084】

【図1】本発明の実施例に係る液晶表示装置910の斜視図。

【図2】本発明の第1の実施例に係るアクティブマトリクス基板101の構成図。

【図3】本発明の実施例に係るアクティブマトリクス基板101の画素回路図。

【図4】本発明の電子機器の実施例を示すブロック図。

【図5】本発明の実施例に係るアクティブマトリクス基板101の画素部の平面図。

【図6】図5A-A'に沿った断面図。

【図7】図5B-B'に沿った断面図。

【図8】本発明の第1の実施例に係る受光センサー350P-1、遮光センサー350D-1の平面図。

40

【図9】図8C-C'に沿った断面図。

【図10】図8D-D'に沿った断面図。

【図11】本発明の第1の実施例に係る受光センサー350P-1～350P-6、遮光センサー350D-1～350D-6の等価回路図。

【図12】本発明の第1の実施例に係る受光センサー350P-1～350P-6、遮光センサー350D-1～350D-6の簡略化した等価回路図。

【図13】本発明の第1の実施例に係る受光センサー350P-1～350P-6、遮光センサー350D-1～350D-6を構成するPINダイオードの特性を示したグラフ。

【図14】本発明の第1の実施例に係る検出回路360の回路図。

50

【図15】本発明の実施例に係る外部光の検出照度とバックライト輝度の設定図。

【図16】半透過液晶表示装置のための外部光の検出照度とバックライト輝度の設定図。

【図17】本発明の第2の実施例に係る受光センサー351P-1、遮光センサー351D-1の平面図。

【図18】図17F-F'に沿った断面図。

【図19】従来例の説明に係る受光センサー359P-1、遮光センサー359D-1の平面図。

【図20】図19E-E'に沿った断面図。

【符号の説明】

【0085】

101...アクティブマトリクス基板、102...張り出し部、201-1~201-480...走査線、202-1~202-1920...データ線、301...走査線駆動回路、302...データ線駆動回路、320...信号入力端子、330-1~330-2...対向導通部、335...共通電位配線、350P-1~350P-6, 351P-1~351P-6...受光センサー、350D-1~350D-6, 351D-1~351D-6...遮光センサー、360...検出回路、361...自己補正電圧回路、611P-1~611P-6, 611D-1~611D-6...バックライト遮光電極、612P-1~612P-6, 612D-1~612D-6...透明電極、781...中央演算回路、784...外部電源回路、910...液晶表示装置、911...液晶パネル(本発明の「パネル」の一例)、912...対向基板、922...ネマティック相液晶材料、923...シール材、926...バックライトユニット、927...導光板、940...ブラックマトリクス、990-1~990-6, 991-1~991-6...受光開口部、LA...外光、LB...バックライト光。 20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図13】

【図12】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

---

フロントページの続き

(56)参考文献 特開2002-314117(JP,A)

特開2006-118965(JP,A)

特開2005-72387(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 31/10 - 31/119