# WORLD INTELLECTUAL PROPERTY ORGANIZATION

### INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(51) International Patent Classification 6:

C23C 16/56, 16/40, H01L 21/3105

(11) International Publication Number:

WO 99/64645

(43) International Publication Date:

16 December 1999 (16.12.99)

(21) International Application Number:

PCT/US99/13300

**A1**

US

(22) International Filing Date:

11 June 1999 (11.06.99)

(30) Priority Data:

09/096,858

12 June 1998 (12.06.98)

**Published**

With international search report.

Before the expiration of the time limit for amending the claims and to be republished in the event of the receipt of amendments.

DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT,

(81) Designated States: JP, KR, European patent (AT, BE, CH, CY,

(71) Applicant: APPLIED MATERIALS, INC. [US/US]; 3050 Bowers Avenue, Santa Clara, CA 95054 (US).

(72) Inventors: NARWANKAR, Pravin, K.; 392 Waverly Street, Sunnyvale, CA 94086 (US). SAHIN, Turgut; 11110 Chadwick Place, Cupertino, CA 95014 (US). URDAHL, Randall, S.; 1361 Ormonde Way, Mountain View, CA 94043 (US). VELAGA, Ankineedu; 8802 Heritage Bay Circle, Orlando, FL 32826 (US). LIU, Patricia; 18813 Bellgrove Circle, Saratoga, CA 95070 (US).

(74) Agents: BERNADICOU, Michael, A. et al.; Blakely, Sokoloff, Taylor & Zafman LLP, 7th floor, 12400 Wilshire Boulevard, Los Angeles, CA 90025 (US).

(54) Title: A METHOD AND APPARATUS FOR THE FORMATION OF DIELECTRIC LAYERS

#### (57) Abstract

A method and apparatus for forming and annealing a dielectric layer. According to the present invention an active atomic species is generated in a first chamber. A dielectric layer formed on a substrate is then exposed to the active atomic species in a second chamber, wherein the second chamber is remote from the first chamber.

### FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

| AL | Albania                  | ES | Spain               | LS | Lesotho               | SI                     | Slovenia                 |

|----|--------------------------|----|---------------------|----|-----------------------|------------------------|--------------------------|

| AM | Armenia                  | FI | Finland             | LT | Lithuania             | SK                     | Slovakia                 |

| AT | Austria                  | FR | France              | LU | Luxembourg            | SN                     | Senegal                  |

| AU | Australia                | GA | Gabon               | LV | Latvia                | SZ                     | Swaziland                |

| ΑZ | Azerbaijan               | GB | United Kingdom      | MC | Monaco                | TD                     | Chad                     |

| BA | Bosnia and Herzegovina   | GE | Georgia             | MD | Republic of Moldova   | TG                     | Togo                     |

| BB | Barbados                 | GH | Ghana               | MG | Madagascar            | TJ                     | Tajikistan               |

| BE | Belgium                  | GN | Guinea              | MK | The former Yugoslav   | TM                     | Turkmenistan             |

| BF | Burkina Faso             | GR | Greece              |    | Republic of Macedonia | TR                     | Turkey                   |

| BG | Bulgaria                 | HU | Hungary             | ML | Mali                  | TT                     | Trinidad and Tobago      |

| BJ | Benin                    | IE | Ireland             | MN | Mongolia              | UA                     | Ukraine                  |

| BR | Brazil                   | IL | Israel              | MR | Mauritania            | $\mathbf{UG}$          | Uganda                   |

| BY | Belarus                  | IS | Iceland             | MW | Malawi                | US                     | United States of America |

| CA | Canada                   | IT | Italy               | MX | Mexico                | UZ                     | Uzbekistan               |

| CF | Central African Republic | JP | Japan               | NE | Niger                 | VN                     | Viet Nam                 |

| CG | Congo                    | KE | Kenya               | NL | Netherlands           | YU                     | Yugoslavia               |

| CH | Switzerland              | KG | Kyrgyzstan          | NO | Norway                | $\mathbf{z}\mathbf{w}$ | Zimbabwe                 |

| CI | Côte d'Ivoire            | KP | Democratic People's | NZ | New Zealand           |                        |                          |

| CM | Cameroon                 |    | Republic of Korea   | PL | Poland                |                        |                          |

| CN | China                    | KR | Republic of Korea   | PT | Portugal              |                        |                          |

| CU | Cuba                     | KZ | Kazakstan           | RO | Romania               |                        |                          |

| CZ | Czech Republic           | LC | Saint Lucia         | RU | Russian Federation    |                        | <b>-</b> ·               |

| DE | Germany                  | LI | Liechtenstein       | SD | Sudan                 |                        |                          |

| DK | Denmark                  | LK | Sri Lanka           | SE | Sweden                |                        |                          |

| EE | Estonia                  | LR | Liberia             | SG | Singapore             |                        |                          |

|    |                          |    |                     |    |                       |                        |                          |

# A METHOD AND APPARATUS FOR THE FORMATION OF DIELECTRIC LAYERS

#### **BACKGROUND OF THE INVENTION**

#### 1. FIELD OF THE INVENTION

The present invention relates to the field of dielectric formation and more specifically to a method and apparatus for annealing a dielectric film.

#### 2. DISCUSSION OF RELATED ART

Integrated circuits are made up of literally millions of active and passive devices such as transistors, capacitors and resistors. In order to provide more computational power and/or more storage capability in an integrated circuit, device features are reduced or scaled down in order to provide higher packing density of devices. An important feature to enable scaling of devices is the ability to form high quality, high dielectric constant films for capacitor and gate dielectrics.

High dielectric constant films are generally ceramic films (i.e., metaloxides) such as tantalum pentaoxide and titanium oxide. When these films are deposited they tend to have vacancies at the anionic (oxygen) sites in the lattice. Presently these vacancies are filled by annealing the film in a gas mixture which can provide an active species to occupy the lattice vacancies. For example, furnace anneals and rapid thermal oxidation (RNO) are presently used to anneal dielectric films. In such processes a substrate is placed in a furnace or a chamber of a rapid thermal apparatus and heated to a high temperature, greater than 800°C, while an anneal gas such as O<sub>2</sub> or N<sub>2</sub> is fed directly into the furnace or chamber, respectively, where the substrate is

located. These processes must be performed at very high temperatures, greater than 800°C, in order to generate the active species from the anneal gas.

A problem with utilizing such high anneal temperatures is that dielectric films such as tantalum pentaoxide crystallize when exposed to high temperatures which can lead to high leakage currents. Additionally high anneal temperatures can cause other ions to diffuse into the film, especially at the interfaces of the devices, and cause poor electrical performance. Still further, many modern high density processes require a reduced thermal budget in order to prevent or minimize dopant diffusion or redistribution in a device. Still further some processes utilize materials with low melting points which preclude subsequent use of high temperature processing.

Thus, what is desired is a method and apparatus for forming a high quality, high dielectric constant dielectric film at a low temperature.

#### **SUMMARY OF THE INVENTION**

A method and apparatus for annealing a dielectric layer is described. According to the present invention active atomic species are generated in a first chamber. A dielectric layer formed on a substrate is then exposed to the active atomic species in a second chamber which is remote from the first chamber.

#### BRIEF DESCRIPTION OF THE DRAWINGS

**Figure 1** is a flow chart which illustrates a process of forming a dielectric layer in accordance with the present invention.

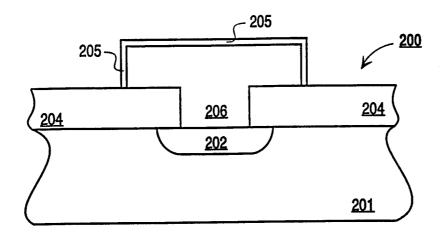

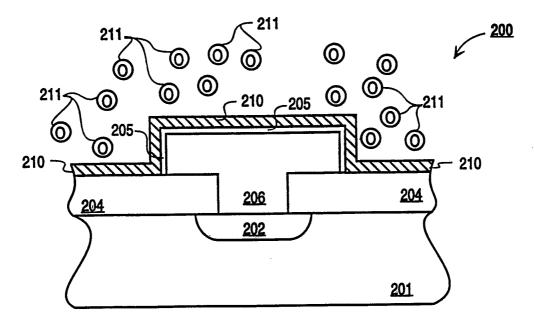

**Figure 2a** is an illustration of a cross-section view of a substrate including a interlayer dielectric and a bottom electrode.

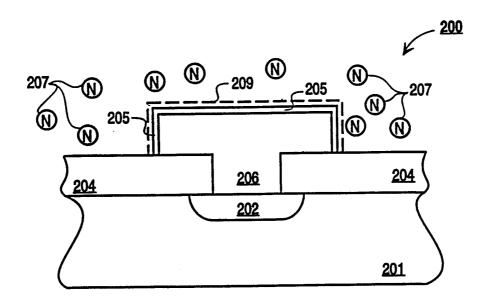

**Figure 2b** is an illustration of a cross-sectional view showing the passivation of the substrate of figure 2a.

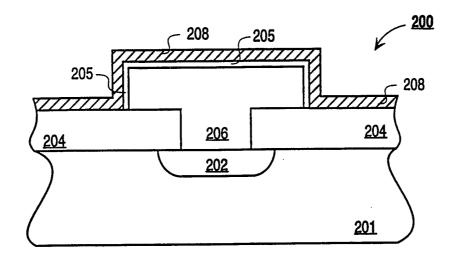

**Figure 2c** is an illustration of a cross-sectional view showing the formation of a dielectric film on the substrate of Figure 2b.

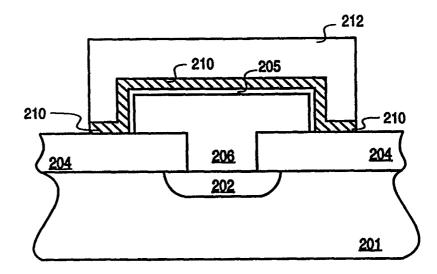

Figure 2d is an illustration of a cross-sectional view showing the formation of an annealed dielectric film on the substrate of Figure 2b.

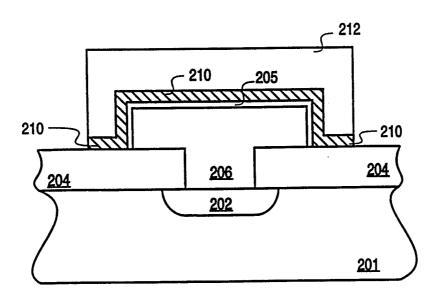

**Figure 2e** is an illustration of a cross-sectional view showing the formation of a top electrode on the substrate of Figure 2d.

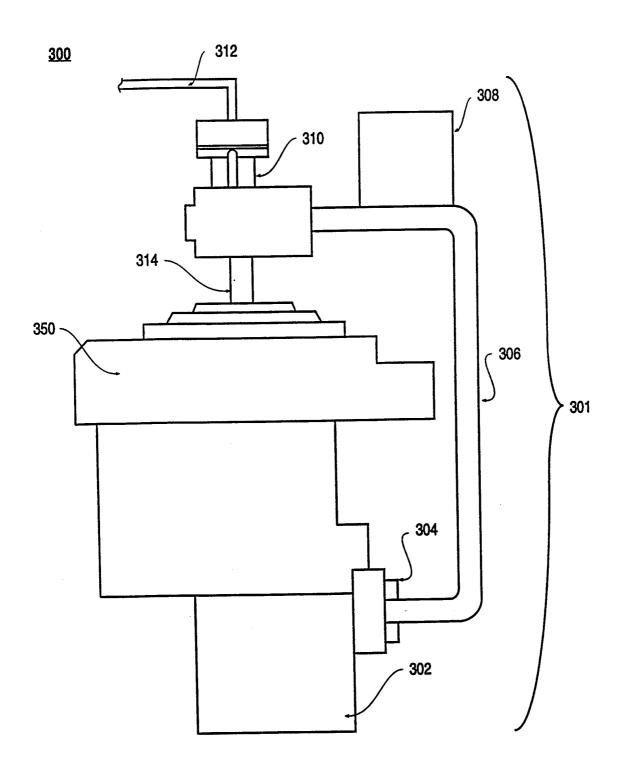

Figure 3a is an illustration of an apparatus which may be utilized to anneal a dielectric layer in accordance with the present invention.

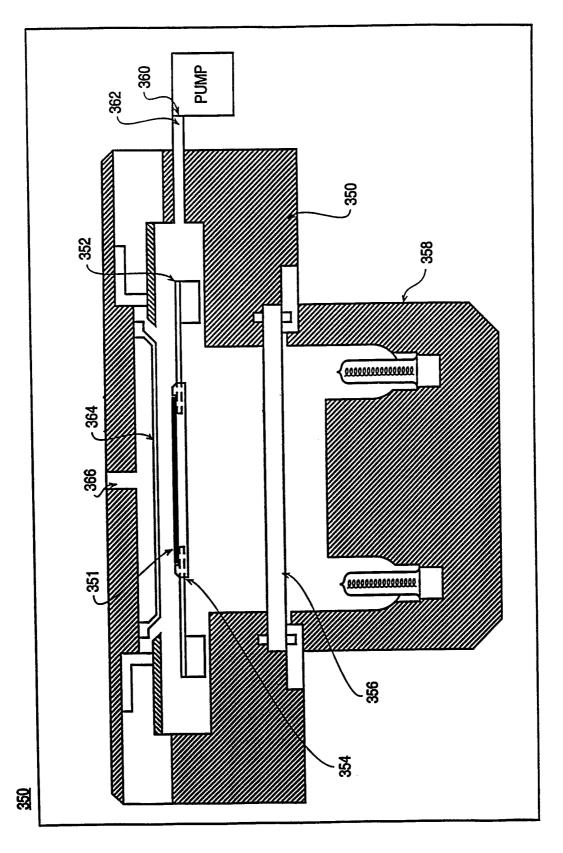

**Figure 3b** is an illustration of a chamber which may be used in the apparatus of Figure 3a.

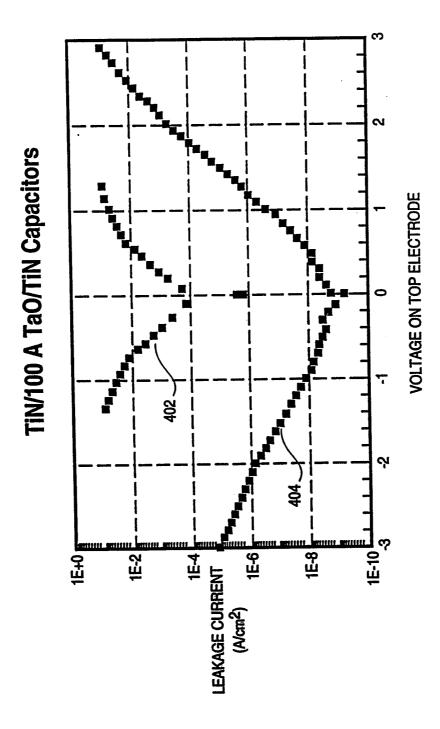

**Figure 4** is a graph which illustrates how leakage current varies for different electrode voltages for a capacitor formed with a unannealed tantalum pentaoxide dielectric layer and for a capacitor formed with a tantalum pentaoxide dielectric layer annealed with remotely generated active atomic species.

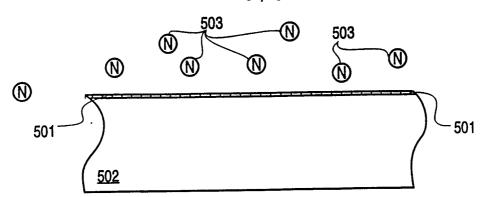

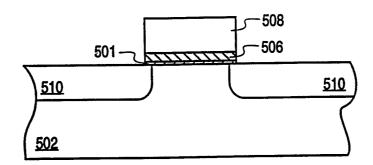

**Figure 5a** is an illustration of a cross-section view of a substrate having been passivated with active atomic species.

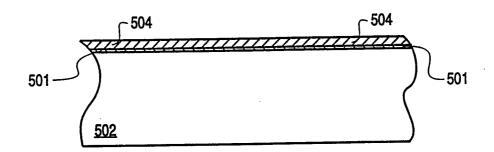

**Figure 5b** is an illustration of the cross-sectional view as showing the formation of the dielectric film on the substrate of Figure 5a.

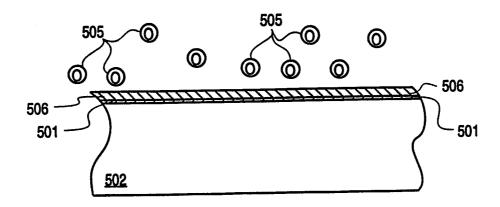

Figure 5c is an illustration of cross-sectional view showing the formation of an annealed dielectric on the substrate of Figure 5a.

Figure 5d is an illustration of the cross-sectional view showing the formation of a gate electrode and source/drain regions on the substrate of Figure 5c.

#### DETAILED DESCRIPTION OF THE PRESENT INVENTION

The present invention describes a novel method and apparatus for annealing a dielectric film. In the following description numerous specific details such as specific equipment configurations, and process parameters are set forth in order to provide a thorough understanding of the present invention. One skilled in the art will appreciate the ability to use alternative configurations and process details to the disclosed specifics without departing from the scope of the present invention. In other instances, well known semiconductor processing equipment and methodology have not been described in detail in order to not unnecessarily obscure the present invention.

The present invention describes a novel method and apparatus for passivating and/or annealing films. According to the present invention highly reactive atomic species are used to nitridate, passivate, deposit and anneal films. The highly reactive atomic species are formed in a plasma created by exposing an anneal gas such as  $O_2$  and  $N_2O$ , and  $N_2$  to microwaves. The plasma creates electrically neutral highly energized atoms from the molecular anneal gas. The plasma used to generate the active atomic species is created in a cavity or chamber which is separate (remote) from the chamber in which the substrate to be annealed or passivated is located. Because the atomic species are in a highly energized state when they enter the anneal chamber, they readily react with films and substrates, and so do not require high substrate

temperatures to initiate reaction. Because the present invention utilizes remotely generated highly reactive atomic species low substrate temperatures, less than or equal to 400°C, can be used nitridating, passivating, depositing, and annealing films and substrate. The low temperature processes of the present invention can substantially reduce the thermal budget necessary to manufacturer integrated circuits. Additionally because the active atomic species are remotely generated, the substrate to be annealed or passivated is not exposed to the harmful plasma used for generating the active atomic species.

In one embodiment of the present invention remotely generated active atomic species are used to passivate a silicon substrate prior to the formation of a gate dielectric layer or are used to passivate a capacitor electrode prior to the formation of a capacitor dielectric layer thereon. It is to be appreciated that as gate and capacitor dielectric film thicknesses shrink, to enable the fabrication of high density integrated circuits, the atomic level interfaces between the substrate and dielectric are becoming increasingly more important for device reliability and performance. By passivating a substrate with remotely generated active atomic species one can improve the atomic level interfaces between the substrate and the dielectric film and thereby improve device reliability and performance.

In another embodiment of the present invention, remotely generated active atomic species are used to anneal an active dielectric film, such as a gate dielectric or a capacitor dielectric. According to this embodiment of the present invention a dielectric film is deposited over substrate. The dielectric film is then exposed to remotely generated active atomic species, such as reactive oxygen atoms or reactive nitrogen atoms. The highly energized atomic species readily react with the dielectric film to fill vacancies in the lattice which left unfilled can lead to high leakage currents and poor device performance. The remotely generated active atomic species can be used to anneal a wide range of dielectrics such as but not limited to silicon oxides, such as silicon dioxide and

silicon oxynitride, transition-metal dielectrics such as tantalum pentaoxide ( $Ta_2$   $O_5$ ), titanium oxide ( $TiO_2$ ) and titanium doped tanatalum pentaoxide, as well as ferroelectric and piezoelectric dielectrics such as BST, and PZT. Additionally, active atomic species, such as reactive nitrogen atoms can be used to anneal dielectric barrier layers, such as silicon nitride, to improve their barrier qualities.

In an embodiment of the present invention the remotely generated active atomic species are provided into the deposition chamber while the dielectric film is being deposited. In this way the dielectric film is annealed as it is deposited thereby eliminating the need for a separate anneal step.

As such remotely generated active atomic species can be used in all phases of dielectric film formation including substrate passivation prior to dielectric layer deposition, annealing during dielectric deposition and annealing after dielectric deposition. In this way high quality, high performance capacitor and gate dielectrics as well as barrier layers can be fabricated.

In one specific embodiment of the present invention, remotely generated reactive oxygen atoms are used to anneal a transition-metal dielectric used as a capacitor dielectric in a dynamic random access memory (DRAM). In this embodiment of the present invention a transition-metal dielectric film is formed by chemical vapor deposition (CVD) over a bottom electrode of a DRAM cell. The transition-metal film is then annealed at a temperature less than 400°C with reactive oxygen atoms formed in a chamber separate from the anneal chamber. The remotely generated reactive oxygen atoms readily react with the deposited transition-metal film and satisfy open sites in the film. Additionally, the reactive oxygen atoms remove carbon contaminates by chemically reacting with carbon and forming carbon dioxide (CO<sub>2</sub>) vapor which is then exhausted from the chamber. By annealing the dielectric film with remotely generated reactive oxygen atoms, the leakage current of the film can be substantially reduced. A top capacitor electrode can then be formed on

the high quality high dielectric constant film thereby improving the performance and reliability of the fabricated cell.

A method of forming and annealing a dielectric layer in accordance with the present invention will be described in reference to Figure 1 and Figures 2a-2e. Figure 1 illustrates a flow chart which depictsasingle process which utilizes the different nitridation, passivation, deposition, and anneal processes of the present invention. Figures 2a-2e illustrate an embodiment of the present invention where the processes of the present invention are used to form a capacitor of a DRAM cell. It is to be appreciated that these specific details are only illustrative of an embodiment of the present invention and are not to be taken as limiting to the present invention. Additionally, it is to be appreciated that the nitridation, passivation, deposition and anneal processes of the present invention need not all be used in a single process and can be used independently or in different combination with one another to form a wide variety of different integrated circuits.

An example of an apparatus 300 which can be used to provide active atomics species for the anneal and/or passivation steps of the present invention is illustrated in Figures 3a and 3b. An example of a commercially available apparatus which can be used to provide active atomic species is the Applied Materials Centura Advanced Strip Passivation Plus (ASP) chamber. Apparatus 300 includes a remote plasma generator 301 which generates and provides active atomic species to a process chamber 350 in which the substrate to be passivated or annealed is located. Remote plasma generator 301 includes a magnatron 302 which generates microwaves with a microwave source. Magnatron 302 can preferably generate up to 10,000 watts of 2.5 Ghz microwave energy. It is to be noted that the amount of power required is dependent (proportional) to the size of anneal chamber 350. For an anneal chamber used to process 300mm wafers, 10,000 watts of power should be sufficient. Although a microwave source is used to generate a plasma in apparatus 300, other energy sources such as radio frequency (RF) may be used.

Magnatron 302 is coupled to an isolator and dummy load 304 which is provided for impedance matching. The dummy load absorbs the reflected power so no reflective power goes to the magnatron head. Isolator and dummy load 304 is coupled by a wave guide 306, which transmits microwave energy to an autotuner 308. Autotuner 308 consist of an impedance matching head and a separate detector module that uses three stepper motor driven impedance matching stubs to reduce the reflective power of the microwave energy directed to the power source. Autotuner 308 focuses the microwave energy into the center of a microwave applicator cavity (or chamber) 310 so that energy is absorbed by annealed gas fed into the applicator cavity 310. Although an autotuner is preferred a manual tuner may be employed.

Applicator 310 uses microwave energy received from magnatron 302 to create a plasma from the anneal gas as it flows down through a quartz plasma tube located inside applicator 310. A source 312, such as a tank, of a anneal gas such as but not limited to  $O_2$ ,  $N_2O$ , and  $N_2$  used for generating the active atomic species is coupled to microwave applicator 310. Additionally, a source of an inert gas such as argon (Ar) or helium (He) can also be coupled to applicator 310. A prefire mercury lamp can be used to radiate ultraviolet light into the plasma tube to partially ionize the process gases and thereby make it easier for the microwave energy to ignite the plasma.

The microwave energy from magnetron 302 converts the anneal gas into a plasma which consist of essentially three components; ionized or charged atoms (radicals), activated (reactive) atomic species, and nondissociated anneal gas. For example when  $O_2$  is the anneal gas, microwave energy disassociates the  $O_2$  gas into oxygen radicals, reactive oxygen atoms, and some anneal gas remains as  $O_2$  molecules. When  $N_2$  is the anneal gas, microwaves disassociate the  $N_2$  gas into nitrogen radicals, reactive nitrogen atoms, and some anneal gas remains as  $N_2$  molecules. Reactive atomic species such as reactive oxygen atoms or reactive nitrogen atoms are not charged or ionized but are highly energized atoms. Because the reactive atomic species are highly energized they

are in a highly reactive state so they readily react with dielectric films to fill vacancies therein or to passivate films or substrates. Because the atomic species are highly energized when they enter anneal chamber 350, high temperatures are not necessary in chamber 350 to activate the anneal gas.

Applicator 310 is bolted to the lid of chamber 350. The concentrated plasma mixture flows downstream through conduit 314 to chamber 350. As a plasma flows through the conduit 314 the ionized atoms become electrically neutral before reaching chamber 350 and become highly reactive atomic species. Thus, only electrically neutral, highly reactive atoms flow into chamber 350. Although the process gas at this point is highly reactive, the mixture is no longer electrically damaging to the substrate or electrical devices such as transistors formed therein. Because the active atomic species are generated at location (chamber 310) which is separate or remote from the chamber 350 in which the substrate to be annealed is located, the active atomic species are said to be "remotely generated".

Chamber of 350 of apparatus 300, as shown in Figure 3b, includes a wafer support 352 for supporting a wafer or substrate 351 face up in chamber 350. Wafer support 352 can include an aluminum chuck 354. Chamber 350 includes a quartz window 356 through which infrared radiation from a plurality (14) of quartz tungsten halogen lamp 358 is transmitted. During processing, the lamps mounted directly below the process chamber radiantly heat the chuck which in turn heats the wafer by conduction. A closed loop temperature control system senses the temperature of the substrate or wafer using a thermocouple mounted in the chuck. The temperature control system regulates the temperature of the wafer by varying the intensity of lamps 358. Although lamps are preferably used as the heat source for heating the wafer, other heat sources, such as resistive heaters, can be used. A vacuum source 360, such as the pump, is coupled to an exhaust outlet 362 and controls the chamber pressure and removes gas by products. A shower head or gas distribution plate 364 is mounted directly above the wafer. Shower head 364

consist of three quartz plates having a plurality of holes formed therein to evenly distribute the active atomic species over the wafer as they flow through gas inlet 366.

In one embodiment of the present invention, chamber 350 is also configured to receive deposition gases used to deposit a film by chemical vapor deposition (CVD). In this way, a dielectric film can be annealed in the same chamber as used to deposit the film, or the dielectric film can be annealed as it is deposited. Additionally, chamber 350 can be a thermal reactor such as the Applied Material's Poly Centura single wafer chemical vapor deposition reactor or the Applied Material's RTP Centura with the honeycomb source, each configured to receive active atomic species from remote plasma generator 301. In one embodiment of the present invention apparatus 300 is part of a cluster tool which includes among other chambers, a chemical vapor deposition (CVD) chamber, a load lock, and a transfer chamber with a robot arm. Configuring the various chambers around a transfer chamber in the form of a cluster tool enables wafers or substrates to be transferred between the various chambers of the cluster tool without being exposed to an oxygen ambient.

The nitridation, passivation, deposition and anneal steps of the present invention occur on a substrate. For the purpose of the present invention a substrate is the material on which dielectric films are deposited and annealed in accordance with the present invention. The substrate can be a substrate used in the manufacturing of semiconductor products such as silicon substrates and gallium arsenide substrates and can be other substrates used for other purposes such as glass substrates used for the production of flat panel displays.

In one embodiment of the present invention, the substrate is a substrate used in the fabrication of a dynamic random access memory (DRAM) cells such as substrate 200 shown in Figure 2a. Substrate 200 includes well known silicon epitaxial substrate 201 having a doped region 202 and a patterned interlayer dielectric 204. A bottom capacitor electrode 206 is formed in contact with the

diffusion region 202 and over ILD 204. Bottom capacitor electrode 206 can be formed by any well known technique such as by blanket depositing a polysilicon layer by chemical vapor deposition (CVD) utilizing a reactive gas comprising silane (SiH<sub>4</sub>) and H<sub>2</sub> and then patterning the blanket deposited material into an electrode with well known photolithography and etching techniques. If bottom electrode 206 is a polysilicon electrode it will typically be doped to a density between  $2-5\times10^{20}$  atoms/cm<sup>3</sup>. Bottom electrode 206 can also be other types of capacitor electrodes such as but not limited to hemispherical grained polysilicon (HSG) or "rough poly" electrodes and metal electrodes such as titanium nitride (TiN) and tugsten (W) electrodes. In still other cases, the monocyrstalline silicon substrate 201 can act as the bottom electrode.

The first step, in one embodiment of the present invention, as set forth in block 102 of flow chart 100, is to nitridate substrate 200 to form a thin, between 10-25Å, silicon nitride barrier layer 205 on bottom electrode 206 as shown in Figure 2a. Nitridating bottom electrode 206 is desirable when bottom electrode 206 is a silicon electrode. Silicon nitride film 205 forms an oxidation prevention barrier layer for bottom electrode 206. In this way, oxygen can not penetrate grain boundaries of polysilicon electrode 206 and form oxides therein which can lead to a decrease in the effective dielectric constant of a capacitor dielectric and to an increase in electrode resistance. Additionally, in well known capacitor structures where the monocrystalline silicon substrate 201 acts as the bottom electrode, nitridating substrate 201 is desirable.

A thin silicon nitride layer can be formed by nitridating substrate 200 by exposing substrate 200 to remotely generated reactive nitrogen atoms in anneal chamber 350 while substrate 200 is heated to a temperature between 700 - 900°C and chamber 350 maintain at a pressure between 0.5 torr - 2 torr. Reactive nitrogen atoms can be formed by flowing between 0.5 to 2 SLM of  $N_2$  or ammonia (NH $_3$ ) into cavity 310 and applying a power between 1400-5000 watts to magnatron 302 to create plasma from the  $N_2$  or NH $_3$  gas in cavity 310. The nitradation process forms silicon nitride only on those locations where

silicon is available to react with the reactive nitrogen atoms, such as polysilicon electrode 206 and not on those areas where no silicon is available for reaction such as ILD 206. A suitable silicon nitride layer 205 can be formed by nitridating substrate 200 with remotely generated reactive nitrogen atoms for between 30-120 seconds. Alternatively, a thin silicon nitride layer 205 can be formed by other well known techniques such as by thermal nitridation in a LPCVD batch type furnace.

Next, as set forth in step 104 of flow chart 100, in an embodiment of the present invention, substrate 200 is passivated with remotely generated reactive nitrogen atoms, as shown in Figure 2b, to cure defects in silicon nitride barrier layer 205. Silicon nitride barrier layer 205 can be passivated by placing substrate 200 on chuck 354 in chamber 350 and heating substrate 200 to a temperature between 300-500 while an N<sub>2</sub> anneal gas is fed into cavity 310 at a rate of between 0.5-2 SLM and a power of between 1400-5000 watts is provided to magnatron 302. Microwaves from magnatron 302 create a plasma in cavity 310 from the N<sub>2</sub> process gas. Highly reactive electrically neutral nitrogen atoms 207 then flow through conduit 314 into chamber 350 where they passivate 209 substrate 200. Exposing substrate 200 to active nitrogen atoms 207 can be used to stuff the capacitor electrode 206 with nitrogen atoms and thereby prevent subsequent oxidation of the capacitor electrode. Silicon nitride layer 205 can be sufficiently passivated by exposing substrate 200 to remotely generated reactive nitrogen atoms for between 30-120 seconds. Alternatively, silicon nitride barrier layer 205 can be passivated by subsituting forming gas (3-10% H, and 97-90% N,) for the N, anneal gas. The addition of hydrogen (H<sub>2</sub>) helps to cure defects and to remove contaminates.

Next, as set forth in block 106, a dielectric film is formed over substrate 200. In one embodiment of the present invention a high dielectric constant dielectric film 208 is blanket deposited over ILD 204 and bottom electrode 206 of substrate 200 as shown in Figure 2c. In an embodiment of the present invention the dielectric film is a transition metal dielectric film such as, but not

limited to, tantalum pentaoxide ( $Ta_2O_5$ ) and titanium oxide ( $TiO_2$ ). In another embodiment dielectric layer 208 is a tantalum pentaoxide film doped with titanium. Additionally dielectric layer 208 can be a composite dielectric film comprising a stack of different dielectric films such as a  $Ta_2O_5/TiO_2/Ta_2O_5$  stacked dielectric film. Additionally, dielectric layer 208 can be a piezoelectric dielectric such as Barium Strontium Titanate (BST) and Lead Zerconium Titanate (PZT) or a ferroelectric.

In other embodiments of the present invention dielectric layer 208 can be a silicon-oxide dielectric such as silicon dioxide and silicon oxynitride and composite dielectric stacks of silicon-oxide and silicon nitride film such as well known ONO and NO and nitrided oxides. The fabrication of such oxides are well known and can be used in the fabrication of gate dielectric layers and capacitor dielectrics. For example a low temperature silicon dioxide film can be formed by chemical vapor deposition utilizing a silicon source, such as TEOS, and an oxygen source, such as  $O_2$ .

In order to form a dielectric layer 208 onto substrate 200, the substrate can be placed into a thermal process chamber such as the chamber of an Applied Materials CVD single wafer reactor. Alternatively, substrate 201 can be placed or left in anneal chamber 350 configured to receive deposition gases. The substrate is then heated to a desired deposition temperature while the pressure within the chamber is pumped down (reduced) to a desired deposition pressure. Deposition gases are then fed into the chamber and a dielectric layer formed therefrom.

To blanket deposit a tantalum pentaoxide ( $Ta_2O_5$ ) dielectric film by thermal chemical vapor deposition a deposition gas mix comprising, a source of tantalum, such as but not limited to, TAETO [Ta (OC2H5)5] and TAT-DMAE [Ta (OC2H5)4 (OCHCH2 N(CH3)2], and source of oxygen such as  $O_2$  or  $N_2O$  can be fed into a deposition chamber while the substrate is heated to a deposition temperature of between 300-500°C and the chamber maintained at a deposition pressure of between 0.5 -10 Torr. The flow of deposition gas over

the heated substrate results in thermal decomposition of the metal organic Tacontaining precursor an subsequent deposition of a tantalum pentaoxide film. In one embodiment TAETO or TAT-DMAE is fed into the chamber at a rate of between 10 - 50 milligrams per minute while  $O_2$  or  $N_2O$  is fed into the chamber at a rate of 0.3 - 1.0 SLM. TAETO and TAT-DMAE can be provided by direct liquid injection or vaporized with a bubbler prior to entering the deposition chamber. A carrier gas, such as  $N_2$ ,  $H_2$  and He, at a rate of between 0.5-2.0 SLM can be used to transport the vaporized TAETO or TAT-DMAE liquid into the deposition chamber. Deposition is continued until a dielectric film 508 of a desired thickness is formed. A tantalum pentaoxide ( $Ta_2O_5$ ) dielectric film having a thickness between 50-200 Å provides a suitable capacitor dielectric.

It has been found that the use of nitrous oxide ( $N_2O$ ) as the oxidizer (source of oxygen), as opposed to oxygen gas  $O_2$  improves the electrical properties of the deposited tantalum pentaoxide ( $Ta_2O_5$ ) dielectric film during deposition. The use of  $N_2O$ , as opposed to  $O_2$ , has been found to reduce the leakage current and enhance the capacitance of fabricated capacitors. The inclusion of  $N_2O$  as an oxidizer aids in the removal of carbon from the film during growth which helps to improve the quality of the film.

In an embodiment of the present invention dielectric layer 208 is a tantalum pentaoxide ( $Ta_2O_5$ ) film doped with titanium (Ti). A tantalum pentaoxide film doped with titanium can be formed by thermal chemical vapor deposition by providing a source of titanium, such as but not limited to TIPT ( $C_{12}H_{26}O_4Ti$ ), into the process chamber while forming a tantalum pentaoxide film as described above. TIPT diluted by approximately 50 % with a suitable solvent such as isopropyl alcohol (IPA) can be fed into the process chamber by direct liquid injection or through the use of a bubbler and carrier gas such as  $N_2$ . A TIPT diluted flow rate of between 5-20 mg/minute can be used to produce a tantalum pentaoxide film having a titanium doping density of between 5-20 atomic percent and a dielectric constant between 20-40. The precise Ti doping density can be controlled by varying the tantalum source

flow rate relative to the titanium source flow rate. It is to be appreciated that a tantalum pentaoxide film doped with titanium atoms exhibits a higher dielectric constant than an undoped tantalum pentaoxide film.

In another embodiment of the present invention dielectric layer 208 is a composite dielectric layer comprising a stack of different dielectric materials such as a  $Ta_2O_5/TiO_2/Ta_2O_5$  stack. A  $Ta_2O_5/TiO_2/Ta_2O_5$  composite film can be formed by first depositing a tantalum pentaoxide film as described above. After depositing a tantalum pentaoxide film having a thickness between 20-50 Å the flow of the tantalum source is stopped and replaced with a flow of a source of titanium, such as TIPT, at a diluted flow rate of between 5-20mg/min. After depositing a titanium oxide film having a thickness of between 20-50 Å, the titanium source is replaced with the tantalum source and the deposition continued to form a second tantalum pentaoxide film having a thickness of between 20-50 Å. By sandwiching a higher dielectric constant titanium oxide ( $TiO_2$ ) film between two tantalum pentaoxide ( $Ta_2O_5$ ) films, the dielectric constant of a composite stack is increased over that of a homogeneous layer of tantalum pentaoxide ( $Ta_2O_5$ ).

Next, as set forth in block 108 of flow chart 100, dielectric film 208 is annealed with remotely generated active atomic species 211 as shown in Figure 2d, to form an annealed dielectric layer 210. Dielectric film 208 can be annealed by placing substrate 200 into anneal chamber 350 coupled to remote plasma generator 301. Substrate 200 is then heated to an anneal temperature and exposed to active atomic species 211 generated by disassociating an anneal gas in applicator chamber 310. By generating the active atomic species in a chamber remote from the anneal chamber (the chamber in which the substrate is situated) a low temperature anneal can be accomplished without exposing the substrate to the harmful plasma used to form the active atomic species. With the process and apparatus of the present invention anneal temperatures of less than 400°C can be used. The use of remotely generated active atomic

species to anneal dielectric film 208 enables anneal temperatures of less than or equal to the deposition temperature of the dielectric film to be used.

In one embodiment of the present invention dielectric film 208 is a transition metal dielectric and is annealed with reactive oxygen atoms formed by remotely disassociating  $O_2$  gas. Dielectric layer 208 can be annealed in chamber 350 with a reactive oxygen atoms created by providing an anneal gas comprising two SLM of  $O_2$  and one SLM of N2 into chamber 310, and applying a power between 500 - 1500 watts to magnatron 302 to generate microwaves which causes a plasma to ignite from the anneal gas. Alternatively, reactive oxygen atoms can be formed by flowing an anneal gas comprising two SLM of  $O_2$  and three SLM of argon (Ar) into cavity 310. While reactive oxygen atoms are fed into anneal chamber 350, substrate 200 is heated to a temperature of approximately 300°C and chamber 350 maintained at an anneal pressure of approximately 2 Torr. Dielectric layer 208 can be sufficiently annealed by exposing substrate 200 to reactive oxygen atoms for between 30-120 seconds.

An inert gas, such as  $N_2$  or argon (Ar), is preferably included in the anneal gas stream in order to help prevent recombination of the active atomic species. It is to be noted that as the active atomic species (e.g. reactive oxygen atoms) travel from the applicator cavity 310 to the anneal chamber 350, they collide with one another and recombine to form  $O_2$  molecules. By including an inert gas, in the anneal gas mix, the inert gas does not disassociate and so provides atoms which the active atomic species can collide into without recombining. Additionally, in order to help prevent recombination of the active atomic species, it is advisable to keep the distance between cavity 310 and anneal chamber 350 as short as possible.

Annealing a transition-metal dielectric film 208 with reactive atoms oxygen fills oxygen vacancies (satisfies sites) in the dielectric film 208 which greatly reduces the leakage of the film. Additionally, annealing transition metal dielectric 208 helps to remove carbon (C) in the film which can contribute to leakage. Carbon can be incorporated into transition metal dielectrics

because the tantalum and titanium sources, TAT-DMAE, TAETO, and TIPT are carbon containing compounds. The reactive oxygen atoms remove carbon from the film by reacting with carbon and forming carbon dioxide (CO<sub>2</sub>) vapor which can then be exhausted out from the chamber.

Figure 4 illustrates how exposing a tantalum pentaoxide dielectric film to remotely generated reactive oxygen atoms improves the quality and electrical performance of the as deposited film. Graph 402 shows how the leakage current of a capacitor having a 100Å unannealed tantalum pentaoxide dielectric film varies for different top electrode voltages. Graph 404 shows how the leakage current of a capacitor having a  $100\text{\AA}$  tantalum pentaoxide dielectric film annealed with remotely generated reactive oxygen atoms varies for different top electrode voltages. As can be seen from graph 402, a capacitor utilizing an unannealed tantalum pentaoxide dielectric experiences high leakage current of about  $1 \times 10^{-1}$  (amps/cm<sup>2</sup>) when  $\pm 1.5$  volts is applied to the top electrode and a high leakage current of  $1x10^{-6}$  (amps/cm<sup>2</sup>) when zero volts is applied to the top electrode. In comparison, when the tantalum pentaoxide dielectric is exposed to remotely generated reactive oxygen atoms, the leakage current has a relatively low leakage current of  $1x10^{-5}$  (amps/cm<sup>2</sup>) when  $\pm 1.5$  volts is applied to the top electrode and a leakage current of less than 1x10-9 (amps/cm<sup>2</sup>) when zero volts is applied to the top electrode. As is readily apparent from Figure 4, exposing the tantalum pentaoxide dielectric film to remotely generated active oxygen atoms dramatically improves (reduces) the leakage current of the film.

In an embodiment of the present invention, as set forth in block 107 of flow chart 100 the deposition step 106 and the anneal step 108 occur simultaneously so that the dielectric film is annealed as it is deposited. A dielectric film can be deposited and annealed simultaneously using a single deposition/anneal chamber coupled to receive a remote plasma from a remote plasma generator source and coupled to receive a deposition gas mix. For example in one embodiment of the present invention a deposition gas mix

comprising a metal source such as a TAT-DMAE or TIPT, or a silicon source, such as TEOS, and a source of oxygen such as  $O_2$  or  $N_2O$  can be fed into a common anneal/deposition chamber while the substrate is heated to a desired deposition temperature and the chamber maintained at a desired deposition pressure. Simultaneously, an anneal gas, such as  $O_2$ , can be supplied into applicator cavity chamber 310 of the remote plasma generator 300 at a rate of between 0.5 - 2 SLM. Reactive oxygen atoms can then flow from chamber 310 into the anneal/deposition chamber. The reactive oxygen atoms then react with the metal or silicon provided from the deposition gas mix to form a metal-oxide or silicon-oxide compound respectively. In one embodiment of the present invention the only source of oxygen atoms into the deposition/anneal chamber is reactive oxygen atoms from applicator 310.

The next step of the present invention, as set forth in block 110 of flow chart 100 is to complete the processing of the device. For example, as shown in Figure 2e, a top capacitor electrode 212 can be formed over annealed dielectric layer 210. Any well known technology can be used to form top electrode 212 including blanket depositing a polysilicon film or metal film, such as TiN, over annealed dielectric film 210 and then using well known photolithography and etching techniques to pattern the electrode film and dielectric layer.

In another embodiment of the present invention, remotely generated active atomic species can be used to fabricate a metal oxide semiconductor (MOS) transistor. The first step, as shown in Figure 5a, which is optional, is to nitridate a monocrystalline silicon substrate 502 with remotely generated reactive nitrogen atoms 503 as describe above. Nitridating substrate 502 with remotely generated reactive nitrogen atom forms a thin silicon nitride film 501 on substrate 502 which improves the interface between the silicon substrate 502 and the subsequently deposited gate dielectric layer. Next, as shown in Figure 5b a gate dielectric layer 504 is formed over nitridated substrate 502. Gate dielectric layer 504 can be a thermally grown silicon dioxide film, a CVD deposited silicon dioxide film, or a transition metal film such as tantalum

pentaoxide or titanium oxide or combinations thereof. Gate dielectric 504 will typically have a thickness between 20 to 100Å. Next, as shown in Figure 5c, the dielectric film 504 is annealed with remotely generated active atomic species 505, such as reactive oxygen atoms, to form an annealed dielectric film 506 as described above. Annealing of the gate dielectric film fills vacancies in the lattice and generally improves the quality of the film. The annealing step can occur as a separate step after the deposition of the gate dielectric or can occur simultaneous with the deposition of the gate dielectric. After forming annealed gate dielectric 506, a gate electrode material, such as polysilicon or a metal or a combination thereof, can be blanket deposited over annealed gate dielectric 506 and then patterned into a gate electrode 508, as shown in Figure 5d, with well known photolithography and etching techniques. A pair of source/drain regions 510 can then be formed on opposite sides of the gate electrode 508 with well known ion implantation or solid source diffusion techniques, in order to complete fabrication of the MOS device.

A novel method and apparatus for forming and/or annealing a dielectric film with a remotely generated active atomic species has been described. Utilizing a, remotely generated active atomic species to anneal and/or deposit a film enables a high quality, high dielectric constant film to be formed at low temperatures. Although the present invention has been described with respect to specific equipment, and with respect to a specific processes it is to be appreciated that the described details are to be taken as illustrative rather than limiting, wherein the scope of the present invention is to be measured by the appended claims which follow.

Thus, a method and apparatus for annealing a dielectric film at low temperatures has been described.

#### **IN THE CLAIMS**

#### We claim:

1. A method of annealing a dielectric layer, said method comprising the steps of:

forming a dielectric layer on a substrate;

generating an active atomic species in a first chamber; and

exposing said dielectric layer to said active atomic species wherein said

substrate is located in a second chamber separate from said first chamber while

exposing said dielectric layer to said active atomic species.

- 2. The method of claim 1 wherein said active atomic species comprises reactive oxygen atoms.

- 3. The method of claim 1 wherein said active atomic species comprises reactive nitrogen atoms.

- 4. The method of claim 1 wherein said dielectric layer comprises a metal-oxide.

- 5. The method of claim 1 wherein said dielectric layer comprises a transition metal dielectric.

- 6. The method of claim 5 wherein said dielectric layer comprises tantalum pentaoxide ( $Ta_2O_5$ ).

7. The method of claim 1 wherein said dielectric layer is exposed to said active atomic species while being heated to a temperature of less than 400°C.

- 8. A method of forming a dielectric layer comprising:

generating an active atomic species in a first chamber; and

depositing a dielectric layer onto a substrate by chemical vapor

deposition in a second chamber and while depositing said dielectric layer,

providing said active atomic species into said second chamber.

- 9. The method of claim 8 wherein said active atomic species comprises oxygen radicals.

- 10. The method of claim 8 wherein said dielectric layer a metal oxide dielectric.

- 11. The method of claim 8 wherein said dielectric layer comprises a transition metal dielectric.

- 12. The method of claim 11 wherein said dielectric layer comprises tantalum pentaoxide ( $Ta_2O_5$ ).

- 13. The method of claim 8 wherein said dielectric layer comprises a silicon-oxide.

- 14. A method of annealing a deposited oxide, said method comprising the steps of:

locating a substrate in a first chamber, said substrate having a deposited oxide formed thereon;

generating reactive oxygen atoms in a second chamber; and

transporting said reactive oxygen atoms from said second chamber into said first chamber and exposing said deposited oxide to said reactive oxygen atoms.

- 15. The method of claim 14 wherein said deposited oxide is exposed to said reactive oxygen atoms while heating said substrate to at a temperature of less than 400°C.

- 16. The method of claim 14 wherein said second chamber is a microwave applicator cavity of a remote plasma generator.

- 17. The method of claim 14 wherein said reactive oxygen atoms are formed by generating a plasma from O<sub>2</sub> molecules.

- 18. The method of claim 14 wherein said reactive oxygen atoms are formed by generating a plasma from N2O molecules.

- 19. The method of claim 14 wherein said reactive oxygen atoms are formed by generating a plasma from O<sub>2</sub> molecules utilizing microwaves.

- 20. The method of claim 14 wherein said deposited oxide is a silicon-oxide.

- 21. The method of claim 14 wherein said deposited oxide is a metal-oxide.

- 22. The method of claim 21 wherein said deposited metal oxide is a transition metal oxide.

23. The method of claim 22 wherein said transition metal-oxide is tantalum pentaoxide ( $Ta_2O_5$ ).

24. A method of forming a capacitor, said method comprising the steps of:

forming a bottom electrode;

depositing a transition metal dielectric on said bottom electrode in a deposition chamber;

generating reactive oxygen atoms by forming a plasma from an oxygen containing gas in a microwave applicator cavity in a remote plasma generation chamber;

annealing said transition metal dielectric by exposing said transition metal dielectric to said reactive oxygen atoms, wherein said annealing step occurs in a chamber separate from said microwave applicator cavity; and

forming a top electrode on said reactive oxygen atom exposed transition metal dielectric.

- 25. The method of claim 24 wherein said transition metal dielectric is tantalum pentaoxide ( $Ta_2O_5$ ) deposited by chemical vapor deposition utilizing a source gas comprising TAETO.

- 26. The method of claim 24 wherein said transition metal dielectric is tantalum pentaoxide ( $Ta_2O_5$ ) formed by chemical vapor deposition utilizing a source gas comprising TAT-DMAE.

- 27. The method of claim 25 wherein said tantalum pentaoxide dielectric layer is formed utilizing a source gas comprising O<sub>2</sub>.

- 28. The method of claim 24 wherein said transition metal dielectric layer is deposited at a temperature between 300-500°C.

29. The method of claim 24 wherein said transition metal dielectric is formed with a source gas comprising  $N_2O$ .

- 30. The method of claim 24 wherein said transition metal dielectric is annealed in the deposition chamber.

- 31. The method of claim 24 wherein said transition metal dielectric film is annealed at a temperature less than 400°C.

- 32. The method of claim 24 wherein said transition metal dielectric is annealed in a chamber different than the deposition chamber in which said transition metal dielectric was deposited.

- 33. A method of forming a dielectric film, said method comprising the steps of:

placing a substrate in the deposition chamber;

heating said substrate to a deposition temperature;

providing a metal source into said chamber;

thermally decomposing said metal source to provide metal atoms;

generating reactive oxygen atoms in a second chamber;

providing said reactive oxygen atoms into said deposition chamber; and

forming a dielectric film on said substrate by combining said metal

atoms with said reactive oxygen atoms.

34. The method of claim 33 wherein no other source of oxygen is provided into said deposition chamber other then said reactive oxygen atoms during said formation of said dielectric film.

35. The method of claim 33 wherein said reactive oxygen atoms are formed from a plasma formed by applying microwaves to oxygen gas  $(O_2)$ .

- 36. The method of claim 33 wherein said reactive oxygen atoms are formed from a plasma created by applying microwaves to N<sub>2</sub>O molecules.

- 37. A method of passivating a silicon nitride film, said method comprising the steps of:

locating a substrate in a first chamber, said substrate having a silicon nitride layer formed thereon;

generating reactive nitrogen atoms in a second chamber; and transporting said reactive nitrogen atoms from said second chamber into said first chamber and exposing said silicon nitride film to said reactive oxygen atoms.

- 38. The method of claim 37 wherein said reactive nitrogen atoms are formed from an anneal gas comprising  $N_2$ .

- 39. The method of claim38 wherein said reactive nitrogen atoms are formed from an anneal gas comprising  $N_2$  and  $H_2$ .

- 40. A method of forming a silicon nitride film on a substrate, said method comprising the step of:

locating a substrate in a first chamber, said substrate having a silicon surface;

generating active nitrogen atoms in a second chamber; and transporting said reactive nitrogen atoms from said second chamber into said first chamber and reacting said silicon surface with said reactive nitrogen atoms to form a silicon nitride film on said substrate.

41. The method of claim 40 wherein said reactive nitrogen atoms are formed from an annealed gas comprising  $N_2$ .

- 42. The method of claim 40 wherein said reactive nitrogen atoms are formed from an annealed gas comprising ammonia (NH<sub>3</sub>).

- 43. A method of forming a tantalum pentaoxide dielectric film, said method comprising the steps of:

placing a substrate into a deposition chamber;

providing a metal organic tantalum containing precursor into said chamber;

providing nitrous oxide (N2O) into said chamber;

thermally decomposing said metal organic tantalum containing precursor in said chamber to provide tantalum atoms; and

reacting said tantalum atoms with said nitrous oxide ( $N_2O$ ) to form a tantalum pentaoxide ( $Ta_2O_5$ ) dielectric film on said substrate.

- 44. The method of claim 43 further comprising the step of heating said substrate to a temperature between 300-500°C while providing said metal organic tantalum precursor and said nitrous oxide (N<sub>2</sub>O) into said chamber.

- 45. The method of claim 43 wherein said metal organic tantalum containing precursor is selected from the group consisting of TAT-DMAE and TAETO.

FIG. 1

FIG. 2a

FIG. 2b

FIG. 2c

FIG. 2d

FIG. 2e

FIG. 3a

FIG. 3b

**FIG. 4**

# FIG. 5a

FIG. 5b

FIG. 5c

FIG. 5d

Inter: Tal Application No PCT/US 99/13300

CLASSIFICATION OF SUBJECT MATTER C23C16/40 H01L21/3105 C23C16/56 According to International Patent Classification (IPC) or to both national classification and IPC **B. FIELDS SEARCHED** Minimum documentation searched (classification system followed by classification symbols) IPC 6 C23C Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched Electronic data base consulted during the international search (name of data base and, where practical, search terms used) C. DOCUMENTS CONSIDERED TO BE RELEVANT Citation of document, with indication, where appropriate, of the relevant passages Relevant to claim No. Category <sup>a</sup> χ US 5 376 628 A (SEKIGUCHI ATSUSHI ET AL) 1,2,4,5, 27 December 1994 (1994-12-27) 7-11,14, 15,17, 18,21,22 column 8, line 23 - line 68 3,6,12, Υ 13,16, 19,20,23 column 10, line 64 -column 11, line 5 column 12, line 19 - line 59 US 5 290 609 A (KAWAMURA KOHEI ET AL) 24,25, Y 27-31, 1 March 1994 (1994-03-01) 33 - 35column 6, line 18 - line 36 32-36 Α Further documents are listed in the continuation of box C. Patent family members are listed in annex. χ Special categories of cited documents: "T" later document published after the international filing date or priority date and not in conflict with the application but "A" document defining the general state of the art which is not considered to be of particular relevance cited to understand the principle or theory underlying the invention "E" earlier document but published on or after the international "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to filing date "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another involve an inventive step when the document is taken alone "Y" document of particular relevance; the claimed invention citation or other special reason (as specified) cannot be considered to involve an inventive step when the document is combined with one or more other such docu-"O" document referring to an oral disclosure, use, exhibition or ments, such combination being obvious to a person skilled other means "P" document published prior to the international filing date but later than the priority date claimed "&" document member of the same patent family Date of mailing of the international search report Date of the actual completion of the international search 08/11/1999 1 November 1999 Name and mailing address of the ISA Authorized officer European Patent Office, P.B. 5818 Patentlaan 2 NL – 2280 HV Rijswijk Tel. (+31–70) 340–2040, Tx. 31 651 epo ni, Ekhult, H Fax: (+31-70) 340-3016

1

Inter mal Application No PCT/US 99/13300

|            | ation) DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                          |                                                |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| Category ° | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                  | Relevant to claim No.                          |

| X          | PATENT ABSTRACTS OF JAPAN vol. 015, no. 490 (E-1144), 11 December 1991 (1991-12-11) & JP 03 212938 A (SEIKO EPSON CORP), 18 September 1991 (1991-09-18)                                                                                                                             | 40-42                                          |

| Α          | abstract<br>                                                                                                                                                                                                                                                                        | 37–40                                          |

| X          | YASUDA T ET AL: "LOW-TEMPERATURE PREPARATION OF SIO2/SI(100) INTERFACES USING A TWO -STEP REMOTE PLASMA-ASSISTED OXIDATION-DEPOSITION PROCESS" APPLIED PHYSICS LETTERS, vol. 60, no. 4, 27 January 1992 (1992-01-27), pages 434-436, XP000305288 ISSN: 0003-6951 the whole document | 8,14                                           |

| X          | PATENT ABSTRACTS OF JAPAN vol. 017, no. 225 (C-1055), 10 May 1993 (1993-05-10) -& JP 04 362017 A (NIPPON MINING CO LTD), 15 December 1992 (1992-12-15)                                                                                                                              | 43-45                                          |

| Υ          | abstract                                                                                                                                                                                                                                                                            | 25,28,<br>29,33-35                             |

| Α          | & DATABASE WPI Section Ch, Week 9304 Derwent Publications Ltd., London, GB; Class E35, AN 1993-033213 "HIGHLY ORIENTED TANTALUM OXIDE MEMBRANE" & JP 04 362017 A (NIPPON MINING), 15 December 1992 (1992-12-15) abstract                                                            | 36                                             |

| Υ          | ALERS G B ET AL: "NITROGEN PLASMA ANNEALING FOR LOW TEMPERATURE TA205 FILMS" APPLIED PHYSICS LETTERS, vol. 72, no. 11, 16 March 1998 (1998-03-16), pages 1308-1310, XP000742858 ISSN: 0003-6951 page 1309, left-hand column, line 1-12                                              | 3,6,12,<br>16,19,<br>23-25,<br>27,28,<br>30,31 |

| Y          | PATENT ABSTRACTS OF JAPAN vol. 016, no. 318 (E-1232), 13 July 1992 (1992-07-13) & JP 04 092423 A (HITACHI LTD; OTHERS: 01), 25 March 1992 (1992-03-25) abstract                                                                                                                     | 13,20                                          |

|            | -/                                                                                                                                                                                                                                                                                  |                                                |

1

Inter. Inal Application No PCT/US 99/13300

| Category ° | ation) DOCUMENTS CONSIDERED TO BE RELEVANT  Citation of document, with indication,where appropriate, of the relevant passages                                                                                                                                     | Relevant to claim No. |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Category   | Citation of document, with indication, where appropriate, or the relevant passages                                                                                                                                                                                | Maisvant to Claim No. |

| A          | WO 95 26355 A (LEEDHAM TIMOTHY JOHN ;DRAKE SIMON ROBERT (GB)) 5 October 1995 (1995-10-05) page 27, line 20 -page 28, line 32                                                                                                                                      | 26,45                 |

| A          | DATABASE WPI Section Ch, Week 9646 Derwent Publications Ltd., London, GB; Class L04, AN 1996-462756 XP002120114 BAEK ET AL: "MFG. INSULATION LAYER OF CAPACITOR HAVING HIGH DIELECTRIC CONSTANT" & KR 9 500 861 A (HUNDAI), 2 February 1995 (1995-02-02) abstract | 32                    |

| Т          | US 5 907 780 A (GILMER MARK C ET AL) 25 May 1999 (1999-05-25) column 7, line 23 - line 26                                                                                                                                                                         | 26,45                 |

|            |                                                                                                                                                                                                                                                                   |                       |

|            |                                                                                                                                                                                                                                                                   |                       |

|            |                                                                                                                                                                                                                                                                   |                       |

|            |                                                                                                                                                                                                                                                                   |                       |

|            |                                                                                                                                                                                                                                                                   |                       |

|            |                                                                                                                                                                                                                                                                   |                       |

|            |                                                                                                                                                                                                                                                                   |                       |

|            |                                                                                                                                                                                                                                                                   |                       |

1

Information on patent family members

Inter anal Application No PCT/US 99/13300

| Patent document cited in search report | Publication<br>date | Patent family<br>member(s)                   | Publication date                       |

|----------------------------------------|---------------------|----------------------------------------------|----------------------------------------|

| US 5376628 A                           | 27-12-1994          | JP 1755662 C<br>JP 2014801 A<br>JP 4046882 B | 23-04-1993<br>18-01-1990<br>31-07-1992 |

| US 5290609 A                           | 01-03-1994          | JP 2764472 B<br>JP 5267567 A                 | 11-06-1998<br>15-10-1993               |

| JP 03212938 A                          | 18-09-1991          | NONE                                         |                                        |

| JP 04362017 A                          | 15-12-1992          | NONE                                         |                                        |

| JP 04092423 A                          | 25-03-1992          | NONE                                         |                                        |

| WO 9526355 A                           | 05-10-1995          | AU 1955395 A                                 | 17-10-1995                             |

| KR 9500861 A                           | 02-02-1995          | NONE                                         |                                        |

| US 5907780 A                           | 25-05-1999          | NONE                                         |                                        |