(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2012년03월15일

(11) 등록번호 10-1122618

(24) 등록일자 2012년02월24일

- (51) 국제특허분류(Int. Cl.)

*G02F 1/136* (2006.01)

- (21) 출원번호 10-2005-0013957

(22) 출원일자 2005년02월21일

심사청구일자 2010년02월22일

(65) 공개번호 10-2006-0042137

(43) 공개일자 2006년05월12일

(30) 우선권주장

093104658 2004년02월24일 대만(TW)

(56) 선행기술조사문현

US06671020 B2\*

JP2001264773 A\*

- \*는 심사관에 의하여 인용된 문현

- (73) 특허권자

치 메이 옵토일렉트로닉스 코포레이션

대만, 타이난 카운티, 타이난 싸이언스-베이스드

인더스트리얼 파크, 치 예 로드, 넘버1

(72) 발명자

왕 청이

대만 744 타이난 싸이언스 베이스드 인더스트리얼

파크 타이난 카운티 치-예 로드 넘버 1

(74) 대리인

리엔목특허법인

전체 청구항 수 : 총 36 항

심사관 : 임동재

(54) 발명의 명칭 액정 표시 장치 및 이를 위한 스토리지 커패시터

**(57) 요약**

특유하게 제작된 스토리지 커패시터를 가지는 액정 표시 장치를 개시한다. 이 액정 표시 장치는 두 기판 사이에

개재된 액정층과 액정층의 배향을 조절하기 위해 두 기판 중 어느 하나 상에 구비된 조절 구조에 의해 복수개의

면적으로 각각 분할된 복수개의 픽셀 영역을 포함한다. 스토리지 커패시터는 각 픽셀 영역 안에 제1 커패시터 전

극을 가진다. 제1 커패시터 전극은 몸체와 몸체의 한 측면으로부터 신장하는 적어도 하나의 신장부를 가지며, 신

장부는 광 투과 상태에서 픽셀 영역의 어두운 면적 안에 위치한다.

**대표도 - 도1**

## 특허청구의 범위

### 청구항 1

매트릭스로 배열된 복수개의 픽셀 영역을 가지는 액정 표시 장치로서,

수직 정렬을 위해 가공된 제1 및 제2 기판;

상기 제1 및 제2 기판 사이에 개재되는 액정층으로서, 상기 액정층에 실질적인 전계가 인가되지 않으면 상기 제1 기판의 주표면에 대체로 수직인 방향으로 정렬되는 액정 분자를 포함하는 액정층;

전압이 인가되면 상기 액정 분자가 비스듬하게 정렬되어 배향이 복수개의 방향을 포함하도록 상기 액정층의 배향을 조절하기 위해 상기 제1 및 제2 기판 중 적어도 어느 하나 상에 구비되는 꺾인 부분을 포함하는 조절 구조;

상기 각 픽셀 영역 안의 픽셀 전극;

상기 각 픽셀 영역 안의 제1 커패시터 전극으로서, 몸체와 상기 몸체의 한 측면으로부터 바깥쪽으로 신장하는 신장부를 가지는 제1 커패시터 전극;

상기 각 픽셀 영역 안의 제2 커패시터 전극으로서, 몸체와 상기 몸체의 한 측면으로부터 바깥쪽으로 신장하는 신장부를 가지며, 상기 제2 커패시터 전극의 신장부는 상기 조절 구조의 꺾인 부분과 상기 조절 구조의 꺾인 부분에 인접한 상기 픽셀 전극의 가장자리에 의하여 정의되는 상기 픽셀 영역의 삼각형 면적에 대응하는 위치에 형성되며, 상기 조절 구조와 상기 픽셀 전극의 가장자리 사이의 각도는 90도 미만이고, 상기 몸체는 상기 삼각형 면적으로부터 바깥쪽으로 제1 방향으로 신장하고 상기 신장부는 상기 제1 방향에 평행하지 않은 제2 방향으로 신장하는 제2 커패시터 전극;

상기 제2 커패시터 전극과 픽셀 전극이 함께 상기 제1 커패시터 전극에 대한 대향 전극으로 작용하도록, 상기 제2 커패시터 전극과 픽셀 전극을 전기적으로 커플링하고, 상기 각 픽셀 영역들 내에 연결부 면적을 정의하는 연결부; 및

상기 제1 및 제2 기판의 사이에 셀 간격을 유지하기 위한 복수의 스페이서들로서, 상기 픽셀 영역의 삼각형 면적에 대응하여 상기 삼각형 면적 내의 스페이서 배치 영역 내에 배치되고, 암-상태 광 누설을 완화시키는 복수의 스페이서들;

을 포함하고, 상기 스페이서 배치 영역은 상기 연결부 면적과 상이하고,

상기 조절 구조는 상기 제1 기판 상에 제공된 돌출부의 어레이와 상기 픽셀 전극 상에 제공된 슬릿의 어레이를 포함하며 상기 돌출부는 서로에 대해 평행하게 실질적으로 지그재그 패턴으로 배열되어 있고 상기 슬릿과 돌출부는 교대로 배열되어 있고, 상기 슬릿은 복수개의 텁니 모양(indentation)을 가지는 것을 특징으로 하는 액정 표시 장치.

### 청구항 2

제1항에 있어서, 상기 제1 기판은 공통 전극을 더 포함하는 것을 특징으로 하는 액정 표시 장치.

### 청구항 3

제1항에 있어서, 상기 면적은 광 투과 상태에서 상기 픽셀 영역의 더 어두운 영역이 상기 스페이서 배치 영역을 포함하는 것을 특징으로 하는 액정 표시 장치.

### 청구항 4

제1항에 있어서, 상기 스페이서 배치 영역은 상기 조절 구조와 상기 픽셀 전극의 가장자리로 둘러싸인 예각 삼각형 면적인 것을 특징으로 하는 액정 표시 장치.

### 청구항 5

제1항에 있어서, 상기 연결부는 상기 제2 커패시터 전극의 신장부와 상기 신장부에 인접한 상기 제2 커패시터 전극의 몸체에 의해 정의된 영역 안에 위치하는 것을 특징으로 하는 액정 표시 장치.

**청구항 6**

제1항에 있어서, 상기 제2 기판 상에 형성된 복수개의 평행한 게이트 라인과, 상기 게이트 라인에 수직이며 서로 평행한 복수개의 데이터 라인을 더 포함하여, 상기 각 픽셀 영역이 두 개의 인접한 게이트 라인과 두 개의 인접한 데이터 라인에 의해 정의되는 것을 특징으로 하는 액정 표시 장치.

**청구항 7**

제6항에 있어서, 상기 제1 커패시터 전극과 게이트 라인은 제1 금속층으로 형성되고, 상기 제2 커패시터 전극과 데이터 라인은 제2 금속층으로 형성된 것을 특징으로 하는 액정 표시 장치.

**청구항 8**

제1항에 있어서, 상기 제2 커패시터 전극의 신장부는 실질적으로 삼각형 윤곽(contour)을 가진 것을 특징으로 하는 액정 표시 장치.

**청구항 9**

제1항에 있어서, 상기 제2 커패시터 전극의 신장부는 실질적으로 사다리꼴 윤곽을 가진 것을 특징으로 하는 액정 표시 장치.

**청구항 10**

제1항에 있어서, 상기 제2 커패시터 전극의 신장부는 상기 제2 커패시터 전극의 몸체와 135도로 놓인 적어도 하나의 가장자리를 가진 것을 특징으로 하는 액정 표시 장치.

**청구항 11**

제1항에 있어서, 상기 제2 커패시터 전극의 신장부는 적어도 하나의 가지(branch)를 가진 것을 특징으로 하는 액정 표시 장치.

**청구항 12**

제1항에 있어서, 상기 제2 커패시터 전극의 신장부는 상기 제2 커패시터 전극의 몸체와 135도로 각각 놓인 두 개의 가지를 포함하는 것을 특징으로 하는 액정 표시 장치.

**청구항 13**

삭제

**청구항 14**

제1항에 있어서, 상기 돌출부는 복수개의 가지를 가지는 것을 특징으로 하는 액정 표시 장치.

**청구항 15**

삭제

**청구항 16**

제1항에 있어서, 상기 각 픽셀 영역 안에서, 상기 돌출부 중 하나는 꺾인 부분을 가지고 상기 제2 커패시터 전극의 신장부는 실질적으로 상기 꺾인 부분과 상기 꺾인 부분에 인접한 데이터 라인 사이에 형성되어 있는 것을 특징으로 하는 액정 표시 장치.

**청구항 17**

제1항에 있어서, 상기 조절 구조는 상기 제1 기판 상에 제공된 제1 슬릿의 어레이와 상기 픽셀 전극 상에 제공된 제2 슬릿의 어레이를 포함하며 상기 제1 슬릿은 서로에 대해 평행하게 실질적으로 지그재그 패턴으로 배열되어 있고 상기 제1 슬릿과 제2 슬릿은 교대로 배열되어 있는 것을 특징으로 하는 액정 표시 장치.

**청구항 18**

제1항에 있어서, 상기 스페이서들과 상기 연결부는 상기 제2 커페시터 전극의 몸체를 따라 일렬로 배열된 것을 특징으로 하는 액정 표시 장치.

### 청구항 19

제1항에 있어서, 상기 연결부보다 상기 스페이서 배치 영역이 상기 신장부의 최대 신장된 부분에 더 가까운 것을 특징으로 하는 액정 표시 장치.

### 청구항 20

매트릭스로 배열된 복수개의 픽셀 영역을 가지는 액정 표시 장치로서,

제1 및 제2 기판;

상기 제1 및 제2 기판 사이에 개재되는 액정층;

상기 각 픽셀 영역이 두 개의 인접한 게이트 라인과 두 개의 인접한 데이터 라인에 의해 정의되는, 상기 제2 기판 상에 형성된 복수개의 게이트 라인과 데이터 라인;

상기 제1 기판 상에 구비되는 제1 조절 구조의 어레이;

상기 제2 기판 상의 픽셀 전극으로서, 상기 픽셀 전극은 제2 조절 구조의 어레이를 포함하고, 상기 제1 조절 구조와 상기 제2 조절 구조는 교대로 배열되며 상기 각 픽셀 영역은 상기 제1 조절 구조와 상기 제2 조절 구조에 의해 복수개의 영역으로 분할되는 픽셀 전극; 및

상기 픽셀 전극과 함께 스토리지 커페시터 유닛을 형성하기 위한 상기 각 픽셀 영역 안의 제1 커페시터 전극으로서, 상기 각 픽셀 영역들 내에서 상기 제1 조절 구조들 중 하나가 꺾인 부분을 포함하는 제1 커페시터 전극; 및

상기 제1 및 제2 기판의 사이에 셀 간격을 유지하기 위한 복수의 스페이서들로서, 상기 스페이서들은 스페이서 배치 영역에 배치되고, 상기 스페이서 배치 영역은 암-상태 광 누설을 완화시키기 위하여 상기 제1 조절 구조의 꺾인 부분과 상기 제1 조절 구조의 상기 꺾인 부분에 이웃하는 데이터 라인에 의하여 정의되는 삼각형 면적 내에 위치하는 복수의 스페이서들;

을 포함하고,

상기 제2 조절 구조는 복수개의 톱니 모양을 갖는 슬릿들의 어레이인 것을 특징으로 하는 액정 표시 장치.

### 청구항 21

제20항에 있어서, 상기 제1 기판은 공통 전극을 더 포함하는 것을 특징으로 하는 액정 표시 장치.

### 청구항 22

제21항에 있어서, 상기 제1 조절 구조는 상기 공통 전극 상에 제공된 돌출 구조들의 어레이이고 상기 제2 조절 구조는 실질적으로 지그재그 패턴으로 배열되어 있는 슬릿들의 어레이인 것을 특징으로 하는 액정 표시 장치.

### 청구항 23

제20항에 있어서, 상기 액정층은 복수개의 액정 분자를 포함하고, 상기 제1 및 제2 기판은 상기 액정 분자의 방향이 상기 제1 기판 및 제2 기판의 표면에 대체로 수직이 되도록 수직 정렬하기 위해 가공된 것을 특징으로 하는 액정 표시 장치.

### 청구항 24

제20항에 있어서, 상기 액정층은 음의 유전상수 이방성을 가지는 액정 물질로 형성되는 것을 특징으로 하는 액정 표시 장치.

### 청구항 25

제20항에 있어서, 상기 데이터 라인은 서로 평행하고 상기 픽셀 영역 안에 상기 픽셀 전극이 배치되어 있는 것을 특징으로 하는 액정 표시 장치.

### 청구항 26

제25항에 있어서, 상기 게이트 라인은 상기 데이터 라인에 수직인 것을 특징으로 하는 액정 표시 장치.

### 청구항 27

제25항에 있어서,

상기 각 픽셀 영역 안의 제2 커패시터 전극; 및

상기 제2 커패시터 전극과 픽셀 전극이 함께 상기 제1 커패시터 전극에 대한 대향 전극으로 작용하도록, 상기 제2 커패시터 전극과 픽셀 전극을 전기적으로 커플링하고, 상기 각 픽셀 영역 안에 연결부 면적을 정의하는 연결부;

를 더 포함하고, 상기 스페이서 배치 영역은 상기 연결부 면적과 상이한 것을 특징으로 하는 액정 표시 장치.

### 청구항 28

제27항에 있어서, 상기 연결부 면적은 상기 제2 커패시터 전극의 신장부와 상기 신장부에 인접한 상기 제2 커패시터 전극의 몸체에 의해 정의된 영역 안에 위치하는 것을 특징으로 하는 액정 표시 장치.

### 청구항 29

제27항에 있어서, 상기 제1 커패시터 전극과 게이트 라인은 제1 금속층으로 형성되고, 상기 제2 커패시터 전극과 데이터 라인은 제2 금속층으로 형성된 것을 특징으로 하는 액정 표시 장치.

### 청구항 30

제20항에 있어서, 상기 제1 조절 구조는 실질적으로 지그재그 패턴으로 배열된 돌출부의 어레이인 것을 특징으로 하는 액정 표시 장치.

### 청구항 31

제30항에 있어서, 상기 돌출부는 복수개의 가지를 가지는 것을 특징으로 하는 액정 표시 장치.

### 청구항 32

삭제

### 청구항 33

제20항에 있어서,

상기 제1 커패시터 전극이 제1 방향으로 신장되는 몸체와 상기 제1 방향과 상이한 제2 방향으로 신장되는 신장부를 갖고, 상기 제1 커패시터 전극의 신장부는 실질적으로 삼각형 윤곽을 가지며, 상기 제1 커패시터 전극의 상기 신장부는 실질적으로 상기 삼각형 면적 내에 형성된 것을 특징으로 하는 액정 표시 장치.

### 청구항 34

제33항에 있어서, 상기 제1 커패시터 전극의 신장부는 실질적으로 사다리꼴 윤곽을 가진 것을 특징으로 하는 액정 표시 장치.

### 청구항 35

제33항에 있어서, 상기 제1 커패시터 전극의 신장부는 상기 제1 커패시터 전극의 몸체와 135도로 놓인 적어도 하나의 가장자리를 가진 것을 특징으로 하는 액정 표시 장치.

### 청구항 36

제33항에 있어서, 상기 제1 커패시터 전극의 신장부는 적어도 하나의 가지를 가진 것을 특징으로 하는 액정 표시 장치.

청구항 37

제33항에 있어서, 상기 제1 커패시터 전극의 신장부는 상기 제2 커패시터 전극의 몸체와 135도로 각각 놓인 두 개의 가지를 포함하는 것을 특징으로 하는 액정 표시 장치.

청구항 38

제33항에 있어서, 상기 제1 방향과 제2 방향 사이의 각도는 135도인 것을 특징으로 하는 액정 표시 장치.

청구항 39

제33항에 있어서, 상기 제2 방향은 상기 제1 커패시터 전극의 신장부에 인접한 상기 제1 조절 구조에 평행한 것을 특징으로 하는 액정 표시 장치.

청구항 40

삭제

청구항 41

삭제

청구항 42

삭제

청구항 43

삭제

청구항 44

삭제

청구항 45

삭제

청구항 46

삭제

청구항 47

삭제

청구항 48

삭제

청구항 49

삭제

청구항 50

삭제

청구항 51

삭제

청구항 52

작제

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

##### 발명이 속하는 기술 및 그 분야의 종래기술

- [0008] 본 발명은 액정 표시 장치를 위한 커페시터에 관한 것으로, 더욱 상세하게는 멀티-도메인(multi-domain) 수직 정렬 액정 표시 장치를 위한 스토리지 커페시터에 관한 것이다.

- [0009] 액정 표시 장치(liquid crystal display : LCD)는 마주보는 두 장의 유리 기판과 그 사이에 개재된 액정층을 갖는 액정 표시 셀을 주로 포함한다. 수직 정렬(vertically aligned : VA) LCD는 음의 유전상수 이방성을 가지는 액정 물질과 수직 정렬 박막을 사용하는 모드이다. 전압이 인가되지 않으면, 액정 문자는 수직 방향으로 정렬되어 흑색 표시(black display)가 된다. 소정의 전압이 인가되면, 액정 문자가 수평 방향으로 정렬되어 백색 표시(white display)가 된다. 트위스티드 네마티드(twisted nematic : TN) LCD와 비교해서, 수직 정렬(VA) LCD는 높은 콘트라스트, 높은 응답 속도, 및 우수한 시야각을 제공한다.

- [0010] 그러나, VA LCD는 표시 면적에 수직이 아닌 방향에서 보여졌을 때 감소된 콘트라스트 레이션(ratio)와 콘트라스트 리버설(reversal)로 인한 문제를 여전히 가지고 있다. 빛과 액정 문자의 상호 작용의 결과, 수직 입사각으로 셀을 통과하는 빛은 수직이 아닌 입사각으로 셀을 통과하는 빛과는 다른 양상으로 액정 문자와 상호작용한다. 광 투과 상태(백색)와 비투과 상태(흑색) 사이의 콘트라스트 레이션은 표시 장치에 수직이 아닌 각도에서 급격하게 감소하여, 평면 텔레비전 스크린 및 대화면 컴퓨터 스크린과 같은 많은 응용 분야에 표시 장치를 덜 바람직하게 만든다.

- [0011] VA LCD의 시야각 성능은 픽셀 안의 액정 문자의 배향(orientation)을 복수개의 상호 다른 방향으로 맞추는 것에 의해 개선될 수 있다는 것이 알려져 있다. 유럽특허 제0884626-A2는 액정의 배향을 조절하는 도메인 조절 수단(regulating means)을 가지는 멀티-도메인 VA LCD를 개시하는데, 여기서는 전압이 인가되면 액정 문자가 비스듬하게 정렬되어, 배향이 각 픽셀 영역 안에 복수개의 방향을 포함하게 된다.

- [0012] 일반적으로, 위에 기술된 VA LCD는 칼라 필터(color filter : CF) 기판과 박막 트랜지스터(thin film transistor : TFT) 기판을 주로 포함하는 TFT LCD이다. CF 기판에는 일반적으로 복수개의 칼라 필터와 공통 전극이 구비되어 있다. TFT 기판에는 일반적으로 서로 평행하게 형성된 복수개의 게이트 라인, 게이트 라인에는 수직이고 서로에 대해서는 평행하게 형성된 복수개의 데이터 라인, TFT와 픽셀 전극이 구비되어 있다. 통상적으로, 기판 사이의 간격을 정의하기 위해, 기판 사이에 스페이서(미도시)가 형성된다.

- [0013] 위에 기술한 LCD에는 일반적으로 TFT가 꺼진 후에도 소정 시간 동안의 정해진 한계 안에서 픽셀 전극에서의 전압이 유지되도록 스토리지 커페시터(Cs)가 구비된다. 스토리지 커페시터는 불투명한 금속으로 형성되어 스토리지 커페시터가 차지하는 면적은 표시 면적으로 사용될 수 없기 때문에 표시 휴도를 감소시킨다. 그러나, 화질을 향상시키기 위해서는 큰 Cs를 갖게 하는 것이 바람직하다. 따라서, 표시 휴도와 Cs 크기 사이의 균형이 탈성되어야만 한다.

##### 발명이 이루고자 하는 기술적 과제

- [0014] 본 발명의 목적은 LCD의 총 휴도를 크게 증가시키고 소정의 커페시턴스를 제공하기 위해 특유하게 디자인된 스토리지 커페시터를 구비하는 멀티-도메인 수직 정렬(MVA) LCD를 제공하는 것이다.

#### 발명의 구성 및 작용

- [0015] 상기 열거한 목적 및 다른 목적을 달성하기 위하여, 본 발명에 따른 MVA LCD는 주로 두 기판 사이에 개재된 액정층 및 전압이 인가되면 액정 문자가 비스듬하게 정렬되어 배향이 복수개의 방향을 포함하도록 상기 액정층의 배향을 조절하기 위해 상기 두 기판 중 적어도 어느 하나 상에 구비되는 조절 구조를 포함한다. 본 발명에 따른 스토리지 커페시터는 주로 제1 커페시터 전극, 제2 커페시터 전극 및 픽셀 전극과 함께 스토리지 커페시터를 형성하기 위한 각 픽셀 영역 안의 연결부를 포함한다. 상기 제1 커페시터 전극과 제2 커페시터 전극은 각각 몸체

와 상기 몸체의 한 측면으로부터 신장하는 적어도 하나의 신장부(다른 말로, 날개부)를 가진다.

[0016] 상기 열거한 목적 및 다른 목적을 달성하기 위하여, 상기 제2 커패시터 전극의 신장부는 상기 조절 구조와 상기 조절 구조에 인접한 상기 픽셀 전극의 가장자리에 의해 정의된 상기 픽셀 영역의 면적 중 하나에 면하는 위치에 형성되고, 상기 조절 구조와 상기 픽셀 전극의 가장자리 사이의 각도는 90도 미만이다. 상기 제2 커패시터 전극의 몸체는 상기 면적으로부터 바깥쪽으로 제1 방향으로 신장하고 상기 제2 커패시터 전극의 신장부는 상기 제1 방향에 평행하지 않은 제2 방향으로 신장한다. 상기 커패시터 전극의 신장부가 추가적인 용량성 면적을 제공할 수 있으므로, 소정의 커파시턴스를 제공하면서도 픽셀 영역의 다른 면적 안의 커패시터 전극의 다른 부분의 총 면적을 감소시키는 방향으로 커패시터 전극이 디자인될 수 있다.

[0017] 상기 제1 커패시터 전극의 신장부는 실질적으로 삼각형 윤곽 또는 사다리꼴 윤곽을 가짐이 이해되어야 한다. 상기 제1 커패시터 전극의 신장부는 상기 제2 커패시터 전극의 몸체와 135도로 놓인 적어도 하나의 가장자리를 가진다. 뿐만 아니라, 상기 제1 커패시터 전극의 신장부는 상기 제2 커패시터 전극의 몸체와 135도의 각도로 놓인 가지(branch)를 가질 수 있다.

[0018] 위에 언급한 연결부는 상기 제2 커패시터 전극과 픽셀 전극이 함께 상기 제1 커패시터 전극에 대한 대향 전극으로 작용하도록, 상기 제2 커패시터 전극과 픽셀 전극을 전기적으로 커플링하는 데에 이용된다. 상기 연결부는 상기 제1 커패시터 전극의 신장부와 상기 신장부에 인접한 상기 제2 커패시터 전극의 몸체에 의해 정의된 영역 안에 위치하는 것이 바람직하다.

[0019] 본 발명에 이용하기 위한 MVA LCD는 복수개의 평행한 게이트 라인과, 상기 게이트 라인에 수직이며 서로 평행한 복수개의 데이터 라인을 주로 포함하며, 각 픽셀 영역이 두 개의 인접한 게이트 라인과 두 개의 인접한 데이터 라인에 의해 정의되는 박막 트랜지스터(TFT) LCD일 수 있다.

[0020] 위에 언급한 조절 구조는 돌출부과 슬릿의 어레이를 포함할 수 있는데, 여기서 상기 돌출부는 실질적으로 지그재그 패턴으로 그리고 서로에 대해 평행하게 배열되어 있고 상기 슬릿과 돌출부는 교대로 배열되어 있다. 상기 각 픽셀 영역 안에서, 상기 돌출부 중 하나는 꺾인 부분을 가진다. 본 발명의 일 실시예에서, 상기 각 픽셀 영역은 상기 돌출부과 슬릿에 의해 복수개의 면적으로 분할되고, 상기 꺾인 부분과 상기 꺾인 부분에 인접한 데이터 라인 사이에 정의된 면적은 광 투과 상태에서 다른 면적보다 어둡다. 따라서, 이 실시예에서, 상기 제1 커패시터 전극의 신장부는 실질적으로 상기 꺾인 부분과 상기 꺾인 부분에 인접한 데이터 라인 사이에 형성된다.

#### 실시예

[0022] 본 발명은 특유하게 디자인된 스토리지 커패시터를 구비하는 멀티-도메인 수직 정렬(MVA) LCD를 제공한다. 본 발명에 이용되기 위한 LCD는 주로 제1 기판과 제2 기판 사이에 개재된 액정층 및 이 두 기판 중 적어도 어느 하나 상에 제공되는 조절 구조를 포함한다. 상기 기판은 수직 정렬을 위해, 예를 들어 수직 정렬 박막을 이용해 가공되어, 상기 액정층에 실질적인 전계가 인가되지 않으면 상기 기판의 가공된 면에 대체로 수직인 방향으로 상기 액정층 안의 액정 분자가 정렬된다. 상기 액정층은 음의 유전상수 이방성을 가진다. 상기 조절 구조는 전압이 인가되면 상기 액정 분자가 비스듬하게 정렬되어 각 픽셀 영역 안에서 배향이 복수개의 방향을 포함하도록 상기 액정층의 배향을 조절함으로써 시야각 성능을 개선한다. 각 픽셀 영역은 상기 조절 구조에 의해 복수개의 면적으로 분할된다. 노말 흑색(normally black) LCD의 경우, 광 투과 상태에서 일부 면적은 다른 면적보다 어둡다. 그 이유는 후술된다. 상기 제1 기판 상에 제공된 조절 구조와 상기 제2 기판 상에 제공된 픽셀 전극 사이의 각도가 90도 미만인 면적 안에서, 액정 분자는 서로 충돌하도록 다른 방향으로 기울어져 있어 액정 분자의 불규칙한 정렬을 초래함으로써 LCD의 휘도에 악영향을 미친다. 불규칙하게 정렬된 액정 분자는 전압이 인가되지 않을 때 광 누설을 일으키고 전압이 인가될 때에는 어두운 면적을 형성함으로써 휘도를 감소시킬 수 있다. 본 발명에 따른 스토리지 커패시터는 주로 상기 픽셀 전극과 함께 스토리지 커패시터 유닛을 형성하기 위한 상기 각 픽셀 영역 안의 제1 커패시터 전극을 포함한다. 상기 제1 커패시터 전극은 몸체와 상기 몸체의 한 측면으로부터 신장하는 적어도 하나의 신장부(다른 말로, 날개부)를 가진다. LCD의 총 휘도를 증가시키고 소정 스토리지 커파시턴스를 제공하기 위하여, 제2 커패시터 전극의 신장부는 광 투과 상태에서 픽셀 영역의 어두운 면적에 형성된다.

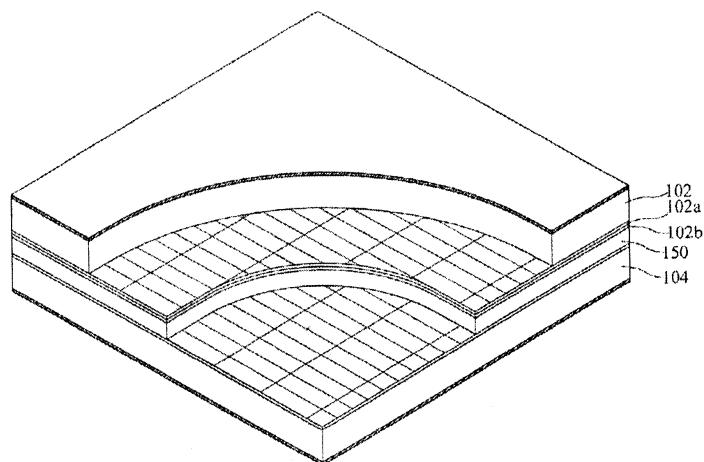

[0023] 본 발명의 MVA LCD는 바람직하게는 박막 트랜지스터(TFT) LCD이다. 도 6에 도시한 바와 같이, 본 발명의 제1 기판(102)은 그 상부에 칼라 필터(102a)와 공통 전극(102b)이 형성되기 때문에 칼라 필터(CF) 기판이라고 불리며, 제2 기판(104)은 TFT 기판이라고 불린다. 흔히, 기판 사이의 셀 간격을 정의하기 위해 기판 사이에 스페이서(170)가 형성된다. 당업자라면 칼라 필터가 제1 기판 대신에 제2 기판 상에 TFT와 함께 제공될 수 있음을 알 수

있을 것이다.

[0024]

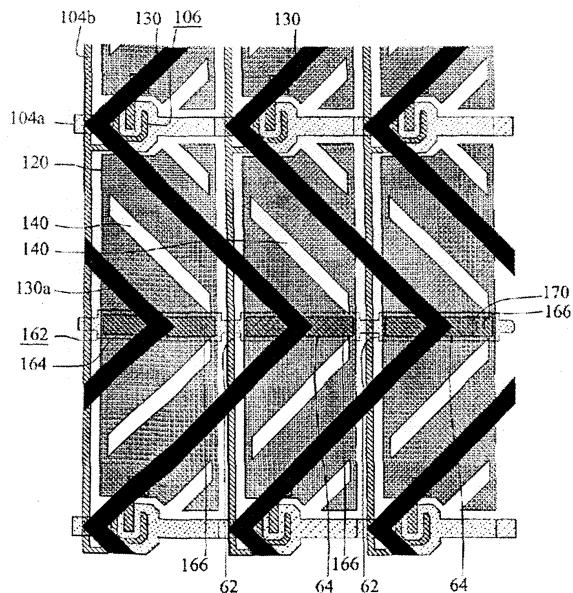

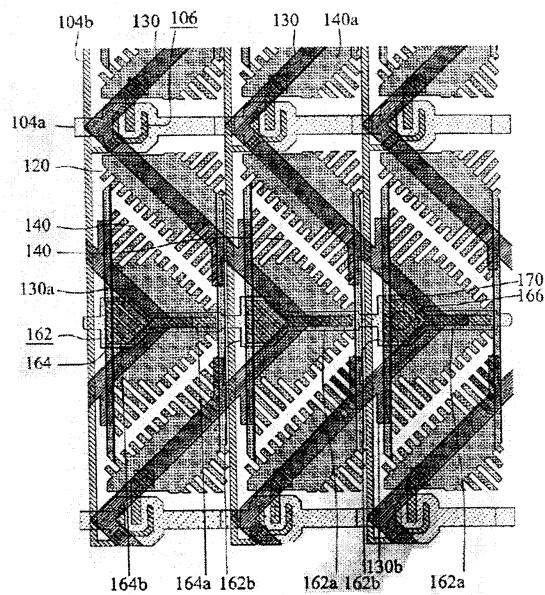

도 1은 본 발명의 일 실시예에 따른 MVA LCD(100)의 일부에 대한 상면도로서, 간단히 도시하기 위하여 TFT를 형성하는 비정질 반도체 패턴은 생략하였다. LCD(100)의 TFT 기판에는 복수개의 평행한 게이트 라인(104a), 게이트 라인에 수직이며 서로 평행한 복수개의 데이터 라인(104b)과, 게이트 라인(104a)과 데이터 라인(104b)이 교차하는 곳에 매트릭스처럼 형성된 복수개의 박막 트랜지스터(TFTs)(106)와 픽셀 전극(120)이 제공되어 있다. 픽셀 전극(120)은 두 개의 인접한 게이트 라인(104a)과 두 개의 인접한 데이터 라인(104b)에 의해 둘러싸인 영역 안에 배치되어 있다. 이 실시예에서, 위에 언급한 조절 구조는 복수개의 돌출부(130)와 슬릿(140)을 포함한다. 액정층(도 6) 안의 액정 분자의 정렬은 전압의 인가에 의해 유도되어 복수개의 서로 다른 방향을 포함함으로써 LCD(100)의 시야각을 크게 증가시킨다. 돌출부(130)는 제1 기판(102) 상에 서로 평행하게 정렬되어 있고 실질적으로 지그재그 패턴으로 꺾여있다. 슬릿(140)은 픽셀 전극(120) 상에 제공된다. 도 1에 도시한 바와 같이, 돌출부(130)와 슬릿(140)은 교대로 배열되어 있다. 제1 기판(102)의 공통 전극(102b) 상에 복수개의 슬릿을 형성함으로써 돌출부(130)가 교체될 수 있음을 주목.

[0025]

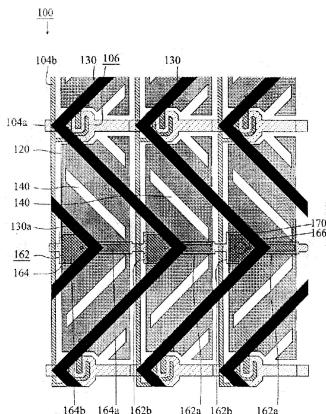

도 2는 도 1의 MVA LCD(100)의 일부에 대한 상면도로서, 도시의 간단함을 위해 픽셀 전극(120)과 돌출부(130)가 생략된 것이다. 본 발명의 LCD에서 스토리지 커패시터(Cs)는 픽셀 영역 안에 제공된다. 게이트 금속층은 제1 커패시터 전극(162), TFT(106)의 게이트 전극뿐만 아니라 위에 언급한 게이트 라인(104a)을 형성하는 데 이용되고, 데이터 금속층은 제2 커패시터 전극(164), TFT(106)의 소스/드레인 전극뿐만 아니라 위에 언급한 데이터 라인(104b)을 형성하는 데 이용된다. 이 실시예에서, 커패시터 전극(162, 164) 각각은 게이트 라인(104a)의 신장 방향과 평행한 방향으로 신장하는 몸체(162a, 164a)와 몸체(162a, 164a)의 두 측면으로부터 바깥쪽으로 신장하는 신장부(162b, 164b)를 가진다. 몸체(162a, 164a)의 신장 방향은 신장부(162b, 164b)의 신장 방향과 평행하지 않다. 제1 커패시터 전극(162)의 몸체(162a)는 픽셀 영역을 가로질러 형성된다. 커패시터 전극(162, 164)의 신장부(162b, 164b)는 실질적으로 사다리꼴 윤곽을 가진다. 스토리지 커패시터는 제2 커패시터 전극(164)과 픽셀 전극(120)이 함께 제1 커패시터 전극(162)에 대한 대향 전극으로 작용하도록, 제2 커패시터 전극(164)을 픽셀 전극(120)에 전기적으로 커플링하는 연결부를 포함한다. 연결부는 비아홀을 포함할 수 있고, 이 비아홀을 통한 연결은 픽셀 전극(120)을 형성하는 데에 사용되는 ITO와 같은 금속층으로 형성될 수 있다. 제1 커패시터 전극(162)과 대향 전극은 스토리지 커패시턴스 유닛을 형성한다. 스토리지 커패시턴스 유닛의 목적은 TFT가 꺼진 후에도 소정 시간 동안의 정해진 한계 안에서 픽셀 전극에서의 전압이 유지되도록 하는 것이다.

[0026]

도 1에서 보는 바와 같이, 두 개의 인접한 게이트 라인(102a)과 두 개의 인접한 데이터 라인(104b)에 의해 정의되는 픽셀 영역 안에서, 돌출부(130)는 삼각형의 꺾인 부분(130a)을 가진다. 이 실시예에서, 각 픽셀 영역은 돌출부(130)와 슬릿(140)에 의해 복수개의 면적으로 분할되고, 돌출부(130)의 꺾인 부분(130a)과 꺾인 부분(130a)에 인접한 데이터 라인(104b) 사이에 정의된 면적은 광 투과 상태에서 다른 면적보다 어둡다. 따라서, 이 실시예에서, 제1 커패시터 전극(162)의 신장부(162b)는 실질적으로 돌출부(130)의 꺾인 부분(130a)과 꺾인 부분(130a)에 인접한 데이터 라인(104b) 사이에 형성된다. 따라서, 본 발명은 위에 언급한 스토리지 커패시터 디자인에 의해, 다시 말해 낮은 휘도의 표시 면적(즉, 꺾인 부분(130a)과 꺾인 부분(130a)에 인접한 데이터 라인(104b) 사이에 정의된 면적)을 감소시키고, 높은 휘도의 표시 면적(즉, 꺾인 부분(130a)과 꺾인 부분(130a)에 인접한 슬릿(140) 사이에 정의된 면적)을 증가시킴으로써, 총 휘도를 크게 증가시킬 수 있다.

[0027]

스페이서(170)가 그 부근의 액정 분자의 정렬에 악영향을 끼쳐 암-상태 광 누설 또는 어두워진 광-상태의 문제를 초래할 수 있으므로, 스페이서는 각 픽셀 영역의 어두운 면적, 즉 돌출부(130)의 꺾인 부분(130a)과 꺾인 부분(130a)에 인접한 데이터 라인(104b) 사이에 정의된 면적 안에 배치되는 것이 바람직하다. 뿐만 아니라, 스페이서는 제1 커패시터 전극(162)의 신장부(162b)와 신장부(162b)에 인접한 제1 커패시터 전극(162)의 몸체(162a) 사이에 각각 배치되어 스페이서(170)로 인해 어두워진 면적을 마스킹하는 것이 바람직하다.

[0028]

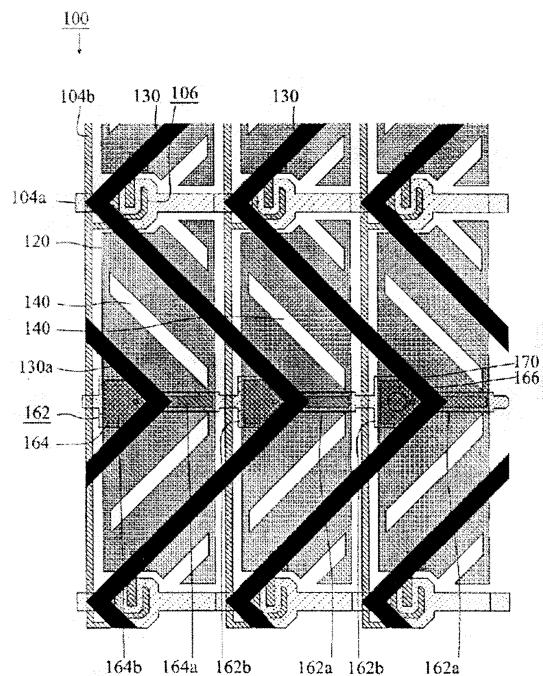

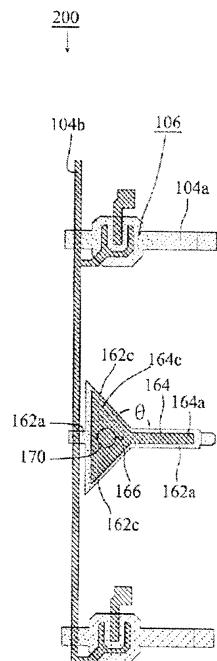

도 3은 본 발명의 일 실시예에 따른 MVA LCD(200)의 일부에 대한 상면도로서, 도시의 간단함을 위해 픽셀 전극(120)과 돌출부(130)가 생략된 것이다. LCD(200)는 커패시터 전극(162, 164)이 사다리꼴 신장부(162b, 164b) 대신에 삼각형 신장부(162c, 164c)를 각각 가진다는 것을 제외하고는 도 2에 도시한 LCD(100)와 거의 동일하다. 몸체(162a, 164a)의 신장 방향은 신장부(162c, 164c)의 신장 방향과 평행하지 않다.

[0029]

제1 커패시터 전극(162)의 신장부(162b, 162c)는 제1 커패시터 전극(162)의 몸체(162a)와 135도의 각도(도 2와 도 3에서 θ로 표시)로 놓인 적어도 하나의 가장자리를 가진 것을 주목. 제2 커패시터 전극(164)의 신장부(164b, 164c)도 제2 커패시터 전극(164)의 몸체(164a)와 135도의 각도로 놓인 적어도 하나의 가장자리를 가진다.

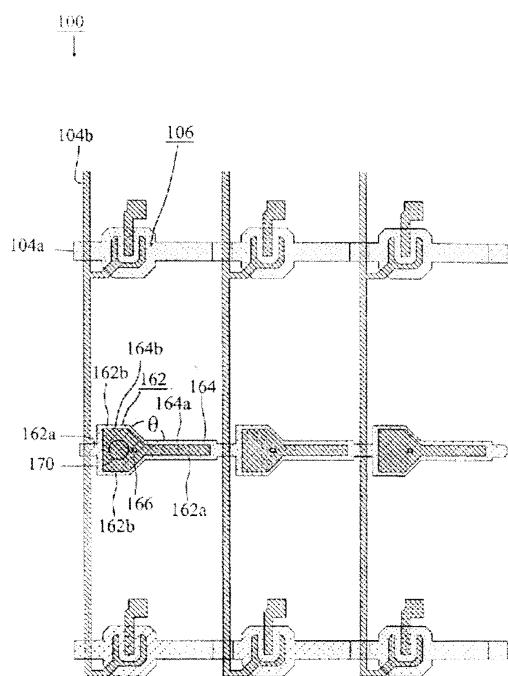

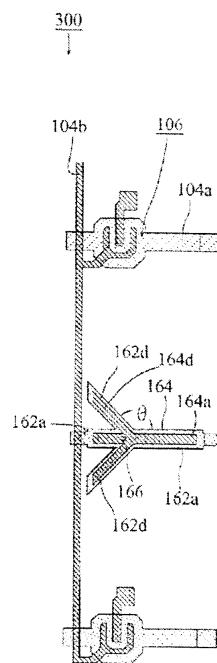

[0030] 도 4는 본 발명의 일 실시예에 따른 MVA LCD(300)의 일부에 대한 상면도로서, 도시의 간단함을 위해 픽셀 전극(120)과 돌출부(130)가 생략된 것이다. LCD(300)는 커패시터 전극(162, 164)이 각각 한 쌍의 가지같은 신장부(162d, 164d)를 가진다는 것을 제외하고는 도 2에 도시한 LCD(100)와 거의 동일하다. 가지같은 신장부(162d)와 몸체(162a) 사이의 각도(도 4에서 θ로 표시)가 135도임을 주목. 이 실시예에서, 커패시터 전극(162, 164)의 몸체(162a, 164a)의 신장 방향과 신장부(162d, 164d)의 신장 방향 사이의 각도는 135도이다. 신장부(162d, 164d)의 신장 방향은 신장부(162d, 164d)에 인접한 조절 구조(예를 들어 도 1에 도시한 돌출부(130))의 신장 방향과 거의 평행하다.

[0031] 도 5는 본 발명의 일 실시예에 따른 MVA LCD(400)의 일부에 대한 상면도이다. LCD(400)는 픽셀 전극(120) 안에 형성된 슬릿(140)이 복수개의 바늘 같은 텁니 모양(indentation)(140a)을 가지고 돌출부(130)가 불규칙하게 배열된 액정 분자에 의해 점유된 면적을 감소시키기 위한 가지(130b)를 가져 암-상태의 광 누설 또는 광-상태의 어두워짐을 초래하는 면적을 감소시킨다는 것을 제외하고는 도 1에 도시한 LCD(100)와 거의 동일하다. 이 실시예에서, 스토리지 커패시터는 도 3 및 도 4에 도시한 것과 같은 윤곽과 배열 또는 삼각형, 사각형, 오각형, 육각형, 다각형, 직선형 측면을 가지는 다른 모양, 또는 아크(arc)를 포함하는 그러나 이것에 한정되지는 않고 다른 형상의 신장부를 가지도록 디자인될 수 있다. 그리고, 본 실시예에서 LCD(400)는 슬릿(140a)과 가지(130b)를 동시에 구비하는 것으로 도시되었지만, 본 발명에 따른 LCD는 슬릿(140a)만을 가지거나 가지(130b)만을 가질 수 있다.

[0032] 도 7은 제1 커패시터 전극(62)과 제2 커패시터 전극(64)이 구비된 종래 LCD의 일부에 대한 상면도이다. 도 1 및 도 7을 참조하면, 본 발명은 앞서 언급한 디자인, 즉 낮은 휘도의 표시 면적을 감소시키고(신장부의 제공에 의함), 높은 휘도의 표시 면적을 증가시킴으로써(커패시터 전극의 일부를 신장부로 배열함에 의함), 거의 동일한 스토리지 커패시턴스를 실현하면서도(제1 커패시터 전극과 제2 커패시터 전극의 중첩 면적은 도 1과 도 7에서 거의 동일) 크게 증가된 총 휘도를 제공한다. 더군다나, 본 발명은 약  $100 \times 300 \mu\text{m}$ 의 단일 픽셀 사이즈를 가지는 LCD에 적용될 수 있고 관찰자는 커패시터 전극의 신장부를 볼 수 없다. 그리고, 본 발명이 더 큰 픽셀 사이즈, 예를 들면  $212 \times 637 \mu\text{m}$ 의 LCD에 적용되는 경우라도 관찰자는 여전히 커패시터 전극의 신장부를 볼 수 없다.

[0033] 이상에서는 본 발명의 실시예에 대하여 설명하였으나, 본 발명은 상기한 실시예에만 한정되는 것은 아니고 첨부된 청구항의 범위로부터 벗어나지 않으면서 다른 다양한 변경이나 변형이 가능하다.

### 발명의 효과

[0034] 본 발명에 따르면, 종래의 LCD와 거의 동일한 스토리지 커패시턴스를 실현하면서도 크게 증가된 총 휘도를 얻을 수 있다.

### 도면의 간단한 설명

[0001] 도 1은 본 발명의 일 실시예에 따른 멀티-도메인 수직 정렬(MVA) LCD의 일부에 대한 상면도이다.

[0002] 도 2는 도 1의 MVA LCD의 상면도로서, 간단히 도시하기 위해 픽셀 전극과 돌출부를 생략한 것이다.

[0003] 도 3은 본 발명의 다른 실시예에 따른 MVA LCD의 일부에 대한 상면도로서, 간단히 도시하기 위해 픽셀 전극과 돌출부를 생략한 것이다.

[0004] 도 4는 본 발명의 다른 실시예에 따른 MVA LCD의 일부에 대한 상면도로서, 간단히 도시하기 위해 픽셀 전극과 돌출부를 생략한 것이다.

[0005] 도 5는 본 발명의 다른 실시예에 따른 MVA LCD의 일부에 대한 상면도이다.

[0006] 도 6은 본 발명의 일 실시예에 따른 액정 표시 장치의 일부에 대한 단면도이다.

[0007] 도 7은 종래 액정 표시 장치의 일부에 대한 상면도이다.

## 도면

## 도면1

## 도면2

## 도면3

## 도면4

도면5

도면6

도면7