(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7372027号

(P7372027)

(45)発行日 令和5年10月31日(2023.10.31)

(24)登録日 令和5年10月23日(2023.10.23)

(51)国際特許分類

H 0 2 M 7/48 (2007.01)

F I

H 0 2 M

7/48

F Z A B

請求項の数 9 (全23頁)

|          |                             |          |                                             |

|----------|-----------------------------|----------|---------------------------------------------|

| (21)出願番号 | 特願2018-41630(P2018-41630)   | (73)特許権者 | 000005108<br>株式会社日立製作所<br>東京都千代田区丸の内一丁目6番6号 |

| (22)出願日  | 平成30年3月8日(2018.3.8)         | (74)代理人  | 110000062<br>弁理士法人第一国際特許事務所                 |

| (65)公開番号 | 特開2019-161720(P2019-161720) | (72)発明者  | 三好 智之<br>東京都千代田区丸の内一丁目6番6号<br>株式会社日立製作所内    |

| A)       |                             | (72)発明者  | 白石 正樹<br>東京都千代田区丸の内一丁目6番6号<br>株式会社日立製作所内    |

| (43)公開日  | 令和1年9月19日(2019.9.19)        | (72)発明者  | 森 瞳宏<br>東京都千代田区丸の内一丁目6番6号<br>株式会社日立製作所内     |

| 審査請求日    | 令和3年2月5日(2021.2.5)          | (72)発明者  | 仲田 清                                        |

| 審判番号     | 不服2023-1599(P2023-1599/J1)  |          |                                             |

| 審判請求日    | 令和5年1月31日(2023.1.31)        |          |                                             |

最終頁に続く

(54)【発明の名称】 インバータ装置

## (57)【特許請求の範囲】

## 【請求項1】

3相各相の上アームに接続される第1のデュアルゲートIGBTおよび当該3相各相の下アームに接続される第2のデュアルゲートIGBTと、

前記第1および前記第2のデュアルゲートIGBTそれぞれに逆並列に接続されるダイオードとから構成されるインバータ装置であって、

前記第1および前記第2のデュアルゲートIGBTそれぞれは、第1および第2のゲート端子を有し、前記第1および前記第2のゲート端子の少なくともいずれかに閾値電圧以上の電圧を印加することで非導通状態から導通状態へ移行し、前記第1および第2のゲート端子に前記閾値電圧未満の電圧が印加されることで導通状態から非導通状態へ移行する特性を有し、

前記第1のデュアルゲートIGBTの前記第1のゲート端子は、第1のPWM信号を用いて生成した第1のゲート信号により駆動され、前記第1のデュアルゲートIGBTの前記第2のゲート端子は、第3のPWM信号を用いて生成した第3のゲート信号により駆動され、

前記第2のデュアルゲートIGBTの前記第1のゲート端子は、第2のPWM信号を用いて生成した第2のゲート信号により駆動され、前記第2のデュアルゲートIGBTの前記第2のゲート端子は、第4のPWM信号を用いて生成した第4のゲート信号により駆動され、

前記第1のPWM信号は、負荷を駆動制御するための電圧指令信号に基づいて導通幅が

変調されると共に、当該第1のPWM信号は、前記第2のPWM信号が非導通の期間幅より短い導通幅であり、かつ当該導通幅が前記第2のPWM信号の非導通の期間内に生成され、前記第2のPWM信号が導通から非導通に変化するタイミングから少なくとも2μ秒経過した後に非導通から導通に変化し、

前記第2のPWM信号は、前記第1のPWM信号の正負を逆相にした信号であると共に、当該第2のPWM信号は、前記第1のPWM信号が非導通の期間幅より短い導通幅であり、かつ当該導通幅が前記第1のPWM信号の非導通の期間内に生成され、前記第1のPWM信号が導通から非導通に変化するタイミングから少なくとも2μ秒経過した後に非導通から導通に変化し、

前記第3のPWM信号は、前記第1のPWM信号の導通幅が前記第1のゲート信号と前記第3のゲート信号との間のターンオン時のタイミングディレイ時間およびターンオフ時のタイミングディレイ時間を加算したタイミングディレイ期間より大きい場合には、当該第1のPWM信号と同じ導通幅の期間内に位置し当該第1のPWM信号の導通幅より短い導通幅に変調され、前記第1のPWM信号の導通幅が当該タイミングディレイ期間以下の場合には、非導通のままであると共に、当該第3のPWM信号は、前記第1のPWM信号が非導通から導通へ変化するタイミングから少なくとも1μ秒経過した後に非導通から導通へ変化し、前記第1のPWM信号が導通から非導通へ変化するタイミングから少なくとも5μ秒以前に導通から非導通へ変化し、

前記第4のPWM信号は、前記第2のPWM信号の導通幅が前記第2のゲート信号と前記第4のゲート信号との間のターンオン時のタイミングディレイ時間およびターンオフ時のタイミングディレイ時間を加算したタイミングディレイ期間より大きい場合には、当該第2のPWM信号と同じ導通幅の期間内に位置し当該第2のPWM信号の導通幅より短い導通幅に変調され、前記第2のPWM信号の導通幅が当該タイミングディレイ期間以下の場合には、非導通のままであると共に、当該第4のPWM信号は、前記第2のPWM信号が非導通から導通へ変化するタイミングから少なくとも1μ秒経過した後に非導通から導通へ変化し、前記第2のPWM信号が導通から非導通へ変化するタイミングから少なくとも5μ秒以前に導通から非導通へ変化し、

前記第1のデュアルゲートIGBTの前記第1のゲート端子の端子電圧を検知し、当該端子電圧から当該第1のゲートのオン・オフ動作をセンスして第1のフィードバック信号として前記第1のPWM信号と比較し、当該双方の信号が異なる際には警告信号を出力し、

前記第2のデュアルゲートIGBTの前記第1のゲート端子の端子電圧を検知し、当該端子電圧から当該第1のゲートのオン・オフ動作をセンスして第2のフィードバック信号として前記第2のPWM信号と比較し、当該双方の信号が異なる際には警告信号を出力し、前記警告信号に基づいて、前記第1から第4のPWM信号全てを非導通とすることを特徴とするインバータ装置。

#### 【請求項2】

請求項1に記載のインバータ装置であって、

前記第1のデュアルゲートIGBTの前記第2のゲート端子の端子電圧を検知し、当該端子電圧から当該第2のゲートのオン・オフ動作をセンスして第3のフィードバック信号として前記第3のPWM信号と比較し、当該双方の信号が異なる際には警告信号を出力し、前記第2のデュアルゲートIGBTの前記第2のゲート端子の端子電圧を検知し、当該端子電圧から当該第2のゲートのオン・オフ動作をセンスして第4のフィードバック信号として前記第4のPWM信号と比較し、当該双方の信号が異なる際には警告信号を出力することを特徴とするインバータ装置。

#### 【請求項3】

請求項1に記載のインバータ装置であって、

前記ダイオードは、半導体基体に炭化ケイ素を用いたショットキーバリアダイオードであることを特徴とするインバータ装置。

#### 【請求項4】

請求項1から3のいずれか1項に記載のインバータ装置であって、

10

20

30

40

50

前記第1および第2のPWM信号を生成するPWM制御演算部と、

前記第1のPWM信号を受けて前記第3のPWM信号を生成する第1のPWM信号変換部と、

前記第2のPWM信号を受けて前記第4のPWM信号を生成する第2のPWM信号変換部と、

前記第1から第4のPWM信号をそれぞれに受けて前記第1から第4のゲート信号を生成する第1から第4のゲート出力回路部と

を備え、

前記第1のPWM信号変換部、前記第1のゲート出力回路部および前記第3のゲート出力回路部により第1のゲート駆動回路を構成し、

前記第2のPWM信号変換部、前記第2のゲート出力回路部および前記第4のゲート出力回路部により第2のゲート駆動回路を構成する

ことを特徴とするインバータ装置。

【請求項5】

請求項1から3のいずれか1項に記載のインバータ装置であって、

前記第1および第2のPWM信号を生成するPWM制御演算部と、

前記第1のPWM信号を受けて前記第3のPWM信号を生成する第1のPWM信号変換部と、

前記第2のPWM信号を受けて前記第4のPWM信号を生成する第2のPWM信号変換部と、

前記第1から第4のPWM信号をそれぞれに受けて前記第1から第4のゲート信号を生成する第1から第4のゲート出力回路部と

を備え、

前記第1のゲート出力回路部および前記第3のゲート出力回路部により第1のゲート駆動回路を構成し、

前記第2のゲート出力回路部および前記第4のゲート出力回路部により第2のゲート駆動回路を構成し、

前記第1のPWM信号変換部および前記第2のPWM信号変換部を前記PWM制御演算部内に設ける

ことを特徴とするインバータ装置。

【請求項6】

請求項4または5に記載のインバータ装置であって、

前記PWM制御演算部は、プログラム可能な集積回路から構成される

ことを特徴とするインバータ装置。

【請求項7】

請求項1から6のいずれか1項に記載のインバータ装置を搭載した電気鉄道車両。

【請求項8】

3相各相の上アームに接続される第1のデュアルゲートIGBTおよび当該3相各相の下アームに接続される第2のデュアルゲートIGBTと、前記第1および前記第2のデュアルゲートIGBTそれぞれに逆並列に接続されるダイオードとから構成されるインバータ装置の駆動方法であって、

前記第1および前記第2のデュアルゲートIGBTそれぞれは、第1および第2のゲート端子を備え、前記第1および前記第2のゲート端子の少なくともいずれかに閾値電圧以上の電圧が印加されることで非導通状態から導通状態へ移行し、前記第1および前記第2のゲート端子に前記閾値電圧未満の電圧が印加されることで導通状態から非導通状態へ移行する特性を有し、

前記第1のデュアルゲートIGBTの前記第1のゲート端子を、第1のPWM信号を用いて生成した第1のゲート信号により駆動し、前記第1のデュアルゲートIGBTの前記第2のゲート端子を、第3のPWM信号を用いて生成した第3のゲート信号により駆動し、前記第2のデュアルゲートIGBTの前記第1のゲート端子を、第2のPWM信号を用い

10

20

30

40

50

て生成した第2のゲート信号により駆動し、前記第2のデュアルゲートIGBTの前記第2のゲート端子を、第4のPWM信号を用いて生成した第4のゲート信号により駆動し、前記第1のPWM信号を、負荷を駆動制御するための電圧指令信号に基づいて導通幅を変調すると共に、当該第1のPWM信号を、前記第2のPWM信号が非導通の期間幅より短い導通幅であり、かつ当該導通幅が前記第2のPWM信号の非導通の期間内に生成し、前記第2のPWM信号が導通から非導通に変化するタイミングから少なくとも2μ秒経過した後に非導通から導通に変化させ、

前記第2のPWM信号を、前記第1のPWM信号の正負を逆相にした信号と共に、当該第2のPWM信号を、前記第1のPWM信号が非導通の期間幅より短い導通幅であり、かつ当該導通幅が前記第1のPWM信号の非導通の期間内に生成し、前記第1のPWM信号が導通から非導通に変化するタイミングから少なくとも2μ秒経過した後に非導通から導通に変化させ、

前記第3のPWM信号を、前記第1のPWM信号の導通幅が前記第1のゲート信号と前記第3のゲート信号との間のターンオン時のタイミングディレイ時間およびターンオフ時のタイミングディレイ時間を加算したタイミングディレイ期間より大きい場合には、当該第1のPWM信号と同じ導通幅の期間内に位置し当該第1のPWM信号の導通幅より短い導通幅に変調し、前記第1のPWM信号の導通幅が当該タイミングディレイ期間以下の場合には、非導通のままですると共に、当該第3のPWM信号を、前記第1のPWM信号が非導通から導通へ変化するタイミングから少なくとも1μ秒経過した後に非導通から導通へ変化させ、前記第1のPWM信号が導通から非導通へ変化するタイミングから少なくとも5μ秒以前に導通から非導通へ変化させ、

前記第4のPWM信号を、前記第2のPWM信号の導通幅が前記第2のゲート信号と前記第4のゲート信号との間のターンオン時のタイミングディレイ時間およびターンオフ時のタイミングディレイ時間を加算したタイミングディレイ期間より大きい場合には、当該第2のPWM信号と同じ導通幅の期間内に位置し当該第2のPWM信号の導通幅より短い導通幅に変調し、前記第2のPWM信号の導通幅が当該タイミングディレイ期間以下の場合には、非導通のままですると共に、当該第4のPWM信号を、前記第2のPWM信号が非導通から導通へ変化するタイミングから少なくとも1μ秒経過した後に非導通から導通へ変化させ、前記第2のPWM信号が導通から非導通へ変化するタイミングから少なくとも5μ秒以前に導通から非導通へ変化させ、

前記第1のデュアルゲートIGBTの前記第1のゲート端子の端子電圧を検知し、当該端子電圧から当該第1のゲートのオン・オフ動作をセンスして第1のフィードバック信号として前記第1のPWM信号と比較し、当該双方の信号が異なる際には警告信号を出力し、前記第2のデュアルゲートIGBTの前記第1のゲート端子の端子電圧を検知し、当該端子電圧から当該第1のゲートのオン・オフ動作をセンスして第2のフィードバック信号として前記第2のPWM信号と比較し、当該双方の信号が異なる際には警告信号を出力することを特徴とするインバータ装置の駆動方法。

#### 【請求項9】

請求項8に記載のインバータ装置の駆動方法であって、

前記第1のデュアルゲートIGBTの前記第2のゲート端子の端子電圧を検知し、当該端子電圧から当該第2のゲートのオン・オフ動作をセンスして第3のフィードバック信号として前記第3のPWM信号と比較し、当該双方の信号が異なる際には警告信号を出力し、前記第2のデュアルゲートIGBTの前記第2のゲート端子の端子電圧を検知し、当該端子電圧から当該第2のゲートのオン・オフ動作をセンスして第4のフィードバック信号として前記第4のPWM信号と比較し、当該双方の信号が異なる際には警告信号を出力することを特徴とするインバータ装置の駆動方法。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、インバータ装置に関し、特に、鉄道車両等に使用されるモータをPWM(P

10

20

30

40

50

u l s e W i d t h M o d u l a t i o n : パルス幅変調) 制御により駆動するインバータ装置に好適である。

【背景技術】

【0002】

近年の省エネ、地球環境保全の世界的な動向に連動して、交流モータを用いる様々な製品に対して、そのモータの駆動源に電力変換装置が適用されている。中でも、電気鉄道車両や風力発電システムなど、モータ容量の大きな分野へ拡大している。特に、電気鉄道用のモータ駆動システムは、高効率を達成するためにモータ本体の高効率化やそれを駆動する変換器の高効率化が進められている。

【0003】

一般に、交流モータを可变速駆動するためには、直流電力を任意の周波数と電圧に変換する電力変換装置としてインバータが用いられ、インバータを構成する半導体スイッチング素子を PWM 制御することにより、交流モータへの印加電圧および周波数を制御している。

【0004】

従来の一般的なインバータ装置の回路構成としては、例えば、特許文献 1 にも示されるように(図 1)、交流モータを構成する 3 相の誘導性負荷に対し、上アームと下アームから構成される半導体スイッチング素子である IGBT が接続される。インバータとして動作する際、IGBT には、導通損失とスイッチング損失と呼ばれる電力損失が発生する。

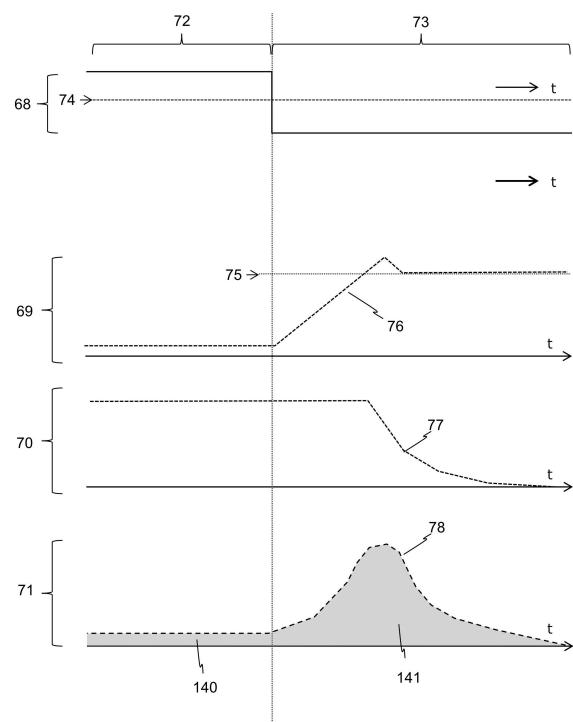

【0005】

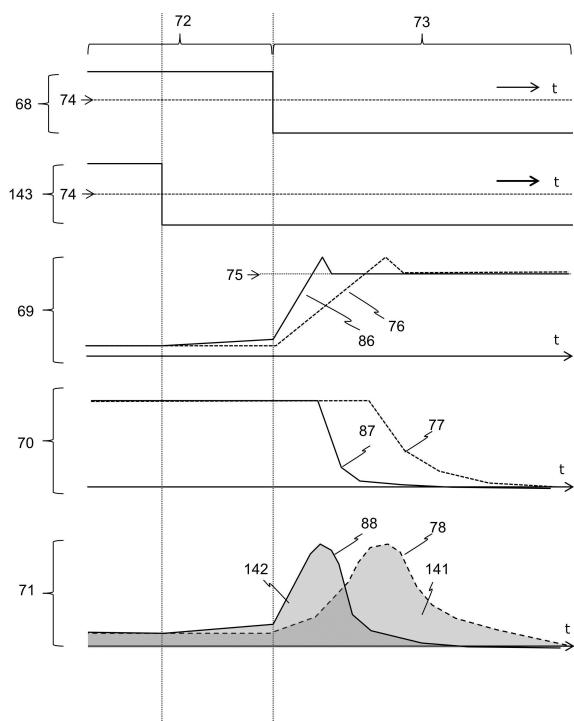

図 1 6 は、IGBT の導通時 7 2 および非導通時 7 3 における、ゲート信号 6 8、コレクタ・エミッタ間の電圧波形 6 9、コレクタ電流波形 7 0 および双方による電流・電圧積 7 1 を示す図である。ゲートにオン信号が印加されることによる IGBT の導通時においては、導通により電流が流れると共に、オン電圧がコレクタ・エミッタ間に印加される。これは、IGBT の内部のキャリアに起因した抵抗による電圧降下であり、このオン電圧と電流の積 7 8 によって電力損失 1 4 0 が発生する。次に、ゲートにオフ信号が印加されると、IGBT の内部のキャリアが排出されてコレクタ・エミッタ間電圧が上昇し、その電圧がインバータの印加電圧 7 5 に達すると、キャリアの排出が止まり、電流が低下する。このオン状態からオフ状態に推移する際に電流・電圧積 7 8 は上昇し、ターンオフ損失と呼ぶ電力損失 1 4 1 が生じる。さらに、ゲートにオフ状態からオン信号が印加する際も、同様の原理で電流・電圧積が上昇し、ターンオン損失と呼ぶ電力損失が生じる。このターンオフ損失とターンオン損失との和がスイッチング損失である。

【0006】

インバータでは、この IGBT の導通損失とスイッチング損失とによって、素子が発熱する。そこで、これによる温度上昇を抑制するため、IGBT 1 つの素子に流す電流を制限し、並列数を増加することで温度規格を保ち所望の性能を得る対策を行っている。従って、1 素子当たりに発生する電力損失を下げ、許容電流定格を増加することによって、体積当たりの変換効率の向上を図り、また素子の並列数が低減して素子の占有体積やコストの低減といった効果を生み出すことができる。

【0007】

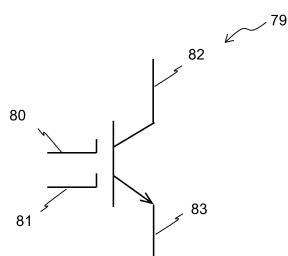

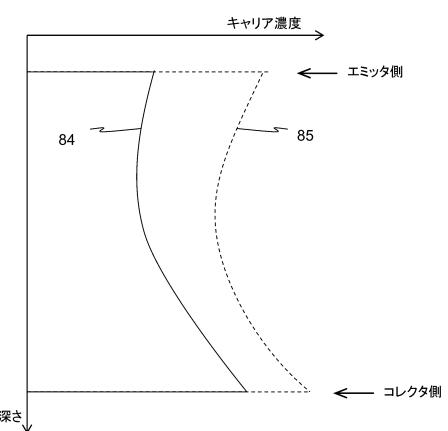

また、IGBT の電力損失を低減できる技術として、特許文献 2 および 3 に示される 2 つのゲート端子から構成されるデュアルゲート IGBT がある。図 1 7 は、デュアルゲート IGBT 7 9 のシンボル図である。1 つのコレクタ端子 8 2、1 つのエミッタ端子 8 3 に対し、2 つのゲート端子 8 0、8 1 を有し、2 つのゲート端子に入力するゲート信号によって、IGBT の導通・非導通を制御できるデュアルゲート IGBT である。図 1 8 は、デュアルゲート IGBT 導通時のキャリア濃度プロファイルを示す図である。2 つのゲートにオン信号を与えた場合 8 5 および 1 つのゲートにオン信号を与えてもう 1 つのゲートにオフ信号を与えた場合 8 4 のそれぞれのキャリア濃度を示している。2 つのゲートにオン信号を与えた場合 8 5 は、エミッタからの正孔キャリアの注入が促進し、IGBT 内部は高いキャリア濃度となり、これによって IGBT 導通時のオン電圧を低減するこ

10

20

30

40

50

できる。一方、1つのゲートにオン信号を与えて1つのゲートにオフ信号を与えた場合84は、正孔キャリアがエミッタへ排出され、これによって内部のキャリア濃度を低減することができる。つまり、デュアルゲートIGBTでは、新たに付加した1つのゲートとそれに与えるゲート電圧によって、IGBT導通時のキャリア濃度を変調することが可能である。この特徴を利用し、ターンオフスイッチングの直前に1つのゲート信号を先行してオフする駆動方式を適用することで、ターンオフ直前のキャリア濃度が下がり、低ターンオフ損失の特長を導出することができる。

【先行技術文献】

【特許文献】

【0008】

10

【文献】国際公開第2012/165196号

【文献】特開2005-191221号公報

【文献】国際公開第2014/038064号

【発明の概要】

【発明が解決しようとする課題】

【0009】

本願発明者が、デュアルゲートIGBTをモータ駆動用のPWM制御インバータ装置に適用することについて鋭意検討した結果、次の知見を得るに至った。

【0010】

20

本発明は、デュアルゲートIGBTの2つのゲート信号を適当なタイミングで導入することで、低損失な効果を導出するものである。図19は、デュアルゲートIGBTの導通時72および非導通時73における、2つのゲート信号68と143、コレクタ・エミッタ間の電圧波形69、コレクタ電流波形70および双方による電流・電圧積71を示す図である。なお、図19で示すコレクタ・エミッタ間の電圧波形69、コレクタ電流波形70および電流・電圧積71において、実線がデュアルゲートIGBTの特性を示し、破線が従来のシングルゲート型IGBTの特性を示している。デュアルゲートIGBTでは、スイッチングゲート68がオン状態72からオフ信号が入力する直前において、もう一方のキャリア制御ゲート143が先行してオフ信号を導入する駆動手法を適用する。キャリア制御ゲート143がオフすることで、IGBT内部のキャリア濃度が低減し、オン電圧が一時的に増加する。その後にスイッチングゲート68がオフすることで、IGBTは導通状態から非導通状態へ推移するが、キャリア濃度が低い状態から非導通状態へ推移することで、IGBT内部の空乏化が促進し、従来に対し高速にコレクタ・エミッタ間電圧69が上昇する(波形86)。さらに、キャリアも高速に排出されることから、電流70も短時間で0Aへ推移する(波形87)こととなる。これによって、電流・電圧積71の時間積分により導出されるターンオフ損失142は、従来のシングルゲート型IGBTにおけるターンオフ損失141に比べて大幅に低減されることとなる。この特性により、デュアルゲートIGBTとその駆動手法は、電力変換機能の低損失化、高効率化に有効な技術である。

30

【0011】

一方で、デュアルゲートIGBTをモータ駆動用のPWM制御インバータ装置に適用するためには、交流出力波形の品質と動作信頼性を維持して低損失性能を導出することのできる上下アームの駆動方式や、2つの駆動信号を生み出す回路およびその回路配置の最適化が必要不可欠であった。

40

【0012】

本発明は、従来型のIGBTを用いたPWM制御のインバータ装置に対し、インバータの相各相の上下アームを構成するIGBTにデュアルゲートIGBTを適用して電力損失の低いインバータ装置を提供することを目的とする。

【課題を解決するための手段】

【0013】

上記課題を解決するため、本発明に係るインバータ装置は、3相各相の上アームに接続

50

される第 1 のデュアルゲート IGBT および当該 3 相各相の下アームに接続される第 2 のデュアルゲート IGBT と、第 1 および第 2 のデュアルゲート IGBT それぞれに逆並列に接続されるダイオードとから構成され、第 1 および第 2 のデュアルゲート IGBT それは、第 1 および第 2 のゲート端子を有し、第 1 および第 2 のゲート端子の少なくともいづれかに閾値電圧以上の電圧を印加することで非導通状態から導通状態へ移行し、第 1 および第 2 のゲート端子に閾値電圧未満の電圧が印加されることで導通状態から非導通状態へ移行する特性を有し、第 1 のデュアルゲート IGBT の第 1 のゲート端子は、第 1 の PWM 信号を用いて生成した第 1 のゲート信号により駆動され、第 1 のデュアルゲート IGBT の第 2 のゲート端子は、第 3 の PWM 信号を用いて生成した第 3 のゲート信号により駆動され、第 2 のデュアルゲート IGBT の第 1 のゲート端子は、第 2 の PWM 信号を用いて生成した第 2 のゲート信号により駆動され、第 2 のデュアルゲート IGBT の第 2 のゲート端子は、第 4 の PWM 信号を用いて生成した第 4 のゲート信号により駆動され、第 1 の PWM 信号は、負荷を駆動制御するための電圧指令信号に基づいて導通幅が変調されると共に、当該第 1 の PWM 信号は、第 2 の PWM 信号が非導通の期間幅より短い導通幅であり、かつ当該導通幅が第 2 の PWM 信号の非導通の期間内に生成され、第 2 の PWM 信号が導通から非導通に変化するタイミングから少なくとも 2  $\mu$  秒経過した後に非導通から導通に変化し、第 2 の PWM 信号は、第 1 の PWM 信号の正負を逆相にした信号であると共に、当該第 2 の PWM 信号は、第 1 の PWM 信号が非導通の期間幅より短い導通幅であり、かつ当該導通幅が第 1 の PWM 信号の非導通の期間内に生成され、第 1 の PWM 信号が導通から非導通に変化するタイミングから少なくとも 2  $\mu$  秒経過した後に非導通から導通に変化し、第 3 の PWM 信号は、第 1 の PWM 信号の導通幅が第 1 のゲート信号と第 3 のゲート信号との間のターンオン時のタイミングディレイ時間およびターンオフ時のタイミングディレイ時間を加算したタイミングディレイ期間より大きい場合には、当該第 1 の PWM 信号と同じ導通幅の期間内に位置し当該第 1 の PWM 信号の導通幅より短い導通幅に変調され、第 1 の PWM 信号の導通幅が当該タイミングディレイ期間以下の場合には、非導通のままであると共に、当該第 3 の PWM 信号は、第 1 の PWM 信号が非導通から導通へ変化するタイミングから少なくとも 1  $\mu$  秒経過した後に非導通から導通へ変化し、第 1 の PWM 信号が導通から非導通へ変化するタイミングから少なくとも 5  $\mu$  秒以前に導通から非導通へ変化し、第 4 の PWM 信号は、第 2 の PWM 信号の導通幅が第 2 のゲート信号と第 4 のゲート信号との間のターンオン時のタイミングディレイ時間およびターンオフ時のタイミングディレイ時間を加算したタイミングディレイ期間より大きい場合には、当該第 2 の PWM 信号と同じ導通幅の期間内に位置し当該第 2 の PWM 信号の導通幅より短い導通幅に変調され、第 2 の PWM 信号の導通幅が当該タイミングディレイ期間以下の場合には、非導通のままであると共に、当該第 4 の PWM 信号は、第 2 の PWM 信号が非導通から導通へ変化し、第 2 の PWM 信号が導通から非導通へ変化するタイミングから少なくとも 1  $\mu$  秒経過した後に非導通から導通へ変化し、第 2 の PWM 信号が導通から非導通へ変化するタイミングから少なくとも 5  $\mu$  秒以前に導通から非導通へ変化し、第 1 のデュアルゲート IGBT の第 1 のゲート端子の端子電圧を検知し、当該端子電圧から当該第 1 のゲートのオン・オフ動作をセンスして第 1 のフィードバック信号として第 1 の PWM 信号と比較し、当該双方の信号が異なる際には警告信号を出力し、第 2 のデュアルゲート IGBT の第 1 のゲート端子の端子電圧を検知し、当該端子電圧から当該第 1 のゲートのオン・オフ動作をセンスして第 2 のフィードバック信号として第 2 の PWM 信号と比較し、当該双方の信号が異なる際には警告信号を出力し、警告信号に基づいて、第 1 から第 4 の PWM 信号全てを非導通とすることを特徴とする。

#### 【発明の効果】

#### 【0014】

本発明によれば、インバータ動作において、IGBT がスイッチングする際のターンオフスイッチング損失およびターンオンスイッチング損失を低減させる効果を奏することにより、低損失と高品質を両立したモータ駆動用インバータ装置を提供することができる。

#### 【図面の簡単な説明】

10

20

30

40

50

## 【0015】

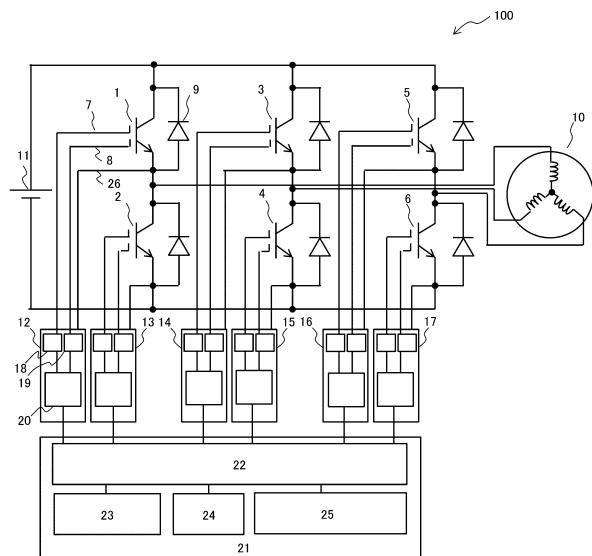

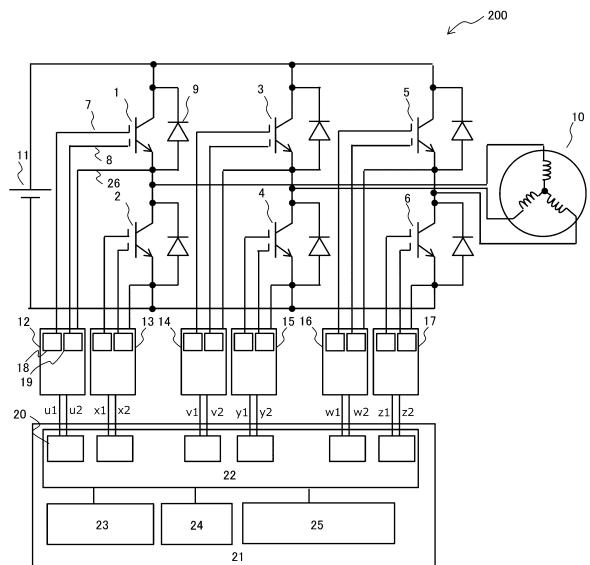

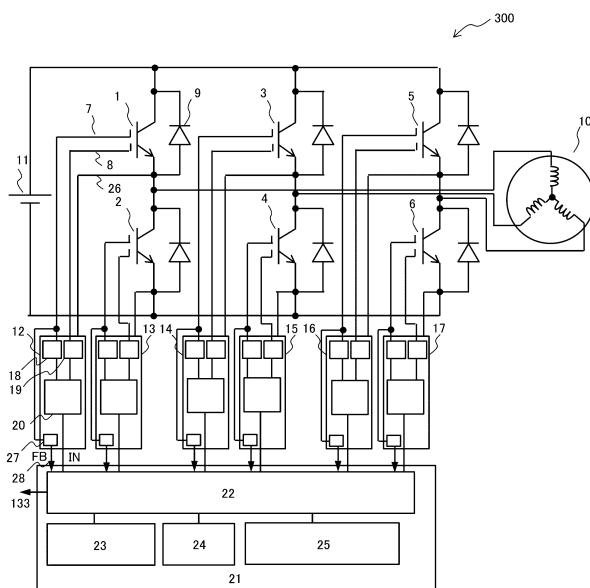

【図1】本発明の実施例1に係るインバータ装置の回路図である。

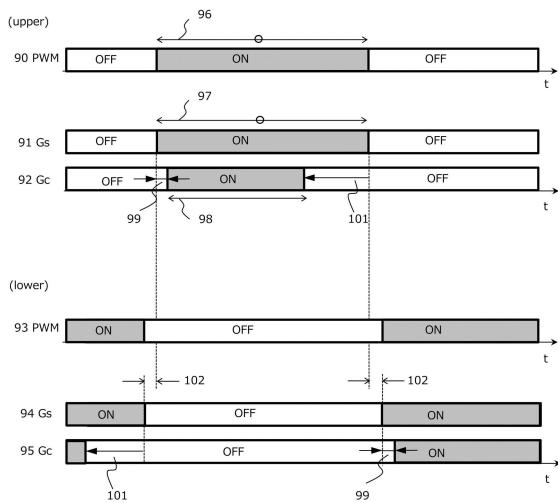

【図2】実施例1に係るインバータ動作を実現するための制御信号を示す図である。

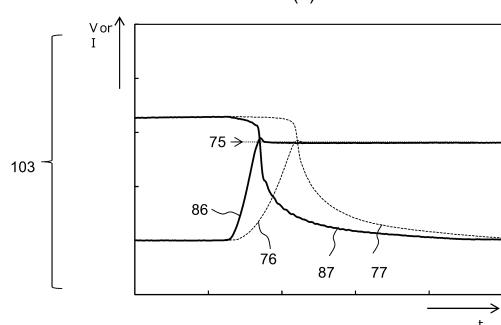

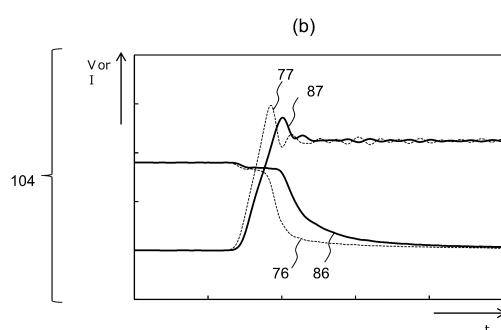

【図3】デュアルゲートIGBTのターンオフおよびターンオン時のスイッチング波形を示す図である。

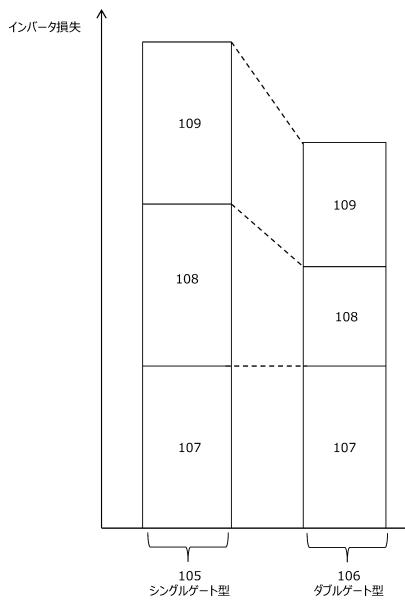

【図4】従来のインバータ装置および本発明に係るインバータ装置のインバータ損失を示す図である。

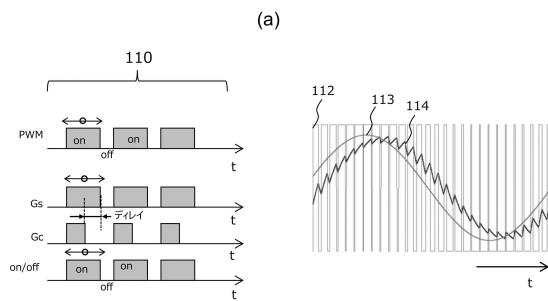

【図5】本発明を適用したインバータ装置および適用しないインバータ装置の入力信号および出力波形を示す図である。

【図6】本発明の実施例2に係るインバータ装置の回路図である。

10

【図7】実施例2に係るインバータ動作を実現するための制御信号を示す図である。

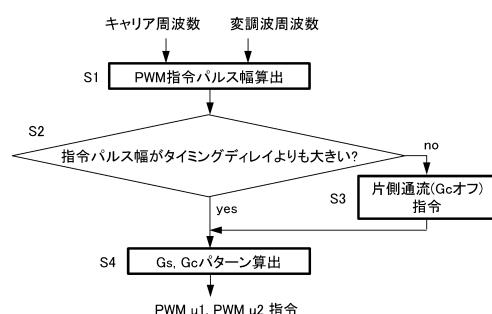

【図8】実施例2におけるデュアルゲートIGBTの制御信号を決定するシーケンスを示すフローチャートである。

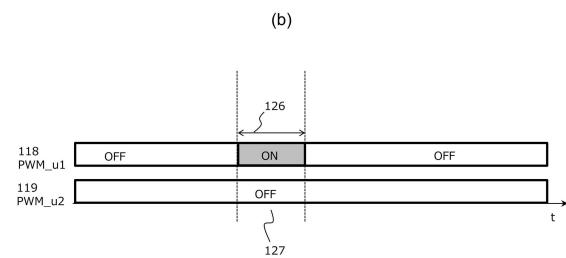

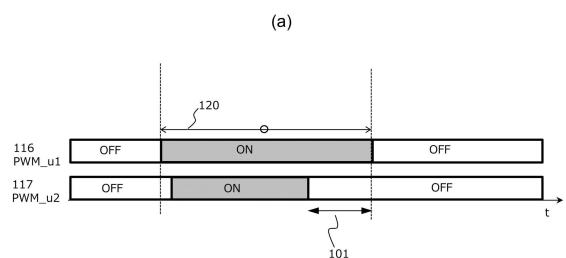

【図9】通常幅動作時および狭幅動作時における指令信号を示す図である。

【図10】本発明の実施例3に係るインバータ装置の回路図である。

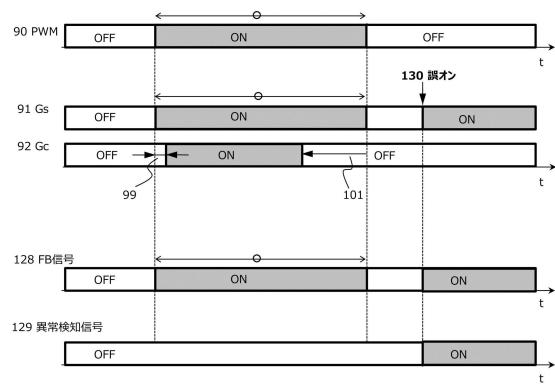

【図11】実施例3におけるフィードバック信号および異常検知信号をゲート制御信号と共に示す図である。

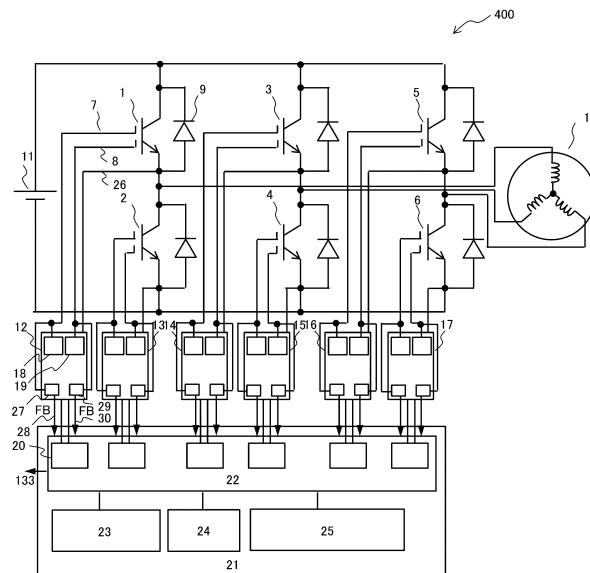

【図12】本発明の実施例4に係るインバータ装置の回路図である。

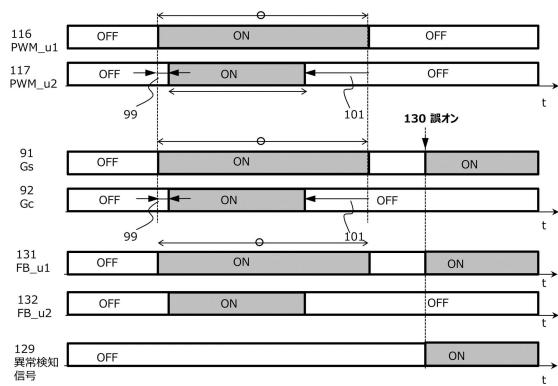

【図13】実施例4におけるフィードバック信号および異常検知信号(Gs誤オン動作時)をゲート制御信号と共に示す図である。

20

【図14】実施例4におけるフィードバック信号および異常検知信号(Gc誤オン動作時)をゲート制御信号と共に示す図である。

【図15】本発明の実施例5に係るインバータ装置の回路図である。

【図16】IGBTの導通および非導通時における、ゲート信号、コレクタ・エミッタ間電圧、コレクタ電流および電流・電圧積を示す図である。

【図17】デュアルゲートIGBTのシンボル図である。

【図18】デュアルゲートIGBT導通時のキャリア濃度プロファイルを示す図である。

【図19】デュアルゲートIGBTの導通および非導通時における、2つのゲート信号、コレクタ・エミッタ間電圧、コレクタ電流および電流・電圧積を示す図である。

## 【発明を実施するための形態】

30

## 【0016】

以下、図面を参照して、本発明の実施形態として、実施例1～実施例5について説明する。

## 【実施例1】

## 【0017】

図1は、本発明の実施例1に係るインバータ装置100の回路図である。

本実施例1は、IGBTとして2つの独立制御が可能であるゲートを有するデュアルゲートIGBTを適用したインバータ装置である。交流モータを構成する3相の誘導性負荷10(以下では、「モータ10」という場合もある)に対し、上アームと下アームから構成される半導体スイッチング素子であるデュアルゲートIGBT1～6が接続される。デュアルゲートIGBT1～6には、それぞれ逆並列にダイオード9が接続される。

40

## 【0018】

デュアルゲートIGBT1～6は、2つの絶縁ゲート端子7および8(以下、単に「ゲート端子」と称す)と1つのエミッタ端子26から構成され、該2つのゲート端子それぞれに印加するゲート・エミッタ間電圧(以下、「ゲート電圧」と称す)によって導通・非導通を制御する。すなわち、少なくとも1つのゲート端子に印加された閾値電圧以上のゲート電圧によって、導通状態となり、2つのゲート端子に印加された閾値電圧未満のゲート電圧によって、非導通状態となる。

## 【0019】

インバータ装置100には、電圧源11から直流電力が供給され、IGBT1～6のゲ

50

ート端子 7 および 8 に印加されるゲート電圧によって、IGBT 1 ~ 6 それぞれが高速にターンオン、ターンオフを繰り返して、誘導性負荷 10 に交流電力を供給する。これにより、交流モータに回転力が与えられる。

#### 【0020】

デュアルゲート IGBT 1 のゲート電圧は、3 相上下アームの IGBT 1 ~ 6 の各々に接続したゲート駆動回路 12 ~ 17 によって生成される。ここで、デュアルゲート IGBT の 2 つのゲート端子 7 および 8 と、ゲート駆動回路 12 から出力され 2 つのゲート端子 7 および 8 それに接続される 2 つのゲート配線は、各々が電気的に絶縁され、ゲート駆動回路 12 によって独立に制御される。また、エミッタ端子 26 もゲート駆動回路 12 に接続され、内部の基準電位に固定される。

10

#### 【0021】

ゲート駆動回路の構成については、ゲート駆動回路 12 を例に採ると、デュアルゲート IGBT 1 のゲート 7 および 8 を駆動する信号を生成する PWM 信号変換部 20 と 2 つの出力バッファ 18 および 19 とから構成される。2 つの出力バッファ 18 および 19 は、PWM 信号変換部 20 で生成された 2 つの PWM 信号を、IGBT 1 のゲート 7 および 8 をオン・オフできる電圧に調整するためのスイッチング素子（図示せず）等から構成される。PWM 信号変換部 20 それぞれは、3 相上下アームに対する各 PWM 信号を受けて、ディレイを設けた 2 つの PWM 信号に変換する機能を有し、かつ入力された PWM 信号を絶縁された信号に変換する機能を有する。

#### 【0022】

ゲート駆動回路 12 の入力信号である PWM 信号は、ゲート駆動回路 12 と電気的に分離した基板上に配置される PWM インバータ制御装置 21 が備える PWM 制御演算部 22 により生成される。PWM 制御演算部 22 は、モータ 10 を駆動する 3 相各相の電圧指令信号（変調波）、搬送波（キャリア波）およびベクトル制御演算部 25 からの信号に基づいて、導通幅の変調された PWM 信号を生成する比較器や演算器（図示せず）を有する。また、PWM インバータ制御装置 21 が備えるベクトル制御演算部 25 は、インバータの出力線に設けた電流センサ（図示せず）により検出される IGBT の出力電流値と設定値との偏差を小さくするための演算を行い、高品質なインバータ交流出力信号を実現するための制御信号を PWM 制御演算部 22 へ伝える。

20

#### 【0023】

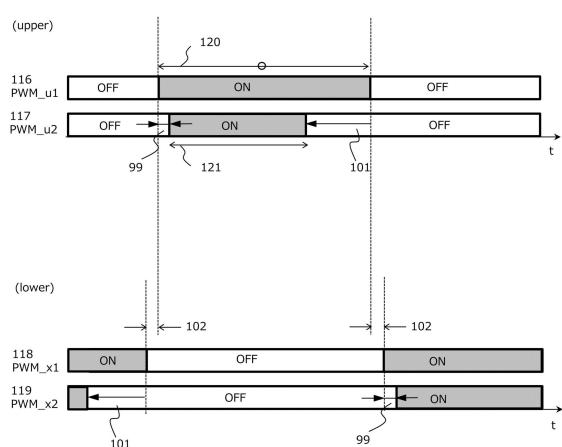

図 2 は、本実施例 1 に係るインバータ動作を実現するための制御信号を示す図である。図 2 には、インバータを構成する 3 相の内、1 相の上下アームに配置されたデュアルゲート IGBT を指令する PWM 信号 90 および 93、それぞれを基に生成されたゲート駆動信号として、2 つの上ゲート信号 91 と 92 および下アームゲート信号 94 と 95 を示している。ここで、それ以外の 2 相の上下アームに配置されたデュアルゲート IGBT を指令する PWM 信号およびゲート駆動信号は、図 2 に図示した信号から 120° 位相をずらした信号である（図示せず）。

30

#### 【0024】

PWM 制御演算部 22 より生成された上下アームの信号は、逆相にてオン・オフするタイミングを有し、また上下アームが同時にオンの信号を導入し、デュアルゲート IGBT が短絡状態となることを防ぐために、オン・オフの切替時に、上下アームが同時にオフする非ラップ期間 102 を設けている。非ラップ期間 102 としては、2 μ秒 ~ 20 μ秒が望ましい。

40

#### 【0025】

ここで、デュアルゲート IGBT の 2 つのゲートの一方をスイッチングゲート（Gs）、他方をキャリア制御ゲート（Gc）と定義する。Gs 信号 91 は、PWM 信号 90 と同じ導通幅および非導通幅で駆動する。この Gs 信号 91 のタイミングにより、デュアルゲート IGBT は導通または非導通状態となり、スイッチング動作を行う。一方、Gc 信号 92 は、Gs 信号 91 がオフからオン状態に変化した後、一定のディレイ時間 99 を設けてオフからオン状態に移行する。この制御により、デュアルゲート IGBT は低いトラン

50

スコンダクタンスによってターンオンするため、コレクタ・エミッタ間電圧 ( $V_{ce}$ ) の急峻な変化  $dV_{ce}/dt$  が抑制される。これによって、ターンオン時のノイズ低減の効果を奏することができる。

#### 【0026】

一方、 $G_s$  信号 91 が PWM 信号 90 と同じ導通幅の後、オンからオフ信号が入ってデュアルゲート IGBT がターンオフすることになるが、このタイミングの直前において、 $G_s$  信号 91 に先行して  $G_c$  信号 92 にオフ指令が入る。この制御により、デュアルゲート IGBT は、ターンオフスイッチング直前に、 $G_c$  信号 92 のオフ指令によって IGBT 内部のキャリア濃度が低減し、より高速でかつ低いテール電流でのターンオフスイッチングが可能となる。これによって、ターンオフ時の低電力損失の効果を奏することができる。さらに、デュアルゲート IGBT が導通時は、 $G_s$  信号 91 と  $G_c$  信号 92 の両者のゲートにオン指令が入るため、IGBT 内部のキャリア濃度を高め、低い導通損失の効果も奏することができる。ここで、ターンオン時の  $G_s$  信号と  $G_c$  信号とのタイミング遅延 (ディレイ) 99 は、1 μ秒以上が望ましく、また、ターンオフ時の  $G_c$  信号と  $G_s$  信号とのタイミング遅延 (ディレイ) 101 は、5 μ秒以上が望ましい。

10

#### 【0027】

対アームのデュアルゲート IGBT、また別相のデュアルゲート IGBT についても、入力の PWM 信号に応じて、上記と同じタイミングと導通幅で  $G_s$  と  $G_c$  の信号が入るものとする。ここで、PWM 信号 90 を受けて、上述した 2 つの  $G_s$  信号 91 および  $G_c$  信号 92、それらの遅延時間 99 および 101 は、3 相上下アーム毎に配置されたゲート駆動回路 12 の内部に設けられた PWM 信号変換部 20 により導出される。

20

#### 【0028】

次に、図 3 から 5 を参照して、本実施例 1 による効果を説明する。図 3 (a) に、デュアルゲート IGBT のターンオフスイッチング時の電圧および電流の波形 103 を、図 3 (b) に、デュアルゲート IGBT のターンオンスイッチング時の電圧および電流の波形 104 を示す。ここで、実線はデュアルゲート IGBT、破線は従来のシングルゲート型 IGBT の各特性を示し、電圧波形が 76 と 86 で、電流波形が 77 と 87 である。

#### 【0029】

ターンオフスイッチング時において (図 3 (a))、デュアルゲート IGBT は、ターンオフスイッチング直前に、 $G_c$  を  $G_s$  に先行してオフする指令が適用されることにより、キャリア濃度を低下させる。これにより、従来に対し、 $dV_{ce}/dt$  が上昇し、高速に電源電圧 75 へ  $V_{ce}$  が上昇する (電圧波形 86)。さらにその後、高速に電流が 0 A へ推移し、電流のテール期間が低減する (電流波形 87)。この特性によって、電流と電圧の積により発生する電力損失が、デュアルゲート IGBT では、従来のシングルゲート型 IGBT (電圧波形 76 および電流波形 77) に対し小さくなり、ターンオフ損失を低減させる効果を奏する。

30

#### 【0030】

一方、ターンオンスイッチング時において (図 3 (b))、片側のゲート即ち  $G_s$  のオン信号によってターンオンするため、その瞬間の IGBT のトランスコンダクタンスが下がり、コレクタ電流 ( $I_c$ ) の上昇  $dI_c/dt$  が低下する (電流波形 87)。この際、対アームのデュアルゲート IGBT に逆並列接続されたダイオードが、通流状態から逆阻止状態へ推移するリカバリー状態となる。デュアルゲート IGBT の低  $dI_c/dt$  の特性によって、対アームダイオードのリカバリー電流起因の電流跳ね上がりが抑制され、ターンオン損失が下がると共に、その電流起因のノイズも抑制され低減する。

40

以上のように、デュアルゲート IGBT を適用することによって、損失低減と低ノイズ化の効果を奏することができる。

#### 【0031】

図 4 は、従来のシングルゲート型 IGBT を適用したインバータ装置によるインバータ損失 105 (左側の棒グラフ) と、本発明に係るデュアルゲート IGBT を適用したインバータ装置によるインバータ損失 106 (右側の棒グラフ) とを示す図である。図 4 では

50

、インバータ装置の内のIGBT素子で発生する電力損失とその内訳を示している。IGBTでインバータ動作時に発生する電力損失は、導通損失107、ターンオフスイッチング損失108およびターンオンスイッチング損失109で占められる。この内、ターンオフスイッチング損失108およびターンオンスイッチング損失109が、IGBTが導通と非導通の間を推移する際に発生するスイッチング損失である。

#### 【0032】

図示のとおり、デュアルゲートIGBTを採用することによって、IGBT特有の低い導通損失107を維持し、ターンオフスイッチング損失108およびターンオンスイッチング損失109をそれぞれ低減することができる。その効果はそれぞれ、およそ30%および10%の低減率である。これにより、インバータ装置にあってIGBTで発生する電力損失を、数10%低減できる効果を奏する。

10

#### 【0033】

図5は、図5(a)に、本発明に係るデュアルゲートIGBTによるインバータ装置の入力信号110および1相の出力電流波形114を示し、図5(b)に、本発明を適用しないデュアルゲートIGBTによるインバータ装置の入力信号111および1相の出力電流波形154を示す図である。ここで、本発明を適用しないデュアルゲートIGBTによるインバータ装置では、PWM信号に対してGs信号の導通幅が長い場合の1例を示す。

#### 【0034】

本発明に係るインバータ装置では、Gs信号の導通幅とPWM信号の導通幅とが等しく(図5(a))、本発明を適用しないインバータ装置と比較して、出力電流114において電流脈動(リップル)の小さい正弦波を生成でき、交流波形の品質が高い。これは、PWM信号のオン・オフ指令に対して、デュアルゲートIGBTの導通・非導通の幅をそれぞれ等しく制御することによる効果である。

20

#### 【0035】

一方、本発明を適用しないインバータ装置では、PWM信号のオン指令に対し、Gs信号の導通幅が長いため、PWMオン指令と次のPWMオン指令の間隔が狭くなる際に、Gs信号と次のGs信号の間隔が無くなることで、IGBTの導通時間が指令に対し長くなる(図5(b))。この制御では、導通時間が指令に対し実質長くなることから出力電流154の脈動は大きくなり、変調波の再現性が低く、交流波形の品質が劣ることとなる。

30

#### 【0036】

したがって、本発明では、PWM指令におけるオン指令幅とGs信号の幅とを等しく設定することによって、交流出力波形の高い品質を実現する効果を奏することができる。

#### 【実施例2】

#### 【0037】

図6は、本発明の実施例2に係るインバータ装置200の回路図である。

本実施例2も、先の実施例1と同様に、IGBTに2つの独立制御が可能であるゲートを有するデュアルゲートIGBTを適用したインバータ装置である。回路構成において、実施例1と同様の構成要素には、同じ付番をしている。実施例1との相違点は、ゲート駆動回路12～17およびPWM制御演算部22における内部構成にあり、その他の構成要素については実施例1と同様であるので、説明は省略する。

40

#### 【0038】

次に、2つのPWM信号も、実施例1と同様に、ゲート駆動回路12～17と電気的に分離した基板上に配置されるPWMインバータ制御装置21内部のPWM制御演算部22により生成される。PWM制御演算部22は、キャリア周波数演算部23、変調波演算部24およびベクトル制御演算部25の信号を受けて生成される最適な指令信号に基づいて、3相上下アームの各デュアルゲートIGBT1～6の導通・非導通タイミングを決める2つのPWM信号を出力し、各ゲート駆動回路12～17と接続する。本実施例2に係るPWM信号変換部20は、実施例1とは異なり、ゲート駆動回路12～17を構成する基板に配置せずに、PWM制御演算部22に内蔵された構成を採り、デュアルゲートIGBTの駆動を指令する2つのPWM信号が生成される。

50

## 【0039】

各ゲート駆動回路12～17は、各相、各アームそれぞれ2つのPWM信号の入力を受ける。例えば、ゲート駆動回路12を例に採ると、2つのPWM信号は絶縁された信号に変換され、出力バッファ18および19によってそれぞれ電圧変換される。PWM制御演算部22は、ゲート駆動回路12と電気的に分離した基板上に配置されるPWMインバータ制御装置21内部で構成される。本実施例2の構成では、各ゲート駆動回路12～17にはPWM信号変換部が不要であり、実施例1と比較してインバータ装置の省体積化を計ることが可能である。

## 【0040】

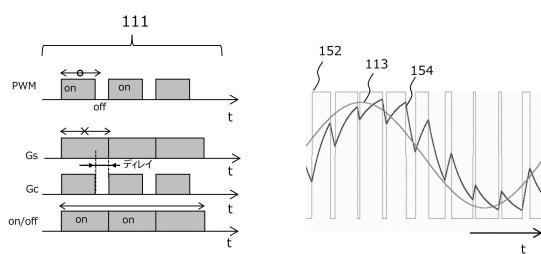

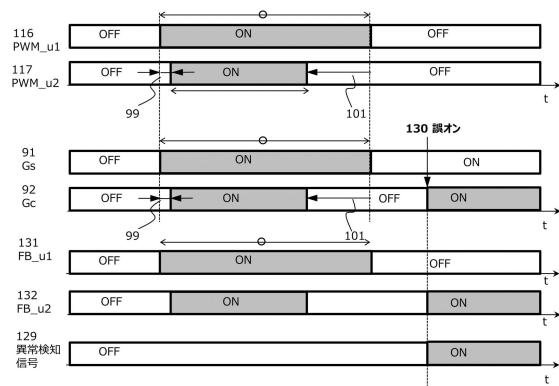

図7は、本実施例2におけるインバータ動作を実現するための制御信号を示す図である。図7には、インバータを構成する3相の内、1相の上下アームに配置されたデュアルゲートIGBTを指令する制御信号として、それぞれ2つのPWM\_u1 116とPWM\_u2 117、および、PWM\_x1 118とPWM\_x2 119を示している。ここで、それ以外の2相の上下アームに配置されたデュアルゲートIGBTの指令信号およびゲートの駆動信号は、図7に図示した信号から120°位相をずらした信号である。

10

## 【0041】

また、デュアルゲートIGBTの2つのゲートの内、スイッチングゲート(Gs)は、u1、x1、v1、y1、w1およびz1の指令信号を受け、キャリア制御ゲート(Gc)は、u2、x2、v2、y2、w2およびz2の指令信号を受けて動作するものとする。デュアルゲートIGBTの導通時間はGsのオン時間で決まり、PWM信号の内、u1、x1、v1、y1、w1およびz1の指令信号は、インバータの交流出力正弦波を実現するため、キャリア周波数演算部23、変調波演算部24およびベクトル制御演算部25により算出された信号である。

20

## 【0042】

一方、u2、x2、v2、y2、w2およびz2の指令信号は、u1、x1、v1、y1、w1およびz1の指令におけるオン幅より短く、u1、x1、v1、y1、w1およびz1のオン指令が入った後にオン指令が入り、u1、x1、v1、y1、w1およびz1のオフ指令が入る前にオフ指令が入る。

## 【0043】

上下アームの信号は、逆相にてオン・オフするタイミングを有しており、また上下アームが同時にオンの信号を導入し、デュアルゲートIGBTが短絡状態となることを防ぐために、オン・オフの切替時に、上下アームが同時にオフする非ラップ期間102が、u1とx1との間、v1とy1との間およびw1とz1との間に設けている。ここで、非ラップ期間102は、2μ秒～20μ秒が望ましい。

30

## 【0044】

デュアルゲートIGBTの導通、非導通の制御は、u1、x1、v1、y1、w1およびz1のタイミングにより行われ、それぞれにゲート駆動回路を介して接続されたGsのゲート電圧により行われる。デュアルゲートIGBTのターンオン動作は、Gsがu1、x1、v1、y1、w1およびz1のPWM指令を受けて、オフからオン状態に変化した後一定のディレイ時間を設け、u2、x2、v2、y2、w2およびz2のPWM指令を受けて、オフからオン状態に変化するシーケンスにより行われる。この制御により、デュアルゲートIGBTは低いトランスコンダクタンスによってターンオンするため、急峻なコレクタ・エミッタ間電圧(Vce)の変化dvce/dtが抑制される。これによって、実施例1と同様に、前述したターンオン時のノイズ低減の効果を奏することができる。

40

## 【0045】

一方、デュアルゲートIGBTのターンオフ動作は、Gsがu1、x1、v1、y1、w1およびz1のPWM指令を受けて、オンからオフ状態に変化する直前に、Gcが先行してu2、x2、v2、y2、w2およびz2のPWM指令を受けて、オンからオフ状態に変化するシーケンスにより行われる。この制御により、デュアルゲートIGBTは、ターンオフスイッチング直前に、Gcのオフ信号によってIGBT内部のキャリア濃度が低

50

減し、より高速でかつ低いテール電流でのターンオフスイッチングが可能となる。これによって、実施例1と同様に、前述したターンオフ時の低電力損失の効果を導出できる。

#### 【0046】

さらに、デュアルゲートIGBTが導通時は、GsとGc両者のゲートにオン信号が入るため、IGBT内部のキャリア濃度を高められ、低い導通損失の効果を導出できる。ここで、ターンオン時のGs信号とGc信号のタイミング遅延(ディレイ)は、1μ秒以上が望ましく、また、ターンオフ時のGc信号とGs信号のタイミング遅延(ディレイ)は、5μ秒以上が望ましい。以上のディレイを確保できるように、u1、x1、v1、y1、w1およびz1、また、u2、x2、v2、y2、w2およびz2のPWM指令が設定される。なお、以上のディレイ時間を有した2つのPWM信号は、PWM制御演算部22に配置されたPWM信号変換部20において生成される。

10

#### 【0047】

次に、図8および9を参照して、先の実施例1で説明した効果に加え、本実施例2が奏する効果を説明する。

デュアルゲートIGBTの2つのゲート信号の動作タイミングを決める2つのPWM信号は、PWM制御演算部22を構成するプログラム可能な集積回路(例えば、ゲートアレイ)によって生成されるが、指令パルス幅に応じて異なるパターンの信号を生成できる。図8は、本実施例2におけるデュアルゲートIGBTの2つのゲート信号(GsおよびGc)を決定するシーケンスを示すフローチャートである。PWM制御においては、導通幅の変調された様々なオン指令幅をもった入力信号でIGBTを動作させる必要があるが、2つのゲート信号に設定するタイミングディレイよりも短いオン指令幅(狭幅指令)においても、本実施例2により正常に動作させることができる。

20

#### 【0048】

PWM制御演算部22は、ステップS1で、キャリア周波数および変調波周波数に基づいてPWM指令パルス幅を算出する。ステップS2で、この算出した指令パルス幅がタイミングディレイよりも大きいか否かを判断する。

#### 【0049】

判断が「no」の場合、すなわち、狭幅指令の時には、Gc信号は非導通を維持する片側通流(Gcオフ)指令を設定して、以下のステップS4へ移行する。これにより、狭幅動作においても、導通・非導通の制御がデュアルゲートIGBTにおいて可能となる。

30

一方で、判断が「yes」の場合、すなわち、タイミングディレイよりも長い通常幅のオン指令をステップS4に対して設定する。

#### 【0050】

PWM制御演算部22は、ステップS4で、ステップS2またはS3の指令に基づいて、前述のようにディレイを有した2つのゲート信号(GsおよびGc)のパターンを算出し、例えば、u1およびu2の指令信号を出力する。

以上のシーケンスにより、前述した低インバータ損失の効果を奏することができる。

#### 【0051】

図9は、通常幅動作時および狭幅動作時におけるu1およびu2の指令信号116～119を示す図である。図9(a)が通常幅動作時で、図9(b)が狭幅動作時である。

40

通常幅動作時では、図9(a)に示すように、タイミングディレイを有した2つの指令信号u1およびu2がデュアルゲートIGBTを駆動する。一方、狭幅動作時では、図9(b)に示すように、u2はオフ状態を維持し、u1のみにオン・オフのパターンを有した指令を出力する。このように、キャリア周波数演算部23、変調波演算部24およびベクトル制御演算部25により算出されたオン指令幅に応じ、2つの指令信号を最適に変化させることが可能となる。

#### 【実施例3】

#### 【0052】

図10は、本発明の実施例3に係るインバータ装置300の回路図である。

本実施例3も、先の実施例1および2と同様に、IGBTに2つの独立制御が可能であ

50

るゲートを有するデュアルゲート IGBT を適用したインバータ装置である。回路構成において、実施例 1 と同様の構成要素には、同じ付番をしている。実施例 1 との相違点は、異常動作の検知機能をゲート駆動回路 12 ~ 17 および PWM 制御演算部 22 に設けた点にあり、その他の構成要素については実施例 1 と同様であるので、説明は省略する。

#### 【0053】

本実施例 3 は、異常な動作を検知するために、以下の構成を実施例 1 の回路構成に追加している。3 相上下アームの各デュアルゲート IGBT 1 ~ 6 において同様の構成を追加しているので、デュアルゲート IGBT 1 を例に採って説明する。デュアルゲート IGBT 1 の導通・非導通のタイミングを制御するスイッチングゲート (Gs) 端子 7 の信号線をゲート駆動回路 12 内部のレベル変換部 27 で受け、PWM インバータ制御装置 21 内の PWM 制御演算部 22 へ戻すフィードバック信号線 28 を設ける。このフィードバック信号線 28 は、デュアルゲート IGBT 1 の Gs 端子 7 の端子電圧を検知することにより Gs 端子 7 における動作信号をセンスし、Gs のオン・オフ動作の情報をフィードバック信号として PWM 制御演算部 22 へ通知する。プログラム可能な集積回路（例えば、ゲートアレイ）から構成される PWM 制御演算部 22 は、PWM 指令とフィードバック信号とを比較して、PWM 指令に対するフィードバック信号の相異を判断し、異なっていればアラームを発する機能やオン指令を遮断してオフ指令を発する機能を有する。

#### 【0054】

次に、実施例 1 で説明した効果に加え、本実施例 3 が奏する効果を説明する。図 11 は、本実施例 3 におけるフィードバック (FB) 信号および異常検知信号をゲート制御信号と共に示す図である。

#### 【0055】

フィードバック信号線 28 が、制御された Gs 信号と同一のオン・オフ動作のタイミングに関する情報をフィードバック信号として通知することから、PWM 制御演算部 22 は、PWM 指令とフィードバック信号とを比較して、PWM 指令に対するフィードバック信号の相異を判断することができる。したがって、PWM 指令に対して、デュアルゲート IGBT が PWM 指令と異なる動作をした際に、警告信号等を PWM 制御演算部 22 から発することが可能となる。

#### 【0056】

例えば、図 11 に示すように、PWM 信号 90 がオフの指令をデュアルゲート IGBT に与えている間に、何らかの原因によりデュアルゲート IGBT が自らの Gs 端子を介して誤オン動作 130 して導通した際に、フィードバック (FB) 信号 128 を受けた PWM 制御演算部 22 は、PWM 指令 90 との比較によって異常を検知できる。この機能により、誤オン動作による上下アーム短絡によってデュアルゲート IGBT 素子が破壊し得る事態が発生することを、異常検知信号 129 に基づいて PWM 指令を再設定することで防止することができる。例えば、PWM 制御演算部 22 は、異常を検知したデュアルゲート IGBT および該異常を検知したデュアルゲート IGBT と対になって上下アームを構成する他方のデュアルゲート IGBT に対して、それぞれの Gs 信号および Gc 信号に対する PWM 指令を非導通指令に再設定する。

また、本実施例 3 におけるフィードバック (FB) 信号 128 は、インバータ装置内部の故障検知にも有効な情報源となる。

#### 【0057】

以上では、本実施例 3 として、実施例 1 の回路構成に対して、Gs 端子 7 からの信号線とフィードバック信号線 28 を設けるようにしたが、実施例 2 の回路構成に対して、これらの信号線を設けるようにしてもよい。

#### 【実施例 4】

#### 【0058】

図 12 は、本発明の実施例 4 に係るインバータ装置 400 の回路図である。

本実施例 4 も、先の実施例 1 から 3 と同様に、IGBT に 2 つの独立制御が可能であるゲートを有するデュアルゲート IGBT を適用したインバータ装置である。本実施例 4 の

回路構成は、実施例2の回路構成をベースとするもので、すなわち、実施例1とは異なり、PWM信号変換部20は、ゲート駆動回路12～17を構成する基板には存在せず、PWM制御演算部22に内蔵され、また、実施例3に倣って、3相上下アームの各デュアルゲートIGBT1～6において、デュアルゲートIGBTの導通・非導通のタイミングを制御するスイッチングゲート(Gs)端子7の端子電圧を検知する信号線を設け、さらに追加して、キャリア制御ゲート(Gc)端子8の端子電圧を検知する信号線も設けたものである(ここでは、デュアルゲートIGBT1を例に採って説明)。

#### 【0059】

具体的には、ゲート駆動回路12の内部にレベル変換部27および29を設け、PWMインバータ制御装置21の内部のPWM制御演算部22へ戻すフィードバック信号線28および30を設けたものである。フィードバック信号線28および30は、デュアルゲートIGBT1のGs端子7の端子電圧およびGc端子8の端子電圧それぞれを検知し、Gs信号およびGc信号それぞれと同一のオン・オフ動作の情報をフィードバック信号として通知する。また、プログラム可能な集積回路(例えば、ゲートアレイ)から構成されるPWM制御演算部22は、PWM指令に対するフィードバック信号の相異を判断し、異なつていればアラームを発する機能やオン指令を遮断してオフ指令を発する機能を有する。

#### 【0060】

次に、実施例2で説明した効果に加え、本実施例4が奏する効果を説明する。図13および14は、本実施例4におけるフィードバック(FB)信号および異常検知信号をゲート制御信号と共に示す図である。

フィードバック信号線28が、Gs信号と同一のオン・オフ動作のタイミングに関する情報をフィードバック信号として通知することから、PWM制御演算部22は、PWM指令に対するフィードバック信号(デュアルゲートIGBTの導通・非導通の動作)の相異を判断することができる。また同様に、フィードバック信号線30が、Gc信号と同一のオン・オフ動作のタイミングに関する情報をフィードバック信号として通知することから、PWM制御演算部22は、PWM指令に対するフィードバック信号(Gc信号による動作)の相異を判断することができる。したがって、PWM指令に対して、デュアルゲートIGBTのGs信号およびGc信号がPWM指令と異なる動作をした際に、警告信号をPWM制御演算部22から発することが可能となる。

#### 【0061】

例えば、図13に示すように、PWM\_u1信号116がオフの指令をデュアルゲートIGBTにGs信号91として与えている間に、何らかの原因によりデュアルゲートIGBTが自らのGs端子を介して誤オン動作130して導通した際に、フィードバック信号線28を介してフィードバック信号FB\_u1信号131を受けたPWM制御演算部22は、PWM指令(PWM\_u1信号116)との比較によって異常を検知できる。

#### 【0062】

また例えば、図14に示すように、PWM\_u2信号117がオフの指令をデュアルゲートIGBTにGc信号92として与えている間に、何らかの原因によりデュアルゲートIGBTが自らのGc端子を介して誤オン動作130をした際に、フィードバック信号線30を介してフィードバック信号FB\_u2信号132を受けたPWM制御演算部22は、PWM指令(PWM\_u2信号117)との比較によって異常を検知できる。

#### 【0063】

以上の機能により、デュアルゲートIGBTのGs信号またはGc信号から誤オン動作による上下アーム短絡によってIGBT素子が破壊し得る事態が発生することを、異常検知信号129に基づいてPWM指令を再設定することで防止することができる。例えば、PWM制御演算部22は、異常を検知したデュアルゲートIGBTおよび該異常を検知したデュアルゲートIGBTと対になって上下アームを構成する他方のデュアルゲートIGBTに対して、それぞれのGs信号およびGc信号に対するPWM指令を非導通指令に再設定する。

また、本実施例4における各フィードバック信号は、インバータ装置内部の故障検知に

10

20

30

40

50

も有効な情報源となる。

【0064】

以上では、本実施例4として、実施例2の回路構成に対して、G<sub>s</sub>端子7およびG<sub>c</sub>端子8からの各信号線とフィードバック信号線28およびフィードバック信号線29を設けるようにしたが、実施例1の回路構成に対して、これらの信号線を設けるようにしてもよい。

【実施例5】

【0065】

図15は、本発明の実施例5に係るインバータ装置500の回路図である。

本実施例5は、先の実施例1から4と同様に、IGBTに2つの独立制御が可能であるゲートを有するデュアルゲートIGBTを適用したインバータ装置であるところ、デュアルゲートIGBTと逆並列に接続するダイオードとして、半導体基体にSiC（炭化ケイ素、シリコンカーバイド）を用いたショットキーバリアダイオード（SiC-SBD）を採用した点が先の実施例1～4と異なるものである。

【0066】

図15に示す回路構成は、前述のショットキーバリアダイオードの相違を除くと、先の実施例1の回路構成とその動作様も含めて同様であるので、説明は省略する。また、本実施例5の回路構成については、先の実施例1の回路構成に拘束されるものではなく、先の実施例2から4それぞれの回路構成としてもよい。

【0067】

次に、先の実施例1から4で説明した効果に加え、本実施例5が奏する効果を説明する。インバータ動作により発生するインバータ装置内の電力損失は、前述したIGBTの導通損失、ターンオフ損失およびターンオン損失に加え、逆並列に接続したダイオードのリカバリー損失および導通損失により構成される。ダイオードの対アームに配置されたIGBTがターンオンスイッチングすることで、ダイオードは順方向に通流した状態から逆阻止状態に推移し、リカバリー電流と呼ぶ順方向電流とは逆方向の電流が一時的に通流する。

【0068】

ここで、リカバリー損失とは、このリカバリー電流と印加される逆方向電圧から、電流・電圧積により発生する電力損失である。このリカバリー電流は、ダイオードの導通状態におけるキャリアに依存し、キャリアが正孔と電子の両者から構成されるpnダイオードでは、伝導度変調に寄与したキャリアが消滅するまでに時間を要するため、リカバリー電流が大きくなるが、ショットキーバリアダイオードは、キャリアが電子もしくは正孔の一方から構成されるため、逆阻止状態となった際に即座にキャリアが消滅し、リカバリー電流が小さくなる特長がある。特に、半導体基体にSiCを適用したSiC-SBDは、高耐圧な性能も併せ持つ。

【0069】

したがって、インバータ装置500として、SiC-SBD31とデュアルゲートIGBT1を組みわせた本実施例5は、ターンオフ損失とターンオン損失に加え、リカバリー損失も小さくすることができ、さらに低損失なインバータ装置を提供できることになる。

【0070】

以上、先の実施例1から5において説明したとおり、本発明を適用することにより、低電力損失でかつ低ノイズな交流出力を得ることができるインバータ装置を提供することができ、また併せて、短いパルスでも動作可能な高品質な交流正弦波を維持でき、さらに、異常な動作を検知し安全性を確保できる高信頼性も実現可能である。

【符号の説明】

【0071】

1…U相上アームのデュアルゲートIGBT、2…U相下アームのデュアルゲートIGBT、3…V相上アームのデュアルゲートIGBT、4…V相下アームのデュアルゲートIGBT、5…W相上アームのデュアルゲートIGBT、6…W相下アームのデュアルゲートIGBT、7…スイッチングゲート（G<sub>s</sub>）、8…キャリア制御ゲート（G<sub>c</sub>）、9…

10

20

30

40

50

ダイオード、10…3相の誘導性負荷（モータ）、11…電源電圧、12…U相上アームのゲート駆動回路、13…U相下アームのゲート駆動回路、14…V相上アームのゲート駆動回路、15…V相下アームのゲート駆動回路、16…W相上アームのゲート駆動回路、17…W相下アームのゲート駆動回路、18…G<sub>s</sub>駆動用出力バッファ、19…G<sub>c</sub>駆動用出力バッファ、20…PWM信号変換部、21…PWMインバータ制御装置、22…PWM制御演算部、23…キャリア周波数演算部、24…変調波演算部、25…ベクトル制御演算部、26…エミッタ端子、27…G<sub>s</sub>レベル変換部、28…G<sub>s</sub>フィードバック信号線、29…G<sub>c</sub>レベル変換部、30…G<sub>c</sub>フィードバック信号線、31…SiCのショットキーバリアダイオード（SiC-SBD）、40…ダイオード、41…U相上アームのIGBT（従来のシングルゲート型）、42…U相下アームのIGBT（従来のシングルゲート型）、43…V相上アームのIGBT（従来のシングルゲート型）、44…V相下アームのIGBT（従来のシングルゲート型）、45…W相上アームのIGBT（従来のシングルゲート型）、46…W相下アームのIGBT（従来のシングルゲート型）、47…ゲート、48…U相上アームのゲート駆動回路、49…U相下アームのゲート駆動回路、50…V相上アームのゲート駆動回路、51…V相下アームのゲート駆動回路、52…W相上アームのゲート駆動回路、53…W相下アームのゲート駆動回路、54…PWM回路、55…電流センサ、56…変調波（出力したい周波数の正弦波）、57…キャリア波（3角波信号）、58…PWM波形、59…U相のゲート信号、60…V相のゲート信号、61…W相のゲート信号、62…U-V線間電圧、63…V-W線間電圧、64…W-U線間電圧、65…U相電流、66…V相電流、67…W相電流、68…ゲート信号、69…電圧、70…電流、71…電流・電圧積、72…導通時、73…非導通時、74…IGBTの閾値電圧、75…電源電圧、76…従来IGBTのコレクタ・エミッタ間電圧、77…従来IGBTのコレクタ電流、78…従来IGBTの電流・電圧積、79…デュアルゲートIGBT、80…第1のゲート端子、81…第2のゲート端子、82…コレクタ端子、83…エミッタ端子、84…第1のゲートにオン信号を与え、第2のゲートにオフ信号を与えた場合のキャリア濃度分布、85…第1のゲートと第2のゲートにオン信号を与えた場合のキャリア濃度分布、86…デュアルゲートIGBTのコレクタ・エミッタ間電圧、87…デュアルゲートIGBTのコレクタ電流、88…デュアルゲートIGBTの電流・電圧積、90…上アームPWM信号、91…上アームG<sub>s</sub>信号、92…上アームG<sub>c</sub>信号、93…下アームPWM信号、94…下アームG<sub>s</sub>信号、95…下アームG<sub>c</sub>信号、96…PWM信号の導通指令期間、97…G<sub>s</sub>信号の導通指令期間、98…G<sub>c</sub>信号の導通指令期間、99…ターンオンディレイ期間、100…実施例1に係るインバータ装置、101…ターンオフディレイ期間、102…非ラップ期間、103…ターンオフスイッチング時の電圧、電流波形、104…ターンオンスイッチング時の電圧、電流波形、105…シングルゲート型IGBT（従来）を適用したインバータ装置、106…デュアルゲートIGBT（本発明）を適用したインバータ装置、107…導通損失、108…ターンオフスイッチング損失、109…ターンオンスイッチング損失、110…本発明を適用したPWM信号、G<sub>s</sub>信号、G<sub>c</sub>信号、導通/非導通期間、111…本発明を適用しないPWM信号、G<sub>s</sub>信号、G<sub>c</sub>信号、導通/非導通期間、112…本発明を適用したG<sub>s</sub>信号、113…変調波（インバータのターゲット波形）、114…本発明を適用した出力電流波形、116…上アームPWM\_u1信号、117…上アームPWM\_u2信号、118…下アームPWM\_x1信号、119…下アームPWM\_x2信号、120…上アームPWM\_u1信号の導通指令期間、121…上アームPWM\_u2信号の導通指令期間、122…PWM指令パルス幅算出、123…片側通流（G<sub>c</sub>オフ）指令、124…G<sub>s</sub>、G<sub>c</sub>パターン算出、125…PWM\_u1, PWM\_u2信号指令、126…狭幅オンパルス幅、127…非導通指令、128…フィードバック信号、129…異常検知信号、130…デュアルゲートIGBTの誤オン動作、131…上アームフィードバック\_u1信号、132…上アームフィードバック\_u2信号、133…正常/異常動作信号、140…導通損失、141…従来IGBTのターンオフスイッチング損失、142…デュアルゲートIGBTのターンオフスイッチング損失、143…第2のゲート信号、152…本

10

20

30

40

50

発明を適用しない Gs 信号、154...本発明を適用しないインバータの出力電流波形、200...実施例2に係るインバータ装置、300...実施例3に係るインバータ装置、400...実施例4に係るインバータ装置、500...実施例5に係るインバータ装置、600...従来のインバータ装置

【図面】

【図1】

図1

【図2】

図2

10

20

30

40

【図3】

図3

(a)

【図4】

図4

50

【図5】

図5

(b)

【図7】

図7

【 四 6 】

図6

10

20

【 四 8 】

8

30

40

【図 9】

図9

【図 10】

図10

10

20

【図 11】

図11

【図 12】

図12

30

40

50

【図 1 3】

図13

【図 1 4】

図14

10

【図 1 5】

図15

【図 1 6】

図16

20

30

40

50

【図17】

図17

【図18】

図18

10

20

【図19】

図19

30

40

50

---

フロントページの続き

東京都千代田区丸の内一丁目6番6号 株式会社日立製作所内

(72)発明者 石川 勝美

東京都千代田区丸の内一丁目6番6号 株式会社日立製作所内

(72)発明者 河野 恭彦

東京都千代田区丸の内一丁目6番6号 株式会社日立製作所内

(72)発明者 堀田 裕介

東京都千代田区丸の内一丁目6番6号 株式会社日立製作所内

合議体

審判長 須田 勝巳

審判官 脇岡 剛

審判官 吉田 美彦

(56)参考文献 特開2017-028811号公報 (JP, A)

特開平06-125256号公報 (JP, A)

特開2017-078927号公報 (JP, A)

特開2017-204918号公報 (JP, A)

特開2004-222367号公報 (JP, A)

特開2008-054375号公報 (JP, A)

国際公開第2014/038064号 (WO, A1)

(58)調査した分野 (Int.Cl., DB名)

H02M 1/00 - 7/98