(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-79887

(P2004-79887A)

(43) 公開日 平成16年3月11日(2004.3.11)

(51) Int.Cl.<sup>7</sup>

H01L 29/78

H01L 29/417

F 1

H01L 29/78

H01L 29/50

301B

M

テーマコード(参考)

4M104

5F140

審査請求 未請求 請求項の数 7 O L (全 10 頁)

(21) 出願番号

特願2002-240537(P2002-240537)

(22) 出願日

平成14年8月21日(2002.8.21)

(71) 出願人 503121103

株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

(74) 代理人 100096781

弁理士 堀井 豊

(74) 代理人 100098316

弁理士 野田 久登

(74) 代理人 100109162

弁理士 酒井 将行

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【要約】

【課題】Si結晶膜の表面の自然酸化に起因したSi結晶膜での導電性の低下によって生じる問題が解消された半導体装置を提供する。

【解決手段】SiGe結晶膜基板2上には、チャネル領域として機能するSi結晶膜4bが形成されている。また、Si結晶膜4bの上には、チャネル領域として機能するSiGe結晶膜4aが形成されている。また、SiGe結晶膜4aおよびSi結晶膜4bの両側には、ソース/ドレイン領域として機能するSi結晶膜3が形成されている。また、SiGe結晶膜4a上には、ゲート絶縁膜5を介してゲート電極6が形成されている。前述の構成によれば、SiGe結晶膜4aがSi結晶膜4bの自然酸化を抑制する。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

電子が流れる導電性部と、

該導電性部の下面に接することにより、該導電性部を構成する半導体に格子歪を生じさせて、該導電性部を流れる電子の移動度を向上させる移動度向上部と、前記半導体基板の表面を構成しながら前記導電性部の上面を覆うことにより、前記導電性領域が自然酸化されることを抑制する機能を有する酸化抑制部とを有する半導体基板を備えた、半導体装置。

**【請求項 2】**

前記酸化抑制部は、該導電性部を流れる電子の移動度を向上させる機能を有する、請求項 1 に記載の半導体装置。 10

**【請求項 3】**

前記酸化抑制部と前記移動度向上部とは同じ組成の物質により構成されている、請求項 1 に記載の半導体装置。

**【請求項 4】**

第 1 SiGe 層上に形成され、電子が移動する Si 層と、

該 Si 層上に該 Si 層に接して形成され、かつ、表面層を構成する第 2 SiGe 層とを有する半導体基板を備えた、半導体装置。

**【請求項 5】**

前記 Si 層および前記第 2 SiGe 層がトランジスタのチャネル領域として用いられた、請求項 4 に記載の半導体装置。 20

**【請求項 6】**

前記チャネル領域上に形成されたゲート絶縁膜を備え、

該ゲート絶縁膜が高誘電体膜である、請求項 4 に記載の半導体装置。

**【請求項 7】**

前記 Si 層および前記第 2 SiGe 層がトランジスタのソース / ドレイン領域として用いられた、請求項 4 ~ 6 のいずれかに記載の半導体装置。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、半導体基板を備えた半導体装置に関するものである。 30

**【0002】****【従来の技術】**

半導体基板を備えた半導体装置の一例の半導体を用いたトランジスタとしては、DRAM (Dynamic Random Access Memory) のトランジスタが広く知られている。図 5 は、従来の DRAM のトランジスタの断面図である。図 5 に示す従来の DRAM のトランジスタは次のような構造である。

**【0003】**

従来のトランジスタは、半導体基板 1 上の p 型不純物を含む SiGe 結晶膜基板 2 が形成されている。また、SiGe 結晶膜基板 2 上には、チャネル領域として機能する p 型不純物を含む Si 結晶膜 4 が形成されている。また、Si 結晶膜 4 の両側には、ソース / ドレイン領域として機能する n 型不純物を含む Si 結晶膜 3 が形成されている。また、Si 結晶膜 4 上には、ゲート絶縁膜 5 を介してゲート電極 6 が形成されている。 40

**【0004】**

前述の Si 結晶膜 3、Si 結晶膜 4、ゲート絶縁膜 5 およびゲート電極 6 により n チャネルトランジスタ 7 が構成されている。

**【0005】**

上記従来のトランジスタにおいては、Si 結晶膜 4 は、SiGe 結晶膜基板 2 上に形成されている。そのため、Si 結晶膜 4 に格子歪みが生じている。それにより、Si 結晶膜 4 中を流れる電子の移動度が向上している。つまり、従来のトランジスタは、SiGe 結晶膜基板 2 上に形成された Si 結晶膜 4 を、チャネル領域を構成する材料として利用するこ 50

とによって、ドレイン電流を大きくしている。

【0006】

なお、従来技術では、Si結晶膜4は、半導体基板内に形成され、電子が流れる導電性部の一例として記載されているとともに、SiGe結晶膜2は、導電性部の下面に接することにより、導電性部を構成する半導体に格子歪を生じさせて、その導電性部を流れる電子の移動度を向上させる移動度向上部の一例として記載されている。

【0007】

【発明が解決しようとする課題】

上記従来のトランジスタは、チャネル領域としてのSi結晶膜4の表面がゲート絶縁膜に接触する構造である。したがって、ゲート絶縁膜5を形成する段階において、Si結晶膜4の表面が外側に露出している。そのため、導電性部の一例のSi結晶膜4の表面に自然酸化膜等が形成され易い構造となっている。このため、ゲート絶縁膜5を形成した後にゲート絶縁膜5の存在に起因してSi結晶膜4の表面が酸化される。その結果、ゲート絶縁膜5自体の誘電率が低下する。それにより、ゲート電極に電圧を印加した場合に、Si結晶膜4に形成されるチャネル領域が不完全なものとなってしまう。その結果、所望のドレイン電流を得ることができないという問題が発生する。

【0008】

また、従来のトランジスタでは、ソース／ドレイン領域としてのSi結晶膜4の表面と、ソース／ドレイン領域に電流を流す導電性部材（たとえば、コンタクトプラグ）とが接触している。この導電性部材を形成する段階においても、Si結晶膜4の表面が外側に露出している。そのため、従来のトランジスタは、導電性部の一例のSi結晶膜4の表面に自然酸化膜等が形成され易くなっている。このため、導電性部材とソース／ドレイン領域としてのSi結晶膜4との間のコンタクト抵抗が増加する。その結果、トランジスタ動作速度が低下するという問題が発生する。

【0009】

本発明は、上述のような問題に鑑みてなされたものであり、その目的は、導電性部の表面の自然酸化に起因した導電性部での導電性の低下によって生じる問題が解消された半導体装置を提供することである。

【0010】

他の目的は、Si結晶膜の表面の自然酸化に起因したSi結晶膜での導電性の低下によって生じる問題が解消された半導体装置を提供することである。

【0011】

【課題を解決するための手段】

本発明の一の局面の半導体装置は、半導体基板を備えている。半導体基板は、電子が流れる導電性部と、導電性部の下面に接することにより、導電性部を構成する半導体に格子歪を生じさせて、導電性部を流れる電子の移動度を向上させる移動度向上部と、半導体基板の表面を構成しながら導電性部の上面を覆うことにより、導電性領域が自然酸化されることを抑制する機能を有する酸化抑制部とを有している。

【0012】

上記の構成によれば、半導体基板の表面層が自然酸化されにくい酸化抑制部により構成されているため、半導体基板の表面層が自然酸化されることに起因して生じる問題が解消される。また、移動度向上部の影響により格子歪が生じている導電部を電子が移動するため、電子の移動度が向上する。

【0013】

また、酸化抑制部は、導電性部を流れる電子の移動度を向上させる機能を有していることが好ましい。

【0014】

上記の構成によれば、導電部での電子の移動度がさらに向上する。

また、酸化抑制部と移動度向上部とは同じ組成の物質により構成されていることが好ましい。

10

20

30

40

50

**【 0 0 1 5 】**

上記の構成によれば、酸化抑制部にも導電部に格子歪を生じさせる機能が備えられているため、電子の移動度を低下させるおそれがない。

**【 0 0 1 6 】**

本発明の他の局面の半導体装置は、第1SiGe層上に形成されたSi層と、Si層上にSi層に接して形成され、かつ、表面層を構成する第2SiGe層とを有する半導体基板を備えており、Si層を電子が移動する様で用いられる。

**【 0 0 1 7 】**

上記の構成によれば、半導体基板の表面層が自然酸化されにくい第2SiGe層により構成されているため、半導体基板の表面層が自然酸化されることに起因して生じる問題が解消される。また、第1SiGe層の影響により格子歪が生じているSi層を電子が移動するため、電子の移動度は低下しない。さらに、Si層の表面に設けられているのは、Si層に格子歪が生じさせる第1SiGe層であるため、電子の移動度を低下させるおそれがない。

**【 0 0 1 8 】**

また、Si層および第2SiGe層は、トランジスタのチャネル領域として用いられてもよい。

**【 0 0 1 9 】**

上記の構成によれば、ゲート絶縁膜とチャネル領域とが接触することに起因したチャネル領域の自然酸化が抑制されるため、チャネル領域の自然酸化に起因したドレイン電流の低下が抑制される。

**【 0 0 2 0 】**

また、本発明の他の局面の半導体装置は、チャネル領域上に形成されたゲート絶縁膜を備え、ゲート絶縁膜が高誘電体膜であってもよい。

**【 0 0 2 1 】**

上記の構成によれば、自然酸化による性能の低下が著しい高誘電体膜の自然酸化を抑制することができる。

**【 0 0 2 2 】**

また、Si層および第2SiGe層は、トランジスタのソース／ドレイン領域として用いられてもよい。

**【 0 0 2 3 】**

上記の構成によれば、ソース／ドレイン領域の表面の自然酸化が抑制されるため、ソース／ドレイン領域とソース／ドレイン領域に接続される導電性部材との間でのコンタクト抵抗の増加を抑制することができる。

**【 0 0 2 4 】****【 発明の実施の形態】**

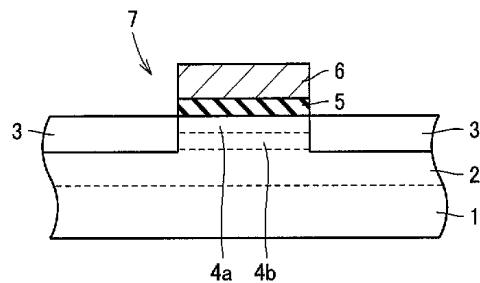

以下、図1～図4を用いて、本発明の実施の形態の半導体装置を説明する。

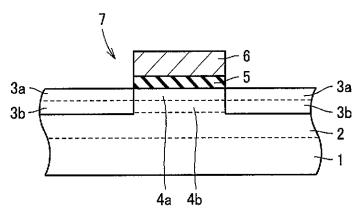

**【 0 0 2 5 】****(実施の形態1)**

まず、図1を用いて、本発明の実施の形態1の半導体装置を説明する。

**【 0 0 2 6 】**

図1に示すように、本実施の形態の半導体装置は、半導体基板1上にp型不純物を含むSiGe結晶膜基板2が形成されている。また、SiGe結晶膜基板2上には、チャネル領域として機能するp型不純物を含むSi結晶膜4bが形成されている。また、Si結晶膜4bの上には、チャネル領域として機能するp型不純物を含むSiGe結晶膜4aが形成されている。また、SiGe結晶膜4aおよびSi結晶膜4bの両側には、ソース／ドレイン領域として機能するn型不純物を含むSi結晶膜3が形成されている。また、SiGe結晶膜4a上には、ゲート絶縁膜5を介してゲート電極6が形成されている。なお、SiGe結晶膜4aは極薄膜である。

**【 0 0 2 7 】**

10

20

30

40

50

前述の Si 結晶膜 3、SiGe 4a、Si 4b、ゲート絶縁膜 5 およびゲート電極 6 により、n チャネルトランジスタ 7 が構成されている。

【0028】

上記本実施の形態の半導体装置によれば、チャネル領域の表面には、自然酸化されにくい SiGe 結晶膜 4a が用いられている。したがって、チャネル領域の表面に自然酸化膜を形成することなく、ゲート絶縁膜 5 を形成することができる。その結果、ゲート絶縁膜の誘電率の低下を抑制することができる。故に、ゲート電極に電圧を印加したときに、チャネル領域が不完全なものとなることが抑制される。したがって、トランジスタは、所望のドレイン電流を得ることができる。

【0029】

また、上記本実施の形態の半導体装置は、チャネル領域には、格子歪みのある Si 結晶膜 4b が形成されている。そのため、チャネル領域を流れる電子の移動度を低下させることなく、所望のドレイン電流を得ることができる。

【0030】

さらに、Si 結晶膜 3 の表面に設けられているのは、Si 結晶膜 3 に格子歪が生じさせる SiGe 結晶膜 4a であるため、電子の移動度を低下させるおそれがない。

【0031】

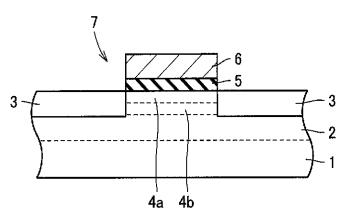

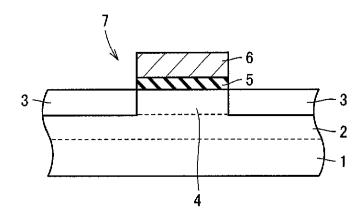

(実施の形態 2)

次に、図 2 を用いて本発明の実施の形態 2 の半導体装置を説明する。図 2 に示すように、本実施の形態の半導体装置は、半導体基板 1 上に p 型不純物を含む SiGe 結晶膜基板 2 が形成されている。また、SiGe 結晶膜基板 2 上には、チャネル領域として機能する p 型不純物を含む Si 結晶膜 4b が形成されている。また、Si 結晶膜 4b の上には、チャネル領域として機能する p 型不純物を含む SiGe 結晶膜 4a が形成されている。また、SiGe 結晶膜 4a および Si 結晶膜 4b の両側には、ソース / ドレイン領域として機能する、n 型不純物を含む Si 結晶膜 3b と Si 結晶膜 3b の上に位置する n 型不純物を含む SiGe 結晶膜 3a とが形成されている。また、SiGe 結晶膜 4a 上には、ゲート絶縁膜 5 を介してゲート電極 6 が形成されている。なお、p 型不純物を含む SiGe の結晶膜 4a は極薄膜である。

【0032】

前述の SiGe 結晶膜 3a、Si 結晶膜 3b、SiGe 結晶膜 4a、Si 結晶膜 4b、ゲート絶縁膜 5 およびゲート電極 6 により、n チャネルトランジスタ 7 が構成されている。

【0033】

上記本実施の形態の半導体装置によれば、チャネル領域の表面には、自然酸化されにくい SiGe 結晶膜 4a が用いられている。したがって、実施の形態 1 の半導体装置と同様に、トランジスタは、所望のドレイン電流を得ることができる。

【0034】

また、上記本実施の形態の半導体装置は、チャネル領域には、格子歪みのある Si 結晶膜 4b が形成されている。そのため、チャネル領域を流れる電子の移動度を低下させることなく、所望のドレイン電流を得ることができる。

【0035】

さらに、Si 結晶膜 4b の表面に設けられているのは、Si 結晶膜 4b に格子歪を生じさせる SiGe 結晶膜 4a であるため、電子の移動度を低下させるおそれがない。

【0036】

また、本実施の形態の半導体装置は、ソース / ドレイン領域の表面に自然酸化されにくい SiGe 結晶膜 3a が用いられている。そのため、ソース / ドレイン領域の表面に自然酸化膜を形成することなく、ソース / ドレイン領域表面に直接導電性部材を接続することができる。その結果、ソース / ドレイン領域とソース / ドレイン領域に接続された導電性部材との間でのコンタクト抵抗の増加を抑制することができる。したがって、トランジスタの動作速度の低下が抑制される。

【0037】

10

20

30

40

50

また、SiGe結晶膜3aの比抵抗はSi結晶膜3bに比べ桁違いに低い。そのため、ソース／ドレイン領域の抵抗を十分に低下させることができる。したがって、トランジスタの動作の高速化を促進することができる。

#### 【0038】

さらに、Si結晶膜3bの表面に設けられているのは、Si結晶膜3bに格子歪が生じさせるSiGe結晶膜3aであるため、電子の移動度を低下させるおそれがある。

#### 【0039】

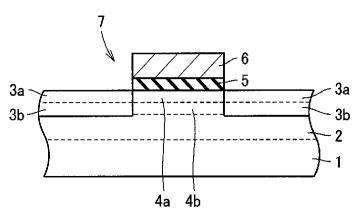

(実施の形態3)

次に、図3を用いて、本発明の実施の形態3の半導体装置を説明する。

#### 【0040】

図3に示すように、本実施の形態の半導体装置は、半導体基板1上にn型不純物を含むSiGe結晶膜基板2が形成されている。また、SiGe結晶膜基板2上には、チャネル領域として機能するn型不純物を含むSi結晶膜4bが形成されている。また、Si結晶膜4bの上には、チャネル領域として機能するn型不純物を含むSiGe結晶膜4aが形成されている。また、SiGe結晶膜4aおよびSi結晶膜4bの両側には、ソース／ドレイン領域として機能するp型不純物を含むSi結晶膜3が形成されている。また、SiGeの結晶膜4a上には、ゲート絶縁膜5を介してゲート電極6が形成されている。なお、n型不純物を含むSiGeの結晶膜4aは極薄膜である。

#### 【0041】

前述のSi結晶膜3、SiGe結晶膜4a、Si結晶膜4b、ゲート絶縁膜5およびゲート電極6により、Pチャネルトランジスタ7が構成されている。

#### 【0042】

すなわち、本実施の形態の半導体装置は、実施の形態1の半導体装置と比較した場合に、n型とp型とが逆になっていること以外相違点はない。

#### 【0043】

上記本実施の形態の半導体装置によれば、実施の形態1の半導体装置と同様に、チャネル領域の表面には、自然酸化されにくいSiGe結晶膜4aが用いられている。したがって、チャネル領域の表面に自然酸化膜を形成することなく、ゲート絶縁膜5を形成することができる。その結果、ゲート絶縁膜の誘電率の低下を抑制することができる。故に、ゲート電極に電圧を印加したときに、チャネル領域が不完全なものとなることが抑制される。したがって、トランジスタは、所望のドレイン電流を得ることができる。

#### 【0044】

また、上記本実施の形態の半導体装置は、実施の形態1の半導体装置と同様に、チャネル領域には、格子歪みのあるSi結晶膜4bが形成されている。そのため、チャネル領域を流れる電子の移動度を低下させることなく、所望のドレイン電流を得ることができる。

#### 【0045】

さらに、Si結晶膜4bの表面に設けられているのは、Si結晶膜4bに格子歪が生じさせるSiGe結晶膜4aであるため、電子の移動度を低下させるおそれがある。

#### 【0046】

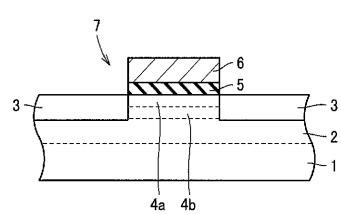

(実施の形態4)

次に、図4を用いて、本発明の実施の形態4の半導体装置を説明する。

#### 【0047】

図4に示すように、本実施の形態の半導体装置は、半導体基板1上にn型不純物を含むSiGe結晶膜基板2が形成されている。また、SiGe結晶膜基板2上には、チャネル領域として機能するn型不純物を含むSi結晶膜4bが形成されている。また、Si結晶膜4bの上には、チャネル領域として機能するn型不純物を含むSiGe結晶膜4aが形成されている。また、SiGe結晶膜4aおよびSi結晶膜4bの両側には、ソース／ドレイン領域として機能するp型不純物を含むSi結晶膜3bと、Si結晶膜3bの上に位置するp型不純物を含むSiGe結晶膜3aが形成されている。また、SiGeの結晶膜4aの上には、ゲート絶縁膜5を介してゲート電極6が形成されている。なお、n型不純物

10

20

30

40

50

を含む SiGe 結晶膜 4a は極薄膜である。

【0048】

前述の SiGe 結晶膜 3a、Si 結晶膜 3b、SiGe 結晶膜 4a、Si 結晶膜 4b、ゲート絶縁膜 5 およびゲート電極 6 により、p チャネルトランジスタ 7 が構成されている。

【0049】

すなわち、本実施の形態の半導体装置は、実施の形態 2 の半導体装置と比較した場合に、n 型と p 型とが逆になっていること以外相違点はない。

【0050】

上記本実施の形態の半導体装置によれば、実施の形態 2 に記載の半導体装置と同様に、チャネル領域の表面には、自然酸化されにくい SiGe 結晶膜 4a が用いられている。したがって、実施の形態 2 の半導体装置と同様に、トランジスタは、所望のドレイン電流を得ることができる。10

【0051】

また、上記本実施の形態の半導体装置は、実施の形態 2 の半導体装置と同様に、チャネル領域には、格子歪みのある Si 結晶膜 4b が形成されている。そのため、チャネル領域を流れる電子の移動度を低下させることなく、所望のドレイン電流を得ることができる。

【0052】

さらに、Si 結晶膜 4b の表面に設けられているのは、Si 結晶膜 4b に格子歪が生じさせる SiGe 結晶膜 4a であるため、電子の移動度を低下させるおそれがない。

【0053】

また、本実施の形態の半導体装置は、実施の形態 2 の半導体装置と同様に、ソース / ドレイン領域の表面に自然酸化されにくい SiGe 結晶膜 3a が用いられている。そのため、ソース / ドレイン領域の表面に自然酸化膜を形成することなく、ソース / ドレイン領域表面に直接導電性部材を接続することができる。その結果、ソース / ドレイン領域とソース / ドレイン領域に接続された導電性部材との間でのコンタクト抵抗の増加を抑制することができる。したがって、トランジスタの動作速度の低下が抑制される。20

【0054】

また、SiGe 結晶膜 3a の比抵抗は Si 結晶膜 3b に比べ桁違いに低い。そのため、ソース / ドレイン領域の抵抗を十分に低下させることができる。したがって、トランジスタの動作の高速化を促進することができる。30

【0055】

さらに、Si 結晶膜 3b の表面に設けられているのは、Si 結晶膜 3b に格子歪が生じさせる SiGe 結晶膜 3a であるため、電子の移動度を低下させるおそれがない。

【0056】

(実施の形態 5)

本実施の形態の半導体装置の構造は、図 1 ~ 図 4 を用いて説明した実施の形態 1 ~ 4 のいずれかに記載の半導体装置の構造と同様である。しかしながら、実施の形態 1 ~ 4 の半導体装置の構造においては、ゲート絶縁膜は単に誘電体膜であるものとして述べられているが、本実施の形態の半導体装置においては、絶縁膜を高誘電体膜である Al<sub>2</sub>O<sub>3</sub> 膜または HfO<sub>2</sub> 膜を用いる。その結果、本実施の形態の半導体装置によれば、自然酸化による性能の低下が著しい高誘電体膜の自然酸化を抑制することができる。40

【0057】

なお、上述の実施の形態 1 ~ 4 の半導体装置においては、本発明の、半導体基板内に形成され電子が流れる導電性部として、Si 結晶膜 3b, 4b が用いられている。また、本発明の、導電性部の下面に接することにより、導電性部を構成する半導体に格子歪を生じさせて、該導電性部を流れる電子の移動度を向上させる移動度向上部として、SiGe 結晶膜基板 2 が用いられている。また、半導体基板の表面を構成しながら導電性部の上面を覆うことにより、導電性領域が自然酸化されることを抑制する機能を有する酸化抑制部として、SiGe 結晶膜 3a, 4a が用いられている。

【0058】

10

20

30

40

50

上記の構成によれば、半導体基板の表面層が自然酸化されにくい酸化抑制部により構成されているため、半導体基板の表面層が自然酸化されることに起因して生じる問題が解消される。また、移動度向上部の影響により格子歪が生じている導電部を電子が移動するため、電子の移動度が向上する。

#### 【0059】

また、酸化抑制部としてのSiGe結晶膜3a, 4aは、導電性部としてのSi結晶膜3b, 4bを流れる電子の移動度を向上させる機能を有している。

#### 【0060】

上記の構成によれば、導電部での電子の移動度がさらに向上する。

さらに、酸化抑制部としてのSiGe結晶膜3a, 4aと移動度向上部としてのSiGe結晶膜基板2とは同じ組成の物質により構成されている。10

#### 【0061】

上記の構成によれば、酸化抑制部にも導電部に格子歪を生じさせる機能が備えられているため、電子の移動度を低下させるおそれがない。

#### 【0062】

また、実施の形態1～4の半導体装置では、Si結晶膜を上下から挟む膜として、SiGe結晶膜を用いたが、SiGe結晶膜の代わりに、SiGeC結晶膜を用いても、実施の形態1～4の半導体装置と同様の効果を得ることができる。

#### 【0063】

また、今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなく特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。20

#### 【0064】

#### 【発明の効果】

本発明の一の局面の半導体装置によれば、半導体基板の表面層が自然酸化されにくい酸化抑制部により構成されているため、半導体基板の表面層が自然酸化されることに起因して生じる問題が解消される。

#### 【0065】

本発明の他の局面の半導体装置によれば、Si結晶膜の表面の自然酸化に起因したSi結晶膜での導電性の低下に起因する問題が解消される。30

#### 【図面の簡単な説明】

【図1】本発明の実施の形態1の半導体装置の断面図である。

【図2】本発明の実施の形態2の半導体装置の断面図である。

【図3】本発明の実施の形態3の半導体装置の断面図である。

【図4】本発明の実施の形態4の半導体装置の断面図である。

【図5】従来の半導体装置の断面図である。

#### 【符号の説明】

1 半導体基板、2 SiGe結晶膜基板、3a SiGe結晶膜、3b Si結晶膜、40

4a SiGe結晶膜、4b Si結晶膜、5 ゲート絶縁膜、6 ゲート電極、7 トランジスタ。

【図1】

【図2】

【図3】

【図4】

【図5】

## フロントページの続き

(72)発明者 相原 一洋

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

F ターム(参考) 4M104 AA01 AA02 CC05 EE16 GG09 GG10 GG14

5F140 AA00 AA01 AA10 AC28 AC32 BA01 BA05 BA17 BB06 BB13

BB18 BD11 BE07 BH05 BH08 BH13 BH27