(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

9 August 2007 (09.08.2007)

PCT

(10) International Publication Number

WO 2007/090055 A1

## (51) International Patent Classification:

*H01L 27/02* (2006.01)      *H01L 31/0352* (2006.01)

*H01L 29/36* (2006.01)

R. [US/US]; c/o MEMC Electronic Materials, Inc., 501 Pearl Drive, P.O. Box 8, St. Peters, Missouri 63376 (US).

## (21) International Application Number:

PCT/US2007/061128

(74) Agents: HEJLEK, Edward, J. et al.; Senniger Powers, #1 Metropolitan Square, 16th Floor, St. Louis, Missouri 63102 (US).

## (22) International Filing Date: 26 January 2007 (26.01.2007)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

60/763,643      31 January 2006 (31.01.2006) US

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LV, LY, MA, MD, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(71) Applicant (for all designated States except US): MEMC ELECTRONIC MATERIALS, INC. [US/US]; 501 Pearl Drive, P.O. Box 8, St. Peters, Missouri 63376 (US).

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM),

[Continued on next page]

## (54) Title: SEMICONDUCTOR WAFER WITH HIGH THERMAL CONDUCTIVITY

(57) Abstract: This invention generally relates to an epitaxial silicon semiconductor wafer with increased thermal conductivity to transfer heat away from a device layer, while also having resistance to common failure mechanisms, such as latch-up failures and radiation event failures. The semiconductor wafer comprises a lightly-doped device layer, a highly-doped protective layer, and a lightly-doped substrate. The invention is also directed to a process for forming such an epitaxial silicon wafer.

WO 2007/090055 A1

European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

— before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments

**Published:**

— with international search report

*For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.*

## SEMICONDUCTOR WAFER WITH HIGH THERMAL CONDUCTIVITY

### FIELD OF THE INVENTION

[0001] The present invention generally relates to a semiconductor wafer and a process for making the same. More particularly, the present invention relates to a semiconductor wafer having improved thermal conductivity characteristics, offering advantages when used as a substrate for a high-speed processor device.

### BACKGROUND OF THE INVENTION

[0002] Within the semiconductor industry, the overall scaling trend has been to increase the silicon power density by increasing transistor density and operating frequency on processor devices. However, the power reductions gained from design and process modifications are not sufficient to offset the higher operating temperatures accompanying the increased power density. In turn, the semiconductor's electrical performance and reliability is significantly degraded at higher operating temperature, reducing the semiconductor's processor speed and lifespan. As such, it is increasingly important to lower the semiconductor junction temperatures across the structure, particularly avoiding local hot spots in areas that run at higher power density.

[0003] Currently, the majority of high performance processor devices are fabricated on a thin (about 2 - 4  $\mu\text{m}$ ), lightly-doped (about  $1 \times 10^{15}$  -  $1 \times 10^{16}$  carriers/cm $^3$ ) epitaxial silicon layer grown over a heavily-doped (about  $10^{19}$  carriers/cm $^3$ ) silicon substrate wafer, wherein boron is a preferred dopant. This type of wafer is generally referred to as a P/P++ epitaxial wafer or P/P+ epitaxial wafer. Epitaxial silicon layers such as these are typically grown by a chemical vapor deposition process wherein a substrate is heated while a gaseous silicon compound is passed over the wafer surface to affect pyrolysis or decomposition.

[0004] The heavily-doped silicon substrate below the device layer is intended to provide protection against many common device failure mechanisms, such as device latch-up failures, failures related to diffusion leakage current, or some radiation event-related failures. For example, latch-up

failure refers to an electron-collection phenomenon resulting in a dead short circuit at a parasitic junction, but which can be prevented using, *inter alia*, strategic doping designs. Therefore, the arrangement of a lightly-doped device layer on a heavily-doped silicon substrate provides desirable latch-up and low diffusion current characteristics.

[0005] One disadvantage to using a heavily-doped silicon substrate is its poor thermal conductivity, as compared to the lightly-doped device layer; the thermal conductivity of lightly-doped silicon has been reported to be about 20% greater than heavily-doped silicon, and possibly even higher. See, e.g., P. Komarov et al., *Transient Thermo-Reflectance Measurements of the Thermal Conductivity and Interface Resistance of Metallized Natural and Isotopically-Pure Silicon*, 34 Microelectronics Journal No. 12, at 1115-1118 (2003). The difference in thermal conductivity is significant because the majority of heat generated in the thin device layer is transferred to the ambient environment by dissipation through the silicon substrate, and lesser thermal conductivity tends to reduce efficiency and reliability.

[0006] To improve heat removal from the device layer, efforts have previously focused on improving the thermal transfer characteristics from the back of the silicon substrate, through the packaging, and to the environment during use. While design of the packaging material and heat sinks have reduced the thermal resistance at this interface to maintain lower die temperatures, such efforts do not address the problem of localized heating at hot spots in the device layer.

[0007] Backside autodoping, i.e., the migration of dopant atoms from the back or sides of the substrate into the device layer, is another problem commonly encountered when a heavily doped substrate is integrated with a lightly doped device layer. One conventional approach to limit this effect is to form a backside oxide seal on the highly doped substrate. However, the oxide seal can not be integrated into the epitaxial silicon structure in the case of double-side polished wafers.

[0008] Heavily doped substrates having a lightly doped epitaxial layer also present challenges when used in CMOS Image Sensor applications wherein backside illumination technology is desirable. Currently, commercially available

image sensors are illuminated from the device side. For typical device-side illumination applications, a CMOS Image Sensor silicon wafer comprises a substrate that is doped to a P+ or P++ concentration and an epitaxial layer doped to a P concentration. The known use of device-side illumination cannot meet the scaling trends and goals in such applications, which include reducing pixel size and increasing circuit functionality via advanced metal interconnections. Backside illumination is believed to realize these goals, while also improving the device's fill factor and quantum efficiency. These terms are used as different ways to measure the net amount of light energy that is actually able to illuminate the image sensors. Fill factor, which refers to the percentage or fraction of the image sensor that is capable of being exposed to light, is reduced in traditional device-side illumination devices by increasingly complex metallization layers and films, as well as advanced device topography. As the fill factor decreases, so does the quantum efficiency, which measures how efficiency projected light is able to generate active electron carriers.

[0009] These desired improvements in image sensor performance are possible using backside illumination technology because device-side features such as device patterns, metallization layers, interconnects, and films do not impede the illumination process. The result is nearly 100% fill factor, improved flexibility in antireflection coatings, and increased quantum efficiency. Moreover, backside illumination allows for integration of advanced device architecture and interconnections. However, backside illumination must be performed within a few microns of the device side photodiode to efficiently convert visible light to electrical signals. This requires consistent and uniform material removal from the backside of the original, as-formed silicon structure to create a smooth backside surface, which requires thinning the silicon structure from several hundred microns to just a few microns, such as less than about 15  $\mu\text{m}$ . Furthermore, the backside surface must be capable of being passivated against recombination of photon-generated carriers at the surface, while also directing these photon-generated carriers to a collecting photodiode with an electric field within the Image Sensor device. Such features are not readily ascertained using conventional mechanical or chemical means to thin the silicon structure. Mechanical means of thinning may not be feasible with such small dimensions,

while controlling chemical removal rates is difficult within the tolerances of the image sensor's physical features.

## SUMMARY OF THE INVENTION

[0010] Among the various aspects of the present invention is a silicon semiconductor wafer with favorable heat transfer characteristics while providing resistance to common semiconductor failure mechanisms.

[0011] Briefly, therefore, the present invention is directed to a semiconductor wafer comprising a silicon device layer, a substrate, and a silicon protective layer disposed between the device layer and the substrate. The substrate has a central axis, a front surface, and a back surface that are generally perpendicular to the central axis, a circumferential edge, and a radius extending from the central axis to the circumferential edge. The protective layer has a thickness of at least about 0.5  $\mu\text{m}$  and is doped, the concentration of the dopant in the protective layer being between about  $6.0 \times 10^{17}$  carriers/cm<sup>3</sup> and about  $1.0 \times 10^{20}$  carriers/cm<sup>3</sup>. The substrate and the device layer are also doped with the concentration of dopant in the substrate and device layer being less than about  $1 \times 10^{17}$  carriers/cm<sup>3</sup>.

[0012] The present invention is further directed to a process for the preparation of this semiconductor wafer.

[0013] Other objects and features will be in part apparent and in part pointed out hereinafter.

## BRIEF DESCRIPTION OF THE DRAWINGS

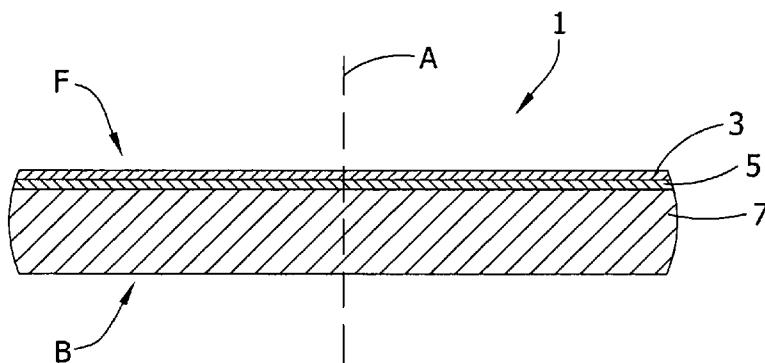

[0014] Figure 1 is a schematic cross-section of a semiconductor wafer of the invention.

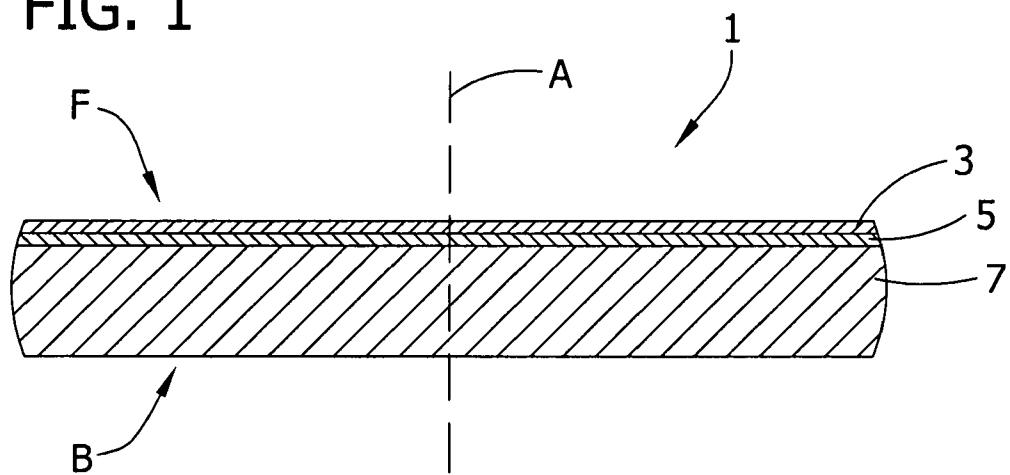

[0015] Figure 2 is a schematic top-down view of a semiconductor wafer of the invention, wherein the axis in Figure 2 is coincident with the axis in Figure 1.

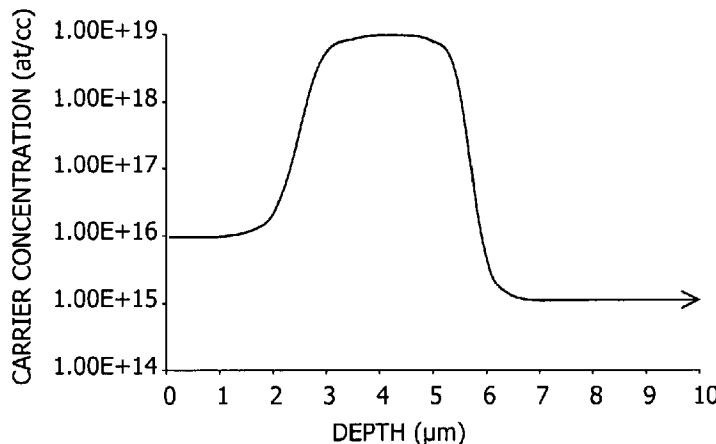

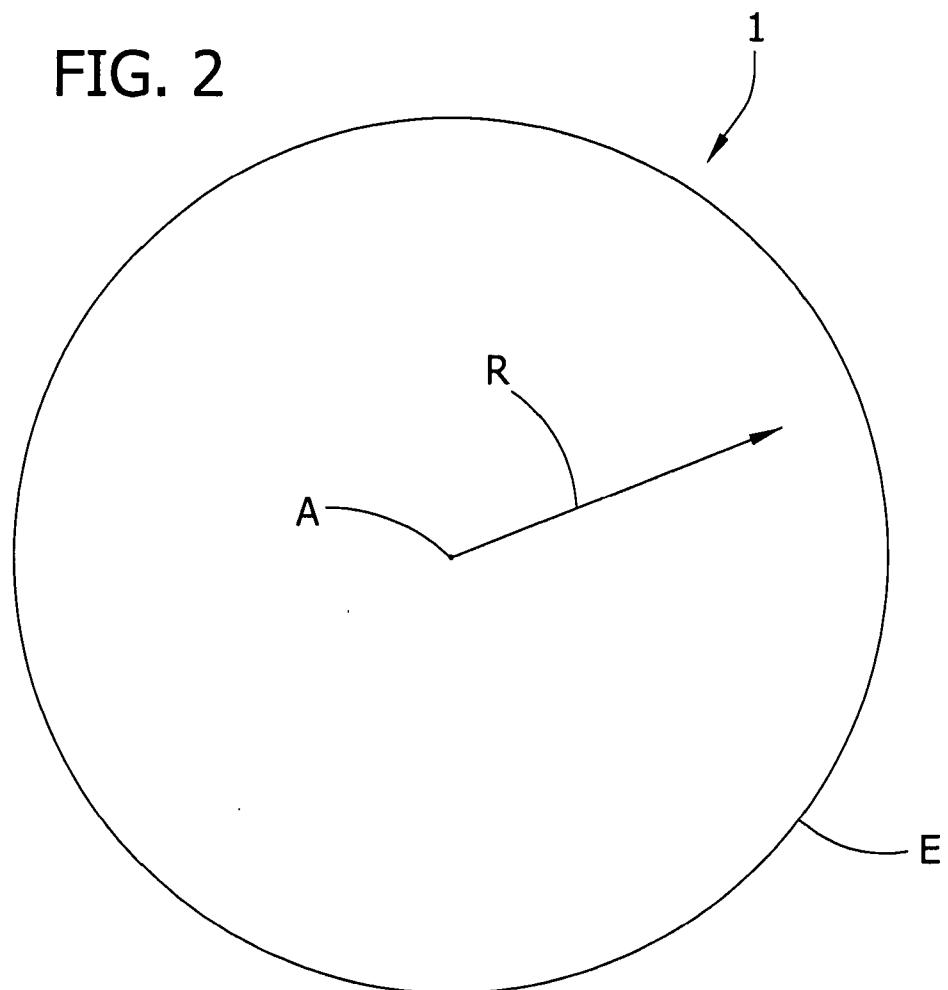

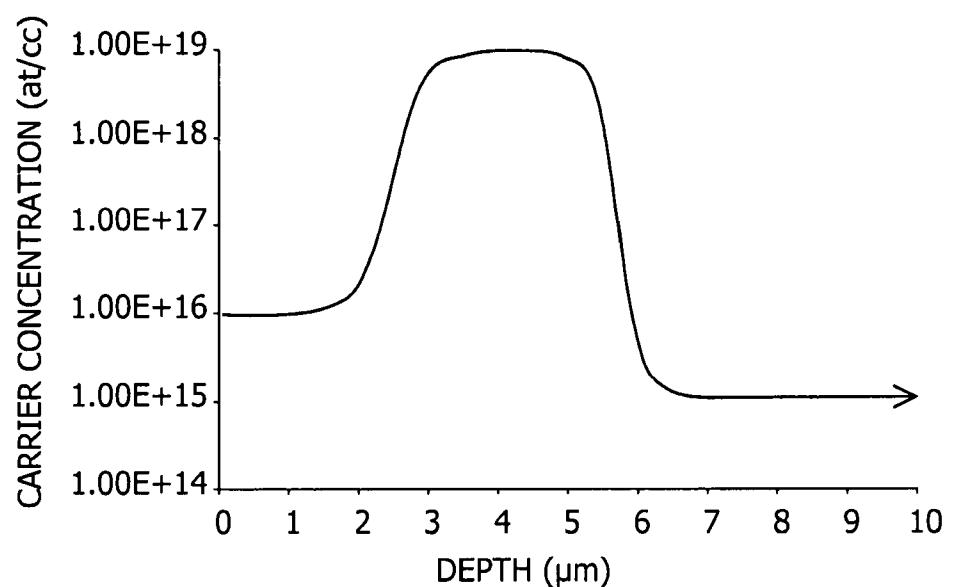

[0016] Figure 3 is a graphical representation of the carrier concentration profile for an semiconductor wafer having a highly doped protective layer and a lightly doped substrate.

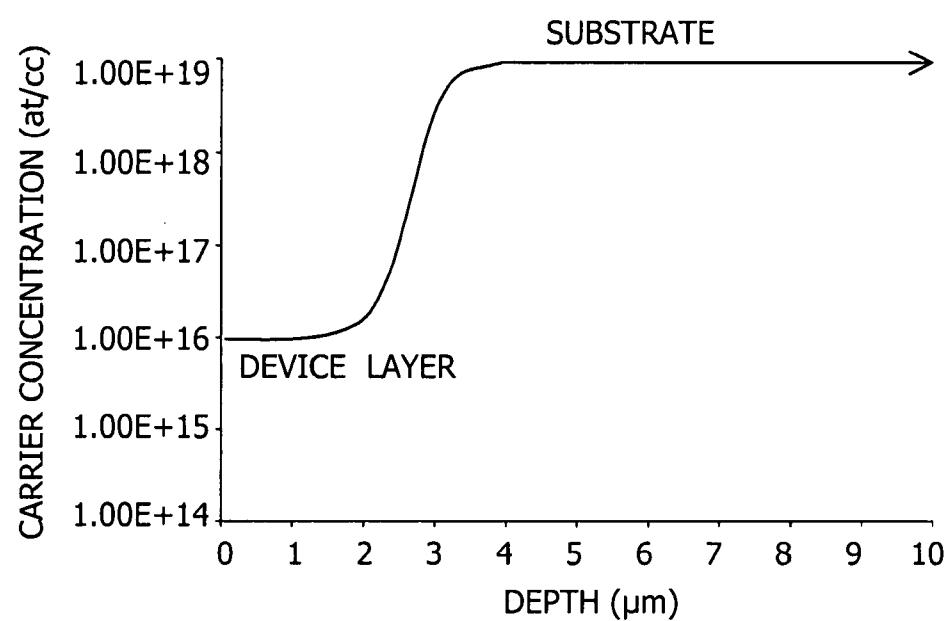

[0017] Figure 4 is a graphical representation of the carrier concentration profile for a semiconductor wafer having a lightly doped device layer and a highly doped substrate detailed in Example 1.

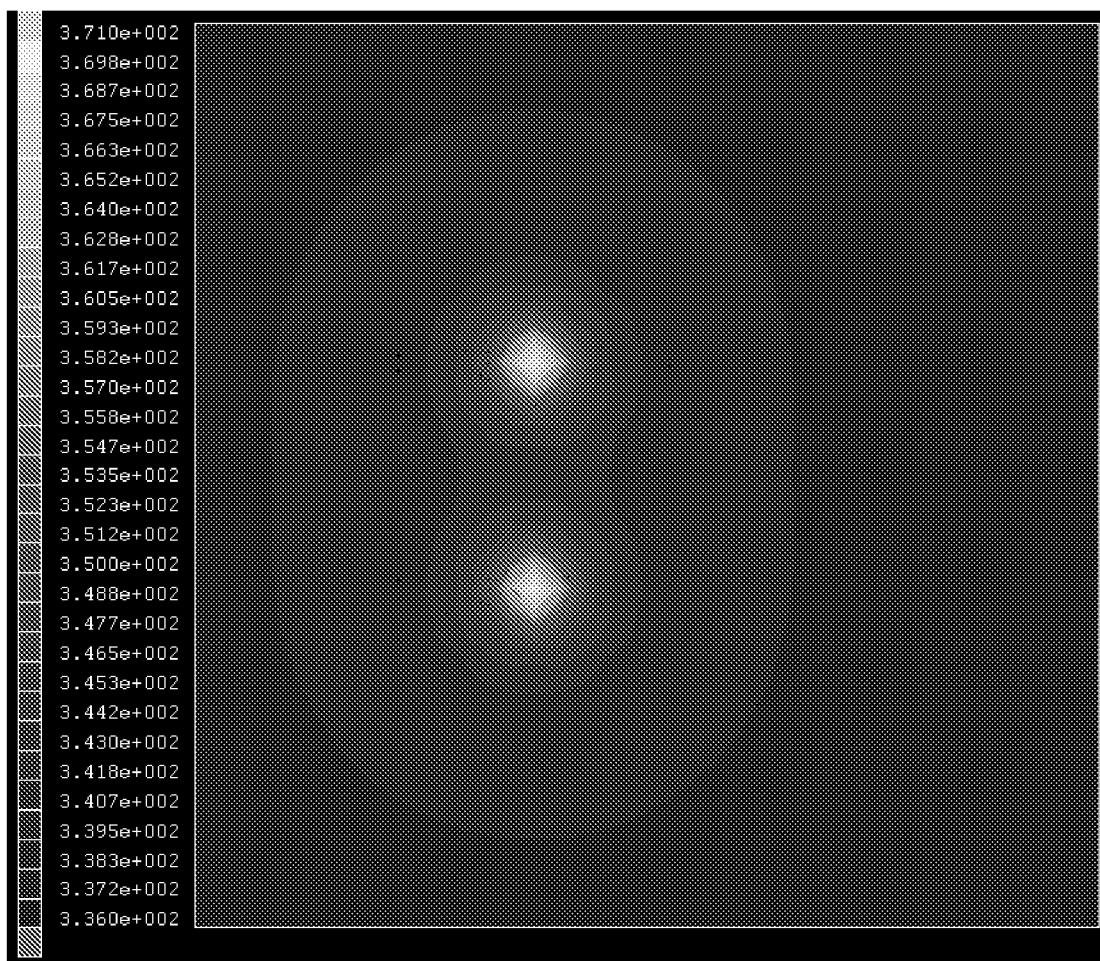

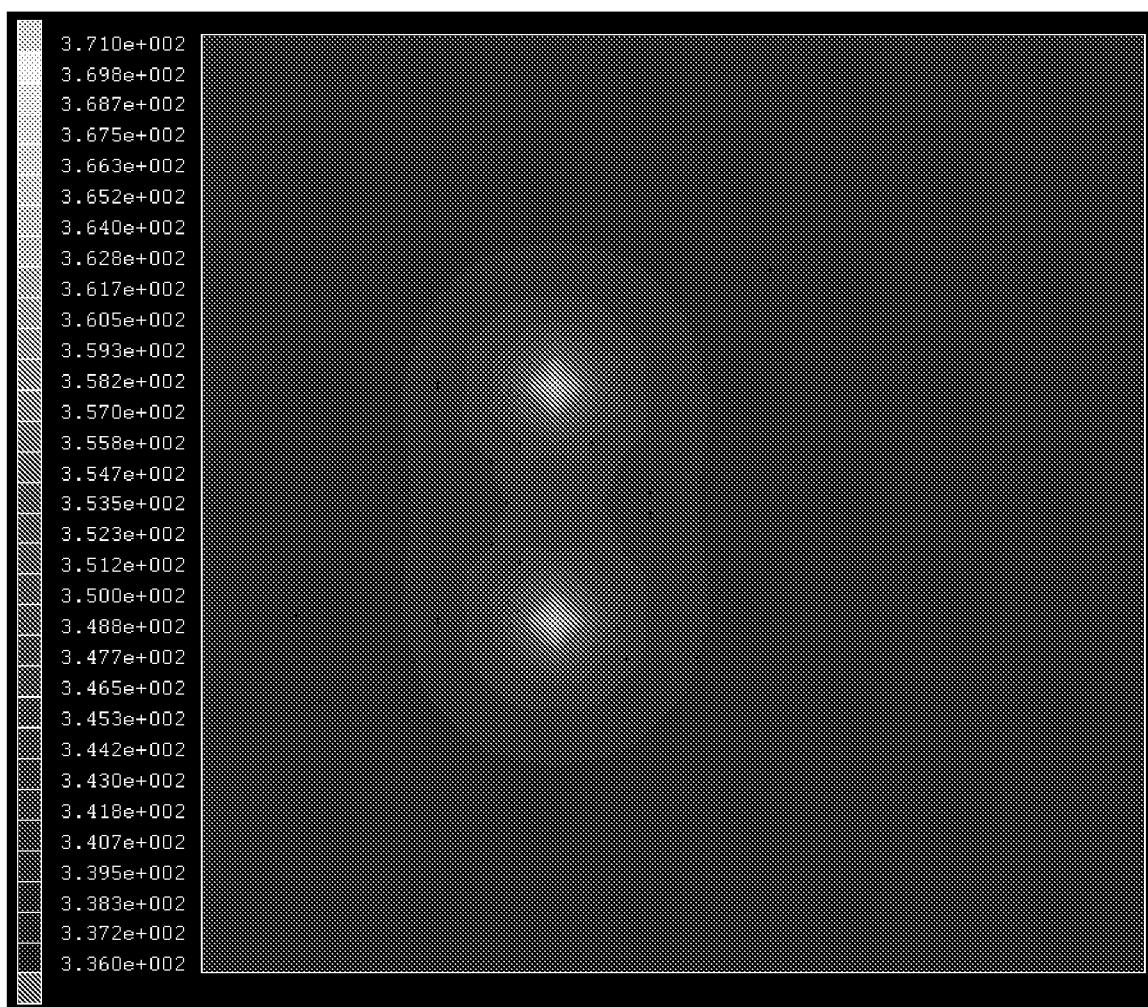

[0018] Figure 5 is a thermal diagram for heat dissipation under localized heating for a 250  $\mu\text{m}$  semiconductor wafer having a highly doped substrate.

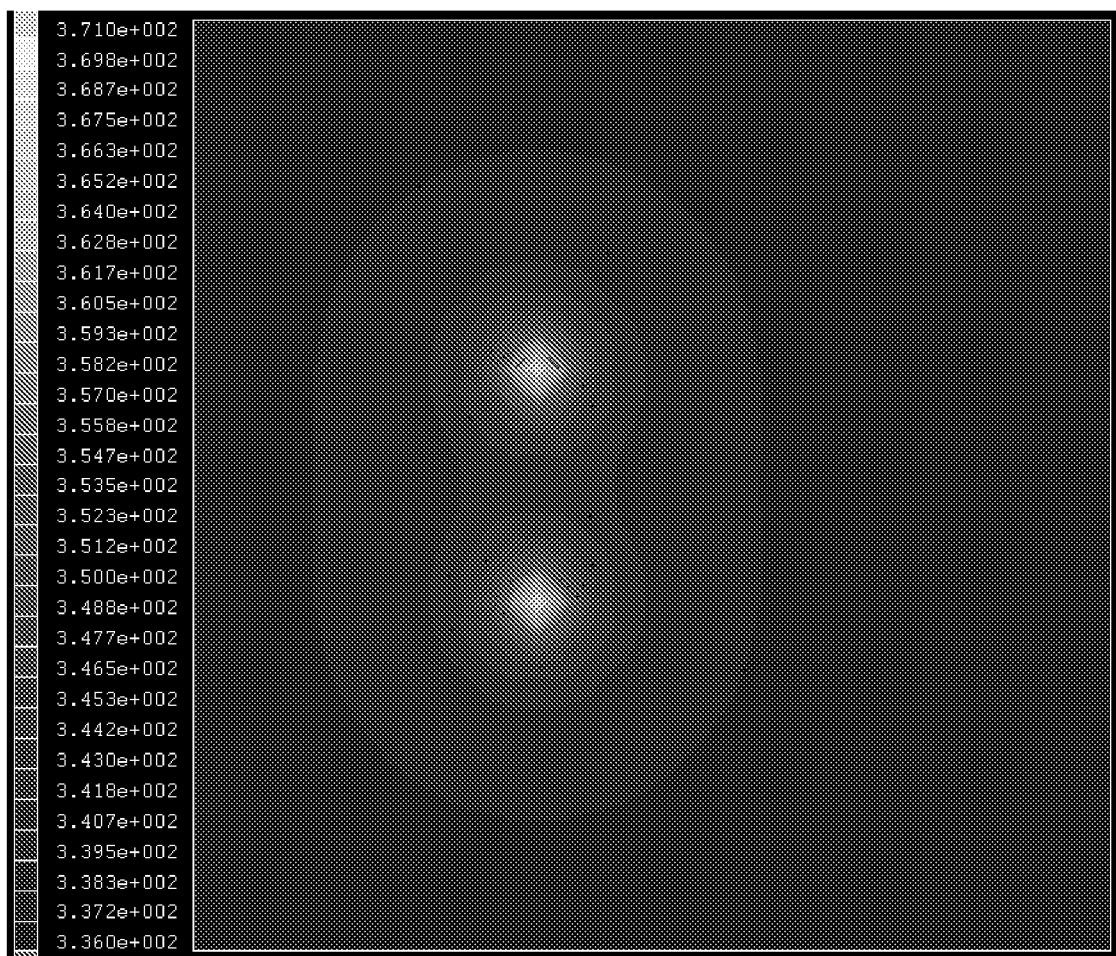

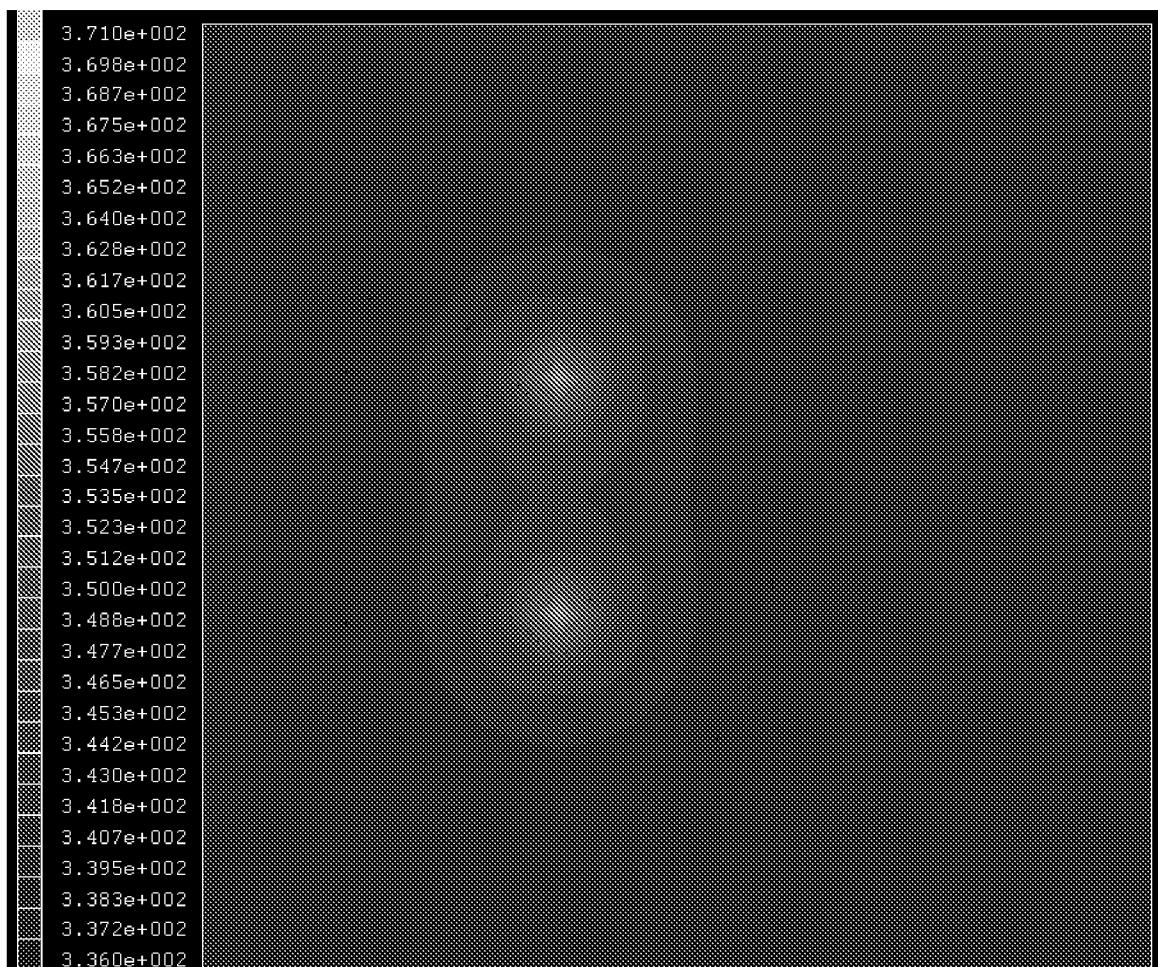

[0019] Figure 6 is a thermal diagram for heat dissipation under localized heating for a 250  $\mu\text{m}$  semiconductor wafer having a highly doped protective layer and a lightly doped substrate.

[0020] Figure 7 is a thermal diagram for heat dissipation under localized heating for a 500  $\mu\text{m}$  semiconductor wafer having a highly doped substrate.

[0021] Figure 8 is a thermal diagram for heat dissipation under localized heating for a 500  $\mu\text{m}$  semiconductor wafer having a highly doped protective layer and a lightly doped substrate.

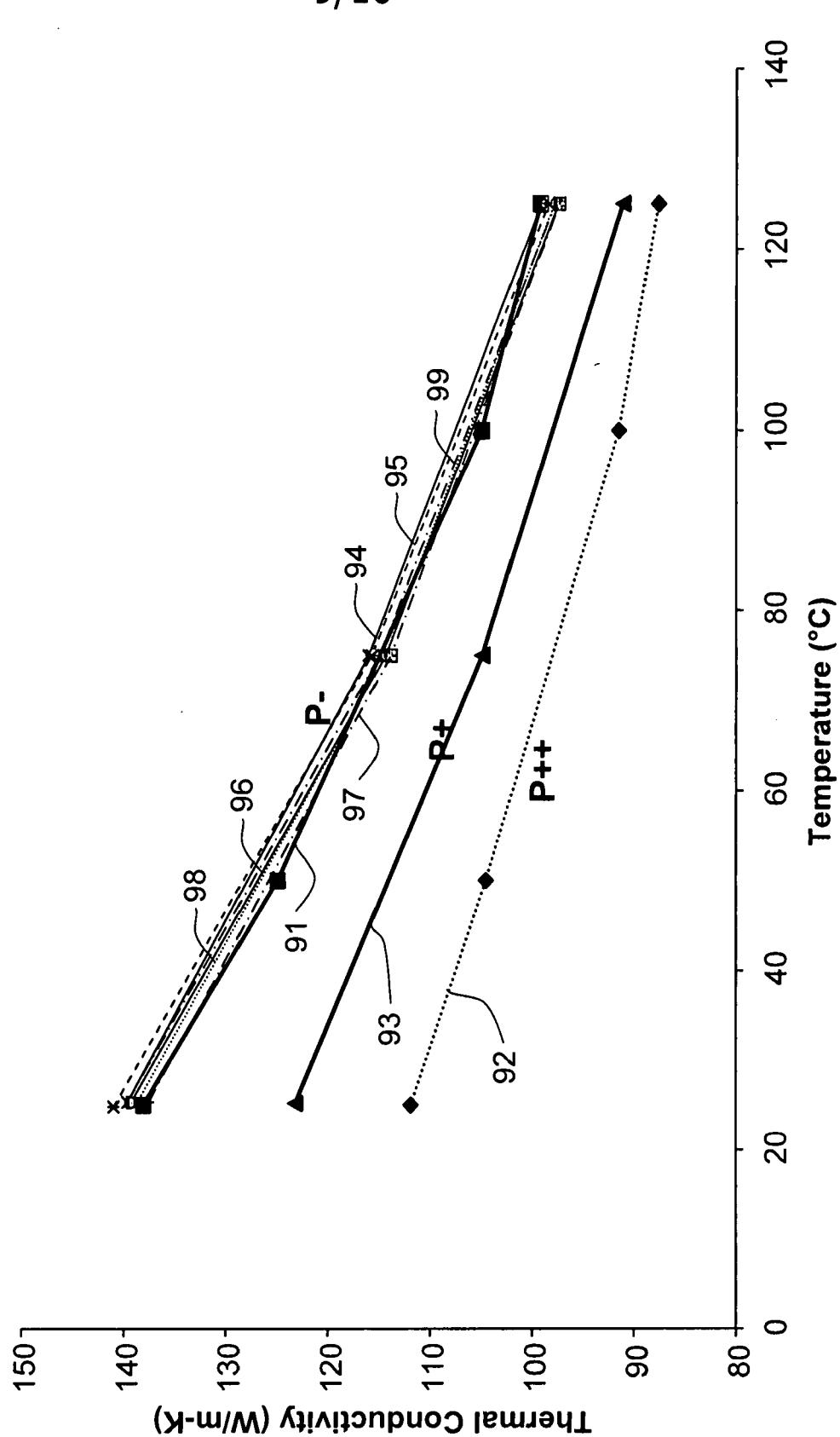

[0022] Figure 9 is a graph showing the thermal conductivity for multiple semiconductor structures as a function of temperature detailed in Example 2.

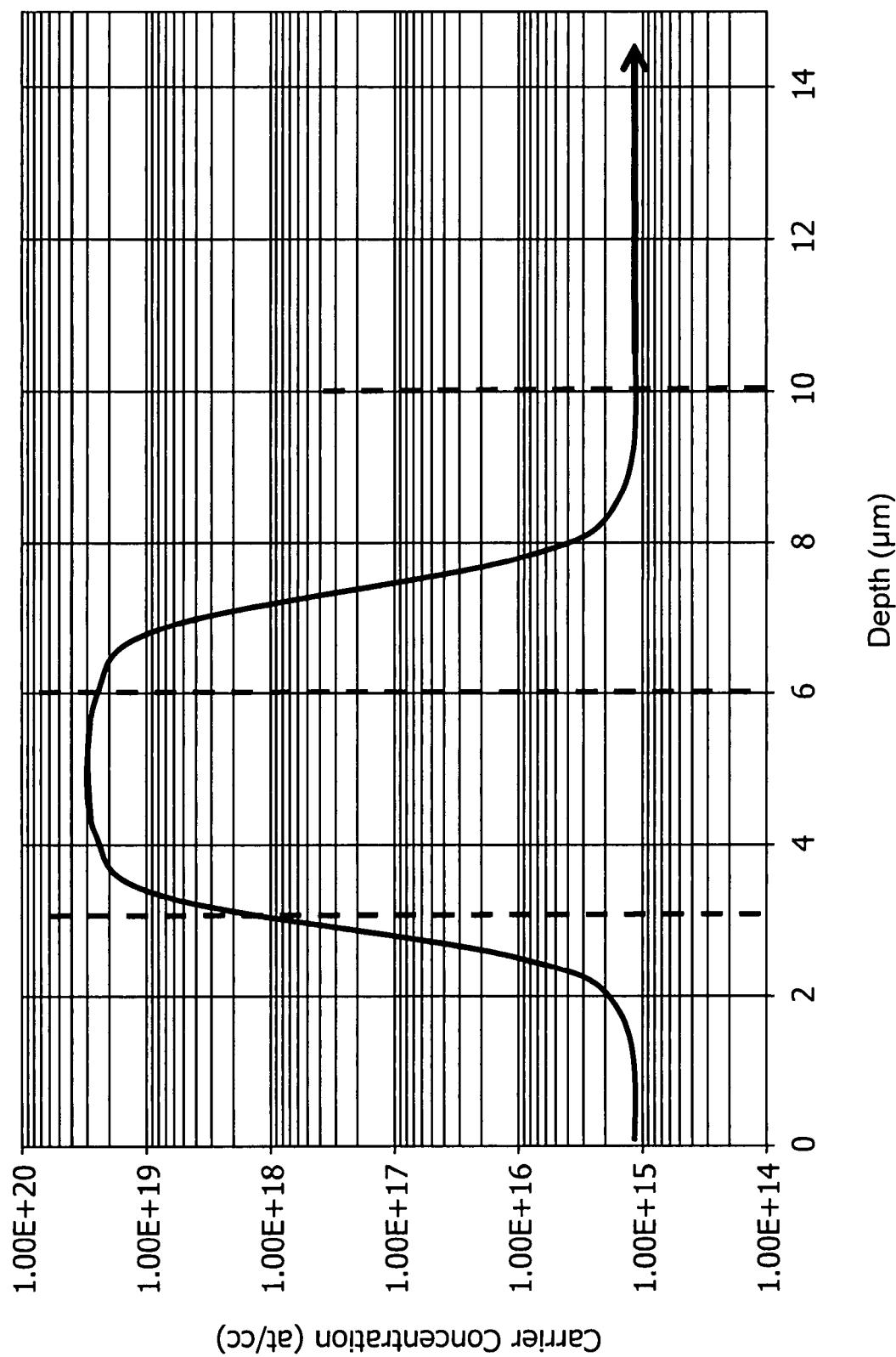

[0023] Figure 10 is a graphical representation of the carrier concentration profile for a semiconductor wafer for an image sensor application.

[0024] Corresponding reference characters indicate corresponding parts throughout the drawings.

## DETAILED DESCRIPTION OF THE INVENTION

[0025] Referring now to Figure 1, among the various aspects of the present invention is a semiconductor wafer 1 with improved thermal conductivity. Semiconductor wafer 1 has a front surface F, a back surface B, and an imaginary central axis A, with the terms "front" and "back" being used in this context merely to distinguish the two major, generally planar surfaces of the wafer. Semiconductor wafer 1 also comprises silicon device layer 3, silicon protective layer 5, and substrate 7.

[0026] To inhibit various commonly known device failure mechanisms, the thermal conductivity of substrate 7 is preferably at least 5% greater than the

thermal conductivity of protective layer 5 (at temperatures not in excess of 125 °C). More preferably, the thermal conductivity of substrate 7 is at least 10% greater than the thermal conductivity of protective layer 5 (at temperatures not in excess of 125 °C). For example, in some embodiments, the thermal conductivity of substrate 7 will be at least 15% greater, at least 20% greater, or even at least 25% greater than the thermal conductivity of protective layer 5 at temperatures not in excess of 125 °C.

[0027] Referring now to Figure 2, semiconductor wafer 1 has an imaginary radius, R, extending from axis A, to edge E of semiconductor wafer 1. Because the semiconductor wafers of the present invention are used as a starting material in device fabrication processes, it is generally preferred that device layer 3 and silicon protective layer 5 extend substantially across the diameter of the wafer. That is, it is generally preferred that device layer 3 and silicon protective layer 5 incorporate and are symmetrically disposed about axis A and extend at least 90% of the length of radius R from the axis to semiconductor wafer edge E. More preferably, device layer 3 and silicon protective layer 5 incorporate and are symmetrically disposed about axis A and extend at least 99% of the length of radius R from the axis to semiconductor wafer edge E.

[0028] Referring now to Figure 3, a carrier concentration profile for an exemplary semiconductor wafer of the present invention is illustrated. As depicted, the device layer of the semiconductor wafer (the region of the wafer from a depth of 0 to about 2  $\mu$ m) has a dopant concentration of about  $1 \times 10^{16}$  atoms/cm<sup>3</sup>, the silicon protective layer (the region of the wafer from a depth of about 3 to about 5  $\mu$ m) has a dopant concentration of  $1 \times 10^{19}$  atoms/cm<sup>3</sup>, and the substrate (the region of the wafer at depths greater than about 6  $\mu$ m) has a dopant concentration of about  $1 \times 10^{15}$  atoms/cm<sup>3</sup>. In accord with the invention, either P-type or N-type dopants may be employed to dope each of the device layer 32, the protective layer 33, and the substrate 34, when semiconductor materials are selected for the substrate.

#### *I. The Substrate*

[0029] In general, the substrate comprises a material on which additional layers may be formed and which typically has a thermal conductivity of at least about 120 W/m·K. The substrate may comprise a single stratum of material, or it may comprise multiple strata. Typically, however, the substrate is sliced from a single crystal silicon ingot grown according to one of the known techniques, such as the Czochralski ("Cz") or float zone methods. Accordingly, for the purposes of illustration, reference to a single crystal silicon wafer will be utilized hererin. Therefore, in one application, the starting material for the wafer of the present invention is a silicon substrate that has been sliced from a single crystal ingot grown in accordance with Cz crystal growing methods, typically having a nominal diameter of 150 mm, 200 mm, 300 mm, or more. The substrate may be polished or, alternatively, lapped and etched but not polished. Such methods, as well as standard silicon slicing techniques, are disclosed in, e.g., FUMIO SHIMURA, SEMICONDUCTOR SILICON CRYSTAL TECHNOLOGY (1989) and SILICON CHEMICAL ETCHING (Josef Grabmaier ed., 1982). Preferably, the substrates are polished and cleaned by standard methods known to those skilled in the art. See, e.g., HANDBOOK OF SEMICONDUCTOR SILICON TECHNOLOGY (William C. O'Mara et al. eds., 1990).

[0030] In general, the single crystal silicon substrate is lightly doped such that it is P- or N- silicon, as those designations are conventionally used in the art and described herein. That is, for P-type doping applications, the silicon substrate generally has less than about  $1 \times 10^{16}$  carriers/cm<sup>3</sup>, such as less than about  $5 \times 10^{15}$  carriers/cm<sup>3</sup>. Furthermore, the substrate typically contains at least about  $5 \times 10^{14}$  carriers/cm<sup>3</sup> to minimize undesirable phenomena observed at lower doping levels, such as oxygen-related thermal donor generation. For example, the P-doped single crystal silicon substrate typically has between about  $5 \times 10^{14}$  carriers/cm<sup>3</sup> and about  $1 \times 10^{16}$  carriers/cm<sup>3</sup>. For N-type doping applications, the silicon substrate generally has less than about  $5 \times 10^{15}$  carriers/cm<sup>3</sup>, such as less than about  $1 \times 10^{15}$  carriers/cm<sup>3</sup>.

[0031] In another aspect, the silicon substrate has thermal conductivity of at least about 5% greater than the thermal conductivity of P++ or N++ silicon, as those terms are conventionally used in the art and described herein. In

general, doped silicon's thermal conductivity is inversely related to the doping level and the atmospheric temperature; i.e., doped silicon's thermal conductivity decreases as the concentration of dopant and atmospheric temperature increase. Data collected to date suggests that at room temperature, P++ or N++ silicon exhibits a thermal conductivity of less than about 114 W/m·K. Therefore, the thermal conductivity of the silicon substrate is greater than about 120 W/m·K. More typically, the silicon substrate's thermal conductivity is greater than about 130 W/m·K, such as greater than about 135 W/m·K. In some applications, the thermal conductivity will be greater than about 140 W/m·K, or even greater than about 150 W/m·K.

[0032] The single crystal silicon substrate contains at least one dopant to give the substrate various desirable properties. For example, the substrate may comprise P-type dopants (i.e., elements from Group 3 of the Periodic Table, e.g., boron, aluminum, gallium and indium) or N-type dopants (i.e., elements from Group 5 of the Periodic Table, e.g., phosphorus, arsenic, antimony). When P-type doping is desired, the dopant is preferably boron. When N-type doping is desired, the dopant is preferably phosphorus.

## *II. Protective Layer*

[0033] The protective layer typically comprises highly-doped silicon to provide protection against common device failure mechanisms, such as latch-up and low diffusion current failures. Depending on the application, any one of the appropriate P-type or N-type dopants noted above may be used to form the protective layer. Generally, the protective layer typically comprises greater than about  $1 \times 10^{18}$  carriers/cm<sup>3</sup>. For example, for P-type doping applications, the highly-doped silicon protective layer comprises between about  $1 \times 10^{18}$  carriers/cm<sup>3</sup> and about  $1 \times 10^{20}$  carriers/cm<sup>3</sup>. Common ranges include between about  $8.5 \times 10^{18}$  carriers/cm<sup>3</sup> and about  $2.0 \times 10^{19}$  carriers/cm<sup>3</sup> when the dopant concentration is characterized as P++, and between about  $3.2 \times 10^{18}$  carriers/cm<sup>3</sup> and about  $8.5 \times 10^{18}$  carriers/cm<sup>3</sup> when the dopant concentration is characterized as P+. In one preferred embodiment, the protective layer's dopant concentration is between about  $1.0 \times 10^{19}$  carriers/cm<sup>3</sup> and about  $1.25 \times 10^{19}$

carriers/cm<sup>3</sup>. For N-type doping applications, the highly-doped silicon protective layer comprises between about  $6.0 \times 10^{17}$  carriers/cm<sup>3</sup> and about  $5 \times 10^{19}$  carriers/cm<sup>3</sup>. Common ranges include between about  $1.2 \times 10^{19}$  carriers/cm<sup>3</sup> and about  $3.5 \times 10^{19}$  carriers/cm<sup>3</sup> when the dopant concentration is characterized as N++, and between about  $6.0 \times 10^{17}$  carriers/cm<sup>3</sup> and about  $4.5 \times 10^{18}$  carriers/cm<sup>3</sup> when the dopant concentration is characterized as N+.

[0034] In another aspect, the protective layer is characterized by a thermal conductivity lower than the substrate's thermal conductivity. That is, the protective layer is characterized by thermal conductivity of less than about 114 W/m·K at room temperature. For example, the protective layer is characterized by thermal conductivity of less than about 110 W/m·K, or even less than about 100 W/m·K at room temperature.

[0035] In light of the substrate's thermal conductivity noted above, the substrate has a thermal conductivity of greater than about 120 W/m·K protective layer and the protective layer has a thermal conductivity of less than about 114 W/m·K. For example, in one application, the substrate's thermal conductivity is greater than 130 W/m·K and the protective layer's thermal conductivity is less than about 114 W/m·K. In another application, the substrate's thermal conductivity is greater than 135 W/m·K and the protective layer's thermal conductivity is less than about 110 W/m·K.

[0036] The resistivity of the protective layer is an alternative way by which the carrier concentration can be estimated. The resistivity of the protective layer is generally between about 2.5 mΩ·cm and about 25 mΩ·cm, with common ranges being between about 5 mΩ·cm and about 10 mΩ·cm and between about 10 mΩ·cm and about 20 mΩ·cm. In one preferred embodiment, the protective layer's resistivity is about 8 mΩ·cm.

[0037] In general, the protective layer is thick enough to provide the desired protection, yet as thin as possible to promote heat transfer from the device layer to the high thermal conductivity substrate. Typically, the protective layer is at least about 1 μm thick, such as between about 1 μm and about 10 μm thick. More typically, the protective layer will be between about 1 μm and about

5  $\mu\text{m}$  thick; and for some applications, the protective layer will be between about 1  $\mu\text{m}$  and about 3  $\mu\text{m}$  thick.

[0038] Any known technique for forming a heavily-doped silicon protective layer on a silicon substrate may be used to form the protective layer. For example, the protective layer may be formed by using epitaxial deposition, ion implantation, and gas phase doping plus high temperature diffusion. Each of these techniques are well-known and are detailed further in literature references readily available to one skilled in the art, such as STANLEY WOLF & R.N. TAUBER, SILICON PROCESSING FOR THE VLSI ERA - PROCESS TECHNOLOGY (1st ed. 1986) and STEPHEN A. CAMPBELL, THE SCIENCE AND ENGINEERING OF MICROELECTRONIC FABRICATION (2nd ed. 2001).

[0039] An epitaxial layer may be deposited or grown on a surface of the above-described substrate by means generally known in the art, such as the epitaxial growth process described in U.S. Patent No. 5,789,309. Typically, growth of the epitaxial layer is achieved by chemical vapor deposition, because this is one of the most flexible and cost effective methods for growing epitaxial layers on semiconductor material. One advantage to forming the protective layer by epitaxial deposition is that existing epitaxial growth reactors can be used in conjunction with a direct dopant feed during epitaxial growth. For example, when doping the silicon with boron, a high concentration diborane source gas can be mixed with the carrier gas used to dope the epitaxially grown protective layer.

[0040] In another embodiment, ion implantation techniques are used to force dopant atoms into the single crystal silicon substrate. In yet another embodiment, gas phase doping techniques are used to force the dopant atoms into the single crystal silicon substrate. When either an ion implantation or a gas phase doping technique is used, the technique is carried out at an elevated temperature or is followed by a high temperature anneal to diffuse the dopant atoms into the substrate to form the protective layer.

[0041] Regardless of the specific technique used to form the highly-doped silicon protective layer, the dopant profile created by the transition between the highly-doped protective layer to the lightly-doped substrate also

creates an electric field that directs excess charge carriers away from this interface into the substrate. By creating an electric field that moves charge carriers away from the protective layer, and therefore away from the device layer, the protective layer also effectively reduces the impact of radiation-induced events or failures.

### *III. Device Layer*

[0042] In general, the device layer is sufficiently thick enough to comprise at least one level of electrical devices. The device layer may comprise more than one level of electrical devices; thus, the thickness will vary depending on the number of levels required for a particular application. The device layer is generally less than about 25  $\mu\text{m}$  thick. For example, the device layer will typically be between about 1  $\mu\text{m}$  and about 25  $\mu\text{m}$  thick. For some applications, the device layer will be between about 1  $\mu\text{m}$  and about 20  $\mu\text{m}$  thick. In other applications, the device layer will be between about 1  $\mu\text{m}$  and about 10  $\mu\text{m}$  thick. In yet other applications, the device layer will be between about 1  $\mu\text{m}$  and about 5  $\mu\text{m}$  thick, such as, e.g., in high speed microprocessor device. Alternatively, for some applications such as, e.g., power devices, the device layer will be between about 5  $\mu\text{m}$  and about 20  $\mu\text{m}$ .

[0043] To create the device layer, the semiconductor wafer may undergo any suitable epitaxial deposition technique, as described above. The growth is carried out for a time sufficient to form a device layer of desired thickness in an epitaxial growth reactor. The device layer may be doped after the epitaxial layer is grown or in conjunction with its growth. A direct dopant feed may be employed when the device layer is doped during growth; e.g., a diborane source gas can be used when doping the silicon with boron. The dopant level is in accord with conventional silicon device layers, such that it is typically referred to as being P, P-, N, or N-. That is, the device layer typically comprises between about  $7.5 \times 10^{14}$  carriers/cm<sup>3</sup> and about  $2.5 \times 10^{16}$  carriers/cm<sup>3</sup>. For example, the device layer typically comprises between about  $1 \times 10^{15}$  carriers/cm<sup>3</sup> and about  $1 \times 10^{16}$  carriers/cm<sup>3</sup>. Depending on the application, any one of the appropriate P-type (e.g., boron) or N-type dopants (e.g., phosphorus) noted

above may be used. Typical applications for a device layer doped with P-type dopants include, e.g., high speed microprocessor devices such as, e.g., memory and logic applications. Typical applications for a device layer doped with N-type dopants include, e.g., power devices.

#### *IV. Resulting Wafer Characteristics and Applications*

##### *A. Backside Autodoping Prevention*

[0044] In one embodiment, the present invention is utilized to form a P/P+/P- semiconductor structure; i.e., the invention can be used to form a lightly doped P- substrate with a highly doped P+ protective layer and an intermediately doped P device layer. Such a semiconductor structure may be used in applications where backside autodoping is to be avoided, such as, e.g., heavily doped substrates with a lightly doped device layer where an oxide seal is undesirable, as with structures with a double sided polish. By forming a P/P+/P- semiconductor structure according to the present invention, the functional equivalent of the P to P+ transition from the device layer to the protective layer is realized, with the added benefit of avoiding the migration of dopant atoms from the backside of the structure to the device layer because of the substrate's lower doping level. In this application, the substrate has a dopant level below about  $1 \times 10^{16}$  carriers/cm<sup>3</sup>, the protective P+ layer has a dopant level of between about  $3.2 \times 10^{18}$  carriers/cm<sup>3</sup> and about  $8.5 \times 10^{18}$  carriers/cm<sup>3</sup>, and the device layer has a dopant level of between about  $1 \times 10^{14}$  carriers/cm<sup>3</sup> and about  $4 \times 10^{16}$  carriers/cm<sup>3</sup>. The protective layer may also be a P++ layer having between about  $8.5 \times 10^{18}$  carriers/cm<sup>3</sup> and about  $2.0 \times 10^{19}$  carriers/cm<sup>3</sup>. Furthermore, the protective P+ layer is typically between about 1  $\mu\text{m}$  and about 10  $\mu\text{m}$  thick, while the device layer is typically between about 2  $\mu\text{m}$  and about 5  $\mu\text{m}$  thick.

##### *B. Backside Illumination Applications*

[0045] Additionally, a P/P++/P- semiconductor structure formed according to the present invention is useful in the production of thin silicon structures for use in backside illumination applications, such as, e.g., improved CMOS Image Sensor devices. Figure 16 shows a typical carrier concentration

profile for a typical P/P++/P- semiconductor structure in this application. After a P/P++/P- semiconductor structure is formed, the back surface of the P- substrate is exposed to an alkaline etchant for a time period sufficient to remove substantially all of the substrate material and yield a uniformly thinned P/P++ silicon structure with a highly uniform thickness. That is, in this application of the present invention, the highly doped P++ (or even P+++) protective layer acts as an etch stop for alkaline etchants. Typical etchants comprise compounds such as, e.g., tetramethylammonium hydroxide (TMAH), potassium hydroxide (KOH), and sodium hydroxide (NaOH), in appropriate concentrations. In one preferred application, TMAH is used in the alkaline etchant, with about 25 wt% being one preferred concentration of TMAH. The highly doped protective layer acts as an etch stop using alkaline etchants because the P- substrate is etched at an etching rate of about 10x to about 20x faster than the P++ protective layer. For example, Figure 10 graphically shows how the alkaline etchant may be used to remove material to at least the dashed vertical line shown at about 10  $\mu\text{m}$ , and possibly to remove material to the dashed vertical line shown at about 6  $\mu\text{m}$ . The etching performed for this application may optionally occur in an electrochemical cell, which would increase the etching rate and facilitate an optional electrochemical passivation step after etching.

[0046] Optionally, mechanical means, e.g., grinding or polishing, are employed to remove a substantial portion of the back surface of the P- substrate before exposing the remaining back surface of the P- substrate to the alkaline chemical etchant. In this case, mechanical means are employed to remove more than about 75% of the P- substrate's thickness, such as more than about 80%, 90%, or even more than about 95% of the substrate's thickness before employing the alkaline etchant. For example, referring again to Figure 10, mechanical means may be used to remove material to at least the dashed vertical line shown at about 10  $\mu\text{m}$ , and the alkaline etchant may be subsequently used to remove additional material to the dashed vertical line shown at about 6  $\mu\text{m}$ . Further, the P++ surface exposed by the substrate's removal is optionally exposed to an acidic etchant to further thin the P/P++ silicon structure and further smooth the P++ surface. In one application, e.g., the

acidic etchant comprises a solution of hydrofluoric, nitric, and acetic acids (HNA). Referring again to Figure 10, the acidic etchant may be used to remove material from the dashed vertical line shown at about 6  $\mu\text{m}$  to the dashed vertical line shown at about 3  $\mu\text{m}$ .

[0047] In this application, the substrate has a dopant level below about  $1 \times 10^{16}$  carriers/cm<sup>3</sup>, the protective layer has a dopant level of greater than about  $1.0 \times 10^{19}$  carriers/cm<sup>3</sup>, such as between about  $1.0 \times 10^{19}$  carriers/cm<sup>3</sup> and about  $1.0 \times 10^{20}$  carriers/cm<sup>3</sup>. For example, the protective layer may have between about  $5.0 \times 10^{19}$  carriers/cm<sup>3</sup> and about  $1.0 \times 10^{20}$  carriers/cm<sup>3</sup>. Silicon doped with such concentrations are commonly referred to as highly doped P++ or even P+++ silicon layers. Furthermore, the thickness of the protective layer is limited in this application, with higher doping concentrations corresponding to thinner protective layers. For example, the protective layer acting as the etch stop is typically less than about 5  $\mu\text{m}$  thick, such as less than 2  $\mu\text{m}$ , less than about 1  $\mu\text{m}$  thick, or even less than about 0.5  $\mu\text{m}$  thick. In one application, the protective layer further comprises Ge to act as a crystal lattice strain reliever, which permits the highly doped protective layer to have greater thicknesses than reported above. Finally, the device layer is typically between about 2  $\mu\text{m}$  and about 15  $\mu\text{m}$  thick, such as between about 2  $\mu\text{m}$  and about 10  $\mu\text{m}$  thick. In one application, the device layer is between about 2  $\mu\text{m}$  and about 5  $\mu\text{m}$  thick.

[0048] The resulting P/P++ silicon structure's backside P++ surface is smooth, which minimizes light scattering during backside illumination. Also, the doping gradient formed by the transition from device layer to the protective layer creates an electric field that promotes electron migration away from the backside illuminated surface and toward the device layer, which is advantageous in image sensor devices as quantum efficiency is increased at photodiode junctions.

[0049] Having described the invention in detail, it will be apparent that modifications and variations are possible without departing from the scope of the invention defined in the appended claims.

## EXAMPLES

[0050] The following non-limiting examples are provided to further illustrate the present invention.

### EXAMPLE 1

[0051] Two types of semiconductor wafers were prepared, the first type having a P- substrate, representing an exemplary semiconductor wafer of the present invention, and the second type having a P++ substrate, representing a semiconductor wafer known in the art. P-type dopants were used for each type of semiconductor wafer. The semiconductor wafers having P- substrates had a carrier concentration profile wherein a device layer having a concentration of about  $1 \times 10^{16}$  carriers/cm<sup>3</sup> extended approximately 2  $\mu\text{m}$  into the wafer, a protective layer having a concentration of about  $1 \times 10^{19}$  carriers/cm<sup>3</sup> extended from a depth of about 3 to about 5  $\mu\text{m}$  into the wafer, and a substrate having a concentration of about  $1 \times 10^{15}$  carriers/cm<sup>3</sup> extended from about 6  $\mu\text{m}$  through the depth of the wafer. The semiconductor wafers having P++ substrates had a carrier concentration profile wherein a device layer having a concentration of about  $1 \times 10^{16}$  carriers/cm<sup>3</sup> extended approximately 2  $\mu\text{m}$  into the wafer and substrate having a concentration of about  $1 \times 10^{19}$  carriers/cm<sup>3</sup> extended from about 3  $\mu\text{m}$  through the depth of the wafer. The doping profiles for each respective type of semiconductor wafer are shown in Figures 3 and 4.

[0052] Notably, Figures 3 and 4 show that the carrier dopant profile associated with each type of semiconductor wafer is the same to a depth of about 4  $\mu\text{m}$ , i.e., both types of wafer share a P/P++ transition at about 2 to 3  $\mu\text{m}$  from the wafers' front surface. Such a transition confirms that device failure protection will be present in the semiconductor wafers exemplary of the present invention at the device/protective layer interface. Also, the doping gradient at the interface between the heavily-doped protective layer and the lightly-doped substrate creates an electrical field that further reduces the collection of charge carriers generated in the substrate below the device layer, thereby improving the protective function of the protective layer in the semiconductor wafers exemplary of the present invention.

[0053] Thermal modeling was then performed on wafers depicted in Figures 3 and 4 under two conditions: uniform heating and localized hot spots. The simulations were generated using the accepted 20% thermal conductivity difference between lightly-doped P- and heavily-doped P++ substrates. The two conditions were modeled with power distributed to a 20 mm x 20 mm grid, representing a theoretical die, which was partitioned into 1 mm x 1 mm grid squares. For modeling wafers under the uniform heating condition, an operating power of 160 W was uniformly distributed over the 20 mm x 20 mm grid. To model wafers with localized hot spots, a localized power increase of 10x (i.e. 1600 W) was concentrated in two detached 1mm x 1mm grid squares to simulate hot spots while maintaining the same overall die operating power. The modeling was carried out for die thicknesses of 250  $\mu\text{m}$  and 500  $\mu\text{m}$  under both conditions. The results of the thermal modeling are shown below in Tables 1 and 2, corresponding to the uniform heating condition and the localized hot spots condition, respectively. The model also assumed a heat transfer coefficient of 0.84 kW/m<sup>2</sup>K at the bottom of the substrate, which is based on published values in the literature.

Table 1:

| Substrate doping | Die Thickness     | Maximum T (°C) |

|------------------|-------------------|----------------|

| P++              | 250 $\mu\text{m}$ | 65.0           |

|                  | 500 $\mu\text{m}$ | 65.9           |

| P-               | 250 $\mu\text{m}$ | 64.8           |

|                  | 500 $\mu\text{m}$ | 65.6           |

Table 2:

| Substrate doping | Die Thickness     | Maximum T (°C) |

|------------------|-------------------|----------------|

| P++              | 250 $\mu\text{m}$ | 97.5           |

|                  | 500 $\mu\text{m}$ | 90.1           |

| P-               | 250 $\mu\text{m}$ | 92.5           |

|                  | 500 $\mu\text{m}$ | 85.7           |

[0054] The results of the thermal modeling show that under uniform power distribution, both wafers provide similar heat dissipation. Specifically, Table 1 shows that, as compared to the corresponding P++ substrate samples, the maximum die temperature reached in both the P- substrate samples was only 0.2 °C lower for the 250  $\mu\text{m}$  samples and 0.3 °C lower for the 500  $\mu\text{m}$  samples. This small improvement in heat dissipation indicates that the doping concentration of a given wafer's substrate has little impact on heat dissipation under uniform heating.

[0055] But in the model for localized hot spots, Table 2 shows that the semiconductor wafer having the P- substrate more effectively dissipated heat from the local hot spots. Specifically, the P- substrate wafer samples resulted in a maximum die temperature approximately 5 °C lower for the 250  $\mu\text{m}$  sample and 4.4 °C lower for the 500  $\mu\text{m}$  sample than the maximum die temperatures of the corresponding P++ substrate wafers.

[0056] Temperature contour maps were also created to further demonstrate the difference between the wafers from the hot spot simulation. Figures 5 and 6 are directed to wafers with a total thickness of about 250  $\mu\text{m}$ , with Figure 5 showing the temperature contour map of the wafer having a P++ substrate and Figure 6 showing the temperature contour map of the wafer having a P- substrate. Similarly, Figures 7 and 8 are directed to wafers with a total thickness of about 500  $\mu\text{m}$ , with Figure 7 showing the temperature contour map of the wafer having a P++ substrate and Figure 8 showing the temperature contour map of the wafer having a P- substrate. All four of these temperature contour maps show that the temperatures in the 1 mm x 1 mm grid square hot spots were less intense in the wafers having a P- substrate than in the wafer having a P++ substrate.

## EXAMPLE 2

[0057] In addition to the two semiconductor wafers formed in Example 1, seven more semiconductor wafers were formed having different substrates, as detailed below. Apart from Sample 95 below, all the samples were formed according to the CZ growth method.

[0058] For purposes of this Example, the semiconductor wafer formed having a P- substrate from Example 1 is referred to as sample 91, whereas the semiconductor wafer having a P++ substrate is referred to as sample 92.

[0059] Further, Sample 93 is a semiconductor wafer consisting essentially of P+ material; i.e., material that is doped at a level between that of the invention's protective layer and substrate, such as about  $5 \times 10^{18}$  carriers/cm<sup>3</sup>.

[0060] Sample 94 is a semiconductor wafer consisting essentially of silicon material being doped with both P- and N- doping levels; i.e., the material comprised less than about  $1 \times 10^{16}$  P-type carriers/cm<sup>3</sup> and less than about  $1 \times 10^{16}$  N-type carriers/cm<sup>3</sup>, such as about  $1 \times 10^{15}$  carriers/cm<sup>3</sup> of each dopant.

[0061] Sample 95 is a semiconductor wafer consisting essentially of silicon material formed according to the float zone method and being doped such that it is P- material, as defined for Sample 94.

[0062] Sample 96 is a semiconductor wafer consisting essentially of silicon material being doped such that it is P- material, as defined for Sample 94, and having a low concentration of oxygen interstitials.

[0063] Sample 97 is a semiconductor wafer consisting essentially of silicon material being doped such that it is P- material, as defined for Sample 94, and having a high concentration of oxygen interstitials.

[0064] Sample 98 is a semiconductor wafer structure having a substrate that is doped such that it is P- material and an epitaxial layer of P- material formed thereon, as P- is defined for Sample 94. The P- epitaxial layer is about 10  $\mu\text{m}$  thick.

[0065] Sample 99 is a semiconductor wafer structure having a substrate that is doped such that it is P- material and an epitaxial layer of P- material formed thereon, as P- is defined for Sample 94. The P- epitaxial layer is about 50  $\mu\text{m}$  thick.

[0066] Samples 91-99 were subjected to thermal conductivity measurements at 25 °C, 50 °C, 75 °C, 100 °C, and 125 °C. The results are graphically represented in Figure 15, which shows the lowest thermal conductivity for Sample 92 and the highest thermal conductivity for Samples 91 and 94-99, regardless of temperature. The fact that Samples 91 and 94-99 all

displayed substantially similar thermal conductivity profiles indicates that the variables changed between these samples has little impact on their thermal conductivity. Further, Sample 93 displays a thermal conductivity between Sample 92 and the group of Samples 91 and 94-99. This confirms that a silicon structure's doping concentration is the variable with the greatest influence on the thermal conductivity. Moreover, the data shows about a 23% increase in thermal conductivity at about 25 °C from Sample 92 to Samples 91 and 94-99, while an increase of about 13% corresponds to about 125 °C. This confirms that the semiconductor structure of the invention, as described herein, displays at least a 5% increase in thermal conductivity at the temperatures between about 25 °C and about 125 °C.

[0067] When the terms "dopant," "lightly-doped," "heavily-doped," or other terms and phrases referring to dopants are used herein, it is to be understood that either P-type or N-type dopants are being referenced, unless explicitly stated otherwise.

[0068] When introducing elements of the present invention or the preferred embodiment(s) thereof, the articles "a", "an", "the" and "said" are intended to mean that there are one or more of the elements. The terms "comprising", "including" and "having" are intended to be inclusive and mean that there may be additional elements other than the listed elements.

[0069] In view of the above, it will be seen that the several objects of the invention are achieved and other advantageous results attained.

[0070] As various changes could be made in the above products and methods without departing from the scope of the invention, it is intended that all matter contained in the above description and shown in the accompanying drawings shall be interpreted as illustrative and not in a limiting sense.

## WHAT IS CLAIMED IS:

1. A semiconductor wafer comprising:

a substrate having a central axis, a front surface and a back surface that are generally perpendicular to the central axis, a circumferential edge, and a radius extending from the central axis to the circumferential edge, wherein the

5 substrate has a dopant concentration below about  $1 \times 10^{17}$  carriers/cm<sup>3</sup>;

a silicon device layer; and

a silicon protective layer disposed between the device layer and the substrate, the protective layer being doped with a dopant concentration between about  $6.0 \times 10^{17}$  carriers/cm<sup>3</sup> and about  $1.0 \times 10^{20}$  carriers/cm<sup>3</sup> and having a

10 thickness of at least about 0.5  $\mu\text{m}$ .

2. The semiconductor wafer of claim 1 wherein the protective layer has a thickness between about 1  $\mu\text{m}$  and about 5  $\mu\text{m}$ .

3. The semiconductor wafer of claim 1 wherein the protective layer is doped with a dopant concentration between about  $8.5 \times 10^{18}$  carriers/cm<sup>3</sup> and about  $2.0 \times 10^{19}$  carriers/cm<sup>3</sup>.

4. The semiconductor wafer of claim 1 wherein the protective layer is doped with a dopant concentration between about  $3.2 \times 10^{18}$  carriers/cm<sup>3</sup> and about  $8.5 \times 10^{18}$  carriers/cm<sup>3</sup>.

5. The semiconductor wafer of claim 3 wherein the substrate has a dopant concentration between about  $5 \times 10^{14}$  carriers/cm<sup>3</sup> and about  $1 \times 10^{16}$  carriers/cm<sup>3</sup>.

6. The semiconductor wafer of claim 1 wherein the device layer is doped with a P-type dopant.

7. The semiconductor wafer of claim 1 wherein the device layer is doped with boron.

8. The semiconductor wafer of claim 1 wherein:

the substrate is doped with a P-type dopant in a concentration between about  $5 \times 10^{14}$  carriers/cm<sup>3</sup> and about  $1 \times 10^{16}$  carriers/cm<sup>3</sup>;

the protective layer is doped with a P-type dopant in a concentration between about  $3.2 \times 10^{18}$  carriers/cm<sup>3</sup> and about  $2.0 \times 10^{19}$  carriers/cm<sup>3</sup>, and has a thickness between about 1  $\mu\text{m}$  and about 10  $\mu\text{m}$ ; and

the device layer is doped with a P-type dopant in a concentration between about  $1 \times 10^{14}$  carriers/cm<sup>3</sup> and about  $4 \times 10^{16}$  carriers/cm<sup>3</sup>.

9. The semiconductor wafer of claim 1 wherein:

the protective layer is doped with a P-type dopant in a concentration above about  $1.0 \times 10^{19}$  carriers/cm<sup>3</sup> and about  $1.0 \times 10^{20}$  carriers/cm<sup>3</sup>, and has a thickness of less than about 5  $\mu\text{m}$ ; and

the device layer is between about 2  $\mu\text{m}$  and about 15  $\mu\text{m}$  thick.

10. The semiconductor wafer of claim 9 wherein the protective layer has a thickness of less than about 2  $\mu\text{m}$  and the device layer is between about 2  $\mu\text{m}$  and about 5  $\mu\text{m}$  thick.

11. A process for the preparation of a semiconductor wafer comprising a substrate having a central axis, a front surface and a back surface that are generally perpendicular to the central axis, a circumferential edge, and a radius extending from the central axis to the circumferential edge, wherein the substrate has a dopant concentration below about  $1 \times 10^{17}$  carriers/cm<sup>3</sup>, the process comprising:

forming a protective layer on the front surface of the substrate, the protective layer being doped with a dopant concentration between about  $6.0 \times 10^{17}$  carriers/cm<sup>3</sup> and about  $1.0 \times 10^{20}$  carriers/cm<sup>3</sup> and having a thickness of at least about 0.5  $\mu\text{m}$ ; and

forming a device layer on the exposed surface of the protective layer parallel to the front surface of the substrate, the device layer being doped with a dopant concentration below about  $1 \times 10^{17}$  carriers/cm<sup>3</sup>.

12. The process of claim 11 wherein the protective layer is formed by exposing the surface of the substrate to an atmosphere comprising silicon and a dopant to deposit a silicon epitaxial layer.

13. The process of claim 11 wherein the protective layer is formed by implanting dopant ions in the surface of the substrate.

14. The process of claim 11 wherein the first layer is formed by exposing the surface of the substrate to a gas comprising a dopant to form a gas phase-doped layer.

15. The process of claim 11 wherein the protective layer has a thickness between about 1  $\mu\text{m}$  and about 5  $\mu\text{m}$ .

16. The process of claim 11 wherein the protective layer is doped with a dopant concentration between about  $8.5 \times 10^{18}$  carriers/cm<sup>3</sup> and about  $2.0 \times 10^{19}$  carriers/cm<sup>3</sup>.

17. The process of claim 11 wherein the protective layer is doped with a dopant concentration between about  $3.2 \times 10^{18}$  carriers/cm<sup>3</sup> and about  $8.5 \times 10^{18}$  carriers/cm<sup>3</sup>.

18. The process of claim 16 wherein the substrate has a dopant concentration between about  $5 \times 10^{14}$  carriers/cm<sup>3</sup> and about  $1 \times 10^{16}$  carriers/cm<sup>3</sup>.

19. The process of claim 11 wherein the device layer is doped with a P-type dopant.

20. The process of claim 11 wherein the device layer is doped with boron.

21. The process of claim 11 wherein:

the substrate is doped with a P-type dopant in a concentration between about  $5 \times 10^{14}$  carriers/cm<sup>3</sup> and about  $1 \times 10^{16}$  carriers/cm<sup>3</sup>;

the protective layer is doped with a P-type dopant in a concentration between about  $3.2 \times 10^{18}$  carriers/cm<sup>3</sup> and about  $2.0 \times 10^{19}$  carriers/cm<sup>3</sup>, and has a thickness between about 1  $\mu\text{m}$  and about 10  $\mu\text{m}$ ; and

the device layer is doped with a P-type dopant in a concentration between about  $1 \times 10^{14}$  carriers/cm<sup>3</sup> and about  $4 \times 10^{16}$  carriers/cm<sup>3</sup>.

22. The process of claim 11 wherein:

the substrate is doped with a P-type dopant in a concentration between about  $5 \times 10^{14}$  carriers/cm<sup>3</sup> and about  $1 \times 10^{16}$  carriers/cm<sup>3</sup>;

the protective layer is doped with a P-type dopant in a concentration between about  $1.0 \times 10^{19}$  carriers/cm<sup>3</sup> and about  $1.0 \times 10^{20}$  carriers/cm<sup>3</sup>, and has a thickness of less than about 3  $\mu\text{m}$ ;

the device layer has a thickness between about 2  $\mu\text{m}$  and about 15  $\mu\text{m}$ ; and

the process further comprises a first etching step, wherein the back surface of the substrate is exposed to an alkaline etchant for a time period sufficient to remove substantially all of the substrate, exposing the protective layer.

23. The process of claim 22 wherein the etchant comprises a compound selected from the group consisting of potassium hydroxide, sodium hydroxide, tetramethylammonium hydroxide, and combinations thereof.

24. The process of claim 22 wherein the process further comprises exposing the protective layer exposed by the first etch to a second etching step, wherein the protective layer is exposed to an acidic etchant.

25. The process of claim 24 wherein the acidic etchant comprises a solution of hydrofluoric, nitric, and acetic acids.

26. The process of claim 22 wherein the protective layer has a thickness of less than about 2  $\mu\text{m}$  and the device layer is between about 2  $\mu\text{m}$  and about 5  $\mu\text{m}$  thick.

1/10

FIG. 1

2/10

FIG. 2

3/10

FIG. 3

4/10

**FIG. 4**

**PRIOR ART**

5/10

## FIG. 5

### PRIOR ART

6/10

FIG. 6

7/10

## FIG. 7

### PRIOR ART

8/10

FIG. 8

FIG. 9

10/10

FIG. 10

## INTERNATIONAL SEARCH REPORT

International application No

PCT/US2007/061128

A. CLASSIFICATION OF SUBJECT MATTER

INV. H01L27/02 H01L29/36

ADD. H01L31/0352

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

H01L

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                     | Relevant to claim No.  |

|-----------|--------------------------------------------------------------------------------------------------------|------------------------|

| X         | US 5 023 200 A (BLEWER ROBERT S [US] ET AL) 11 June 1991 (1991-06-11)                                  | 1-7,<br>9-20,<br>22-26 |

| Y         | column 3, lines 40-60; figures 2,3,6<br>abstract                                                       | 8,21                   |

| X         | US 4 628 591 A (ZORINSKY ELDON J [US] ET AL) 16 December 1986 (1986-12-16)                             | 1-5,10,<br>11,15-18    |

| Y         | abstract; figures 1-6                                                                                  | 8,21                   |

| X         | US 6 635 950 B1 (ISHIDA HIDETSUGU [JP] ET AL) 21 October 2003 (2003-10-21)<br>abstract; figures 1,2,10 | 1-5,10,<br>11,15-18    |

| A         | US 4 729 964 A (NATSUAKI NOBUYOSHI [JP] ET AL) 8 March 1988 (1988-03-08)<br>abstract; figure 5         | 1-26                   |

|           |                                                                                                        | -/-                    |

Further documents are listed in the continuation of Box C.

See patent family annex.

## \* Special categories of cited documents :

- \*A\* document defining the general state of the art which is not considered to be of particular relevance

- \*E\* earlier document but published on or after the international filing date

- \*L\* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- \*O\* document referring to an oral disclosure, use, exhibition or other means

- \*P\* document published prior to the international filing date but later than the priority date claimed

- \*T\* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

- \*X\* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

- \*Y\* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

- \*&\* document member of the same patent family

|                                                                                                                                                                                         |                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Date of the actual completion of the international search                                                                                                                               | Date of mailing of the international search report |

| 18 June 2007                                                                                                                                                                            | 03/07/2007                                         |

| Name and mailing address of the ISA/<br>European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,<br>Fax: (+31-70) 340-3016 | Authorized officer<br><br>Dauw, Xavier             |

## INTERNATIONAL SEARCH REPORT

International application No

PCT/US2007/061128

## C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                 | Relevant to claim No. |

|-----------|--------------------------------------------------------------------------------------------------------------------|-----------------------|

| A         | EP 0 368 768 A1 (SGS THOMSON<br>MICROELECTRONICS [FR])<br>16 May 1990 (1990-05-16)<br>abstract; figure 1A<br>----- | 1-26                  |

| A         | US 4 104 090 A (POGGE HANS BERNHARD)<br>1 August 1978 (1978-08-01)<br>abstract; figure 1<br>-----                  | 1-26                  |

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/US2007/061128

| Patent document cited in search report |    | Publication date | Patent family member(s) |             | Publication date |

|----------------------------------------|----|------------------|-------------------------|-------------|------------------|

| US 5023200                             | A  | 11-06-1991       | NONE                    |             |                  |

| US 4628591                             | A  | 16-12-1986       | JP                      | 61180446 A  | 13-08-1986       |

| US 6635950                             | B1 | 21-10-2003       | NONE                    |             |                  |

| US 4729964                             | A  | 08-03-1988       | JP                      | 2057463 C   | 23-05-1996       |

|                                        |    |                  | JP                      | 7093282 B   | 09-10-1995       |

|                                        |    |                  | JP                      | 61237422 A  | 22-10-1986       |

| EP 0368768                             | A1 | 16-05-1990       | DE                      | 68915510 D1 | 30-06-1994       |

|                                        |    |                  | DE                      | 68915510 T2 | 05-01-1995       |

|                                        |    |                  | FR                      | 2638892 A1  | 11-05-1990       |

|                                        |    |                  | JP                      | 2180015 A   | 12-07-1990       |

|                                        |    |                  | JP                      | 2697199 B2  | 14-01-1998       |

|                                        |    |                  | US                      | 5032540 A   | 16-07-1991       |

| US 4104090                             | A  | 01-08-1978       | BR                      | 7801029 A   | 02-01-1979       |

|                                        |    |                  | CA                      | 1092252 A1  | 23-12-1980       |

|                                        |    |                  | DE                      | 2805169 A1  | 31-08-1978       |

|                                        |    |                  | ES                      | 466901 A1   | 01-10-1978       |

|                                        |    |                  | FR                      | 2382096 A1  | 22-09-1978       |

|                                        |    |                  | GB                      | 1544393 A   | 19-04-1979       |

|                                        |    |                  | IT                      | 1113108 B   | 20-01-1986       |

|                                        |    |                  | JP                      | 53105988 A  | 14-09-1978       |

|                                        |    |                  | NL                      | 7802011 A   | 28-08-1978       |

|                                        |    |                  | SE                      | 428508 B    | 04-07-1983       |

|                                        |    |                  | SE                      | 7802044 A   | 25-08-1978       |