(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2019-169579

(P2019-169579A)

(43) 公開日 令和1年10月3日(2019.10.3)

| (51) Int.Cl.            | F 1           | テーマコード (参考) |           |  |

|-------------------------|---------------|-------------|-----------|--|

| HO 1 L 21/28 (2006.01)  | HO 1 L 21/28  | 3 O 1 R     | 4 M 1 O 4 |  |

| HO 1 L 21/288 (2006.01) | HO 1 L 21/288 | M           |           |  |

| HO 1 L 29/47 (2006.01)  | HO 1 L 21/288 | E           |           |  |

| HO 1 L 29/872 (2006.01) | HO 1 L 29/48  | M           |           |  |

| HO 1 L 29/417 (2006.01) | HO 1 L 29/50  | M           |           |  |

審査請求 未請求 請求項の数 17 O L (全 23 頁) 最終頁に続く

|           |                            |          |                                                 |

|-----------|----------------------------|----------|-------------------------------------------------|

| (21) 出願番号 | 特願2018-55445 (P2018-55445) | (71) 出願人 | 000003078<br>株式会社東芝<br>東京都港区芝浦一丁目1番1号           |

| (22) 出願日  | 平成30年3月23日 (2018.3.23)     | (71) 出願人 | 317011920<br>東芝デバイス&ストレージ株式会社<br>東京都港区芝浦一丁目1番1号 |

|           |                            | (74) 代理人 | 100119035<br>弁理士 池上 徹真                          |

|           |                            | (74) 代理人 | 100141036<br>弁理士 須藤 章                           |

|           |                            | (74) 代理人 | 100088487<br>弁理士 松山 允之                          |

|           |                            | (72) 発明者 | 犬宮 誠治<br>東京都港区芝浦一丁目1番1号 東芝デバイス&ストレージ株式会社内       |

|           |                            |          | 最終頁に続く                                          |

(54) 【発明の名称】半導体装置及びその製造方法

## (57) 【要約】

【課題】信頼性を向上することが可能な半導体装置を提供する。

【解決手段】実施形態の半導体装置は、銅を主成分とし、厚さが $5 \mu\text{m}$ 以上 $50 \mu\text{m}$ 未満の第1の電極パッドと、銅を主成分とし、厚さが $5 \mu\text{m}$ 以上 $50 \mu\text{m}$ 未満の電極層と、第1の電極パッドと電極層との間に設けられた半導体層と、を備える。

【選択図】図3

## 【特許請求の範囲】

## 【請求項 1】

銅を主成分とし、厚さが 5  $\mu\text{m}$  以上 50  $\mu\text{m}$  未満の第 1 の電極パッドと、

銅を主成分とし、厚さが 5  $\mu\text{m}$  以上 50  $\mu\text{m}$  未満の電極層と、

前記第 1 の電極パッドと前記電極層との間に設けられた半導体層と、

を備える半導体装置。

## 【請求項 2】

前記第 1 の電極パッドの端部の厚さが中央部の厚さより厚い請求項 1 記載の半導体装置。

。

## 【請求項 3】

前記電極層の端部の厚さと中央部の厚さが略同一である請求項 1 又は請求項 2 記載の半導体装置。

10

## 【請求項 4】

前記電極層の端部が前記半導体層の端部よりも内側にある請求項 1 ないし請求項 3 いずれか一項記載の半導体装置。

## 【請求項 5】

前記第 1 の電極パッド及び前記電極層が、鉄 (Fe)、コバルト (Co)、及び、ニッケル (Ni) から成る群から選ばれる少なくともいずれか一つの元素を含む請求項 1 ないし請求項 4 いずれか一項記載の半導体装置。

20

## 【請求項 6】

前記第 1 の電極パッド及び前記電極層の中の前記元素の含有量が 0.01 原子 % 以上 0.4 原子 % 以下である請求項 5 記載の半導体装置。

## 【請求項 7】

前記元素は銅の結晶粒界に偏析している請求項 5 又は請求項 6 記載の半導体装置。

## 【請求項 8】

銅を主成分とし、厚さが 5  $\mu\text{m}$  以上 50  $\mu\text{m}$  未満の第 2 の電極パッドを更に備え、前記半導体層は前記第 2 の電極パッドと前記電極層との間に設けられた請求項 1 ないし請求項 7 いずれか一項記載の半導体装置。

## 【請求項 9】

銅 (Cu) を主成分とし、鉄 (Fe)、コバルト (Co)、及び、ニッケル (Ni) から成る群から選ばれる少なくともいずれか一つの元素を含み、厚さが 5  $\mu\text{m}$  以上 50  $\mu\text{m}$  未満の第 1 の電極パッドと、

30

電極層と、

前記第 1 の電極パッドと前記電極層との間に設けられた半導体層と、

を備える半導体装置。

## 【請求項 10】

前記第 1 の電極パッドの中の前記元素の含有量が 0.01 原子 % 以上 0.4 原子 % 以下である請求項 9 記載の半導体装置。

## 【請求項 11】

前記元素は銅の結晶粒界に偏析している請求項 9 又は請求項 10 記載の半導体装置。

40

## 【請求項 12】

第 1 の面と第 2 の面とを有する半導体基板の前記第 2 の面の側の周辺部が残存するよう前記第 2 の面の側の中央部を薄くし、

前記第 1 の面の側にレジストパターンを形成し、

電界めっき装置を用い電解めっき法により、前記第 1 の面の側に銅 (Cu) を主成分とし厚さが 5  $\mu\text{m}$  以上 50  $\mu\text{m}$  未満の第 1 の金属膜と、前記第 2 の面の側に銅を主成分とし厚さが 5  $\mu\text{m}$  以上 50  $\mu\text{m}$  未満の第 2 の金属膜とを同時に形成する半導体装置の製造方法。

。

## 【請求項 13】

前記半導体基板が前記第 1 の面に所定の幅を有するダイシングラインを有し、

50

前記第2の金属膜の前記ダイシングラインに対応する部分を除去し、前記ダイシングラインに沿って前記半導体基板を切断し、前記半導体基板から複数の半導体チップを形成する請求項12記載の半導体装置の製造方法。

【請求項14】

前記電解めっき法により、前記第1の金属膜及び前記第2の金属膜を形成する際に、電界めっき液中に、鉄イオン、コバルトイオン、及び、ニッケルイオンから成る群から選ばれる少なくともいずれか一つのイオンを添加する請求項12又は請求項13記載の半導体装置の製造方法。

【請求項15】

前記電界めっき液の中の3価の前記イオンの濃度をモニタし、モニタした結果に基づき2価の前記イオンの供給を行う請求項14記載の半導体装置の製造方法。

10

【請求項16】

前記電解めっき法により、前記第1の金属膜及び前記第2の金属膜を形成する際に、前記半導体基板の前記第1の面の側と前記第2の面の側に異なる電圧を印加する請求項12ないし請求項15いずれか一項記載の半導体装置の製造方法。

【請求項17】

前記電解めっき法により、前記第1の金属膜及び前記第2の金属膜を形成した後に、前記電界めっき装置を、60以上水を用いて洗浄する請求項12ないし請求項16いずれか一項記載の半導体装置の製造方法。

20

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

パワー半導体デバイスでは、半導体チップの発熱による温度上昇に起因する信頼性の低下が問題になる。例えば、発熱によりトランジスタの閾値電圧のばらつきが生じ、デバイス動作が不安定となるおそれがある。また、発熱によりデバイスが破壊するおそれがある。

30

【0003】

発熱による温度上昇を抑制するため、半導体チップの表面に設けられる電極に、熱伝導率の大きな銅を用いることがある。熱伝導率の大きな銅を電極に用いることで、半導体チップの冷却を行い、半導体チップの発熱による温度上昇を抑制する。

【0004】

半導体チップの冷却効果を高めるためには、電極に用いる銅の厚さを厚くすることが望ましい。しかし、銅の厚さを厚くすると、電極の応力が大きくなり半導体チップの反りが大きくなる。半導体チップの反りにより、半導体チップにクラックが生じたり、接合層として用いるはんだの中にボイドが生じたりするおそれがある。

40

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2011-77460号公報

【特許文献2】特許4591084号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

50

本発明が解決しようとする課題は、信頼性を向上することが可能な半導体装置を提供することにある。

【課題を解決するための手段】

【0007】

本発明の一態様の半導体装置は、銅を主成分とし、厚さが5μm以上50μm未満の第1の電極パッドと、銅を主成分とし、厚さが5μm以上50μm未満の電極層と、第1の電極パッドと電極層との間に設けられた半導体層と、を備える。

【図面の簡単な説明】

【0008】

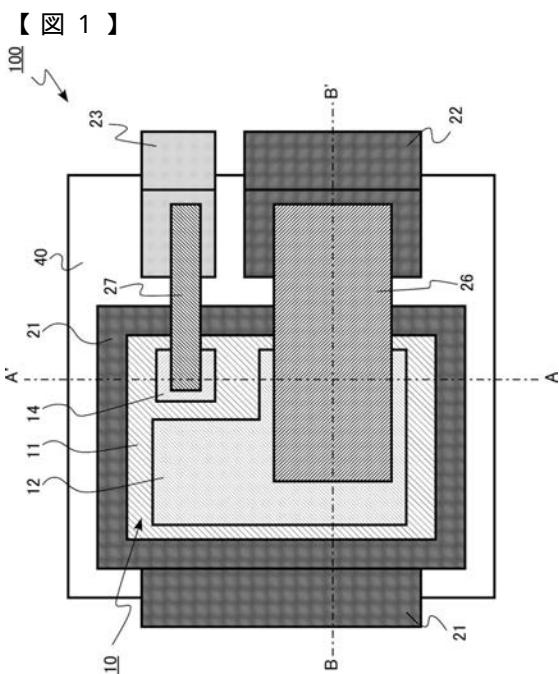

【図1】第1の実施形態の半導体装置の模式上面図。

10

【図2】第1の実施形態の半導体装置の模式断面図。

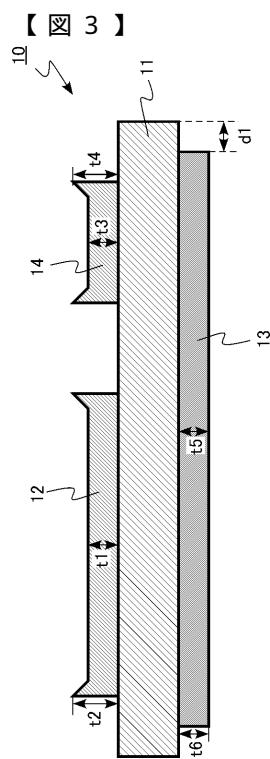

【図3】第1の実施形態の半導体装置の模式断面図。

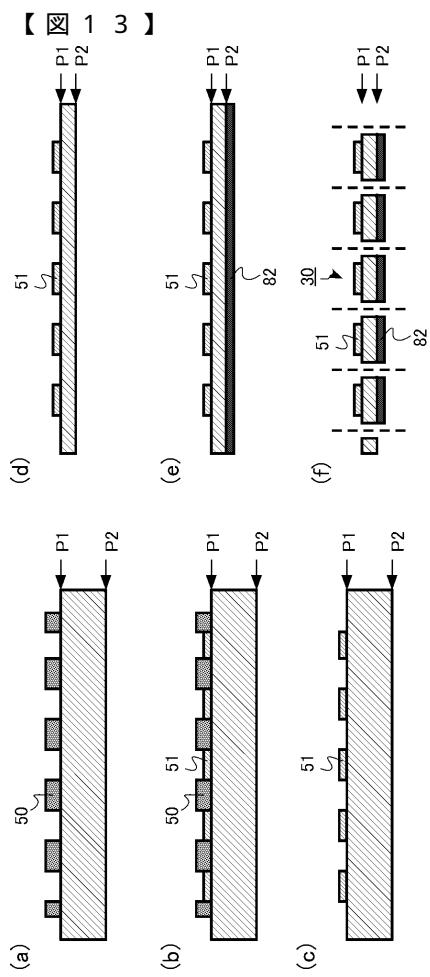

【図4】第1の実施形態の半導体装置の製造方法を示す図。

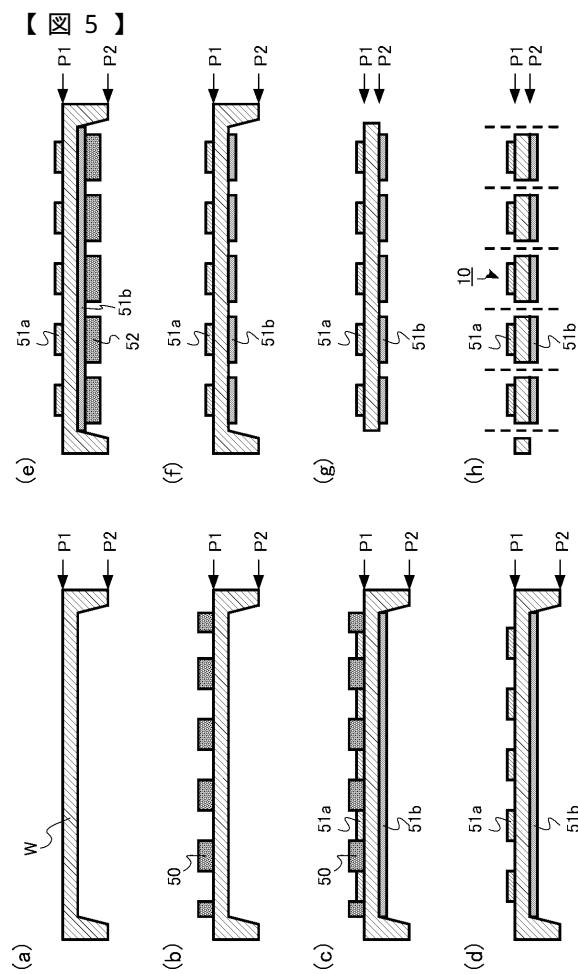

【図5】第1の実施形態の半導体装置の製造方法を示す図。

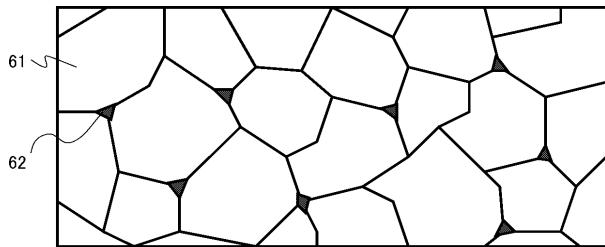

【図6】第2の実施形態の半導体装置の電極の模式断面図。

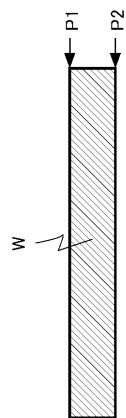

【図7】第2の実施形態の半導体装置の製造方法の説明図。

【図8】第2の実施形態の半導体装置の作用及び効果の説明図。

【図9】第2の実施形態の半導体装置の作用及び効果の説明図。

【図10】第2の実施形態の半導体装置の作用及び効果の説明図。

20

【図11】第3の実施形態の半導体装置の模式断面図。

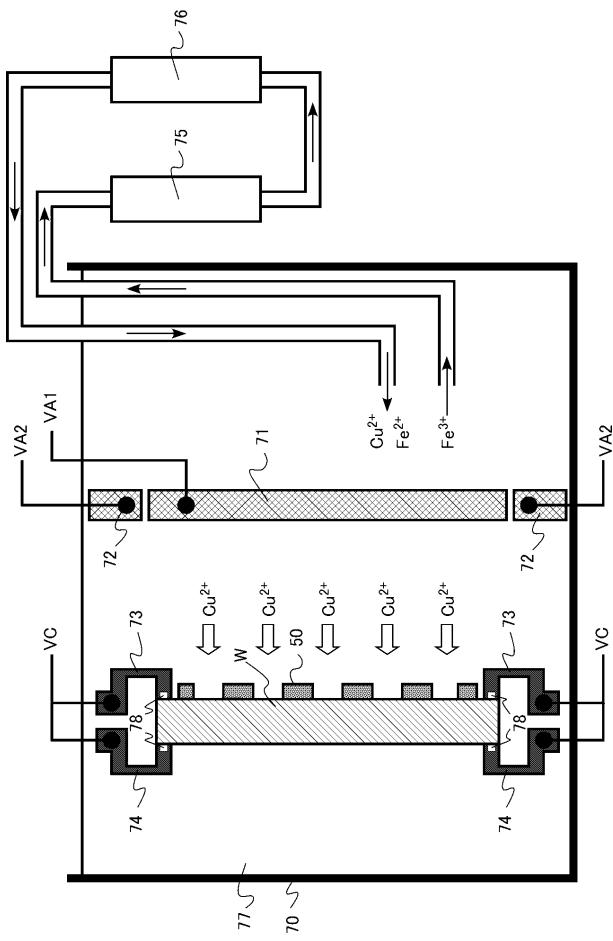

【図12】第3の実施形態の半導体装置の製造方法を示す図。

【図13】第3の実施形態の半導体装置の製造方法を示す図。

【図14】第3の実施形態の半導体装置の製造方法の説明図。

【発明を実施するための形態】

【0009】

本明細書中、同一又は類似する部材については、同一の符号を付し、重複する説明を省略する場合がある。

【0010】

本明細書中、部品等の位置関係を示すために、図面の上方向を「上」、図面の下方向を「下」と記述する場合がある。本明細書中、「上」、「下」の概念は、必ずしも重力の向きとの関係を示す用語ではない。

30

【0011】

本明細書中に記載される電極を構成する元素の種類は、例えば、SIMS (Secondary Ion Mass Spectrometry) 又はEDX (Energy Dispersive X-ray Spectroscopy) により測定することができる。また、電極中の添加元素の分布は、例えば、EDX により識別することができる。また、電極厚さ等の長さは、例えば、SEM (Scanning Electron Microscopy) 又はTEM (Transmission Electron Microscopy) により測定することができる。

40

【0012】

本明細書中、銅を主成分とする金属とは、金属を構成する総元素の中で、銅の占める原子割合が最も大きい金属を意味する。本明細書中、銅を主成分とする金属とは、例えば、銅の占める原子割合が90%以上の金属である。

【0013】

(第1の実施形態)

第1の実施形態の半導体装置は、銅(Cu)を主成分とし、厚さが5μm以上50μm未満の第1の電極パッドと、銅を主成分とし、厚さが5μm以上50μm未満の電極層と、第1の電極パッドと電極層との間に設けられた半導体層と、を備える。

【0014】

第1の実施形態の半導体装置は、半導体チップ10又は半導体パッケージ100である

50

。半導体チップ10は、電力制御や電力供給に用いられるパワー半導体チップである。また、半導体パッケージ100は、半導体チップ10を含むパワー半導体パッケージである。

【0015】

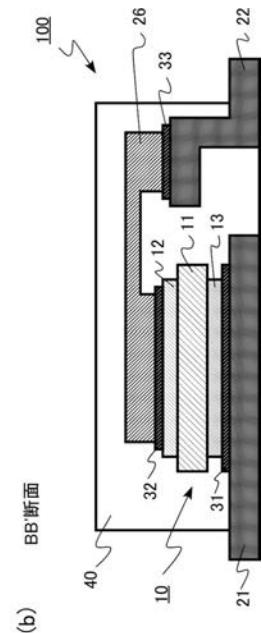

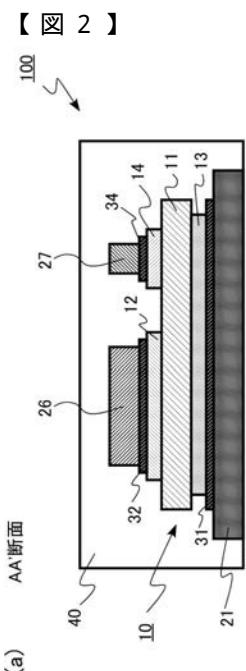

図1は、第1の実施形態の半導体装置の模式上面図である。図2は、第1の実施形態の半導体装置の模式断面図である。図2(a)は、図1のAA'断面図である。図2(b)は、図1のBB'断面図である。

【0016】

半導体パッケージ100は、半導体チップ10、ドレインリード21、ソースリード22、ゲートリード23、ソースコネクタ26、ゲートコネクタ27、第1の接合層31、第2の接合層32、第3の接合層33、第4の接合層34、モールド樹脂40を備える。

【0017】

半導体チップ10は、半導体層11、ソース電極パッド12(第1の電極パッド)、ドレイン電極13(電極層)、ゲート電極パッド14(第2の電極パッド)を備える。半導体チップ10は、例えば、縦型パワーMOSFET(Metal Oxide Field Effect Transistor)である。

【0018】

ソース電極パッド12は、第1の電極パッドの一例である。ドレイン電極13は、電極層の一例である。ゲート電極パッド14は、第2の電極パッドの一例である。

【0019】

ドレインリード21は、板状の金属である。ドレインリード21は、例えば、銅を主成分とする金属である。ドレインリード21は、例えば、純銅又は銅合金である。ドレインリード21は、第1の電極端子の一例である。ドレインリード21の下面は、例えば、モールド樹脂40の下面に露出する。

【0020】

ソースリード22は、金属である。ソースリード22は、例えば、銅を主成分とする金属である。ソースリード22は、例えば、純銅又は銅合金である。

【0021】

ゲートリード23は、金属である。ゲートリード23は、例えば、銅を主成分とする金属である。ゲートリード23は、例えば、純銅又は銅合金である。

【0022】

半導体チップ10は、ドレインリード21の上に設けられる。

【0023】

ドレインリード21と半導体チップ10の間には、第1の接合層31が設けられる。第1の接合層31によりドレインリード21と半導体チップ10は、接合される。第1の接合層31は、例えば、はんだである。第1の接合層31によりドレインリード21とドレイン電極13が電気的に接続される。

【0024】

ソースコネクタ26は、半導体チップ10の上に設けられる。ソースコネクタ26は、金属である。ソースコネクタ26は、例えば、銅を主成分とする金属である。ソースコネクタ26は、例えば、純銅又は銅合金である。

【0025】

半導体チップ10とソースコネクタ26の間には、第2の接合層32が設けられる。第2の接合層32により半導体チップ10とソースコネクタ26は、接合される。第2の接合層32は、例えば、はんだである。第2の接合層32により、ソース電極パッド12とソースコネクタ26が電気的に接続される。

【0026】

ソースコネクタ26は、ソースリード22の上に設けられる。ソースコネクタ26とソースリード22の間には、第3の接合層33が設けられる。第3の接合層33によりソースリード22とソースコネクタ26は、接合される。第3の接合層33は、例えば、はん

10

20

30

40

50

だである。

【0027】

第3の接合層33により、ソースコネクタ26とソースリード22が電気的に接続される。ソース電極パッド12は、第2の接合層32、ソースコネクタ26、第3の接合層33を介して、ソースリード22に電気的に接続される。

【0028】

ゲートコネクタ27は、半導体チップ10の上に設けられる。ゲートコネクタ27は、金属である。ゲートコネクタ27は、例えば、銅を含む金属である。ゲートコネクタ27は、例えば、純銅又は銅合金である。

【0029】

半導体チップ10とゲートコネクタ27の間には、第4の接合層34が設けられる。第4の接合層34により半導体チップ10とゲートコネクタ27は、接合される。第4の接合層34は、例えば、はんだである。第4の接合層34により、ゲート電極パッド14とゲートコネクタ27が電気的に接続される。

【0030】

ゲートコネクタ27は、ゲートリード23の上に設けられる。ゲートコネクタ27とゲートリード23の間には、図示しない第5の接合層が設けられる。第5の接合層によりゲートリード23とゲートコネクタ27は、接合される。第5の接合層は、例えば、はんだである。

【0031】

第5の接合層により、ゲートコネクタ27とゲートリード23が電気的に接続される。ゲート電極パッド14は、第4の接合層34、ゲートコネクタ27、第5の接合層を介して、ゲートリード23に電気的に接続される。

【0032】

モールド樹脂40は、半導体チップ10、ソースコネクタ26及びゲートコネクタ27を囲む。モールド樹脂40は、例えば、エポキシ樹脂である。

【0033】

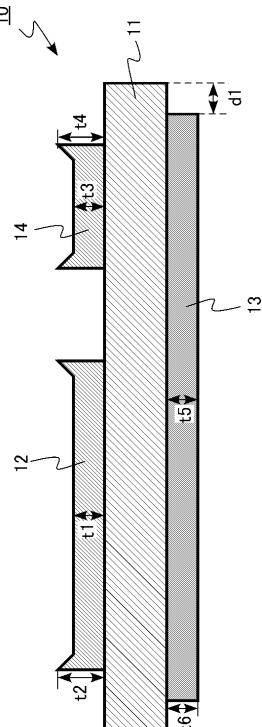

図3は、第1の実施形態の半導体装置の模式断面図である。図3は、半導体チップ10の詳細を示す図である。

【0034】

半導体層11は、単結晶の半導体である。半導体層11は、例えば、単結晶シリコン、単結晶炭化珪素(SiC)又は単結晶窒化物半導体である。

【0035】

半導体層11は、ソース電極パッド12とドレイン電極13との間に設けられる。半導体層11は、ゲート電極パッド14とドレイン電極13との間に設けられる。

【0036】

ソース電極パッド12は、銅を主成分とする金属である。ソース電極パッド12は、例えば、純銅である。ソース電極パッド12の中央部の厚さ(図3中のt1)は、5μm以上50μm未満である。

【0037】

ソース電極パッド12の端部の厚さ(図3中のt2)は、例えば、ソース電極パッド12の中央部の厚さt1よりも厚い。ソース電極パッド12の端部の厚さt2は、例えば、ソース電極パッド12の中央部の厚さt1の1.1倍以上1.5倍以下である。

【0038】

ゲート電極パッド14は、銅を主成分とする金属である。ゲート電極パッド14は、例えば、純銅である。ゲート電極パッド14の中央部の厚さ(図3中のt3)は、5μm以上50μm未満である。

【0039】

ゲート電極パッド14の端部の厚さ(図3中のt4)は、例えば、ゲート電極パッド14の中央部の厚さt3よりも厚い。ゲート電極パッド14の端部の厚さt4は、例えば、

10

20

30

40

50

ゲート電極パッド 1 4 の中央部の厚さ  $t_3$  の 1.1 倍以上 1.5 倍以下である。

【0040】

ドレイン電極 1 3 は、銅を主成分とする金属である。ドレイン電極 1 3 は、例えば、純銅である。ドレイン電極 1 3 の中央部の厚さ（図 3 中の  $t_5$ ）は、5  $\mu\text{m}$  以上 50  $\mu\text{m}$  未満である。

【0041】

ドレイン電極 1 3 の端部の厚さ（図 3 中の  $t_6$ ）は、例えば、ドレイン電極 1 3 の中央部の厚さ  $t_5$  と略同一である。ドレイン電極 1 3 の端部の厚さ  $t_6$  は、ドレイン電極 1 3 の中央部の厚さ  $t_5$  と公差の範囲で同一である。ドレイン電極 1 3 は、例えば、全体に均一な厚さを有する。

10

【0042】

ドレイン電極 1 3 の端部は、半導体層 1 1 の端部よりも所定の距離（図 3 中の  $d_1$ ）だけ内側にある。所定の距離  $d_1$  は、例えば、15  $\mu\text{m}$  以上 115  $\mu\text{m}$  以下である。

【0043】

半導体層 1 1 の上には、例えば、図示しない層間絶縁膜が設けられる。層間絶縁膜は、例えば、酸化膜、窒化膜、酸窒化膜、又は、樹脂膜である。層間絶縁膜は、例えば、酸化シリコン膜とポリイミド膜の積層膜である。

【0044】

ソース電極パッド 1 2 と半導体層 1 1との間には、例えば、図示しないソース電極が設けられる。ソース電極は、例えば、銅と異なる金属である。ソース電極は、例えば、アルミニウムを主成分とする金属である。ソース電極は、例えば、半導体層 1 1 に接する。

20

【0045】

ソース電極とソース電極パッド 1 2 との間には、例えば、図示しないバリアメタル層が設けられる。バリアメタル層は、例えば、金属又は金属窒化物である。バリアメタル層は、例えば、チタン、タンタル、窒化チタン、窒化タンタル、窒化タンゲステンである。

【0046】

なお、半導体層 1 1 の上に、ソース電極を介さずに、ソース電極パッド 1 2 が設けられても構わない。この場合、例えば、半導体層 1 1 とソース電極パッド 1 2 との間に、図示しないバリアメタル層が設けられる。バリアメタル層は、例えば、金属又は金属窒化物である。バリアメタル層は、例えば、チタン、タンタル、窒化チタン、窒化タンタル、窒化タンゲステンである。

30

【0047】

ゲート電極パッド 1 4 と半導体層 1 1 との間には、例えば、図示しないゲート電極が設けられる。ゲート電極は、例えば、多結晶半導体である。ゲート電極は、例えば、多結晶シリコンである。

【0048】

ゲート電極とゲート電極パッド 1 4 との間には、例えば、図示しないバリアメタル層が設けられる。バリアメタル層は、例えば、金属又は金属窒化物である。バリアメタル層は、例えば、チタン、タンタル、窒化チタン、窒化タンタル、窒化タンゲステンである。

40

【0049】

次に、第 1 の実施形態の半導体装置の製造方法の一例について説明する。

【0050】

第 1 の実施形態の半導体装置の製造方法は、第 1 の面と第 2 の面とを有する半導体基板の第 2 の面の側の周辺部が残存するよう第 2 の面の側の中央部を薄くし、第 1 の面の側にレジストパターンを形成し、電界めっき装置を用い電解めっき法により、第 1 の面の側に銅（Cu）を主成分とし厚さが 5  $\mu\text{m}$  以上 50  $\mu\text{m}$  未満の第 1 の金属膜と、第 2 の面の側に銅を主成分とし厚さが 5  $\mu\text{m}$  以上 50  $\mu\text{m}$  未満の第 2 の金属膜とを同時に形成する。

【0051】

図 4、図 5 は、第 1 の実施形態の半導体装置の製造方法を示す図である。図 4 (a) は、製造途中の半導体装置の上面図、図 4 (b) は図 4 (a) の C-C' 断面図である。図 5

50

は、製造途中の半導体装置の断面図である。

【0052】

シリコン基板Wに、複数のMOSFET101を形成する(図4)。シリコン基板Wは、半導体基板の一例である。シリコン基板Wは、第1の面P1と第2の面P2を有する。以下、第1の面P1を表面、第2の面P2を裏面と称する。シリコン基板Wの厚さは、例えば、750μmである。

【0053】

MOSFET101の間には、後に、ダイシングにより個片化するための所定の幅を有するダイシングライン102が設けられる。ウェハWの表面には、図示しない酸化シリコン膜とポリイミド膜の積層保護膜が形成されている。

10

【0054】

積層保護膜の開口部に、図示しないソース電極とゲート電極とが露出する。ソース電極とゲート電極とは、アルミニウムを主成分とする金属である。ダイシングライン102上では、積層保護膜が除去されシリコン基板Wが露出している。

【0055】

シリコン基板Wの表面に、図示しないバリアメタル層とシード層を形成する。バリアメタル層とシード層はPVD法(Physical Vapor Deposition法)により堆積する。例えば、バリアメタル層は厚さ150nmのチタン、シード層は厚さ500nmの銅である。

20

【0056】

次に、シリコン基板Wの周辺部が残存するようシリコン基板Wの裏面の側の中央部を薄くする。具体的には、シリコン基板Wの表面を図示しないバックグラインドテープで保護する。この状態で、シリコン基板Wの周辺部の約3mmを除く部分の裏面側を研削する(図5(a))。研削により、例えば、シリコン基板Wの厚さを65μmにする。

【0057】

次に、ウェットエッティングにより裏面側のシリコンを、例えば、15μmエッティングする。ウェットエッティングには混酸を用いる。裏面側のシリコンをエッティングすることにより、研削により生じたダメージを除去する。

【0058】

次に、シリコン基板Wの裏面に、図示しないバリアメタル層とシード層を形成する。バリアメタル層とシード層はPVD法により堆積する。例えば、バリアメタル層は厚さ150nmのチタン、シード層は厚さ500nmの銅である。なお、バリアメタル層を堆積する前に、希フッ酸処理を行い、自然酸化膜を除去することが好ましい。

30

【0059】

次に、表面のバックグラインドテープを剥離する。次に、リソグラフィ法を用いて、シリコン基板Wの表面に、レジストパターン50を形成する(図5(b))。レジストの膜厚は、例えば、25μmである。レジストパターン50は、シリコン基板Wの表面のソース電極上、ゲート電極上が開口されている。

【0060】

次に、電界めっき装置を用いた電解めっき法により、シリコン基板Wの表面のソース電極上、ゲート電極上に、第1の銅めっき膜51a(第1の金属膜)を形成する。同時に、シリコン基板Wの裏面に、第2の銅めっき膜51b(第2の金属膜)を形成する(図5(c))。第1の銅めっき膜51a及び第2の銅めっき膜51bの厚さは、例えば、20μmである。

40

【0061】

第1の銅めっき膜51aは、ソース電極パッド12及びゲート電極パッド14となる。第2の銅めっき膜51bは、ドレイン電極13となる。

【0062】

次に、シリコン基板Wの表面のレジストパターン50を有機溶剤で除去する(図5(d))。次に、シリコン基板Wの表面のレジストパターン50で覆われていた銅のシード層

50

を除去する。次に、水酸化カリウム過酸化水素水溶液を用いてチタンのバリアメタル層を除去する。シード層とバリアメタル層を除去することにより、ソース電極パッド12とゲート電極パッド14とを電気的に分離する。

【0063】

次に、シリコン基板Wの表面に、図示しない耐酸性の保護テープを張り付ける。次に、リソグラフィ法を用いて、裏面側のダイシングライン102に対応する領域と、裏面側のシリコン基板Wの周辺部の約5mmの領域を露出させるように、レジストパターン52を形成する(図5(e))。

【0064】

次に、リン硝酢酸水溶液を用いて、裏面側のダイシングライン102に対応する領域と、裏面側のシリコン基板Wの周辺部との、第2の銅めっき膜51b及び銅のシード層を除去する。次に、レジストパターン52を除去した後、水酸化カリウム過酸化水素水溶液を用いて、裏面側のダイシングライン102に対応する領域と、裏面側のシリコン基板Wの周辺部とに露出したチタンのバリアメタル層を除去する(図5(f))。

【0065】

次に、シリコン基板Wの裏面側に、図示しないダイシングシートを張り付ける。次に、シリコン基板Wの周辺部の厚い部分をブレードで分離し除去する(図5(g))。

【0066】

次に、ブレードダイシングを用いて、シリコン基板Wをダイシングライン102に沿って切断し、複数のMOSFET101を分離し、複数の半導体チップ10とする(図5(h))。なお、ブレードダイシングに代えて、レーザダイシングやプラズマダイシングを用いることも可能である。

【0067】

以上の製造方法により、第1の実施形態の半導体チップ10が製造される。

【0068】

次に、第1の実施形態の半導体装置の作用及び効果について説明する。

【0069】

パワー半導体デバイスでは、半導体チップの発熱による温度上昇に起因する信頼性の低下が問題になる。例えば、発熱によりトランジスタの閾値電圧のばらつきが生じ、デバイス動作が不安定となるおそれがある。また、発熱によりデバイスが破壊するおそれがある。

【0070】

発熱による温度上昇を抑制するため、半導体チップの表面に設けられる電極に、熱伝導率の大きな銅を用いることがある。熱伝導率の大きな銅を電極に用いることで、半導体チップの冷却を行い、半導体チップの発熱による温度上昇を抑制する。

【0071】

半導体チップの冷却効果を高めるためには、電極に用いる銅の厚さを厚くすることが望ましい。しかし、銅の厚さを厚くすると、電極の応力が大きくなり半導体チップの反りが大きくなる。半導体チップの反りにより、半導体チップにクラックが生じるおそれがある。半導体チップの接合には、例えば、はんだが用いられる。半導体チップの反りにより、はんだリフロー工程ではんだ中に発生するガスの排出が困難になり、はんだの中にボイドが生じたりするおそれがある。よって、電極に用いる銅の厚さを厚くすることで、パワー半導体デバイスの信頼性が低下するおそれがある。

【0072】

第1の実施形態の半導体装置では、半導体チップ10の両面に銅を主成分とする厚さ5μm以上の電極を設ける。すなわち、半導体チップ10の表面に、銅を主成分とするソース電極パッド12と、銅を主成分とするゲート電極パッド14とを設ける。また、半導体チップ10の裏面に銅を主成分とするドレイン電極13を設ける。

【0073】

半導体チップ10の両面に厚い銅を主成分とする電極を設けることで、半導体チップ1

10

20

30

40

50

0の冷却効果が向上する。したがって、半導体チップ10内の発熱による温度上昇が抑制される。よって、半導体チップ10の信頼性が向上する。

【0074】

そして、半導体チップ10の両面の電極の応力がバランスし、半導体チップの反りが抑制される。したがって、銅の電極の厚さを5μm以上としても半導体チップの反りが抑制される。よって、半導体チップ10のクラックや、はんだの中のボイドの発生が抑制され、半導体チップ10の信頼性が向上する。

【0075】

なお、電極の厚さが5μmを下回ると、半導体チップ10の冷却効果が不十分となる。また、電極の厚さが50μm以上になると、電極による応力が大きくなりすぎ、半導体チップ10の信頼性が低下する。

10

【0076】

第1の実施形態の半導体チップ10では、ソース電極パッド12の端部の厚さt2は、ソース電極パッド12の中央部の厚さt1よりも厚いことが好ましい。ソース電極パッド12の上の第2の接合層32には、例えば、はんだが用いられる。端部の厚さt2を中央部の厚さt1よりも厚くすることで、はんだリフロー工程の際に、はんだがソース電極パッド12の外にはみ出すことが抑制される。

【0077】

また、ゲート電極パッド14の端部の厚さt4は、ゲート電極パッド14の中央部の厚さt3よりも厚いことが好ましい。ゲート電極パッド14の上の第4の接合層34には、例えば、はんだが用いられる。端部の厚さt4を中央部の厚さt3よりも厚くすることで、はんだリフロー工程の際に、はんだがゲート電極パッド14の外にはみ出すことが抑制される。

20

【0078】

はんだがソース電極パッド12及びゲート電極パッド14の外にはみ出すことが抑制されることで、ソース電極とゲート電極の間のショートが抑制される。

【0079】

ソース電極パッド12の端部の厚さt2は、ソース電極パッド12の中央部の厚さt1の1.1倍以上1.5倍以下であることが好ましい。また、ゲート電極パッド14の端部の厚さt4は、ゲート電極パッド14の中央部の厚さt3の1.1倍以上1.5倍以下であることが好ましい。上記範囲を下回ると、ソース電極とゲート電極の間のショートが生じるおそれがある。また、上記範囲を上回るような形状を形成することは、製造上困難である。

30

【0080】

ソース電極パッド12及びゲート電極パッド14の端部の厚さは、例えば、電界めっき法でめっき膜を形成する際の、レジストパターンやめっき条件を調整することで制御される。

【0081】

また、第1の実施形態の半導体チップ10では、ドレイン電極13の端部の厚さt6は、ドレイン電極13の中央部の厚さt5と略同一であることが好ましい。これにより、ドレインリード21とドレイン電極13を接合する第1の接合層31の材料であるはんだをリフローする際に、はんだ中のガスの排出経路が塞がれにくい。よって、はんだの中にボイドが生じることが抑制される。

40

【0082】

半導体層11の端部には、ダイシングの際に生じた微小なクラックが存在する。仮に、微小なクラックが存在する領域にドレイン電極13が接すると、電極の応力により微小なクラックが拡張し、半導体チップ10の動作に影響を与え、信頼性が低下するおそれがある。

【0083】

第1の実施形態の半導体チップ10では、ドレイン電極13の端部は、半導体層11の

50

端部よりも所定の距離  $d_1$  だけ内側にあることが好ましい。これにより、微小なクラックが存在する領域にドレイン電極 13 は接しない。よって、半導体チップ 10 の動作の信頼性の低下が回避できる。

【0084】

また、第 1 の実施形態の半導体チップ 10 では、半導体チップ 10 の両面に厚い電極を備えることで、抗折強度が向上する。したがって、半導体層 11 の厚さを薄くして、MOSFET のオン抵抗を低減することが可能となる。

【0085】

以上、第 1 の実施形態によれば、信頼性を向上することが可能な半導体チップ 10 及び半導体パッケージ 100 が実現できる。

10

【0086】

(第 2 の実施形態)

第 2 の実施形態の半導体装置は、第 1 の電極パッド及び電極層が、鉄 (Fe)、コバルト (Co)、及び、ニッケル (Ni) から成る群から選ばれる少なくともいずれか一つの元素を含む点で、第 1 の実施形態と異なっている。以下、第 1 の実施形態と重複する内容については記述を省略する。

【0087】

第 2 の実施形態の半導体装置は、半導体チップ又は半導体モジュールである。半導体チップは、電力制御や電力供給に用いられるパワー半導体チップである。また、半導体パッケージは、半導体チップを含むパワー半導体パッケージである。

20

【0088】

第 2 の実施形態の半導体チップ及び半導体モジュールは、ソース電極パッド 12、ゲート電極パッド 14 及びドレイン電極 13 の材料の組成のみが、第 1 の実施形態の半導体チップ 10 及び半導体パッケージ 100 と異なる。

【0089】

第 2 の実施形態の半導体チップ及び半導体モジュールは、ソース電極パッド 12、ゲート電極パッド 14 及びドレイン電極 13 等の電極が銅を主成分とする金属であり、鉄 (Fe)、コバルト (Co)、及び、ニッケル (Ni) から成る群から選ばれる少なくともいずれか一つの添加元素を含む。

30

【0090】

図 6 は、第 2 の実施形態の半導体装置の電極の模式断面図である。図 6 は、ソース電極パッド 12、ゲート電極パッド 14 及びドレイン電極 13 の一部の模式断面図である。

【0091】

ソース電極パッド 12、ゲート電極パッド 14 及びドレイン電極 13 は、銅結晶 61 と、添加元素偏析領域 62 を含む。添加元素偏析領域 62 は、銅結晶の結晶粒界に存在する。添加元素は、銅の結晶粒界に偏析する。添加元素偏析領域 62 には、例えば、銅と添加元素との合金又は固溶体が形成されている。

【0092】

添加元素の含有量は、例えば、0.01 原子 % 以上 0.4 原子 % 以下である。ここで、添加元素の含有量は、添加元素と銅の合計量に対する添加元素の量の割合で定義される。

40

【0093】

次に、第 2 の実施形態の半導体装置の製造方法の一例について説明する。

【0094】

第 2 の実施形態の半導体装置の製造方法は、電解めっき法により、第 1 の金属膜及び第 2 の金属膜を形成する際に、電界めっき液中に、鉄イオン、コバルトイオン、及び、ニッケルイオンから成る群から選ばれる少なくともいずれか一つのイオンを添加する点で、第 1 の実施形態の半導体装置の製造方法と異なる。以下、第 1 の実施形態の半導体装置の製造方法と重複する内容については、一部記述を省略する。

【0095】

図 7 は、第 2 の実施形態の半導体装置の製造方法の説明図である。以下、添加元素が鉄

50

である場合を例に説明する。

【0096】

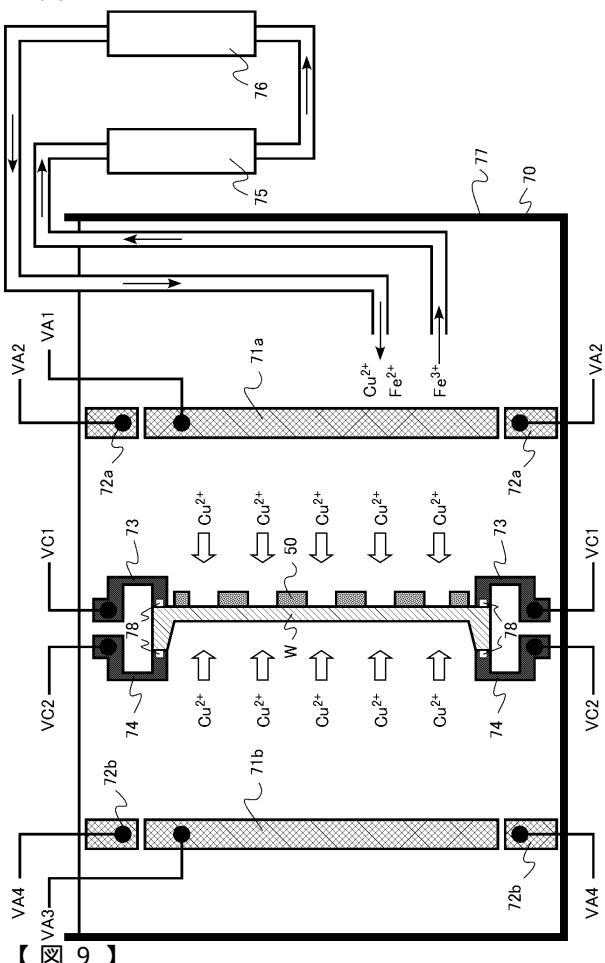

図7は、第2の実施形態の半導体装置の製造方法に用いられる電界めっき装置の構成を示す。電界めっき装置は、めっき槽70、第1の内部アノード電極71a、第1の外部アノード電極72a、第2の内部アノード電極71b、第2の外部アノード電極72b、表面カソード電極73、裏面カソード電極74、イオン濃度分析器75、銅イオン供給器76、押さえリング78を備える。めっき槽70には、めっき液77が貯留される。

【0097】

シリコン基板Wの表面のソース電極上、ゲート電極上及び裏面に銅めっき膜を形成するために、シリコン基板Wをカソードに固定する。カソードは、表面カソード電極73と裏面カソード電極74を有する。シリコン基板Wを、表面カソード電極73と裏面カソード電極74の間に固定する。

10

【0098】

シリコン基板Wの表面には、レジストパターン50が形成されている。レジストパターン50は、シリコン基板Wの表面のソース電極上、ゲート電極上が開口されている。

【0099】

表面カソード電極73と裏面カソード電極74には、異なるカソード電圧が印加可能である。シリコン基板Wの表面には、負電圧VC1を印加する。シリコン基板Wの裏面には、負電圧VC2を印加する。負電圧VC1と負電圧VC2は、直流電圧又は直流電圧にパルス波電圧を重畠した電圧を用いる。負電圧VC1と負電圧VC2は、表面と裏面に成膜する銅めっき膜の所望の膜厚を実現するために、適切な電圧となるように設定する。

20

【0100】

表面カソード電極73及び裏面カソード電極74と、シリコン基板Wとの間には、シリコン基板Wの端部に、めっき液が回り込まないように、押さえリング78が設けられる。押さえリング78の材質は、めっき液に対して耐性がある材料を選択する必要がある。

【0101】

シリコン基板Wの表面側のアノードは、第1の内部アノード電極71aと第1の外部アノード電極72aを有する。第1の内部アノード電極71aの径は、シリコン基板Wの径よりも大きい。第1の外部アノード電極72aは、第1の内部アノード電極71aの周囲にリング状に設けられている。

30

【0102】

第1の内部アノード電極71aには電圧VA1が印加され、第1の外部アノード電極72aには電圧VA2が印加される。シリコン基板Wの表面に成膜する銅めっき膜の面内分布が均一になるように、電圧VA1と電圧VA2が設定される。電圧VA1と電圧VA2は、カソードに対して正電位を有する。すなわち、カソードの電位よりもアノードの電位が高くなるようにする。電圧VA1と電圧VA2は、直流電圧又は直流電圧にパルス波電圧を重畠した電圧を用いる。

【0103】

シリコン基板Wの裏面側のアノードは、第2の内部アノード電極71bと第2の外部アノード電極72bを有する。第2の内部アノード電極71bの径は、シリコン基板Wの径よりも大きい。第2の外部アノード電極72bは、第2の内部アノード電極71bの周囲にリング状に設けられている。

40

【0104】

第2の内部アノード電極71bには電圧VA3が印加され、第2の外部アノード電極72bには電圧VA4が印加される。シリコン基板Wの表面に成膜する銅めっき膜の面内分布が均一になるように、電圧VA3と電圧VA4が設定される。電圧VA3と電圧VA4は、カソードに対して正電位を有する。すなわち、カソードの電位よりもアノードの電位が高くなるようにする。電圧VA3と電圧VA4は、直流電圧又は直流電圧にパルス波電圧を重畠した電圧を用いる。

【0105】

50

第2の内部アノード電極71bの電圧VA3は、第1の内部アノード電極71aの電圧VA1と異なる電圧とすることが可能である。また、第2の外部アノード電極72bの電圧VA4は、第1の内部アノード電極71aの電圧VA2と異なる電圧とすることが可能である。

【0106】

電圧VA1、電圧VA2、電圧VA3、電圧VA4は、表面と裏面に成膜する銅めっき膜の所望の膜厚を実現するために、適切な電圧となるように設定する。

【0107】

銅メッキ膜（以下、Cuめっき膜とも表記）への鉄（以下、Feとも表記）の添加は、銅めっき液（以下、Cuめっき液とも表記）の銅イオン（以下、Cu<sup>2+</sup>とも表記）に2価の鉄イオン（以下、Fe<sup>2+</sup>とも表記）を添加することにより行う。Cu<sup>2+</sup>がカソードに移動して、カソードから電子を受け取り、シリコン基板W上にCuめっき膜として析出する。一方、Fe<sup>2+</sup>はアノードの表面で電子をアノードに与えて3価の鉄イオン（以下、Fe<sup>3+</sup>とも表記）に変化する。同時に、カソード側ではFe<sup>2+</sup>がカソードの表面から電子を受け取り、FeとしてCuめっき膜中に混入する。

10

【0108】

Fe<sup>2+</sup>がFe<sup>3+</sup>となるとCuめっき液中のFe<sup>3+</sup>濃度が高くなる。Fe<sup>3+</sup>濃度が高くなると、Cuめっき膜の成膜速度が遅くなる。イオン濃度分析器75により、Cuめっき液中のFe<sup>3+</sup>濃度をモニタし、一定濃度に達すると、Fe<sup>3+</sup>は銅イオン供給器76に送られて、銅イオン供給器76の中にあるCuボールと反応する。反応の結果、Fe<sup>3+</sup>はFe<sup>2+</sup>となり、CuはCu<sup>2+</sup>になる。そして、銅イオン供給器76からめっき槽70の中に、Cu<sup>2+</sup>とFe<sup>2+</sup>が供給される。

20

【0109】

なお、銅メッキ膜へコバルト(Co)やニッケル(Ni)を添加する場合にも、鉄(Fe)と同様の方法で行うことが可能である。

【0110】

一度、電界めっき装置を用いてシリコン基板Wに銅メッキ膜を形成した後、次のシリコン基板Wに銅メッキ膜を形成する前に、電界めっき装置の洗浄を行う。

30

【0111】

電界めっき装置の洗浄に60以上100未満の水を用いることが好ましい。例えば、60以上100未満の水で洗浄した後、4以上30以下の水で洗浄する。洗浄に60以上100未満の水を用いることにより、洗浄に要する時間を短縮することが可能となる。

【0112】

特に、銅めっき液に鉄イオン、ニッケルイオン、コバルトイオンなどを添加した場合、60以上100未満の水を用いることで、洗浄効率が向上する。

【0113】

次に、第2の実施形態の半導体装置の作用及び効果について説明する。

【0114】

第2の実施形態の半導体チップ及び半導体モジュールは、ソース電極パッド12、ゲート電極パッド14及びドレイン電極13が、銅を主成分とし、鉄(Fe)、コバルト(Co)、及び、ニッケル(Ni)から成る群から選ばれる少なくともいずれか一つの添加元素を含む。

40

【0115】

銅を主成分とする電極が、鉄、コバルト又はニッケルを添加元素として含むことにより、電極の応力が低下する。

【0116】

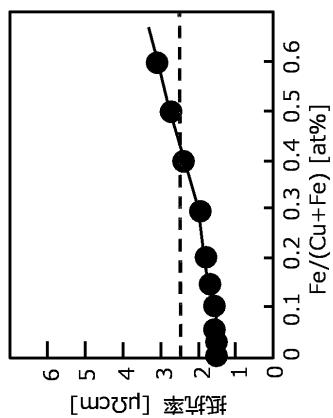

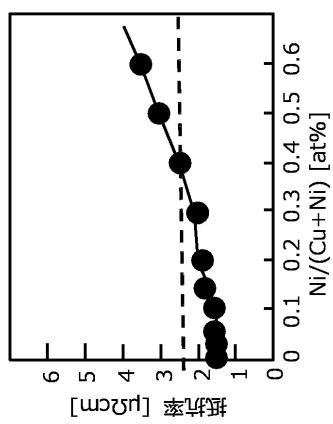

図8は、第2の実施形態の半導体装置の作用及び効果の説明図である。図8(a)は、銅膜の引張応力と銅膜中の鉄(Fe)の含有量との関係を示す。図8(b)は、銅膜の抵抗率と鉄の含有量との関係を示す。鉄の含有量は、銅膜中の鉄と銅の合計量に対する鉄の

50

量の割合 ( $Fe / (Cu + Fe)$ ) で定義される。

【0117】

図 8 (a) から明らかなように、鉄を 0.01 原子%以上で添加することで銅膜の引張応力が 15 MP 以下となる。また、鉄を 0.02 原子%以上で添加することで銅膜の引張応力が 10 MP 以下となる。鉄の添加により銅の結晶粒成長が抑制され、引張応力が低下すると考えられる。

【0118】

一方、図 8 (b) から明らかなように、鉄を添加することで、銅膜の抵抗率は上昇する。鉄の添加量が 0.4 原子%以下であれば、銅膜の抵抗率は  $2.5 \mu cm$  以下となる。鉄の添加量が 0.3 原子%以下であれば、銅膜の抵抗率は  $2 \mu cm$  以下となる。

10

【0119】

第 2 の実施形態の半導体チップ及び半導体モジュールは、電極の銅膜中に鉄を添加元素として含有することにより、電極の応力が低減する。したがって、半導体チップ 10 に厚い銅を主成分とする電極を設けたとしても、半導体チップの反りが抑制される。よって、半導体チップ 10 の信頼性が向上する。

【0120】

電極を形成する銅膜中の鉄の含有率は、0.01 原子%以上 0.4 原子%以下であることが好ましく、0.02 原子%以上 0.3 原子%以下であることがより好ましい。上記範囲を下回ると、応力の低減効果が十分に得られないおそれがある。上記範囲を上回ると抵抗率が大きくなりすぎオン抵抗が許容範囲を超えるおそれがある。

20

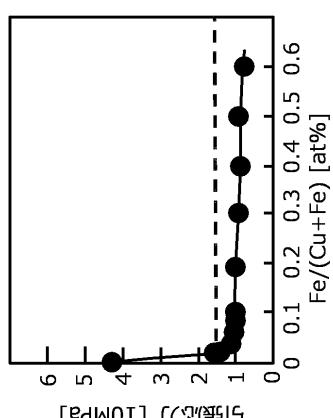

【0121】

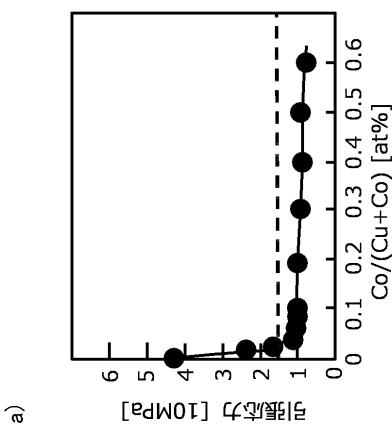

図 9 は、第 2 の実施形態の半導体装置の作用及び効果の説明図である。図 9 (a) は、銅膜の引張応力と銅膜中のコバルト (Co) の含有量との関係を示す。図 9 (b) は、銅膜の抵抗率とコバルトの含有量との関係を示す。コバルトの含有量は、銅膜中のコバルトと銅の合計量に対するコバルトの量の割合 ( $Co / (Cu + Co)$ ) で定義される。

【0122】

図 9 (a) から明らかなように、コバルトを 0.02 原子%以上で添加することで銅膜の引張応力が 15 MP 以下となる。また、コバルトを 0.025 原子%以上で添加することで銅膜の引張応力が 10 MP 以下となる。コバルトの添加により銅の結晶粒成長が抑制され、引張応力が低下すると考えられる。

30

【0123】

一方、図 9 (b) から明らかなように、コバルトを添加することで、銅膜の抵抗率は上昇する。コバルトの添加量が 0.25 原子%以下であれば、銅膜の抵抗率は  $2.5 \mu cm$  以下となる。コバルトの添加量が 0.2 原子%以下であれば、銅膜の抵抗率は  $2 \mu cm$  以下となる。

30

【0124】

第 2 の実施形態の半導体チップ及び半導体モジュールは、電極の銅膜中にコバルトを添加元素として含有することにより、電極の応力が低減する。したがって、半導体チップ 10 に厚い銅を主成分とする電極を設けたとしても、半導体チップの反りが抑制される。よって、半導体チップ 10 の信頼性が向上する。

40

【0125】

電極を形成する銅膜中のコバルトの含有率は、0.02 原子%以上 0.25 原子%以下であることが好ましく、0.025 原子%以上 0.2 原子%以下であることがより好ましい。上記範囲を下回ると、応力の低減効果が十分に得られないおそれがある。上記範囲を上回ると抵抗率が大きくなりすぎオン抵抗が許容範囲を超えるおそれがある。

【0126】

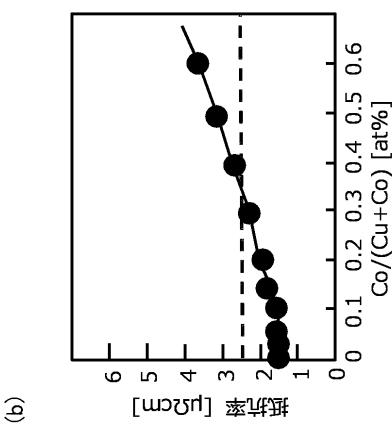

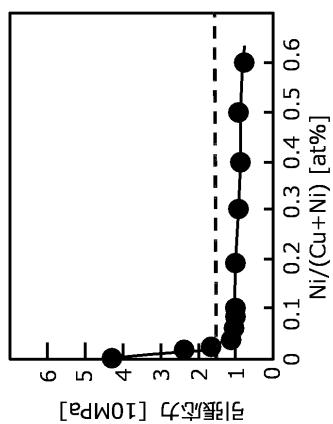

図 10 は、第 2 の実施形態の半導体装置の作用及び効果の説明図である。図 10 (a) は、銅膜の引張応力と銅膜中のニッケル (Ni) の含有量との関係を示す。図 10 (b) は、銅膜の抵抗率とニッケルの含有量との関係を示す。ニッケルの含有量は、銅膜中のニッケルと銅の合計量に対するニッケルの量の割合 ( $Ni / (Cu + Ni)$ ) で定義される

50

。

## 【0127】

図10(a)から明らかなように、ニッケルを0.02原子%以上で添加することで銅膜の引張応力が15MP以下となる。また、ニッケルを0.025原子%以上で添加することで銅膜の引張応力が10MP以下となる。ニッケルの添加により銅の結晶粒成長が抑制され、引張応力が低下すると考えられる。

## 【0128】

一方、図10(b)から明らかなように、ニッケルを添加することで、銅膜の抵抗率は上昇する。ニッケルの添加量が0.4原子%以下であれば、銅膜の抵抗率は $2.5 \mu \Omega \cdot cm$ 以下となる。ニッケルの添加量が0.3原子%以下であれば、銅膜の抵抗率は $2 \mu \Omega \cdot cm$ 以下となる。

## 【0129】

第2の実施形態の半導体チップ及び半導体モジュールは、電極の銅膜中にニッケルを添加元素として含有することにより、電極の応力が低減する。したがって、半導体チップ10に厚い銅を主成分とする電極を設けたとしても、半導体チップの反りが抑制される。よって、半導体チップ10の信頼性が向上する。

## 【0130】

電極を形成する銅膜中のニッケルの含有率は、0.02原子%以上0.4原子%以下であることが好ましく、0.025原子%以上0.3原子%以下であることがより好ましい。上記範囲を下回ると、応力の低減効果が十分に得られないおそれがある。上記範囲を上回ると抵抗率が大きくなりすぎオン抵抗が許容範囲を超えるおそれがある。

## 【0131】

添加元素として、鉄、ニッケル、コバルトは、いずれも同様の効果を奏するが、引張応力と抵抗率の最適化を図る観点からは、鉄が最も添加元素として好ましく、ニッケルが次に好ましく、コバルトがその次に好ましい。

## 【0132】

以上、第2の実施形態によれば、第1の実施形態と比較して、電極の応力が低減することで更に信頼性を向上することが可能な半導体チップ及び半導体パッケージが実現できる。

## 【0133】

## (第3の実施形態)

第3の実施形態の半導体装置は、銅(Cu)を主成分とし、鉄(Fe)、コバルト(Co)、及び、ニッケル(Ni)から成る群から選ばれる少なくともいずれか一つの元素を含み、厚さが $5 \mu m$ 以上 $50 \mu m$ 未満の第1の電極バッドと、電極層と、第1の電極バッドと電極層との間に設けられた半導体層と、を備える。

## 【0134】

第3の実施形態の半導体装置は、半導体チップの片面のみに厚い銅を主成分とする電極が設けられる点で第2の実施形態と異なっている。以下、第1の実施形態及び第2の実施形態と重複する内容については記述を省略する。

## 【0135】

第3の実施形態の半導体装置は、半導体チップ30又は半導体モジュールである。半導体チップ30は、電力制御や電力供給に用いられるパワー半導体チップである。また、半導体パッケージは、半導体チップ30を含むパワー半導体パッケージである。

## 【0136】

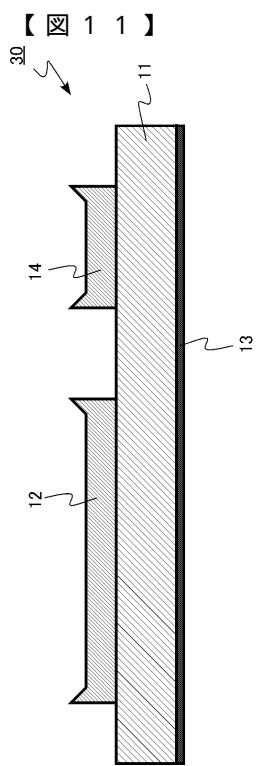

図11は、第3の実施形態の半導体装置の模式断面図である。図11は、半導体チップ30の模式断面図である。

## 【0137】

半導体層11は、単結晶の半導体である。半導体層11は、例えば、単結晶シリコン、単結晶炭化珪素(SiC)、単結晶窒化物半導体である。

## 【0138】

10

20

30

40

50

半導体層11は、ソース電極パッド12とドレイン電極13との間に設けられる。半導体層11は、ゲート電極パッド14とドレイン電極13との間に設けられる。

【0139】

ソース電極パッド12は、銅を主成分とする金属である。ソース電極パッド12は、鉄(Fe)、コバルト(Co)、及び、ニッケル(Ni)から成る群から選ばれる少なくともいすれか一つの添加元素を含む。ソース電極パッド12の厚さは、5μm以上50μm未満である。

【0140】

ゲート電極パッド14は、銅を主成分とする金属である。ゲート電極パッド14は、鉄(Fe)、コバルト(Co)、及び、ニッケル(Ni)から成る群から選ばれる少なくともいすれか一つの添加元素を含む。ゲート電極パッド14の厚さは、5μm以上50μm未満である。

10

【0141】

ドレイン電極13は、金属、金属化合物又は金属半導体化合物である。ドレイン電極13は、例えば、銅、ニッケル、チタン、窒化チタン、ニッケルシリサイド又はチタンシリサイドである。ドレイン電極13の厚さは、0.1μm以上2μm以下である。

20

【0142】

ソース電極パッド12と半導体層11との間には、例えば、図示しないソース電極が設けられる。ソース電極は、例えば、銅と異なる金属である。ソース電極は、例えば、アルミニウムを主成分とする金属である。

20

【0143】

ソース電極とソース電極パッド12との間には、例えば、図示しないバリアメタル層が設けられる。バリアメタル層は、例えば、金属又は金属窒化物である。バリアメタル層は、例えば、チタン、タンタル、窒化チタン、窒化タンタル、窒化タンクスチタンである。

30

【0144】

なお、半導体層11の上に、ソース電極を介さずに、ソース電極パッド12が設けられても構わない。この場合、例えば、半導体層11とソース電極パッド12との間に、図示しないバリアメタル層が設けられる。バリアメタル層は、例えば、金属又は金属窒化物である。バリアメタル層は、例えば、チタン、タンタル、窒化チタン、窒化タンタル、窒化タンクスチタンである。

30

【0145】

ゲート電極パッド14と半導体層11との間には、例えば、図示しないゲート電極が設けられる。ゲート電極は、例えば、多結晶半導体である。ゲート電極は、例えば、多結晶シリコンである。

40

【0146】

ゲート電極とゲート電極パッド14との間には、例えば、図示しないバリアメタル層が設けられる。バリアメタル層は、例えば、金属又は金属窒化物である。バリアメタル層は、例えば、チタン、タンタル、窒化チタン、窒化タンタル、窒化タンクスチタンである。

【0147】

次に、第3の実施形態の半導体装置の製造方法の一例について説明する。

40

【0148】

第3の実施形態の半導体装置の製造方法は、第1の面と第2の面とを有する半導体基板の第1の面の側にレジストパターンを形成し、電界めっき装置を用い電解めっき法により、第1の面の側に銅(Cu)を主成分とし厚さが5μm以上50μm未満の金属膜を形成する。電解めっき法により、金属膜を形成する際に、電界めっき液中に、鉄イオン、コバルトイオン、及び、ニッケルイオンから選ばれる少なくともいすれか一つのイオンを添加する。以下、第1の実施形態と重複する内容については記述を一部省略する。

【0149】

図12、図13は、第3の実施形態の半導体装置の製造方法を示す図である。図12(a)は、製造途中の半導体装置の上面図、図12(b)は図12(a)のD'D'断面図で

50

ある。図13は、製造途中の半導体装置の断面図である。

【0150】

シリコン基板Wに、複数のMOSFET101を形成する(図12(a))。シリコン基板Wは、半導体基板の一例である。シリコン基板Wは、第1の面P1と第2の面P2を有する。以下、第1の面P1を表面、第2の面P2を裏面と称する。シリコン基板Wの厚さは、例えば、750μmである。

【0151】

MOSFET101の間には、後に、ダイシングにより個片化するための所定の幅を有するダイシングライン102が設けられる。ウェハWの表面には、図示しない酸化シリコン膜とポリイミド膜の積層保護膜が形成されている。

10

【0152】

積層保護膜の開口部に、図示しないソース電極とゲート電極とが露出する。ソース電極とゲート電極とは、アルミニウムを主成分とする金属である。ダイシングライン102上では、積層保護膜が除去されシリコン基板Wが露出している。

【0153】

シリコン基板Wの表面に、図示しないバリアメタル層とシード層を形成する。バリアメタル層とシード層はPVD法により堆積する。例えば、バリアメタル層は厚さ150nmのチタン、シード層は厚さ500nmの銅である。

20

【0154】

次に、リソグラフィ法を用いて、シリコン基板Wの表面に、レジストパターン50を形成する(図13(a))。レジストの膜厚は、例えば、25μmである。レジストパターン50は、シリコン基板Wの表面のソース電極上、ゲート電極上が開口されている。

【0155】

次に、電界めっき装置を用いた電解めっき法により、シリコン基板Wの表面のソース電極上、ゲート電極上に、例えば、厚さ20μmの銅めっき膜51を形成する(図13(b))。銅めっき膜51は、ソース電極パッド12及びゲート電極パッド14となる。銅めっき膜51は、鉄(Fe)、コバルト(Co)、及び、ニッケル(Ni)から成る群から選ばれる少なくともいずれか一つの添加元素を含む。

【0156】

図14は、第3の実施形態の半導体装置の製造方法の説明図である。図14は、電界めっき装置を用いた添加元素を含む銅めっき膜51の製造方法の説明図である。以下、添加元素が鉄である場合を例に説明する。

30

【0157】

図14は、第3の実施形態の半導体装置の製造方法に用いられる電界めっき装置の構成を示す。電界めっき装置は、めっき槽70、内部アノード電極71、外部アノード電極72、表面カソード電極73、裏面カソード電極74、イオン濃度分析器75、銅イオン供給器76、押さえリング78を備える。めっき槽70には、めっき液77が貯留される。

【0158】

表面カソード電極73と裏面カソード電極74には、同一の負電圧VCを印加する。めっき槽70には、銅めっき液の銅イオンに2価の鉄イオンを添加する。その他の銅めっき膜51の製造方法は、第2の実施形態と同様である。

40

【0159】

次に、シリコン基板Wの表面のレジストパターン50を有機溶剤で除去する(図13(c))。次に、シリコン基板Wの表面のレジストパターン50で覆われていた銅のシード層を除去する。次に、水酸化カリウム過酸化水素水溶液を用いてチタンのバリアメタル層を除去する。シード層とバリアメタル層を除去することにより、ソース電極パッド12とゲート電極パッド14とを電気的に分離する。

【0160】

次に、シリコン基板Wの表面に図示しない支持材を設け、シリコン基板Wの裏面を研削することによりシリコン基板Wを薄くする(図13(d))。

50

## 【0161】

次に、シリコン基板Wの裏面に、チタン膜とニッケル膜の積層膜をスパッタ法により形成する(図13(e))。積層膜は、ドレイン電極13となる。

## 【0162】

次に、シリコン基板Wの裏面側にダイシングシートを張り付ける。次に、シリコン基板Wの表面の支持材を除去する。

## 【0163】

次に、ブレードダイシングを用いて、シリコン基板Wをダイシングライン102に沿って切断し、複数のMOSFET101を分離し、複数の半導体チップ30とする(図13(f))。なお、ブレードダイシングに代えて、レーザダイシングやプラズマダイシングを用いることも可能である。

10

## 【0164】

以上の製造方法により、第3の実施形態の半導体チップ30が製造される。

## 【0165】

第3の実施形態の半導体チップ及び半導体パッケージによれば、銅を主成分とする電極の応力が、鉄、コバルト又はニッケルを添加元素として含むことにより、低下する。したがって、半導体チップ30の片側のみに厚い銅を主成分とする電極を設けたとしても、半導体チップの反りが抑制される。よって、半導体チップ30の信頼性が向上する。

## 【0166】

更に応力を抑制する観点から、ソース電極パッド12の厚さ及びゲート電極パッド14の厚さは、30μm以下であることが好ましく、20μm以下であることがより好ましい。

20

## 【0167】

以上、第3の実施形態によれば、電極の応力が低減することで信頼性を向上することが可能な半導体チップ及び半導体パッケージが実現できる。

## 【0168】

第1ないし第3の実施形態では、半導体チップとしてMOSFETを用いる場合を例に説明したが、半導体チップはこれらに限定されるものではない。例えば、半導体チップの上下間に電流が流れる半導体チップであれば、IGBT(Insulated Gate Bipolar Transistor)、SBD(Schottky Barrier Diode)、PINダイオードなど、その他のパワートランジスタやパワーダイオードを適用することも可能である。

30

## 【0169】

また、第1ないし第3の実施形態では、1個の半導体チップが封止された半導体パッケージを例に説明したが、複数の同種又は異種の半導体チップが封止された半導体モジュールに本発明を適用することも可能である。

## 【0170】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。例えば、一実施形態の構成要素を他の実施形態の構成要素と置き換え又は変更してもよい。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

40

## 【符号の説明】

## 【0171】

10 半導体チップ(半導体装置)

11 半導体層

12 ソース電極パッド(第1の電極パッド)

13 ドレイン電極(電極層)

50

|       |                     |

|-------|---------------------|

| 1 4   | ゲート電極パッド (第2の電極パッド) |

| 3 0   | 半導体チップ (半導体装置)      |

| 5 0   | レジストパターン            |

| 1 0 0 | 半導体パッケージ (半導体装置)    |

| 1 0 2 | ダイシングライン            |

| P 1   | 第1の面                |

| P 2   | 第2の面                |

| W     | 半導体基板               |

【図4】

【図6】

【図 7】

【図 9】

【図 8】

(b)

【図 10】

(b)

(b)

(a)

(a)

【図 1 2】

【図 1 4】

## フロントページの続き

|                         |              |            |

|-------------------------|--------------|------------|

| (51) Int.CI.            | F I          | テーマコード(参考) |

| H 01 L 29/423 (2006.01) | H 01 L 29/58 | G          |

| H 01 L 29/49 (2006.01)  |              |            |

(72)発明者 須黒 恭一

東京都港区芝浦一丁目1番1号 東芝デバイス&ストレージ株式会社内

F ターム(参考) 4M104 AA01 AA03 BB01 BB02 BB04 BB14 BB17 BB30 BB32 BB33

BB37 BB38 BB39 CC01 CC03 CC05 DD23 DD33 DD52 DD64

DD71 DD94 FF02 FF06 FF17 FF18 FF26 FF27 GG03 GG09

GG18 HH15 HH20