(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6785738号

(P6785738)

(45) 発行日 令和2年11月18日(2020.11.18)

(24) 登録日 令和2年10月29日(2020.10.29)

(51) Int.Cl.

G06F 12/00 (2006.01)

F 1

G 06 F 12/00 5 6 O F

請求項の数 9 (全 23 頁)

(21) 出願番号 特願2017-193447 (P2017-193447)

(22) 出願日 平成29年10月3日 (2017.10.3)

(65) 公開番号 特開2018-73452 (P2018-73452A)

(43) 公開日 平成30年5月10日 (2018.5.10)

審査請求日 令和2年9月9日 (2020.9.9)

(31) 優先権主張番号 62/414,426

(32) 優先日 平成28年10月28日 (2016.10.28)

(33) 優先権主張国・地域又は機関

米国(US)

(31) 優先権主張番号 15/425,996

(32) 優先日 平成29年2月6日 (2017.2.6)

(33) 優先権主張国・地域又は機関

米国(US)

早期審査対象出願

(73) 特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路129

129, Samsung-ro, Yeongtong-gu, Suwon-si, Gyeonggi-do, Republic

of Korea

(74) 代理人 110000051

特許業務法人共生国際特許事務所

(72) 発明者 季 双 辰

アメリカ合衆国, 93117, カリフォルニア州, ゴレタ, コレヒオ ロード, アパート #1302, 6510

最終頁に続く

(54) 【発明の名称】DRAM基盤のプロセシングユニット

## (57) 【特許請求の範囲】

## 【請求項1】

D P U ( D y n a m i c R a n d o m A c c e s s M e m o r y P r o c e s s i n g U n i t ) であって、

少なくとも 3 以上である第 1 の所定の数のカラム及び 3 以上である第 2 の所定の数のローを有するアレイ内に配置された複数の DRAM 基盤のコンピューティングセルを含む少なくとも 1 つのコンピューティングセルアレイを備え、

前記カラムの各々は、前記カラムの第 1 ロー及び第 2 ロー上で動作するロジック機能を提供し、前記カラムの第 3 ロー内に前記ロジック機能の結果を格納するように構成され、

前記少なくとも 1 つのコンピューティングセルアレイは、前記第 1 の所定の数の 2 倍である第 3 の所定の数のシフトラインを更に含み、

前記シフトラインの各々は、少なくとも 1 つの対応する第 1 のトランジスタを介して前記コンピューティングセルのカラムに連結され、

前記シフトライン及び前記対応する第 1 のトランジスタは、前記少なくとも 1 つのコンピューティングセルアレイ内において、選択されたカラムの 2 つのローのコンピューティングセルの内容を少なくとも 2 つのカラムで右方向又は左方向にシフトするように構成されることを特徴とする D P U 。

## 【請求項2】

前記第 1 の所定の数のカラム内に配置された少なくとも 1 つの DRAM 基盤のメモリセルを含む少なくとも 1 つのデータセルアレイと、

10

20

前記コンピューティングセルのカラムの各々に連結されたセンスアンプと、を更に含み

前記少なくとも1つのデータセルアレイのDRAM基盤のメモリセルのカラムの各々は、対応するコンピューティングセルアレイのカラムに対応し、

前記センスアンプは、前記コンピューティングセルのカラムの読み出しビットラインに電気的に連結される入力、及び前記コンピューティングセルのカラムの書き込みビットラインに電気的に連結される出力を含むことを特徴とする請求項1に記載のDPU。

**【請求項3】**

DPU(Dynamic Random Access Memory Processsing Unit)であって、

10

少なくとも3以上である第1の所定の数のカラム及び3以上である第2の所定の数のローを有するアレイ内に配置された複数のDRAM基盤のコンピューティングセルを含む少なくとも1つのコンピューティングセルアレイと、

前記第1の所定の数のカラム及び少なくとも1つのロー内に配置された少なくとも1つのDRAM基盤のメモリセルを含む少なくとも1つのデータセルアレイと、を備え、

前記カラムの各々は、前記カラムの第1ロー及び第2ロー上で動作するロジック機能を提供し、前記カラムの第3ロー内に前記ロジック機能の結果を格納するように構成され、

前記少なくとも1つのコンピューティングセルアレイは、前記第1の所定の数の2倍である第3の所定の数のシフトラインを更に含み、

前記シフトラインの各々は、少なくとも1つの対応する第1のトランジスタを介して前記コンピューティングセルのカラムに連結され、

20

前記シフトライン及び前記対応する第1のトランジスタは、前記少なくとも1つのコンピューティングセルアレイ内において、選択されたカラムの2つのローのコンピューティングセルの内容を少なくとも2つのカラムで右方向又は左方向にシフトするように構成され、

前記少なくとも1つのデータセルアレイのDRAM基盤のメモリセルのカラムの各々は、対応するコンピューティングセルアレイのカラムに対応することを特徴とするDPU。

**【請求項4】**

DPU(Dynamic Random Access Memory Processsing Unit)であって、

30

3以上である第1の所定の数のカラム及び少なくとも1つのロー内に配置された少なくとも1つのDRAM基盤のメモリセルを含む少なくとも1つのデータセルアレイと、

複数のDRAM基盤のコンピューティングセルを含む少なくとも1つのコンピューティングセルアレイと、

前記コンピューティングセルのカラムの各々に連結されたセンスアンプと、

前記コンピューティングセルの各々に電気的に連結されるデコーダーと、を備え、

前記コンピューティングセルアレイの各々は、前記データセルアレイの各々に対応し、前記第1の所定の数のカラム及び3以上である第2の所定の数のローを有するアレイ内に配置され、

前記コンピューティングセルのカラムの各々は、前記コンピューティングセルのカラムの第1ロー及び第2ロー上で動作するロジック機能を提供し、前記コンピューティングセルのカラムの第3ロー内に前記ロジック機能の結果を格納するように構成され、

40

前記少なくとも1つのコンピューティングセルアレイは、前記第1の所定の数の2倍である第3の所定の数のシフトラインを更に含み、

前記シフトラインの各々は、少なくとも1つの対応する第1のトランジスタを介して前記コンピューティングセルのカラムに連結され、

前記シフトライン及び前記対応する第1のトランジスタは、前記少なくとも1つのコンピューティングセルアレイ内において、選択されたカラムの2つのローのコンピューティングセルの内容を少なくとも2つのカラムで右方向又は左方向にシフトするように構成され、

50

前記センスアンプの各々は、前記コンピューティングセルのカラム内の前記コンピューティングセルのカラムの読み出しビットラインに電気的に連結される入力、及び前記コンピューティングセルのカラムの前記コンピューティングセルのカラムの書き込みビットラインに電気的に連結される出力を含み、

前記デコーダーは、前記カラムのコンピューティングセルを選択するための命令に対応するD R A M基盤のアドレス信号を受信して前記カラムの第1ロー及び第2ロー上で前記ロジック機能を生成し、前記カラムの第3ロー内に前記ロジック機能の結果を格納することを特徴とするD P U。

**【請求項5】**

少なくとも1つのカラムの前記D R A M基盤のコンピューティングセルの各々は、3つのトランジスタ及び1つのキャパシターを含むD R A Mメモリセルを含むことを特徴とする請求項1、3、又は4に記載のD P U。 10

**【請求項6】**

少なくとも1つのカラムの前記D R A M基盤のコンピューティングセルは、N O Rロジック機能を提供することを特徴とする請求項5に記載のD P U。

**【請求項7】**

少なくとも1つのカラムの前記D R A M基盤のコンピューティングセルの各々は、1つのトランジスタ及び1つのキャパシターを含むD R A Mメモリセルを含むことを特徴とする請求項1、3、又は4に記載のD P U。

**【請求項8】**

前記D R A M基盤のコンピューティングセルの各々は、前記D R A M基盤のコンピューティングセルのビットラインに連結されたA L U(A r i t h m e t i c L o g i c U n i t)を更に含み、 20

前記A L Uは、前記ロジック機能を提供することを特徴とする請求項7に記載のD P U。

**【請求項9】**

前記A L Uは、N O Rロジック機能を提供することを特徴とする請求項8に記載のD P U。

**【発明の詳細な説明】**

30

**【技術分野】**

**【0 0 0 1】**

本発明は、メモリシステムに関し、より詳細には、D R A M基盤のプロセシングユニットに関する。

**【背景技術】**

**【0 0 0 2】**

一般的に、G P U(G r a p h i c s P r o c e s s i n g U n i t)及びT P U(T e n s o r P r o c e s s i n g U n i t)がディープラーニング(deep learning)プロセシングのために使用される。ディープラーニングプロセシングはG P U又はT P Uによって効率的に処理できない高度に並列化されたプロセシングを含む。 40

**【先行技術文献】**

**【特許文献】**

**【0 0 0 3】**

**【特許文献1】**米国特許第5,901,095号明細書

**【特許文献2】**米国特許第6,035,384号明細書

**【特許文献3】**米国特許第6,195,738号明細書

**【特許文献4】**米国特許第7,299,099号明細書

**【特許文献5】**米国特許第8,042,082号明細書

**【特許文献6】**米国特許第9,136,872号明細書

50

- 【特許文献 7】米国特許第 9 , 197 , 285 号明細書

【特許文献 8】米国特許第 9 , 317 , 482 号明細書

【特許文献 9】米国特許第 9 , 378 , 181 号明細書

【特許文献 10】米国特許出願公開第 2007 / 0226567 号明細書

【特許文献 11】米国特許出願公開第 2011 / 0302366 号明細書

【特許文献 12】米国特許出願公開第 2012 / 0246380 号明細書

【特許文献 13】米国特許出願公開第 2015 / 0089166 号明細書

【特許文献 14】米国特許出願公開第 2015 / 0131383 号明細書

【特許文献 15】米国特許出願公開第 2016 / 0147667 号明細書

【特許文献 16】米国特許出願公開第 2016 / 0173102 号明細書 10

【特許文献 17】欧州特許出願公開第 1193502 号明細書

【特許文献 18】欧州特許出願公開第 2523352 号明細書

【非特許文献】

【0004】

【非特許文献 1】MATAM, Kiran et al., "Energy-Efficient Large-Scale Matrix Multiplication on FPGAs", 2013 International Conference on Reconfigurable Computing and FPGAs (ReConfig), December 9-11, 2013 (8 pages).

【非特許文献 2】NODA, Hideyuki et al., "A cost-efficient high-performance dynamic TCAM with pipelined hierarchical searching and shift redundancy architecture", IEEE Journal of Solid-State Circuits, Vol. 40, No. 1, January 3, 2005 (10 pages). 20

【非特許文献 3】SESHADRI, Vivek et al., "Fast Bulk Bitwise AND and OR in DRAM", IEEE Computer Architecture Letters, Vol. 14, No. 2, May 18, 2015 (6 pages).

【非特許文献 4】SESHADRI, Vivek et al., "RowClone: Fast and Energy-Efficient In-DRAM Bulk Data Copy and Initialization", MICRO-46, Proc. of 46th IEEE/ACM Int. Symp. on Microarchitecture, December 7, 2013, pp. 185-197. 30

【非特許文献 5】WANG, Gesan et al., "TCAM-Based Forwarding Engine with Minimum Independent Prefix Set (MIPS) for Fast Updating", 2006 IEEE International Conference on Communications, June 11-15, 2006 (7 pages).

【発明の概要】 40

【発明が解決しようとする課題】

【0005】

本発明は、上記従来技術に鑑みてなされたものであって、本発明の目的は、DRAM基盤のプロセシングユニットを提供することにある。

【課題を解決するための手段】

【0006】

上記目的を達成するためになされた本発明の一態様による DPU (Dynamic Random Access Memory Processing Unit) は、少なくとも 1 つのカラムを含むアレイ内に配置された複数の DRAM 基盤のコンピューティングセルを含む少なくとも 1 つのコンピューティングセルアレイを備え、前記少なくとも 1 50

つのカラムは、少なくとも 3 つのローの D R A M 基盤のコンピューティングセルを含み、前記少なくとも 3 つのローの D R A M 基盤のコンピューティングセルは、前記少なくとも 3 つのローの第 1 ロー及び第 2 ロー上で動作するロジック機能を提供し、前記少なくとも 3 つのローの第 3 ロー内に前記ロジック機能の結果を格納する。

#### 【 0 0 0 7 】

上記目的を達成するためになされた本発明の他の態様による D P U ( D y n a m i c R a n d o m A c c e s s M e m o r y P r o c e s s i n g U n i t ) は、少なくとも 1 つのカラムを含むアレイ内に配置された複数の D R A M 基盤のコンピューティングセルを含む少なくとも 1 つのコンピューティングセルアレイと、少なくとも 1 つのカラム内に配置された少なくとも 1 つの D R A M 基盤のメモリセルを含む少なくとも 1 つのデータセルアレイと、を備え、前記少なくとも 1 つのカラムは、少なくとも 3 つのローの D R A M 基盤のコンピューティングセルを含み、前記少なくとも 3 つのローの D R A M 基盤のコンピューティングセルは、前記少なくとも 3 つのローの第 1 ロー及び第 2 ロー上で動作するロジック機能を提供し、前記少なくとも 3 つのローの第 3 ロー内に前記ロジック機能の結果を格納する。10

#### 【 0 0 0 8 】

上記目的を達成するためになされた本発明の更に他の態様による D P U ( D y n a m i c R a n d o m A c c e s s M e m o r y P r o c e s s i n g U n i t ) は、少なくとも 1 つのカラム内に配置された少なくとも 1 つの D R A M 基盤のメモリセルを含む少なくとも 1 つのデータセルアレイと、少なくとも 3 つのローの D R A M 基盤のコンピューティングセルを含む少なくとも 1 つのカラムを含むアレイ内に配置された複数の D R A M 基盤のコンピューティングセルを含む少なくとも 1 つのコンピューティングセルアレイと、前記少なくとも 3 つのローの D R A M 基盤のコンピューティングセルの読み出しビットラインに電気的に連結された入力、及び前記少なくとも 3 つのローの D R A M 基盤のコンピューティングセルの書き込みビットラインに電気的に連結された出力を含むセンスアンプと、前記少なくとも 3 つのローの D R A M 基盤のコンピューティングセルに電気的に連結されたデコーダーと、を備え、前記少なくとも 3 つのローの D R A M 基盤のコンピューティングセルは、前記少なくとも 3 つのローの第 1 ロー及び第 2 ロー上で動作するロジック機能を提供し、前記少なくとも 3 つのローの第 3 ロー内に前記ロジック機能の結果を格納し、前記デコーダーは、前記第 1 ロー及び第 2 ロー上で前記ロジック機能を生成し、前記第 3 ロー内に前記ロジック機能の結果を格納するために、前記少なくとも 3 つのローの D R A M 基盤のコンピューティングセルを選択するための命令に対応する D R A M 基盤のアドレス信号を受信する。20

#### 【 発明の効果 】

#### 【 0 0 0 9 】

本発明によれば、多様な動作に対してプログラム可能且つ再構成可能な D P U を提供することができる。また高性能、エネルギー効率的、低価格のシステムを提供することができる。

#### 【 図面の簡単な説明 】

#### 【 0 0 1 0 】

【 図 1 】本発明の一実施形態による D P U の一例を示すブロック図である。

【 図 2 A 】コンピューティングセルアレイ内のコンピューティングセルに対して使用される 3 つのトランジスタ及び 1 つのキャパシターによる D R A M コンピューティングセルトポグラフィの一例を示す図である。

【 図 2 B 】コンピューティングセルアレイ内のコンピューティングセルに対して使用される 1 つのトランジスタ及び 1 つのキャパシターによる D R A M コンピューティングセルトポグラフィの他の例を示す図である。

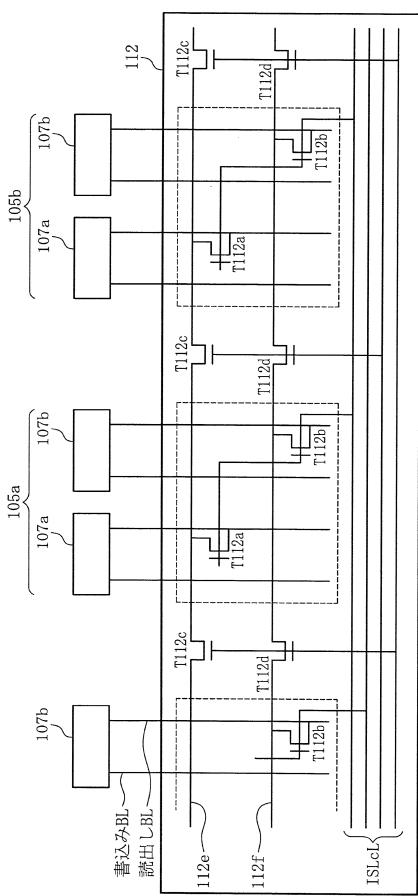

#### 【 図 3 】本発明の一実施形態によるイントラマットシフトアレイの一例を示す図である。

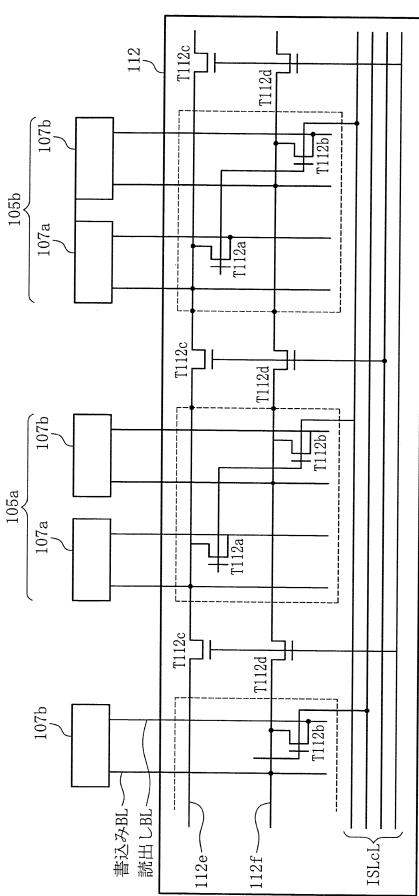

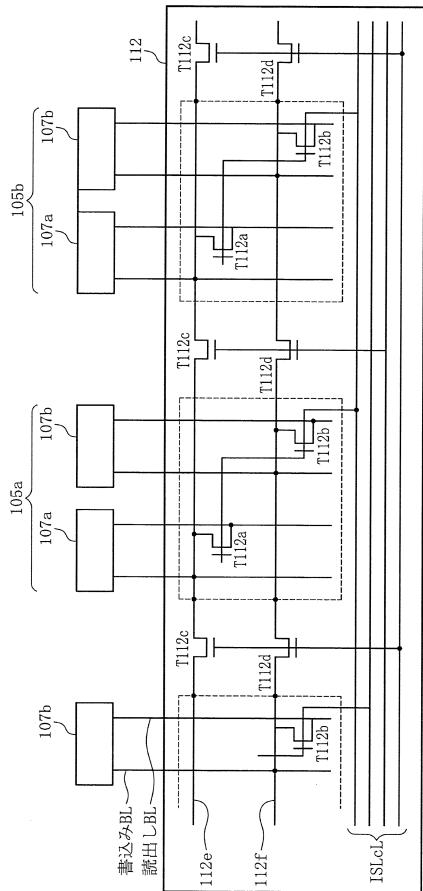

【 図 4 A 】本発明の一実施形態によるインターマットシフトアレイの一例を示す図である。40

【図4B】本発明の一実施形態による左側のインターマットシフトに対する隣接するコンピューティングセルカラムで同様に配置された2つのコンピューティングセル間のインターマットシフトインターネクション構成を概念的に示す図である。

【図4C】本発明の一実施形態による左側のインターマットシフトに対する隣接するコンピューティングセルカラムで同一でないよう配置された2つのコンピューティングセル間のインターマットシフトインターネクション構成を概念的に示す図である。

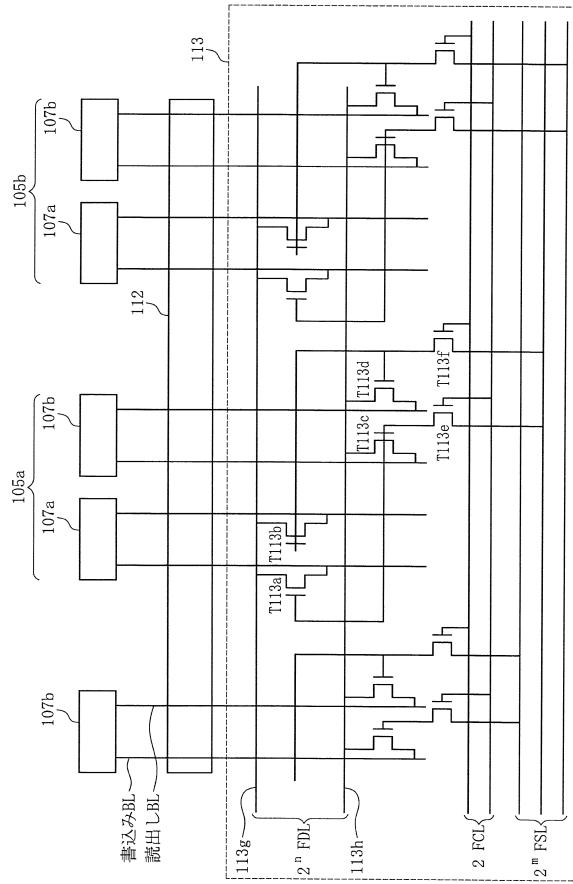

【図5】本発明の一実施形態によるインターマットフォワーディングアレイを示す図である。

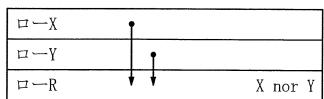

【図6A】本発明の一実施形態によるDPUによって提供されるNORロジック基盤の動作を示す図である。 10

【図6B】本発明の一実施形態によるDPUによって提供されるNORロジック基盤の動作を示す図である。

【図6C】本発明の一実施形態によるDPUによって提供されるNORロジック基盤の動作を示す図である。

【図6D】本発明の一実施形態によるDPUによって提供されるNORロジック基盤の動作を示す図である。

【図6E】本発明の一実施形態によるDPUによって提供されるNORロジック基盤の動作を示す図である。

【図6F】本発明の一実施形態によるDPUによって提供されるNORロジック基盤の動作を示す図である。 20

【図6G】本発明の一実施形態によるDPUによって提供されるNORロジック基盤の動作を示す図である。

【図7】本発明の一実施形態による確率的データアレイを含むDPUの一例を示すプロック図である。

【図8A】多重化動作に変換される加算動作に対する確率的コンピューティング動作を示す図である。

【図8B】ANDロジック動作に変換される乗算動作に対する確率的コンピューティング動作を示す図である。

【図9】本発明の一実施形態によるDPUを含むシステム構造を示す図である。

#### 【発明を実施するための形態】

##### 【0011】

以下、本発明を実施するための形態の具体例を、図面を参照しながら詳細に説明する。

##### 【0012】

本明細書で、多様な詳細な説明を本文の理解を提供するために提示する。しかし、このような詳細な説明無しに記載した本発明の思想が当業者によって容易に具現されることはよく理解される。他の例で、広く公知された方法、手続、構成、及び回路は本文を曖昧にしないために説明しない。

##### 【0013】

詳細な説明で“1つの実施形態”又は“一実施形態”を参照することは、実施形態に関する特定の特徴、構造、又は特性が本文の少なくとも1つの実施形態に含まれることを意味する。即ち、本文の多様な箇所で使用する“1つの実施形態で”又は“一実施形態で”又は“1つの実施形態によって”又は類似な意味を有する他の表現は同一の実施形態を参照することを要求しない。更に、特定の特徴、構造、又は特性は適切な方式により1つ以上の実施形態で組合される。これに関連して、本明細書で使用するように、“例示的な”という単語は“例(example、instance、illustration)として提供される”ということを意味する。本明細書で“例示的な”のように記述した実施形態は、他の実施形態に比べて必ずしも望ましいか又は有利であるものと考えてはならない。また、本文で言及する内容に従って、単数用語は複数の形態も含み、複数用語は単数形態も含む。構成図面を含む多様な図面は、説明の目的のためにのみ本文で言及し、正確な縮尺ではない。同様に、多様な波形及びタイミング図は説明の目的のためにのみ図示 40

10

20

30

40

50

する。例えば、一部の構成要素は明確性のために他の構成要素と比較して誇張して図示する。更に、適切に考えられる場合、参照符号は、対応する構成要素及び／又は類似の構成要素を示すために図面で反復する。

#### 【0014】

本明細書で使用する用語は、特定の実施形態のみを説明するものであり、本発明を制限しようとするものとして意図しない。本明細書で使用するように、文脈上で明確に異なって意味しない限り、単数形態の“1つ”は複数の形態も含むものとして意図する。“構成される”、“構成されている”、“含む”、及び“含んでいる”的用語を本明細書で使用する場合、このような用語は、定まった特徴、整数、段階、動作、要素、及び／又は成分の存在を明示するが、1つ又はそれ以上の他の特徴、整数、段階、動作、要素、成分、及び／又はそれらのグループの追加又は存在を排除しない。“第1”、“第2”のような用語は、先に説明した構成に対するラベルとして使用され、別の定義が無い限り特定の順序（例えば、空間的、時間的、論理的、等）を意図するものではない。更に、同一の参照符号は、同一であるか若しくは類似の機能を有する部品、構成、ブロック、回路、ユニット、又はモジュールに関連する2つ以上の図面に亘って使用される。しかし、このような使用は、説明の簡易化のみのためであり、このような構成及びユニットの構成又は構造的な細部事項が全ての実施形態又は共通的に参照される部分／モジュールで同一なものとして意図せず、本発明の特定の実施形態のみを指称するための1つの手段である。10

#### 【0015】

異なって定義しない限り、全ての用語（技術又は科学用語を含む）は本発明の装置と方法が属する分野で当業者に通常的に理解される同一な意味を有する。また、辞書的な意味として定義した用語は、関連する記述及び／又は本発明の説明の状況に従って解釈されなければならず、このように定義されない限り、理想的に理解されるか若しくは過度に形式的な意味として理解されてはならない。20

#### 【0016】

本明細書に記述する発明は、多様な動作に対してプログラム可能（programmable）であり、再構成可能な（reconfigurable）DPU（DRAM（Dynamic Random Access Memory）based Processing Unit）を提供する。例えば、多様な動作は、加算、乗算、シフト、最大／最小（MIN/MAX）、及び比較（COMPARISON）等を含むが、本発明はこれに制限されない。一実施形態で、DPUは、3つのトランジスタ及び1つのキャパシター（3T1C）を含むDRAMプロセス及び構造に基づく。他の実施形態で、若干の変化と共に、DPUは、1つのトランジスタ及び1つのキャパシター（1T1C）を含むDRAMプロセス及び構造に基づく。従って、DPUは、特定のコンピューティングロジック回路（例えば、アダ（加算器）のような）を含まないが、高度の並列動作を使用するメモリセルを使用する計算を提供する。一実施形態で、DPUは、乗算（multiplication）動作がANDロジック動作に変換され、加算（addition）動作が多重化（multiplexing）動作に変換される確率的（stochastic）コンピューティングアレイを含む。30

#### 【0017】

また、本明細書に記述する発明は、DPUをプログラムし、再構成するためのISA（Instruction Set Architecture）、コンパイラ、ドライバー、ライブラリ、フレームワーク拡張を有する環境（ecosystem）を含むシステム構造を提供する。40

#### 【0018】

更に、本明細書に記述する発明は、データセンター及び／又はモバイルアプリケーションに適合するシステム構造を提供する。そして、システム構造は、GPU/ASIC（Application Specific Integrated Circuit）（TPU）/FPGA（Field-Programmable Gate Array）マシンラーニングアプリケーションに対して選択的に二進（binary）及び固定小数50

点方式( *fixed point* )の計算の両方に対するマシンラーニングアプリケーションのためのPIM( Processor-in Memory )ソリューションを提供する。一実施形態で、本明細書に記述する発明は、高性能、エネルギー効率的、低価格のシステムを提供する。該当システムは、例えば二進加重ニューラルネットワーク( Binary Weight Neural Network )に対する加速化されたディープラーニングを提供する。

#### 【0019】

本明細書に記述する発明は、再構成及びプログラム可能であり、DRAM技術を利用して構成されるDPUに関連する。一実施形態で、DPUは、多様な動作( 例えば、加算、乗算、整列、等 )を遂行するように構成されるDRAM基盤のメモリセルアレイ及びDRAM基盤のコンピューティングセルアレイを含む。10

#### 【0020】

DPUの内部構成は、サブアレイの複数のバンクに連結されたシステムバスを含む。一実施形態で、システムバスはサブアレイのHツリー連結バンクを提供するように構成される。各々のサブアレイはローカルコントローラを含み、各々の独立的なサブアレイは分離的に又は同時に活性化される。一実施形態で、DRAM基盤のセルは2つのアレイ( データセルアレイ及びコンピューティングセルアレイ )に区分される。一実施形態で、コンピューティングセルアレイはDRAM基盤のメモリセルで具現される。他の実施形態で、コンピューティングセルアレイはロジック回路を含むDRAM基盤のメモリセルで具現される。DPU内部構造は、またデータシフト及びデータ移動回路を含む。一実施形態で、確率的データ計算のために構成される第3DRAM基盤のセルアレイがある。20

#### 【0021】

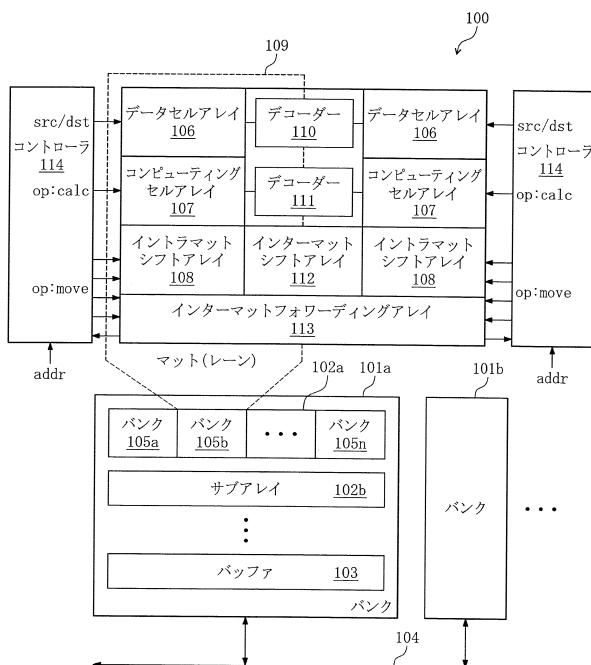

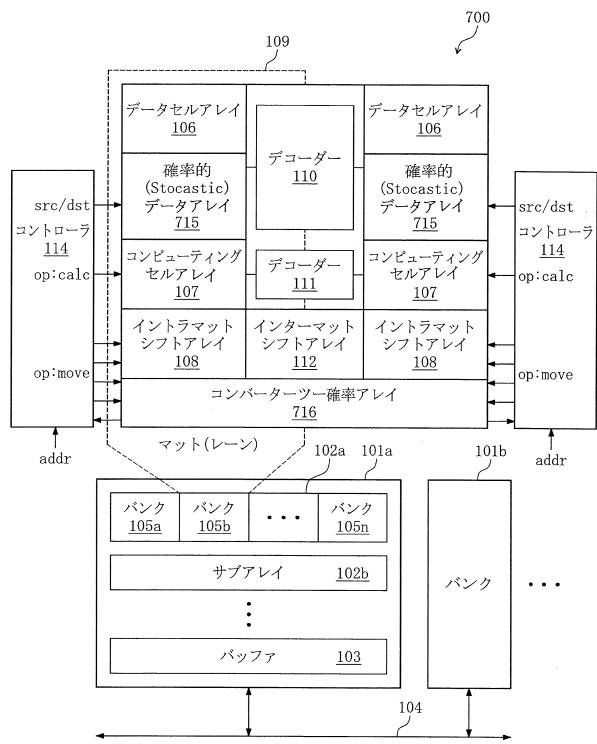

図1は、本発明の一実施形態によるDPU( DRAM( Dynamic Random Access Memory ) based Processing Unit )10

0の一例を示すブロック図である。DPU100は1つ以上のバンク( 101a ~ 101m )を含む。図1では、1つ以上のバンク( 101a ~ 101m )の中のバンク101a、101bのみを図示する。各バンク101は1つ以上のサブアレイ( 102a ~ 102n )を含む。図1では、1つ以上のサブアレイ( 102a ~ 102n )の中のサブアレイ102a、102bのみを図示する。また、各バンク101はバッファ103を含む。バッファ103は、個別サブアレイ102に連結され、システムバス104に連結される。30

バッファ103は、バンク102内の全体ロー( row )を読み出し、その後該当ローを再び同一のバンク又は他のバンクに書き込む。バッファ103は、また該当ローデータのコピーをサブアレイ102内の複数のマット( 105a ~ 105n )にブロードキャスト( broadcast )する。一実施形態で、バンク101及びシステムバス104はHツリー連結バンクを提供する。

#### 【0022】

各サブアレイ102は1つ以上のマット( 又はレーン )105を含む。図1では、1つ以上のマット105の中のサブアレイ102aのマット105a ~ 105nのみを図示する。各マット105は、データセルアレイ106、コンピューティングセルアレイ107、及びイントラマット( intra-mat )シフトアレイ108を含むDPU100の一領域である。マット105の例は点線109で囲まれるように図1で示される。各マット105は、データセルアレイデコーダー110、コンピューティングセルアレイデコーダー111、インターマット( inter-mat )シフトアレイ112、及びインターマットフォワーディングアレイ113を、隣接するマットと共有する。一実施形態で、データセルアレイデコーダー110、コンピューティングセルアレイデコーダー111、及びインターマットシフトアレイ112は、隣接するマット105の間にサブアレイコントローラ114と交互に物理的に配置される。一実施形態で、各デコーダー( 110、111 )は従来のDRAMタイプのメモリデコーダーのように動作する。40

#### 【0023】

一実施形態で、各マット105は通信的に( communicatively )サブア50

レイコントローラ 114 に連結される。各サブアレイコントローラ 114 は他のサブアレイコントローラ 114 から独立して構成される。サブアレイコントローラ 114 はアドレス (addr) として命令をDRAM アドレスバスから受信する。アドレス (即ち、アドレス信号) に応答して、サブアレイコントローラ 114 は、データセルアレイ 106 及びコンピューティングセルアレイ 107 の中の少なくとも 1 つのアレイに出力としてデコーディングされたアドレスを提供する。即ち、サブアレイコントローラ 114 は、関連するデータセルアレイ 106 に対するデータセルアレイデコーダー 110 によってデコーディングされたソース / 目的地 (destination) (src / dst) アドレスを出力する。そして、コンピューティングセルアレイ 107 の場合、サブアレイコントローラ 114 は、コンピューティングセルアレイデコーダー 111 によってデコーディングされた動作 / 計算 (op / calc) アドレスを出力する。また、サブアレイコントローラ 114 は、2つ以上のサブアレイコントローラ 114 が組織化された方法で動作するDRAM バスからのアドレスとして命令を受信する。また、サブアレイコントローラ 114 はデータ移動回路を制御する。例えば、サブアレイコントローラ 114 は、イントラマットシフトアレイ 108、インターマットシフトアレイ 112、及びインターマットフォワードィングアレイ 113 を制御する。

10

#### 【0024】

各データセルアレイ 106 は、少なくとも 1 つのカラム (column) 及び少なくとも 1 つのロー (row) 内に配置される 1 つ以上のDRAM セルを含む。一実施形態で、データセルアレイ 106 は従来のDRAM セルアレイのように構成される。一実施形態で、データセルアレイ 106 は 2K カラム及び 16 ローを含む。他の実施形態で、データセルアレイ 106 は 2K カラムより少ないか又は多いカラムを含み、また 16 ローより少ないか又は多いローを含む。

20

#### 【0025】

各コンピューティングセルアレイ 107 は、少なくとも 1 つのカラム及び少なくとも 1 つのロー内に配置される 1 つ以上のコンピューティングセルを含む。コンピューティングセルアレイ 107 内のカラム数はデータセルアレイ 106 内のカラム数と同一である。一実施形態で、コンピューティングセルアレイ 107 は 2K カラム及び 16 ローを含む。他の実施形態で、コンピューティングセルアレイ 107 は 2K カラムより少ないか又は多いカラムを含み、また 16 ローより少ないか又は多いローを含む。

30

#### 【0026】

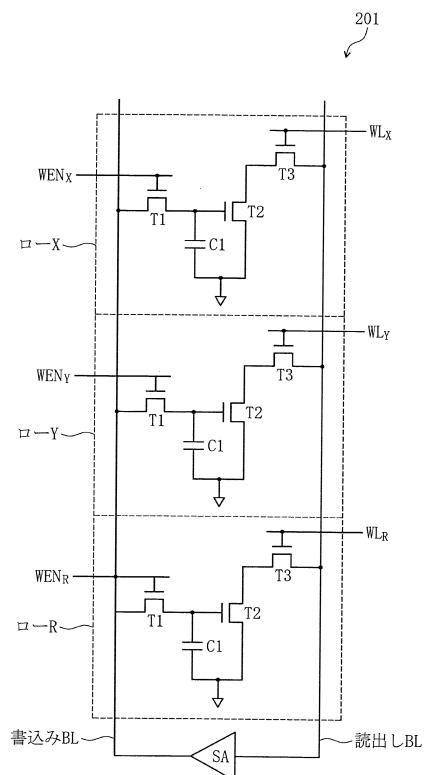

図 2A は、コンピューティングセルアレイ 107 内のコンピューティングセルに対して使用される 3 つのトランジスタ及び 1 つのキャパシター (3T1C) によるDRAM コンピューティングセルトポグラフィ (topography) 201 の一例を示す図である。図 2A に示すように、ロー X 内の 3T1C コンピューティングセルは第 1 トランジスタ T1 を含む。第 1 トランジスタ T1 は、書き込みビットライン (Write BL) に電気的に連結されたソース端、キャパシター C1 の第 1 端及び第 2 トランジスタ T2 のゲート端の両側に電気的に連結されたドレーン端、並びに書き込みイネーブル (WEN) ラインに電気的に連結されたゲート端を含む。キャパシター C1 の第 2 端はグラウンド (ground) ラインに電気的に連結される。第 2 トランジスタ T2 は、グラウンドラインに電気的に連結されたソース端、及び第 3 トランジスタ T3 のソース端に電気的に連結されたドレーン端を含む。第 3 トランジスタ T3 は、ワードライン WL に電気的に連結されたゲート端、及び読み出しビットライン (Read BL) に電気的に連結されたドレーン端を含む。3T1C コンピューティングセルトポグラフィ 201 は、読み出しビットライン (Read BL) に電気的に連結された入力及び書き込みビットライン (Write BL) に電気的に連結された出力を含むセンスアンプ (Sense Amplifier : SA) を含む。

40

#### 【0027】

また、ロー Y 内のコンピューティングセル及びロー R 内のコンピューティングセルの両方は、ロー X 内のコンピューティングセルの配置と同様に、3T1C DRAM 構成に配

50

置された3つのトランジスタ( $T_1 \sim T_3$ )及びキャパシターCを含む。図2Aに示した3つのコンピューティングセル及びセンスアンプ(SA)の一例は、NORロジック動作(即ち、「X NOR Y」ロジック動作)を提供するように構成される。該当NORロジック動作の結果はローRに格納される。 $3T1C\text{DRAM}$ コンピューティングセルの1つのカラムのみを図2Aに明示的に示したが、 $3T1C$ コンピューティングセルが複数のカラム(例えば、2Kカラム)内に構成される等の他の実施形態が可能である。また、3つ以上のローが提供される他の実施形態が可能である。また、図2Aに示した $3T1C\text{DRAM}$ コンピューティングセル構成はNORロジック動作を提供するが、 $3T1C\text{DRAM}$ コンピューティングセルトポグラフィ201のNORロジック動作は多様な機能的な動作を提供するために使用される。例えば、機能的な動作は、排他ノア(XNOR)、加算(ADD)、セレクト(SET)、MAX、SIGN、多重化(MUX)、CSA(Conditional Sum Addition)ロジック、乗算、ポップカウント(popcount)、COMPARE等を含む。但し、本発明はこれに制限されない。また、イントラマットシフトアレイ108及びインターマットシフトアレイ112はシフト機能を提供する。

#### 【0028】

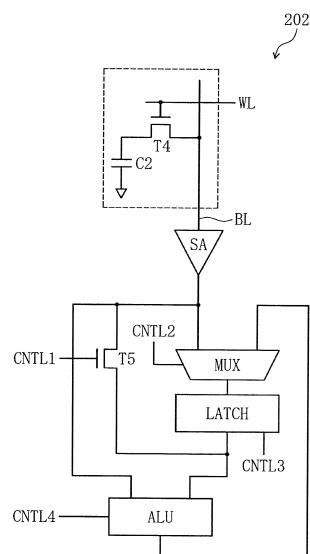

図2Bは、図1のコンピューティングセルアレイ107内のコンピューティングセルに対して使用される1つのトランジスタ及び1つのキャパシター( $1T1C$ )によるDRAMコンピューティングセルトポグラフィ(topography)202の他の例を示す図である。図2Bに示すように、 $1T1C$ コンピューティングセルは第4トランジスタ $T_4$ を含む。第4トランジスタ $T_4$ は、キャパシターC2の第1端に電気的に連結されたソース端、ビットラインBLに電気的に連結されたドレーン端、及びワードラインWLに電気的に連結されたゲート端を含む。キャパシターC2の第2端はグラウンドラインに電気的に連結される。ビットラインBLはセンスアンプ(SA)の入力に電気的に連結される。センスアンプ(SA)の出力は、多重化器(MUX)の第1入力、第5トランジスタ $T_5$ のドレーン端、及びALU(Arithmetic Logic Unit)の入力に電気的に連結される。多重化器(MUX)の出力はラッチ(LATCH)の入力に電気的に連結される。第5トランジスタ $T_5$ のソース端はラッチ(LATCH)の出力に電気的に連結される。ALUの出力は多重化器(MUX)の第2入力に電気的に連結される。図2Bで、第5トランジスタ $T_5$ 、多重化器(MUX)、ラッチ(LATCH)、及びALUは、それぞれコントローラ114から制御信号(CNTL1~NTL4)を受信する。一実施形態で、ALUはNOR機能を提供するように構成される。図2BのビットラインBLに電気的に連結されたロジック回路はNORロジック動作を提供するが、ビットラインBLに電気的に連結されたロジック回路(即ち、ALU)は他の機能動作(例えば、排他ノア(XNOR)、加算(ADD)、セレクト(SET)、MAX、SIGN、多重化(MUX)、CSA(Conditional Sum Addition)ロジック、乗算、ポップカウント(popcount)、COMPARE等)を提供する。但し、本発明はこれに制限されない。また、イントラマットシフトアレイ108及びインターマットシフトアレイ112はシフト機能を提供する。図2Bで1つの $1T1C$ コンピューティングセルのみを図示したが、複数のカラム及びローの $1T1C$ コンピューティングセルが提供される。

#### 【0029】

図2A及び図2Bから分かるように、DPUのコンピューティングセルは、特定の複雑なコンピューティングロジックを含まない。但し、代わりに、DPUのコンピューティングセルは、複数の多様なタイプの計算を遂行する機能(ability)を提供する再プログラマ可能な性質(nature)を有する相対的に単純なトポグラフィを含む。また、DPUのポグラフィは、より多くの計算をより速くより効率的に遂行するためにメモリ構造に内在され、大量並列処理の長所を有するように配置される。

#### 【0030】

図3は、本発明の一実施形態によるイントラマット(intra-mat)シフト(s

10

20

30

40

50

h i f t ) アレイ 1 0 8 の一例を示す図である。イントラマットシフトアレイ 1 0 8 の記述 ( d e s c r i p t i o n ) を単純化するために、図 3 に示すように、4 つのカラムのコンピューティングメモリセルアレイ 1 0 7 の幅のマット 1 0 5 を考慮する。イントラマットシフトアレイ 1 0 8 は、アレイ内に配置された複数の第 6 トランジスタ T 6 ( 図 3 では、1 つのトランジスタのみを T 6 で表示する ) 、2 <sup>n</sup> シフトライン S L s ( n はマット 1 0 5 内のコンピューティングセルのカラムである ) 、n + 2 シフトレフト ( l e f t ) コントロールライン S L c L s 、2 シフトライト ( r i g h t ) コントロールライン S R c L s 、及び n シフトマスクライン S M L s を含む。イントラマットシフトアレイ 1 0 8 の第 6 トランジスタ T 6 の一部は書き込みビットライン ( W r i t e B L ) と 2 <sup>n</sup> シフトライン S L s との間に電気的に連結され、イントラマットシフトアレイ 1 0 8 の他の第 6 トランジスタ T 6 は読み出しビットライン ( R e a d B L ) と 2 <sup>n</sup> シフトライン S L s との間に連結される。このような第 6 トランジスタ T 6 のゲートは n + 2 シフトレフトコントロールライン S L c L s 及び 2 シフトライトコントロールライン S R c L s に電気的に連結される。イントラマットシフトアレイ 1 0 8 の他の第 6 トランジスタ T 6 は n シフトマスクライン S M L s と 2 <sup>n</sup> シフトライン S L s との間に電気的に連結される。イントラマットシフトアレイ 1 0 8 のコントロールラインはマット 1 0 5 に関連するサブアレイコントローラ 1 1 4 に電気的に連結される。

10

#### 【 0 0 3 1 】

コントロールライン ( S L c L s 、 S R c L s ) 上の適切な信号によって、イントラマットシフトアレイ 1 0 8 は、マット 1 0 5 内でデータをレフト ( l e f t ) シフト又はライト ( r i g h t ) シフトする。レフトシフトに対して、データは、サイン ( s i g n ) ビットで満たされ、1 つの動作毎に 1 ビット又は ( n - 1 ) ビット程シフトされる。n はマット 1 0 5 当たりのカラム数である。ライトシフトに対して、命令による制御に従ってデータは 0 又は 1 で満たされる。或いは、データは 2 <sup>0</sup> 、 2 <sup>1</sup> 、 ... 、 2 <sup>k - 1</sup> 、 2 <sup>k</sup> マット当たりのカラム数までシフトされる。2 <sup>k</sup> はカラム数である。

20

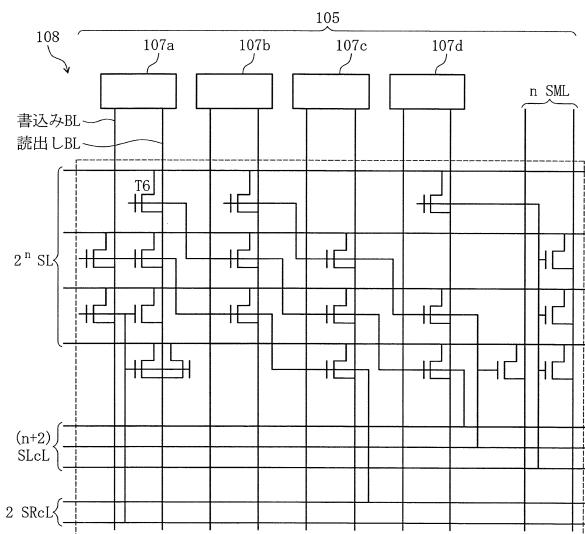

#### 【 0 0 3 2 】

図 4 A は、本発明の一実施形態によるインターマット ( i n t e r - m a t ) シフトアレイ 1 1 2 の一例を示す図である。インターマットシフトアレイ 1 1 2 の記述 ( d e s c r i p t i o n ) を単純化するために、図 4 A ~ 図 4 C に示すように、マット 1 0 5 が 2 つのカラムのコンピューティングメモリセルアレイ 1 0 7 の幅であるマット 1 0 5 の構成を考慮する。即ち、各マット 1 0 5 はコンピューティングメモリセル 1 0 7 a の第 1 カラム及びコンピューティングメモリセル 1 0 7 b の第 2 カラムを含む。インターマットシフトアレイ 1 1 2 は、トランジスタ T 1 1 2 a 、 T 1 1 2 b 、トランジスタ T 1 1 2 c 、 T 1 1 2 d 、データシフトライン 1 1 2 e 、 1 1 2 f 、及びインターマットシフトコントロールライン I S L c L s を含む。マット内で、トランジスタ T 1 1 2 a は、コンピューティングメモリセル 1 0 7 a の第 1 カラムの読み出しビットライン ( R e a d B L ) に電気的に連結されたソース端、データシフトライン 1 1 2 e に電気的に連結されたドレン端を含む。トランジスタ T 1 1 2 b は、コンピューティングメモリセル 1 0 7 b の第 2 カラムの読み出しビットライン ( R e a d B L ) に電気的に連結されたソース端、データシフトライン 1 1 2 f に電気的に連結されたドレン端を含む。データシフトライン ( 1 1 2 e 、 1 1 2 f ) はバッファ 1 0 3 に電気的に連結される。バッファ 1 0 3 は図 4 A に図示していない。異なるマットの間で、トランジスタ T 1 1 2 c は、隣接マット内のデータシフトライン 1 1 2 e にそれぞれ電気的に連結されたソース端及びドレン端を含む。トランジスタ T 1 1 2 d は、隣接マット内のデータシフトライン 1 1 2 f にそれぞれ電気的に連結されたソース端及びドレン端を含む。トランジスタ T 1 1 2 c 、 T 1 1 2 d のゲートはそれぞれ異なるインターマットシフトコントロールライン I S L c L s のそれぞれに連結される。インターマットシフトコントロールライン I S L c L s 上の適切な信号によって、インターマットシフトアレイ 1 1 2 は、異なるマットの間でデータをレフトシフト又はライトシフトする。インターマットシフトアレイ 1 1 2 のコントロールラインはマット 1 0 5 に関連するサブアレイコントローラ 1 1 4 に電気的に連結される。

30

40

50

## 【0033】

図4Bは、本発明の一実施形態による左側のインターマットシフトに対する隣接するコンピューティングセルカラム（マット105a、105b）で同様に配置された2つのコンピューティングセル間のインターマットシフトインターネクション（interconnection）構成を概念的に示す図である。図4Bのインターネクション構成を、利用されるインターネクションノードによって概念的に図示し、利用されるインターネクションノードを強調して図示する。例えば、トランジスタT112c、T112dは活性化され、これに従って導線経路が各々のトランジスタの間に形成される。従って、左側のコンピューティングセルカラム（マット105a）と右側のコンピューティングセルカラム（マット105b）との間でデータシフトライン（112e、112f）は連結される。トランジスタT112c、T112dのゲート端はアクティブなインターマットシフトコントロールラインISLcLに電気的に連結される。マット105b内のトランジスタT112a、T112bは活性化され、従ってマット105b内のコンピューティングセル107aの読み出しビットライン（Read BL）は、マット105bの左側であるマット105a内のコンピューティングセル107aの書き込みビットライン（Write BL）に電気的に連結される。また、これに従って、マット105b内のコンピューティングセル107bの読み出しビットライン（Read BL）は、マット105bの左側であるマット105a内のコンピューティングセル107bの書き込みビットライン（Write BL）に電気的に連結される。

## 【0034】

図4Cは、本発明の一実施形態による左側のインターマットシフトに対する隣接するコンピューティングセルカラム（105a、105b）で同一でないように配置された2つのコンピューティングセル間のインターマットシフトインターネクション（interconnection）構成を、利用されるインターネクションノードによって概念的に図示し、利用されるインターネクションノードを強調して図示する。例えば、トランジスタT112c、T112dは活性化されて導線経路が各々のトランジスタの間に形成される。従って、左側のコンピューティングセルカラム（マット105a）と右側のコンピューティングセルカラム（マット105b）との間でデータシフトライン（112e、112f）は連結される。トランジスタT112c、T112dのゲート端はアクティブなインターマットシフトコントロールラインISLcLに電気的に連結される。マット105aのトランジスタT112a、T112bは活性化され、従ってマット105a内のコンピューティングセル107aの読み出しビットライン（Read BL）は、マット105aの右側であるマット105b内のコンピューティングセル107aの書き込みビットライン（Write BL）に電気的に連結される。また、これに従って、マット105a内のコンピューティングセル107bの読み出しビットライン（Read BL）は、マット105aの右側であるマット105b内のコンピューティングセル107bの書き込みビットライン（Write BL）に電気的に連結される。

## 【0035】

図5は、本発明の一実施形態によるインターマットフォワードィング（forwarding）アレイ113を示す図である。インターマットフォワードィングアレイ113の説明を単純化するために、図5に示すように、2つのカラムのコンピューティングセルアレイ107の幅のマット105の構成を考慮する。即ち、各マット105はコンピューティングセル107aの第1カラム及びコンピューティングセル107bの第2カラムを含む。マット105と共に、インターマットフォワードィングアレイ113は、トランジスタT113a、T113b、トランジスタT113c、T113d、トランジスタT113e、T113f、2<sup>n</sup> フォワードィングデータラインFDL、フォワードィングコントロールラインFCL、及び2<sup>m</sup> フォワードィングセクションラインFSLを含む。ここで、nはマット内のコンピューティングセルのカラム数であり、mはセクション数である。トランジスタT113a、T113bのソース端はそれぞれコンピューティングセル107

a の第 1 カラムの書込みビットライン (W r i t e \_ B L ) 及び読出しビットライン (R e a d \_ B L ) に電気的に連結される。トランジスタ T 1 1 3 a、T 1 1 3 b のドレーン端は第 1 データフォワーディングライン (F D L ) 1 1 3 g に電気的に連結される。トランジスタ T 1 1 3 c、T 1 1 3 d のソース端はそれぞれコンピューティングセル 1 0 7 b の第 2 カラムの書込みビットライン (W r i t e \_ B L ) 及び読出しビットライン (R e a d \_ B L ) に電気的に連結される。トランジスタ T 1 1 3 c、T 1 1 3 d のドレーン端は第 2 データフォワーディングライン (F D L ) 1 1 3 h に電気的に連結される。トランジスタ T 1 1 3 e、T 1 1 3 f のソース端はそれぞれトランジスタ T 1 1 3 a、T 1 1 3 b のゲート端に電気的に連結される。トランジスタ T 1 1 3 e、T 1 1 3 f のドレーン端は両方とも同一のフォワーディングセクションライン F S L に連結される。トランジスタ T 1 1 3 e、T 1 1 3 f のゲート端はそれぞれ異なるフォワーディングコントロールライン F C L s に連結される。フォワーディングコントロールライン F C L s 上の適切な信号によって、インターマットフォワーディングアレイ 1 1 3 は、マットの間でデータをフォワーディングする。インターマットフォワーディングアレイ 1 1 3 のコントロールラインは、相互間でデータがフォワーディングされるマット 1 0 5 に関連するサブアレイコントローラ 1 1 4 に電気的に連結される。

10

## 【 0 0 3 6 】

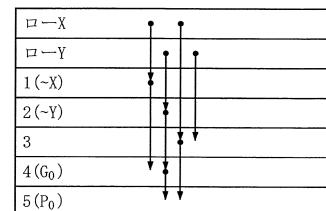

図 6 A ~ 図 6 G は、本発明の一実施形態による D P U によって提供される N O R ロジック基盤の動作を示す図である。図 6 A ~ 図 6 G で、第 1 オペランド (o p e r a n d) はロ - X に格納され、第 2 オペランドはロ - Y 又はロ - W に格納される。図 6 A ~ 図 6 G 内の矢印はコンピューティングセルの全体ローに対する N O R ロジック動作の入出力フローを示す。例えば、図 6 A のロ - X はロ - X のコンピューティングセルに格納されたオペランドの全体ローを示す。ロー X 内に格納されたオペランド及びロー Y 内に格納されたオペランドの N O R ロジック動作の結果は結果ロー R 内に格納される。一実施形態で、ロー X 及びロー Y のオペランドは、例えば 1 0 0 個のカラム (例えば、 $x_1, x_2, \dots, x_{100}$  及び  $y_1, y_2, \dots, y_{100}$ ) を含み、結果はロー R (例えば、 $r_1, r_2, \dots, r_{100}$ ) 内に格納される。即ち、「 $x_i \text{ N O R } y_i = r_i$ 」である。ここで、i はカラムインデックスである。他の実施形態で、ロー X はロー内のコンピューティングセルの選択されたグループのみを示す。

20

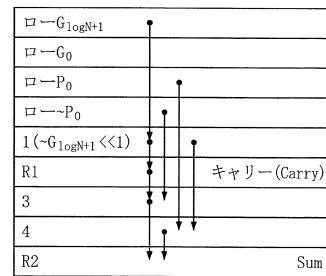

## 【 0 0 3 7 】

図 6 B はプレフィックス (p r e f i x ) K o g g e - S t o n e アダ (加算器) に基づく N ビット数に対するプールアダ (加算器) 動作を例示的に示す。図 6 B で、第 1 N ビットオペランドはロー X 内に格納され、第 2 N ビットオペランドはロー Y 内に格納される。図 6 B 内に示した例示的な加算動作で、中間値 (i n t e r m e d i a t e t e r m) (G<sub>0</sub>、P<sub>0</sub>、G<sub>1</sub>、P<sub>1</sub>、G<sub>2</sub>、P<sub>2</sub>、..., G<sub>1 0 g N + 1</sub>、P<sub>1 0 g N + 1</sub>) が計算される。図 6 B の最上のブロックはロー X 及びロー Y からの入力オペランドを利用して G<sub>0</sub> 及び P<sub>0</sub> を決定する 5 個の分離された動作を示す。第 1 動作で、最上のブロックはロー X の逆 (即ち、~ X) を決定し、これはロー 1 に格納される。第 2 動作はロー Y の逆 (即ち、~ Y) を決定し、これはロー 2 に格納される。第 3 動作は「ロー X N O R ロ - Y」の動作を決定し、これはロー 3 に格納される。第 4 動作は「G<sub>0</sub> = ロ - 1 N O R ロ - 2」を決定し、これはロー 4 に格納される。第 5 動作は「P<sub>0</sub> = ロ - 3 N O R ロ - 4」を決定し、これはロー 5 に格納される。

40

## 【 0 0 3 8 】

図 6 B の中間ブロックを参照すると、最上ブロックからの中間結果 G<sub>0</sub>、P<sub>0</sub> が中間結果 G<sub>i + 1</sub>、P<sub>i + 1</sub> を決定するために使用される。ここで、i はカラムインデックスである。即ち、図 6 A の最上のブロックから決定された中間結果 G<sub>0</sub>、P<sub>0</sub> が中間結果 G<sub>1</sub>、P<sub>1</sub> を決定するために使用される。中間結果 G<sub>1</sub>、P<sub>1</sub> は中間結果 G<sub>2</sub>、P<sub>2</sub> を決定するために使用され、同様に中間結果 G<sub>1 0 g N + 1</sub>、P<sub>1 0 g N + 1</sub> が決定される。図 6 B の最下のブロックで、結果ロー R<sub>1</sub> 及び結果ロー R<sub>2</sub> はそれぞれプールアダ (f u l l a d d e r) 動作に対するキャリー (c a r r y) 結果及び総合 (s u m) 結果を格

50

納する。

**【0039】**

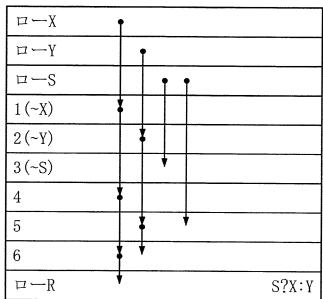

図6Cは3T1C DRAMコンピューティングセルトポグラフィ201によって提供される例示的なセレクター動作を示す。ロー1はローXの逆(即ち、 $\sim X$ )の中間結果を格納する。ロー2はローYの逆(即ち、 $\sim Y$ )の中間結果を格納する。ロー3はローSの逆(即ち、 $\sim S$ )の中間結果を格納する。ロー4は‘ロー1 NOR ロー3’の中間結果を格納する。ロー5は‘ロー2 NOR ローS’の中間結果を格納する。ロー6は‘ロー4 NOR ロー5’の中間結果を格納する。ローRはロー6の逆の結果( $S ? X : Y$ )を格納する。

**【0040】**

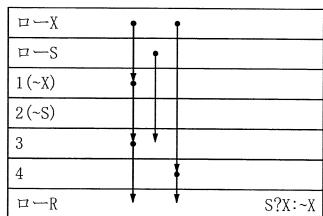

図6Dは3T1C DRAMコンピューティングセルトポグラフィ201によって提供される他の例示的なセレクター動作を示す。ロー1はローXの逆(即ち、 $\sim X$ )の中間結果を格納する。ロー2はローSの逆(即ち、 $\sim S$ )の中間結果を格納する。ロー3は‘ロー1 NOR ローS’の中間結果を格納する。ロー4はローXの逆( $\sim X$ )の中間結果を格納する。ローRは‘ロー3 NOR ロー4’の結果( $S ? X : \sim X$ )を格納する。

**【0041】**

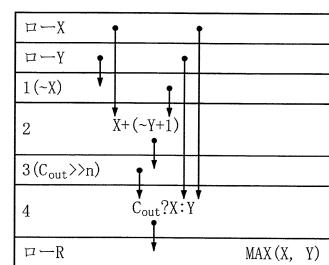

図6Eは3T1C DRAMコンピューティングセルトポグラフィ201によって提供される例示的なMAX/MIN動作を示す。ロー1はローYの逆(即ち、 $\sim Y$ )の中間結果を格納する。ロー2はローX + ( $\sim Y + 1$ )の中間結果を格納する。ロー3は‘ $C_{out} > n$ ’の中間結果を格納する。ロー4は‘ $C_{out} ? X : Y$ ’の中間結果を格納する。ローRは‘MAX(X : Y)’の結果を格納する。

**【0042】**

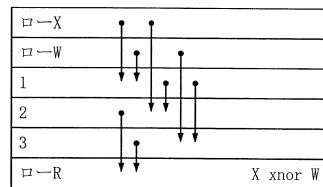

図6Fは3T1C DRAMコンピューティングセルトポグラフィ201によって提供される例示的な1ビット乗算動作を示す。ロー1は‘ローX NOR ローW’の中間結果を格納する。ロー2は‘ローX NOR ロー1’の中間結果を格納する。ロー3は‘ローW NOR ロー1’の中間結果を格納する。結果ローRは‘ロー2 NOR ロー3’の結果(即ち、‘ローX XNOR ローW’の結果)を格納する。

**【0043】**

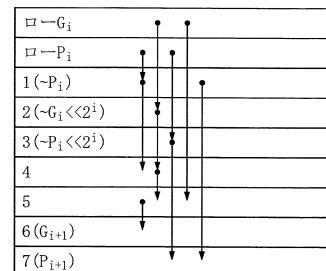

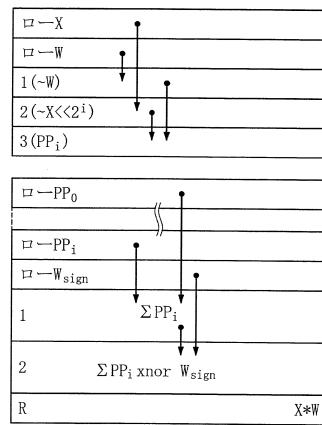

図6Gは3T1C DRAMコンピューティングセルトポグラフィ201によって提供される例示的な複数ビット乗算動作を示す。図6Gの上方のブロックで、ロー1はローWの逆(即ち、 $\sim W$ )の中間結果を格納する。ロー2は $2^i$ 番目のレフトシフトされたローXの逆(即ち、 $\sim X << 2^i$ )の中間結果を格納する。ここで、 $i$ はインデックスである。ロー3は‘ロー1 NOR ロー2’の中間結果( $PP_i = \sim W NOR \sim X << 2^i$ )を格納する。図6Gの下方のブロックで、ロー1は‘ロー $PP_0 SUM ローPP_i (PP_i)$ ’の中間結果を格納する。ロー2は‘ロー2 NOR ロー $W_{sign}$ ’の中間結果を格納する。ローRは‘ $X * W$ ’の結果を格納する。

**【0044】**

図7は、本発明の一実施形態による確率的(stochastic)データアレイ715を含むDPU700の一例を示すブロック図である。図1に示したDPUI100の構成要素と同一な参照インジケータ(indicator)を有するDPUI700の多様な構成要素は同様であり、このような同様の構成要素の記述はここで省略する。DPUI700のサブアレイ102は、(実際の)データセルアレイ106、コンピューティングセルアレイ107、及びイントラマットシフトアレイ108と共に、確率的データアレイ715及びコンバーターツー確率(converter-to-stochastic)アレイ716を含む。

**【0045】**

確率的データアレイ715の各々は、少なくとも1つのカラム及び少なくとも1つのロー内に配置された1つ以上の確率的コンピューティングセルを含む。確率的データアレイ715内のカラム数はデータセルアレイ106及びコンピューティングセルアレイ107内のカラム数と同一である。一実施形態で、確率的データアレイ715は2Kカラム及び

10

20

30

40

50

16 ローを含む。他の実施形態で、確率的データアレイ 715 は 2K カラムより少ないか又は多いカラム、或いは 16 ローより少ないか又は多いローを含む。確率的データアレイ 715 内で、「1」が存在する確率が使用され、2n ビットは n ビット値を示すために使用される。コンバーターツー確率アレイ 716 内の任意数生成器は実数 (real number) を確率的な数に変換するために使用される。ポップカウント動作は確率的な数を再び実数に変換するために使用される。

#### 【0046】

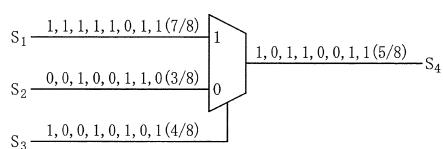

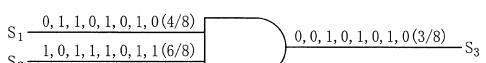

確率的なコンピューティングアプローチを使用して、加算は多重化 (multipealing) 動作に変換され、乗算は AND ロジック動作に変換される。例えば、図 8 A は、多重化動作に変換される加算動作に対する確率的コンピューティング動作を示す図であり、図 8 B は、AND ロジック動作に変換される乗算動作に対する確率的コンピューティング動作を示す図である。確率的コンピューティングに対する従来の技術は巨大なメモリ容量を要求する。しかし、本明細書に記述した発明は高度に効率的な確率的コンピューティングを提供するために使用される。これは DRAM 基盤の DPU が多くの並列 AND 動作及びマックス (MUX) 動作を遂行するためである。本明細書に記述した DPU を使用する確率的コンピューティングは、またディープラーニングが一般的なアプリケーションである複雑な動作を加速化する。

#### 【0047】

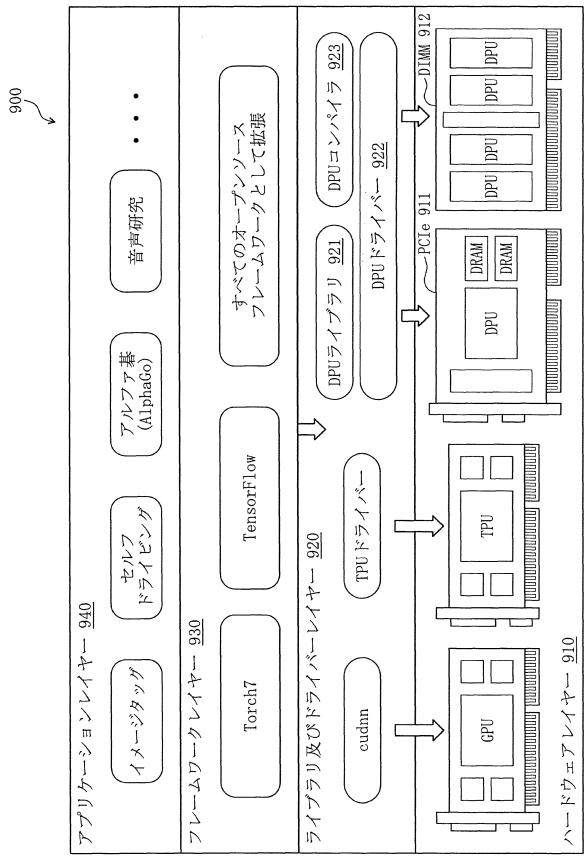

図 9 は、本発明の一実施形態による DPU を含むシステム構造 900 を示す図である。システム構造 900 は、ハードウェアレイヤー 910、ライブラリ及びドライバーレイヤー 920、フレームワークレイヤー 930、及びアプリケーションレイヤー 940 を含む。

#### 【0048】

ハードウェアレイヤー 910 は、本明細書に記述した DPU のような内装された DPU を含むハードウェア装置及び / 又は構成要素を含む。装置及び / 又は構成要素の一実施形態は、1つ以上の内装された DPU を含む PCIe 装置 911 である。装置及び / 又は構成要素の他の実施形態は、1つ以上の内装された DPU を含む DIMM (Dual In-line Memory Module) 912 である。システム構造 900 のハードウェアレイヤー 910 は PCIe 装置及び / 又は DIMM に制限されず、ハードウェアレイヤー 910 は DPU を含む SOC (System On Chip) 装置又は他のメモリタイプ装置を含むことは容易に理解される。ハードウェアレベル 910 で装置及び / 又は構成要素内に内装される DPU は、図 1 の DPU 100 及び / 又は図 7 の DPU 700 と同様に構成される。他の実施形態で、DPU の特定コンピューティングセルアレイは、図 2 A の 3T1C コンピューティングセルトポグラフィ 201 又は図 2 B の 1T1C コンピューティングセルトポグラフィ 202 を含むように構成される。

#### 【0049】

システム構造 900 のライブラリ及びドライバーレイヤー 920 は、DPU ライブラリ 921、DPU ドライバー 922、及び DPU コンパイラー 923 を含む。DPU ライブラリ 921 は、アプリケーションレイヤー 940 で動作する多様なアプリケーションに対するハードウェアレイヤー 910 内の DPU 内サブアレイの各々に対する最適のマッピング機能、リソース割当機能、及びスケジューリング機能を提供するように構成される。

#### 【0050】

一実施形態で、DPU ライブラリ 921 は、移動、加算、乗算等の動作を含むフレームワークレイヤー 930 に対するハイレベル API (Application Programming Interface) を提供する。例えば、DPU ライブラリ 921 は、また標準タイプのルーチン (routines) に対する具現を含む。標準タイプのルーチンに対する具現は、加速化されたディープラーニングプロセスに対して適用されるフォワード (forward) 及びバックワード (backward) コンボリューション (convolution)、プーリング (pooling)、正規化 (normalization)、及び活性化 (activation) レイヤーを含む。但し、本発明はこ

10

20

30

40

50

れに制限されない。一実施形態で、DPUライブラリ921は、CNN(Convolution Neural Network)の全体コンボリューションレイヤーに対する計算をマッピングするAPI類似機能を含む。更に、DPUライブラリ921は、DPU上へのコンボリューションレイヤー計算のマッピングを最適化するためのAPI類似機能を含む。

#### 【0051】

また、DPUライブラリ921は、タスク（例えば、バッチ（batch）、出力チャネル、ピクセル、入力チャネル、コンボリューションカーネル）内の全ての個別又は複数の並列性（parallelism）を、チップ、バンク、サブアレイ、及び／又はマットレベルで該当DPU並列性にマッピングして、リソース割当を最適化するためのAPI類似機能を含む。更に、DPUライブラリ921は、性能（即ち、データ移動フロー）と電力消耗との間で均衡を維持（trade off）する初期化及び／又はランタイム時に最適のDPU構成を提供するAPI類似機能を含む。DPUライブラリ921によって提供される他のAPI類似機能はデザインノブ（knob）タイプ機能を含む。例えば、デザインノブタイプ機能は、バンク当たり活性化されたサブアレイの数、活性化されたサブアレイ当たりの入力機能マップの数、機能マップのパーティショニング（partitioning）、及び／又はコンボリューションカーネルの再使用スキームの設定を含む。また他のAPI類似機能は、各サブアレイに対して特定タスク（例えば、コンボリューションコンピュティング、チャンネル圧縮（sum up）、及び／又はデータディスパッチング（dispatching））を割当することによって、追加的なリソースの割当最適化を提供する。オペランドが整数と確率的数字との間で変換された場合、DPUライブラリ921は、精密度制限を満足させながらも、オーバーヘッドを最小化するAPI類似機能を含む。精密度が予想より低い場合、DPUライブラリ921は、確率的表現のための追加的なビットを使用して値を再び計算するか、又は他のハードウェア（例えば、CPU（Central Processing Unit））にタスクを分担（offload）するAPI類似機能を含む。

#### 【0052】

DPUライブラリ921は、またDPU内の活性化されたサブアレイをスケジュールすると同時にデータ移動をスケジュールして、データ移動がコンピュティング動作によって隠されるAPI類似機能を含む。

#### 【0053】

DPUライブラリ921の他の様相は追加的なDPU開発のための拡張インターフェイスを含む。一実施形態で、DPUライブラリ921は、NOR及びシフトロジックを利用して直接機能をプログラムして標準タイプ動作（例えば、加算、乗算、MAX/MIN等）及び他の動作が提供されるインターフェイスを提供する。拡張インターフェイスは、またインターフェイスを提供し、従ってDPUライブラリ921によって具体的に支援されない動作が、ライブラリ及びドライバーレイヤー920で、SOCコントローラ（図示せず）、CPU/GPU構成要素、及び／又はCPU/TPU構成要素として分担される。DPUライブラリ921の他の様相は、DPUメモリがコンピュティングのために使用されない場合に、メモリの拡張としてDPUのメモリを使用するためのAPI類似機能を提供する。

#### 【0054】

DPUドライバー922は、DPUハードウェアレイヤーをシステムに集積するために、ハードウェアレイヤー910でのDPU、DPUライブラリ921、及びより高いレイヤーでのオペレーティングシステム（OS：Operating System）との間のインターフェイス連結を提供するように構成される。即ち、DPUドライバー922はDPUをシステムOS及びDPUライブラリ921に露出する。一実施形態で、DPUドライバー922は初期化時にDPUコントロールを提供する。一実施形態で、DPUドライバー922はDRAMタイプのアドレス又はDRAMタイプのアドレスのシーケンスの形態で命令をDPUに伝送し、DPUの内外へのデータ移動を制御する。DPUドライバ

10

20

30

40

50

-922は、DPU-CPU及び/又はDPU-GPU通信を処理すると共に多重DPU通信を提供する。

#### 【0055】

DPUコンパイラ923は、DPUライブラリ921からのDPUコードを、DPUを制御するためにDPUドライバー922によって使用されるメモリアドレスの形態であるDPU命令にコンパイルする。DPUコンパイラ923によって生成されたDPU命令は、DPU内の1つ及び/又は2つのロー上で作動する単一命令（例えば、ベクトル命令、及び/又は集合（gathered）ベクトル、リードオン動作命令）である。

#### 【0056】

フレームワークレイヤー930は使いやすい（user-friendly）インターフェイスをライブラリ及びドライバーレイヤー920並びにハードウェアレイヤー910に提供するように構成される。一実施形態で、フレームワークレイヤー930は、アプリケーションレイヤー940で広範囲なアプリケーションと互換可能な使いやすいインターフェイスを提供し、DPUハードウェアレイヤー910をユーザーに透過的に（transparent）提供する。他の実施形態で、フレームワークレイヤー930は、定量化（quantititation）機能を、例えばTorch7タイプアプリケーションやTensorFlowタイプアプリケーションのような、既存の、従来の方法に追加するフレームワーク拡張を含む。但し、本発明はこれに制限されない。一実施形態で、フレームワークレイヤー930はトレーニングアルゴリズムに定量化機能を追加することを含む。他の実施形態で、フレームワークレイヤー930は、既存の割り算、乗算、平方根のバッチ正規化方法に対して、割り算、乗算、平方根の近似方法にシフトする置換を提供する。他の実施形態で、フレームワークレイヤー930は、ユーザーが計算のために使用するビット数を設定する拡張を提供する。他の実施形態で、フレームワークレイヤー930は、DPUライブラリ及びドライバーレイヤー920からフレームワークレイヤー930に多重DPU APIをラップ（wrap）するための容量を提供する。従って、ユーザーは複数のGPUの使用と同様にハードウェアレイヤーで複数のDPUを使用することができる。フレームワークレイヤー930の他の機能は、ユーザーがハードウェアレイヤー910でDPU又はGPUに機能を割当する。

#### 【0057】

アプリケーション940は、広範囲なアプリケーション（例えば、イメージタグ（tag）プロセシング、セルフドライビング/パイロッティング（piloting）運送手段、アルファ碁タイプディープマインドアプリケーション、及び/又は音声研究（speech research）等）を含む。但し、本発明はこれに制限されない。

#### 【0058】

以上、本発明の実施形態について図面を参照しながら詳細に説明したが、本発明は、上述の実施形態に限定されるものではなく、本発明の技術的範囲から逸脱しない範囲内で多様に変更実施することが可能である。

#### 【符号の説明】

#### 【0059】

|                     |                |    |

|---------------------|----------------|----|

| 100、700             | DPU            | 40 |

| 101a～101m、105a～105n | バンク            |    |

| 102a～102n           | サブアレイ          |    |

| 103                 | バッファ           |    |

| 104                 | システムバス         |    |

| 105、105a～105n、109   | マット（レーン）       |    |

| 106                 | データセルアレイ       |    |

| 107                 | コンピューティングセルアレイ |    |

| 107a～107d           | コンピューティングセル    |    |

| 108                 | イントラマットシフトアレイ  |    |

| 110                 | データセルアレイデコーダー  | 50 |

|                 |                           |    |

|-----------------|---------------------------|----|

| 1 1 1           | コンピューティングセルアレイデコーダー       |    |

| 1 1 2           | インターマットシフトアレイ             |    |

| 1 1 2 e、1 1 2 f | データシフトライン                 |    |

| 1 1 3           | インターマットフォワードィングアレイ        |    |

| 1 1 3 g         | 第1データフォワードィングライン          |    |

| 1 1 3 h         | 第2データフォワードィングライン          |    |

| 1 1 4           | サブアレイコントローラ               |    |

| 2 0 1、2 0 2     | D R A M コンピューティングセルトポグラフィ |    |

| 7 1 5           | 確率的データアレイ                 | 10 |

| 7 1 6           | コンバーターツー確率アレイ             |    |

| 9 0 0           | システム構造                    |    |

| 9 1 0           | ハードウェアレイヤー                |    |

| 9 1 1           | P C I e                   |    |

| 9 1 2           | D I M M                   |    |

| 9 2 0           | ライブラリ及びドライバーレイヤー          |    |

| 9 2 1           | D P U ライブラリ               |    |

| 9 2 2           | D P U ドライバー               |    |

| 9 2 3           | D P U コンパイラ               |    |

| 9 3 0           | フレームワークレイヤー               |    |

| 9 4 0           | アプリケーションレイヤー              | 20 |

【図1】

【図2A】

【図2B】

【図3】

【図4A】

【図4B】

【図4C】

【 図 5 】

【図 6 A】

【図6B】

【図 6 C】

【図 6 D】

【図 6 E】

【図 6 F】

【図 6 G】

【図 7】

【図 8 A】

【図 8 B】

【図9】

---

フロントページの続き

(72)発明者 牛 迪 民

アメリカ合衆国， 94087， カリフォルニア州， サニーベール， ホルトハウス テラス

527

(72)発明者 マラディ， クリシュナ

アメリカ合衆国， 95135， カリフォルニア州， サン ノゼ， ロートレック ドライブ

4196

(72)発明者 鄭 宏 忠

アメリカ合衆国， 95032， カリフォルニア州， ロス ガトス， カールトン アベニュー

- #6， 120

審査官 後藤 彰

(56)参考文献 特表2016-536733(JP,A)

特表2016-532919(JP,A)

米国特許出願公開第2009/0164789(US,A1)

米国特許第4068305(US,A)

(58)調査した分野(Int.Cl., DB名)

G06F 12/00