등록특허 10-2534756

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2023년05월18일

(11) 등록번호 10-2534756

(24) 등록일자 2023년05월16일

- (51) 국제특허분류 (Int. Cl.)

*H01L 21/66* (2006.01) *B24B 37/013* (2012.01)

*B24B 49/10* (2006.01) *B24B 49/12* (2006.01)

*H01L 21/304* (2006.01) *H01L 21/306* (2006.01)

*H01L 21/3105* (2006.01)

- (52) CPC특허분류

*H01L 22/26* (2013.01)

*B24B 37/013* (2013.01)

- (21) 출원번호 10-2017-7004233

- (22) 출원일자(국제) 2015년07월09일

심사청구일자 2020년07월08일

- (85) 번역문제출일자 2017년02월15일

- (65) 공개번호 10-2017-0031225

- (43) 공개일자 2017년03월20일

- (86) 국제출원번호 PCT/US2015/039780

- (87) 국제공개번호 WO 2016/010821

국제공개일자 2016년01월21일

- (30) 우선권주장

14/333,395 2014년07월16일 미국(US)

62/026,306 2014년07월18일 미국(US)

- (56) 선행기술조사문헌

JP2013526080 A\*

US20120274932 A1\*

KR1020140025471 A

\*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 24 항

심사관 : 홍종선

(54) 발명의 명칭 증착 이전에 측정이 이루어지는 폴리싱

**(57) 요약**

폴리싱을 제어하는 방법은 베이스 측정(base measurement)를 저장하는 단계를 포함하며, 베이스 측정은, 기판 상에 적어도 하나의 층을 증착한 이후의 그리고 적어도 하나의 층 위에 외측 층을 증착하기 이전의 기판의 측정이다. 외측 층의 증착 이후 그리고 기판 상의 외측 층의 폴리싱 동안, 폴리싱 동안의 기판의 원시 측정들의 시퀀스(뒷면에 계속)

**대 표 도**

스가 인시츄 모니터링 시스템으로부터 수신된다. 원시 측정 및 베이스 측정을 사용하여, 정규화된 측정들의 시퀀스를 생성하기 위해, 각각의 원시 측정이 정규화된다. 정규화된 측정들의 시퀀스로부터의 적어도 하나의 정규화된 측정에 기초하여, 폴리싱 레이트에 대한 조정 또는 폴리싱 종점 중 적어도 하나가 결정된다.

(52) CPC특허분류

*B24B 49/105* (2013.01)

*B24B 49/12* (2013.01)

*H01L 21/304* (2013.01)

*H01L 21/30625* (2013.01)

*H01L 21/31053* (2013.01)

*H01L 22/12* (2013.01)

(72) 발명자

**퀴안, 준**

미국 94087 캘리포니아 써니베일 더블린 웨이 575

**세키네, 타케토**

미국 95014 캘리포니아 쿠퍼티노 스톤브릿지 22791

**레옹, 갈렌 씨.**

미국 95008 캘리포니아 캠벨 세이디 코트 4040

**휴이, 시드니 괴.**

미국 94539 캘리포니아 프리몬트 클레이어 뷰 테라스

3333

## 명세서

### 청구범위

#### 청구항 1

하나 또는 그 초과의 컴퓨터 저장 매체에 저장된 컴퓨터 프로그램으로서,

상기 컴퓨터 프로그램은, 하나 또는 그 초과의 컴퓨터들에 의해 실행될 때, 상기 하나 또는 그 초과의 컴퓨터들로 하여금 동작들을 수행하게 하는 명령들을 포함하고,

상기 동작들은:

베이스 측정(base measurement)을 저장하는 동작 – 상기 베이스 측정은, 반도체 웨이퍼 및 상기 반도체 웨이퍼 위에 놓이는 적어도 하나의 층을 포함하는 기판의 와전류(eddy current) 측정이고, 상기 와전류 측정은 상기 적어도 하나의 층 위의 전도성 외측(outer) 층의 중착 이전에 수행됨 –;

상기 적어도 하나의 층 위의 상기 전도성 외측 층의 중착 이후 그리고 상기 기판 상의 상기 전도성 외측 층의 폴리싱(polishing) 동안, 상기 기판의 와전류들의 원시 측정(raw measurement)들의 시퀀스를 인시츄(in-situ) 모니터링 시스템으로부터 수신하는 동작 – 상기 인시츄 모니터링 시스템은 인시츄 와전류 모니터링 시스템임 –;

상기 원시 측정들에서의 노이즈를 감소시키기 위해, 상기 원시 측정들을 사용하여 그리고 상기 베이스 측정을 사용하여, 조정된 측정들의 시퀀스를 생성하는 동작; 및

적어도 상기 조정된 측정들의 시퀀스에 기초하여, 폴리싱 레이트에 대한 조정 또는 폴리싱 종점 중 적어도 하나를 결정하는 동작을 포함하는,

하나 또는 그 초과의 컴퓨터 저장 매체에 저장된 컴퓨터 프로그램.

#### 청구항 2

제1항에 있어서,

상기 베이스 측정은, 상기 적어도 하나의 층의 중착 이후이나 상기 적어도 하나의 층의 에칭 이전에, 또는 상기 적어도 하나의 층의 에칭 이후이나 배리어(barrier) 층의 중착 이전에, 또는 상기 배리어 층의 중착 이후이나 상기 외측 층의 중착 이전에 측정되는 상기 기판의 와전류 측정인,

하나 또는 그 초과의 컴퓨터 저장 매체에 저장된 컴퓨터 프로그램.

#### 청구항 3

하나 또는 그 초과의 컴퓨터 저장 매체에 저장된 컴퓨터 프로그램으로서,

상기 컴퓨터 프로그램은, 하나 또는 그 초과의 컴퓨터들에 의해 실행될 때, 상기 하나 또는 그 초과의 컴퓨터들로 하여금 동작들을 수행하게 하는 명령들을 포함하고,

상기 동작들은:

베이스 측정을 저장하는 동작 – 상기 베이스 측정은, 반도체 웨이퍼 및 상기 반도체 웨이퍼 위에 놓이는 적어도 하나의 층을 포함하는 기판의 분광 사진(spectrographic) 측정이고, 상기 분광 사진 측정은 상기 적어도 하나의 층 위의 외측(outer) 층의 중착 이전에 수행되고, 상기 적어도 하나의 층은 적어도 하나의 유전체 층을 포함하며, 상기 베이스 측정은 상기 기판으로부터 반사되는 광의 스펙트럼을 나타내는 베이스 스펙트럼(base spectrum)임 –;

상기 적어도 하나의 층 위의 상기 외측 층의 중착 이후 그리고 상기 기판 상의 상기 외측 층의 폴리싱 동안, 상기 기판으로부터 반사되는 광의 스펙트럼들의 원시 측정들의 시퀀스를 인시츄 모니터링 시스템으로부터 수신하는 동작 – 상기 인시츄 모니터링 시스템은 인시츄 광학 모니터링 시스템임 –;

상기 원시 측정들에서의 노이즈를 감소시키기 위해, 상기 원시 측정들을 사용하여 그리고 상기 베이스 측정을

사용하여, 조정된 측정들의 시퀀스를 생성하는 동작; 및

적어도 상기 조정된 측정들의 시퀀스에 기초하여, 폴리싱 레이트에 대한 조정 또는 폴리싱 종점 중 적어도 하나를 결정하는 동작을 포함하는,

하나 또는 그 초과의 컴퓨터 저장 매체에 저장된 컴퓨터 프로그램.

#### 청구항 4

제3항에 있어서,

상기 외측 층은 비-금속 층인,

하나 또는 그 초과의 컴퓨터 저장 매체에 저장된 컴퓨터 프로그램.

#### 청구항 5

제4항에 있어서,

상기 베이스 스펙트럼은, 금속 층 또는 반도체 웨이퍼 위에 놓이는 복수의 유전체 층들의 층착 이후 그리고 상기 복수의 층착된 유전체 층 위에 상기 비-금속 층을 층착하기 이전에, 상기 기판으로부터 반사되는 광의 스펙트럼인,

하나 또는 그 초과의 컴퓨터 저장 매체에 저장된 컴퓨터 프로그램.

#### 청구항 6

제5항에 있어서,

상기 베이스 스펙트럼은, 상기 복수의 유전체 층들의 층착 이후이나 에칭 프로세스 이전에, 또는 상기 에칭 프로세스 이후이나 질화물 층의 층착 이전에, 또는 상기 질화물 층의 층착 이후이나 폴리싱을 받는 상기 비-금속 층을 층착하기 전에 측정되는 상기 기판으로부터 반사되는 광의 스펙트럼인,

하나 또는 그 초과의 컴퓨터 저장 매체에 저장된 컴퓨터 프로그램.

#### 청구항 7

제1항 내지 제6항 중 어느 한 항에 있어서,

상기 조정된 측정들의 시퀀스를 생성하는 것은,

상기 원시 측정 및 상기 베이스 측정을 사용하여, 정규화된 측정들의 시퀀스를 생성하기 위해, 원시 측정의 시퀀스 내의 각각의 원시 측정을 정규화하는 것을 포함하는,

하나 또는 그 초과의 컴퓨터 저장 매체에 저장된 컴퓨터 프로그램.

#### 청구항 8

제7항에 있어서,

정규화하는 것은 나눗셈 연산(division operation)을 포함하고, 여기서, 상기 원시 측정이 문자에 있고, 상기 베이스 측정은 분모에 있는,

하나 또는 그 초과의 컴퓨터 저장 매체에 저장된 컴퓨터 프로그램.

#### 청구항 9

제8항에 있어서,

상기 나눗셈 연산은,

$$R = \frac{A - D_A}{B - D_B}$$

를 만족시키는 정규화된 측정(R)를 계산하고,

여기서, A는 원시 측정이고, B는 베이스 측정이며, 그리고  $D_A$  및  $D_B$ 는, 상기 인시츄 모니터링 시스템에 의해 기판이 측정되지 않을 때에 상기 인시츄 모니터링 시스템에 의해 이루어지는 측정들인,

하나 또는 그 초과의 컴퓨터 저장 매체에 저장된 컴퓨터 프로그램.

#### 청구항 10

기판을 제조하는 방법으로서,

반도체 웨이퍼 위에 적어도 하나의 층을 증착하는 단계;

기판의 베이스 측정을 획득하는 단계 — 상기 베이스 측정은, 상기 적어도 하나의 층의 증착 이후의 그리고 상기 적어도 하나의 층 위의 외측 층의 증착 이전의 상기 기판의 와전류 측정이고, 상기 외측 층은 전도성 층임 —;

상기 적어도 하나의 층 상에 상기 외측 층을 증착하는 단계;

상기 기판의 상기 외측 층을 폴리싱하는 단계;

상기 외측 층의 폴리싱 동안, 인시츄 모니터링 시스템에 의해 상기 기판의 와전류들의 원시 측정들의 시퀀스를 획득하는 단계 — 상기 인시츄 모니터링 시스템은 인시츄 와전류 모니터링 시스템임 —;

상기 원시 측정들에서의 노이즈를 감소시키기 위해, 상기 원시 측정들을 사용하여 그리고 상기 베이스 측정을 사용하여, 조정된 측정들의 시퀀스를 생성하는 단계; 및

상기 조정된 측정들의 시퀀스로부터의 적어도 하나의 조정된 측정에 기초하여, 폴리싱 레이트에 대한 조정 또는 폴리싱 종점 중 적어도 하나를 결정하는 단계를 포함하는,

기판을 제조하는 방법.

#### 청구항 11

제10항에 있어서,

상기 적어도 하나의 층은 상기 반도체 웨이퍼 위의 적어도 하나의 하부(underlying) 전도성 층 및 적어도 하나의 유전체 층을 포함하는 복수의 층들인,

기판을 제조하는 방법.

#### 청구항 12

제11항에 있어서,

상기 베이스 측정은, 상기 기판 상에 복수의 교번하는 층들을 증착한 이후이나 상기 기판을 에칭하기 이전의, 또는 상기 기판을 에칭한 이후이나 배리어 층을 증착하기 이전의, 또는 배리어 층을 증착한 이후이나 상기 전도성 층을 증착하기 이전의, 상기 기판의 와전류 측정인,

기판을 제조하는 방법.

#### 청구항 13

제12항에 있어서,

상기 복수의 교번하는 층들은 폴리실리콘 및 실리콘 산화물을 포함하는,

기판을 제조하는 방법.

#### 청구항 14

기판을 제조하는 방법으로서,

반도체 웨이퍼 위에 적어도 하나의 층을 증착하는 단계 — 상기 적어도 하나의 층은 적어도 하나의 유전체 층을

포함함 –;

기판의 베이스 측정을 획득하는 단계 – 상기 베이스 측정은, 상기 적어도 하나의 층의 증착 이후의 그리고 상기 적어도 하나의 층 위의 외측 층의 증착 이전의 상기 기판의 측정이고, 상기 베이스 측정은 상기 기판으로부터 반사되는 광의 스펙트럼을 나타내는 베이스 스펙트럼임 –;

상기 적어도 하나의 층 상에 상기 외측 층을 증착하는 단계;

상기 기판의 상기 외측 층을 폴리싱하는 단계;

상기 외측 층의 폴리싱 동안, 인시츄 모니터링 시스템에 의해 상기 기판으로부터 반사되는 광의 스펙트럼들의 원시 측정들의 시퀀스를 획득하는 단계 – 상기 인시츄 모니터링 시스템은 인시츄 광학 모니터링 시스템임 –;

상기 원시 측정들에서의 노이즈를 감소시키기 위해, 상기 원시 측정들을 사용하여 그리고 상기 베이스 측정을 사용하여, 조정된 측정들의 시퀀스를 생성하는 단계; 및

상기 조정된 측정들의 시퀀스로부터의 적어도 하나의 조정된 측정에 기초하여, 폴리싱 레이트에 대한 조정 또는 폴리싱 종점 중 적어도 하나를 결정하는 단계를 포함하는,

기판을 제조하는 방법.

### 청구항 15

제14항에 있어서,

상기 외측 층은 비-금속 층인,

기판을 제조하는 방법.

### 청구항 16

제15항에 있어서,

상기 베이스 스펙트럼은, 금속 층 또는 반도체 웨이퍼 위에 놓이는 복수의 유전체 층들의 증착 이후 그리고 상기 복수의 증착된 유전체 층 위에 비-금속 층을 증착하기 이전에, 상기 기판으로부터 반사되는 광의 스펙트럼인,

기판을 제조하는 방법.

### 청구항 17

제14항 내지 제16항 중 어느 한 항에 있어서,

상기 기판 상에 교변하는 비-금속 층들을 증착하는 단계 – 상기 교변하는 비-금속 층들은 적어도 하나의 유전체 층을 포함함 – ;

계단 구조를 생성하기 위해, 상기 기판을 에칭하는 단계;

상기 에칭된 기판 상에 중간 층을 증착하는 단계; 및

상기 중간 층 상에 최외측 층을 증착하는 단계를 포함하는,

기판을 제조하는 방법.

### 청구항 18

제17항에 있어서,

베이스 스펙트럼을 측정하는 것은, 상기 기판 상에 교변하는 산화물 및 질화물 층들을 증착한 이후, 하지만 상기 기판을 에칭하기 전에, 또는 상기 기판을 에칭한 이후, 하지만 질화물 층을 증착하기 전에, 또는 질화물 층을 증착한 이후, 하지만 상기 최외측 층을 증착하기 전에, 상기 베이스 스펙트럼을 측정하는 것을 포함하는,

기판을 제조하는 방법.

### 청구항 19

제10항 내지 제16항 중 어느 한 항에 있어서,

상기 조정된 측정들의 시퀀스를 생성하는 단계는,

정규화된 측정들의 시퀀스를 생성하기 위해, 상기 원시 측정 및 상기 베이스 측정을 사용하여, 상기 원시 측정들의 시퀀스 내의 각각의 원시 측정을 정규화하는 단계를 포함하는,

기판을 제조하는 방법.

## 청구항 20

집적 회로 제조 시스템으로서,

기판을 수용하고 그리고 상기 기판 상에 층들의 스택을 증착하도록 구성된 증착 시스템 – 상기 층들의 스택은 폴리싱을 받을 외측 층 및 상기 외측 층 아래에 있는 적어도 하나의 층을 포함하고, 상기 외측 층은 전도성 층임 – ;

상기 적어도 하나의 층의 증착 이후 그리고 상기 외측 층의 증착 이전에 상기 기판의 와전류 측정을 생성하도록 구성된 계측 시스템; 및

상기 기판을 수용하고 그리고 상기 기판 상의 상기 외측 층을 폴리싱하도록 구성된 폴리싱 시스템을 포함하고,

상기 폴리싱 시스템은 동작들을 수행하도록 구성된 제어기를 포함하며,

상기 동작들은:

상기 계측 시스템으로부터 상기 측정을 수신하고, 상기 측정을 베이스 측정으로서 저장하는 동작;

인시츄 와전류 모니터링 시스템으로부터 폴리싱 동안 상기 기판의 와전류들의 원시 측정들의 시퀀스를 수신하는 동작;

상기 원시 측정들에서의 노이즈를 감소시키기 위해, 상기 원시 측정들을 사용하여 그리고 상기 베이스 측정을 사용하여, 조정된 측정들의 시퀀스를 생성하는 동작; 및

상기 조정된 측정들의 시퀀스로부터의 적어도 하나의 조정된 측정에 기초하여, 폴리싱 레이트에 대한 조정 또는 폴리싱 종점 중 적어도 하나를 결정하는 동작을 포함하는,

집적 회로 제조 시스템.

## 청구항 21

집적 회로 제조 시스템으로서,

기판을 수용하고 그리고 상기 기판 상에 층들의 스택을 증착하도록 구성된 증착 시스템 – 상기 층들의 스택은 폴리싱을 받을 외측 층 및 상기 외측 층 아래에 있는 적어도 하나의 층을 포함하고, 상기 적어도 하나의 층은 적어도 하나의 유전체 층을 포함함 – ;

상기 적어도 하나의 층의 증착 이후 그리고 상기 외측 층의 증착 이전에 상기 기판으로부터 반사되는 광의 스펙트럼의 측정을 생성하도록 구성된 계측 시스템; 및

상기 기판을 수용하고 그리고 상기 기판 상의 상기 외측 층을 폴리싱하도록 구성된 폴리싱 시스템을 포함하고,

상기 폴리싱 시스템은 동작들을 수행하도록 구성된 제어기를 포함하며,

상기 동작들은:

상기 계측 시스템으로부터 상기 측정을 수신하고, 상기 측정을 베이스 측정으로서 저장하는 동작;

인시츄 광학 모니터링 시스템으로부터 폴리싱 동안 상기 기판으로부터 반사되는 광의 스펙트럼들의 원시 측정들의 시퀀스를 수신하는 동작;

상기 원시 측정들에서의 노이즈를 감소시키기 위해, 상기 원시 측정들을 사용하여 그리고 상기 베이스 측정을 사용하여, 조정된 측정들의 시퀀스를 생성하는 동작; 및

상기 조정된 측정들의 시퀀스로부터의 적어도 하나의 조정된 측정에 기초하여, 폴리싱 레이트에 대한

조정 또는 폴리싱 종점 중 적어도 하나를 결정하는 동작을 포함하는,

집적 회로 제조 시스템.

### 청구항 22

제20항 또는 제21항에 있어서,

상기 계측 시스템은 상기 증착 시스템 내의 인-라인 계측 스테이션인,

집적 회로 제조 시스템.

### 청구항 23

제20항 또는 제21항에 있어서,

상기 계측 시스템은 독립형 계측 시스템인,

집적 회로 제조 시스템.

### 청구항 24

제20항 또는 제21항에 있어서,

상기 조정된 측정들의 시퀀스를 생성하는 것은,

정규화된 측정들의 시퀀스를 생성하기 위해, 원시 측정 및 상기 베이스 측정을 사용하여, 상기 원시 측정들의 시퀀스 내의 각각의 원시 측정을 정규화하는 것을 포함하는,

집적 회로 제조 시스템.

## 발명의 설명

### 기술 분야

[0001] 본 개시내용은, 예를 들어 기판들의 화학 기계적 폴리싱 동안의 폴리싱 제어 방법들에 관한 것이다.

### 배경 기술

[0002] 전형적으로, 집적 회로는 실리콘 웨이퍼 상의 전도성, 반도체성, 또는 절연 층들의 순차적인 증착에 의해 기판 상에 형성된다. 하나의 제조 단계는 비-평면 표면 위에 필러(filler) 층을 증착하는 것 및 그러한 필러 층을 평탄화하는 것을 수반한다. 특정 적용예들에 대해, 패터닝된 층의 상단 표면이 노출될 때까지 필러 층이 평탄화된다. 예를 들어, 산화물 필러 층이, 절연 층 내의 트렌치들 또는 홀들을 충진(fill)하기 위해, 패터닝된 절연 층 상에 증착될 수 있다. 평탄화 이후, 비 평면 표면 위에 미리 결정된 두께가 남을 때 까지 또는 아래에 있는(underlying) 층의 상단 표면이 노출될 때 까지, 필러 층이 평탄화된다. 다른 적용예들에 대해, 아래에 있는 패터닝된 층 위에 미리 결정된 두께가 남을 때 까지, 필러 층이 평탄화된다. 또한, 일반적으로, 기판 표면의 평탄화가 포토리소그래피를 위해 요구된다.

[0003] 화학 기계적 폴리싱(CMP)은 하나의 용인된 평탄화 방법이다. 이러한 평탄화 방법은 전형적으로, 기판이 캐리어 헤드 상에 장착될 것을 요구한다. 전형적으로, 기판의 노출된 표면은 회전하는 폴리싱 패드(polishing pad)에 대하여(against) 배치된다. 캐리어 헤드는 기판 상에 제어 가능한 로드(load)를 제공하여 그려한 기판을 폴리싱 패드에 대하여 가압(push)한다. 전형적으로, 폴리싱 액체, 이를테면 연마 입자(abrasive particle)들을 갖는 슬러리가 폴리싱 패드의 표면에 공급된다.

[0004] CMP에서의 하나의 문제는, 폴리싱 프로세스가 완료되었는지의 여부, 예를 들어, 기판 층이 희망하는 편평도(flatness) 또는 두께로 평탄화되었는지의 여부, 또는 희망하는 재료량이 제거된 때를 결정하는 것이다. 기판 층의 초기 두께, 슬러리 조성, 폴리싱 패드 컨디션, 폴리싱 패드와 기판 사이의 상대 속도, 각각의 증착되는 층의 두께들 및 기판에 대한 로드에 있어서의 편차(variation)들이 재료 제거율의 편차들을 야기할 수 있다. 이러한 편차들은 폴리싱 종점(endpoint)에 도달하는 데에 필요한 시간의 편차들을 야기한다. 따라서, 단지 폴

리성 시간의 함수로서 폴리싱 종점을 결정하는 것이 가능하지 않을 수도 있다.

[0005] 몇몇 시스템들에서, 기판은, 예를 들어 폴리싱 패드 내의 원도우를 통해, 폴리싱 동안 인시츄(in-situ)로 광학적으로 모니터링된다. 하지만, 기존의 광학 모니터링 기법들은 반도체 디바이스 제조업자들의 증대되는 요구들을 충족시키지 못할 수도 있다.

### 발명의 내용

#### 해결하려는 과제

#### 과제의 해결 수단

[0006] 몇몇 광학 모니터링 프로세스들에서, 예를 들어 CMP의 폴리싱 프로세스 동안 인시츄로 측정된 스펙트럼은, 최적 매칭 기준 스펙트럼(best matching reference spectrum)을 발견하기 위해 기준 스펙트럼들의 라이브러리와 비교된다. 인시츄로 측정된 스펙트럼은 결과들을 왜곡시킬 수 있는 다수의 노이즈 성분(component)들을 포함할 수 있어서, 기준 스펙트럼들의 라이브러리와의 비교를 부정확하게 한다. 하나의 현저한 노이즈 성분은 하층(underlayer)의 변화(variation)이다. 즉, 프로세스 변화들로 인해, 폴리싱되는 층 아래의 다양한 재료 층들은 굴절률들 및 두께들에 있어서 기판마다 다를 수 있다.

[0007] 이러한 문제들을 해결할 수 있는 정규화(normalization) 방법은, 하나 또는 그 초과의 유전체 층들을 증착한 후, 하지만 폴리싱될 외측 층(들)을 증착하기 전에, 기판의 베이스 스펙트럼(base spectrum)을 측정하는 것을 포함한다. 측정된 베이스 스펙트럼은 폴리싱 동안 획득된 각각의 측정된 스펙트럼들을 정규화하는 데에 사용되며, 이는 이후 기준 스펙트럼들의 라이브러리와 비교되어, 최적 매칭 기준 스펙트럼을 찾을 수 있다.

[0008] 일 양상에서, 머신 판독가능 저장 디바이스에 유형적으로 구현되는 컴퓨터 프로그램 제품은 폴리싱을 제어하는 방법을 수행하기 위한 명령들을 포함한다. 방법은 베이스 스펙트럼을 저장하는 단계를 포함하고, 베이스 스펙트럼은, 금속 층 또는 반도체 웨이퍼 위에 놓이는 복수의 증착되는 유전체 층들의 증착 이후 그리고 복수의 증착되는 유전체 층 위에 비-금속 층을 증착하기 전에, 기판으로부터 반사되는 광의 스펙트럼이다. 복수의 증착되는 유전체 층 위에 비-금속 층을 증착한 이후 그리고 기판 상의 비-금속 층을 폴리싱하는 동안, 폴리싱 동안 기판으로부터 반사되는 광의 원시 스펙트럼들(raw spectra)의 시퀀스의 측정들이 인시츄 광학 모니터링 시스템(in-situ optical monitoring system)으로부터 수신된다. 원시 스펙트럼들의 시퀀스에서의 각각의 원시 스펙트럼은, 원시 스펙트럼과 베이스 스펙트럼을 사용하여, 정규화된 스펙트럼들의 시퀀스를 생성하기 위해 정규화된다. 폴리싱 레이트에 대한 조정 또는 폴리싱 종점 중 적어도 하나가, 정규화된 스펙트럼들의 시퀀스로부터의 적어도 하나의 정규화된 미리 결정된 스펙트럼에 기초하여 결정된다.

[0009] 다른 양상에서, 기판을 제조하기 위한 방법은 기판의 반도체 웨이퍼 또는 금속 층 상에 적어도 하나의 유전체 층을 증착하는 단계를 포함한다. 기판으로부터 반사되는 베이스 스펙트럼이, 적어도 하나의 유전체 층을 증착한 이후, 하지만 최외측(outermost) 층을 증착하기 전에, 광학 계측 시스템(optical metrology system)에 의해 측정된다. 최외측 층은 적어도 하나의 유전체 층 상에 증착되고, 기판의 최외측 층은 폴리싱되며, 그리고 최외측 층의 폴리싱 동안, 기판으로부터 반사되는 원시 스펙트럼들의 시퀀스가 인시츄 광학 모니터링 시스템에 의해 측정된다. 원시 스펙트럼들의 시퀀스에서의 각각의 원시 스펙트럼은, 원시 스펙트럼과 증착 후(post deposition) 베이스 스펙트럼을 사용하여, 정규화된 스펙트럼들의 시퀀스를 생성하기 위해 정규화되며, 그리고 폴리싱 레이트에 대한 조정 또는 폴리싱 종점 중 적어도 하나가, 정규화된 스펙트럼들의 시퀀스로부터의 적어도 하나의 정규화된 미리 결정된 스펙트럼에 기초하여 결정된다.

[0010] 다른 양상에서, 집적 회로 제조 시스템은 증착 시스템, 계측 시스템 및 폴리싱 시스템을 포함한다. 증착 시스템은, 기판을 수용하고 그리고 금속 층 또는 반도체 기판 위에 놓이는 층들의 스택을 증착하도록 구성되며, 층들의 스택은, 폴리싱을 받을 비-금속 층 및 비-금속 층 아래에 있는 적어도 하나의 유전체 층을 포함한다. 계측 시스템은, 적어도 하나의 유전체 층의 증착 이후 그리고 비-금속 층의 증착 이전에 기판으로부터 반사되는 광의 스펙트럼의 측정을 생성하도록 구성된다. 폴리싱 시스템은, 기판을 수용하고 기판 상의 비-금속 층을 폴리싱하도록 구성되며, 그리고 동작들을 수행하도록 구성된 제어기를 포함하며, 동작들은: 계측 시스템으로부터 광의 스펙트럼의 측정을 수신하고, 그러한 측정을 베이스 스펙트럼으로서 저장하는 것; 인시츄 광학 모니터링 시스템에 의해, 폴리싱 동안 기판으로부터 반사되는 광의 원시 스펙트럼들의 시퀀스의 측정들을 수신하는 것; 원시 스펙트럼 및 베이스 스펙트럼을 사용하여, 정규화된 스펙트럼들의 시퀀스를 생성하기 위해, 원

시 스펙트럼들의 시퀀스에서의 각각의 원시 스펙트럼을 정규화하는 것; 및 정규화된 스펙트럼들의 시퀀스로부터의 적어도 하나의 정규화된 미리 결정된 스펙트럼에 기초하여, 폴리싱 레이트에 대한 조정 또는 폴리싱 종점 중 적어도 하나를 결정하는 것을 포함한다.

[0011] 다른 양상에서, 폴리싱 시스템은 캐리어, 플래튼(platen), 인시츄 광학 모니터링 시스템 및 제어기를 포함한다. 상기 캐리어는 기판을 장착하도록 구성되고, 상기 기판은, 금속 층 또는 반도체 기판 위에 놓이는 층들의 스택을 포함하며, 층들의 스택은, 폴리싱을 받을 비-금속 층 및 비-금속 층 아래에 있는 복수의 중착되는 유전체 층들을 포함한다. 플래튼은, 기판과 접촉하도록 구성되는 폴리싱 패드를 수용한다. 제어기는 동작들을 수행하도록 구성되며, 동작들은: 복수의 중착되는 유전체 층들의 중착 이후 그리고 비-금속 층의 중착 이전에 기판으로부터 반사되는 광의 스펙트럼인 중착 후 베이스 스펙트럼을 저장하는 것; 인시츄 광학 모니터링 시스템에 의해, 폴리싱 동안 기판으로부터 반사되는 광의 원시 스펙트럼들의 시퀀스의 측정들을 수신하는 것; 원시 스펙트럼 및 중착 후 베이스 스펙트럼을 사용하여, 정규화된 스펙트럼들의 시퀀스를 생성하기 위해, 원시 스펙트럼들의 시퀀스에서의 각각의 원시 스펙트럼을 정규화하는 것; 및 정규화된 스펙트럼들의 시퀀스로부터의 적어도 하나의 정규화된 미리 결정된 스펙트럼에 기초하여, 폴리싱 레이트에 대한 조정 또는 폴리싱 종점 중 적어도 하나를 결정하는 것을 포함한다.

[0012] 다른 양상에서, 머신 판독가능 저장 디바이스에 유형적으로 구현되는 컴퓨터 프로그램 제품은, 하나 또는 그 초과의 컴퓨터들에 의해 실행될 때, 하나 또는 그 초과의 컴퓨터들로 하여금 동작들을 수행하게 하는 명령들을 포함하며, 동작들은: 베이스 측정(base measurement)을 수신하는 것을 포함하고, 베이스 측정은, 반도체 웨이퍼 위에 놓이는 적어도 하나의 층의 중착 이후의 그리고 적어도 하나의 층 위에 전도성 층을 중착하기 이전의 기판의 와전류(eddy current) 측정이다. 적어도 하나의 층 위에 전도성 층을 중착한 이후 그리고 기판 상의 전도성 층의 폴리싱 동안, 기판의 원시 측정들의 시퀀스가 인시츄 와전류 모니터링 시스템으로부터 수신된다. 원시 측정 및 베이스 측정을 사용하여, 정규화된 측정들의 시퀀스를 생성하기 위해, 원시 측정의 시퀀스에서의 각각의 원시 측정이 정규화되며, 그리고 적어도 정규화된 측정들의 시퀀스에 기초하여, 폴리싱 레이트에 대한 조정 또는 폴리싱 종점 중 적어도 하나를 결정하는 것을 포함한다.

[0013] 구현예들은 다음의 장점을 중 하나 또는 그 초과를 선택적으로 포함할 수 있다. 기판의 폴리싱 종점을 결정함에 있어서의 정확성은, 기판들 상의, 아래에 있는 중착된 층들의 두께들 및/또는 굴절률들의 편차들로부터 노이즈를 필터링함으로써 개선될 수 있다. 폴리싱 동안, 기판의 스펙트럼 측정들을 획득함으로써, 폴리싱을 받고 있는 최외측 재료 층의 두께가 추적될 수 있다.

### 도면의 간단한 설명

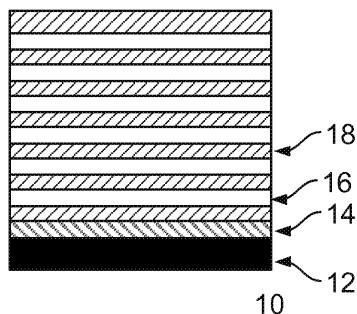

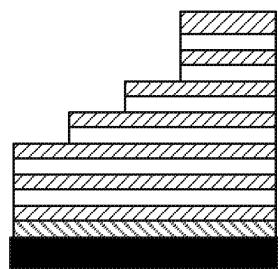

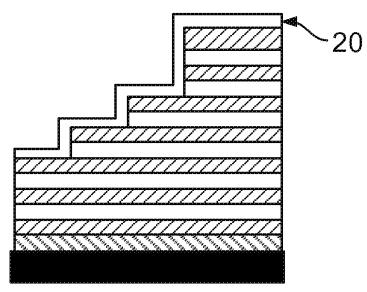

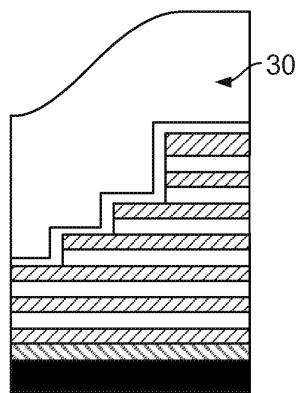

[0014] 도 1a-1e는 폴리싱 이전, 폴리싱 동안 및 폴리싱 이후의 예시적인 기판의 개략적인 단면도들이다.

[0015] 도 2는 폴리싱 장치의 예의 개략적인 단면도를 예시한다.

[0016] 도 3은 다수의 구역들을 갖는 기판의 개략적인 평면도를 예시한다.

[0017] 도 4는 폴리싱 패드의 평면도를 예시하며, 그리고 기판 상에서 인시츄 측정들이 취해지는 위치들을 도시한다.

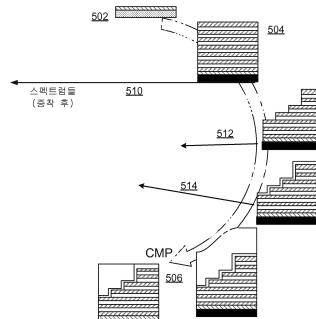

[0018] 도 5는 중착 후 베이스 스펙트럼들이 측정될 수 있는 예시적인 기판의 상이한 제조 스테이지들을 예시한다.

[0019] 도 6은 측정된 스펙트럼으로부터 생성되는 값들의 시퀀스를 예시한다.

[0020] 도 7은 값들의 시퀀스에 대해 피팅(fit)되는 선형 함수(linear function)를 예시한다.

[0021] 도 8은 기판을 제조하고 폴리싱 종점을 검출하기 위한 예시적인 프로세스의 흐름도이다.

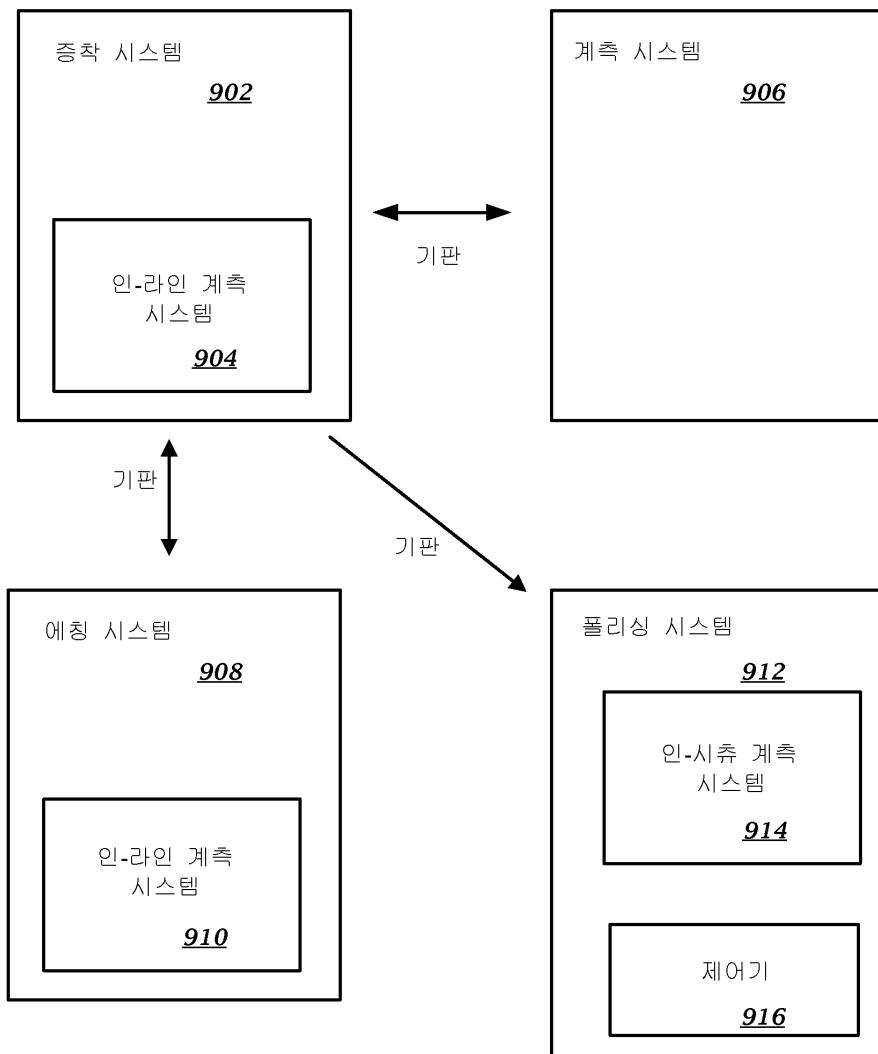

[0022] 도 9는 제조 퍼실리티(fabrication facility)의 개략적인 예시이다.

[0023] 다양한 도면들에서의 동일한 참조 번호들 및 명칭designation)들은 동일한 엘리먼트들을 나타낸다.

### 발명을 실시하기 위한 구체적인 내용

[0024] 기판은, 금속 층 또는 반도체 기판 위에 놓이는 층들의 스택을 포함할 수 있고, 층들의 스택은, 폴리싱을 받고 있는 최외측 층 및 그러한 최외측 층 위에 놓이는 복수의 중착된 층들을 포함한다. 몇몇

구현예들에서, 최외측 층은 비-금속 층이다. 예로서, 예를 들어 3D NAND 구조와 같은, 유전체 재료들의 교변하는 층들을 갖는 기판에 대해 전체적으로 참조된다. 다른 기판들이 사용될 수 있고, 도 1에서 설명되는 기판은 하나의 예임을 이해해야 한다.

[0016] 예로서, 도 1a에서의 기판(10)을 참조하면, 예를 들어 유리 시트 또는 반도체 웨이퍼와 같은 기판 베이스(12)는 중간 층 구조(14)를 선택적으로 포함하고, 이러한 중간 층 구조(14)는 하나 또는 그 초과의 패터닝된 또는 패터닝되지 않은 금속, 산화물, 질화물 또는 폴리실리콘 층들을 포함할 수 있다.

[0017] [0026] 적어도 하나의 부가적인 유전체 층이, 최외측 층과 중간 층 구조(14)(또는, 중간 층 구조가 없는 경우에는, 기판 베이스(12)) 사이에 증착된다. 몇몇 구현예들에서, 적어도 하나의 부가적인 유전체 층은 단일 층이다. 몇몇 구현예들에서, 적어도 하나의 유전체 층은, 층 구조(14) 위에, 예를 들어 전도성 재료 위에 증착되는 복수의 교변하는 층들을 포함한다. 교변하는 층들은, 제 1 층 재료(16)와 제 2 층 재료(18) 사이에서 교변한다. 예를 들어, 제 1 층(16), 예를 들어 산화물 또는 질화물이 전도성 층(14) 위에 증착된다. 제 2 층(18), 예를 들어 질화물 또는 산화물이 제 1 층 위에 증착된다. 예를 들어, 제 1 유전체 층은 실리콘 산화물일 수 있고, 제 2 유전체 층은 실리콘 질화물일 수 있다. 증착은, 재료들의 교변하는 층들을 생성하기 위해 한번 또는 그 초과의 횟수만큼 반복된다. 또한, 제 1 층(16) 또는 제 2 층(18)은 유전체라기 보다는 폴리실리콘일 수 있다.

[0018] [0027] 도 1b는 에칭 프로세스가 수행된 이후의 기판(10)을 예시한다. 기판(10)은 계단 구조를 생성하도록 에칭되었으며, 예를 들어, 기판은 패턴에 따라 패터닝 및 에칭되었다. 패터닝은 도 1a에서 설명된 기판(10)에 포토레지스트를 도포(apply)하는 것을 포함할 수 있고, 이는 에칭 이후의 구조, 예를 들어 계단 구조를 정의한다. 에칭 이후, 포토레지스트가 기판을 패터닝하는 데에 사용된 경우, 플라즈마 애싱 프로세스(plasma ashing process)가, 기판(10) 상에 남아있는 포토레지스트를 제거할 수 있다.

[0019] [0028] 도 1c는 계단 구조 위에 층(20)을 증착한 이후의 기판(10)을 예시한다. 층(20)은 질화물, 예를 들어 실리콘 질화물일 수 있다. 기판(10)에 따라, 질화물 층(20)은 3D NAND 플래시 메모리 구조에서 절연물, 배리어(barrier) 또는 전하 트랩(charge trap)으로서 작용할 수 있다.

[0020] [0029] 도 1d는 리세스(recess)들, 예를 들어 계단 구조에 의해 남겨지는 리세스를 충진하기에 충분히 두꺼운 외측 갭 필러 층(outer gap filler layer)(30)을 증착한 이후의 기판(10)을 예시한다. 외측 갭 필러 층(30)은 비-금속 층, 예를 들어 산화물이다. 예를 들어, 층(30)은 실리콘 산화물일 수 있다. 도 1e는 화학 기계적 평탄화 프로세스를 수행한 이후의 기판(10)을 예시한다. 화학 기계적 폴리싱은, 질화물 층(20)이 노출될 때 까지 기판을 평탄화하는 데에 사용될 수 있다.

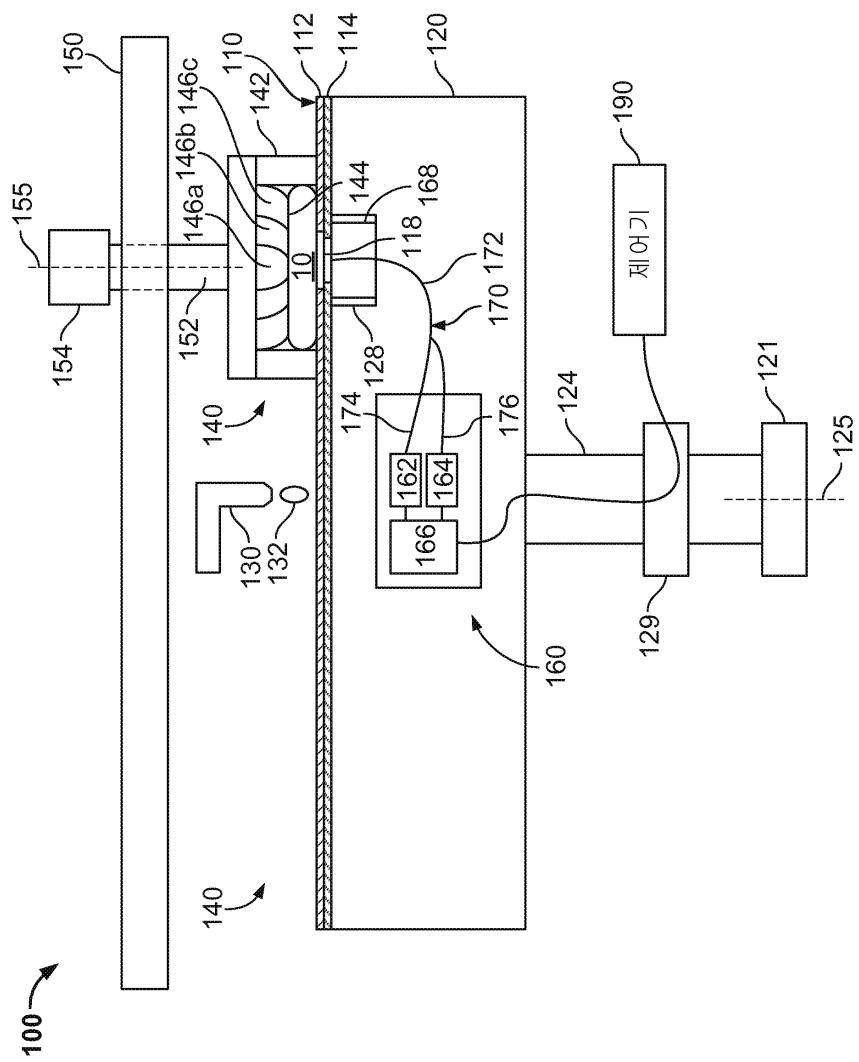

[0021] [0030] 도 2는 폴리싱 장치(100)의 예를 예시한다. 폴리싱 장치(100)는 회전가능한 디스크-형상의 플래튼(120)을 포함하고, 이러한 플래튼 상에 폴리싱 패드(110)가 위치된다. 플래튼은 축(125)을 중심으로 회전하도록 동작가능하다. 예를 들어, 모터(121)가 구동 샤프트(124)를 선회(turn)시켜서 플래튼(120)을 회전시킬 수 있다. 폴리싱 패드(110)는 외측 폴리싱 층(112) 및 보다 연성인 백킹(soft backing) 층(114)을 가지는 2-층 폴리싱 패드일 수 있다.

[0022] [0031] 폴리싱 장치(100)는 슬러리와 같은 폴리싱 액체(132)를 폴리싱 패드(110) 상으로 분배하기 위한 포트(130)를 포함할 수 있다. 폴리싱 장치는 또한, 폴리싱 패드(110)를 마멸시켜(abrade) 폴리싱 패드(110)를 일정한 연마 상태(abrasive state)로 유지하기 위한 폴리싱 패드 컨디셔너(conditioner)를 포함할 수 있다.

[0023] [0032] 폴리싱 장치(100)는 하나 또는 그 초과의 캐리어 헤드들(140)을 포함한다. 각각의 캐리어 헤드(140)는 기판(10)을 폴리싱 패드(110)에 대하여 유지하도록 동작가능하다. 각각의 캐리어 헤드(140)는, 각각의 개별 기판과 연관된 폴리싱 파라미터들, 예를 들어 압력의 독립적인 제어를 가질 수 있다.

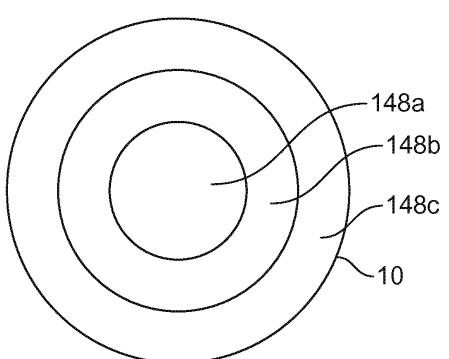

[0024] 특히, 각각의 캐리어 헤드(140)는 기판(10)을 가요성 멤브레인(144) 아래에 유지(retain)하기 위한 유지 링(retaining ring)(142)을 포함할 수 있다. 각각의 캐리어 헤드(140)는 또한, 멤브레인에 의해 정의되는 복수의 독립적으로 제어가능한 가압가능 챔버들, 예를 들어 3개의 챔버들(146a-146c)을 포함하고, 이러한 챔버들은 가요성 멤브레인(144) 상의 그리고 그에 따라 기판(10) 상의 관련된 구역들(148a-148c)에 독립적으로 제어 가능한 압력을 인가할 수 있다(도 3 참조). 도 3을 참조하면, 중앙 구역(148a)은 실질적으로 원형일 수 있고, 그리고 나머지 구역들(148b-148c)은 중앙 구역(148a) 주위의 동심의 환형 구역들일 수 있다. 비록 예시의 용이함을 위해 도 2 및 3에서 3개의 챔버들 만이 도시되지만, 하나 또는 2개의 챔버들, 또는 4개 또는 그 초과의 챔버들, 예를 들어 5개의 챔버들이 존재할 수 있다.

- [0025] [0034] 도 2로 돌아가면, 각각의 캐리어 헤드(140)는 지지 구조(150), 예를 들어 캐러셀(carousel) 또는 트랙에 의해 현수되고(suspended), 그리고 구동 샤프트(152)에 의해 캐리어 헤드 회전 모터(154)에 연결되며, 그에 따라 캐리어 헤드가 축(155)을 중심으로 회전할 수 있다. 선택적으로, 각각의 캐리어 헤드(140)는, 예를 들어 캐러셀(150) 상의 슬라이더들 상에서; 또는 캐러셀 그 자체의 회전 진동에 의해, 또는 트랙을 따르는 병진운동(translational)에 의해, 축방향으로 진동(oscillate)할 수 있다. 동작시, 플래튼은 그 중심 축(125)을 중심으로 회전되고, 그리고 각각의 캐리어 헤드는 그 중심 축(155)을 중심으로 회전되며 그리고 폴리싱 패드의 상단 표면을 가로질러 축방향으로 병진운동된다(translated).

- [0026] [0035] 단지 하나의 캐리어 헤드(140)만이 도시되었지만, 폴리싱 패드(110)의 표면적이 효율적으로 사용될 수 있도록, 보다 많은 캐리어 헤드들이 제공되어 부가적인 기판들을 유지할 수 있다. 따라서, 동시적인 폴리싱 프로세스를 위해 기판들을 유지하도록 적응되는 캐리어 헤드 어셈블리들의 수는, 적어도 부분적으로, 폴리싱 패드(110)의 표면적에 기초할 수 있다.

- [0027] [0036] 폴리싱 장치는 또한, 하기에서 논의되는 바와 같이 폴리싱 레이트를 조정할지의 여부 또는 폴리싱 레이트에 대한 조정을 결정하거나 종점 검출을 위해 사용될 수 있는 인시츄 광학 모니터링 시스템(160), 예를 들어 분광 사진(spectrographic) 모니터링 시스템을 포함할 수 있다. 폴리싱 패드를 통한 광학 액세스(optical access)는, 애퍼처(aperture)(즉, 패드를 통해 이어지는(run) 훌) 또는 솔리드 윈도우(solid window)(118)을 포함시킴으로써, 제공된다.

- [0028] [0037] 광학 모니터링 시스템(160)은 광 소스(162), 광 검출기(164), 그리고 제어기(190), 예를 들어 컴퓨터와 광 소스(162) 및 광 검출기(164) 사이에서 신호들을 송신 및 수신하기 위한 회로망(166)을 포함할 수 있다. 하나 또는 그 초과의 광섬유들, 예를 들어 두 갈래로 나뉜(bifurcated) 광섬유(170)가 사용되어, 광 소스(162)로부터의 광을 폴리싱 패드 내의 광학 액세스로 송신할 수 있고, 기판(10)으로부터 반사된 광을 검출기(164)로 송신할 수 있다.

- [0029] [0038] 회로망(166)의 출력은 디지털 전자 신호일 수 있고, 그러한 신호는 구동 샤프트(124) 내의 회전식 커플러(rotary coupler)(129), 예를 들어 슬립 링을 통해 광학 모니터링 시스템을 위한 제어기(190)에 전달된다. 유사하게, 제어기(190)로부터 회전식 커플러(129)를 통해 광학 모니터링 시스템(160)에 전달되는 디지털 전자 신호들 내의 제어 명령들에 응답하여, 광 소스가 턴 온 또는 턴 오프될 수 있다. 대안적으로, 회로망(166)은 무선 신호에 의해 제어기(190)와 통신할 수 있다.

- [0030] [0039] 광 소스(162)는 백색 광을 방출하도록 동작가능할 수 있다. 하나의 구현예에서, 방출되는 백색 광은 200-800 나노미터의 파장들을 갖는 광을 포함한다. 적합한 광 소스는 제논 램프 또는 제논 수은 램프이다. 몇몇 다른 구현예들에서, 방출되는 광은, 근적외선 스펙트럼의 파장들, 예를 들어 800-1400 나노미터의 파장들을 갖는 광을 포함한다.

- [0031] [0040] 광 검출기(164)는 분광계(spectrometer)일 수 있다. 분광계는 전자기 스펙트럼의 일부에 걸쳐 광의 세기를 측정하기 위한 광학 기구이다. 적절한 분광계는 격자(grating) 분광계이다. 분광계에 대한 전형적인 출력은, 파장(또는 주파수)의 함수로서의, 광의 세기이다.

- [0032] [0041] 상기 주목한 바와 같이, 광 소스(162) 및 광 검출기(164)는, 이들의 동작을 제어하도록 그리고 이들의 신호들을 수신하도록 동작가능한 컴퓨팅 디바이스, 예를 들어 제어기(190)에 연결될 수 있다. 컴퓨팅 디바이스는, 폴리싱 장치 근처에 위치된 마이크로프로세서, 예를 들어 프로그램가능한 컴퓨터를 포함할 수 있다. 제어와 관련하여, 컴퓨팅 디바이스는, 예를 들어 광 소스의 활성화를 플래튼(120)의 회전과 동기화시킬 수 있다.

- [0033] [0042] 몇몇 구현예들에서, 인시츄 모니터링 시스템(160)의 광 소스(162) 및 검출기(164)는 플래튼(120) 내에 설치되고, 플래튼(120)과 회전한다. 이 경우, 플래튼의 운동은 센서가 각각의 기판을 가로질러 스캐닝하게 할 것이다. 특히, 플래튼(120)이 회전할 때, 제어기(190)는 광학 액세스가 기판(10) 아래를 지나기 직전에 시작하여 그 직후에 끝나는 일련의 플래시들을 광 소스(162)가 방출하게 할 수 있다. 대안적으로, 컴퓨팅 디바이스는 각각의 기판(10)이 광학 액세스 위를 지나기 직전에 시작하여 그 직후에 끝나는 광을 광 소스(162)가 연속적으로 방출하게 할 수 있다. 어느 경우이든, 검출기로부터의 신호는 샘플링 주파수에서 스펙트럼 측정들을 생성하기 위해 샘플링 기간에 걸쳐서 통합될(integrated) 수 있다.

- [0034] [0043] 동작시, 제어기(190)는, 예를 들어 광 소스의 특정 플래시에 대해 또는 검출기의 시간 프레임(time frame) 동안 광 검출기에 의해 수신되는 광의 스펙트럼을 설명하는 정보를 운반(carry)하는 신호를 수신할 수 있다. 따라서, 이러한 스펙트럼은 폴리싱 동안 인시츄로 측정되는 스펙트럼이다.

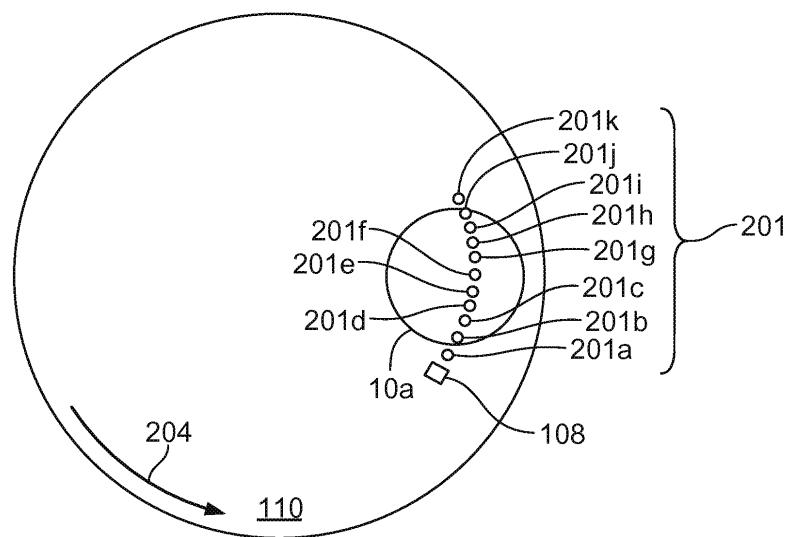

- [0035] [0044] 도 4에 의해 도시된 바와 같이, 검출기가 플래튼 내에 설치되는 경우, (화살표(204)에 의해 도시된) 플래튼의 회전으로 인해, 윈도우(108)가 캐리어 헤드 아래에서 이동할 때, 샘플링 주파수에서 스펙트럼 측정들을 실행하는 광학 모니터링 시스템은 기판(10)을 가로지르는 호형(arc)으로 위치들(201)에서 스펙트럼 측정들이 이루어지게 할 것이다. 예를 들어, 포인트들(201a 내지 201k) 각각은 모니터링 시스템에 의한 스펙트럼 측정의 위치를 나타낸다(포인트들의 수는 예시적이며; 샘플링 주파수에 따라서, 도시된 것보다 더 많거나 더 적은 측정들이 이루어질 수 있다). 샘플링 주파수는 윈도우(108)의 스위프(sweep) 당 5개 내지 20개의 스펙트럼들이 수집되도록 선택될 수 있다. 예를 들어, 샘플링 기간은 3 내지 100 밀리초일 수 있다.

- [0036] [0045] 도시된 바와 같이, 플래튼의 1 회전에 걸쳐서, 기판(10) 상의 상이한 반경들로부터 스펙트럼들이 획득된다. 즉, 몇몇 스펙트럼들은 기판(10)의 중심에 더 가까운 위치들로부터 획득되고, 몇몇은 에지에 더 가깝다. 따라서, 타이밍, 모터 인코더 정보, 및 기판 및/또는 유지 링의 에지의 광학적 검출에 기초하여, 기판을 가로지르는 광학 모니터링 시스템의 임의의 주어진 스캔에 대해, 제어기(190)는 스캔으로부터 각각의 측정된 스펙트럼에 대하여 (스캐닝 중인 기판의 중심에 대한) 방사상 위치를 계산할 수 있다. 폴리싱 시스템은 또한 회전식 위치 센서, 예를 들어 고정식 광학 차단기(optical interrupter)를 통과할 플래튼의 에지에 부착된 플랜지를 포함하여, 어느 기판인지에 대해 및 측정된 스펙트럼의 기판 상의 위치에 대해 결정하기 위한 추가 데이터를 제공할 수 있다. 그에 따라, 제어기는 측정된 다양한 스펙트럼들을 기판들(10a 및 10b) 상의 제어가능한 구역들(148b 내지 148e)(도 2 참조)과 연관시킬 수 있다. 몇몇 구현예들에서, 스펙트럼의 측정 시간은 방사상 위치의 정확한 계산을 위한 대체물로서 사용될 수 있다.

- [0037] [0046] 플래튼의 다수의 회전들에 걸쳐서, 각각의 구역에 대해, 시간의 경과에 따라 스펙트럼들의 시퀀스가 획득될 수 있다. 임의의 특정 이론으로 제한되지 않으면서, 기판(10)으로부터 반사되는 광의 스펙트럼은, 최외측 층의 두께의 변화들로 인해 (예를 들어, 기판에 걸친 단일 스위프 동안이 아니라, 플래튼의 다수의 회전들에 걸쳐서) 폴리싱이 진행됨에 따라 전개(evolve)되며, 그에 따라, 시변(time-varying) 스펙트럼들의 시퀀스를 산출한다. 또한, 층 스택의 특정 두께들에 의해 특정 스펙트럼들이 나타난다.

- [0038] [0047] 몇몇 구현예들에서, 제어기, 예를 들어 컴퓨팅 디바이스는, 증착 이후에 하지만 폴리싱 이전에 측정되는, 기판(10)의 측정된 증착 후 베이스 스펙트럼을 수신하고, 각각의 구역으로부터의 측정된 스펙트럼들의 시퀀스를 정규화하도록 프로그램될 수 있다. 제어기는 이후, 각각의 구역에 대한 최적 매칭 기준 스펙트럼들의 시퀀스를 생성하기 위해, 각각의 구역으로부터의 정규화된 측정된 스펙트럼들의 시퀀스로부터의 각각의 정규화된 스펙트럼을 다수의 기준 스펙트럼들과 비교하도록 프로그램될 수 있다.

- [0039] [0048] 본원에서 사용되는 바와 같이, 기준 스펙트럼은 기판의 폴리싱 전에 생성되는 미리 정의되는 스펙트럼이다. 기준 스펙트럼은, 실제 폴리싱 레이트가, 예상되는 폴리싱 레이트를 따른다는 가정하에, 스펙트럼이 나타날 것으로 예상되는 폴리싱 프로세스에서의 시간을 나타내는 값과 미리 정의된 연관성을 가질 수 있는 바, 즉 폴리싱 동작 이전에 정의될 수 있다. 대안적으로 또는 부가적으로, 기준 스펙트럼은, 최외측 층, 예를 들어 폴리싱될 층의 두께와 같은 기판 특성의 값과 미리 정의된 연관성을 가질 수 있다.

- [0040] [0049] 기준 스펙트럼은, 예를 들어, 테스트 기판, 예를 들어, 알려진 층 두께들의 증착된 층들을 포함하는 테스트 기판으로부터의 스펙트럼들을 측정함으로써 경험적으로 생성될 수 있다. 예를 들어, 복수의 기준 스펙트럼들을 생성하기 위해, 셋업 기판은, 스펙트럼들의 시퀀스가 수집되는 동안, 디바이스 웨이퍼들의 폴리싱 중에 사용될 동일한 폴리싱 파라미터들을 사용하여 폴리싱된다. 각각의 스펙트럼에 대해, 스펙트럼이 수집되었던 폴리싱 프로세스에서의 시간을 나타내는 값이 기록된다. 예를 들어, 값은 경과 시간 또는 플래튼 회전들의 수일 수 있다.

- [0041] [0050] 경험적으로 결정되는 것에 부가하여, 기준 스펙트럼들의 일부 또는 전부는 이론으로부터, 예를 들어, 기판 층들의 광학 모델을 사용하여 계산될 수 있다. 예를 들어, 광학 모델은, 알려진 두께들의 증착된 층들, 및 주어진 외측 층 두께(D)를 포함하는 주어진 기판에 대한 기준 스펙트럼을 계산하는 데에 사용될 수 있다. 기준 스펙트럼이 수집될 폴리싱 프로세스에서의 시간을 나타내는 값은, 예를 들어, 외측 층이 균일한 폴리싱 레이트로 제거된다고 가정함으로써, 계산될 수 있다.

- [0042] [0051] 폴리싱을 받고 있는 기판의 측정된 스펙트럼은 하나 또는 그 초파의 라이브러리들로부터의 기준 스펙트럼들에 대해 비교될 수 있다.

- [0043] [0052] 몇몇 구현예들에서, 각각의 기준 스펙트럼에는 인덱스 값이 할당된다. 일반적으로, 각각의 라이브러리는, 기판의 예상되는 폴리싱 시간에 걸쳐서 각각의 플래튼 회전에 대해 많은 기준 스펙트럼들(320), 예를 들어

하나 또는 그 초과, 예를 들어 정확히 하나의 기준 스펙트럼을 포함할 수 있다. 이러한 인덱스는, 기준 스펙트럼이 관찰될 것으로 예상되는 폴리싱 프로세스에서의 시간을 나타내는 값, 예를 들어 숫자(number)일 수 있다. 스펙트럼들은, 특정 라이브러리에서의 각각의 스펙트럼이 고유의 인덱스 값을 갖도록 인덱싱될 수 있다. 인덱싱은, 테스트 기판의 스펙트럼들이 측정된 순서로 인덱스 값들이 시퀀싱되도록 구현될 수 있다. 폴리싱이 진행됨에 따라, 인덱스 값은, 단조롭게 변하도록, 예를 들어 증가 또는 감소하도록 선택될 수 있다. 특히, 기준 스펙트럼들의 인덱스 값들은, (폴리싱 레이트가, 라이브러리에서의 기준 스펙트럼들을 생성하는 데에 사용되는 테스트 기판 또는 모델의 폴리싱 레이트를 따른다는 가정하에), 그러한 인덱스 값들이 시간 또는 플래튼 회전들의 수의 선형 함수를 형성하도록 선택될 수 있다. 예를 들어, 인덱스 값은, 기준 스펙트럼들이 테스트 기판에 대해 측정되었거나 또는 광학 모델에서 나타나게 될 플래튼 회전들의 수에 비례, 예를 들어 그러한 플래튼 회전들의 수와 같을 수 있다. 따라서, 각각의 인덱스 값은 정수(whole number)일 수 있다. 인덱스 넘버(index number)는, 연관된 스펙트럼이 나타나게 될 예상되는 플래튼 회전을 나타낼 수 있다.

[0044] [0053] 기준 스펙트럼들 및 이들의 연관된 인덱스 값들은 기준 스펙트럼들의 라이브러리에 저장될 수 있다. 예를 들어, 각각의 기준 스펙트럼 및 그것의 연관된 인덱스 값은 데이터베이스의 레코드(record)에 저장될 수 있다. 기준 스펙트럼들의 기준 라이브러리들의 데이터베이스는 폴리싱 장치의 컴퓨팅 디바이스의 메모리에 구현될 수 있다.

[0045] [0054] 상기 주목한 바와 같이, 각각의 기판의 각각의 구역에 대해, 기판의 그러한 구역에 대해 측정된 스펙트럼들의 시퀀스에 기초하여, 제어기(190)는 최적 매칭 스펙트럼들의 시퀀스를 생성하도록 프로그램될 수 있다. 최적 매칭 기준 스펙트럼은, 폴리싱 동안 획득되는 측정된 스펙트럼을 특정 라이브러리로부터의 기준 스펙트럼들과 비교함으로써 결정될 수 있다.

[0046] [0055] 측정되는 원시 스펙트럼들은 기판으로부터 측정된 증착 후 베이스 스펙트럼을 사용하여 정규화된다. 증착 후 베이스 스펙트럼을 획득하는 것이, 도 5와 관련하여 하기에서 설명된다. 베이스 스펙트럼은 기판을 폴리싱하기 전에 획득될 수 있다. 특히, 베이스 스펙트럼은, 기판 상에 하나 또는 그 초과의 유전체 층들을 증착한 이후, 하지만 폴리싱될 층을 증착하기 전에, 측정될 수 있다. 베이스 스펙트럼은, 교변하는 산화물 및 질화물 층들의 전체 스택을 증착한 이후 측정될 수 있다. 예를 들어, 교변하는 층들의 스택은, 3D NAND 메모리의 생성시에 증착되는 ONON 스택(즉, 교변하는 산화물 및 질화물 층들의 스택)일 수 있다. 몇몇 구현예들에서, 베이스 스펙트럼은, 기판을 예칭하기 전에, 예를 들어 계단 구조를 생성하기 전에, 측정된다. 몇몇 구현예들에서, 베이스 스펙트럼은, 기판을 예칭한 이후, 하지만 중간 층, 예를 들어 질화물 층을 증착하기 전에, 측정된다. 몇몇 구현예들에서, 베이스 스펙트럼은, 중간 층을 증착한 이후, 하지만 예칭된 애피처를 충진하기에 충분히 두꺼운 캡 필터 층, 예를 들어 산화물 층을 증착하기 전에, 측정된다. 원시 스펙트럼을 정규화한 이후, 정규화된 스펙트럼은 그런 다음, 최적의 매치를 결정하기 위해, 예를 들어, 교차-상관(cross-correlation), 제곱된 차들의 합 등을 계산함으로써, 기준 스펙트럼들과 비교된다.

[0047] [0056] 베이스 스펙트럼은, 독립형 계측 스테이션, 예를 들어 Nova Measuring Instruments 또는 Nanometrics로부터의 시스템에서, 또는 도 5와 관련하여 설명되는 증착 또는 예칭 프로세스들을 수행하는 것을 담당하는 증착 또는 예칭 시스템 내에 통합되는 인-라인 계측 스테이션에서 측정될 수 있다.

[0048] [0057] 정규화는 나눗셈 연산(division operation)을 포함할 수 있고, 여기서, 원시 스펙트럼이 분자에 있고, 베이스 스펙트럼이 분모에 있다. 베이스 스펙트럼은, 광이 도달할 것으로 예상되는 맨 아래 층의 재료 및 다수의 유전체 층들로부터 반사되는 광의 스펙트럼일 수 있다. 베이스 스펙트럼의 측정은, 예를 들어, 층 스택의 증착 후, 예칭 후, 및 중간층의 증착 후에, 측정을 위한 3개의 프로세스 포인트들과 관련하여 상기에서 설명되었다.

[0049] [0058] 측정된 스펙트럼은 다음과 같이 정규화될 수 있다:

$$R = (A - DA) / (B - DB)$$

[0050] 여기서, R은 정규화된 스펙트럼이고, A는 원시 스펙트럼이고, DA 및 DB는 다크 컨디션(dark condition) 하에서 획득된 다크 스펙트럼(dark spectrum)들이며, 그리고 B는 베이스 스펙트럼이다. 다크 스펙트럼은, 인시츄 광학 모니터링 시스템에 의해 기판이 측정되지 않을 때 인시츄 광학 모니터링 시스템에 의해 측정되는 스펙트럼이다. 몇몇 구현예들에서, DA 및 DB는 동일한 스펙트럼이다. 몇몇 구현예들에서, DA는, 예를 들어, 동일한 플래튼 회전에서, 원시 스펙트럼이 수집될 때에 수집되는 다크 스펙트럼이며, 그리고 DB는, 예를 들어 동일한 플래튼 회전에서, 원시 스펙트럼이 수집될 때에 수집되는 다크 스펙트럼이다.

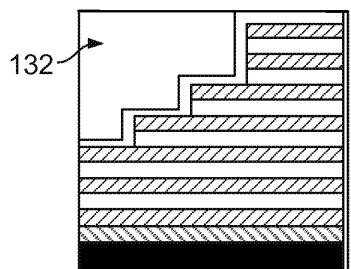

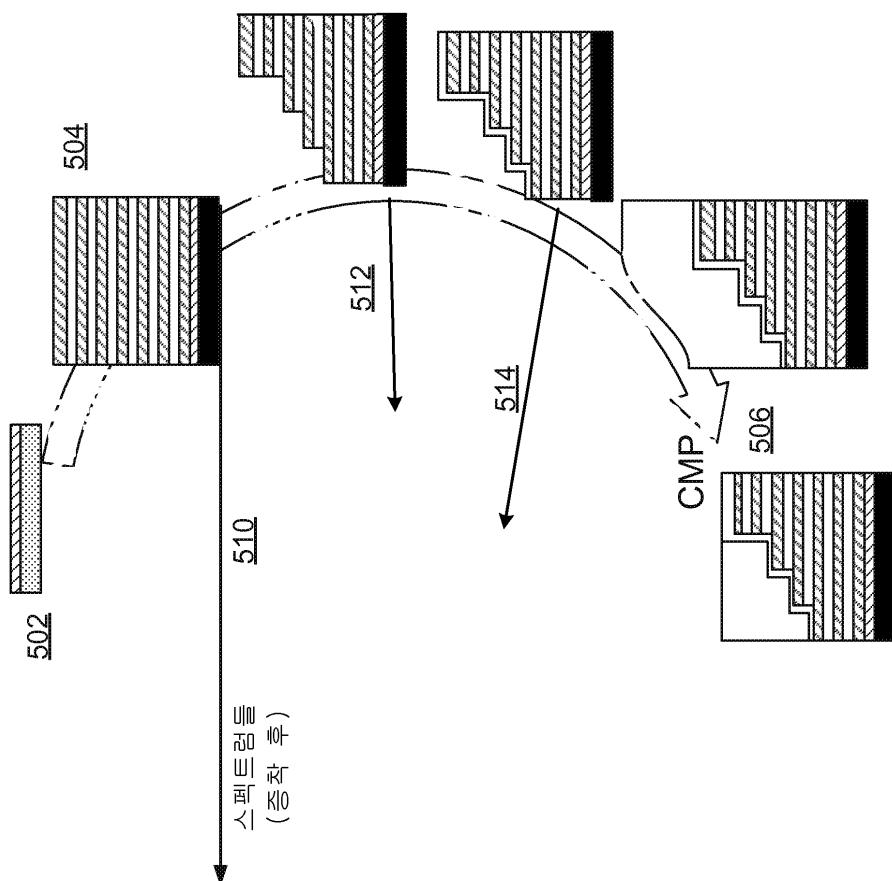

- [0052] [0059] 도 5는 중착 후 베이스 스펙트럼들이 측정될 수 있는 상이한 제조 스테이지들을 예시한다. 도 5는, 초기 스테이지(502)로부터, 중착 후 스테이지(504)(예를 들어, 중착된 유전체 재료들의 층들을 갖는 기판(502))까지의 그리고 마지막의 폴리싱 후 스테이지(506)까지의, 상이한 제조 스테이지들에서의 예시적인 기판(502)을 예시한다. 중착 후 베이스 스펙트럼, 예를 들어, 중착 후 스테이지, 즉 스테이지(504) 및 그 이후에 기판의 스펙트럼을 획득하기 위해, 광학 모니터링 시스템에 의해 스펙트럼이 측정될 수 있다. 상기 설명된 바와 같이, 중착 후 베이스 스펙트럼은 또한, 에칭 후(post etch) 기판(512), 예를 들어, 기판 상에 중착된 하나 또는 그 초과의 층들로부터 재료(예를 들어, 중착(510) 이후 기판으로부터 제거되는 재료)를 제거한 이후의 기판의 스펙트럼으로부터 획득될 수 있다. 또한, 중착 후 베이스 스펙트럼은, 캡 필 전 기판(pre gap fill substrate)(514), 예를 들어, 에칭(512) 이후, 하지만 캡 필 층(예를 들어, 두꺼운 산화물)의 중착 이전에, 기판에 도포되는 재료의 층(예를 들어, 질화물 중착 층)을 갖는 기판의 스펙트럼으로부터 획득될 수 있다.

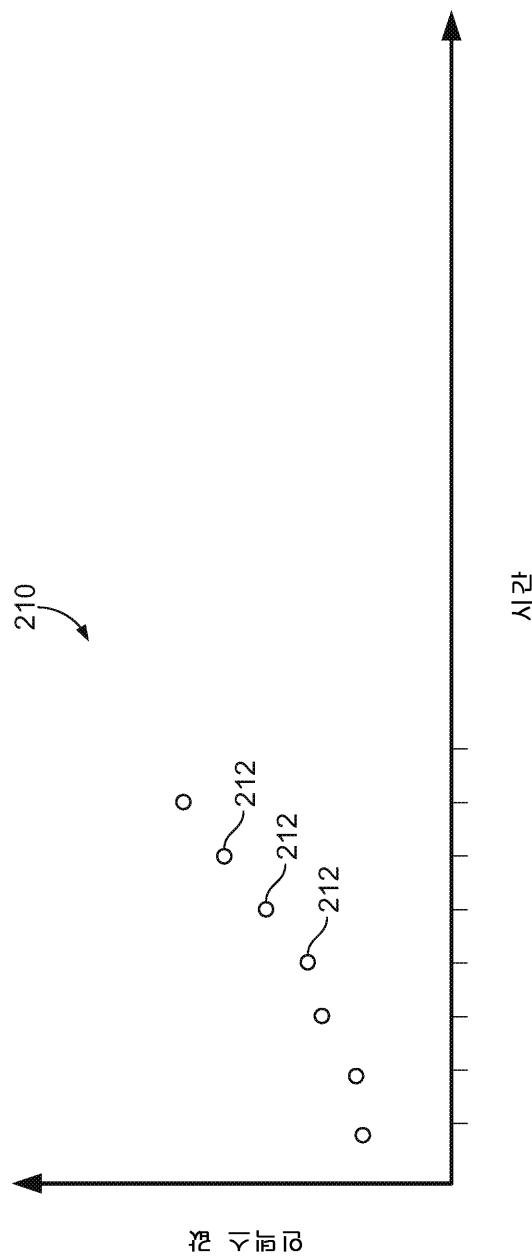

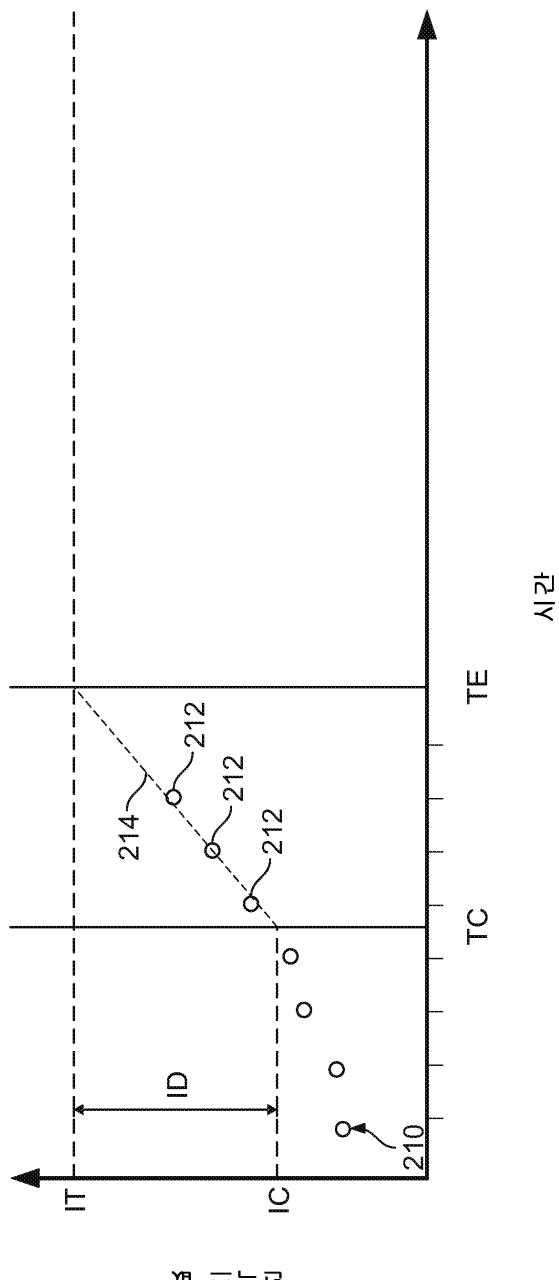

- [0053] [0060] 이제, 단일 기판의 단일 구역에 대한 결과들 만을 예시하는 도 6을 참조하면, 인덱스 값들(212)의 시변 시퀀스를 생성하기 위해, 시퀀스 내의 최적 매칭 스펙트럼들 각각의 인덱스 값이 결정될 수 있다. 인덱스 값들의 이러한 시퀀스는 인덱스 트레이스(210)라 지칭될 수 있다. 몇몇 구현예들에서, 인덱스 트레이스는, 예를 들어, 측정된 중착 후 베이스 스펙트럼에 대해 정규화된, 각각의 정규화된 측정된 스펙트럼을, 정확히 하나의 라이브러리로부터의 기준 스펙트럼들과 비교함으로써 생성된다. 일반적으로, 인덱스 트레이스(210)는 기판 아래에서의 광학 모니터링 시스템의 스위프 당 하나의, 예를 들어 정확히 하나의 인덱스 값을 포함할 수 있다.

- [0054] [0061] 광학 모니터링 시스템의 단일 스위프로 특정 구역에 대하여 다수의 스펙트럼들("현재 스펙트럼들(current spectra)"이라 지칭됨)이 측정 및 정규화되는 주어진 인덱스 트레이스(210)에 대해, 현재의 정규화된 측정된 스펙트럼들 각각과 하나 또는 그 초과의, 예를 들어 정확히 하나의 라이브러리의 기준 스펙트럼들 간에 최적 매치(best match)가 결정될 수 있다. 몇몇 구현예들에서, 각각의 선택된 현재 스펙트럼들은 선택된 라이브러리 또는 라이브러리들의 각각의 기준 스펙트럼들에 대해 비교된다. 대안적으로, 몇몇 구현예들에서, 현재 스펙트럼들은 결합, 예를 들어 평균화됨(averaged) 수 있으며, 그리고 결과적인 결합된 스펙트럼이 기준 스펙트럼들에 대해 비교되어, 최적 매치 및 그에 따라 인덱스 값을 결정한다.

- [0055] [0062] 요약하면, 각각의 인덱스 트레이스는 인덱스 값들(212)의 시퀀스(210)를 포함하며, 시퀀스의 각각의 특정 인덱스 값(212)은, 주어진 라이브러리로부터, 정규화된 측정된 스펙트럼에 가장 근접하게 피팅(fit)되는 기준 스펙트럼의 인덱스를 선택함으로써 생성된다. 인덱스 트레이스(210)의 각각의 인덱스에 대한 시간 값은, 정규화된 측정된 스펙트럼이 측정된 시간과 동일할 수 있다.

- [0056] [0063] 도 7에 도시된 바와 같이, 함수, 예를 들어 공지된 차수(order)의 다항식 함수, 예를 들어 1차 함수(first-order function)(예를 들어, 라인(214))가, 예를 들어 강건한 라인 피팅(robust line fitting)을 사용하여, 스펙트럼들의 인덱스 값들의 시퀀스에 피팅된다. 다른 함수들, 예를 들어, 2차(second-order)의 다항식 함수들이 사용될 수 있지만, 라인이 계산의 용이성을 제공한다. 라인(214)이 타겟 인덱스(IT)를 가로지르는 종점 시간(TE)에서 폴리싱이 중단될 수 있다.

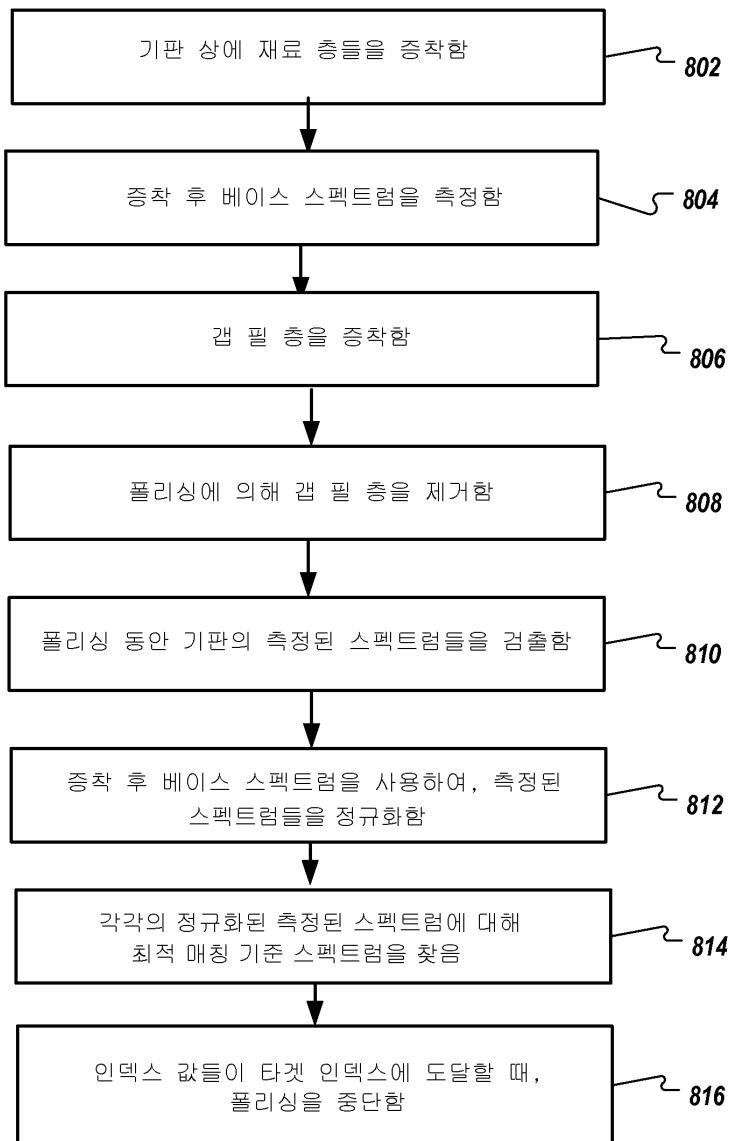

- [0057] [0064] 도 8은 제품 기판(product substrate)을 제조하고 폴리싱하는 방법의 흐름도를 도시한다. 제품 기판은 적어도, 라이브러리의 기준 스펙트럼들을 생성하기 위해 사용되는 테스트 기판들과 동일한 층 구조 및 동일한 패턴을 가질 수 있다. 몇몇 구현예들에서, 도 8의 방법은, 도 9와 관련하여 하기 설명되는 제조 퍼실리티를 사용하여 수행될 수 있다. 도 8은, 예를 들어 3D NAND 구조와 같은 예시적인 기판을 제조 및 폴리싱하는 방법을 예시하지만, 단계(804) 및 단계들(808-816)은 임의의 적합한 제조된 기판에 대해 적용될 수 있음을 이해해야 한다.

- [0058] [0065] 도 9는 제조 퍼실리티(900)의 개략적인 예시이다. 제조 퍼실리티(900)는, 인-라인 계측 시스템(904)을 선택적으로 포함하는 중착 시스템(902), 예를 들어, 화학 기상 중착 시스템 또는 플라즈마 강화 화학 기상 중착 시스템을 포함한다. 몇몇 구현예들에서, 제조 퍼실리티(900)는 독립형 계측 시스템(906)을 포함할 수 있다.

- [0059] [0066] 제조 퍼실리티(900)는, 기판을 수용하고, 기판을 패터닝하고, 예칭 프로세스를 수행할 수 있는 예칭 시스템(908)을 더 포함한다. 예칭 시스템(908)은 인라인 계측 시스템(910)을 포함할 수 있다.

- [0060] [0067] 또한, 제조 퍼실리티(900)는, 기판을 수용하고, 기판 상의 외측 재료 층을 폴리싱, 예를 들어 제거할 수 있는 폴리싱 시스템(912)을 포함한다. 폴리싱 시스템(912)은, 인시츄 광학 계측 시스템(914), 및 동작들을 수행하도록 구성된 제어기(916)를 갖도록 구성된다.

- [0061] [0068] 재료의 층들이 기판 상에 중착된다(단계 802). 도 1a 및 도 5와 관련하여 상기 주목한 바와 같이, 기

판 베이스(12), 예를 들어 유리 시트 또는 반도체 웨이퍼는, 기판 베이스 위에 배치되는 전도성 층(14), 예를 들어 금속, 이를테면 구리, 텅스텐 또는 알루미늄을 포함할 수 있다.

[0062] 기판은 증착 시스템(902)으로 운반된다. 몇몇 구현예들에서, 교번하는 층들, 예를 들어, 교번하는 제1 층 재료 및 제2 층 재료가 증착 시스템(902)에 의해 기판 위에, 또는 몇몇 구현예들에서는 전도성 층(14) 위에 증착된다. 예를 들어, 제1 유전체 층(16), 예를 들어 산화물 또는 질화물이 전도성 층 위에 증착되며, 그리고 제2 유전체 층, 예를 들어 산화물 또는 질화물이 제1 층 위에 증착된다. 예를 들어, 제1 유전체 층은 실리콘 산화물일 수 있고, 제2 유전체 층은 실리콘 질화물일 수 있다. 증착은, 재료들의 교번하는 층들의 스택을 생성하기 위해 한번 또는 그 초과의 횟수만큼 반복된다. 도 1과 관련하여 상기 설명된 바와 같이, 층들 중 하나, 예를 들어, 제1 층 재료 또는 제2 층 재료는 폴리실리콘일 수 있다.

[0063] [0070] 단계(804)에서 설명되는 바와 같이, 기판으로부터 반사되는 스펙트럼이 제조 프로세스에서의 이 시점(point)에서 측정될 수 있고, 증착 후 베이스 스펙트럼으로서 저장될 수 있다. 기판은, 증착 시스템(902) 내의 인-라인 계측 시스템(904)에 의해, 또는 독립형 계측 시스템(906)에 의해 측정될 수 있다.

[0064] [0071] 다음으로, 예를 들어, 계단 구조를 생성하기 위해, 기판이 패터닝 및 에칭된다. 에칭을 수행하기 위해, 기판은 에칭 시스템(908)으로 운반될 수 있다. 임의의 남아있는 포토레지스트를 제거한 후, 대안적으로, 기판으로부터 반사되는 스펙트럼이 제조 프로세스에서의 이 시점에서 측정되고, 증착 후 베이스 스펙트럼으로서 저장될 수 있다. 기판은, 에칭 시스템(908) 내의 인-라인 계측 시스템(910)에 의해, 또는 독립형 계측 시스템(906)에 의해 측정될 수 있다.

[0065] [0072] 다음으로, 중간 층, 예를 들어, 도 1에서와 같은 질화물 층(20), 이를테면 실리콘 질화물이, 에칭된 애페처를 갖는 교번하는 재료 층들 위에 증착된다. 중간 층의 증착은, 교번하는 층들의 스택을 증착한 것과 동일한 증착 시스템(902)에 의해 또는 상이한 증착 시스템에 의해 수행될 수 있다. 대안적으로, 기판으로부터 반사되는 스펙트럼이, 외측 캡 필 층(30)의 증착 이전에, 제조 프로세스의 이 시점에서 측정되고, 증착 후 베이스 스펙트럼으로서 저장될 수 있다. 기판은, 인-라인 계측 시스템, 예를 들어 증착 시스템(902) 내의 인-라인 계측 시스템(904)에 의해, 또는 독립형 계측 시스템(906)에 의해 측정될 수 있다.

[0066] [0073] 결과적으로, 제품 기판은, 증착 후에, 하지만 폴리싱 전에 그리고 폴리싱될 층의 증착 전에 측정된다(단계 804). 제품 기판으로부터 반사되는 스펙트럼은, 하기 설명되는 바와 같이, 폴리싱 동안 측정되는 스펙트럼들을 정규화하는 데에 사용하기 위해 측정된다. 증착 후 베이스 스펙트럼, 예를 들어, 폴리싱 동안 측정되는 원시 스펙트럼들을 정규화하는 데에 사용되는, 증착 후 스테이지에서의 기판의 스펙트럼을 획득하기 위해, 제품 기판이 측정된다. 증착 후 베이스 스펙트럼은, 증착 이후 그리고 에칭 이전에, 제품 기판의 스펙트럼으로부터 측정될 수 있다. 증착 후 베이스 스펙트럼은 또한, 에칭 이후, 예를 들어, 계단 구조를 생성하기 위해, 제품 기판 상에 증착된 하나 또는 그 초과의 층들로부터 재료를 제거한 이후, 측정될 수 있다. 또한, 증착 후 베이스 스펙트럼은, 에칭, 및 제품 기판 상에 질화물 층을 증착한 이후, 하지만 폴리싱 전에 측정될 수 있다.

[0067] [0074] 증착 후 베이스 스펙트럼을 측정한 후, 외측 캡 필 층, 예를 들어 두꺼운 산화물이 기판 상에 증착된다(단계 806). 중간 층의 증착은, 교번하는 층들의 스택을 증착한 것과 동일한 증착 시스템(902)에 의해, 그리고 /또는 중간 층을 증착한 것과 동일한 증착 시스템(902)에 의해, 또는 상이한 증착 시스템에 의해 수행될 수 있다.

[0068] [0075] 캡 필 층을 제거하기 위해 제품 기판이 폴리싱된다(단계 808). 예를 들어, 캡 필 층은, 폴리싱 시스템(912), 예를 들어, 도 2에서 설명된 폴리싱 장치에서, 폴리싱 패드를 사용하여, 폴리싱 및 제거될 수 있다. 물론, 단계들(802-806)은 다른 곳에서 수행될 수 있으며, 그에 따라, 폴리싱 시스템(912)의 특정 오퍼레이터에 대한 프로세스는 단계(808)에서 시작된다.

[0069] [0076] 인시츄 계측 시스템(914)은, 상기 설명된 인시츄 모니터링 시스템(914)을 사용하여, 폴리싱 동안 제품 기판의 측정된 스펙트럼들을 검출하는 데에 사용된다(단계 810).

[0070] [0077] 폴리싱 시스템(912) 내의 제어기(916)는, 상기 논의된 바와 같이, 측정된 증착 후 베이스 스펙트럼을 사용하여, 측정된 스펙트럼들을 정규화한다(단계 812). 몇몇 구현예들에서, 함수, 예를 들어 선형 함수가, 캡 필 층의 클리어런스(clearance)가 검출되는 시간(TC) 이후 수집되는 스펙트럼들에 대한 인덱스 값들의 시퀀스에 대해 피팅된다.

[0071] [0078] 정규화된 측정된 스펙트럼들을 분석하여 인덱스 값들의 시퀀스를 생성하며, 그리고 인덱스 값들의 시퀀스에 대해 함수가 피팅된다. 특히, 측정된 스펙트럼들의 시퀀스 내의 각각의 측정된 스펙트럼에 대해, 인덱스

값들의 시퀀스를 생성하기 위해, 최적으로 피팅되는 기준 스펙트럼에 대한 인덱스 값이 결정된다(단계 814). 즉, 정규화된 측정된 스펙트럼들을 분석하여 인덱스 값들의 시퀀스를 생성하며, 그리고 인덱스 값들의 시퀀스에 대해 함수가 피팅된다.

[0072] [0079] 인덱스 값(예를 들어, 인덱스 값들의 새로운 시퀀스에 대해 피팅되는 선형 함수로부터 생성되는 계산된 인덱스 값)이 타겟 인덱스에 도달하면, 폴리성이 중단될 수 있다(단계 816). 타겟 두께(IT)가 폴리성 동작 이전에 사용자에 의해 설정되어 저장될 수 있다. 대안적으로, 제거하기 위한 타겟 양(target amount)이 사용자에 의해 설정될 수 있고, 제거하기 위한 타겟 양으로부터 타겟 인덱스(IT)가 계산될 수 있다.

[0073] [0080] 폴리성 균일성을 개선하기 위해, 폴리성 파라미터들을 조정하도록, 예를 들어, 기판 상의 하나 또는 그 초과의 구역들의 폴리성 레이트를 조정하도록, 최외측 층, 예를 들어 캡 필 층의 클리어런스가 검출된 이후 수집되는 스펙트럼들로부터의 인덱스 값들에 대해 피팅되는 함수를 사용하는 것이 또한 가능하다.

[0074] [0081] 몇몇 구현예들에서, 각각의 구역에 대해 인덱스 트레이스가 생성될 수 있다. 폴리성 종점을 검출하는 데에 사용되는 것에 대해 대안적으로 또는 부가적으로, 인덱스 트레이스들은, 상이한 구역들이, 폴리성을 감소시키는 타겟 두께에 더 가까운 자신들의 타겟 두께에 도달하도록, 예를 들어, 미국 특허 출원 일련 번호 제13/094,677호에서 설명된 바와 같이, 폴리성 균일성을 개선하기 위해 구역들 중 하나 또는 그 초과에 대한 폴리성 레이트를 조정하게 될 폴리성 파라미터에 대한 조정을 계산하는 데에 사용될 수 있다.

[0075] [0082] 비록 상기의 논의가, 플래튼 내에 설치된 광학 종점 모니터를 가지는 회전하는 플래튼을 추정하고 있기는 하지만, 시스템은 모니터링 시스템과 기판 사이의 다른 타입들의 상대적인 운동에 대해 적용가능할 수 있다. 예를 들어, 몇몇 구현예들에서, 예를 들어 케도 운동에서, 광 소스는 기판의 상이한 위치들을 획단하지만, 기판의 에지는 가로지르지 않는다. 그러한 경우들에서, 수집된 스펙트럼들은 여전히 그룹화될 수 있고, 예를 들어 스펙트럼들은 특정 빈도수(frequency)로 수집될 수 있으며 그리고 소정 시간 기간 내에 수집된 스펙트럼들이 그룹의 일부로 고려될 수 있다. 그러한 시간 기간은, 각각의 그룹에 대해 5개 내지 20개의 스펙트럼들이 수집될 수 있을 정도로 충분히 길어야 한다.

[0076] [0083] 또한, 상기 논의가 정규화를 위해 베이스 스펙트럼을 사용하는 것에 대해 집중하였지만, 베이스 스펙트럼은 다른 적용예들에 대해 사용될 수 있다. 제 1 예로서, 정규화보다는, 베이스 스펙트럼은 폴리성 프로세스 동안 기준 스펙트럼으로서 사용될 수 있다.

[0077] [0084] 제 2 예로서, 베이스 스펙트럼에서의 밸리들 또는 피크들의 위치가 결정될 수 있다. 이러한 데이터는 스펙트럼 특징 추적 알고리즘(spectral feature tracking algorithm)에서 타겟을 조정하는 데에 사용될 수 있다. 예를 들어, 본원에서 참조로서 포함되는 미국 특허 제7,998,358호에서 설명되는 알고리즘은, 베이스 스펙트럼에서의 밸리 또는 피크의 위치에 기초하여 타겟 위치를 소정의 양 만큼 변경시킴으로써, 조정될 수 있다.

[0078] [0085] 제 3 예로서, 나눗셈보다는, 측정된 스펙트럼으로부터 베이스 스펙트럼을 뺄 수 있다.

[0079] [0086] 제 4 예로서, 여러 가지의 저장된 종점 알고리즘들 중 하나가 베이스 스펙트럼에 기초하여 제어기에 의해 자동적으로 선택될 수 있다. 예를 들어, 폴리성 이전에, 베이스 스펙트럼은 복수의 스펙트럼들과 비교될 수 있고, 최적 매칭 스펙트럼이 식별될 수 있다. 복수의 스펙트럼들 각각은, 연관된 알고리즘 타입, 예를 들어 푸리에 변환, 스펙트럼 특징 추적, 기준 스펙트럼에 대한 차이의 추적, 또는 라이브러리로부터의 매칭하는 기준 스펙트럼의 식별을 가질 수 있다. 제어기가, 어떤 스펙트럼이 최적으로 매칭하는지를 결정한 후, 제어기는 그 스펙트럼과 연관된 종점 알고리즘을 자동적으로 선택할 수 있다.

[0080] [0087] 또한, 상기 논의가 유전체 층의 폴리성 동안 측정되는 스펙트럼의 정규화에 대해 집중하였지만, 이러한 접근법은 전도성 층의 폴리성 동안 와전류 측정의 정규화에도 또한 적용가능할 것이다. 이 경우, 최외측 층은 전도성 층, 예를 들어 구리와 같은 금속이다. 예를 들어, 미국 특허 공보 제2012/0276661호에서 설명되는 바와 같은 와전류 모니터링 시스템이 광학 모니터링 시스템을 대체하며, 폴리성 동안 기판을 모니터링하는 데에 사용된다. 독립형 또는 인-라인 와전류 계측 디바이스가, 반도체 웨이퍼 위에 놓이는 전도성 층의 증착 이후, 하지만 최외측 전도성 층의 증착 이전에, 기판의 베이스 측정을 생성하는 데에 사용된다. 와전류 측정은 다음과 같이 정규화될 수 있다:

$$R = (A - DA) / (B - DB)$$

[0082] 여기서, R은 정규화된 측정이고, A는 폴리성 동안의 원시 측정(raw measurement)이고, DA 및 DB는, 센서가 기판 아래 있지 않을 때 인시큐 와전류 모니터링 시스템에 의해 이루어지는 측정들이며, 그리고 B는 외측의 전도성의

최외측 층의 중간 이전에 이루어지는 베이스 측정이다.

[0083] [0088] 본 명세서에서 사용되는 바와 같이, 기판이라는 용어는, 예를 들어, 제품 기판(예를 들어, 다수의 메모리 또는 프로세서 디자인을 포함함), 테스트 기판, 및 게이팅(gating) 기판을 포함할 수 있다. 기판이라는 용어는 원형 디스크들 및 직사각형 시트들을 포함할 수 있다.

[0084] [0089] 본 명세서에서 설명되는 본 발명의 실시예들은, 디지털 전자 회로로 또는 컴퓨터 소프트웨어, 펌웨어, 또는, 본 명세서에서 개시된 구조적 수단들 및 그 구조적 수단들의 구조적인 균등률들을 포함하는, 하드웨어로, 또는 이들의 조합들로 구현될 수 있다. 본 발명의 실시예들은, 데이터 프로세싱 장치, 예를 들어 프로그램가능 프로세서, 컴퓨터, 또는 다수의 프로세서들 또는 컴퓨터들에 의해 실행하기 위한, 또는 그러한 데이터 프로세싱 장치의 동작을 제어하기 위한, 하나 또는 그 초과의 컴퓨터 프로그램 제품들로서, 즉 머신 관리가능 저장 매체에 유형적으로 구현되는 하나 또는 그 초과의 컴퓨터 프로그램들로서 구현될 수 있다. 컴퓨터 프로그램(또한, 프로그램, 소프트웨어, 소프트웨어 애플리케이션, 또는 코드로 알려져 있음)은, 컴파일링된 또는 해석된(interpreted) 언어들을 포함하는 임의의 형태의 프로그래밍 언어로 작성될 수 있고, 그리고 독립형(stand-alone) 프로그램과 같은, 또는 모듈, 컴포넌트, 서브루틴, 또는 컴퓨팅 환경에서 사용하기에 적합한 다른 유닛과 같은 것을 포함하는, 임의의 형태로 전개될(deployed) 수 있다. 컴퓨터 프로그램이 반드시 파일에 상응하는 것은 아니다. 프로그램은, 다른 프로그램들 또는 데이터를 유지하는 파일의 일부 내에, 해당 프로그램에 전용되는 단일 파일 내에, 또는 다수의 협력적인(coordinated) 파일들(예를 들어, 하나 또는 그 초과의 모듈들, 서브 프로그램들, 또는 코드의 부분들을 저장하는 파일들) 내에 저장될 수 있다. 컴퓨터 프로그램은 하나의 컴퓨터 상에서, 또는 하나의 장소(site)의 또는 다수의 장소들에 걸쳐 분산되고 통신 네트워크에 의해 서로 연결되어 있는 다수의 컴퓨터들 상에서 실행되도록 전개될 수 있다. 본 명세서에 설명된 프로세스들 및 논리 흐름들은, 입력 데이터에 대해 동작하고 출력을 생성함으로써 기능들을 수행하도록 하나 또는 그 초과의 컴퓨터 프로그램들을 실행하는 하나 또는 그 초과의 프로그램가능 프로세서들에 의해 수행될 수 있다. 프로세스들 및 논리 흐름들은 또한, 특수 목적 논리 회로망, 예를 들어 FPGA(field programmable gate array) 또는 ASIC(application specific integrated circuit)에 의해 수행될 수 있고, 그리고 장치는 또한 그러한 FPGA 또는 ASIC로서 구현될 수 있다.

[0085] [0090] 상기 설명된 폴리싱 장치 및 방법들은 다양한 폴리싱 시스템들에서 적용될 수 있다. 폴리싱 패드 또는 캐리어 헤드들, 또는 양자 모두가 이동되어, 폴리싱 표면과 기판 간에 상대 운동을 제공할 수 있다. 예를 들어, 플래튼은 회전하는 것이 아니라, 궤도 운동(orbit)을 할 수 있다. 폴리싱 패드는 플래튼에 고정된 원형(또는 어떠한 다른 형상)의 패드일 수 있다. 종점 검출 시스템의 일부 양상들은, 예를 들어 폴리싱 패드가 연속적이거나, 선형으로 이동하는 릴-투-릴(reel-to-reel) 벨트인 경우, 선형 폴리싱 시스템들에 대해 적용가능할 수 있다. 폴리싱 층은 표준(예를 들어, 필러들을 가지거나 가지지 않는 폴리우레탄) 폴리싱 재료, 연성 재료, 또는 고정형-연마(fixed-abrasive) 재료일 수 있다. 상대적인 포지셔닝(positioning)의 용어들이 사용되며; 폴리싱 표면 및 기판은 수직 배향 또는 어떠한 다른 배향으로 유지될 수 있음을 이해해야 한다.

[0086] [0091] 본 발명의 특정 실시예들이 설명되었다. 다른 실시예들이 하기의 청구항들의 범위 내에 있다.

## 도면

### 도면 1a

도면 1b

10

도면 1c

10

도면 1d

10

도면 1e

10

도면2

도면3

도면4

도면5

도면6

도면7

## 도면8

800 →

도면9

900