(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-14094

(P2004-14094A)

(43) 公開日 平成16年1月15日(2004.1.15)

(51) Int.Cl.<sup>7</sup>G 11 C 11/401

H 01 L 21/8242

H 01 L 27/108

F 1

G 11 C 11/34

H 01 L 27/10

テーマコード(参考)

5 F 08 3

5 M 02 4

審査請求 未請求 請求項の数 66 O L (全 46 頁)

(21) 出願番号 特願2003-33112 (P2003-33112)

(22) 出願日 平成15年2月12日 (2003.2.12)

(31) 優先権主張番号 10/167,754

(32) 優先日 平成14年6月11日 (2002.6.11)

(33) 優先権主張国 米国(US)

(71) 出願人 000005108

株式会社日立製作所

東京都千代田区神田駿河台四丁目6番地

(74) 代理人 100068504

弁理士 小川 勝男

(74) 代理人 100086656

弁理士 田中 恭助

(74) 代理人 100094352

弁理士 佐々木 幸

(72) 発明者 ブライアン・アトウッド

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

(72) 発明者 矢野 和男

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

最終頁に続く

(54) 【発明の名称】半導体メモリ素子

## (57) 【要約】

## 【課題】

D R A Mにおける小面積利得セル・メモリ技術を用いたセルの大きさが、D R A Mと比べて大きすぎるという問題がある。これは追加のトランジスタまたは配線に使う空間で使用される余分な面積によるものである。さらに、利得セル技術は、保存容量が小さいことによる保持時間の短さと漏れ電流の大きいという問題が挙げられる。

## 【解決手段】

本発明によれば、隣接するセルの間で基準ノードを共有することにより、半導体メモリ・セルを小さい表面積で実現できる。さらに、定電圧がストレージ・ノードに書き込まれるので、ワード線用に電圧ブースト回路を追加する必要がなくなり、メモリアレイの周辺回路で必要な面積を減少できる。また、この種のメモリ・セルは、容量素子を追加してリテンション時間を増加できる。

## 【選択図】図1

図 1

**【特許請求の範囲】****【請求項 1】**

複数のワード線と、

複数のデータ線と、

前記ワード線とデータ線の交点にあるメモリ・セルとを含み、各メモリ・セルはさらに第1のスイッチ素子と、

第1のコンデンサ素子とを含み、

前記第1のコンデンサ素子の第1の端子は、前記第1のスイッチ素子の第1の端子へ電気的に接続され、

前記第1のスイッチ素子の第1の端子はストレージノードとして働き、電荷は前記第1のスイッチ素子から転送され、前記データ線の電圧値に基づいて前記ストレージノードへ多値電圧値として蓄積されるメモリ素子において、

前記メモリ・セルへの書き込み動作においては前記複数のデータ線の電圧関係が  $V_a > V_b$  を満たす場合には、書き込み動作終了後において前記ストレージノードの電荷は  $Q_a < Q_b$  になるように動作を行い、前記データ線の電圧関係が逆の場合は前記ストレージノードの電荷関係も逆になるような動作を行なうことを特徴とする半導体メモリ素子。

**【請求項 2】**

前記第1のスイッチ素子の前記ストレージノードに接続されていない第2の端子は、書き込み動作時に書き込み電圧に依存せず一定の電圧である共通線に接続されることを特徴とする請求項1に記載の半導体メモリ素子。

**【請求項 3】**

前記スイッチ素子は書き込みトランジスタから構成され前記書き込みトランジスタのソースまたはドレインが前記ストレージ・ノードへ電気的に接続されるようにすることを特徴とする請求項1に記載の半導体メモリ素子。

**【請求項 4】**

前記書き込みトランジスタのゲート電極は書き込みワード線へ電気的に接続されることを特徴とする請求項3に記載の半導体メモリ素子。

**【請求項 5】**

前記第1のコンデンサ素子はストレージ・トランジスタであり前記第1のコンデンサ素子の第1の端子は前記ストレージ・トランジスタのゲート電極であることを特徴とする請求項1に記載の半導体メモリ素子。

**【請求項 6】**

前記メモリ・セルに保存される情報は前記ストレージ・トランジスタのソース・ドレイン間のコンダクタンス変化によって識別可能であることを特徴とする請求項5に記載の半導体メモリ素子。

**【請求項 7】**

前記ストレージ・トランジスタのソースまたはドレインが読み出しデータ線へ電気的に接続されることを特徴とする請求項5に記載の半導体メモリ素子。

**【請求項 8】**

前記ストレージ・トランジスタのソースまたはドレインが共通の電圧基準へ電気的に接続されることを特徴とする請求項5に記載の半導体メモリ素子。

**【請求項 9】**

前記メモリ・セルはさらに読み出しどランジスタを含み前記ストレージ・トランジスタのソースまたはドレインが前記読み出しどランジスタのソースまたはドレインへ電気的に接続されることを特徴とする請求項5に記載の半導体メモリ素子。

**【請求項 10】**

前記ストレージ・トランジスタのソースまたはドレインへ接続されていない前記読み出しどランジスタのソースまたはドレインが読み出しデータ線へ接続されることを特徴とする請求項9に記載の半導体メモリ素子。

**【請求項 11】**

10

20

30

40

50

前記ストレージ・トランジスタのソースまたはドレインへ接続されていない前記読み出しトランジスタのソースまたはドレインが共通の電圧基準へ接続されることを特徴とする請求項9に記載の半導体メモリ素子。

【請求項12】

前記読み出しトランジスタのゲート電極は読み出しづード線へ電気的に接続されることを特徴とする請求項9に記載の半導体メモリ素子。

【請求項13】

前記ストレージ・トランジスタのソースまたはドレインへ接続されていない前記読み出しトランジスタのソースまたはドレインが共通の電圧基準へ接続されることと、

前記読み出しトランジスタのソースまたはドレインへ接続されていない前記ストレージ・トランジスタのソースまたはドレインがデータ線へ電気的に接続されることを特徴とする請求項12に記載の半導体メモリ素子。 10

【請求項14】

前記ストレージ・トランジスタのソースまたはドレインへ接続されていない前記読み出しトランジスタのソースまたはドレインがデータ線へ接続されることと、

前記読み出しトランジスタのソースまたはドレインへ接続されていない前記ストレージ・トランジスタのソースまたはドレインが共通の電圧基準へ電気的に接続されることを特徴とする請求項12に記載の半導体メモリ素子。

【請求項15】

前記スイッチ素子は書き込みトランジスタを含み、前記書き込みトランジスタのソースまたはドレインが前記ストレージ・ノードへ電気的に接続されることを特徴とする請求項1 20に記載の半導体メモリ素子。

【請求項16】

前記ストレージ・ノードへ電気的に接続されていない前記書き込みトランジスタのソースまたはドレインが定電圧基準へ電気的に接続されることを特徴とする請求項15に記載の半導体メモリ素子。

【請求項17】

前記書き込みトランジスタのゲートは書き込みワード線へ接続され前記書き込みワード線と読み出しづード線が接続されることを特徴とする請求項15に記載の半導体メモリ素子。 30

【請求項18】

前記メモリ・セルはさらにアクセス・コンデンサ素子を含み、前記アクセス・コンデンサ素子の一方の端子が前記ストレージ・ノードへ電気的に接続されることを特徴とする請求項1に記載の半導体メモリ素子。

【請求項19】

前記アクセス・コンデンサ素子の第2の端子が読み出しづード線へ接続されることを特徴とする請求項18に記載の半導体メモリ素子。

【請求項20】

前記メモリ・セルはさらにアクセス・コンデンサ素子を含み、前記アクセス・コンデンサ素子の一方の端子が前記ストレージ・ノードへ電気的に接続されることを特徴とする請求項5に記載の半導体メモリ素子。 40

【請求項21】

前記アクセス・コンデンサ素子の第2の端子が読み出しづード線へ接続されることを特徴とする請求項20に記載の半導体メモリ素子。

【請求項22】

前記ストレージ・ノードに保持された情報は前記読み出しづード線を活性化し前記ストレージ・トランジスタのドレインからソースへのコンダクタンス変化を測定することにより識別できることを特徴とする請求項21に記載の半導体メモリ素子。

【請求項23】

前記スイッチ素子は前記ストレージ・トランジスタのチャンネルと異なる極性の不純物を 50

ドーピングしたチャンネルを備えるトランジスタを含むことを特徴とする請求項 20 に記載の半導体メモリ素子。

【請求項 24】

前記読み出しワード線と前記書き込みワード線は 1 つのワード線で構成され、前記 1 つのワード線には、書き込み電圧、読み出し電圧、前記書き込み電圧と読み出し電圧の中間のスタンバイ電圧が印加されることを特徴とする請求項 23 に記載の半導体メモリ素子。

【請求項 25】

複数のデータ線が複数のデータ線対に構成され、前記メモリ・セルは前記複数のデータ線が電気的に平衡になるように構成されることを特徴とする請求項 1 に記載の半導体メモリ素子。

10

【請求項 26】

各データ線対について差動增幅を実行するのに適した複数のセンスアンプをさらに含むことを特徴とする請求項 25 に記載の半導体メモリ素子。

【請求項 27】

各々の前記センスアンプに一つづつ複数のプリチャージ回路をさらに含み前記センスアンプの各々が検出增幅を行なうための交差接続 CMOS 論理反転構造になるように 2 個の PMOS と 2 個の NMOS トランジスタで構成されることを特徴とする請求項 26 に記載の半導体メモリ素子。

【請求項 28】

複数のダミーセルをさらに含み、データ線の各対が接続されたダミーセルを有し、前記ダミーセルは読み出し動作によりアクセスされている前記メモリ・セルに接続されていないデータ線対のデータ線へ接続されていることと、前記ダミーセルは前記 2 本のデータ線電圧の間のほぼ中間の電圧を出力することを特徴とする請求項 27 に記載の半導体メモリ素子。

20

【請求項 29】

信号増幅を行なうための少なくとも 1 個のセンスアンプをさらに含み、前記センスアンプは前記増幅器の 2 個の入力端子が 2 本のシングルエンデッド・データ線へ電気的に接続されるように構成されることを特徴とする請求項 1 に記載の半導体メモリ素子。

【請求項 30】

複数のダミーセルをさらに含み、各々のシングルエンデッド・データ線は接続されたダミーセルを有し、

30

読み出し動作中に、前記読み出し動作によってアクセスされているメモリ・セルへ接続されていないが同じセンスアンプへ接続されている前記ダミーセルは前記センスアンプへ接続されたデータ線対のデータ線に接続されることと、さらに前記ダミーセルは前記 2 本のデータ線電圧のほぼ中間の電圧を出力することを特徴とする請求項 29 に記載の半導体メモリ素子。

【請求項 31】

前記ストレージ・ノードに保存された前記メモリ・セルの情報を復元するようにリフレッシュ動作を行なうことを特徴とする請求項 1 に記載の半導体メモリ素子。

【請求項 32】

前記スイッチ素子は絶縁薄膜上に 5 ナノメートルを越えない厚みの半導体材料で形成されたチャンネルにより接続されるソース領域とドレイン領域が金属または半導体材料から製造された半導体デバイス書き込み要素を含み、前記チャンネルの電圧レベルが前記半導体デバイス書き込み要素のゲート電極の電圧により影響を受けることを特徴とする請求項 1 に記載の半導体メモリ素子。

40

【請求項 33】

前記第 1 のコンデンサ素子は少なくとも 1 つのストレージ・トランジスタよりなり、前記ストレージ・トランジスタのゲート電圧は電気的に前記スイッチ素子の 1 つの端子に接続され、ストレージ・ノードとして働くことを特徴とする請求項 32 に記載の半導体メモリ素子。

50

**【請求項 3 4】**

前記半導体デバイス書き込み要素のソースとドレインは前記ストレージ・トランジスタのゲート電極として同じ材料層から製造されることを特徴とする請求項31に記載の半導体メモリ素子。

**【請求項 3 5】**

前記メモリ・セルはアクセス・コンデンサ素子をさらに含み前記アクセス・コンデンサ素子の一方の端子が前記ストレージ・ノードに接続されることを特徴とする請求項33に記載の半導体メモリ素子。

**【請求項 3 6】**

前記アクセス・コンデンサ素子の第2の端子は読み出しワード線に接続されることを特徴 10 とする請求項35に記載の半導体メモリ素子。

**【請求項 3 7】**

前記アクセス・コンデンサ素子の一方の端子は前記ストレージ・トランジスタのゲート電極で形成されることを特徴とする請求項35に記載の半導体メモリ素子。

**【請求項 3 8】**

前記アクセス・コンデンサ素子の第1のプレートは前記半導体デバイス書き込み要素のソース及びドレインと同じ材料層により形成されることを特徴とする請求項35に記載の半導体メモリ素子。

**【請求項 3 9】**

複数のワード線と、

複数のデータ線と、

前記ワード線とデータ線の交点にあるメモリ・セルとを含み、各メモリ・セルは、ゲート端子がストレージ・ノードへ電気的に接続してあるストレージ・トランジスタと、

ゲート端子が読み出しワード線へ電気的に接続してありソースまたはドレイン領域が前記ストレージ・トランジスタのソースまたはドレイン領域へ接続される読み出しトランジスタと、

ゲート端子が書き込みワード線へ電気的に接続される半導体書き込みデバイスとを含み、前記半導体書き込みデバイスはソース領域とドレイン領域が絶縁層の上部に5ナノメートルを越えない厚みの半導体材料で形成されたチャンネルによって接続される金属または半導体材料から製造されることを特徴とする半導体メモリ素子。

**【請求項 4 0】**

複数のセンスアンプをさらに含み、前記センスアンプの一つが各データ線に接続されて読み出し動作中に信号を增幅することを特徴とする請求項39に記載の半導体メモリ素子。

**【請求項 4 1】**

前記ストレージ・トランジスタがNチャンネルMOSデバイスであることを特徴とする請求項40に記載の半導体メモリ素子。

**【請求項 4 2】**

読み出しデータ線上の信号を增幅してパストランジスタ経由で書き込みデータ線へ印加してから書き込みトランジスタを活性化してデータを保存するような方法でリフレッシュ動作が行なわれることを特徴とする請求項41に記載の半導体メモリ素子。

**【請求項 4 3】**

書き込みデータ線と読み出しデータ線が組み合わされることを特徴とする請求項41に記載の半導体メモリ素子。

**【請求項 4 4】**

データ線上の信号を增幅してから書き込みトランジスタを活性化しデータを保存するような方法でリフレッシュ動作が行なわれることを特徴とする請求項43に記載の半導体素子。

**【請求項 4 5】**

複数のワード線と、

複数のデータ線対と、

20

30

40

50

前記ワード線とデータ線対の交点にあるメモリ・セルとを含み、前記メモリ・セルの各々が2個の転送トランジスタを含み、第1の転送トランジスタは第1のストレージ・ノードから第1のデータ線対へデータを転送し、第2の転送トランジスタは第2のストレージ・ノードから第2のデータ線対へデータを転送し、各転送トランジスタは同一のワード線によって活性化され、

絶縁薄膜上で5ナノメートルを越えない厚みを有する半導体材料で形成されるチャンネルによって接続されたソース領域とドレイン領域が金属または半導体材料で製造される2個のストレージ半導体デバイスをさらに含み、前記チャンネルの電圧レベルが前記半導体デバイスのゲート電極の電圧により影響を受け、前記半導体デバイスは前記第1と第2のストレージ・ノードへ交差接続により反転して構成される

10

ことを特徴とする半導体メモリ素子。

【請求項46】

前記ストレージ半導体デバイスのドレインまたはソースからの電流リークが前記転送トランジスタのドレインまたはソースからの電流リークより小さいことを特徴とする請求項45に記載の半導体メモリ素子。

【請求項47】

一対のデータ線に読み出し動作中に差分信号が提示されることを特徴とする請求項46に記載の半導体メモリ素子。

【請求項48】

差分信号を増幅してアクセスされたメモリ・セルにある情報を判定できるように各データ線対に接続されたセンスアンプをさらに含むことを特徴とする請求項47に記載の半導体メモリ素子。

20

【請求項49】

前記メモリ・セルの各々がさらにアクセス・トランジスタと、

ゲート端子が前記ストレージ・ノードの一方に接続され、ソースまたはドレイン領域が接地ノードに接続され、接地ノードに接続されていない前記ソースまたはドレイン領域の他方がアクセス・トランジスタのソースまたはドレイン領域に接続される読み出しどランジスタとを含み、

前記アクセス・トランジスタはゲート端子を含み、ゲート端子はワード線に電気的に接続され、前記読み出しどランジスタに接続されていない前記ソースまたはドレイン領域の他方が読み出しデータ線へ電気的に接続されることを特徴とする請求項45に記載の半導体メモリ素子。

30

【請求項50】

一対のデータ線に読み出し動作中に差分信号が提示されることを特徴とする請求項49に記載の半導体メモリ素子。

【請求項51】

前記読み出しどデータ線の電圧レベルを読み出し動作中に検出して前記メモリ・セルに保存された情報の値を検出することを特徴とする請求項50に記載の半導体メモリ素子。

【請求項52】

直列メモリ・セルの前記ストレージ・トランジスタのソースまたはドレイン領域が読み出しどデータ線へ電気的に接続され、同じ直列メモリ・セルの前記ストレージ・トランジスタのソースまたはドレイン領域の他方がサブデータ線へ電気的に接続されることを特徴とする請求項35に記載の半導体メモリ素子。

40

【請求項53】

前記メモリ・セルはさらにアクセス・トランジスタを含み、前記アクセス・トランジスタのソースまたはドレインが前記サブデータ線へ電気的に接続され、前記サブデータ線へ接続されていない前記アクセス・トランジスタのソースまたはドレインがソース・データ線へ電気的に接続され、前記アクセス・トランジスタのゲート端子がサブカラム・アクセス・ワード線へ電気的に接続されることを特徴とする請求項52に記載の半導体メモリ素子。

50

**【請求項 5 4】**

直列メモリ・セルのストレージ・トランジスタのソースまたはドレイン領域が前記列内の隣接するストレージ・トランジスタのソースまたはドレイン領域へ電気的に接続されることを特徴とする請求項 3 5 に記載の半導体メモリ素子。

**【請求項 5 5】**

前記列の一端にある前記ストレージ・トランジスタのソースまたはドレイン領域がデータ線へ電気的に接続されることを特徴とする請求項 5 4 に記載の半導体メモリ素子。

**【請求項 5 6】**

前記メモリ素子はさらにアクセス・トランジスタを含み、前記列の一端にある前記ストレージ・トランジスタのソースまたはドレイン領域が前記アクセス・トランジスタのソースまたはドレイン領域へ電気的に接続され、前記ストレージ・トランジスタへ接続されていない前記アクセス・トランジスタのソースまたはドレイン領域がソース・データ線へ電気的に接続され、前記アクセス・トランジスタのゲート電極がサブカラム・アクセス・ワード線へ電気的に接続されるようにしてあることを特徴とする請求項 5 4 に記載の半導体メモリ素子。 10

**【請求項 5 7】**

複数のワード線と、

複数のデータ線と、

前記ワード線とデータ線の交点にあるメモリ・セルとを含み、前記メモリ・セルの各々がゲート端子がストレージ・ノードへ電気的に接続してあるストレージ・トランジスタと、前記ストレージ・ノードへ電気的に接続された書き込みワード線によって活性化される半導体書き込みデバイスとを含み、前記半導体デバイスはソース領域とドレイン領域が絶縁薄膜上で 5 ナノメートルを越えない厚みの半導体材料で形成されるチャンネルによって接続された導体から製造されることを特徴とする半導体メモリ素子。 20

**【請求項 5 8】**

前記導体が金属または半導体材料であることを特徴とする請求項 5 7 に記載の半導体メモリ素子。

**【請求項 5 9】**

マスキング・ステップを含めて前記ストレージ・トランジスタの多結晶シリコン・ゲート端子が N 型または P 型の不純物打ち込みを有し前記書き込みトランジスタの多結晶シリコン・ソース及びドレイン領域が前記ストレージ・トランジスタと対向する型の不純物打ち込みを有するようにすることを特徴とする請求項 5 8 に記載の半導体メモリ素子。 30

**【請求項 6 0】**

前記書き込みトランジスタの前記多結晶シリコン・ドレイン及びソース領域の上部が前記多結晶シリコン・ドレイン及びソース領域の下部より高い不純物濃度を有することを特徴とする請求項 5 8 に記載の半導体メモリ素子。

**【請求項 6 1】**

第 1 導電型の多結晶シリコンの層と、金属またはシリサイドの層と、第 2 導電型の多結晶シリコン層が積層され構成される縦型スタック構造を用い、前記縦型スタック構造の下部は前記ストレージ・トランジスタのゲート端子に、また前記縦型スタック構造の上部は前記書き込みトランジスタのソースまたはドレイン領域になるように前記縦型スタック構造を構成することを特徴とする請求項 5 8 に記載の半導体メモリ素子。 40

**【請求項 6 2】**

前記書き込みトランジスタのソースまたはドレイン領域の一方が前記ストレージ・トランジスタのソースまたはドレインの垂直方向に真上に製造されることと、これら 2 つの垂直方向に向いた端子が 2 つの端子の間のコンタクトにより電気的に接続されることを特徴とする請求項 5 8 に記載の半導体メモリ素子。

**【請求項 6 3】**

前記書き込みトランジスタのチャンネル領域は前記垂直方向に形成され、前記書き込みトランジスタのチャンネル領域が前記ストレージ・トランジスタの多結晶シリコン・ゲート 50

端子を前記ストレージ・トランジスタのゲート端子の垂直方向に真上に配置された金属または多結晶シリコンのデータ線と接続するようにしてあることを特徴とする請求項 5 8 に記載の半導体メモリ素子。

【請求項 6 4】

半導体または金属の層が垂直方向に形成され、絶縁層によりチャンネル領域から電気的に絶縁され、前記書き込みトランジスタのゲート端子として機能することを特徴とする請求項 6 3 に記載の半導体メモリ素子。

【請求項 6 5】

複数のワード線と、

複数のデータ線と、

10

前記ワード線とデータ線の交点にあるメモリ・セルとから構成され、前記メモリ・セルの各々はゲート端子がストレージ・ノードへ電気的に接続してあるストレージ・トランジスタと、

前記デバイスのゲート端子へ電気的に接続された書き込みワード線により活性化される半導体書き込みデバイスとを含み、前記デバイスのソースまたはドレイン領域が前記ストレージ・ノードへ電気的に接続され、

一対のメモリ・セルの各々が別のデータ線へ接続されることと、前記各々のセルで前記ストレージ・ノードへ接続されていない前記メモリ・セルの対の各々の前記半導体書き込みデバイスのソースまたはドレイン領域が電気的に接続されることを特徴とする半導体メモリ素子。

20

【請求項 6 6】

第 1 のスイッチ素子と、

第 1 のキャパシタ素子とを含み、前記第 1 のキャパシタ素子の第 1 の端子はストレージ・ノードで前記第 1 のスイッチ素子の第 1 の端子へ電気的に接続され、前記第 1 のスイッチ素子は外部データ線の電圧に基づいて充電ノードへ電荷を転送するのに適していることと、

さらに前記外部データ線は少なくとも 2 つの電圧値を取得するのに適し前記メモリ・セルへの書き込み動作中に前記少なくとも 2 つのデータ線電圧値の高い方に関係するストレージ・ノードでの電荷が前記少なくとも 2 つのデータ線電圧値の低い方のストレージ・ノードでの電荷より低いことを特徴とする半導体メモリ素子。

30

【発明の詳細な説明】

【0 0 0 1】

【発明の属する技術分野】

本発明は半導体メモリに係り、特にダイナミック・ランダム・アクセス・メモリ (D R A M) に関するもので、さらに詳しくは、本発明は高密度低電力半導体メモリ用の一連のセル構造、構成、活性化方式に関する。

40

【0 0 0 2】

【従来の技術】

従来の D R A M メモリ・セルは 1 個のトランジスタと 1 個のコンデンサで構成され（これを 1 T 1 C 構造と呼ぶ）高いビット密度が要求される場合、半導体メモリとして一般に使用されている。この技術は幾つかの欠点がありデバイス寸法が小さくなるにつれ大幅に複雑化する。もっとも注目すべきは、D R A M セルが内部利得を持たないため、大容量素子 (~ 3 0 f F) を各セルに製造して充分に検出できる程度に大きな電荷を蓄える必要がある。そのため複雑なコンデンサ構造と高価な材料を使用して充分な容量のデバイスを製造する必要があり、製造が高価になり標準論理回路プロセスと非互換になる。

【0 0 0 3】

これらの制約に応えて、小面積利得セル・メモリ技術が提案された。これらは 2 個または 3 個のトランジスタセルで構成し電荷は読み出しトランジスタの導通が変化するような方法で保存し、内部利得を提供する（例えば、特許文献 1 または 2 を参照）。しかし、これらの技術が広く受け入れられるのを妨げるような様々な問題を示している。問題の中でも

50

、セルの大きさがD R A Mと比べて大きすぎる。これは追加のトランジスタまたは配線に使う空間で使用される余分な面積による。たとえば、多くのセルで、2本のデータ線と2本のワード線が必要で、セルサイズが線ピッチの2倍に制限される。

#### 【 0 0 0 4 】

利得セル技術が示す他の問題としては保存容量が小さいことによる保持時間の短さと漏れ電流の大きいことが挙げられる（例えば、特許文献3または4を参照）。さらに、駆動検出方式が従来のD R A Mメモリに使われている方式よりも複雑になることが多い。マルチトランジスタ利得セルには複雑な製造プロセスが必要で、これによりD R A Mの代用としての利用の可能性が減少する。

#### 【 0 0 0 5 】

##### 【特許文献1】

特開平5-243522号公報

##### 【特許文献2】

特開2001-282588号公報

##### 【特許文献3】

特開昭62-226494号公報

##### 【特許文献4】

特開2000-269457号公報

#### 【 0 0 0 6 】

##### 【発明が解決しようとする課題】

上記の従来技術で述べたように、従来のD R A Mメモリ・セルの1T1C構造は、デバイス寸法が小さくなるにつれ大幅に複雑化すると言う問題がある。これらの制約に応えて、これらは2個または3個のトランジスタセルで構成し電荷は読み出しトランジスタの導通が変化するような方法で保存し、内部利得を提供する小面積利得セル・メモリ技術が提案された。しかし、この技術においても、セルの大きさがD R A Mと比べて大きすぎるという問題がある。これは追加のトランジスタまたは配線に使う空間で使用される余分な面積によるものである。さらに、利得セル技術は、保存容量が小さいことによる保持時間の短さと漏れ電流の大きいという問題が挙げられる。

#### 【 0 0 0 7 】

本発明は、少なくとも一つの好適実施例において、複数のメモリ・セルを含み、各々が利得セル構造を含むメモリを提供することを目的とする。さらに、本発明は方法を書き込む方法を含み、ストレージ・ノードに保存された電荷がデータ線の電圧と逆比例の関係を有する。従来のメモリではストレージ・ノードは書き込みデータ線へ書き込みトランジスタ経由で接続されるが、本発明の方法ではノードが通常書き込みデータ線に接続され一定の基準電圧に固定される。この場合、情報の状態とは関係なく一定電圧がストレージ・ノードに書き込まれる。

#### 【 0 0 0 8 】

さらに、データ線とストレージ・ノード間の容量（キャパシタンス）はセルへ情報を書き込むのに利用される。このデータ線の電圧が書き込み動作中の情報を決定する。書き込みワード線を活性化する前、データ線は希望する保存電圧値とは逆の関係に設定される。ワード線がこのあとで活性化されて電荷がストレージ・ノードへ転送され基準ノードの一定電圧と等価化される。ワード線が非活性化された後、基準電圧ノードからストレージ・ノードを遮断し、データ線をスタンバイ状態の電圧に復帰させる。このデータ線電圧での電荷がデータ線とストレージ・ノードの間の容量的関係のためストレージ・ノードに対する電荷を発生させ、情報がセルに保存される。

#### 【 0 0 0 9 】

##### 【課題を解決するための手段】

上記目的を達成するために、半導体メモリ・セルは隣接するセルの間で基準ノードを共有することにより小さい表面積を実現できる。さらに、定電圧がストレージ・ノードに書き込まれるので、ワード線用に電圧ブースト回路を追加する必要がなくなり、メモリアレイ

10

20

30

40

50

の周辺回路で必要な面積が減少する。この技術は本発明にしたがって提示される幾つかの 2 T および 3 T メモリ・セル構造で使用される。

【 0 0 1 0 】

さらに、本発明の少なくとも一つの実施例によれば、薄型チャンネル・トランジスタを備える内部利得ありのメモリ・セルがストレージ・ノードへの電荷転送素子として使用される。この薄型チャンネル・トランジスタは幾つかの方法で製造できるが、5 ナノメートルと等しいかそれ以下の厚みのチャンネル領域を持つように画成する。薄型チャンネル・トランジスタはソース・ドレイン間の漏れ電流が 10 のマイナス 16 乗アンペアを越えないことが特徴である。このデバイスでは、3 T (3 トランジスタ) メモリ・セルを製造すると従来のセルの 100 倍を越える保持時間 (リテンション時間) が得られ、低電力ダイナミック・メモリとして 3 T セルを適当な解決策にすることができる。 10

【 0 0 1 1 】

本発明によれば、メモリ・セルは定電圧基準ノード書き込み方法と薄型チャンネル電荷転送トランジスタを組み合わせて高密度低電力ダイナミック・メモリを実現するメモリが提供される。このメモリ・セルはダブルゲート読み出しトランジスタのある 2 T 構造と、ストレージ及び読み出しトランジスタが別々に各セルに含まれる 3 T セルで製造される。さらに、2 T セルに由来しサブカラムに構成した直列接続のメモリ・セルを持つか、サブカラムに構成した並列接続メモリ・セルを持つメモリも提供される。

【 0 0 1 2 】

本発明は従来の D R A M メモリに匹敵するかこれを越える密度が得られる。また、この種のメモリ・セルは、容量素子を追加してリテンション時間を増加させるように提供される。 20

【 0 0 1 3 】

少なくとも一つの実施例において、メモリはスタティック型動作を行なう 4 トランジスタ (4 T) 構成でメモリ・セルに使用される薄型チャンネル・トランジスタを含む。メモリ・セルは 2 個のアクセス・トランジスタと 2 個の薄型チャンネル・トランジスタを交差結合自己復元構造で含むのが望ましい。データ線からバルク・トランジスタを通るソース・ドレイン間の漏れ電流はストレージ・ノードからの漏れ電流より大きく、安定なメモリを実現でき、リフレッシュ動作の必要性がない。さらに、薄型チャンネル・トランジスタはバルク・トランジスタより大幅に小さい表面積で製造でき、メモリ・セルの寸法を劇的に縮小できる。さらに別の実施例では、別々の 2 トランジスタ読み出し回路を各セルに含めることで 4 トランジスタ・セルの読み出し時間の遅さを克服する。このようにすると、低電力高速メモリ・セルができる。 30

【 0 0 1 4 】

【発明の実施の形態】

本発明の図面及び説明は、本発明を明解に理解するために必要な要素を図示する目的で簡略化しており、同時に簡明にするために、周知と思われる他の要素は除外してある。本発明を実施するためにその他の要素が望ましいか、または必要であることは当業者には理解されよう。しかし、このような要素は当該技術において周知であって、本発明のより良い理解を助けるものではないため、このような要素の説明は本明細書では提供しない。本明細書での以下の詳細な説明は添付の図面を参照して提供する。 40

【 0 0 1 5 】

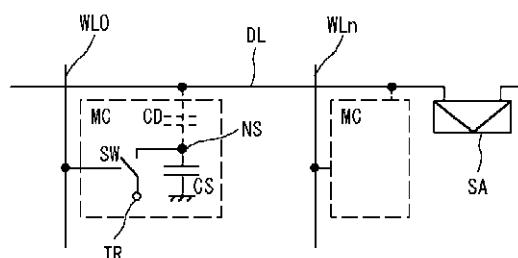

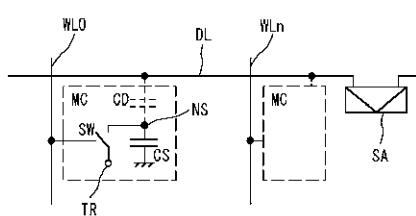

本発明の少なくとも一つの好適な実施例において、メモリ・セルは図 1 に示したように 1 個のストレージ・キャパシタ C S にストレージ・ノード N S で接続してある少なくとも 1 個のスイッチ素子 S W から構成する。スイッチ素子 S W は定電圧基準ノード T R または書き込みデータ線のどちらかに結合される。さらに、キャパシタに蓄えられる電荷の関係が書き込みサイクルの書き込みワード線活性化区間の間にデータ線の電圧に対して逆になるような方法で、たとえばデータ線とストレージ・ノード N S との間の容量結合 C D などで、データ線 D L がセルに接続してある。

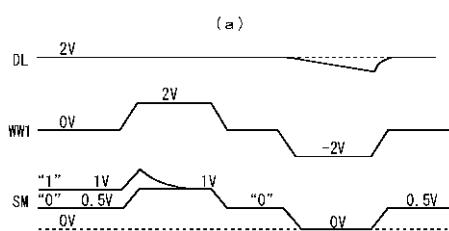

【 0 0 1 6 】

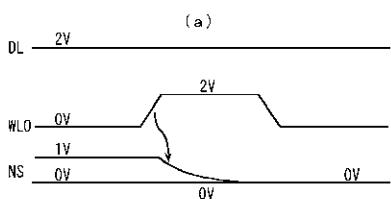

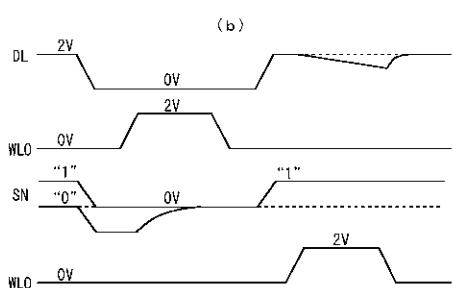

情報を書き込む方法は、2進値データを保存する以下のような方法で説明できる。図2aに示してあるように低値データを書き込む場合、データ線DLはデータ保存状態の間と同じ電圧に維持される。その後、書き込みワード線WL0がスイッチ素子SWを作動させ電荷をストレージ・ノードNSへ転送できるようにして、ストレージ・ノードNSにかかる電圧が基準ノードTRの定電圧と等しくなるようにする。電荷転送スイッチSWはこのあとで書き込みワード線WL0経由で停止され、ストレージ・ノードNSの電圧が低値を表わす基準ノードの電圧V<sub>TR</sub>と等しいままになるようとする。

【0017】

高値データ書き込み動作について図2bを参照して説明する。最初に、データ線DLがスタンバイ状態の電圧より低い電圧にセットされる。この後、低値データ書き込み動作の場合と同様にスイッチSWを活性化してから停止させ、ストレージ・ノード電圧V<sub>NS</sub>を基準ノードの電圧V<sub>TR</sub>と等しくする。この時点で、データ線DLはスタンバイ状態の電圧に復帰する。何らかのメカニズムたとえば、データ線DLとストレージ・ノードNSをリンクする容量結合CDが存在するため、ストレージ・ノードにかかる電圧はデータ線にかかる電圧の変化に対する何らかの比率で上昇する。

【0018】

図1に示した図面で、ストレージ・ノードNSにかかる電圧はV<sub>TR</sub> + V<sub>DL</sub> \* CD / (CS + CD)に等しい。ここでV<sub>TR</sub>、V<sub>DL</sub>、CD、CSはそれぞれ基準ノード電圧、データ線にかかる電圧変化、データ線からストレージ・ノードへの容量、ストレージ・ノードのキャパシタンスである。このようにすると、データ線にかかる電圧が変化しなかった場合とはことなる電圧値がセルに保存される。同様に、データ線電圧とセル・ストレージ電荷の間の逆の関係が示される。これは、データ線DLにかかる電圧が導電性経路を通じて直接ストレージ・ノードNSへ転送される従来の場合とは対照的である。従来の書き込み方法では、ストレージ・ノードNSにかかる電圧が電荷転送フェーズの間にデータ線DLにかかる電圧と比例するようにセットされるため、ストレージ・ノードにかかる電荷はデータ線にかかる電圧に直接比例する。

【0019】

本発明により可能になる書き込み方法の一例として、図1に示した理想的な回路を考えてみると、値が1fFのストレージ・キャパシタCS、ストレージ・キャパシタと接地端子TR(0V)の間に接続されたスイッチSW、1fFのキャパシタンスCDを備えデータ線ヒストレージ・ノードNSの間に接続された2Vのスタンバイ電圧になっているデータ線DLがある。低値データ書き込みの間、図2aに図示してあるように、データ線DL電圧は2Vに維持されるが電荷転送スイッチSWは開いている。ストレージ・ノードNSにかかる電圧は書き込みワード線WL0が2Vに上昇したときに0Vに等しくなる。等価化の後、ワード線を0Vに下げ、書き込みスイッチSWを停止する。このようにすると、0Vがストレージ・キャパシタCSに保存される。

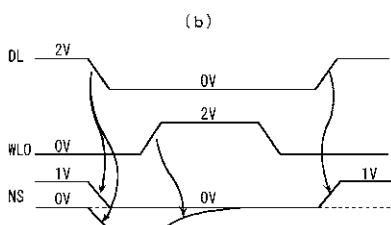

【0020】

図2bに示したように高値データの書き込み中は、データ線DL電圧が0Vに下がる。スイッチSWが作動すると、ストレージ・ノードNSがもう一度ソース・ドライン電圧と等しくなり、低値データ書き込みプロセスと同様にストレージ・キャパシタCSに0Vを保存する。この時点で、データ線DLは2Vに復帰する。データ線DLとストレージ・ノードNSの間の容量結合CDにより次式による電圧上昇が起こる：電圧(ノード)の変化 = 電圧(データ線)変化 \* C(ストレージ・ノードに対するデータ線) / C(ストレージ・ノード全体) [VN = VD \* CS / CTOT]。この場合、合計キャパシタンスは2fFであるから、1Vの変化がストレージ・ノードNSで観察される。このようにして、低値データは0Vで高値データは1Vになる。

【0021】

この方式では幾つかの現象が指摘されるに値する。その一つはデータ線DL電圧の下降と上昇が、アクセスされていないこのデータ線に接続してあるメモリ・セルに対してはなんの影響も与えないことである。これはデータ線DLがスタンバイ電圧から偏った場合でも

10

20

30

40

50

保存されている電荷がストレージ・ノード NS から移動するための経路がないことによる。別の作用は、書き込みワード線 WL 0 に接続してある全てのメモリ・セルが同時に書き込まれることである。これはデータ線 DL に新しいデータ値を提示する必要があるか、またはデータ線にセルのそれまでの内容を提示して保存されているデータに対する変化を行なわないようにする必要がある。半導体メモリに関する特定の利点については以下で説明する。

#### 【 0 0 2 2 】

データ線にかかる電圧の変化とは逆比例する保存電荷を持つセルに二つの別々の電圧値を保存できる基本的な書き込み動作を説明した。この動作コンセプトは、以下で「容量結合書き込み方法」と呼ぶことにするが、本発明で提示する実施例の少なくとも一つで使用される。容量結合書き込み方法はデータ線を適当な電圧値に設定してからワード線を活性化し、さらにデータ線をスタンバイ電圧レベルまで復元することにより多値データに拡張できる。このようにすると、多値データを各セルに保存でき、メモリのデータ密度を上昇させることができる。また、この動作では追加の書き込みデータ線の使用も不可能ではない。たとえば、書き込みデータ線電圧を何らかのレベルにセットして高速な書き込み時間を保証し、別のレベルにセットして長時間のデータ保持を保証することができる。読み出しデータ線の電圧レベルを調整することに加えて、書き込みデータ線の電圧レベルはある部分で読み出し動作中のストレージ・ノードのデータ値を決定することができる。この場合、高値データ書き込みサイクルの間にデータ線へ高電圧を印加し、低値データ書き込みサイクルの間にデータ線へ低電圧を印加する。

10

20

30

40

#### 【 0 0 2 3 】

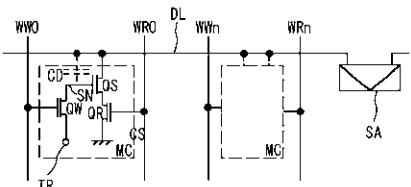

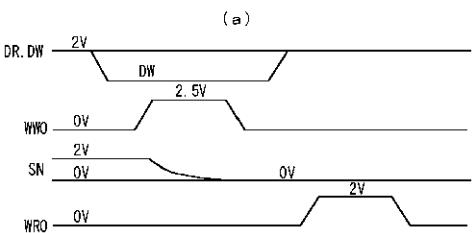

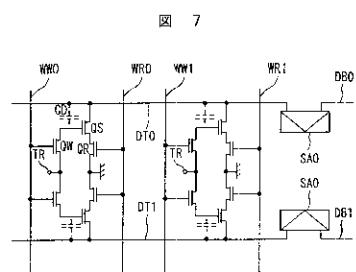

本発明の第 1 の代表的実施例では容量結合書き込み方法に基づく半導体メモリが実現可能で図 3 に図示してあるように単一のメモリ・セル MC に 3 個のトランジスタを含む。各々のメモリ・セル MC はストレージ・トランジスタ QS を含み、ストレージ・ノード NS のコンデンサ素子としてトランジスタ QS のゲートが機能する。書き込みトランジスタ・デバイス QW は電荷転送要素（すなわち SW ）として使用されるもので、書き込みワード線 WW 0 によって作動され、ストレージ・ノード NS と定電圧基準ノード TR の間に接続される。さらに、データ線 DL はキャパシタ CD によりストレージ・トランジスタ QS へ電気的に接続してある。読み出しトランジスタ QR はストレージ・トランジスタ QS のソースと定電圧基準ノード TR の間に接続され、読み出しワード線 WR 0 がゲート端子へ電気的に接続されている。

#### 【 0 0 2 4 】

この構造は図 5 に示した従来の 3T 構造と比較できる。従来のセルでは、各メモリ・セル MC は本実施例に示したセルと同様にストレージ・トランジスタ QS 、読み出しトランジスタ QR 、書き込みトランジスタ QW で構成される。しかし、読み出しトランジスタ QR は読み出しデータ線 DR 0 とストレージ・トランジスタ QS のドレインに直結され、ストレージ・トランジスタのソースは定電圧基準ノード TR ( 0 V ) へ接続され、ゲート端子がストレージ・ノード NS として機能し、書き込みトランジスタ QW はゲート端子へ接続された書き込みワード線 WW 0 により作動された場合書き込みデータ線 DW とストレージ・ノード NS を接続する。

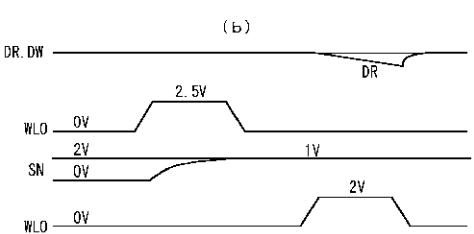

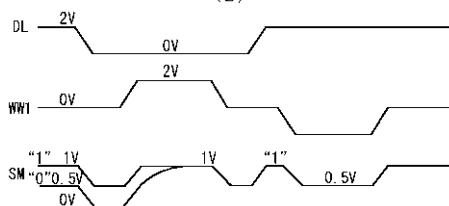

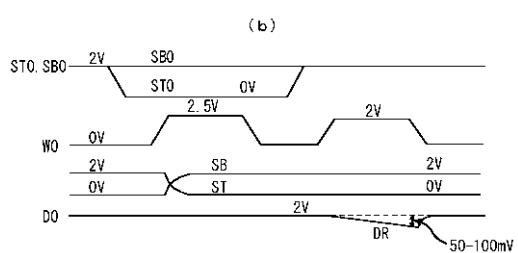

#### 【 0 0 2 5 】

これらの構造の間の一つの相違点は、従来の場合、図 6 a と図 6 b に図示してある波形のように、ストレージ・ノード NS に保存される電圧がアクセス中の書き込みデータ線 DW の値にセットされることである。書き込み動作では、電圧が書き込みデータ線 DW に提示されてから書き込みワード線 WW 0 が活性化され、高電圧 ( 2 V ) が高電圧データを書き込み、低電圧が低電圧データを書き込む。書き込みワード線 WW 0 が供給電圧 ( 2.5 V ) 以上の一つの閾値電圧 Vt を越えて上昇すると、ストレージ・ノード電圧は書き込みデータ線 DW と等しくなり、ついで書き込みワード線 WW 0 の電圧下降により書き込みトランジスタ QW が停止される。書き込みデータ線 DW はスタンバイ状態の電圧 ( 0 V ) にセットされる。このようにすると、電荷は書き込みワード線 WW 0 が活性化している期間中

50

に書き込みデータ線 D W に存在している電圧と直接比例してストレージ・ノード N S にセットされる。

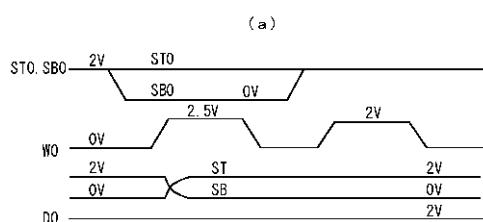

【 0 0 2 6 】

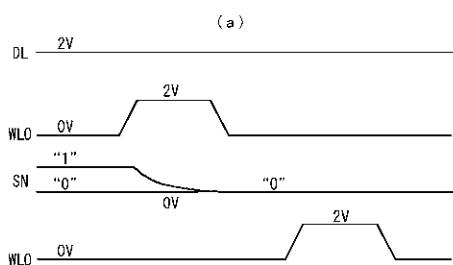

図 4 a と図 4 b に図示したこの代表的実施例に示したメモリでの書き込み動作は前述の容量結合方法に基づいたもので、書き込みワード線 W W 0 が書き込みトランジスタ Q W を活性化し、ストレージ・ノード N S と定電圧基準ノード T R を等価化する。データ線 D L 電圧を希望のストレージ・ノード電圧に逆比例して調節してから書き込みワード線 W W 0 の活性化を行ない、書き込み動作の後でスタンバイ電圧に復帰する。言い換えれば、データ線 D L は高値ストレージ・ノード・データでは低電圧 (0 V) にセットし、低値ストレージ・ノード・データでは高電圧 (2 V) にセットする。ストレージ・ノード N S が定電圧基準ノード T R (0 V) に等しくなった後、データ線 D L をスタンバイ状態電圧 (2 V) に復元する。C D がデータ線 D L とストレージ・ノード N S の間に存在しストレージ・トランジスタ Q S のゲート・ソース間キャパシタンスとノードへの配線からのキャパシタンスの和を構成するので、データ線 D L の電圧上昇によりストレージ・ノード N S での電圧の上昇が起こる。データ線 D L は低値ビット書き込みの場合変化しないことから、図 4 a に示したように、ストレージ・ノード N S は基準電圧 (0 V) のままとなる。

【 0 0 2 7 】

低電圧 (0 V) からスタンバイ電圧状態 (2 V) へ復元される場合、図 4 b に示したように、電圧は  $V_d * C_d / C_{tot}$  にしたがってストレージ・ノード N S へ誘導される。ここで  $V_d$ ,  $C_d$ ,  $C_{tot}$  はそれぞれデータ線電圧の変化、ストレージ・ノードに対するデータ線からのキャパシタンス、ストレージ・ノードの総キャパシタンスである。たとえば、 $V_d = 2 V$ ,  $C_d = 1 fF$ ,  $C_{tot} = 2 fF$  とすると、1 V の電圧がストレージ・ノード N S に結合される。明らかに、データ線電圧の大きな変化と、ストレージ・ノード・キャパシタンス C D とストレージ・ノード総キャパシタンスに対するデータ線キャパシタンスの大きな比により、大きな信号マージンが実現される。データ線 D L がスタンバイ状態電圧に復帰することでストレージ・デバイスが導通領域に入った場合、データ線からストレージ・ノードへのキャパシタンス C D は、チャンネルの導通によりゲート・ソース間キャパシタンスが増加することで増加する。

【 0 0 2 8 】

本実施例のメモリ・セルでは、情報がストレージ・トランジスタ Q S のゲートにセットされた電圧で表現されるので、このデータを決定するのに充分な方法はストレージ・トランジスタの導通の変化を検出することである。読み出し動作は読み出しワード線 W R 0 を活性化することにより読み出しトランジスタ Q R を導通領域にセットし、次にデータ線 D L を経由してまたはこの現象の副産物として生成された電流を検出することを含む。ストレージ・トランジスタ Q S の導通状態はゲート端子の電圧に依存するから、セルを流れる電流は保存されているデータの値により変化する。本実施例では、データ線 D L に接続した電圧センスアンプ S A でこの導通状態を検出する。読み出し動作の前に、データ線電圧をセット電圧までプリチャージしてから浮動状態にする。読み出しワード線 W R 0 を活性化すると、メモリ・セル M C から取り出される電流により、データ線に保存されている電荷の現象に由来するデータ線 D L の電圧レベルの低下が起こる。電圧センスアンプ S A を使用してこの電圧変化を検出し、メモリ・セル M C の情報値に対応するデジタル信号を生成する。

【 0 0 2 9 】

本実施例のメモリ構造の利点は、第 1 の代表的実施例の書き込み技術と 3 T メモリ・セル構造の組み合わせによることは注意すべきである。図 7 は本実施例のメモリの  $2 \times 2$  アレイを示したもので、書き込みデータ線を書き込まれるデータと無関係な値にセットすることで隣接するメモリ・セルがこのノードを共有できることを示している。従来の 3 T の例では、隣接セルに対して独立したデータ線を使用する必要があるが、本発明の方法により隣接するセルとの 1 本の接続を共有することでメモリ・セルの大きさを減少できる。

【 0 0 3 0 】

10

20

30

40

50

さらに、この技術は、従来の例では必要とされるワード・ブースト技術を必要としない。従来の場合、V<sub>dd</sub> (2V) または0Vを書き込みノードに提示することでそれぞれ高値及び低値がストレージ・ノードに書き込まれる。ストレージ・ノードへV<sub>dd</sub>を書き込む場合、書き込みトランジスタの閾値電圧V<sub>t</sub> (すなわち0.5V) では、ワード線電圧はV<sub>dd</sub> + V<sub>t</sub>までブーストする (すなわち2.5V) ことで充分な電圧転送を保証する必要がある。本発明で提供する容量結合書き込み方法では、書き込みノードが低電圧 (0V) にセットできるので、ブースト電圧を必要としないように書き込み電圧をセットできる (すなわち2V)。言い換えれば、両方の場合で低電圧が書き込まれるため、書き込み電圧はブースト電圧回路なしの場合でもV<sub>t</sub>より大きな差を必ず維持している。したがって、メモリは大面積大電力ワード・ブースト回路技術が不要になるので周辺回路の寸法を縮小でき、動作電力も削減できる。図7は読み出し、書き込み、スタンバイ状態でのメモリ・セル・アレイの動作電圧の例も示してある。このメモリ・デバイスの動作では電圧ブーストまたはダウンコンバートが不要である。

10

20

30

40

50

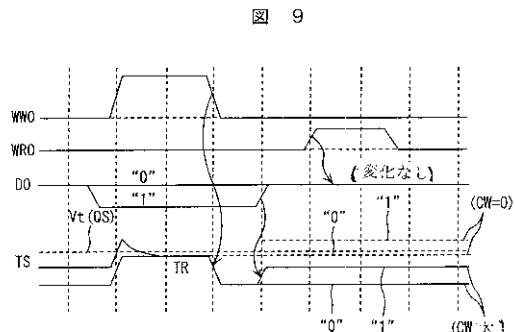

#### 【0031】

本実施例のメモリ・セルでは、Nチャンネル・デバイスまたはPチャンネル・デバイスをストレージ・デバイスとして使用できる、またはデータ線からソース・ノードへの容量が書き込み動作中に増加するようにデバイスの閾値電圧を調節する努力を行なうことができる。これらの例が有益な例を説明するため、セルのさらに正確な回路図を図8に示す。実際の半導体メモリでは、書き込みワード線WW0とストレージ・ノードNSの間のキャパシタンスCW、ならびにストレージ・ノードNSと読み出しトランジスタQR及びストレージ・トランジスタQSが共有する中間ノードNIの間のキャパシタンスCIが存在する。

#### 【0032】

図9に示したように書き込み動作中は、ストレージ・ノードNS電圧が定電圧基準ノードTRと等しくなってから、書き込みワード線WW0電圧を下げて書き込みトランジスタQWを停止する。書き込みワード線WW0とストレージ・ノードNSの間にはキャパシタンスCWが存在するので、電圧は式V<sub>W</sub>\*C<sub>W</sub>/C<sub>TOT</sub>にしたがってストレージ・ノードへ結合される。ここでV<sub>W</sub>, C<sub>W</sub>, C<sub>TOT</sub>はそれぞれワード線の電圧変化、ワード線とストレージ・ノードの間のキャパシタンス、C<sub>W</sub>, C<sub>S</sub>, C<sub>D</sub>, C<sub>I</sub>の総和に等しいストレージ・ノードの総キャパシタンスである。この場合、ストレージ・ノードにかかる電圧は書き込みワード線WW0とストレージ・ノードの間にキャパシタンスがない場合に予測される値より小さい (図9のキャパシタンスCW = 0)。両方のデータ値で保存される電圧が低すぎてストレージ・トランジスタQSが導通領域に入る (図9の「大CW」) 場合がある。言い換えれば、Nチャンネル・ストレージ・トランジスタで電圧が閾値電圧以下になることがある (図9のV<sub>t</sub>(QS))。

#### 【0033】

さらなる注意点は中間ノードNIとストレージ・ノードの間の容量結合CIである。高値データのスタンバイ状態では、中間ノードNIの電圧はおよそ読み出しデータ線の値になるが、これはストレージ・トランジスタQSが導通領域にあるためである。ただし読み出し期間中ストレージ読み出しトランジスタQSが活性化すると電圧は下降する。中間ノードNIでの電圧下降は式V<sub>i</sub>\*C<sub>i</sub>/C<sub>tot</sub>にしたがいストレージ・ノードNSの電圧降下を引き起す。ここでV<sub>i</sub>, C<sub>i</sub>, C<sub>tot</sub>はそれぞれ中間ノードでの電圧変化、中間ノードとストレージ・ノードの間のキャパシタンス、ストレージ・ノードの総キャパシタンスである。

#### 【0034】

この動作により高値状態にあるストレージ・ノードの電圧はストレージ・トランジスタQSが導通する点より下まで低下する。いずれかのデータ状態での導通が欠如している場合の解決方法の一つとしては、処理中にストレージ・トランジスタQSの閾値電圧を変化させ、高値電圧が少なくとも読み出しトランジスタQRを導通領域にまで活性化するのに充分なようにすることである。Nチャンネル・デバイスの場合、ストレージ・トランジスタ

Q S の閾値電圧を下降させることでデバイスは標準閾値電圧が高すぎる場合に導通できるようになる。別の解決方法はNチャンネル・デバイスをPチャンネル・ストレージ・トランジスタに置き換えることである。Pチャンネル型デバイスの場合、保存されているデータの電圧状態が低い程導通が良くなる。したがって、ワード線の電圧下降と中間ノードの電圧下降で発生した負の電圧は実際には大きな導通を発生する。

#### 【0035】

さらに、Nチャンネル書き込みデバイスはPチャンネル・デバイスに置き換えられる。この場合、ワード線の極性を反転させ、停止状態のストレージ・ノードの電圧の増加を惹起する必要がある。これらの技術の組み合わせはメモリ・セルが読み出し動作中にメモリ・セルのデータ状態の少なくとも一方について充分な電流を流せるように勘案できる。要するに、NチャンネルかPチャンネルのストレージ・トランジスタQ S が本実施例ではいっそう適している場合があり、また本明細書で説明する効果のため、言い換えれば一方の種類のトランジスタでの充分な読み出し動作を禁止するセル内の様々なキャパシタンスの相互作用により、後述の実施例でも同様である。

10

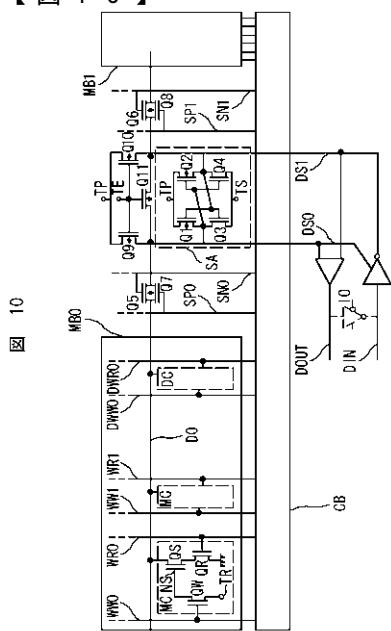

#### 【0036】

この代表的実施例での半導体メモリの周辺回路とのアレイ構造が図10に示してある。各メモリ・セルM C は前述したような3T構造を含みデータ線D 0 に接続してある。多数データ線と多数の読み出し書き込みワード線のあるメモリ・セルのアレイはメモリ・ブロックM B 0 に統合される。さらに、読み出しワード線W R 0 、W R 1 と書き込みワード線W W 0 、W W 1 の信号を制御する制御ブロックC B がメモリ・セルに接続される。

20

#### 【0037】

本実施例の追加コンポーネントはアクセスしたメモリ・セルM C の情報の値を決定するために使用する差電圧センスアンプS A である。電圧センスアンプS A は一対のNチャンネル・トランジスタ(Q 3 , Q 4 )と一対のPチャンネル・トランジスタ(Q 1 , Q 2 )を自己復元フリップフロップ構成で含む。この構成はメモリ・セルM C のせまいピッチで製造できることから適当な候補である。電圧センスアンプS A の更なる特徴はPチャンネル・パストランジスタQ 7 とNチャンネル・パストランジスタQ 5 で、これらは電圧センスアンプS A からメモリ・セルのデータ線を分離する。読み出し動作中に50~100mVの小さな差分信号がデータ線上に発生すると、カットオフ・スイッチQ 5 とQ 7 が選択線(S P 0 , ストレージ・ノード0)により停止されてデータ線D 0 が差電圧センスアンプS A から分離される。增幅器は独立した制御信号T S により作動して最大振幅差信号を生成する。

30

#### 【0038】

この電圧センスアンプS A の構造は幾つかの有利な特徴を持っている。第一にはメモリ・セルに保存される情報が読み出し動作で消去されないため、読み出し後の書き換え動作が不要なことである。したがって、增幅ステージの間にセンスアンプからデータ線を分離することにより、増幅器はデータ線を充電する必要がないので大幅に高速な読み出し動作が期待できる。同様に、データ線が分離されているので、最大電圧振幅が発生せず、プリチャージ・フェーズの間に、従来のDRAMセルに見られるようなVddの半分のプリチャージに対向して、データ線はおよそ100mVだけ充電される必要がある。最後に、データ線キャパシタンスの差は不可避的に増幅器の雑音源になる。データ増幅中にデータ線を分離することでこの雑音源を効果的に減少する。

40

#### 【0039】

また、本実施例のメモリオプションとして含まれるのはダミーセル構造D C である。セルの各カラムは一つのダミーセルD C を含むのが望ましい。このセルD C は通常のメモリ・セルM C で生成される二つの値のほぼ中間の信号を生成する。メモリ・セル・アクセス中に、読み出しワード線がデータ線に接続されたセルについてアサートされると、アクセスされているメモリ・セルM C のカラムとほぼ一致する電気的特性を持っているカラムに接続されたダミーセルについてダミー読み出しワード線がアサートされる。ダミーセルD C の使用は幾つかの理由から検出速度を劇的に改善する。差電圧センスアンプS A はデー

50

タの弁別に使用されるので、アクセスしたデータ線の電圧を基準電圧と比較する必要がある。ダミーセルDCは温度やプロセス変動に対して比較的低感度の電圧基準を生成できる。さらに、幾つかの雑音源たとえばワード線からデータ線への雑音がアクセス期間中に生成される。ダミーセルDCを経由して等価な雑音が生成されるので、ダミーセルを使用することでこうした雑音源の多くを効果的に打ち消すことができ、電圧センスアンプSAが確実にデータを判定するのに必要な時間を削減することができる。

#### 【0040】

本実施例で説明したメモリは「オープン・データ線」アーキテクチャに構成するのが望ましく、1本のワード線が通過する全てのカラムでセルを活性化するようにする。これにより従来のDRAMメモリで使用されているような、ワード線が通過するカラムの半分だけのメモリ・セルを活性化する「折り曲げデータ線」アーキテクチャより高いメモリ密度が可能になる。

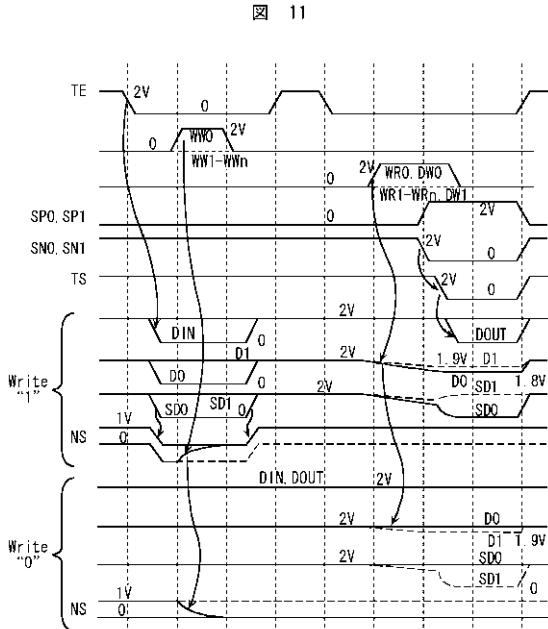

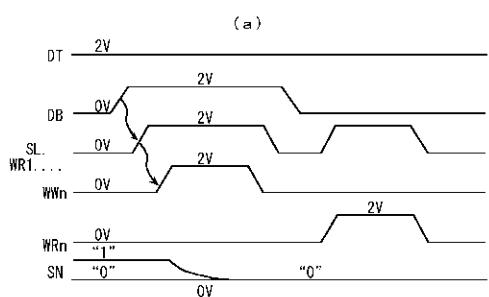

#### 【0041】

本実施例のメモリでのアクセス及び動作波形を図11に示す。この例では、書き込みワード線WW0に接続されているメモリ・セルは最初に書き込まれ、続けて読み出される。チャートの下半分は二つのセクションに分割しており、一方は高値データ書き込みアクセス（「1」書き込み）、他方は低値データ書き込みアクセス（「0」書き込み）である。書き込み動作は前述の容量結合書き込み方法に続き、データ線D0が書き込まれる電荷と逆比例する電圧でDINによりセットされる。さらに、ストレージ・ノードへのデータ線キャパシタンスCDはこの例のストレージ・ノード総キャパシタンスCTOTの半分であると仮定している。したがって、高値データ書き込みアクセスでのデータ線全振幅2Vでは、1Vの信号がストレージ・ノードに発生する。

#### 【0042】

低値データ書き込みアクセスでは、データ線D0が高電圧に維持される一方で書き込みワード線WW0がパルスされて定電圧基準ノードTR(0V)に対してストレージ・ノードNS電圧を平滑化する。データ線D0電圧は変化しないので、ストレージ・ノードNS電圧は書き込み動作後でも低値状態(0V)に留まる。高値データ書き込み動作では、データ線DLが低電圧状態(0V)まで引き下げられる。ストレージ・ノード電圧は書き込みワード線WW0をパルスしたときに0に等しくなり、データ線D0がスタンバイ電圧(2V)に復帰したときに容量結合書き込み方法にしたがって1Vのデータ信号が保存される。

#### 【0043】

データは前述した方法にしたがって読み出され、読み出しワード線WR0が活性化されデータ線(D0, D1)電圧がメモリ・セルとダミー読み出しトランジスタの導通にしたがって減少する。適当な信号がデータ線に発生すると、パストランジスタQ5, Q6, Q7, Q8が選択信号SPO, SNO, SP1, SN1により停止され、電圧センスアンプSAが信号TSにより作動する。最後に、増幅された信号がDOUT端子から読み出される。

#### 【0044】

本実施例に説明してあるメモリはまたリフレッシュしようとするセルの列のデータが最初に読み出されてそのセルに直接書き戻されるリフレッシュ方法を含むのが望ましい。最初に、標準的な読み出し動作を行ない読み出しワード線WR0が活性化し、充分な検出電圧が差電圧センスアンプSAに発生するとPチャンネルとNチャンネルのパストランジスタ・ペア(Q5, Q7)が非活性化し、センスアンプが活性化して最大振幅信号を発生する。この動作に続けて、PチャンネルとNチャンネルのパストランジスタQ5, Q7はもう一度活性化されてデータ線に最大増幅信号を提示する。この時点で、書き込み動作が行なわれ書き込みトランジスタQWが活性化してから非活性化されストレージ・ノードNSを等価化して容量結合書き込みが行なえるようになる。Nチャンネルのストレージ・トランジスタQSをもつメモリ・セルに保存された高電圧の場合、読み出し動作は低電圧データより大きな電流を発生し、ダミーセルDCに接続されたデータ線の電圧より低いデータ線

10

20

30

40

50

電圧が発生する。したがって、差電圧センスアンプ S A は低値供給レールへこの信号を増幅する。言い換えれば、セルに保存された高電圧は電圧センスアンプ S A に低電圧を発生し、またその逆も行なわれる。低値の供給電圧はデータ線に提示され書き込み動作が実行され、高電圧が容量結合書き込み方法にしたがってストレージ・ノードに書き戻される。同様に、供給高電圧がデータ線に提示されてから、書き込み動作が行なわれ、低電圧がストレージ・ノードに書き戻される。

#### 【 0 0 4 5 】

このようにして、単純なリフレッシュ動作を説明したように行なうことができる。P チャンネル素子をメモリ・セル M C 内のストレージ素子として使用する場合、ストレージ・ノードの低電圧では低電圧がセンスアンプから読み出される。したがって、この書き戻し動作は電圧反転回路を含める必要がある。このため、インバータ I 0 を D O U T 信号から D I N 信号に挿入してリフレッシュ部分の間だけ動作させ正しいデータ極性がセルに書き戻されるように保証することができる。第 1 の代表的実施例と同様に、N チャンネル・ストレージ・トランジスタを P チャンネル・トランジスタで置き換えることが可能な場合がある。これ以外のリフレッシュ方法も本実施例で想定しており、代表的な別のリフレッシュ回路については後述する。

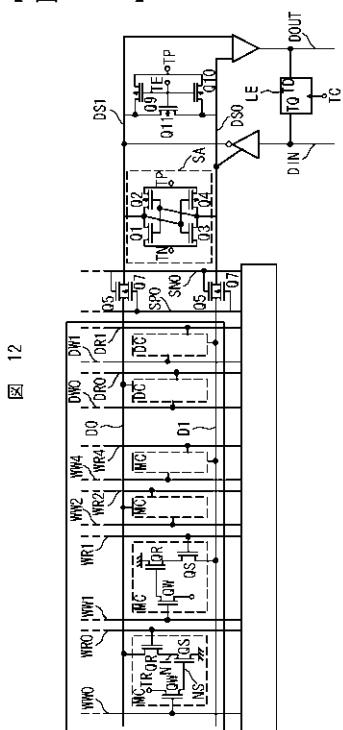

#### 【 0 0 4 6 】

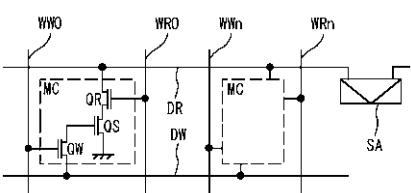

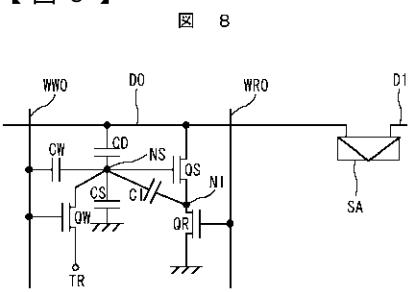

第 2 の代表的実施例では、図 12 のようなメモリを提供し、メモリ・セル M C の構造は読み出しトランジスタ Q R がデータ線 D 0 に直接接続されるような 3 トランジスタ構造を含む。さらに、書き込みトランジスタ Q W は定電圧基準 T R からストレージ・ノード N S へのスイッチ素子として機能し、ストレージ・トランジスタ Q S を使用してゲート端子がストレージ・ノード N S として機能させ、ソースを定電圧基準（すなわち接地電位）へ接続し、ドレインは読み出しトランジスタ Q R のソース領域へ接続する。書き込み動作は保存された電荷が読み出し動作の電荷転送期間の間にデータ線に逆比例する前述の容量結合原理に基づいている。主な相違点は、書き込みサイクルの容量結合効果が、詳細には後述するように、中間ノード N I とストレージ・ノード N S の総キャパシタンスの間のキャパシタンスから生成されることである。

#### 【 0 0 4 7 】

このセル構造の利点はストレージ・トランジスタ Q S をデータ線 D 0 から分離したことによる。ストレージ・トランジスタ Q S のゲート電極の電圧はメモリ・セルに保存されたデータにしたがって変動するので、ゲートから接合点までのキャパシタンスも変動する。第 1 の代表的実施例のようにこの接合点が直接データ線 D 0 に接続される場合、データ線のキャパシタンスは、差電圧の検出が阻害されるように変動することがある。本実施例では、読み出しトランジスタ Q R をデータ線に直結し、データ線に一定のビット・キャパシタンスを提示することにより潜在的に頑強な読み出し動作を実現可能にするものである。

#### 【 0 0 4 8 】

本実施例によるメモリは一対のデータ線データ線 D 0 、 D 1 へメモリ・セルの一つのカラムが接続されてデータ線が電気的に平衡になるようにした折り曲げデータ線構造も特徴としている。別の好適な特徴としては、一本のワード線をこれと交差するセルの半分だけに接続することである。つまり、ワード線が活性化された場合、これと交差するデータ線のうちの半分だけが活性化される。これによりワード線の電圧上昇に起因する雑音源を打ち消す差分信号が得られ、隣接するデータ線の間のキャパシタンスによる雑音源を減少させる。

#### 【 0 0 4 9 】

電圧センスアンプ S A は第 1 の代表的実施例と同様の構造をもつものが提供される。これには 2 個の N チャンネル・トランジスタ Q 1 、 Q 3 と 2 個の P チャンネル・トランジスタ Q 2 、 Q 4 からなるフリップフロップの対を含む。電圧センスアンプ S A は、 N チャンネル・トランジスタのソース・ノード T N の電圧降下による活性化時に、センスアンプデータ線 S D 0 、 S D 0 に最大振幅電圧を出力する。このようにすると、 2 本のデータ線 D 0

10

20

30

40

50

, D 1 に発生する差分信号は最大値電圧まで増幅できる。

【0050】

本実施例では、2個のダミーセルDCを各カラムに含め、一方のダミーセルの出力をデータ線D0, D1の対の一方に接続し、他方の出力をデータ線の対の他方に接続するのが望ましい。第2の実施例の場合と同様に、ダミーセルDCは通常のメモリ・セルが生成する2つの信号のほぼ中間の信号を生成するように構成する。読み出し動作の間、アクセスされたメモリ・セルによって、D0, D1のデータ線対の一方だけにデータが提示される。データ線対の他方に接続されたダミーセルDCに対応するダミー・ワード線DRの活性化は基準信号を提示する。この対は電圧センスアンプSAに提示され、増幅器が前述したようにデータ線上の差分を最大振幅電圧まで増幅する。ダミーセルによる解決方法では、各データ線対D0, D1について充分な基準を生成でき、高速な読み出し動作が得られる。

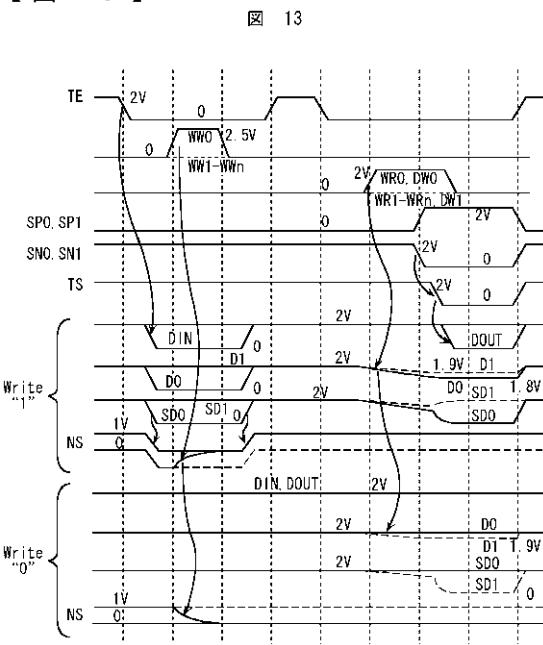

【0051】

書き込み動作は図13に示した波形に詳細に示されているように以下の原理にしたがって行なわれる。第1に、データ線D0へ電圧が提示される。第1の代表的実施例と同様に、データ線D0上の高電圧はストレージ・ノードNSに低電圧を書き込み、逆の場合も同様である。これに続けて読み出しトランジスタQRの活性化で中間ノードNIへデータ線電圧が流れる。データ線D0が高電位状態にある場合、ブーストされた読み出しワード線WR0を用いて読み出しワード線の電圧が供給電圧Vdd(すなわち2V)にトランジスタの閾値電圧Vt(すなわち0.5V)を加えたものより大きいか等しければ、データ線D0の最大信号を中間ノードNIへ流すことができる。それ以外の場合、読み出しワード線WR0の電圧が供給電圧Vddと等しければ中間ノードNI電圧へ転送される電圧はVdd - Vt(すなわち1.5V)と等しくなる。

【0052】

この動作につづけて、書き込みワード線WW0の活性化と非活性化が行なわれて書き込みトランジスタ入力の定電圧基準ノードTRとストレージ・ノードNSを等電位にする。次に、データ線D0の電圧がスタンバイ状態に復帰する。データ線が0から供給電圧Vdd(2V)へ上昇する場合、読み出しワード線電圧が供給電圧Vdd(2V)に設定されていれば中間ノードNI電圧は0からVdd - Vt(1.5V)まで上昇する。この動作はほぼ $V_i * C_i / C_{tot}$ の容量結合書き込み方法にしたがってストレージ・ノードNSへ電圧を結合する。ここで $V_i, C_i, C_{tot}$ はそれぞれ中間ノードでの電圧変化、中間ノードヒストレージ・ノードの間のキャパシタンス、ストレージ・ノードの総キャパシタンスである。最後に、読み出しトランジスタQRが読み出しワード線WR0により非活性化され、データ線D0からセルを電気的に分離する。

【0053】

本実施例で説明したメモリは2つの独立したサイクルに分割されたリフレッシュ方法を含むのが望ましい。第1のサイクルでは、リフレッシュしようとするセルの行についてデータがストレージ・レジスタLEに読み出される。これに続けて第1の実施例の標準の読み出しサイクルと同様の動作を行なうが、電圧が電圧センスアンプSAと出力データ線DOUTに完全に発生した後で、データはノードTCでデータ保存信号の活性化により入力TDを介してストレージ・レジスタLEに保存される点がとなる。後続のサイクルでは、リフレッシュ動作はストレージ・ノードNS上の電圧が完全に復帰されるように行なわれる。このサイクルの間、ストレージ・レジスタに保存された電圧が入力データDINに提示されNチャンネルとPチャンネルのパストランジスタ対Q5, Q7の活性化により直接データ線D0へ渡される。このデータが読み出しデータ線にセットされてから、リフレッシュしている行の書き込みデータ線が活性化されて非活性化され、次にデータ線が高電圧に復帰する。このようにすると、容量結合書き込み方法にしたがってデータを完全にリフレッシュできる。

【0054】

ストレージ・トランジスタがPチャンネルの場合、データ・レジスタLEは反転型でなければならない。これはPチャンネル・ストレージ・トランジスタQSでは高電圧が書き込

10

20

30

40

50

み動作中にデータ線に提示された場合読み出し中に低値信号がデータ線に発生するためである。この場合、ストレージ・レジスタ<sub>L E</sub>は保存されたビットの反転信号を出力する必要がある。リフレッシュ動作を二つのサイクルへ分割する利点の一つは、リフレッシュ動作割り込みによるアクセス時間の遅延が減少できることである。これはリフレッシュサイクルが書き戻し動作のすぐ後で読み出し動作を行なうことにより構成される従来の場合に對して、リフレッシュ割り込みが存在する場合に高速なアクセスを提供する。

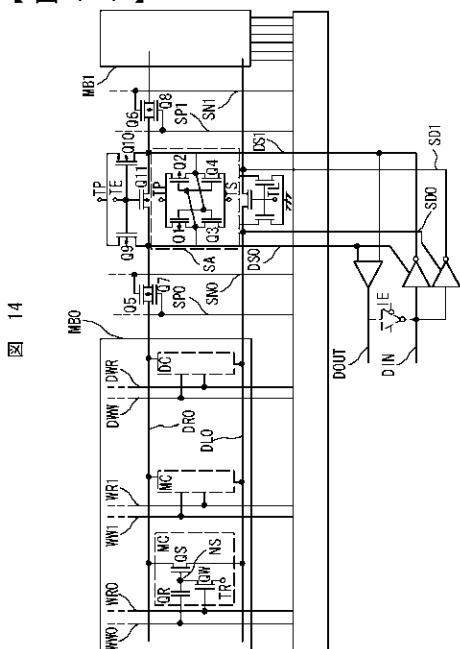

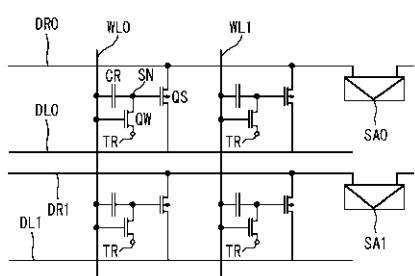

#### 【0055】

第3の代表的実施例は図14に示したようなメモリで、ストレージ・トランジスタ<sub>Q S</sub>と書き込みトランジスタ<sub>Q W</sub>を含む基本セルを含む。ストレージ書き込みトランジスタ<sub>Q S</sub>はソース・ノードが定電圧基準ノード<sub>T R</sub>へ接続してあり、ドレインノードがストレージ・トランジスタ<sub>Q S</sub>のゲート端子かストレージ・ノード<sub>N S</sub>に接続してある。ストレージ・トランジスタ<sub>Q S</sub>のソース・ノードとドレインノードはそれぞれ独立した読み出しデータ線<sub>D R 0</sub>とソースデータ線<sub>D L 0</sub>に接続する。さらに、ストレージ・トランジスタ<sub>Q S</sub>はストレージ・ゲートのゲート以上の第2のゲートを含み、これが読み出しワード線<sub>W R 0</sub>へ接続され読み出しワード線とゲート端子<sub>N S</sub>の間のキャパシタンス素子<sub>C R</sub>を形成する。

#### 【0056】

本実施例のメモリ・セルはオプションで第1の代表的実施例のそれと類似したアレイ構造を使用する。言い換えれば、オープン・データ線構造を使用してセルの寸法を縮小し、データ線の対がNチャンネル2個とPチャンネル2個のトランジスタのフリップフロップ対で構成された差電圧センスアンプ<sub>S A</sub>に入力する作動検出法を使用する。電圧センスアンプ<sub>S A</sub>はPチャンネルとNチャンネルのパストランジスタ対によってデータ線から分離される。

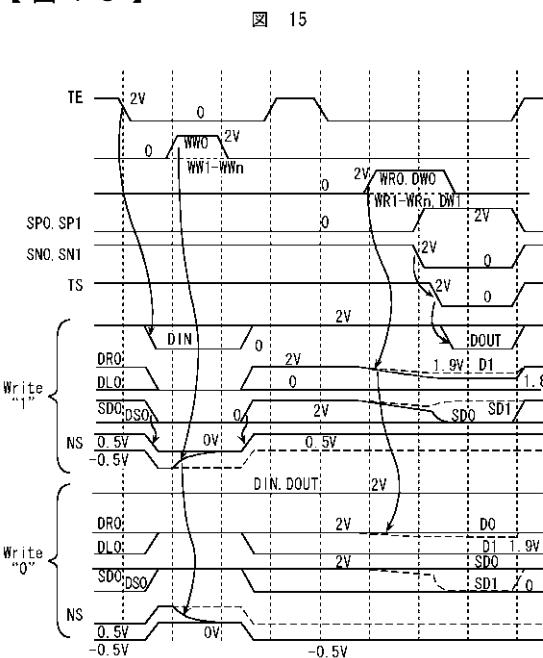

#### 【0057】

書き込み動作は第1実施例に示した容量結合書き込み方法と同様な方法に後続する。この方法を以下で説明し図15に図示する。スタンバイ状態の間、読み出しデータ線<sub>D R 0</sub>は高電圧レベル(2V)に維持され、ソース・データ線<sub>D L</sub>は低電圧レベル(0V)に維持される。低値を書き込むためには、読み出しデータ線<sub>D R 0</sub>を一定に維持したままソース・データ線<sub>D L</sub>を高値(2V)に引き上げる。この動作は書き込みワード線<sub>W W 0</sub>(0V)による書き込みトランジスタ<sub>Q W</sub>の活性化と非活性化に続き定電圧基準ノード<sub>T R</sub>とストレージ・ノード<sub>N S</sub>を等電圧にする。最後に、ソース電圧をスタンバイ状態の低電圧レベル(0V)に引き下げる。この場合、ストレージ・ノード<sub>N S</sub>には $(-V_s * C_s / C_{t o t})$ の誘導電圧がかかる。ここで $V_s$ ,  $C_s$ ,  $C_{t o t}$ はそれぞれソース線の電圧変化、ソース線とストレージ・ノードの間のキャパシタンス、ストレージ・ノードの総キャパシタンスである。

#### 【0058】

高レベル(0V)を書き込むには、読み出しデータ線<sub>D R 0</sub>をまず低電圧レベルまで下げる同時にソース・データ線<sub>D L</sub>を一定に保持しておく。ストレージ・ノード<sub>N S</sub>が定電圧基準ノード<sub>T R</sub>(0V)と等電位になった後、書き込みトランジスタ<sub>Q W</sub>を停止し読み出しデータ線<sub>D R 0</sub>をスタンバイ状態の電圧に復帰する(2V)。読み出しデータ線<sub>D R 0</sub>が上昇するので、 $V_R * C_R / C_{T O T}$ にしたがってストレージ・ノード<sub>N S</sub>に電圧が誘導される。ここで $V_R$ ,  $C_R$ ,  $C_{T O T}$ はそれぞれ読み出しデータ線<sub>D R 0</sub>の電圧変化、読み出しデータ線<sub>D R 0</sub>とストレージ・ノード<sub>N S</sub>の間のキャパシタンス、ストレージ・ノード<sub>N S</sub>の総キャパシタンスである。 $V_R$ と $V_S$ の高値および $C_R$ 対 $C_{T O T}$ ,  $C_S$ 対 $C_{T O T}$ の比率が高いことが、全てストレージ・ノードへの信号マージンの高さに關係する。

#### 【0059】

読み出し動作は読み出しワード線<sub>W R 0</sub>の電圧(2V)上昇を含む。読み出しワード線<sub>W R 0</sub>とストレージ・ノード<sub>N S</sub>の間には容量結合<sub>C R</sub>が存在するので、電圧が $V_W * C_W / C_{T O T}$ にしたがってストレージ・ノードに誘導される。ここで $V_W$ ,  $C_W$ ,  $C_{T O T}$

10

20

30

40

50

はそれぞれ読み出しワード線 W R 0 の電圧変化、読み出しワード線 W R 0 とストレージ・ノード N S の間のキャパシタンス、ストレージ・ノードのキャパシタンスである。したがって、読み出し動作の間に、ストレージ・トランジスタ Q S のゲート端子にかかる電圧は、低電圧データと高電圧データのそれぞれについて、 $( - V S * C S + V W * C W ) / C T O T$  と  $( V R * C R + V W * C W ) / C T O T$  で与えられる。通常、読み出しワード線 W R 0 が活性化したときにゲート端子の電圧だけがストレージ・トランジスタ Q S の閾値電圧 V t を越えるように値を設計する。したがって、現在アクセスされているセルだけが読み出しアクセス時に電流を発生する。

#### 【 0 0 6 0 】

このセル構造は 3 T タイプに対して狭い面積であると言う利点がある。さらに、セル面積は書き込みトランジスタ Q W への入力端子を隣接するセルの間で共有できるため従来の 2 T タイプに比べて減少できる。同様に、書き込みトランジスタの定電圧基準ノード T R からの入力電圧が供給電圧より低い少なくとも一つの閾値電圧に保持できることから、非ブースト型ワード書き込み電圧を第 1 の代表的実施例と同様に用いることができる。さらなる注意点は、書き込み動作の間、有効メモリ・セルを動作させるようにソースまたは読み出しデータ線の一方だけを調節すれば良いことである。言い換えれば、ソース・データ線を低信号用書き込み動作の間に活性化するのを省略できる。これ以外に、高信号用読み出し動作の間に読み出しデータ線を活性化するのも省略できる。ストレージ・ノードが一定電圧に維持されていれば、このデータ線を隣接セル間で共有することが可能であり、さらにセル面積を減少させられる。

#### 【 0 0 6 1 】

本実施例によるメモリ・セルではリフレッシュ方法は第 1 の代表的実施例で用いていたのと同様なものが望ましい（ただし別のリフレッシュ方法もあり得る）。相違点はソース・データ線 D L 0 も読み出しデータ線 D R 0 と一緒に活性化しなければならないことである。ソース・データ線駆動回路は読み出しデータ線と同じ回路を使用する、すなわち D I N 線から S D L 0 線への信号、および D I N 線から S D L 0 線への反転信号を渡す回路を使用する。したがって、D O U T の出力は読み出しデータ線駆動回路とソース・データ線駆動回路の両方に供給される。この動作によって、リフレッシュ動作の書き戻し部分の間、ソース・データ線 D L 0 と読み出しデータ線 D R 0 の両方を同じ電圧にセットする。さらに、P チャンネル・トランジスタをストレージ・トランジスタ Q S として動作させることができ、この場合 D O U T 出力信号は読み出しデータ線 D R 0 およびソース・データ線 D L 0 駆動回路へ送信する前にインバータ回路 I E で反転する必要がある。

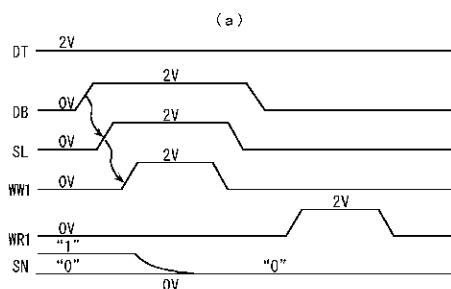

#### 【 0 0 6 2 】

第 4 の代表的実施例では図 14 に示したような第 3 実施例で用いたのと同じ構造のメモリが使用できるが、单一の書き込みワード線 W L 0 が、図 16 に示したように、書き込みトランジスタ Q W とストレージ・トランジスタ Q S の第 2 ゲート C R の両方へ接続してある点で異なる。さらに、ストレージ・トランジスタ Q S のチャンネル・タイプは書き込みトランジスタ Q W と逆のタイプである。この説明では、書き込みトランジスタ Q W は N チャンネル・タイプでありストレージ・トランジスタ Q S が P チャンネル・タイプであると仮定する。しかし、この構造は本実施例の趣旨を変更することなく逆転させることができる。図 17 a と図 17 b は各々低値データ書き込み動作と高値データ書き込み動作のアクセス波形を示している。説明を簡略にするため、定電圧基準ノード T R の電圧は 1 V とし、第 2 ゲート C R のキャパシタンスとデータ線からストレージ・ノード N S へのキャパシタンスが両方ともストレージ・ノード総キャパシタンスの 1 / 4 であると仮定する。スタンバイ状態では、書き込みワード線 W L 0 電圧が書き込みトランジスタ Q W と読み出しトランジスタ Q R のどちらかを活性化するのに必要な電圧の間の中間の値で保持される。

#### 【 0 0 6 3 】

書き込み動作は第 3 の代表的実施例で説明した読み出しデータ線 D R 0 とソース・データ線 D L 0 の活性化方法と同様に開始する。読み出しデータ線 D R 0 とソース・データ線 D L 0 を適当な電圧にセットし、書き込みワード線 W L 0 を高電圧に上昇させて書き込みト

10

20

30

40

50

ランジスタ Q W を活性化しストレージ・ノード N S と定電圧基準ノード T R を等電圧にする。書き込みワード線 W L 0 の非活性化に続けて、読み出しデータ線とソース・データ線をスタンバイ状態に戻すことでストレージ・ノード N S にかかる電圧値を保存する。第 3 の代表的実施例と同様に、高値で保存される電圧は  $V_{ref} + V_r * C_r / C_{tot}$  、また低値の電圧は  $V_{ref} - V_s * C_s / C_{tot}$  である。低電圧状態がストレージ・トランジスタ Q S を活性化しないように値を設計する。

## 【 0 0 6 4 】

読み出し動作は読み出しデータ線 D R 0 が浮動し書き込みワード線 W L 0 電圧が下がったときに開始する。ストレージ・ノードに誘導される電圧の変化は  $-V_w * C_w / C_{tot}$  である。ストレージ・トランジスタ Q S が少なくともデータ値の一方で導通領域に入るようこれら値を設計する。この時点で、電流がメモリ・セルを通って流れ、読み出しデータ線 D R 0 に電圧変化を惹起する。データを識別した後、読み出し動作は書き込みワード線 W L 0 電圧をスタンバイ状態にまで上昇させて終了する。

## 【 0 0 6 5 】

本実施例によるメモリ・セル M C では、アレイ構造、電圧センスアンプ S A 、リフレッシュ方法が全て第 3 の代表的実施例の 2 T 構造と同様であるのが望ましい。このメモリ・アレイではセルあたり 1 本のワード線を使用するため小面積サイズを実現している。

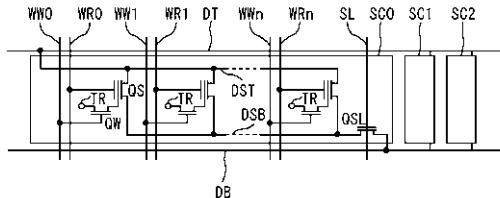

## 【 0 0 6 6 】

第 5 の代表的実施例では、図 18 に示したようなメモリが得られ、ここで直列の 2 T メモリ・セルにストレージ・トランジスタ Q S が並列に接続されて、第 4 の代表的実施例で示したような容量結合書き込み技術を使用する。セル構造は第 3 の代表的実施例のメモリ・セルと同様で、書き込みトランジスタ Q W がストレージ・トランジスタ Q S のゲート電極と定電圧基準ノード T R に接続してある。同様に、ストレージ・トランジスタ Q S は第 2 ゲートが第 1 ゲートの付近に固定され読み出しワード線 W R 0 が電圧上昇したときにセルを活性化するために使用する。このメモリと第 3 の代表的実施例のメモリの間の主な相違点はカラム内のセルのサブセット M C 0 について各ストレージ・トランジスタ Q S のソース端子がサブ・ソース・データ線 D S B に接続してあることである。このサブ・ソース・データ線 D S B はさらに、選択線 S L を活性化したときサブカラム・アクセス・トランジスタ Q S L 経由で主ソース・データ線 D B に接続される。

## 【 0 0 6 7 】

書き込み動作は第 1 実施例のそれと同一であり波形を図 19 a と図 19 b に図示してある。要約すると、読み出しデータ線の電圧は書き込みビットと対向する極性の値にセットされ、データは読み出しデータ線がスタンバイ電圧に復帰した後でセットされる。読み出し動作は第 3 の代表的実施例と同様で、読み出しワード線 W R 0 が電圧 ( 2 V ) にセットされ、これが第 2 ゲートの接続を介してストレージ・トランジスタ Q S を活性化する。さらに、サブカラム・アクセス・トランジスタ Q S L も選択線 S L 0 によって活性化されメモリ・セルを通る電流パスを有効にする。このセルではサブカラム・アクセス・トランジスタ Q S L による最小限の増加があるものの 2 T セルの小さいサイズを実現する。しかし、このセルは読み出し動作の間に読み出しデータ線に接続されるセル個数を実効的に減少したことにより通常の 2 T メモリで考えられる大きなリード電流を克服している。その結果として選択されていないセルからの電流が劇的に減少したことによる高速な読み出し時間が得られる。

## 【 0 0 6 8 】

このメモリでは第 1 の代表的実施例で提示したのと同一のオープン・データ線構造、同一の差電圧センスアンプ S A 、ダミーセル概念、類似のリフレッシュ動作を使用する。しかし、第 2 の代表的実施例（及びその他）で提示した周辺回路および方法も、条件が整っていれば使用できる。さらに、回路内の他のノードからの結合効果がストレージ・トランジスタを導通領域に入らないようにすると思われる場合には、ストレージ・トランジスタ Q S で N チャンネル・デバイスを P チャンネル・デバイスに置き換えることができる。同様に、サブカラム・アクセス・トランジスタとセル書き込みトランジスタを P チャンネル・

10

20

30

40

50

デバイスに置き換える逆の極性のアクセス信号に入れ換えることができる。

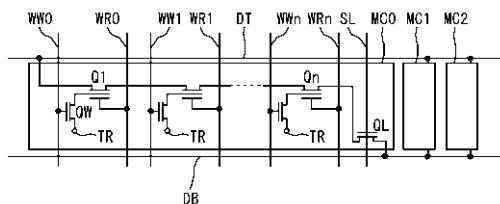

【0069】

第6の代表的実施例では図20に示したメモリを説明し、ここでは直列の2Tメモリ・セルのストレージ・トランジスタQSが直列に接続されて第1の代表的実施例で示した容量結合書き込み技術を使用する。セル構造は第3の代表的実施例で示した構造と同様であるのが望ましい。このメモリではサブカラムMC0のストレージ・トランジスタQSが次のストレージ・トランジスタのソースへ直列に接続してある一つのストレージ・トランジスタのドレインと直列の構造に接続される。さらに、各ストレージ・トランジスタQSは第2ゲートが第3実施例と同様に読み出しワード線WR0へ接続してある。書き込みトランジスタQWはストレージ・ゲートを定電圧基準ノードTRへ接続する。各サブカラムはアクセス・トランジスタQL経由で主ソース・データ線DBへ接続し、アクセス・トランジスタQLは第1のストレージ・トランジスタQSnへサブカラム直列に接続される。

10

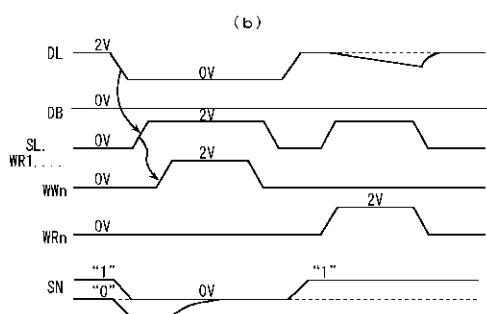

【0070】

書き込み動作について以下で説明し波形を図21aと図21bに示す。この場合、ストレージ・トランジスタQS<sub>n</sub>のストレージ・ノードNSが書き込まれると仮定する。しかし、この技術はサブカラム直列のあらゆるストレージ・トランジスタに適用できる。最初に、容量結合書き込み方法で指定された通りデータ線に電圧を提示し、データ線の低電圧をストレージ・ノードの高電圧に書き込み、データ線の高電圧をストレージ・ノードの低電圧に書き込む。サブカラムのセル全部の読み出しワード線は現在アクセスされているセルの読み出しワード線(WR<sub>n</sub>)がストレージ・ノードにかかる電圧とは関係なく関連しているストレージ・トランジスタを導通領域に入れる電圧にセットされる。さらに、サブカラムのアクセス・トランジスタQLが選択線SLによって活性化される(2V)。このようにすると、現在アクセスされているストレージ・トランジスタQS<sub>n</sub>のソース端子とドレイン端子がソース・データ線と読み出しデータ線各々の電圧とほぼ等しくなる。アクセスされているセルの書き込みワード線(WW<sub>n</sub>)を活性化してから非活性化してストレージ・ノード電圧と定電圧基準を等電位にする。この動作に続けて、ソース・データ線と読み出しデータ線をスタンバイ電圧状態に戻す。この動作はアクセスしているストレージ・トランジスタのストレージ・ノードにかかる電圧を、ストレージ・トランジスタQS<sub>n</sub>のゲート・ソース間およびゲート・ドレイン間キャパシタンスからの容量結合を介して調節する。このようにすることでデータ値をセルに保存できる。

20

【0071】

読み出し方法はアクセスされていないサブカラムにあるセルの読み出しワード線を、データが保存されているかどうかと関係なくトランジスタが導通状態になる点まで上昇させることによる。さらに、サブカラムのアクセス・トランジスタQLを活性化してサブカラムを通る電流経路を提供する。アクセスされたセルの読み出しワード線(WR<sub>n</sub>)を、ストレージ・トランジスタQS<sub>n</sub>の導通が保存されているデータに依存する電圧にセットする。ストレージ・ノードの電圧が高い場合、低電流データより大きな電流がアクセスされたトランジスタに流れる。この電流はデータ線の電圧変化を発生させ、読み出しデータ線に接続された差電圧センスアンプSAで検出することができ、アクセスしたセルに保存されている値を識別することができるようになる。

30

【0072】

本実施例で説明したメモリはオープン・データ線構造で構成され、差電圧センスアンプを使用し、第1の実施例に全て提示したリフレッシュ回路方法とダミーセル技術(またはこれに代わるデバイス)を含む。さらに、Nチャンネル・デバイスが前述した通常の動作状態で導通領域に入れない場合、ストレージ・トランジスタQSとしてNチャンネル・トランジスタをPチャンネル・トランジスタに置き換えても良い。この技術は、ストレージ・トランジスタのドレインとソースの接点を除外したことにより第6の代表的実施例の並列接続タイプより小さいセル面積を実現する。しかし、サブカラム電流経路の直列抵抗のためアクセス速度は低下する。

40

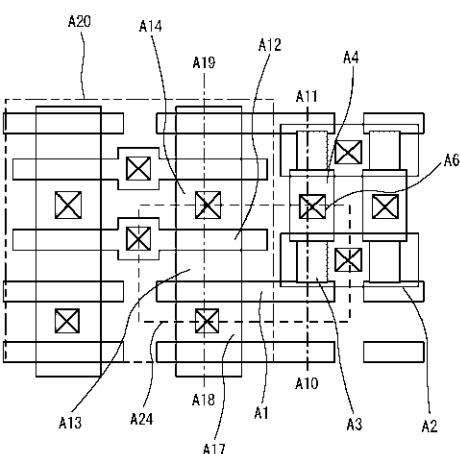

【0073】

50

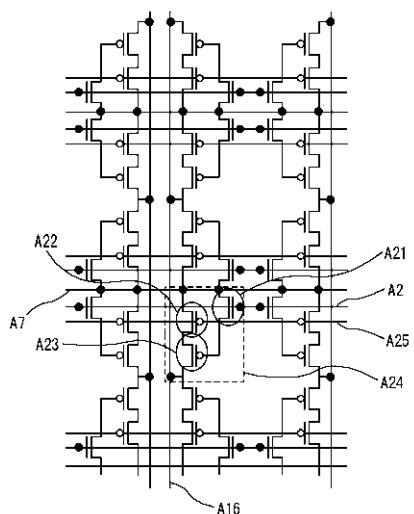

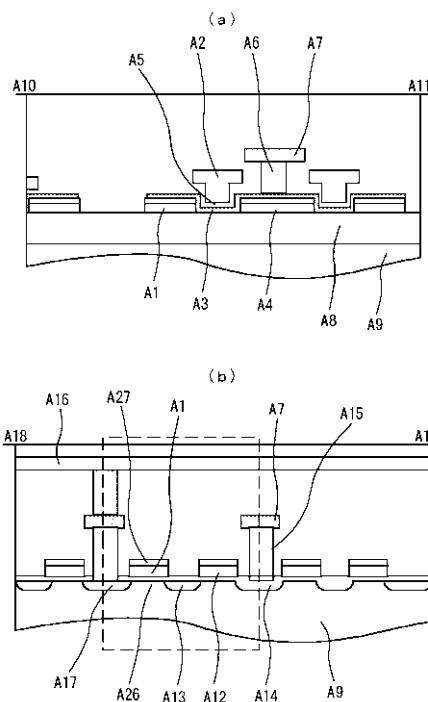

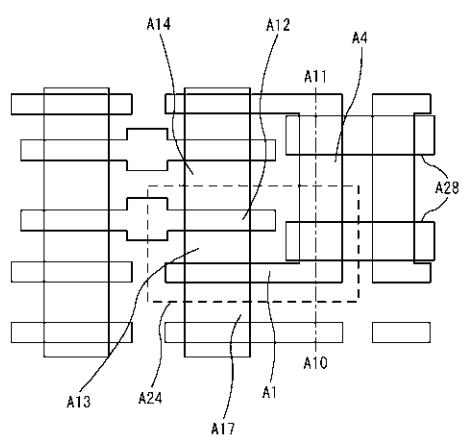

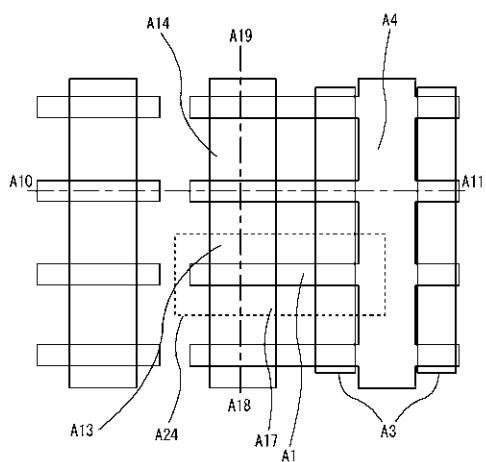

第7の代表的実施例では図22から図25に示したメモリが、第1実施例で記載した3T構造にした薄型チャンネル・トランジスタを使用できる。図22はアレイ構造の他のセルによって包囲された一つのセルA24のレイアウトを示してある。簡明にする目的で、図22にはメタル・ルーティング用のコンタクト層までの層だけを示してある。データ線A16は第2のメタル層に垂直方向に走りコモン・ソース線A7が第1のメタル層で水平方向に配置されている。図23は3×5の平衡回路アレイに構成した15個のセルを示し、ユニットセルA24が破線で画成される。図24aはA10とA11の間の断面図を示し、図24bはA18とA19の間の断面図を示す。さらに、図25に示したレイアウト・パターンは本実施例のメモリ・アレイの製造プロセスの図示を補助する目的で22の同じパターンによるマスクの縮小セットである。

10

## 【0074】

本実施例で提供されるメモリは3トランジスタ構造A21, A22, A23を含み、第1の実施例のメモリ・セルと同じ接続で構成される。このメモリの特徴は書き込みトランジスタが絶縁層A8の上に製造される点である。Nチャンネル書き込みトランジスタは150ナノメートル厚までのシリコン化合物表面にNタイプ多結晶シリコンによるソースA1とドレインA4領域を作成し2ナノメートル厚固有シリコン・チャンネル領域A3を作成するのが望ましい。P型多結晶シリコンをゲート端子A2に使用して書き込みトランジスタの閾値電圧を調節する。Nチャンネル読み出し保存トランジスタA12はP型ウェル領域内のN型拡散で形成してN型多結晶シリコン・ゲート電極を使用する。

20

## 【0075】

本実施例に示したメモリ・セルMCの特徴は薄型チャンネル多結晶シリコン・トランジスタである。従来のメモリ・セルMCでは従来型の書き込みトランジスタを使用して電荷をストレージ・ノードへ転送し、書き込みトランジスタが非活性化した後でこの電荷を維持するようにしている。しかし、トランジスタには幾つかの発生源からのリーク電流があるので、たとえばソースからドレインへの閾値下リーク電流や、ソースあるいはドレインからバルク領域への接合リークなどのため、この電荷は永久に維持されるものではない。標準的なCMOSプロセスでは、これは10の-14乗から10の-13乗アンペア程度のレベルである。数十ミリ秒のリテンション時間とするには、20~30fFの容量素子が各ストレージ・ノードで必要になる。本実施例では、薄型チャンネル多結晶シリコン・トランジスタを使用するメモリを提示する。

30

## 【0076】

通常、多結晶シリコン薄膜トランジスタは従来のトランジスタに比べて大きなリーク電流を示す。そのため、通常の多結晶シリコン・トランジスタを使用することでメモリ・セルのリテンション時間は減少する。しかし、本発明の以下の実施例に示してある薄型チャンネル・トランジスタの構造と製造ステップを使用すると、従来のバルクまたは多結晶シリコン・トランジスタよりもリーク電流が大幅に少ない薄型チャンネル・トランジスタを本発明で使用することができる。

## 【0077】

さらに詳しくは、ドレインとソース領域を接続する2ナノメートル程度の厚みでチャンネルを製造することにより、閾値下リーク電流を10の-18乗アンペアまで減少できる。さらに、このデバイスは絶縁層より上に製造されるので、接合リークがほぼ0アンペアまで減少する。本デバイスの低リーク特性は薄型ジャンクション接続とチャンネル幅による量子閉じ込め効果の結果であり、これがデバイスのバンドギャップを効果的に広げている。このメモリを拡張する一つのオプションとしては、バンドギャップの広い材料を使用してさらにリーク電流を減少させることが挙げられる。たとえば、SiGeは広いチャンネル幅でもSiと同程度のリークを実現できる。薄型チャンネル多結晶シリコン・トランジスタを使用することにより、ストレージ・キャパシタンスとして標準的トランジスタのゲート容量だけを使用しても、電荷をもっと長期間にわたって、おそらくは数分間程度、保存できる。これにより複雑なキャパシタ構造や高価な材料が必要なくなるため大幅に簡単な製造プロセスが実現される。さらに、トランジスタは利得を提供するので、トランジ

40

50

スタのゲートに電荷を保存することで大きな出力信号が得られ非破壊的読み出し動作が可能になり、読み出し動作の速度を増加できる。

【0078】

本実施例によるメモリの製造プロセスについて説明する。P型SOIシリコンウェハを使用して、犠牲酸化ステップの後、SiN層を蒸着する。フォトレジスト・パターンはP型ウェル領域として開けようとする領域に作成しSiN層をエッチングする。このステップの直後に、ホウ素イオン打込みを行ない、レジストを除去して酸化ステップを実行する。このステップでは、SiNに覆われた領域が酸化プロセスにより比較的影響を受けない。SiNを除去してから、P(燐)イオン打込みを行なう。しかし、直前の酸化ステップで覆われていた領域はこの打込みで影響されない。活性化アニーリングステップを実行して全ての酸化物を除去し、N型ウェル(A9)とP型ウェル領域を露出させる。このプロセスでは、様々な電圧を使用するためにSOIウェハを使用すると仮定しているが、N型ウェル領域内にP型ウェル領域を追加で形成しいわゆる「トリプルウェル」構造を実現してこのメモリに必要な様々な電圧レベルに対応するようにすることも容易に行なえる。

10

【0079】

素子分離領域を形成したら数回のイオン打込みステップを行なって適当なフォトレジスト・マスクによりデバイスの閾値電圧を調節し、その後でゲート酸化ステップを実行する。各種電圧レベルに対応するには、ゲート厚みを二つまたはそれ以上のレベルの一方にセットできる。本代表的実施例では、5ナノメートル厚SiO<sub>2</sub>ゲートをメモリ・セルに使用する。この酸化プロセスの後で、固有多結晶シリコン層を蒸着する。マスクド・レジストを使用するとN型トランジスタ領域がN型ドーパントで打ち込まれP型トランジスタ領域はP型ドーパントで打ち込まれる。さらに、書き込みトランジスタはN型ウェル領域の上に配置されるが、多結晶領域はN型ドーパントで打ち込まれる。レジストを除去した後、拡散と活性化アニーリング・プロセスを行なう。多結晶シリコンが硅酸化して書き込み抵抗を減少させ、ゲート領域のマスクがパターン化される。マスク・パターンA24は本実施例では使用しない方が望ましい。

20

【0080】

この時点で、書き込みトランジスタのソースA6とドレインA1の領域がN型多結晶シリコンの同じ層から構成される。レジスト・マスクは拡張領域形成用にパターン化してAsをN型トランジスタに打ち込みBF2をP型トランジスタに打ち込む。レジストを除去してから、SiO<sub>2</sub>あるいはSiNを蒸着しエッチングを行なってゲートの側壁を作成する。レジストをパターン化し、PをN型トランジスタ領域に打ち込みBF2をP型トランジスタ領域に打ち込み、これによって高濃度拡散領域を形成する。10ナノメートル厚SiO<sub>2</sub>層の蒸着後、レジスト・パターン(A28)を使い、SiO<sub>2</sub>とN型多結晶シリコン領域をエッチングする。その結果として、書き込みトランジスタのソースとドレイン領域が分離され両方の領域の側壁が露出する。レジストを除去し、ウェアを洗浄して2ナノメートル厚のアモルファス・シリコン層を蒸着する。さらに5ナノメートル厚のSiO<sub>2</sub>層を蒸着した後、書き込みトランジスタのチャンネル領域を保護するためのレジスト・パターンを形成してSiO<sub>2</sub>層をHF湿潤エッチングする。レジスト層を除去しウェハをO<sub>2</sub>プラズマで酸化し弱い酸化プロセスを確保する。残っている5ナノメートル厚SiO<sub>2</sub>層はこのプロセスで比較的影響を受けにくい。その結果、書き込みトランジスタのチャンネル領域が形成される。さらに5ナノメートル厚のSiO<sub>2</sub>層を蒸着してからN型多結晶シリコンのドーピング層を蒸着する。この層をパターン化してからエッチングし、書き込みトランジスタのゲート領域を形成する。最後に絶縁層を蒸着して、これ以後のコンタクト層と相互接続層を製造するようにする。

30

【0081】

第8代表的実施例では第7実施例で定義し、また同図22から図25で定義したような3トランジスタ型メモリ・セルを使用するメモリができる。トランジスタとアレイは第1実施例のメモリ・セルと同じ接続関係に構成される。このメモリのユニークな特徴は、書き込みトランジスタA21が第7実施例で説明したNチャンネル薄型チャンネル・トランジ

40

50

スタでありストレージ・トランジスタ A 2 3 と読み出しトランジスタ A 2 2 が P チャンネル・トランジスタである。 P チャンネル読み出し及び保存トランジスタ A 1 2 は N 型ウェル領域の P 型拡散層に形成され P 型多結晶シリコン・ゲート電極を使用している。

#### 【 0 0 8 2 】

第 1 実施例を参照して上記で説明したように、書き込みトランジスタ A 2 1 とストレージ・トランジスタ A 2 3 に逆のタイプのトランジスタを使用することにより、メモリの動作マージンを増加できる。このメモリが書き込みトランジスタとして薄型チャンネル多結晶シリコン・トランジスタを使用していることと、閾値下リーク電流を制限する同じ効果により、書き込みサイクルの「 ON 」電流も制限される。したがって、典型的な N チャンネル・トランジスタが P チャンネル・トランジスタより高い易動度を有していることから N チャンネル・デバイスを選択することにより書き込みプロセスを高速化する。そのため、ストレージ・トランジスタは上記で説明したようにできる限り広い電圧マージンが得られるように P チャンネル・デバイスとして選択する。他方で、メモリ・セルに書き込まれる前のデータを格納するメモリ・バッファを含めることができるために、遅いメモリ・セルへの書き込み動作はメモリのパフォーマンスに影響しない。しかし、メモリ読み出しアクセスサイクルは同じ方法で遅延させることができない。この理由から、読み出しプロセスが遅すぎるような場合、 N チャンネル・ストレージ・トランジスタと P チャンネル書き込みトランジスタを使用できる。

#### 【 0 0 8 3 】

N チャンネル・トランジスタについて N 型ゲート電極を使用し P チャンネル・トランジスタについては P 型ゲート電極を使用するのが普通である。したがって、本実施例で使用するメモリ・セルでは、ストレージ・トランジスタの P 型ゲートは書き込みトランジスタの N 型ソースまたはドレイン領域として直接使用することができない。しかし、本実施例では、同じ多結晶シリコン体をストレージ・トランジスタのゲートと書き込みトランジスタのドレインまたはソースに使用できるような方法を提案する。マスキング・パターン A 2 0 は P チャンネル・トランジスタの活性領域を含むプロセスに含まれる。このマスキングを使用して、読み出しトランジスタとストレージ・トランジスタのゲート電極を形成する予定の領域に P 型ドーパント（すなわち B F 2 ）を打ち込む。このマスクの反転を用いることで書き込みトランジスタのソース及びドレイン領域を形成する予定の領域に N 型ドーパント（すなわち A s ）を打ち込む。従来の例では、 P N 接合領域がこの操作によって形成されるため、この製造方法は一般に回避されている。しかし、多結晶シリコン表面を硅酸化することにより、金属化接続が N 型と P 型領域の間に形成され、接合効果を無視することができる。

#### 【 0 0 8 4 】

別の方法は N 型と P 型の多結晶シリコン部分を物理的に分離してから金属相互接続層へのコンタクトを介してこの二つを接続することである。単一の多結晶シリコン接続を使用する利点は、相互接続層を用いて別々の部分を接合するのに対してメモリ・セルの面積を減少できることである。さらに、 N 型と P 型領域でドーピングする不純物濃度が充分に高ければ、接合効果を無視できる。実際に、高い不純物濃度では、接合領域が減少しトンネル電流が N 型と P 型領域の間に流れる。この現象が起るためには、両方の領域で 10 の 2 0 乗のドーピング濃度が望ましい。別の重要な作用は、ストレージ・トランジスタのゲート領域が充分に高い電圧まで上昇した場合、 P N 接合が前向きバイアスされ、接合に起因する抵抗を減少する。他方、この接合抵抗はストレージ・ノードのリーク率をさらに減少させるので、データの保持時間をさらに長くすることができる。

#### 【 0 0 8 5 】

本実施例によるメモリの製造プロセスは第 7 の代表的実施例に示した。相違点は、マスク層 A 2 4 を追加して P 型ドーパントによる多結晶シリコンのドーピングを、 P 型デバイスのゲートとして機能する領域で行ない、 N 型ドーパントによるドーピングを、前述のように多結晶シリコンデバイスのドレイン及びソース領域として用いる領域で行なうことである。このステップは多結晶シリコン層を蒸着した後で行なう。硅酸化ステップを含めるこ

10

20

30

40

50

とで前述のように多結晶シリコンの抵抗を減少する。

【0086】

本実施例に示したメモリも第1の代表的実施例により構成し活性化することができる。要するに、このメモリはオープン・データ線構造に製造でき、差電圧センスアンプSAを使用して信号を弁別し、ダミーセルを使用して基準信号を生成し、第1の実施例にしたがつてデータを読み出し、反転させ、アクセスしたデータセルへ書き戻すリフレッシュ動作を使用することができる。

【0087】

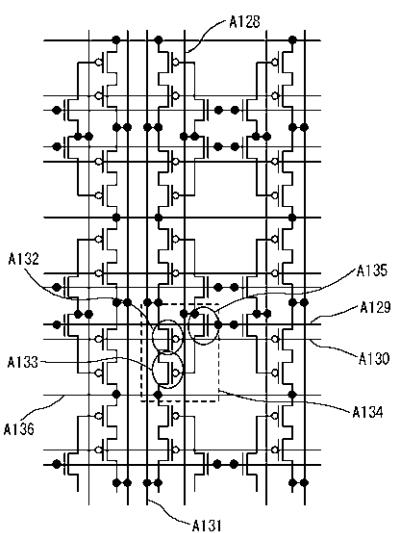

第9の代表的実施例は第7の代表的実施例で従来の3Tメモリ・セル構造で説明した薄型チャンネル・トランジスタを使用するメモリを説明する。このセルの模式図が図26に示してあり、ユニットセルA134は一方のノードがソース線A136に接続してあるストレージ・トランジスタA133と、読み出しデータ線A131とストレージ・トランジスタA133に接続してある読み出しへトランジスタA132と、書き込みデータ線A128をストレージ・トランジスタのゲートに接続する書き込みトランジスタA135とを含み、相違点は書き込みトランジスタが深さ5ナノメートル未満またはこれに等しい薄型チャンネル領域を持っていることである。このメモリ構造とすでに説明した第7の代表的実施例において維持されるメモリ構造との相違点は、ストレージ・ノードへ接続されていない薄型チャンネル書き込みトランジスタのドレインが読み出しへトランジスタのソースとは逆に独立した書き込みデータ線A128へ接続されることである。このメモリは薄型チャンネル・トランジスタを書き込み素子として使用していることで従来の3Tセルとはことなり、第7の代表的実施例で説明した標準的書き込みトランジスタより大幅に長いリテンション時間が可能である。

【0088】

本実施例のメモリでの読み書きアクセス方法は第1の代表的実施例で説明した従来の3Tセル構造のそれで図6aと図6bの波形プロットに図示したものである。図6bで書き込み期間中に高電圧を書き込むには、書き込みデータ線を供給電圧Vddに充電する。供給電圧Vddの最大電圧レベルをストレージ・ノードに伝送するためには、ブースト電圧をVdd+Vtの書き込みワード線に提示する。書き込みトランジスタはこれで活性化され、電荷を輸送してストレージ・ノード電圧と書き込みデータ線を等電位にする。高電圧がストレージ・ノードにセットされた後、書き込みワード線を非活性化し、メモリ・セルMCは供給電圧Vddでスタンバイ状態になる。図6aの書き込み期間中に低電圧をストレージ・ノードへ保存するには、書き込みデータ線を0Vに荷電する。書き込みトランジスタはブースト電圧書き込みワード線により活性化する。書き込みトランジスタが非活性化した後、デバイスは0Vの保存電圧でスタンバイ状態になる。

【0089】

読み出しサイクルは第2の代表的実施例のメモリ・セルと同じ手順にしたがい、読み出しへトランジスタが読み出しワード線により活性化され電流がメモリ・セルに流れる。ストレージ・ノードにかかる電圧でNチャンネルストレージ・トランジスタの導通状態が変化し、高値状態ではデータ線DL電圧の高速な低下が起こる。読み出し状態はメモリ・セルのデータの値を判定するのに充分な電圧変化がデータ線DLに発生して読み出しへトランジスタが非活性化されたときに終了する。

【0090】

本実施例に示したメモリは第1の代表的実施例にて説明したようなオープン・データ線構造、差電圧センスアンプSA、ダミーセル方式を使用するのが望ましい。本実施例のリフレッシュ方法は第1の代表的実施例のそれとはことなり、書き込み動作の後でストレージ・ノードにかかる電圧が書き込み動作の間のデータ線DLにかかる電圧に直接比例する。したがつて、増幅器出力を反転するための反転回路が必要になる。この信号は入力データバッファに入力され書き込み動作が行なわれてアクセスシタセルのデータを完全にリフレッシュする。

【0091】

10

20

30

40

50

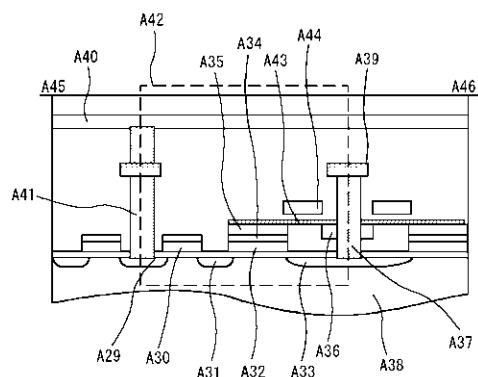

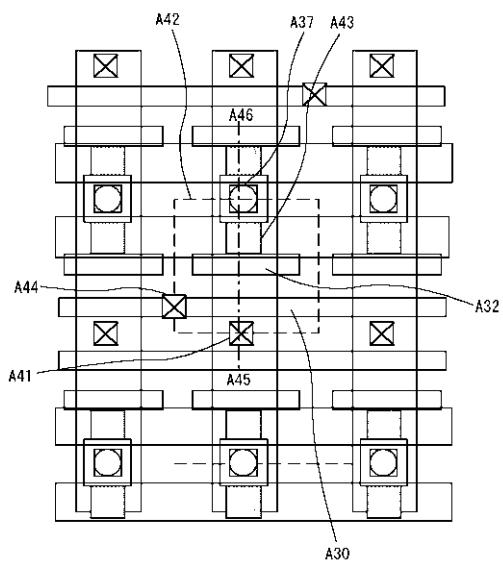

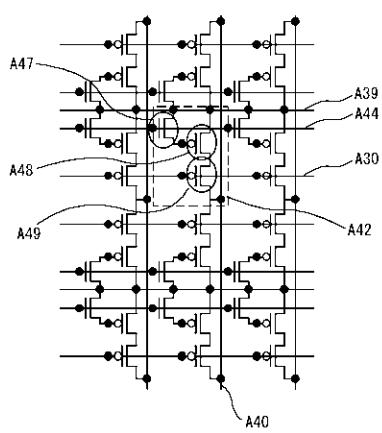

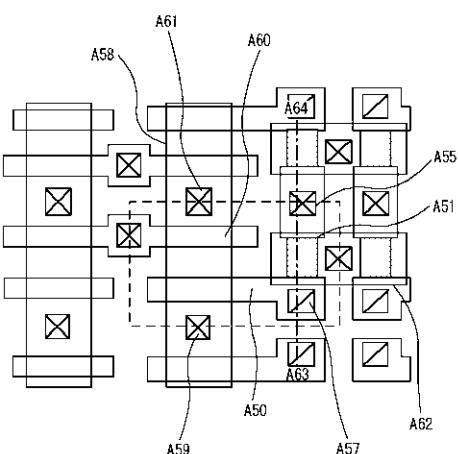

第10の代表的実施例では図27から図29に詳細に示したようなメモリが可能になりこれは第1の代表的実施例による3トランジスタ構造に構成される。図28はユニットセルのレイアウト(A42)を示し、周辺セルはアレイ構造になっている。全部で9個のセルが3×3の構成で、周辺セルの隣接した部分と一緒に示してある。簡明にするため、相互接続層からのパターンは無視してある。図29は破線で示したユニットセル(A42)による3×4平衡セルアレイのレイアウトを示す。図27は図28の点A45とA46の間の断面を示す。

#### 【0092】

本実施例で提供されるメモリはN型多結晶シリコン書き込みトランジスタA47とP型ストレージ・トランジスタA48を前述の実施例と同様に含む。しかし、ストレージ・トランジスタA48と読み出しトランジスタA49の位置的な関係は本実施例で変更されてストレージ・トランジスタA48の直下にP型多結晶シリコン、金属、N型多結晶シリコンの垂直積層構造が形成されてセル面積を減少するようにしてある。ストレージ・トランジスタのゲートとこれより上にある多結晶シリコン層との間の接続を行なうためには、金属層をP型多結晶シリコン・ゲートの直上に蒸着し、続けてこの上のN型層との直接接続を行なう。別の方針としては金属蒸着の代わりに硅酸化プロセスを使用することが挙げられる。

#### 【0093】

本実施例のメモリについて一つの代表的な製造プロセスは第7の代表的実施例のそれから派生したもので、相違点だけを説明する。最初に、SOIウエハの上に第7の代表的実施例で説明したようにトランジスタを作成し、絶縁層を蒸着する。このステップに続けて、プレーナ化処理でPチャンネル・デバイスのゲート領域の上部表面を露出させる。製造プロセスが第7の代表的実施例のそれによるものであれば、N型ウェル領域はP型ウェル領域より高いのでNMOSSデバイスのゲートは露出しない。N型多結晶シリコンを蒸着後、書き込みトランジスタのソース領域A35とドレイン領域A36をパターン化してエッチングする。次に、絶縁層を蒸着し、N型多結晶シリコンの上部表面を露出させるプレーナ化ステップを行なう。

#### 【0094】

この時点では、3ナノメートル厚のアモルファス・シリコン層と5ナノメートル厚のSiO<sub>2</sub>層が蒸着されパターン化され、エッチングされて書き込みトランジスタのチャンネルA43を形成するのが望ましい。5ナノメートル厚のSiO<sub>2</sub>層を蒸着してからN型多結晶シリコンの層と書き込みトランジスタ層を蒸着する。これをパターン化してエッチングし書き込みトランジスタのゲート領域と書き込みトランジスタワード線A44を形成する。特徴は書き込みトランジスタのソース領域A36に侵入するコンタクトA37を使用している点である。このようにすると、書き込みトランジスタのソース領域A36とストレージ・トランジスタのソース領域A33がソース線A39へ同時に電気的に接続される。

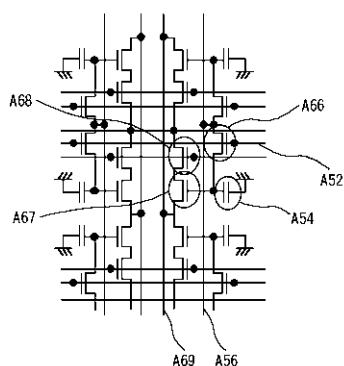

#### 【0095】

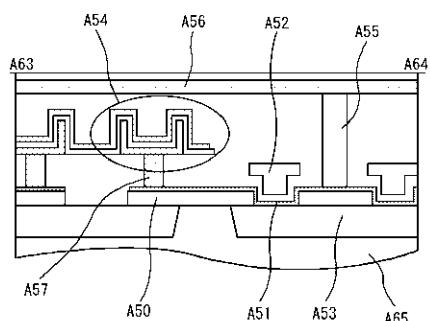

第11の代表的実施例は図30から図32に示してあるように第1の代表的実施例による3トランジスタ構造のメモリ・セルを有するメモリを提供する。相違点はさらにストレージ・ノードA50にストレージ・ノードへ接続されたキャパシタス構造A54を使用していることで、大容量の保存電荷が可能になり、非常に長いリテンション時間のメモリができる。図32の構造は独立した書き込みデータ線A56と読み出しデータ線A69を示しているが、これらは1本のデータ線DLに統合してセル面積を減少することができる。さらに、ストレージ・トランジスタA67のゲートA50はTa<sub>2</sub>O<sub>5</sub>を用いて形成した容量素子A54の一方の端子に接続される。キャパシタの他方の端子は設置ノードへ直接接続される。

#### 【0096】

第1の代表的実施例のメモリ・セルでは、ストレージ・ノードで想定されるキャパシタスが0.2fFである。しかし、Ta<sub>2</sub>O<sub>5</sub>容量構造A54を使用すると、20fFのストレージ・キャパシタスを実現できる。さらに、書き込みトランジスタA66のチャン

10

20

30

40

50

ネル領域 A 5 1 の厚みがおよそ 1 . 5 ナノメートルに減少し、1 0 の - 2 1 乗アンペアのリーク電流がある種の温度条件下で示される。この構造では、1 0 % の保存電荷を減少するのに 1 か月かかると予想される。これによりポータブル用途たとえばリフレッシュ期間を必要としない携帯電話用メモリ・デバイスなどに適したメモリ・デバイスが可能になり、実質的に不揮発性メモリ・デバイスが可能になる。

【 0 0 9 7 】

充分に情報を保持するには、書き込みトランジスタ A 6 6 のゲート領域 A 5 2 とソース領域 A 5 3 の電圧を適当に固定する必要がある。従来の S R A M と比較した場合、本実施例で説明しているメモリはトランジスタ数の減少により小さいセル面積を実現できる。さらに、1 V まで電圧が低くても動作できると予想されるので従来のフラッシュ・メモリや同様なメモリ・デバイスと比べて安価な不揮発性メモリが得られる。およそ 1 0 ナノメートル厚のトンネリング酸化層を高電圧トランジスタと一緒に使用した場合、電圧ブースト回路は不要である。さらに、フラッシュ・メモリやその他の不揮発性メモリ・デバイスとは異なり、実行できる書き込み動作回数に制限がない。

【 0 0 9 8 】

本実施例に示した半不揮発性メモリでは、リフレッシュ動作はバッテリを再充電または交換する際に実行できる。追加のキャパシタ・デバイスが必要なことから、製造プロセスは先行実施例より多くのステップを含むことになる。しかし、このメモリは D R A M 及び論理回路と容易に統合して不揮発性メモリ・ユニットを備える完全なシステムを形成できる。さらに、多くのアナログ及びデジタル回路プロセスがすでに追加のキャパシタ素子を内蔵しているので、このメモリはわずかな追加ステップで製造可能である。このメモリは本発明の他の実施例によるメモリ技術と組み合わせて同一のダイに製造できる。最後に、本実施例では縦型積層キャパシタをストレージ素子として説明するが、このメモリは余分な面積を使う代償にシリコン基板上に作り込んだトレンチ型キャパシタに置き換えることができる。

【 0 0 9 9 】

本実施例に提示するメモリは長いリテンション時間を実現する高抵抗書き込みトランジスタを含むが、書き込み時間は 1 の - 6 乗秒程度であると考えられる。本デバイスは従来型トランジスタをストレージ・デバイス及び読み出しデバイスとして使用しているため高速な読み出し速度を示すことになる。

【 0 1 0 0 】

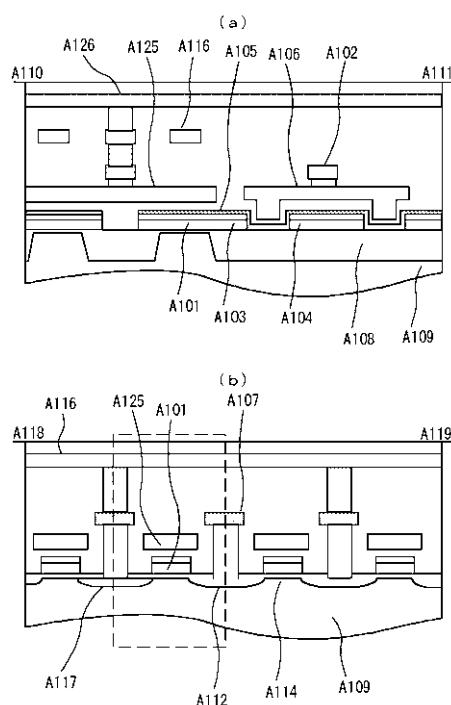

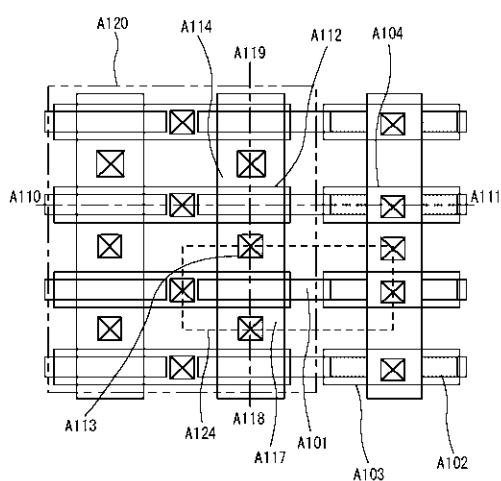

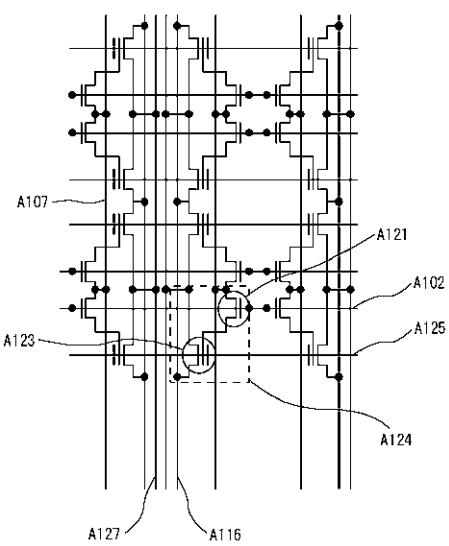

第 1 2 の代表的実施例は図 3 3 から図 3 6 に示してあるメモリを説明し、これは第 3 の代表的実施例で説明した 2 T 構造の薄型チャンネル・トランジスタを使用する。本メモリでは、図 3 5 に示してあるように、書き込みトランジスタ A 1 2 1 が第 7 の代表的実施例で説明したような薄型チャンネル・トランジスタから形成される。図 3 4 は本メモリのユニットセル A 2 4 について周辺セルと 4 × 3 構成にしたレイアウトを示す。メタル相互接続層は説明を簡明にするため省略した。図 3 6 はトランジスタと第 1 の多結晶シリコン層だけのレイアウトを示す。点 A 1 1 0 と A 1 1 1 の間ならびに A 1 1 8 と A 1 1 9 の間の断面図が図 3 3 に示してある。ストレージ・トランジスタ A 1 2 3 は従来の N チャンネル・バルク・トランジスタで形成する。書き込みワード線 A 1 0 2 と読み出しワード線 A 1 2 5 は第 3 の金属相互接続層に形成し水平方向に走行する。データ線 A 1 1 6 は第 2 の金属相互接続層に形成し垂直方向に走行する。ソース線 A 1 0 7 は第 1 の金属相互接続層に形成して水平方向に走行する。

【 0 1 0 1 】

代表的な製造プロセスは第 7 の代表的実施例のメモリで示したフローにしたがうもので、相違点だけを説明する。このフローは薄型チャンネル書き込みトランジスタのゲート A 1 0 4 を形成する多結晶シリコン層が蒸着される点までは同じである。処理ステップを節約するため、この層にはストレージ・トランジスタ A 1 2 3 の第 2 ゲート A 1 1 2 も一緒にパターン化するのが望ましい。この多結晶シリコン層をエッチングしてレジストを除去したら、適当なコンタクト層及び金属層をこれらのデバイスの上に製造する。

10

20

30

40

50

## 【0102】

本メモリの動作およびアレイ方式は第3の代表的実施例に示したメモリと同一で、ストレージ・ノードヘデータを保存するのに、容量結合書き込み方法を使用し、これについてはここでは説明しない。本メモリは揮発性メモリとして幾つかの利点を有している。一つのメモリ・セルで二つのトランジスタしか使用しない点で、これらの一方は絶縁層の上に製造した薄型チャンネル・トランジスタであり、従来のDRAMセルと同程度までの小ささの非常に小さいセル寸法を実現できる。このようにすると、非常に高密度なメモリを実現できる。同様に、第7の代表的実施例で説明したように、薄型チャンネル・トランジスタは従来のトランジスタよりリーク電流が大幅に小さい。したがって、ストレージ素子としてトランジスタのゲート端子だけを使用するセルで長いリテンション時間を実現可能である。これはさらに所定時間でのリフレッシュ動作を減らすことになり低電力メモリ・ユニットが得られる。

10

## 【0103】

第13の代表的実施例は第12の代表的実施例（図33から図36）の図面で示すことができるメモリを実現し第7の代表的実施例に示したような薄型チャンネル・トランジスタを含む2トランジスタ・セル構造のメモリを説明する。この構造との相違点は、Nチャンネル型デバイスの代わりにストレージ・トランジスタとしてPチャンネル・トランジスタを使用している点にある。この場合、薄型チャンネル書き込みトランジスタはNチャンネル・デバイスとしてPチャンネル・デバイスより高い電子易動性による書き込み動作の速度を向上させる。Pチャンネル・ストレージ・トランジスタを使用する利点については第1の代表的実施例で説明しているのでここでは説明しない。

20

## 【0104】

製造手順は第8実施例に示した手順と第12実施例に示した手順の組み合わせである。すなわち、薄型チャンネル・トランジスタのゲート端子として使用する多結晶シリコン層の蒸着までは第8実施例の手順にしたがう。Pチャンネル・ストレージ・トランジスタはP型多結晶シリコン・ゲートを有しNチャンネル薄型チャンネル・デバイスはN型多結晶シリコンのソースとドレイン領域を有しているので第8実施例と同様の追加のマスクA120と硅酸化ステップを含める必要があることには言及する必要がある。第8実施例と同様に、このマスク内の多結晶シリコンはP型ドーパントを打ち込みマスクの外側の多結晶シリコンにはN型ドーパントを打ち込む。つまり、同じ多結晶シリコン部分をP型ストレージ・トランジスタのゲートとN型薄型チャンネル書き込みトランジスタのソースまたはドレインの両方に使用できる。このマスク及び硅酸化ステップによりストレージ・トランジスタのゲートと書き込みトランジスタのソースを一つの多結晶シリコン部分から製造できるようになる。これはコンパクトなセル面積を実現する上で有利である。第12実施例と同様に、ストレージ・トランジスタの第2ゲートは薄型チャンネル書き込みトランジスタのゲートに用いているのと同じ多結晶シリコン蒸着層から形成される。

30

## 【0105】

アレイ構造、センスアンプ、ダミーセル、リフレッシュ方法は全て第3実施例にしたがって実装できるのでここでは説明しない。このメモリ・セルの利点としては、2トランジスタ・セル構造による小さなセル寸法とNチャンネルストレージ・トランジスタが充分でないある種の条件下での高電圧マージンである。

40

## 【0106】

第14の代表的実施例では、第12実施例の図面（図33から図36）に示すことができるメモリが実現され第7実施例に示したような薄型チャンネル・トランジスタを含む2トランジスタ・セル構造を説明する。このメモリは第5実施例に示した並列接続メモリ・セル構造のそれと同様の方法で構成する。レイアウト図は図34と図36に示してあり点A110とA111ならびにA118とA119の間の断面図が図33に示してある。模式図が図35に図示してある。

## 【0107】

第12実施例のレイアウト及び製造に対して本メモリのそれの相違点は、セルが第5実施

50

例で説明したような一連のサブカラム・ブロックに構成される点である。サブカラム・ブロック内の各セルはストレージ・トランジスタを含み、ドレイン領域が読み出しだータ線 A 1 1 6 に接続され、ソース領域がサブカラムのソース・データ線 A 1 2 7 に接続される。サブカラム・ソース・データ線はさらに図 1 8 に示してあるようなサブカラム・アクセス・トランジスタ Q S L のドレイン端子に接続される。このようにすると、一つのサブカラムだけが第 5 実施例で説明したような読み出し動作で電流に寄与する。つまり、本メモリは第 1 2 実施例で実現される小さい面積をアクセス・トランジスタ面積文のわずかなペナルティで実現するが、サブカラム内で選択されていないセルだけが読み出し動作中の電流雑音に関係することから高速な読み出し動作を示す。

#### 【 0 1 0 8 】

10

プロセスは第 1 2 実施例のそれと同一であるからここでは繰り返し説明しない。さらに、メモリ・アレイ構造、検出メカニズム、ダミーセルの概念、リフレッシュ動作は第 5 実施例にしたがって使用し、容量結合書き込み方法を使用する。先行実施例に示したメモリに対して幾つかの変更を行なうことができる。たとえば、P チャンネル・ストレージ・トランジスタを N チャンネル・デバイスの代わりに使用できる。利点と製造プロセスの変化は第 1 3 実施例に示してありここでは説明しない。

#### 【 0 1 0 9 】

20

第 1 5 の好適実施例では第 1 2 実施例の図面（図 3 3 から図 3 6 ）に示すことができるメモリを実現し、第 7 実施例に示した薄型チャンネル・トランジスタを含む 2 トランジスタ・セル構造メモリを説明する。さらに、本メモリは第 6 実施例で説明した直列接続メモリ・セル構造のそれと同様の方法で構成される。レイアウト図は図 3 4 と図 3 6 に示してあり点 A 1 1 0 と A 1 1 1 ならびに A 1 1 8 と A 1 1 9 の間の断面図が図 3 3 に示してある。模式図が図 3 5 に図示してある。

#### 【 0 1 1 0 】

30

第 1 2 実施例のレイアウト及び製造に対する本メモリのレイアウト及び製造における相違点は、第 6 実施例で説明した一連のサブカラム・ブロックにセルが構成される点である。要するに、各メモリ・セルのストレージ・トランジスタ Q S は隣接するメモリ・セルのストレージ・トランジスタと直列に接続される。このサブカラム列の一端にあるストレージ・トランジスタ Q 1 はデータ線 D L に接続され他端にあるストレージ・トランジスタ Q n はサブカラム・アクセス・トランジスタ Q S L に接続され、これがさらにソース・データ線 D L 0 へ接続される。読み書きアクセス方法は第 6 実施例で説明した容量結合書き込み方法にしたがう。本実施例と第 6 実施例での違いは第 7 実施例に説明した様な薄型チャンネル書き込みトランジスタを含めることである。このデバイスをストレージ・ノード・アクセス・トランジスタとして含めることにより、低い閾値下電流リークのため従来のトランジスタに比べ 1 0 0 0 倍リテンション時間を延ばすことができる。

#### 【 0 1 1 1 】

40

本実施例によるメモリではオープン・データ線構造、差電圧センスアンプ、ダミーセルの概念、リフレッシュ方法は第 6 実施例に示したものを使用しここでは繰り返し説明しない。さらに、製造プロセスのフローは第 1 4 実施例で説明しておりここでは繰り返さない。本メモリは、少なくとも第 1 実施例で説明した理由から P チャンネル・ストレージ・トランジスタを N チャンネル・デバイスの代わりに使用することができ、そのための製造プロセス方法は第 8 実施例で説明してある。本デバイスの利点としては直列接続ストレージ・トランジスタでのドレインとソースのコンタクトがないことによる従来の D R A M より小さなセル寸法である。さらに、従来の D R A M より大幅に長いリテンション時間を示すことができる。

#### 【 0 1 1 2 】

50

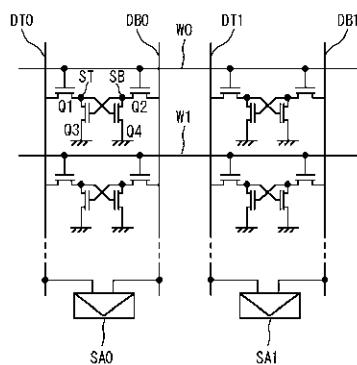

第 1 6 の代表的実施例は図 3 7 に示したようなメモリを提供し、各セルが標準的な 4 T の S R A M 構造で 4 個のトランジスタを含むようにする。さらに、セル内のトランジスタは、トランジスタをゲート端子に接続したワード線 W 0 から活性化したときに一方のバス・トランジスタ Q 1 がプラスのデータ線 D T 0 とプラスのストレージ・ノード N T へ電気的

に接続するように構成する。他方のバス・トランジスタQ2はゲート端子へ接続された同じワード線W0から活性化されたときにマイナスのデータ線DB0とマイナスのストレージ・ノードNBへ電気的に接続する。ストレージ・トランジスタQ3はソース領域が接地ノードへ接続され、ドレイン領域がプラスのストレージ・ノードNTへ、ゲート電極がマイナスのストレージ・ノードNBへ接続してある。最後に、ストレージ・トランジスタQ4は、ソース領域が接地ノードへ接続してあり、ドレイン領域はマイナスのストレージ・ノードNBへ接続してあり、ゲート電極はプラスのストレージ・ノードNTへ接続してある。

#### 【0113】

本実施例のメモリの相違点はストレージ・トランジスタQ3, Q4が第7実施例で説明した薄型チャンネル多結晶シリコン・トランジスタによって実現される点である。この構造を使用することには幾つかの利点がある。後述するように、このメモリはリフレッシュ期間で動作するスタティック型メモリである。そのため、リフレッシュ動作に関係する電力消費を無視できる。第7実施例で説明したように薄型チャンネル・ストレージ・トランジスタは絶縁層の上に製造されるので、従来のSRAMセルに比べて3分の1まで小さいセル寸法を実現できる。さらに、薄型チャンネル・ストレージ・トランジスタはリーク電流の大きさが従来のトランジスタより4桁まで小さいので、このメモリ・セルはスタンバイ状態で従来のSRAMに比べ大幅に低い電力しか消費しない。

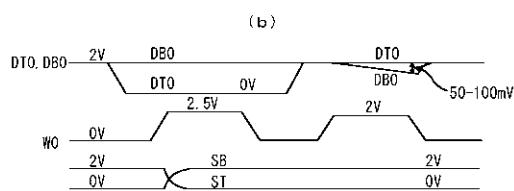

#### 【0114】

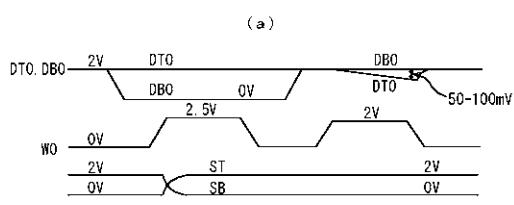

代表的なアクセス動作について説明する。この動作はNチャンネル・パストランジスタQ1, Q2に適用されるが、このメモリはパストランジスタがPチャンネル型である場合も同じ方法で機能する。この場合、ワード線W0の極性を反転させる。図38aと図38bの波形図に示してあるように、スタンバイ状態で、ワード線W0を低値に保持し、データ線DLをストレージ・ノードから絶縁する。高値がセルに保存されている場合高電圧(2V)がプラスのストレージ・ノードNTに保存され、低電圧(0V)がマイナスのストレージ・ノードNBに保存される。プラスのノードにかかる高電圧でストレージ・トランジスタQ3が活性化し、効果的にマイナスのストレージ・ノードNBを低電圧(0V)に保持する。

#### 【0115】

動作の重要な点は高電圧のプラス側ノードである。この場合、ノードを復帰するメカニズムがプラスのデータ線DT0からのリーク電流である。プラスのデータ線DT0からストレージ・ノードNTへパストランジスタQ1を通るリーク電流がプラスのストレージ・ノードNTからストレージ・トランジスタQ3を通りウェルへ流れる充電リークより高い場合には、ノードは自己復帰する。言い換えれば、高電圧のプラスのストレージ・ノードNTからの充電リークがある場合、ノードがデータ線と等電圧になるまで電荷がプラスのデータ線DT0から流れる。同じ言い方で、プラスのストレージ・ノードにかかる低電圧値の場合には、逆のことが言える。マイナスのストレージ・ノードNBはマイナスのデータ線DB0からのリーク電流により高電圧に維持される。薄型チャンネル・トランジスタは従来のトランジスタより大幅に低いリーク電流を示すので、この関連性が保持されることになり、低リーク、小面積スタティック・メモリ・セルを実現できる。

#### 【0116】

読み書きアクセスは従来のSRAM回路と同一で、高値データが図38aに示したように書き込まれ低値データは図38bに示したように書き込まれるので、ここでは詳細に説明しない。要約すると、高値書き込みサイクルでは、高電圧(2V)がプラスのデータ線DT0に現われ低電圧(0V)がマイナスのデータ線DB0に現われる。ワード線W0は活性化され、ストレージ・ノードNT, NBへデータ線上的電圧を転送する。ワード線を低値にした後、データ線は高電圧スタンバイ状態に戻り(2V)、データは前述したように静的に保持される。読み出し動作はプラスのデータ線DT0、マイナスのデータ線DB0を浮動させパストランジスタを活性化することを含む。電流経路はデータ線からセルを通る経路を形成し差電圧がデータ線に発生する。この差分信号をセンスアンプSA0で識別

10

20

30

40

50

しデータをシステムバスに出力する。薄型チャンネル・トランジスタの製造技術については第18実施例でさらに詳細に説明する。

【0117】

第17の代表的実施例は図39に示したようなメモリを提供し、各セルが6個のトランジスタを含み、そのうち4個は第16実施例で説明したような標準の4トランジスタ構造とし、残り2個のトランジスタはセルデータの高速読み出しを可能にするような方法で構成する。パストランジスタQ1, Q2は書き込みデータ線S<sub>T</sub>0, S<sub>B</sub>0に接続され薄型チャンネル・ストレージ・トランジスタQ3, Q4はデータ値がストレージ・ノードN<sub>T</sub>、N<sub>B</sub>に静的に保持されるように構成する。第16実施例では、電流バスが薄型チャンネル・ストレージ・トランジスタを通っているので、読み出し動作は従来のSRAMより大幅に遅い。このため、2個のトランジスタを追加して読み出し動作の速度を向上させる。読み出しトランジスタQ5はソース領域を接地(0V)へ接続しゲート電極をマイナスのストレージ・ノードN<sub>B</sub>へ接続する。アクセス・トランジスタQ6はソース領域をトランジスタQ5のドレイン領域へ接続し、ゲート端子をワード線W<sub>0</sub>へ接続し、ドレイン領域を読み出しデータ線D<sub>0</sub>へ接続する。

10

【0118】

アクセス動作は第16実施例の動作と同様であり、相違点だけを説明する。図40aは高値データのアクセス動作、図40bは低値データのアクセス動作を示す。書き込み動作は書き込みデータ線S<sub>T</sub>0, S<sub>T</sub>1に現われる対向した極性の電圧による同様なパターンにしたがい、高電圧(2V)が高値書き込み動作でプラスの書き込みデータ線に現われ低電圧(0V)が低値書き込み動作でプラスの書き込みデータ線に現われるのは第16実施例で説明したのと同様である。読み出し動作では、ワード線は第16実施例と同様に高電圧(2V)に昇圧される。相違点は、書き込みデータ線にかかる電圧ではなく読み出しデータ線D<sub>0</sub>にかかる電圧が検出されることである。マイナスのストレージ・ノードN<sub>B</sub>は読み出しトランジスタQ6のゲートに接続してあるので、トランジスタはマイナスのストレージ・ノードN<sub>B</sub>が保存高電圧(2V)になっているとき導通状態にあり、マイナスのストレージ・ノードN<sub>B</sub>が低値保存電圧(0V)になっているときシャットオフ状態になる。読み出しデータ線からアクセス及び読み出しトランジスタを通る電流経路が存在するので、読み出しデータ線にかかる電圧はマイナスのストレージ・ノードN<sub>B</sub>にかかる電圧で決定される率で低下する。この電圧が読み出しデータ線に接続されたセンスアンプで検出でき、メモリ・セルの内容を表わすデジタル信号を生成して信号バスへ出力することができる。読み出し及びアクセス・トランジスタは従来のタイプであるから、大きな電流を生成でき、第16実施例で実現できる以上に高速な読み出し動作が得られる。欠点は追加のデータ線と追加のトランジスタによる追加面積である。しかし、メモリ・セルは標準的なSRAMより大幅にリーク電流が小さいので、電力消費を減少させることができる。

20

30

30

【0119】

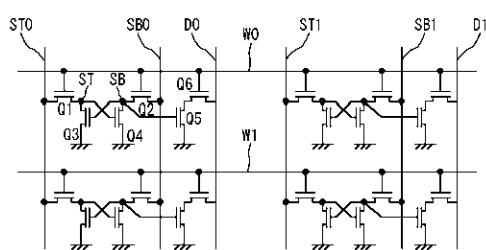

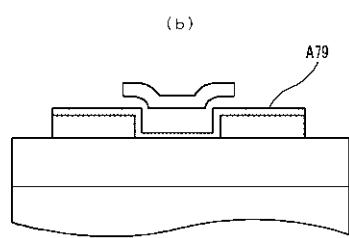

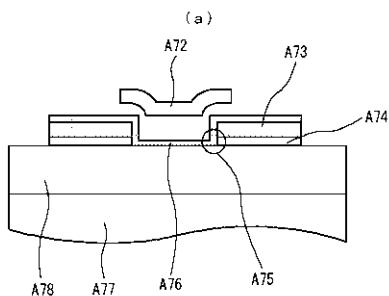

第18の代表的実施例を図41から図44に示す。本実施例では、先行の実施例で使用した薄型チャンネル書き込みトランジスタが示してある。本デバイスの低リーク特性により、ダイナミック・メモリ構造にこれを組み込むことで長いリテンション時間を実現でき、従来のDRAMより電力消費が少ないメモリが得られる。SRAM構造に構成すると、ストレージ段でのリーク電流を減少し、低電力スタティック・メモリ・デバイスが得られる。本発明で要求される低リーク特性を実現するには、薄型チャンネル層トランジスタを使用する。説明を簡明にする目的で、薄型チャンネル・トランジスタだけが図示してある。原理において、本実施例で説明した各種の薄型チャンネル書き込みトランジスタが、本発明で提示した実施例のいずれかの書き込みトランジスタとして使用できる。

40

【0120】

図41aに示してある薄型チャンネル書き込みトランジスタはN型ウェルA77の絶縁層に製造する。このデバイスの一つの特性は、ドレイン領域とソース領域が多層多結晶シリコンから製造され、上層が多量ドーピングN型多結晶シリコン、下層が少量ドーピングN型または固有多結晶シリコンで構成されることである。3ナノメートル厚固有多結晶シリ

50

コン層はチャンネル領域 A 7 6 を形成し、ゲート端子 A 7 2 は多量ドーピング N 型多結晶シリコン層から形成される。ソース及びドレイン領域とチャンネル領域の間の接続で、多結晶シリコンのドーピング密度を減少し、後続の高温処理ステップの間にもチャンネル領域へドーパントが拡散するのを防止する。このようにすると、二つの領域の間の急峻な接合が回避され、デバイスのリーク電流をさらに減少させられる。軽くドーピングした N 型または固有多結晶シリコン層を最初に蒸着し、続けて高度にドーピングした N 型多結晶シリコン層を蒸着し、これがトランジスタのソース及びドレイン領域として機能する。アモルファス・シリコン層をさらに蒸着しソースとドレイン領域を接続するチャンネル領域を形成する。理想的には、図 4 1 b に示したようなソースとドレインの構造は多結晶シリコン構造の上部から底部へ向かってドーパント濃度を段階的に減少させるように製造する。

10

#### 【 0 1 2 1 】

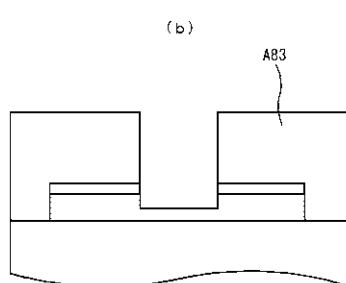

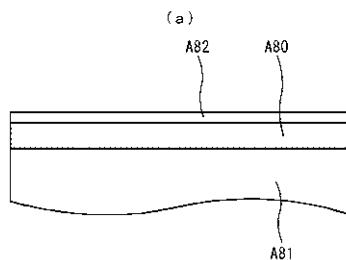

図 4 2 と図 4 3 は別の薄型チャンネル書き込みトランジスタ構造の製造ステップを示したものである。この場合、SOI ウエハを用いてデバイスのチャンネル領域が単結晶シリコンから構成されるようにする。多結晶シリコンではなく単結晶シリコンをチャンネル領域に使用することで、デバイスが易動性の増加により大きな「ON」電流を流せるようにする他、粒子境界個数の減少に支えられた低いトラップサイト密度と低いリークにより大きな閾値下係数を示すようになる。

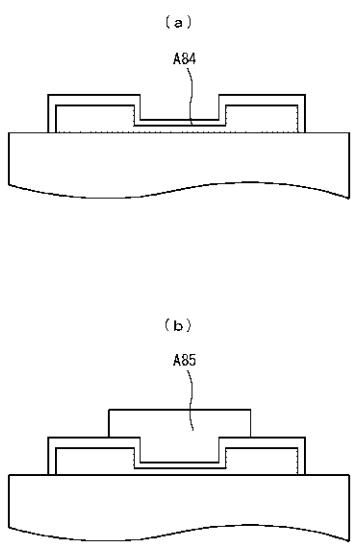

#### 【 0 1 2 2 】

この構造の製造について説明する。50 ナノメートル厚のシリコン層をもつ SOI ウエハを使用し、低エネルギー N 型ドーピング・イオン打込みを行なってから拡散プロセスを行ないシリコン層にドーパントを拡散する。SiO<sub>2</sub> 層 A 8 1 より上のシリコン層 A 8 0 の表面が酸化され、SiO<sub>2</sub> 層 A 8 2 を形成する（図 4 2 a 参照）。マスクを用いてフォトレジストの層をパターン化し、エッチングステップを行なってソース、ドレイン、チャンネル領域を形成する。別のレジスト・パターン A 8 3 をつかって SiO<sub>2</sub> とシリコンをエッチングし、10 ナノメートル厚のシリコン層が残るようにする（図 4 2 b 参照）。レジストを除去し暴露したシリコンを酸化して、3 ナノメートル厚のチャンネル領域 A 8 4 の上に 7 ナノメートル厚の SiO<sub>2</sub> 層を残す（図 4 3 a 参照）。N 型多結晶シリコンを蒸着、パターン化、エッチングしてトランジスタのゲート電極 A 8 5 を形成する（図 4 3 b 参照）。

20

#### 【 0 1 2 3 】

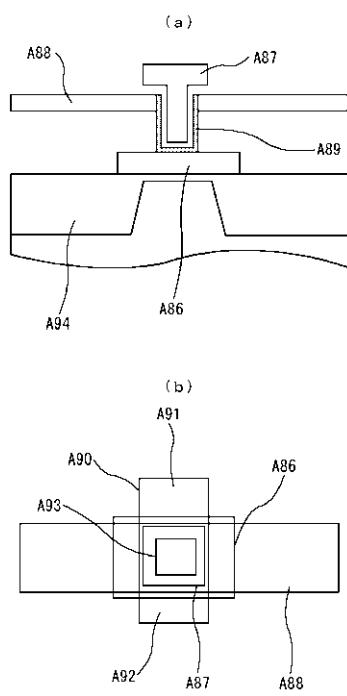

別の薄型チャンネル書き込みトランジスタ構造を図 4 4 に示す。断面図が図 4 4 a に示してあり、この構造のレイアウトが図 4 4 b に示してある。この構造では、書き込みトランジスタは垂直方向に製造しストレージ・トランジスタと組み合わされて小面積デバイス構造となる。ストレージ・トランジスタのゲート領域 A 8 6 は絶縁層 A 9 4 の上に製造して活性領域 A 9 0 を横断するようになる。この構造では同時に読み出しトランジスタのソース A 9 1 およびドレイン A 9 2 領域も画成する。書き込みトランジスタのソース A 8 6 およびドレイン A 8 8 領域は N 型多結晶シリコンから形成し、ドレインが垂直方向にソースの上に配置されるようになる。書き込みトランジスタのソース領域 A 8 6 はストレージ・トランジスタのゲート電極 A 8 6 に接続され、ドレイン領域 A 8 8 は書き込みデータ線に接続される。書き込みトランジスタのチャンネル領域 A 8 9 は書き込みデータ線が侵入するホール・パターン A 9 3 の内側に沿って形成する。

30

#### 【 0 1 2 4 】

チャンネル A 8 9 の制御電極 A 8 7 を P 型多結晶シリコンから形成しコンタクト・ホールを通して書き込みワード線へ接続する。P 型多結晶シリコンを用いることで、書き込みトランジスタの閾値電圧は、制御電圧が 0 V 付近にあるときリーク電流が最小になるようセットされる。本実施例では、ストレージ・トランジスタを作成した後、絶縁層を形成し、この後 N 型多結晶の蒸着を行なう。レジスト・パターンは N 型多結晶シリコンを貫通してストレージ・トランジスタのゲート電極までホール A 9 3 をエッチングするようにマスクする。3.5 ナノメートル厚アモルファス多結晶シリコン層を蒸着後、絶縁層の蒸着と結晶化ステップを行なう。別のレジスト層をパターン化して書き込みトランジスタのゲー

40

50

ト電極 A 87 を形成する。書き込みデータ線 A 88 をパターン化してエッチングする。最後に、各種のコンタクト及び相互接続メタル層をデバイス上に形成する。

【0125】

上記説明は部材の何らかの特定の材料、寸法、または方向に本発明を制限することを意味するものではない。多くの部材 / 方向の置き換えは本発明の範囲内で企図されることである。本明細書で説明した実施例は例として提示したものであって本発明の範囲を制限するために用いるべきではない。

【0126】

本発明はその用途において特定の実施例に関連して説明したが、本明細書の教示に鑑みて当業者において本発明の範囲から逸脱することなくあるいは本発明の範囲を越えることなく更なる実施例や変更を作成できるものである。したがって本明細書の図面ならびに説明は本発明の理解を助けるための例として提供され、本発明の範囲を制限するように解釈されるべきでないことは理解されるべきである。

【0127】

【発明の効果】

本発明によれば、高集積度DRAMが実現できる。さらに、2または3トランジスタ利得セル・メモリのセル寸法を縮小するような書き込み方法を提供する。ダイナミック・メモリは薄型チャンネル・トランジスタを書き込み素子として含み長いデータストレージ・リテンション時間が本発明のメモリ・デバイスで実現される。動作電力が小さく高密度のDRAMセルも実現できる。

【図面の簡単な説明】

【図1】第1の代表的実施例の容量結合書き込み方法を説明する回路図。

【図2】(a)及び(b)は、第1の代表的実施例の容量結合書き込み方法でのアクセス波形を示す図。

【図3】第1の代表的実施例の3Tメモリ・セルの回路図。

【図4】(a)及び(b)は、第1の代表的実施例の3Tメモリ・セルのアクセス波形を示す図。

【図5】従来の3Tメモリ・セル構造の略図を示す図。

【図6】(a)及び(b)は、従来の3Tメモリ・セルのアクセス波形を示す図。

【図7】第1の代表的実施例の3Tメモリ・セルの回路図と電圧表。

【図8】第1の代表的実施例の3Tメモリ・セルの回路図。

【図9】第1の代表的実施例の3Tメモリ・セルのアクセス波形を示す図。

【図10】半導体メモリの回路図。

【図11】半導体メモリの書き込み及び読み出しアクセス波形を示す図。

【図12】第2の代表的実施例の半導体メモリの回路図。

【図13】半導体メモリの書き込み及び読み出しアクセス波形を示す図。

【図14】第3の代表的実施例の半導体メモリの回路図。

【図15】半導体メモリの書き込み及び読み出しアクセス波形を示す図。

【図16】第4の代表的実施例の半導体メモリの回路図。

【図17】(a)及び(b)は、第4の代表的実施例の半導体メモリの書き込み及び読み出しアクセス波形を示す図。

【図18】第5の代表的実施例の半導体メモリの回路図。

【図19】(a)及び(b)は、半導体メモリの書き込み及び読み出しアクセス波形を示す図。

【図20】第6の代表的実施例の半導体メモリの回路図。

【図21】(a)及び(b)は、第6の代表的実施例の半導体メモリの書き込み及び読み出しアクセス波形を示す図。

【図22】第7の代表的実施例の半導体メモリ・アレイのレイアウト・パターンを示す図。

【図23】半導体メモリ・アレイの略図。

10

20

30

40

50

【図24】(a)及び(b)は、第7の代表的実施例の半導体メモリ・アレイ構造の断面図。

【図25】半導体メモリ・アレイのレイアウト・パターンを示す図。

【図26】第9の代表的実施例の半導体メモリ・アレイの略図。

【図27】第10の代表的実施例の半導体メモリ・アレイ構造の断面図。

【図28】半導体メモリ・アレイのレイアウト・パターンを示す図。

【図29】半導体メモリ・アレイの略図。

【図30】第11の代表的実施例の半導体メモリ・アレイ構造の断面図。

【図31】半導体メモリ・アレイのレイアウト・パターンを示す図。

【図32】半導体メモリ・アレイ構造の断面図。

【図33】(a)及び(b)は、第12の代表的実施例の半導体メモリ・アレイ構造の断面図。

【図34】第12の代表的実施例の半導体メモリ・アレイのレイアウト・パターンを示す図。

【図35】半導体メモリ・アレイの略図。

【図36】半導体メモリ・アレイのレイアウト・パターンを示す図。

【図37】第16の代表的実施例の半導体メモリの回路図。

【図38】(a)及び(b)は、半導体メモリの書き込み及び読み出しアクセス波形を示す図。

【図39】第17の代表的実施例の半導体メモリの回路図。

【図40】(a)及び(b)は、半導体メモリの書き込み及び読み出しアクセス波形を示す図。

【図41】(a)及び(b)は、第18の代表的実施例の半導体デバイスの断面図。

【図42】(a)及び(b)は、半導体デバイスの断面図。

【図43】(a)及び(b)は、半導体デバイスの断面図。

【図44】(a)及び(b)は、半導体デバイスの断面図とレイアウト・パターン。

#### 【符号の説明】

W<sub>L</sub>0：書き込みワード線、W<sub>L</sub>n：書き込みワード線、D<sub>L</sub>：データ線、M<sub>C</sub>：メモリ・セル、N<sub>S</sub>：ストレージ・ノード、C<sub>D</sub>：容量結合、S<sub>W</sub>：スイッチ素子、T<sub>R</sub>：定電圧基準ノード、C<sub>S</sub>：ストレージ・キャパシタ、S<sub>A</sub>：電圧センスアンプ、W<sub>R</sub>0：読み出しワード線、Q<sub>S</sub>：ストレージ・トランジスタ、Q<sub>W</sub>：書き込みトランジスタ・デバイス、Q<sub>R</sub>：読み出しトランジスタ、S<sub>N</sub>：選択信号。

10

20

30

【図1】

図 1

【図2】

図 2

【図4】

図 4

【図3】

図 3

【図5】

図 5

【図6】

図 6

【図7】

|                                 | 書き込み   |       |       | 読み込み       | スタンバイ |

|---------------------------------|--------|-------|-------|------------|-------|

|                                 | データセット | ノード転送 | ノード選択 |            |       |

| W <sub>0.1</sub><br>"0"状態       | 2V     | 2V    | 2V    | FLDAT HIGH | 2V    |

| W <sub>0.1</sub><br>"1"状態       | 0      | 0     | 0     | FLDAT HIGH | 2V    |

| W <sub>0</sub>                  | 0      | 2     | 0     | 0          | 0     |

| W <sub>0</sub>                  | 0      | 0     | 0     | 2V         | 0     |

| TR                              | 0      | 0     | 0     | 0          | 0     |

| W <sub>1</sub> , W <sub>1</sub> | 0      | 0     | 0     | 0          | 0     |

【図8】

【図9】

【図10】

【図11】

【 図 1 2 】

【図13】

【 図 1 4 】

【 図 15 】

【図16】

図16

【図17】

図17

(a)

図18

【図18】

【図19】

図19

(a)

【図20】

図20

【図21】

図21

【図22】

図22

【図23】

図23

【図24】

図24

【図25】

図 25

【図26】

図 26

【図27】

図 27

【図28】

図 28

【図 29】

図 29

【図 30】

図 30

【図 32】

図 32

【図 31】

図 31

【図 33】

図 33

【図34】

図34

【図35】

図35

【図36】

図36

【図37】

図37

【図38】

図38

【図39】

図39

【図41】

図41

【図40】

図40

【図42】

図42

【図43】

図43【図44】

図44

## フロントページの続き

(72)発明者 石井 智之

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所中央研究所内

(72)発明者 長部 太郎

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所中央研究所内

(72)発明者 柳沢 一正

東京都小平市上水本町五丁目20番1号 株式会社日立製作所半導体グループ内

(72)発明者 阪田 健

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所中央研究所内

F ターム(参考) 5F083 AD01 AD02 AD03 AD15 AD24 AD56 AD69 GA06 GA09 JA06

JA33 JA35 JA60 LA03 LA13 LA14 LA21 NA03 ZA21

5M024 AA91 BB02 BB35 BB36 CC02 CC03 CC04 CC18 CC50 HH13

PP01 PP02 PP03 PP04 PP05 PP07