(12)发明专利

(10)授权公告号 CN 103579137 B

(45)授权公告日 2020.03.13

(21)申请号 201310324485.5

(51)Int.CI.

(22)申请日 2013.07.30

H01L 23/31(2006.01)

(65)同一申请的已公布的文献号

H01L 23/29(2006.01)

申请公布号 CN 103579137 A

H01L 21/56(2006.01)

(43)申请公布日 2014.02.12

(56)对比文件

(30)优先权数据

CN 102237344 A, 2011.11.09,

13/561811 2012.07.30 US

CN 102593046 A, 2012.07.18,

(73)专利权人 通用电气公司

US 6306680 B1, 2001.10.23,

地址 美国纽约州

CN 101840914 A, 2010.09.22,

(72)发明人 A.V.高达 P.A.麦康奈李

TW 200620587 A, 2006.06.16,

S.S.乔罕

审查员 汪灵

(74)专利代理机构 中国专利代理(香港)有限公司 72001

权利要求书2页 说明书8页 附图7页

(54)发明名称

可靠的表面安装整体功率模块

(57)摘要

本发明涉及可靠的表面安装整体功率模块，公开了一种产生改进的热-机械可靠性和更牢靠的二级封装互连的表面安装封装结构。该表面安装封装结构包括子模块，该子模块具有介电层、附连到介电层的半导体装置、电联接至半导体装置的一级金属互连、以及电联接至一级互连且在与半导体装置相反的一侧形成于介电层上的二级I/O连接，其中二级I/O连接构造成将子模块连接到外部电路。子模块的半导体装置附连到多层衬底结构的第一表面，其中介电材料定位在介电层与多层衬底结构之间，以填充表面安装结构中的间隙并向其提供另外的结构完整性。

1. 一种表面安装结构,包括:

子模块,所述子模块包括:

介电层;

附连到所述介电层的至少一个半导体装置,所述至少一个半导体装置中的每一个包括由半导体材料组成的衬底;

电联接至所述至少一个半导体装置的一级金属互连结构,所述金属互连结构延伸通过穿过所述介电层形成的通孔,以便连接到所述至少一个半导体装置;以及

二级输入/输出I/O连接,其电联接至所述一级金属互连结构且在与所述至少一个半导体装置相反的一侧形成于所述介电层上,所述二级I/O连接构造成将所述子模块连接到外部电路;

具有第一表面和第二表面的多层衬底结构,第一表面包括第一金属层,第二表面包括第二金属层,其中所述子模块的所述至少一个半导体装置附连到所述多层衬底的所述第一表面;以及

一种或多种介电材料,其定位在所述介电层与所述多层衬底结构的所述第一表面之间且至少部分地围绕所述子模块的所述至少一个半导体装置,所述一种或多种介电材料构造成填充所述表面安装结构中的间隙且向其提供另外的结构完整性,

所述第二金属层的体积大于所述第一金属层的体积,并且,所述第二金属层与所述第一金属层之间的体积比提供了应力平衡的表面安装封装和减小其中的翘曲和热应力的互连结构。

2. 根据权利要求1所述的表面安装结构,其特征在于,所述多层衬底结构包括陶瓷绝缘层,所述第一金属层定位在所述绝缘层的一侧上,以形成所述多层衬底结构的所述第一表面,第二金属层定位在所述绝缘层的另一侧上,以形成所述多层衬底结构的所述第二表面。

3. 根据权利要求2所述的表面安装结构,其特征在于,所述第一和第二金属层包括第一和第二直接覆铜DBC层。

4. 根据权利要求3所述的表面安装结构,其特征在于,所述第一DBC层包括图案形成的DBC层,并且所述第二DBC层包括图案形成或未图案形成的DBC层。

5. 根据权利要求4所述的表面安装结构,其特征在于,所述第二DBC层的体积在所述第一DBC层的体积的1倍和2.5倍之间。

6. 根据权利要求4所述的表面安装结构,其特征在于,基于所述一种或多种介电材料的厚度和材料性质、所述至少一个半导体装置的密度、厚度和间距以及所述陶瓷绝缘层的厚度和材料性质中的至少一个,控制所述第二DBC层的厚度或面积和对应的体积。

7. 根据权利要求6所述的表面安装结构,其特征在于,所述一种或多种介电材料和所述陶瓷绝缘层的材料性质包括弹性模量、热膨胀系数(CTE)以及断裂应力和韧度中的至少一个。

8. 根据权利要求1所述的表面安装结构,其特征在于,所述一种或多种介电材料包括定位在所述介电层与所述多层衬底结构的所述第一表面之间的底部填充材料、密封剂、硅胶或模塑料。

9. 根据权利要求1所述的表面安装结构,其特征在于,一种或多种介电材料包括:

定位在所述介电层与所述多层衬底结构的所述第一表面之间的陶瓷或介电片,所述陶

瓷或介电片具有形成于其中的切口,以接纳所述至少一个半导体装置;和

介电填充材料,其定位在所述陶瓷或介电片与所述多层衬底结构的所述第一表面之间,以便填充所述陶瓷或介电片与所述多层衬底结构之间的间隙。

10. 根据权利要求1所述的表面安装结构,其特征在于,所述二级I/O连接包括盘栅阵列(LGA)焊接凸块和球栅阵列(BGA)焊接凸块中的一个。

11. 根据权利要求10所述的表面安装结构,其特征在于,所述表面安装结构还包括定位在所述多层衬底结构与所述子模块之间以将所述子模块固定至所述多层衬底结构的焊接材料、导电粘合剂或烧结金属接头中的一个。

12. 根据权利要求1所述的表面安装结构,其特征在于,所述子模块包括功率覆盖(POL)子模块。

13. 根据权利要求1所述的表面安装结构,其特征在于,所述至少一个半导体装置包括附连到所述介电层的多个半导体装置。

## 可靠的表面安装整体功率模块

### 技术领域

[0001] 本发明的实施例总体上涉及用于封装半导体装置的结构和方法，并且更特定地涉及产生改进的热-机械可靠性和更牢靠的二级封装互连的表面安装封装结构。

### 背景技术

[0002] 表面安装技术是一种用于构成其中表面安装构件或封装直接安装到印刷电路板 (PCB) 的表面上的电子电路或其它类似的外部电路的方法。在行业内，表面安装技术已替代将带有引线的构件装配在电路板中的孔内的通孔技术构成方法。

[0003] 一种普通类型的表面安装的构件是功率半导体装置，其是被用作功率电子电路中的开关或整流器的半导体装置，例如像开关模式电源。大部分功率半导体装置仅仅在变换模式下(即，它们接通或断开)使用，且因此对此进行优化。许多功率半导体装置用于高电压功率应用中，并且被设计成传送大量电流且支持大电压。在使用中，高电压功率半导体装置借助于功率覆盖 (power overlay, POL) 封装和互连系统表面安装至外部电路，其中POL封装还提供去除由该装置产生的热并保护装置与外部环境隔离的途径。

[0004] 标准的POL封装制造工艺典型地始于经由粘合剂将一个或多个功率半导体装置放置到介电层上。然后将金属互连(例如铜互连)电镀到介电层上以形成到功率半导体装置的直接金属连接，以便形成POL子模块。金属互连可呈低轮廓(例如厚度小于200微米)、平坦互连结构的形式，其供以形成往来于功率半导体装置的输入/输出(I/O)系统。然后使用用于电和热连接的焊接互连将POL子模块焊接到陶瓷衬底(带DBC的氧化铝、带AMB Cu的AlN等)。然后使用毛细流动(毛细底部填充)、无流动底部填充或注射模制(模塑料，molding compound)使用介电有机材料来填充在POL介电层与陶瓷衬底之间的半导体周围的间隙，以形成POL封装。

[0005] 在现有的表面安装的POL封装中，封装的长期可靠性受到由于构成材料的不同热膨胀系数(CTE)产生的热-机械应力限制。更具体而言，POL封装的介电有机材料/底部填料和陶瓷衬底的不同CTE引起底部填料和陶瓷衬底中的热和弯曲应力。底部填料和陶瓷衬底中的这些热和弯曲应力继而引起封装的翘曲。当封装的翘曲发生时，封装的二级互连的可靠性受影响。

[0006] 因此，将期望提供一种表面安装封装，其具有减小封装翘曲和热应力的基于应力平衡的设计策略，使得热循环中的封装可靠性可提高。还期望这种封装设计策略改进二级互连的可靠性。

### 发明内容

[0007] 本发明的实施例通过提供一种表面安装封装结构来克服前述缺点，该表面安装封装结构产生改进的热-机械可靠性和更牢靠的二级封装互连。

[0008] 根据本发明的一个方面，一种表面安装结构包括具有介电层和附连到该介电层的至少一个半导体装置的子模块，其中至少一个半导体装置中的每一个包括由半导体材料组

成的衬底。该子模块还包括：电联接到至少一个半导体装置的一级金属互连结构，其延伸通过穿过介电层形成的通孔，以便连接到至少一个半导体装置；以及二级输入/输出(I/O)连接，其电联接至一级金属互连结构且在与至少一个半导体装置相反的一侧形成于介电层上，该二级I/O连接构造成将子模块连接到外部电路。该表面安装结构还包括具有第一表面和第二表面的多层衬底结构，其中子模块的至少一个半导体装置附连到多层衬底的第一表面。该表面安装结构还包括一种或多种介电材料，其定位在介电层与多层衬底结构的第一表面之间且至少部分地围绕子模块的至少一个半导体装置，该一种或多种介电材料构造成填充表面安装结构中的间隙且向其提供另外的结构完整性。

[0009] 根据本发明的另一方面，一种制造表面安装封装和互连结构的方法包括构成子模块的步骤，该子模块包括至少一个半导体装置和绕其形成的封装结构，其中构成子模块的步骤还包括：将至少一个半导体装置附连到介电层；在介电层上方形成一级金属互连结构，其延伸通过介电层中的通孔以电连接到至少一个半导体装置；以及在与至少一个半导体装置相反的一侧在介电层上形成二级输入/输出(I/O)连接，其中二级I/O连接构造成将子模块连接到外部电路。该方法还包括形成衬底结构的步骤，该衬底结构包括中央衬底层以及位于中央衬底层的相反侧上的第一和第二金属层，使得第一和第二金属层分别形成衬底结构的第一表面和第二表面。该方法还包括以下步骤：将子模块附连到衬底结构的第一表面且在介电层与衬底结构的第一表面之间提供介电填充材料，该介电填充材料至少部分地密封子模块的至少一个半导体装置。

[0010] 根据本发明的又一方面，一种功率覆盖(POL)封装结构包括POL子模块，其具有：介电层；附连到介电层的多个半导体装置；一级互连结构，其电联接至多个半导体装置且延伸通过穿过介电层形成的通孔，以便连接到多个半导体装置；以及二级互连结构，用以将POL子模块电联接至外部电路结构，其中二级互连结构包括在介电层和一级互连结构上方形成且构造成建立到外部电路结构的互连的多个焊接凸块(bump)。该POL封装结构还包括具有第一表面和第二表面的多层衬底结构，其中POL子模块的多个半导体装置附连到多层衬底结构的第一表面上。POL封装结构的多层衬底结构还包括形成多层衬底结构的第一表面的第一直接覆铜(direct bond copper, DBC)层、形成多层衬底结构的第二表面的第二DBC层以及被夹置在第一与第二DBC层之间的陶瓷层。POL封装结构还包括定位在介电层与多层衬底结构的第一表面之间且至少部分地围绕子模块的多个半导体装置的密封剂。

[0011] 本发明公开了一种表面安装结构，其包括：子模块；具有第一表面和第二表面的多层衬底结构，其中子模块的至少一个半导体装置附连到多层衬底的第一表面；以及一种或多种介电材料，其定位在介电层与多层衬底结构的第一表面之间且至少部分地围绕子模块的至少一个半导体装置，一种或多种介电材料构造成填充表面安装结构中的间隙且向其提供另外的结构完整性。子模块包括：介电层；附连到介电层的至少一个半导体装置，至少一个半导体装置中的每一个包括由半导体材料组成的衬底；电联接至至少一个半导体装置的一级金属互连结构，金属互连结构延伸通过穿过介电层形成的通孔，以便连接到至少一个半导体装置；以及二级输入/输出(I/O)连接，其电联接至一级金属互连结构且在与至少一个半导体装置相反的一侧形成于介电层上，二级I/O连接构造成将子模块连接到外部电路。

[0012] 优选地，多层衬底结构包括：陶瓷绝缘层；第一金属层，其定位在绝缘层的一侧上，以形成多层衬底结构的第一表面；以及第二金属层，其定位在绝缘层的另一侧上，以形成多

层衬底结构的第二表面。

[0013] 优选地,第一和第二金属层包括第一和第二直接覆铜(DBC)层。

[0014] 优选地,第一DBC层包括图案形成的DBC层,并且第二DBC层包括图案形成或未图案形成的DBC层。

[0015] 优选地,第二DBC层的体积大于第一DBC层的体积。

[0016] 优选地,第二DBC层的体积在第一DBC层的体积的1倍和2.5倍之间。

[0017] 优选地,基于一种或多种介电材料的厚度和材料性质、至少一个半导体装置的密度、厚度和间距以及陶瓷绝缘层的厚度和材料性质中的至少一个,控制第二DBC层的厚度或面积和对应的体积。

[0018] 优选地,一种或多种介电材料和陶瓷绝缘层的材料性质包括弹性模量、热膨胀系数(CTE)以及断裂应力和韧度中的至少一个。

[0019] 优选地,第二DBC层与第一DBC层之间的体积比提供了应力平衡的表面安装封装和减小其中的翘曲和热应力的互连结构。

[0020] 优选地,一种或多种介电材料包括定位在介电层与多层衬底结构的第一表面之间的底部填充材料、密封剂、硅胶或模塑料。

[0021] 优选地,一种或多种介电材料包括:定位在介电层与多层衬底结构的第一表面之间的陶瓷或介电片,陶瓷或介电片具有形成于其中的切口,以接纳至少一个半导体装置;和介电填充材料,其定位在陶瓷或介电片与多层衬底结构的第一表面之间,以便填充陶瓷或介电片与多层衬底结构之间的间隙。

[0022] 优选地,二级I/O连接包括盘栅阵列(LGA)焊接凸块和球栅阵列(BGA)焊接凸块中的一个。

[0023] 优选地,表面安装结构还包括定位在多层衬底结构与子模块之间以将子模块固定至多层衬底结构的焊接材料、导电粘合剂或烧结金属接头中的一个。

[0024] 优选地,子模块包括功率覆盖(POL)子模块。

[0025] 优选地,至少一个半导体装置包括附连到介电层的多个半导体装置。

[0026] 通过结合附图提供的本发明的优选实施例的以下详细描述,这些和其它的优点和特征将更易于理解。

## 附图说明

[0027] 附图示出目前设想到的用于执行本发明的实施例。

[0028] 在附图中:

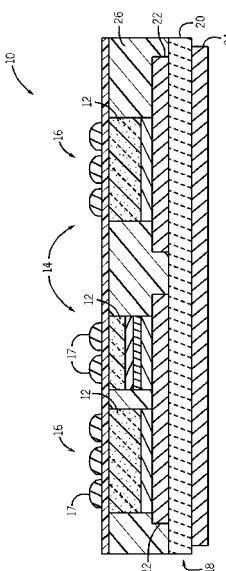

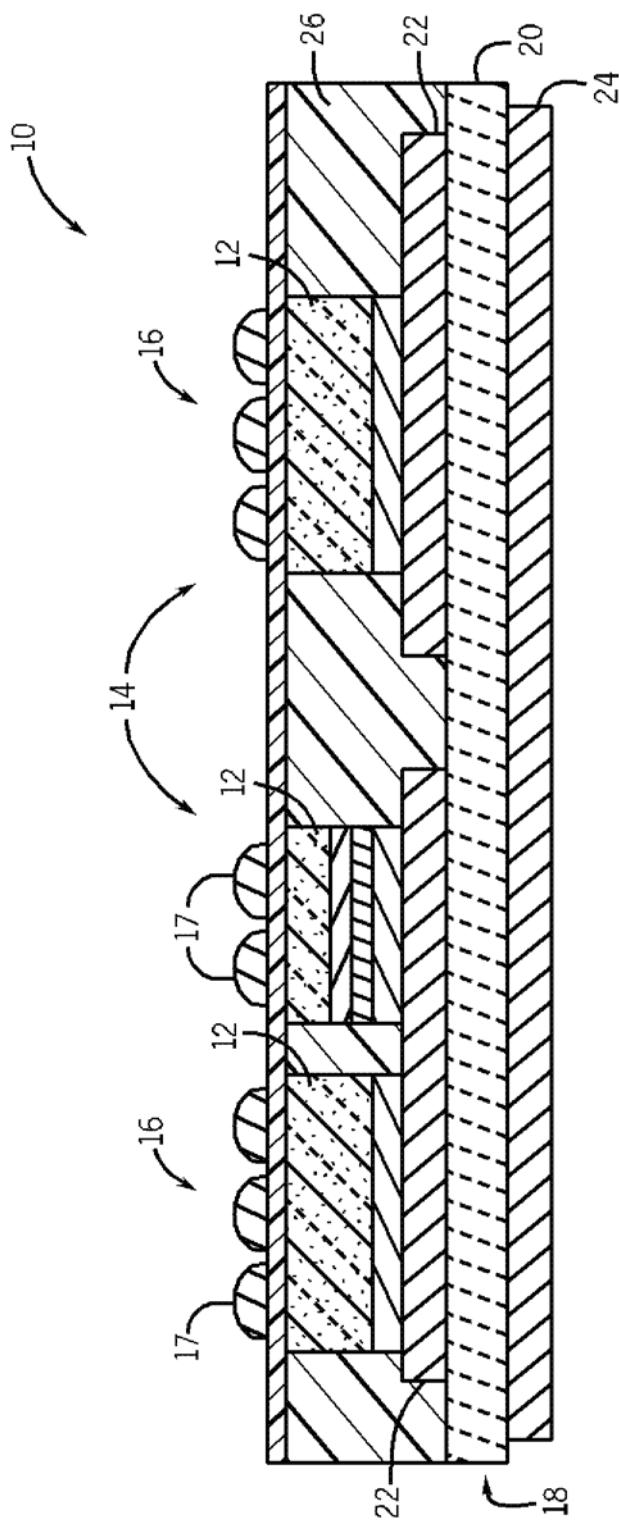

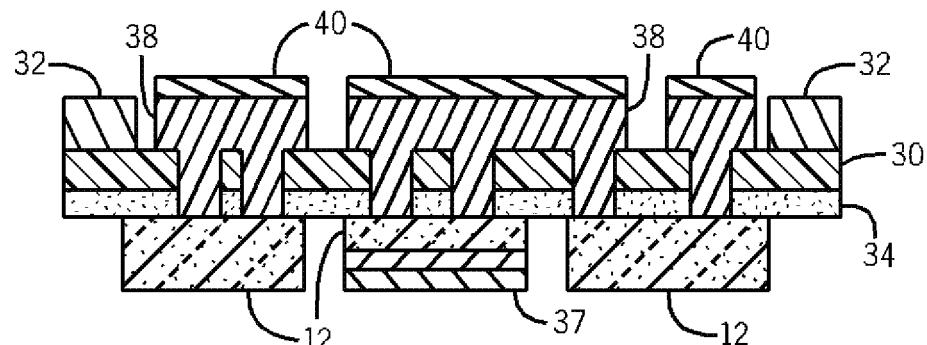

[0029] 图1是根据本发明的实施例的功率覆盖(POL)结构的示意性截面侧视图;

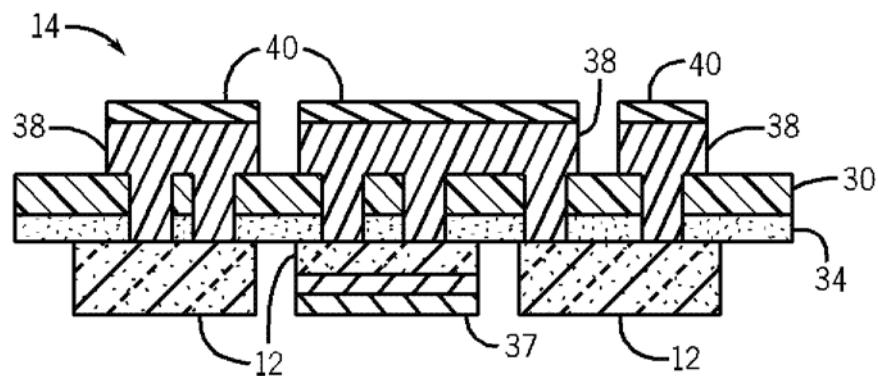

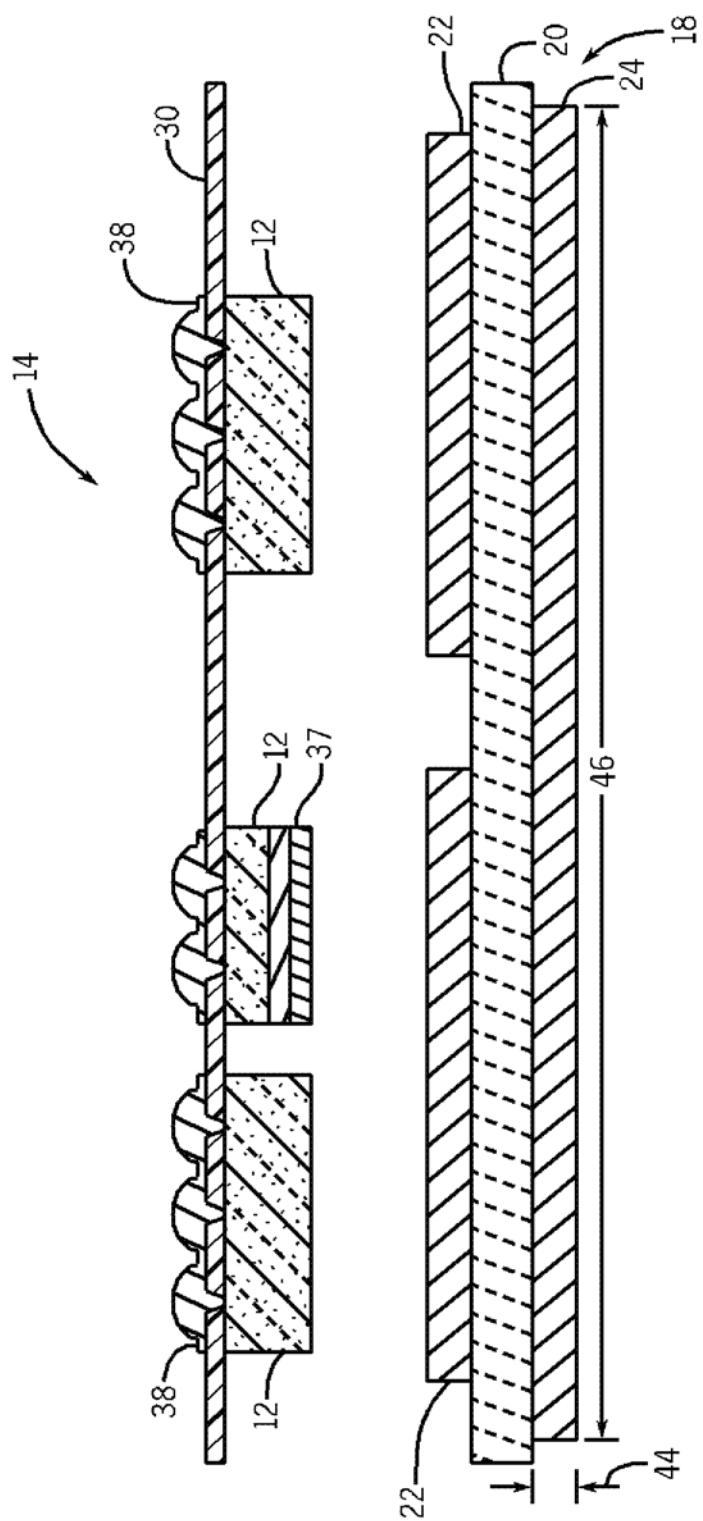

[0030] 图2至图11是根据本发明的实施例在制造/组建过程的各个阶段期间的POL结构的示意性截面侧视图;

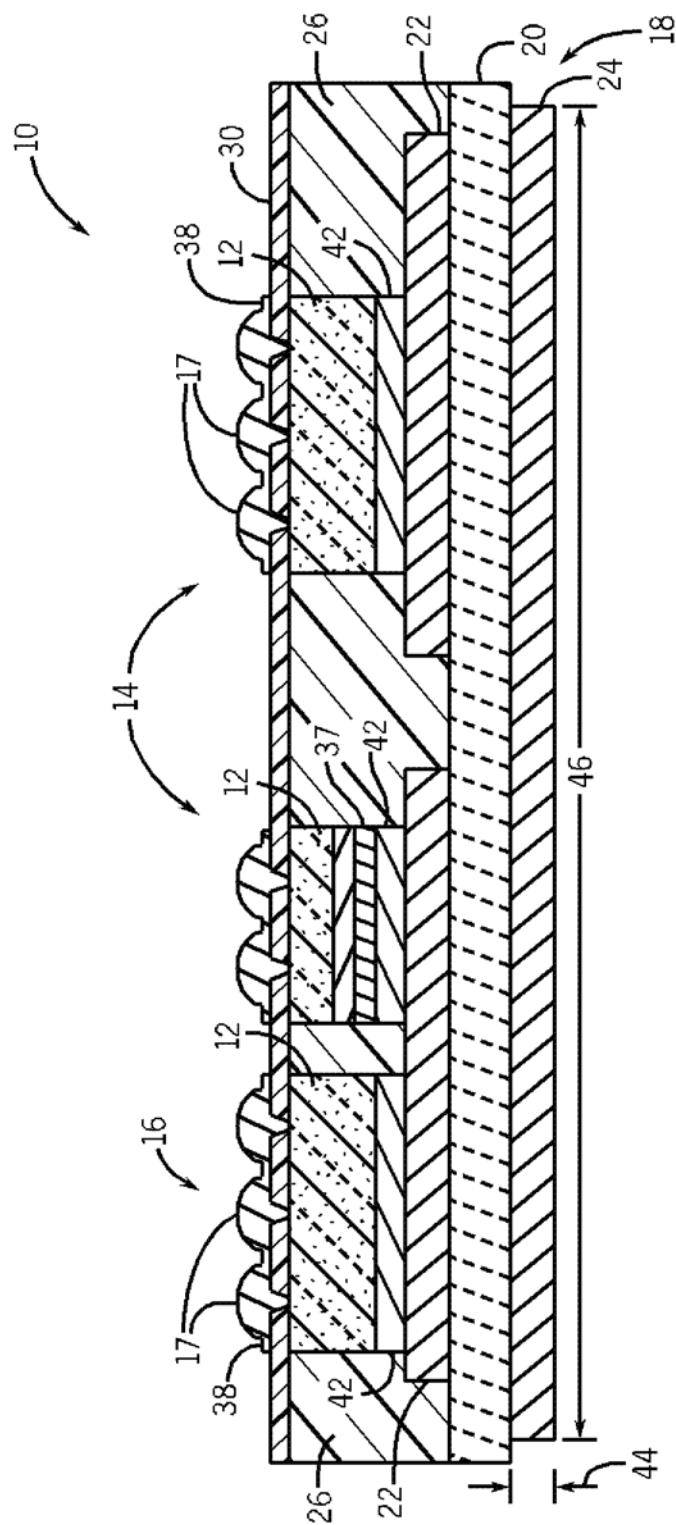

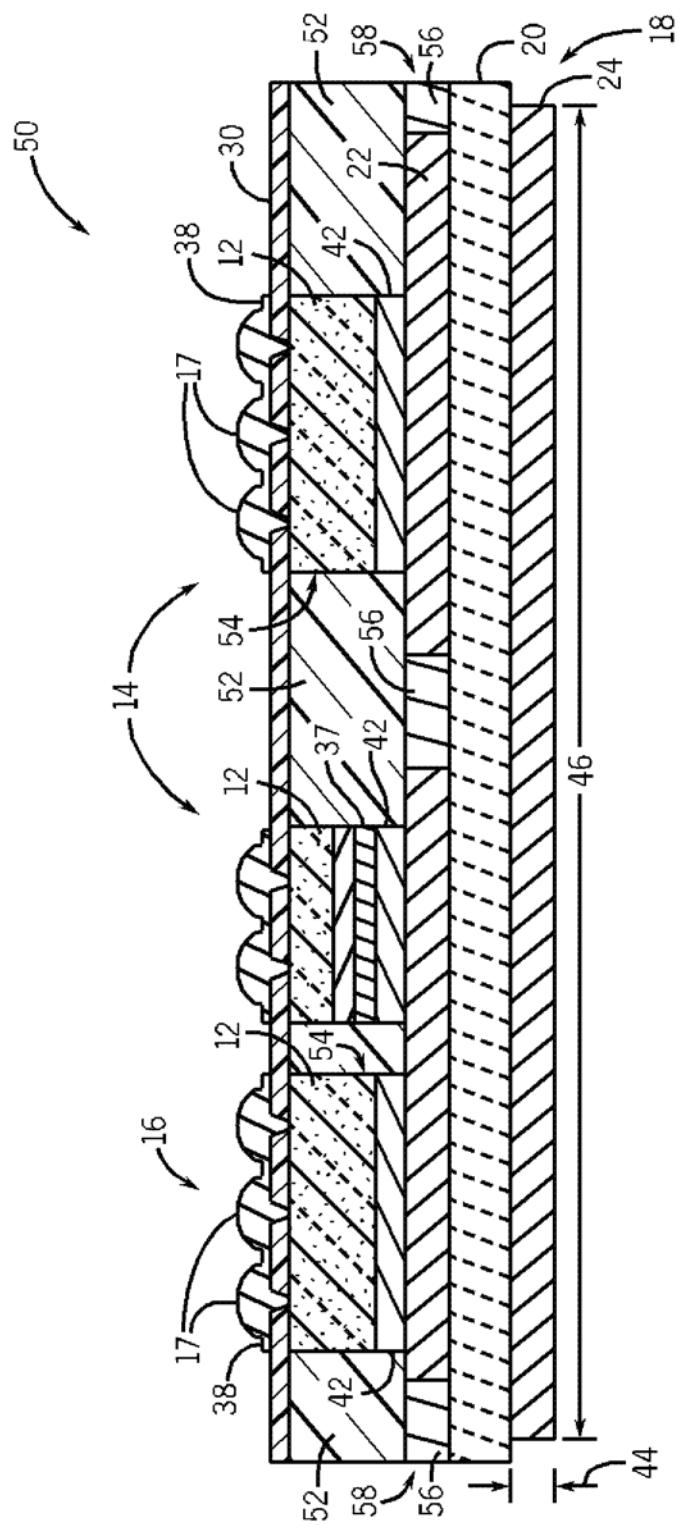

[0031] 图12是根据本发明的另一实施例的POL结构的示意性截面侧视图。

[0032] 附图标记:

[0033] 10 表面安装封装和互连结构

[0034] 12 半导体装置

[0035] 14 POL子模块

|        |    |                  |

|--------|----|------------------|

| [0036] | 16 | 二级输入-输出 (I/O) 连接 |

| [0037] | 17 | 焊接凸块             |

| [0038] | 18 | 多层衬底结构           |

| [0039] | 20 | 氧化铝              |

| [0040] | 22 | 直接覆铜层            |

| [0041] | 24 | 直接覆铜层            |

| [0042] | 26 | 介电材料             |

| [0043] | 30 | 介电层              |

| [0044] | 32 | 框架结构             |

| [0045] | 34 | 粘合剂层             |

| [0046] | 36 | 多个通孔             |

| [0047] | 37 | 铜垫片              |

| [0048] | 38 | 一级互连             |

| [0049] | 39 | 顶面               |

| [0050] | 40 | 焊接掩模层            |

| [0051] | 42 | 焊接材料             |

| [0052] | 44 | 厚度               |

| [0053] | 46 | 覆盖面积             |

| [0054] | 50 | POL结构            |

| [0055] | 52 | 陶瓷或介电片           |

| [0056] | 54 | 切口               |

| [0057] | 56 | 聚合物底部填充材料或模塑料    |

| [0058] | 58 | 间隙。              |

## 具体实施方式

[0059] 本发明的实施例提供了一种具有改进的热-机械可靠性的表面安装封装，以及形成这种表面安装封装的方法。

[0060] 参照图1，示出了根据本发明的实施例的表面安装封装和互连结构10。在图1中所示的实施例中，表面安装封装结构10呈功率覆盖 (POL) 结构的形式，但是认识到，其它表面安装封装结构被认为在本发明的范围内。POL结构10在其中包括一个或多个半导体装置12，根据各种实施例，半导体装置12可呈芯片 (die)、二极管或其它功率电子装置的形式。如图1中所示，三个半导体装置12设于POL结构10中，然而认识到，更多或更少数量的半导体装置12可包括在POL结构10中。半导体装置12封装在POL子模块14内，POL子模块14形成到功率半导体装置12的直接金属连接，其中连接呈例如低轮廓、平坦一级互连结构的形式。

[0061] 二级输入-输出 (I/O) 连接16设在POL子模块14上，以实现POL结构10到外部电路例如印刷电路板 (PCB) (未示出) 的表面安装。根据示例性实施例，二级I/O连接16由构造成附连/固连到PCB上以将POL结构10电联接至PCB的盘栅阵列 (LGA) 焊接凸块17形成，但是也可使用其它合适的二级焊接互连，例如球栅阵列 (BGA) 焊接凸块。LGA焊接凸块17提供抵抗高应力条件下失效的高度可靠的互连结构。

[0062] 如图1中所示, POL结构10还包括POL子模块14附连到其上的多层衬底结构18。根据示例性实施例, 衬底结构18由瓷板(例如氧化铝)20组成, 该瓷板20带有通过高温接合工艺结合到其两侧的一层直接覆铜(DBC)22、24, 其中顶部DBC层22形成结构18的“第一表面”, 而底部DBC层24形成结构18的“第二表面”。对于接合工艺, 可基于例如板20由氧化铝或氮化铝和氮化硅组成而采用不同的硬焊和直接结合技术。衬底结构18的顶部DBC层22或“芯片侧DBC层”然后在烧结后蚀刻, 以基于半导体装置12的数量/布置来按需要图案形成(pattern)该层。在衬底结构18的背面上的底部DBC层24或“非芯片侧DBC层”完全或部分地暴露以提供从POL结构10出来的高效传热。虽然在上文和下文中称作“DBC”层, 但是应认识到, 铝可代替铜用作金属层, 且因此这一实施例被认为在本发明的范围内。因此, 在下文中术语“DBC层”的使用意图涵盖包括结合至瓷板(例如氧化铝)20两侧的任何合适金属材料22、24(诸如铜或铝)片的衬底结构18。如图1中所示, 在POL结构10上还设置介电材料26(即“介电填充材料”)以填充POL结构10中的间隙, 以便向POL结构10提供另外的结构完整性。根据图1中所示的POL结构10的实施例, 介电材料26呈聚合物底部填料(例如毛细底部填料或无流动底部填料)、密封剂、硅胶或模塑料的形式。备选地且如下文将参照图12更详细论述的, 应该认识到, 介电材料26可由陶瓷或介电片和另外的介电填充材料(底部填料、模塑料、硅胶或密封剂)的组合形成。

[0063] 图1的POL结构10因此形成为使得二级封装I/O连接16设置在一级互连侧上, 以用于到PCB或其它外部电路的二级互连。POL结构10的具体构造产生改进的热-机械可靠性和更牢靠的二级封装I/O连接16, 以及优良的电和热性能。

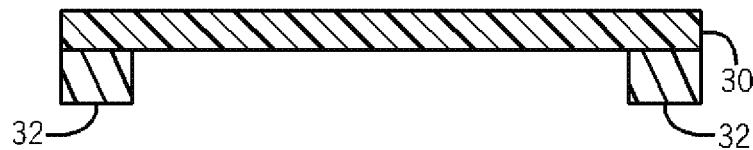

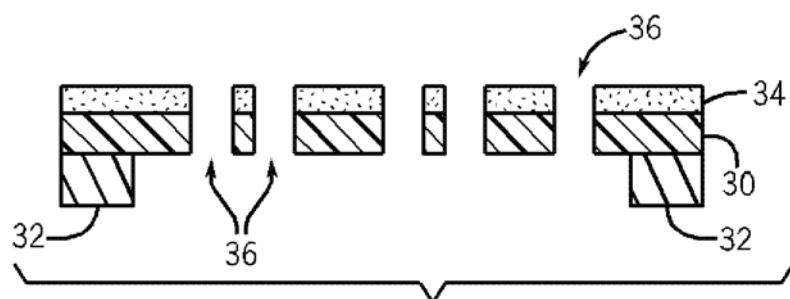

[0064] 现参照图2至图11, 根据本发明的实施例, 提供了用于制造图1的POL结构10的技术的工序的详细视图。如首先在图2至图9中所示, 提供了用于组建POL子模块14的工序。参照图2, POL子模块14的组建过程始于将介电层30或“挠性层”放置且附连到框架结构32上。介电层30呈叠层或膜的形式, 并且放置在框架结构32上, 以在POL子模块14的组建过程期间提供稳定性。根据本发明的实施例, 介电层30可由多种介电材料中的一种形成, 例如Kapton®、Ultem®、聚四氟乙烯(PTFE)、Upilex®、聚砜材料(例如Udel®、Radel®)或另一聚合物膜(如液晶聚合物(LCP)或聚酰亚胺材料)。

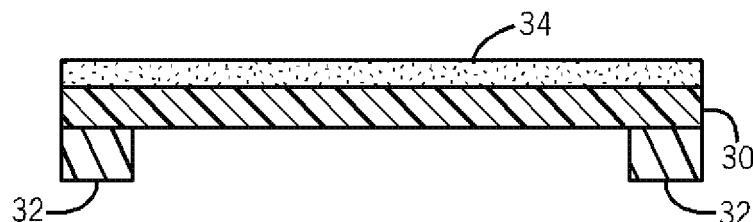

[0065] 如图3中所示, 在将介电层30固定到框架结构32后, 粘合剂层34沉积到介电层30上。然后穿过粘合剂层34和介电层30形成多个通孔36, 如图4中所示。根据本发明的实施例, 通孔36可经由激光消融或激光钻孔工艺、等离子体蚀刻、光界定或机械钻孔工艺而形成。在下一技术步骤中, 一个或多个半导体装置12(例如三个半导体装置)经由粘合剂层34固定到介电层30, 如图5中所示。为了将半导体装置12固定到介电层30, 将半导体装置12放置在粘合剂层34上且然后使粘合剂34固化, 以将半导体装置12固定到介电层30上。根据本发明的一个实施例且如图5中所示, 半导体装置12可具有不同厚度/高度。为了增加半导体装置12的厚度/高度, 可将铜垫片37焊接至一个或多个半导体装置12, 以便增加其厚度/高度, 使得所有半导体装置12的厚度/高度相等且使半导体装置12的背面“平坦化”。

[0066] 虽然穿过粘合剂层34和介电叠层30形成通孔36在图4中示出为在半导体装置12放置到粘合剂层34上之前执行, 但是认识到, 半导体装置12的放置可发生在通孔形成之前。即, 取决于由通孔尺寸施加的约束, 半导体装置12可首先放置于粘合剂层34和介电层30上, 通孔36随后在与形成于半导体装置12上的多个金属电路和/或连接垫(未示出)对应的位置

处形成。而且,可根据需要采用预钻通孔和后钻通孔的组合。

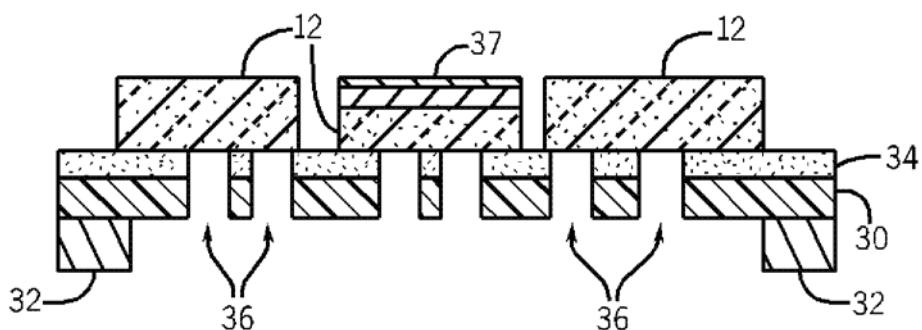

[0067] 现参照图6和图7,在将半导体装置12固定于介电层30上且形成通孔36后,清洁通孔36(诸如通过反应离子蚀刻(RIE)除尘工艺)且随后使其金属化而形成一级互连38。一级金属互连38典型地通过溅射和电镀应用的组合来形成,但是认识到,也可使用金属沉积的其它无电方法。例如,钛粘附层和铜籽晶层可首先经由溅射工艺来施加,然后是将铜的厚度增加到期望水平的电镀工艺。随后将所施加的金属材料图案形成为具有期望形状的金属互连38(即一级互连)且其充当穿过介电层30和粘合剂层30形成的竖直馈通。金属互连38从半导体装置12的电路和/或连接垫(未示出)延伸出,通过通孔/开口36且出来横跨介电层30的顶面39。

[0068] 如图8中所示,焊接掩模层40施加于图案形成的金属互连38上方,以提供用于其铜垫片的保护涂层。除焊接外,认识到该层40可由焊料以外的一些金属材料(诸如Ni或Ni/Au)组成。如图8中进一步所示,二级I/O互连16在介电层30的顶部上施加至焊接掩模层40。在一个实施例中,I/O互连16形成为LGA或BGA焊接凸块17,其焊接到焊接掩模40,以实现POL结构10到外部电路的表面安装。焊接凸块17提供抵抗高应力条件下失效的高度可靠的二级互连结构。

[0069] 在完成POL子模块14的组建时,POL子模块14被分割且从框架结构32移除,如图9中所示。因此提供完成的POL子模块14,其包括半导体装置12、充当金属竖直馈通的一级金属互连38和用于将POL子模块14表面安装到外部电路(诸如PCB)的二级I/O互连16。POL子模块14处置为构件或多芯片模块。

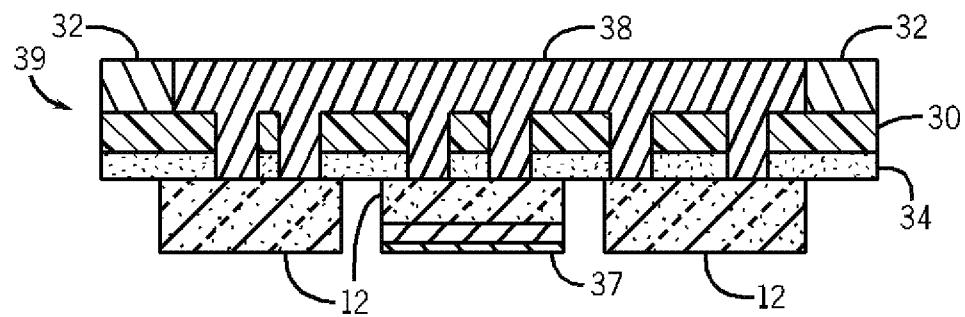

[0070] 现参照图10,制造POL结构10的技术继续将衬底结构18形成为结合到POL子模块14上。衬底结构18由瓷板(例如氧化铝)20组成,该瓷板20带有通过高温接合工艺结合到其两侧的芯片侧DBC层22和非芯片侧DBC层24。如图10中所示,衬底结构18的芯片侧DCB层22例如经由蚀刻工艺而被图案形成,以与POL子模块14的半导体装置12的数量/布置相关联。根据示例性实施例,在衬底结构18的背面上的非芯片侧DBC层24作为连续层未图案形成,以便提供衬底结构18的最大弯曲强度。另外,非芯片侧DBC层24的整个表面可用于热连接(即散热器附连)。

[0071] 如图11中所示,制造POL结构10的技术继续将POL子模块14附连到衬底结构18上。根据本发明的一个实施例,经由焊接材料42将POL子模块14附连到衬底结构18,以便将POL子模块14和衬底结构18固定在一起。即,每个半导体装置12被焊接到芯片侧DBC层22。然而认识到,还可使用导电粘合剂或烧结银来代替焊接材料,以将POL子模块14和衬底结构18固定在一起。然后在POL结构10上提供聚合物底部填料、密封剂或模塑料26(例如环氧树脂或其它有机填充材料),其填充POL结构10中的间隙,如图11中所示,以便约束介电层30并向POL结构10提供另外的电绝缘和结构完整性。

[0072] 如图10和图11中所示,根据本发明的示例性实施例,选择性地执行衬底结构18的形成,以便优化POL结构10的热性能。即,认识到,在衬底结构18中的陶瓷衬底20(其通常具有低CTE)与底部填料26和铜垫/连接22、24、38(其通常具有高CTE)的热膨胀系数(CTE)之间存在失配,并且该CTE失配可引起POL结构10中的不平衡热应力,且由此在陶瓷/绝缘衬底20、底部填充材料26和/或二级I/O互连16(即BGA/LGA焊接凸块17)中导致模块翘曲、弯曲应力和开裂。可通过衬底结构18的选择性形成本文减小POL结构10中不平衡的热应力和由此导

致的翘曲、弯曲应力和开裂。在形成衬底结构18时,选择性地控制非芯片侧DBC层24的厚度(标为44)和覆盖面积(标为46),以便优化POL结构10的热性能。更具体而言,选择/控制非芯片侧DBC层24的体积与芯片侧DBC层22的体积之比,使得底部填料26和陶瓷衬底20中的热/弯曲应力同时减小到可接受的水平以内。通过向衬底背侧(即非芯片侧)上的层24提供另外的DBC体积,非芯片侧上的DBC层24的热膨胀可抵消陶瓷衬底20的芯片侧上的底部填料/密封剂26膨胀,使得热/弯曲应力减小。

[0073] 在确定非芯片侧DBC 24与芯片侧DBC 22的适合的体积比/体积不平衡以及DBC层24的对应厚度44和覆盖面积46时,考虑以下因素:(1)底部填料26的体积及其已知的材料性质,包括底部填充材料的弹性模量、热膨胀系数(CTE)以及断裂应力和韧度;(2)POL子模块14内的芯片12密度、厚度和间距;以及(3)陶瓷衬底20的厚度和材料性质,包括陶瓷衬底的弹性模量和CTE。一般而言,较硬的底部填充材料26需要DBC层22、24之间较大的DBC体积不平衡,以减小模块翘曲和弯曲应力,而柔顺的底部填充材料需要较小的体积不平衡。

[0074] 根据本发明的示例性实施例,对于电子元件封装用的典型有机底部填充材料26,非芯片侧DBC 24和芯片侧DBC 22的DBC体积比/体积不平衡将大于1且小于2.5。即,期望DBC体积比/体积不平衡在该范围内,因为平衡的陶瓷衬底(即DBC比率约为1)将在热循环期间呈现高的不平衡热应力以及归因于陶瓷20(3-9ppm/C)与典型的有机底部填料26(9-50ppm/C)之间的高CTE失配的较大封装曲率(翘曲)。通过将非芯片侧DBC 24与芯片侧DBC 22的DBC体积比增大到1和2.5之间,提供了应力平衡,其减小了POL封装曲率且实现更牢靠的二级模块互连16。关于上文列举的1到2.5的范围,认识到,如果底部填料26的CTE很低,则非芯片侧DBC 24和芯片侧DBC 22的DBC体积比/体积不平衡可小于1,使得CTE失配减小。

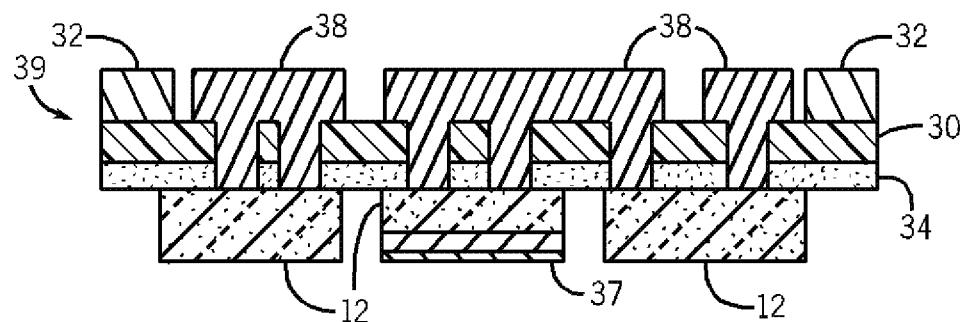

[0075] 现参照图12,根据本发明的另一实施例示出POL结构50,其中使用单独的介电元件以在由芯片12占据的区域中填充介电层30与衬底结构18之间的POL结构50中的间隙。如图12中所示,陶瓷或介电片52邻近介电层30定位在介电层30与多层衬底结构18之间。陶瓷/介电片52包括形成于其中的切口54,以将芯片12接纳在其中。聚合物底部填充材料或模塑料56然后定位在陶瓷/介电片52与多层衬底结构18之间,以便填充陶瓷/介电片52与多层衬底结构18的瓷板/氧化铝20之间的间隙58。与完全使用仅仅介电填充材料56相反,采用陶瓷/介电片52来填充在介电层30与衬底结构18之间的POL结构50中的体积的一部分有益地使POL结构50更不易吸收水分,且可进一步减小POL结构50中的热-机械应力,以便减少开裂、层离等。

[0076] 关于POL结构50,认识到,在确定非芯片侧DBC 24与芯片侧DBC 22的适合的体积比/体积不平衡以及DBC层24的对应厚度44和覆盖面积46时,考虑陶瓷/介电片52和底部填充材料56中的每一个的体积和已知的热-机械材料性质。陶瓷/介电片52和底部填充材料56中的每一个的弹性模量、热膨胀系数(CTE)以及断裂应力和韧度可彼此不同,且因此在确定体积比/体积不平衡时考虑每个单独元件的这些材料性质。

[0077] 有益地,本发明的实施例因此提供了具有二级封装I/O' 16的POL封装和互连结构10,该二级封装I/O' 16设置在POL子模块14的挠性侧(即介电层30的顶部)上以用于到外部电路的二级互连,并且整个非芯片侧DBC层24可用于热连接。POL结构10并入了减小封装翘曲和热应力的基于应力平衡的设计策略,使得热循环中的封装可靠性可提高。非芯片侧DBC层24的热膨胀抵消了在陶瓷衬底20的芯片侧上的底部填料/密封剂膨胀,得到的应力平衡

减小了封装曲率且实现了更牢靠的二级模块互连<sup>16</sup>。非芯片侧DBC层24可形成为提供用于特定封装设计(装置尺寸、密度等)的最佳DBC体积比/体积不平衡,其中非芯片侧DBC层24的体积确定基于二级装配的封装曲率要求,以及介电材料和绝缘材料的弯曲强度和韧度。

[0078] 因此,根据的本发明一个实施例,表面安装结构包括具有介电层和附连到该介电层的至少一个半导体装置的子模块,其中至少一个半导体装置中的每一个包括由半导体材料组成的衬底。该子模块还包括:电联接到至少一个半导体装置的一级金属互连结构,其延伸通过穿过介电层形成的通孔,以便连接到至少一个半导体装置;以及,电联接到一级金属互连结构且在与至少一个半导体装置相反的一侧形成于介电层上的二级输入/输出(I/O)连接,该二级I/O连接构造成将子模块连接到外部电路。该表面安装结构还包括具有第一表面和第二表面的多层衬底,其中子模块的至少一个半导体装置附连到多层衬底的第一表面。表面安装结构还包括定位在介电层与多层衬底结构的第一表面之间且至少部分地围绕子模块的至少一个半导体装置的一种或多种介电材料,该一种或多种介电材料构造成填充表面安装结构中的间隙且向其提供另外的结构完整性。

[0079] 根据本发明的另一实施例,一种制造表面安装封装和互连结构的方法包括构成子模块的步骤,该子模块包括至少一个半导体装置和绕其形成的封装结构,其中构成子模块的步骤还包括:将至少一个半导体装置附连到介电层;在介电层上方形成一级金属互连结构,其延伸通过介电层中的通孔以电连接到至少一个半导体装置;以及在与至少一个半导体装置相反的一侧在介电层上形成二级输入/输出(I/O)连接,其中二级I/O连接构造成将子模块连接到外部电路。该方法还包括形成衬底结构的步骤,该衬底结构包括中央衬底层以及位于中央衬底层的相反侧上的第一和第二金属层,使得第一和第二金属层分别形成衬底结构的第一表面和第二表面。该方法还包括以下步骤:将子模块附连到衬底结构的第一表面且在介电层与衬底结构的第一表面之间提供介电填充材料,该介电填充材料至少部分地密封子模块的至少一个半导体装置。

[0080] 根据本发明的又一实施例,一种功率覆盖(POL)封装结构包括POL子模块,该POL子模块具有:介电层;附连到介电层的多个半导体装置;一级互连结构,其电联接至多个半导体装置且延伸通过穿过介电层形成的通孔,以便连接到多个半导体装置;以及二级互连结构,用以将POL子模块电联接至外部电路结构,其中二级互连结构包括在介电层和一级互连结构上方形成且构造成建立到外部电路结构的互连的多个焊接凸块。POL封装结构还包括具有第一表面和第二表面的多层衬底结构,其中POL子模块的多个半导体装置附连到多层衬底结构的第一表面。POL封装结构的多层衬底结构还包括形成多层衬底结构的第一表面的第一直接覆铜(DBC)层、形成多层衬底结构的第二表面的第二DBC层以及夹置在第一和第二DBC层之间的陶瓷层。POL封装结构还包括定位在介电层与多层衬底结构的第一表面之间且至少部分地围绕子模块的多个半导体装置的密封剂。

[0081] 虽然仅仅结合有限数量的实施例详细地描述了本发明,但应当容易理解,本发明并不限于此类公开的实施例。而是,可修改本发明以并入之前未描述但与本发明的精神和范围相称的任意数量的变型、更改、替代或等效布置。此外,虽然描述了本发明的各种实施例,但应理解,本发明的方面可仅仅包括所述实施例中的一些。因此,本发明不应视为由前文的描述限制,而是仅由所附权利要求的范围限制。

图 1

图 2

图 3

图 4

图 5

图 6

图 7

图 8

图 9

图 10

图 11

图 12