(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7089967号**

**(P7089967)**

(45)発行日 令和4年6月23日(2022.6.23)

(24)登録日 令和4年6月15日(2022.6.15)

(51)国際特許分類

|        |                   |     |        |          |

|--------|-------------------|-----|--------|----------|

| H 01 L | 27/11568(2017.01) | F I | H 01 L | 27/11568 |

| H 01 L | 21/336(2006.01)   |     | H 01 L | 29/78    |

| H 01 L | 29/788(2006.01)   |     |        | 3 7 1    |

| H 01 L | 29/792(2006.01)   |     |        |          |

請求項の数 13 (全30頁)

|          |                             |

|----------|-----------------------------|

| (21)出願番号 | 特願2018-134089(P2018-134089) |

| (22)出願日  | 平成30年7月17日(2018.7.17)       |

| (65)公開番号 | 特開2020-13850(P2020-13850A)  |

| (43)公開日  | 令和2年1月23日(2020.1.23)        |

| 審査請求日    | 令和3年1月15日(2021.1.15)        |

|          |                                                   |

|----------|---------------------------------------------------|

| (73)特許権者 | 302062931<br>ルネサスエレクトロニクス株式会社<br>東京都江東区豊洲三丁目2番24号 |

| (74)代理人  | 110002066<br>特許業務法人筒井国際特許事務所                      |

| (72)発明者  | 井上 真雄<br>東京都江東区豊洲三丁目2番24号 ル<br>ネサスエレクトロニクス株式会社内   |

| (72)発明者  | 門島 勝<br>東京都江東区豊洲三丁目2番24号 ル<br>ネサスエレクトロニクス株式会社内    |

| (72)発明者  | 川嶋 祥之<br>東京都江東区豊洲三丁目2番24号 ル<br>ネサスエレクトロニクス株式会社内   |

| (72)発明者  | 山川 市朗                                             |

最終頁に続く

(54)【発明の名称】 半導体装置およびその製造方法

**(57)【特許請求の範囲】****【請求項1】**

半導体基板上に形成され、且つ、電荷の保持が可能な電荷蓄積層を含む第1ゲート絶縁膜と、前記第1ゲート絶縁膜上に形成された第1ゲート電極とを有する不揮発性メモリセルを備える半導体装置であって、

前記電荷蓄積層は、

前記半導体基板上に形成され、且つ、ハフニウムシリケート膜からなる第1絶縁膜と、前記第1絶縁膜上に形成され、前記第1絶縁膜とは異なる材料からなり、且つ、アルミニウム膜、窒化アルミニウム膜、炭化アルミニウム膜、アルミニウムシリケート膜または酸化アルミニウム膜からなる第1挿入層と、

前記第1挿入層上に形成され、前記第1挿入層とは異なる材料からなり、且つ、ハフニウムシリケート膜からなる第2絶縁膜と、

を有する、半導体装置。

**【請求項2】**

請求項1に記載の半導体装置において、

前記第1挿入層の厚さは、前記第1絶縁膜の厚さおよび前記第2絶縁膜の厚さよりも薄い、半導体装置。

**【請求項3】**

請求項1に記載の半導体装置において、

前記第1ゲート絶縁膜は、前記半導体基板と前記電荷蓄積層との間に、酸化シリコン膜ま

たは酸窒化シリコン膜からなる第3絶縁膜を更に有し、

前記第1絶縁膜は、前記第3絶縁膜に直接接している、半導体装置。

**【請求項4】**

請求項3に記載の半導体装置において、

前記電荷蓄積層は、

前記第2絶縁膜上に形成され、且つ、前記第1挿入層と同じ膜からなる第2挿入層と、

前記第2挿入層上に形成され、前記第2挿入層とは異なる材料からなり、且つ、ハフニウムシリケート膜からなる第4絶縁膜と、

を更に有する、半導体装置。

**【請求項5】**

請求項1に記載の半導体装置において、

前記第1ゲート絶縁膜は、前記電荷蓄積層と前記第1ゲート電極との間に、酸化アルミニウム膜、酸窒化アルミニウム膜またはアルミニウムシリケート膜からなり、且つ、前記第1挿入層よりも厚い厚さを有する第3絶縁膜を更に有する、半導体装置。

**【請求項6】**

請求項1に記載の半導体装置において、

前記第1ゲート絶縁膜は、前記第1ゲート電極と前記電荷蓄積層との間に、第3絶縁膜を更に有し、

前記第3絶縁膜は、

前記電荷蓄積層上に形成され、且つ、酸化アルミニウム膜、酸窒化アルミニウム膜またはアルミニウムシリケート膜からなる第4絶縁膜と、

前記第4絶縁膜上に形成され、且つ、酸化シリコン膜、酸窒化シリコン膜または窒化シリコン膜からなる第5絶縁膜と、

前記第5絶縁膜上に形成され、且つ、酸化アルミニウム膜、酸窒化アルミニウム膜またはアルミニウムシリケート膜からなる第6絶縁膜と、

を有し、

前記第1挿入層の厚さは、前記第4絶縁膜の厚さおよび前記第6絶縁膜の厚さよりも薄い、半導体装置。

**【請求項7】**

請求項6に記載の半導体装置において、

前記第4絶縁膜に含まれる複数の第1結晶粒と、前記第6絶縁膜に含まれる複数の第2結晶粒とは、前記第5絶縁膜によって分離されている、半導体装置。

**【請求項8】**

請求項7に記載の半導体装置において、

前記第4絶縁膜および前記第6絶縁膜は、それぞれ多結晶膜であり、

前記第5絶縁膜は、非晶質膜である、半導体装置。

**【請求項9】**

請求項1に記載の半導体装置において、

前記不揮発性メモリセルは、

前記半導体基板上に形成された第2ゲート絶縁膜と、

前記第2ゲート絶縁膜上に形成された第2ゲート電極と、

を更に有し、

前記第1ゲート電極は、前記第2ゲート電極と絶縁分離されている、半導体装置。

**【請求項10】**

請求項1に記載の半導体装置において、

前記第1挿入層は、酸化アルミニウム膜からなる、半導体装置。

**【請求項11】**

(a) 半導体基板上に、電荷の保持が可能な電荷蓄積層を含む第1ゲート絶縁膜を形成する工程、

(b) 前記第1ゲート絶縁膜上に、第1ゲート電極を形成する工程、

10

20

30

40

50

を有し、

前記(a)工程において、前記電荷蓄積層を形成する工程は、

(a1) 前記半導体基板上に、ハフニウムシリケート膜からなる第1絶縁膜を形成する工程、

(a2) 前記第1絶縁膜上に、アルミニウム膜、窒化アルミニウム膜、炭化アルミニウム膜、アルミニウムシリケート膜または酸化アルミニウム膜からなる第1挿入層を形成する工程、

(a3) 前記第1挿入層上に、ハフニウムシリケート膜からなる第2絶縁膜を形成する工程、

を有する、半導体装置の製造方法。

10

#### 【請求項12】

請求項11に記載の半導体装置の製造方法において、

前記(a3)工程後、熱処理を行う工程、を更に有し、

前記第1絶縁膜および前記第2絶縁膜の各々の前記ハフニウムシリケート膜は、 $Hf_xSi_{1-x}O_2$  ( $0 < x < 1$ ) 膜であり、

$0.9 < x < 1$  である場合には、前記熱処理の温度を 800 以上、975 未満とし、 $0 < x < 0.9$  である場合には、前記熱処理の温度を 975 以上、1050 以下とする、半導体装置の製造方法。

#### 【請求項13】

請求項11に記載の半導体装置の製造方法において、

20

前記(a)工程において、前記電荷蓄積層を形成する工程は、

(a4) 前記第2絶縁膜上に、前記第2絶縁膜の厚さよりも薄い厚さを有し、且つ、アルミニウム膜、窒化アルミニウム膜、炭化アルミニウム膜、アルミニウムシリケート膜または酸化アルミニウム膜からなる第2挿入層を形成する工程、

(a5) 前記第2挿入層上に、前記第2挿入層の厚さよりも厚い厚さを有し、且つ、ハフニウムシリケート膜からなる第3絶縁膜を形成する工程、

を更に有する、半導体装置の製造方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

30

本発明は、半導体装置およびその製造方法に関し、特に、不揮発性メモリセルを有する半導体装置に適用して有効な技術に関するものである。

##### 【背景技術】

##### 【0002】

電気的に書き込みおよび消去が可能な不揮発性メモリとして、フラッシュメモリまたはEEPROM (Electrically Erasable and Programmable Read Only Memory) が広く使用されている。これらの不揮発性メモリセルには、ゲート電極下に、例えば窒化シリコン膜のようなトラップ性絶縁膜を有する電荷蓄積層を設けた、MONOS (Metal Oxide Nitride Oxide Semiconductor) 型トランジスタと呼ばれるメモリセルがある。この電荷蓄積層に電荷の注入および放出を行うことによって、トランジスタの閾値をシフトさせることで、このトランジスタを不揮発性メモリセルとして使用することが可能となる。また、近年では、電荷蓄積層である窒化シリコン膜に代えて、酸化ハフニウム膜などのような高誘電率膜を用いた不揮発性メモリセルも開発されている。

40

##### 【0003】

例えば、特許文献1には、電荷蓄積層にハフニウムシリケート膜を用いた不揮発性メモリセルが開示されている。

##### 【先行技術文献】

##### 【特許文献】

##### 【0004】

##### 【文献】特開2015-53474号公報

50

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

高誘電率膜を用いた不揮発性メモリセルにおいて、リテンション特性などの信頼性を向上させることが望まれている。

**【0006】**

その他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

**【課題を解決するための手段】****【0007】**

本願において開示される実施の形態のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。 10

**【0008】**

一実施の形態である半導体装置は、半導体基板上に形成され、且つ、電荷の保持が可能な電荷蓄積層を含む第1ゲート絶縁膜と、第1ゲート絶縁膜上に形成された第1ゲート電極とを有する不揮発性メモリセルを備える。ここで、電荷蓄積層は、ハフニウム、シリコンおよび酸素を含む第1絶縁膜と、第1絶縁膜上に形成され、第1絶縁膜とは異なる材料からなり、且つ、アルミニウムを含む第1挿入層と、第1挿入層上に形成され、第1挿入層とは異なる材料からなり、且つ、ハフニウム、シリコンおよび酸素を含む第2絶縁膜と、を有する。

**【0009】**

また、一実施の形態である半導体装置は、電荷の保持が可能な電荷蓄積層を有する不揮発性メモリセルを備える。ここで、電荷蓄積層は、ハフニウム、シリコンおよび酸素を含む第1絶縁膜を有する。そして、ハフニウムと異なる金属を含む挿入層が、第1絶縁膜の膜中に、少なくとも1層以上形成されている。 20

**【発明の効果】****【0010】**

一実施の形態によれば、半導体装置の信頼性を向上させることができる。

**【図面の簡単な説明】****【0011】**

【図1】実施の形態1の半導体装置を示す断面図である。 30

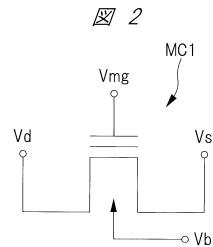

【図2】実施の形態1のメモリセルの等価回路図である。

【図3】「書き込み」、「消去」および「読み出」時における選択メモリセルの各部位への電圧の印加条件の一例を示す表である。

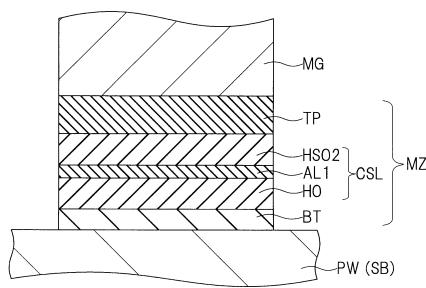

【図4】実施の形態1の半導体装置の要部を拡大した断面図である。

【図5】本願発明者らによる実験結果を示すグラフである。

【図6】電荷蓄積層の内部に存在するトラップ準位を示した模式図である。

【図7】本願発明者らによる実験結果を示すグラフである。

【図8】本願発明者らによる実験結果を示すグラフである。

【図9】実施の形態1の半導体装置の製造工程を説明する断面図である。

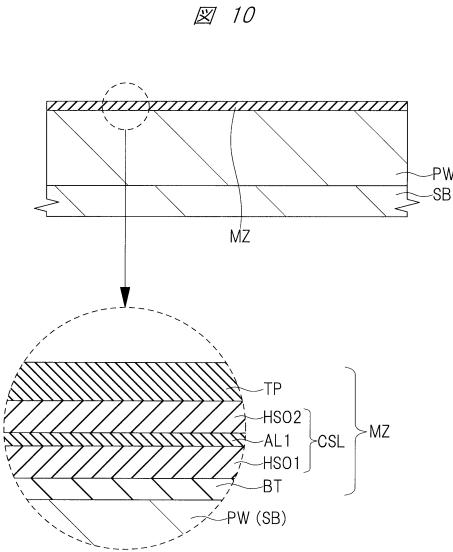

【図10】図9に続く製造工程を説明する断面図である。 40

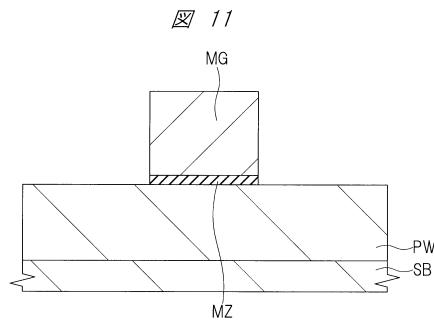

【図11】図10に続く製造工程を説明する断面図である。

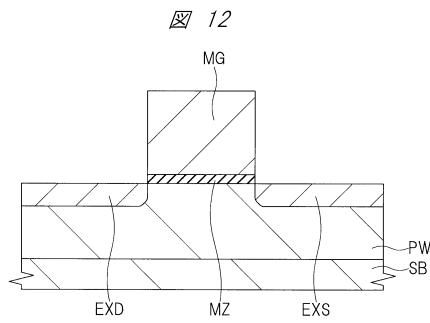

【図12】図11に続く製造工程を説明する断面図である。

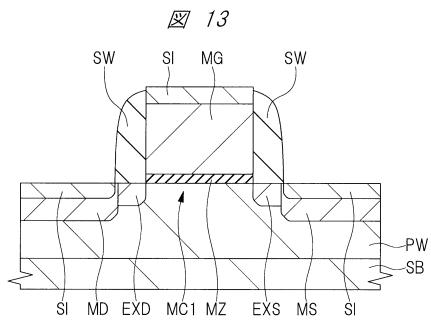

【図13】図12に続く製造工程を説明する断面図である。

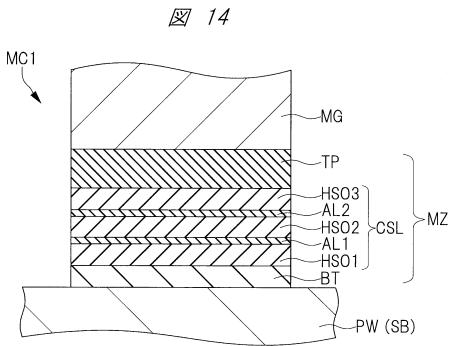

【図14】実施の形態2の半導体装置の要部を拡大した断面図である。

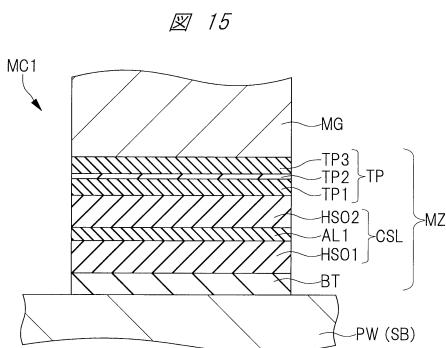

【図15】実施の形態3の半導体装置の要部を拡大した断面図である。

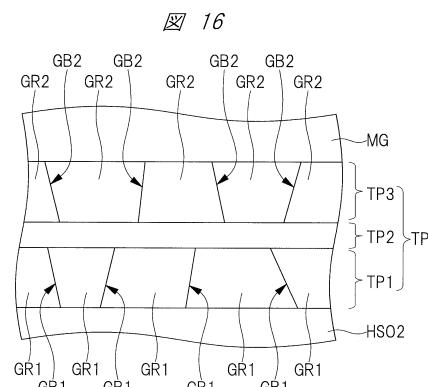

【図16】図15の一部を拡大した断面図である。

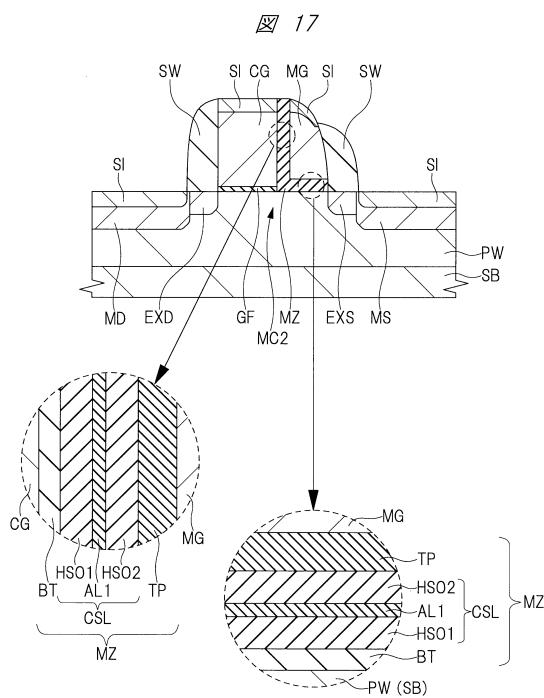

【図17】実施の形態4の半導体装置を示す断面図である。

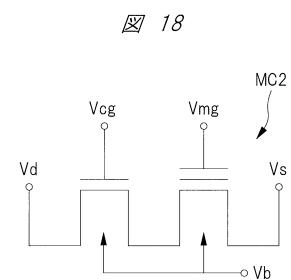

【図18】実施の形態4のメモリセルの等価回路図である。

【図19】「書き込み」、「消去」および「読み出」時における選択メモリセルの各部位への電圧の印加条件の一例を示す表である。 50

【図20】実施の形態4の半導体装置の製造工程を説明する断面図である。

【図21】図20に続く製造工程を説明する断面図である。

【図22】図21に続く製造工程を説明する断面図である。

【図23】図22に続く製造工程を説明する断面図である。

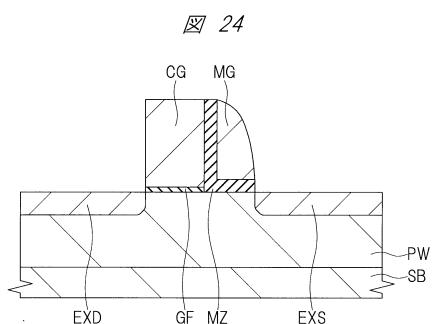

【図24】図23に続く製造工程を説明する断面図である。

【図25】図24に続く製造工程を説明する断面図である。

【図26】変形例の半導体装置を示す断面図である。

【図27】検討例1の半導体装置の要部を拡大した断面図である。

【図28】検討例2の半導体装置の要部を拡大した断面図である。

【図29】検討例3の半導体装置の要部を拡大した断面図である。

10

【発明を実施するための形態】

【0012】

以下の実施の形態においては、便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。また、以下の実施の形態において、要素の数等（個数、数値、量、範囲等を含む）に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でもよい。さらに、以下の実施の形態において、その構成要素（要素ステップ等も含む）は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

20

【0013】

以下、実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態では、特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

30

【0014】

また、実施の形態で用いる図面においては、図面を見易くするためにハッチングを省略する場合もある。

【0015】

（実施の形態1）

<メモリセルMC1の構造>

本実施の形態における不揮発性メモリセルであるメモリセルMC1を備える半導体装置について、図面を参照しながら説明する。図1は、本実施の形態の半導体装置の断面図であり、図2は、図1の要部を拡大した断面図である。

【0016】

本実施の形態のメモリセルMC1は、ゲート絶縁膜MZに電荷の保持が可能な電荷蓄積層CSLを備えたn型のトランジスタであり、電荷蓄積層CSLは、トラップ性絶縁膜を有する。

40

【0017】

図1に示されるように、半導体基板（基板）SBには、p型のウェル領域PWが形成されており、ウェル領域PWには、メモリセルMC1が形成されている。半導体基板SBは、例えば1cm～10cmの比抵抗を有するp型の単結晶シリコン（Si）からなる。

【0018】

半導体基板SB上（すなわちウェル領域PW上）には、ゲート絶縁膜MZが形成されており、ゲート絶縁膜MZ上には、メモリゲート電極MGが形成されている。メモリゲート電極MGは、例えばn型の不純物が導入された多結晶シリコン膜のような導電性膜である

50

。なお、消去時の正孔トンネル電流を確保するために、メモリゲート電極 M G に、p 型の不純物が導入された多結晶シリコン膜、または、不純物が導入されていない多結晶シリコン膜を適用してもよい。また、メモリゲート電極 M G は、例えば窒化チタン膜、アルミニウム膜若しくはタングステン膜のような金属膜、または、これらの金属膜の積層膜であってもよい。

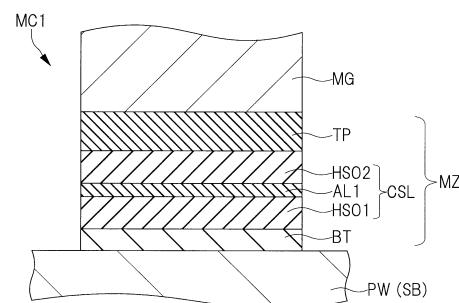

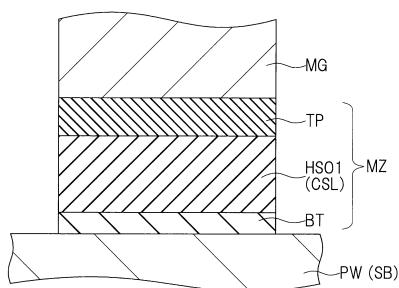

#### 【 0 0 1 9 】

また、図 1 では、図面を見易くするため、ゲート絶縁膜 M Z は単層の絶縁膜として表されているが、後述の図 4 で説明するように、実際には、ゲート絶縁膜 M Z は、絶縁膜 B T、絶縁膜 H S O 1、挿入層 A L 1、絶縁膜 H S O 2 および絶縁膜 T P を有する積層膜である。

#### 【 0 0 2 0 】

メモリゲート電極 M G の側面上には、サイドウォールスペーサ S W が形成されている。サイドウォールスペーサ S W は、例えば酸化シリコン膜と窒化シリコン膜との積層膜からなる。

#### 【 0 0 2 1 】

サイドウォールスペーサ S W 下のウェル領域 P W には、低濃度の n 型不純物領域であるエクステンション領域 E X S およびエクステンション領域 E X D が形成されている。また、サイドウォールスペーサ S W と整合する位置のウェル領域 P W には、エクステンション領域 E X S よりも高濃度の n 型不純物領域である拡散領域 M S 、および、エクステンション領域 E X D よりも高濃度の n 型不純物領域である拡散領域 M D が形成されている。エクステンション領域 E X S および拡散領域 M S は、互いに接続されており、それぞれメモリセル M C 1 のソース領域の一部を構成している。エクステンション領域 E X D および拡散領域 M D は、互いに接続されており、それぞれメモリセル M C 1 のドレイン領域の一部を構成している。

#### 【 0 0 2 2 】

メモリゲート電極 M G 上、拡散領域 M S 上および拡散領域 M D 上には、例えばコバルトシリサイド (C o S i 2) 、ニッケルシリサイド (N i S i) またはニッケルプラチナシリサイド (N i P t S i) からなるシリサイド層 S I が形成されている。シリサイド層 S I は、主に、後述のプラグ P G との接触抵抗を低減するために形成されている。

#### 【 0 0 2 3 】

このようなメモリセル M C 1 上には、層間絶縁膜 I L 1 が形成されている。層間絶縁膜 I L 1 には複数のコンタクトホールが形成され、複数のコンタクトホール内には、複数のプラグ P G が形成されている。プラグ P G は、例えば、チタン膜、窒化チタン膜、または、これらの積層膜からなるバリアメタル膜と、例えばタングステンを主体とする導電性膜とからなる。プラグ P G は、シリサイド層 S I を介して、拡散領域 M S または拡散領域 M D に電気的に接続されている。なお、図示はしていないが、層間絶縁膜 I L 1 中には、メモリゲート電極 M G に電気的に接続されるプラグ P G も存在している。

#### 【 0 0 2 4 】

プラグ P G 上および層間絶縁膜 I L 1 上には、層間絶縁膜 I L 2 が形成されている。層間絶縁膜 I L 2 には配線用の溝が形成され、この溝内には、例えば銅を主体とする導電性膜を有する配線 M 1 が埋め込まれている。また、配線 M 1 はプラグ P G に電気的に接続されている。このような配線は、所謂ダマシン構造の配線である。配線 M 1 の上方には、更に多層の配線および層間絶縁膜も形成されているが、ここではそれらの図示および説明は省略する。

#### 【 0 0 2 5 】

< メモリセル M C 1 の動作について >

以下に、不揮発性メモリセルであるメモリセル M C 1 の動作例について、図 2 および図 3 を参照して説明する。なお、ここで説明するメモリセル M C 1 は、半導体装置内に存在している複数のメモリセル M C 1 のうち、選択メモリセルである。

#### 【 0 0 2 6 】

図 2 は、メモリセル M C 1 の等価回路図である。図 3 は、「書込」、「消去」および「読

10

20

30

40

50

出」時におけるメモリセルMC1の各部位への電圧の印加条件の一例を示す表である。図3の表には、「書込」、「消去」および「読出」時のそれれにおいて、ドレイン領域である拡散領域MDに印加される電圧Vd、メモリゲート電極MGに印加される電圧Vm g、ソース領域である拡散領域MSに印加される電圧Vs、および、ウェル領域PWに印加される電圧Vbが記載されている。

#### 【0027】

なお、図3の表に示したものは電圧の印加条件の好適な一例であり、これに限定されるものではなく、必要に応じて種々変更可能である。また、本実施の形態では、ウェル領域PWから電荷蓄積層CSLへの電子の注入を「書込」と定義し、電荷蓄積層CSLからウェル領域PWへの電子の放出を「消去」と定義する。

10

#### 【0028】

書込動作は、FNトンネル(Fowler Nordheim Tunneling)方式によって行われる。例えば図3の「書込」の欄に示されるような電圧を、書き込みを行うメモリセルMC1の各部位に印加し、ウェル領域PWからメモリセルMC1の電荷蓄積層CSLに電子を注入することで書き込みを行う。注入された電子は、電荷蓄積層CSL中のトラップ準位に捕獲され、その結果、メモリゲート電極MGを有するメモリトランジスタのしきい値電圧が上昇する。すなわち、メモリトランジスタは書込状態となる。

#### 【0029】

消去動作は、FNトンネル方式によって行われる。例えば図3の「消去」の欄に示されるような電圧を、消去を行うメモリセルMC1の各部位に印加し、電荷蓄積層CSL中の電子をウェル領域PWへ放出する。その結果、メモリトランジスタのしきい値電圧が低下する。すなわち、メモリトランジスタは消去状態となる。

20

#### 【0030】

読出動作には、例えば図3の「読出」の欄に示されるような電圧を、読出しを行うメモリセルMC1の各部位に印加する。読出し時のメモリゲート電極MGに印加される電圧Vm gを、書き込み状態におけるメモリトランジスタのしきい値電圧と、消去状態におけるメモリトランジスタのしきい値電圧との間の値にすることで、書き込み状態または消去状態を判別することができる。

#### 【0031】

##### <ゲート絶縁膜MZの詳細な構造>

30

図4は、図1に示される半導体装置の要部を拡大した断面図であり、ゲート絶縁膜MZの詳細な構造を示す断面図である。

#### 【0032】

ゲート絶縁膜MZは、半導体基板SB(ウェル領域PW)とメモリゲート電極MGとの間に介在しており、メモリセルMC1のゲート絶縁膜として機能する膜であり、その内部に電荷蓄積層CSLを有する積層膜である。具体的には、ゲート絶縁膜MZは、半導体基板SB上に形成された絶縁膜BTと、絶縁膜BT上に形成された絶縁膜HSO1と、絶縁膜HSO1上に形成された挿入層AL1と、挿入層AL1上に形成された絶縁膜HSO2と、絶縁膜HSO2上に形成された絶縁膜TPとの積層膜からなる。

#### 【0033】

絶縁膜(ボトム絶縁膜)BTは、例えば酸化シリコン膜または酸窒化シリコン膜であり、例えば2nm~5nmの厚さを有する。

40

#### 【0034】

絶縁膜HSO1は、窒化シリコン膜よりも高い誘電率を有する膜であり、酸化金属膜であり、例えば5nm~9nmの厚さを有する。具体的には、絶縁膜HSO1は、ハフニウム(Hf)、シリコン(Si)および酸素(O)を含む膜であり、好ましくはHfxSi1-xO2(0 < x < 1)膜のようなハフニウムシリケート膜である。なお、絶縁膜HSO1中のトラップ準位の密度を向上させるため、HfxSi1-xO2膜の組成比は、0.6 < x < 1であることが好ましく、x = 0.8であることが最も好ましい。

#### 【0035】

50

挿入層 A L 1 は、ハフニウムとは異なる金属を含む膜であり、アルミニウム( A l )を含む膜であり、例えば 1 nm ~ 4 nm の厚さを有する。具体的には、挿入層 A L 1 は、アルミニウム( A l )膜、窒化アルミニウム( A l N )膜、炭化アルミニウム( A l C )膜、アルミニウムシリケート( A l S i O )膜または酸化アルミニウム膜である。本実施の形態において、挿入層 A L 1 として好ましいのは、アルミニウム( A l )および酸素( O )を含む酸化金属膜であり、最も好ましいの A l 2 O 3 膜のような酸化アルミニウム膜である。

#### 【 0 0 3 6 】

絶縁膜 H S O 2 は、挿入層 A L 1 と異なる材料からなる膜であり、ハフニウム( H f )、シリコン( S i )および酸素( O )を含む膜であり、例えば 5 nm ~ 9 nm の厚さを有する。絶縁膜 H S O 2 は、絶縁膜 H S O 1 と同じ材料であることが好ましい。

10

#### 【 0 0 3 7 】

このように、本実施の形態では、電荷蓄積層 C S L の内部において、ハフニウム、シリコンおよび酸素を含む膜( 絶縁膜 H S O 1 、絶縁膜 H S O 2 )の膜中に、アルミニウムを含む膜( 挿入層 A L 1 )が、1層形成されている。

#### 【 0 0 3 8 】

絶縁膜( トップ絶縁膜 ) T P は、窒化シリコン膜よりも高い誘電率を有する膜であり、絶縁膜 H S O 1 および絶縁膜 H S O 2 と異なる材料からなる酸化金属膜であり、例えば 5 nm ~ 12 nm の厚さを有する。具体的には、絶縁膜 T P は、アルミニウム( A l )および酸素( O )を含む膜であり、好ましくは酸化アルミニウム膜、酸窒化アルミニウム膜またはアルミニウムシリケート膜である。また、絶縁膜 T P として、他の酸化金属膜を用いることもでき、例えば、チタン( T i )、ジルコニア( Z r )、イットリウム( Y )、ランタン( L a )、プラセオジム( P r )またはルテチウム( L u )の何れかの金属の酸化物からなる酸化金属膜を、絶縁膜 T P 1 として用いることもできる。

20

#### 【 0 0 3 9 】

絶縁膜 T P は、主に、電荷蓄積層 C S L の内部に蓄積された電荷が、メモリゲート電極 M G へ抜けることを防止する役目を果たす。このため、絶縁膜 T P は、挿入層 A L 1 よりも、厚い厚さを有していることが好ましい。

#### 【 0 0 4 0 】

ところで、従来の不揮発性メモリセルでは、トラップ準位を備えたゲート絶縁膜としては、酸化シリコン膜、電荷蓄積層である窒化シリコン膜、および、酸化シリコン膜を積層した ONO ( oxide nitride oxide ) 膜が知られている。ONO 膜を採用した場合は、誘電率が比較的低いことから、ゲート絶縁膜の E O T ( Equivalent Oxide Thickness : 酸化膜換算膜厚 ) が大きくなってしまう。このため、ゲート絶縁膜の E O T が大きくなることで動作電圧が高くなる懸念がある。また、ゲート絶縁膜の E O T を小さくするために物理的膜厚を薄くしようとすると、電荷蓄積層内に蓄積した電荷のリークによって、リテンション特性( 電荷保持特性、データ保持特性 ) の劣化が生じる懸念がある。これらは、半導体装置の信頼性を低下させてしまう。

30

#### 【 0 0 4 1 】

本実施の形態では、電荷蓄積層 C S L は、主に、高誘電率膜である絶縁膜 H S O 1 および絶縁膜 H S O 2 によって構成されている。また、絶縁膜 T P も高誘電率膜である。これらの膜により、ゲート絶縁膜 M Z の E O T を抑制しながらゲート絶縁膜 M Z の物理的膜厚を増加させることができるために、リークによるリテンション特性の劣化を防止し、リテンション特性の向上を図ることができる。また、ゲート絶縁膜 M Z の物理的膜厚を確保しながら E O T を低減できるため、リークによるリテンション特性の劣化を防止しながら、メモリセル M C 1 の動作電圧の低減および動作速度の向上を図ることができる。

40

#### 【 0 0 4 2 】

ここで、本実施の形態の電荷蓄積層 C S L が有するトラップ準位は、 H f × S i 1 - x O 2 ( 0 < x < 1 ) 膜である絶縁膜 H S O 1 および絶縁膜 H S O 2 の内部に多く存在するが、絶縁膜 H S O 1 と挿入層 A L 1 との界面付近、および、絶縁膜 H S O 2 と挿入層 A L 1

50

との界面付近に、より多くのトラップ準位が存在している。このため、電荷蓄積層C S Lの中央部に近い位置に、より多くのトラップ準位を存在させることができる。すなわち、電荷蓄積層C S Lの内部のうち、絶縁膜H S O 1の下面から離れた位置、および、絶縁膜H S O 2の上面から離れた位置に、より多くの深いトラップ準位を存在させることができる。また、後述の図7でも説明するが、ハフニウムシリケート膜と酸化アルミニウム膜との界面には、多くの深いトラップ準位が存在する。本実施の形態では、このような界面を形成することができるため、多くの深いトラップ準位を形成することができる。これらにより、電荷蓄積層C S Lの内部に蓄積した電荷が、電荷蓄積層C S Lから抜けにくくなり、メモリセルM C 1のリテンション特性を向上させることができる。

#### 【0043】

また、挿入層A L 1は、電荷蓄積層C S Lの内部におけるトラップ準位を多くするために設けられた膜である。例えば、挿入層A L 1が酸化アルミニウム膜であり、絶縁膜H S O 1および絶縁膜H S O 2がハフニウムシリケート膜である場合、酸化アルミニウム膜の誘電率は、ハフニウムシリケート膜の誘電率よりも低い。このため、挿入層A L 1の厚さは、必要以上に厚くしない方が好ましく、絶縁膜H S O 1の厚さおよび絶縁膜H S O 2の厚さよりも薄いことが好ましい。

#### 【0044】

<検討例1～3の半導体装置と、本実施の形態の半導体装置との比較>

以下に、上述のようなリテンション特性の向上について、図5～図8および図27～図29を用いて詳しく説明する。

#### 【0045】

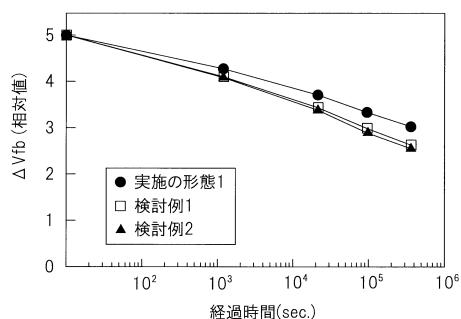

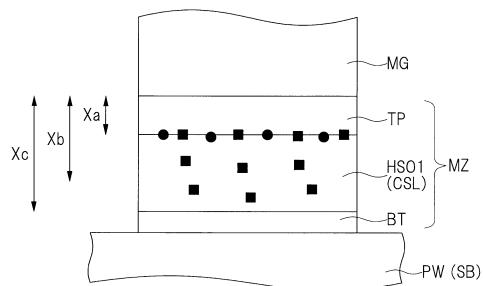

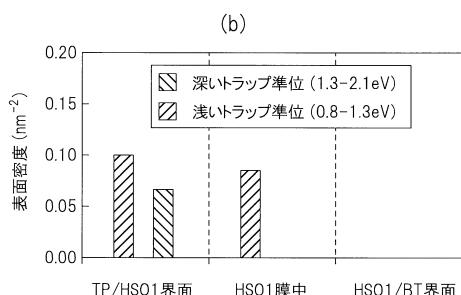

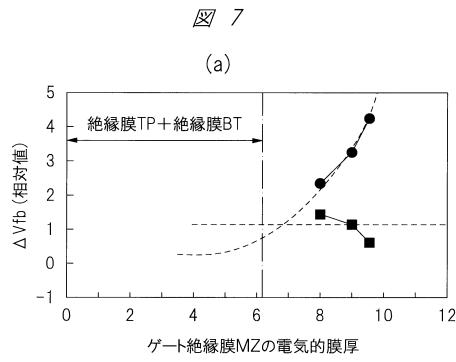

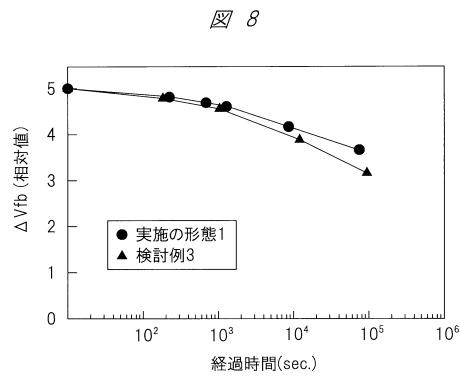

図27～図29は、それぞれ検討例1～検討例3の半導体装置の要部を拡大した断面図であり、図6は、電荷蓄積層C S Lの内部に存在するトラップ準位を示した模式図であり、図5、図7および図8は、本願発明者らによる実験結果を示すグラフである。

#### 【0046】

検討例1の半導体装置は、図27に示されるように、電荷蓄積層C S Lとして絶縁膜H S O 1のみが形成されており、電荷蓄積層C S Lには、挿入層A L 1および絶縁膜H S O 2が含まれていない。また、検討例1の絶縁膜H S O 1の厚さは、本実施の形態の絶縁膜H S O 1の厚さと、挿入層A L 1の厚さと、絶縁膜H S O 2の厚さとを合計した程度の厚さとなっている。

#### 【0047】

検討例2の半導体装置は、図28に示されるように、電荷蓄積層C S Lとして絶縁膜H O、挿入層A L 1および絶縁膜H S O 2が形成されている。絶縁膜H Oは、本実施の形態の絶縁膜H S O 1のような $H_f \times Si_1 - x O_2$  ( $0 < x < 1$ ) 膜ではなく、酸化ハフニウム膜(H f O膜)である。また、検討例2の絶縁膜H Oの厚さは、本実施の形態の絶縁膜H S O 1の厚さと同程度である。

#### 【0048】

検討例3の半導体装置は、図29に示されるように、電荷蓄積層C S Lとして挿入層A L 1および絶縁膜H S O 2が形成されており、絶縁膜H S O 1が形成されていない。このため、検討例3の挿入層A L 1は、絶縁膜B Tと直接接している。また、検討例3の絶縁膜H S O 2の厚さは、本実施の形態の絶縁膜H S O 1の厚さと、絶縁膜H S O 2の厚さとを合計した程度の厚さとなっている。

#### 【0049】

図5の横軸は、メモリセルM C 1に書き動作を行った後に、150℃の高温でメモリセルM C 1を放置した時間を示している。図5の縦軸は、フラットバンド電圧の変動量V f bを示しており、具体的には、書き動作後に一定時間が経過した後のフラットバンド電圧(V f b)と、書き動作を行う前のフラットバンド電圧(V f b i)との差を示している。なお、図5のV f bの値は、フラットバンド電圧の変動量の相対値である。また、ここでは、絶縁膜H S O 1に $H_f \times Si_1 - x O_2$  ( $x = 0.8$ ) 膜を適用し、絶縁膜B Tに酸窒化シリコン(SiON)膜を適用した場合で測定している。また、トップ絶縁膜T

10

20

30

40

50

Pは、酸化アルミニウム膜などの単層膜である場合で説明するが、後述の実施の形態3のように、トップ絶縁膜TPが、絶縁膜TP1～TP3のような積層膜であっても、フラットバンド電圧の変動量Vfbの比率は同様である。

#### 【0050】

図5から判るように、本実施の形態( )、検討例1( )および検討例2( )では、時間の経過と共に、それぞれ上記変動量Vfbが減少しているが、本実施の形態( )では、検討例1( )および検討例2( )よりも、上記変動量Vfbの減少が抑制されている。すなわち、本実施の形態( )では、検討例1( )および検討例2( )よりも、リテンション特性が改善されていることが判る。

#### 【0051】

また、リテンション特性が改善された結果から、本実施の形態( )では絶縁膜HSO1と絶縁膜HSO2との間に、挿入層AL1を形成しているので、本実施の形態( )の電荷蓄積層CSLの内部のトラップ準位は、検討例1( )よりも、増えたと推測できる。

#### 【0052】

また、本実施の形態( )のように、絶縁膜HSO1にHfxSi1-xO2膜を適用したことで、検討例2( )のように、絶縁膜HSO1にHfO膜を適用するよりも、電荷蓄積層CSLの内部のトラップ準位が増えたと推測できる。

#### 【0053】

図6は、検討例1の構造を基にして、電荷蓄積層CSLの内部に存在するトラップ準位を示した模式図である。印は1.3eV～2.1eVのエネルギーを有する深いトラップ準位を示し、印は0.8eV～1.3eVのエネルギーを有する浅いトラップ準位を示している。距離Xaは、メモリゲート電極MGから、絶縁膜TPと絶縁膜HSO1との界面付近までの距離を示している。距離Xbは、メモリゲート電極MGから絶縁膜HSO1の膜中までの距離を示している。距離Xcは、メモリゲート電極MGから、絶縁膜HSO1と絶縁膜BTとの界面付近までの距離を示している。

#### 【0054】

図7(a)は、電荷蓄積層CSLの内部に存在するトラップ準位を、TSC-CV(Thermally Stimulated Current-Capacitance Voltage)法を用いて、エネルギー的な分布深さ毎に分解したグラフを示している。図7(a)の縦軸は、フラットバンド電圧の変動量Vfbを示し、図7(a)の横軸は、ゲート絶縁膜MZの電気的な厚さを示している。ここでは、絶縁膜BTの厚さと絶縁膜TPの厚さとが一定であるとして測定した結果を示している。

#### 【0055】

ここで、電荷蓄積層CSLに蓄積された電荷Qによるフラットバンド電圧の変動量Vfbは、以下の式(1)で表され、メモリゲート電極MGから電荷Qまでの距離Xに比例し、誘電率kに反比例する。なお、容量Cは、電荷Qとメモリゲート電極MGとの間の容量である。

#### 【0056】

$$V_{fb} = Q / C = Q \times X / k \quad (1)$$

距離Xを図6の距離Xa～Xcに当てはめた場合、X=Xaの時には、変動量Vfbはほぼ一定となる。X=Xbの時には、電荷蓄積層CSLの膜中において距離Xbが変化するので、変動量VfbはXbの積分値(Xbdx)に比例する。すなわち、変動量VfbはXbの2乗(Xb^2)に比例する。X=Xcの時には、変動量VfbはXcに比例する。

#### 【0057】

このため、図7(a)の破線で示されるように、深いトラップ準位( )においては、厚さ方向に対して変動量Vfbはほぼ一定となり、浅いトラップ準位( )においては、厚さ方向に対して変動量Vfbはほぼ二次曲線と重なっている。

#### 【0058】

図7(b)は、TSC-CV法を用いて、ゲート絶縁膜MZの膜中に存在するトラップ準位を示したグラフである。

10

20

30

40

50

位の表面密度を求めたグラフである。図7の横軸は、絶縁膜TPと絶縁膜HSO1との界面付近、絶縁膜HSO1の膜中、および、絶縁膜HSO1と絶縁膜BTとの界面付近における、各々の領域を示している。図7の縦軸は、トラップ準位の表面密度の値を示している。ここでは、検討例1の構造において、絶縁膜BTが酸窒化シリコン膜であり、絶縁膜HSO1がハフニウムシリケート膜であり、絶縁膜TPが酸化アルミニウム膜である場合で測定している。

#### 【0059】

図7(b)に示されるように、深いトラップ準位は、酸化アルミニウム膜である絶縁膜TPと、ハフニウムシリケート膜である絶縁膜HSO1との界面に多く存在していることが判る。すなわち、図7(a)および図7(b)の結果から、ゲート絶縁膜MZの内部のトラップ準位は、図6のような分布になっていることが判る。

10

#### 【0060】

本願発明者らは、この結果を応用し、ハフニウムシリケート膜の膜中に酸化アルミニウム膜を挿入することで、ハフニウムシリケート膜と酸化アルミニウム膜との界面を多く形成し、多くの深いトラップ準位を形成することを考案した。すなわち、本実施の形態では、絶縁膜HSO1と絶縁膜HSO2との間に、挿入層AL1が形成されていることで、電荷蓄積層CSLの内部において、多くの深いトラップ準位を存在させることができている。

#### 【0061】

以上のように、図6および図7の結果と、図5の結果とを組み合わせて考察すると、本実施の形態の電荷蓄積層CSLの厚さは、検討例1の電荷蓄積層CSLの厚さとほぼ同じであるにも関わらず、本実施の形態では、検討例1よりも、リテンション特性が改善されている。これは、本実施の形態では、絶縁膜HSO1と絶縁膜HSO2との間に、挿入層AL1を形成することで、絶縁膜HSO1と挿入層AL1との界面付近、および、絶縁膜HSO2と挿入層AL1との界面付近に、より多くの深いトラップ準位を存在させる事ができるからである。言い換えれば、電荷蓄積層CSLの内部において、ハフニウムシリケート膜と酸化アルミニウム膜との界面、すなわち深いトラップ準位が形成され易い界面が増えている。従って、電荷蓄積層CSLの中央部に近い位置に、より多くの深いトラップ準位を存在させることができる。これにより、リテンション特性が改善できるので、半導体装置の信頼性を向上させることができる。

20

#### 【0062】

更に、本実施の形態の電荷蓄積層CSLでは、絶縁膜HSO1は、ハフニウム(Hf)、シリコン(Si)および酸素(O)を含む膜であり、好ましくはHf<sub>x</sub>Si<sub>1-x</sub>O<sub>2</sub>(0 < x < 1)膜のようなハフニウムシリケート膜である。これにより、検討例2のように、絶縁膜HSO1にHfO膜を適用するよりも、電荷蓄積層CSLの内部において、深いトラップ準位を増やすことができ、リテンション特性を改善させることができる。

30

#### 【0063】

図8の横軸は、メモリセルMC1に書き動作を行った後に、室温(26)でメモリセルMC1を放置した時間を示している。図8の縦軸は、図5の縦軸と同様に、フラットバンド電圧の変動量Vfbを示している。

40

#### 【0064】

図8から判るように、本実施の形態( )および検討例3( )では、時間の経過と共に、それぞれ上記変動量Vfbが減少しているが、本実施の形態( )では、検討例3( )よりも、上記変動量Vfbの減少が抑制されている。すなわち、本実施の形態( )では、検討例3( )よりも、リテンション特性が改善されていることが判る。また、図8のグラフは室温でメモリセルMC1を放置したものであるが、例えば150以上的高温でメモリセルMC1を放置した場合には、本実施の形態( )の変動量Vfbと、検討例3( )変動量Vfbとの差が、更に大きくなることは自明である。

#### 【0065】

すなわち、検討例3のように、絶縁膜HSO1を形成せずに、挿入層AL1を絶縁膜BT

50

に直接接するように形成すると、リテンション特性が劣化した。このため、本実施の形態のように、挿入層 A L 1 が絶縁膜 B T に直接接しないように、挿入層 A L 1 は絶縁膜 H S O 1 と絶縁膜 H S O 2との間に形成し、絶縁膜 H S O 1 が絶縁膜 B T に直接接していることが好ましい。これにより、リテンション特性を改善させることができる。

#### 【 0 0 6 6 】

<メモリセル M C 1 の製造方法 >

以下に、図 9 ~ 図 13 を用いて、本実施の形態の半導体装置の製造方法を説明する。

#### 【 0 0 6 7 】

まず、図 9 に示されるように、フォトリソグラフィ法およびイオン注入法によって、例えばボロン ( B ) または二フッ化ボロン ( B F 2 ) を半導体基板 S B 内に導入することで、

10 p 型のウェル領域 P W を形成する。

#### 【 0 0 6 8 】

図 10 は、ゲート絶縁膜 M Z の形成工程を示している。なお、図 10 以降では、図面を見易くするために、ゲート絶縁膜 M Z を単層膜として図示しているが、実際には、図 10 の破線で囲まれた領域である拡大図のように、ゲート絶縁膜 M Z は、絶縁膜 B T 、絶縁膜 H S O 1 、挿入層 A L 1 、絶縁膜 H S O 2 および絶縁膜 T P を有する積層膜である。

#### 【 0 0 6 9 】

まず、例えば I S S G ( In Situ Steam Generation ) 酸化法によって、半導体基板 S B 上に、例えば酸化シリコン膜である絶縁膜 B T を形成する。絶縁膜 B T は、例えば 2 n m ~ 5 n m の厚さを有する。その後、N O 处理またはプラズマ窒化処理を行うことで、酸化シリコン膜を窒化して、酸窒化シリコン膜としてもよい。

20

#### 【 0 0 7 0 】

次に、半導体基板 S B 上に、絶縁膜 B T を介して、絶縁膜 H S O 1 、挿入層 A L 1 および絶縁膜 H S O 2 を有する電荷蓄積層 C S L を形成する。

#### 【 0 0 7 1 】

例えば、L P C V D ( Low Pressure Chemical Vapor Deposition ) 法または A L D ( Atomic Layer Deposition ) 法によって、絶縁膜 B T 上に、ハフニウム ( H f ) 、シリコン ( S i ) および酸素 ( O ) を含む絶縁膜 H S O 1 を形成する。絶縁膜 H S O 1 は、例えば 5 n m ~ 9 n m の厚さを有する。また、絶縁膜 H S O 1 形成時の成膜温度は、例えば

30 200 ~ 500 である。

#### 【 0 0 7 2 】

次に、L P C V D 法または A L D 法によって、絶縁膜 H S O 1 上に、ハフニウムと異なる金属として、アルミニウム ( A l ) を含む挿入層 A L 1 を形成する。挿入層 A L 1 は、例えば 1 n m ~ 4 n m の厚さを有する。また、挿入層 A L 1 形成時の成膜温度は、例えば 200 ~ 500 である。

#### 【 0 0 7 3 】

次に、L P C V D 法または A L D 法によって、挿入層 A L 1 上に、ハフニウム ( H f ) 、シリコン ( S i ) および酸素 ( O ) を含む絶縁膜 H S O 2 を形成する。絶縁膜 H S O 2 は、挿入層 A L 1 と異なる材料からなり、絶縁膜 H S O 1 と同じ材料からなり、例えば 5 n m ~ 9 n m の厚さを有する。また、絶縁膜 H S O 2 形成時の成膜温度は、例えば 200 ~ 500 である。

40

#### 【 0 0 7 4 】

次に、L P C V D 法または A L D 法によって、電荷蓄積層 C S L 上に、アルミニウム ( A l ) および酸素 ( O ) を含む絶縁膜 T P を形成する。絶縁膜 T P は、絶縁膜 H S O 2 と異なる材料からなり、好ましくは酸化アルミニウム膜、酸窒化アルミニウム膜またはアルミニウムシリケート膜であり、例えば 5 n m ~ 10 n m の厚さを有する。また、絶縁膜 T P 形成時の成膜温度は、例えば 200 ~ 500 である。

#### 【 0 0 7 5 】

次に、主に、絶縁膜 H S O 1 、挿入層 A L 1 、絶縁膜 H S O 2 および絶縁膜 T P を結晶化させる目的で、例えば 800 ~ 1050 の熱処理を行う。この熱処理により、これら

50

の絶縁膜が、非晶質膜から多結晶膜となる。ここで、絶縁膜 H S O 1 および絶縁膜 H S O 2 が、 $Hf_xSi_1-xO_2$  ( $0.9 < x < 1$ ) 膜である場合には、熱処理の温度を 800 以上、975 未満とし、絶縁膜 H S O 1 および絶縁膜 H S O 2 が、 $Hf_xSi_1-xO_2$  ( $0 < x < 0.9$ ) 膜である場合には、熱処理の温度を 975 以上、1050 以下とする。このように熱処理の温度を調整することで、絶縁膜 H S O 1 および絶縁膜 H S O 2 を適切に結晶化させることができる。

#### 【 0 0 7 6 】

図 11 は、メモリゲート電極 M G の形成工程を示している。

#### 【 0 0 7 7 】

まず、例えば L P C V D 法によって、ゲート絶縁膜 M Z 上に、例えば多結晶シリコン膜のような導電性膜を形成する。次に、フォトリソグラフィ法およびイオン注入法によって、多結晶シリコン膜に、n 型の不純物を導入する。なお、この導電性膜は、p 型の不純物が導入された多結晶シリコン膜、または、不純物が導入されていない多結晶シリコン膜でもよい。また、この導電性膜は、例えば窒化チタン膜、アルミニウム膜若しくはタングステン膜のような金属膜、または、これらの金属膜の積層膜であってもよい。

10

#### 【 0 0 7 8 】

次に、フォトリソグラフィ法およびエッチング処理によって、上記導電性膜をパターニングし、メモリゲート電極 M G を形成する。その後、ドライエッチング処理およびウェットエッチング処理によって、メモリゲート電極 M G から露出しているゲート絶縁膜 M Z を除去する。

20

#### 【 0 0 7 9 】

図 12 は、エクステンション領域 E X S およびエクステンション領域 E X D の形成工程を示している。

#### 【 0 0 8 0 】

フォトリソグラフィ法およびイオン注入法によって、例えばヒ素 (As) またはリン (P) をメモリゲート電極 M G の横のウェル領域 P W 内に導入することで、n 型の不純物領域であるエクステンション領域 E X S およびエクステンション領域 E X D を形成する。エクステンション領域 E X S はメモリセル M C 1 のソース領域の一部を構成し、エクステンション領域 E X D はメモリセル M C 1 のドレイン領域の一部を構成する。

30

#### 【 0 0 8 1 】

図 13 は、サイドウォールスペーサ S W 、拡散領域 M S 、拡散領域 M D およびシリサイド層 S I の形成工程を示している。

#### 【 0 0 8 2 】

まず、メモリゲート電極 M G を覆うように、例えば L P C V D 法により、例えば窒化シリコン膜からなる絶縁膜を形成する。次に、この絶縁膜に対して異方性エッチングを行うことで、メモリゲート電極 M G の側面に、サイドウォールスペーサ S W を形成する。なお、サイドウォールスペーサ S W を構成する絶縁膜は、酸化シリコン膜と、酸化シリコン膜上に形成された窒化シリコン膜としてもよい。

#### 【 0 0 8 3 】

次に、フォトリソグラフィ法およびイオン注入法によって、サイドウォールスペーサ S W をマスクとして例えばヒ素 (As) またはリン (P) をウェル領域 P W 内に導入することで、n 型の不純物領域である拡散領域 M S および拡散領域 M D を形成する。拡散領域 M S は、エクステンション領域 E X S よりも高い不純物濃度を有し、エクステンション領域 E X S と接続し、メモリセル M C 1 のソース領域の一部を構成する。拡散領域 M D は、エクステンション領域 E X D よりも高い不純物濃度を有し、エクステンション領域 E X D と接続し、メモリセル M C 1 のドレイン領域の一部を構成する。

40

#### 【 0 0 8 4 】

次に、サリサイド (Salicide : Self Aligned Silicide) 技術により、拡散領域 M S 、拡散領域 M D およびメモリゲート電極 M G の各々の上面に、低抵抗のシリサイド層 S I を形成する。

50

**【 0 0 8 5 】**

シリサイド層 S I は、具体的には次のようにして形成することができる。まず、サイドウォールスペーサ S W、拡散領域 M S、拡散領域 M S およびメモリゲート電極 M G を覆うように、シリサイド層 S I 形成用の金属膜を形成する。この金属膜は、例えばコバルト、ニッケルまたはニッケル白金合金からなる。次に、半導体基板 S B に、例えば 300 ~ 500 の第 1 熱処理と、例えば 600 ~ 700 の第 2 熱処理とを施すことによって、拡散領域 M S、拡散領域 M D およびメモリゲート電極 M G に含まれる材料と、上記金属膜と反応させる。これにより、拡散領域 M S、拡散領域 M S およびメモリゲート電極 M G の各々の上面に、シリサイド層 S I が形成される。その後、未反応の金属膜を除去する。

**【 0 0 8 6 】**

以上のようにして、本実施の形態のメモリセル M C 1 が形成される。

**【 0 0 8 7 】**

図 13 の工程後、層間絶縁膜 I L 1、プラグ P G、層間絶縁膜 I L 2 および配線 M 1 を形成することで、図 1 に示される半導体装置が製造される。

**【 0 0 8 8 】**

まず、メモリセル M C 1 を覆うように、層間絶縁膜 I L 1 を形成する。層間絶縁膜 I L 1 としては、酸化シリコン膜の単体膜、または、窒化シリコン膜とその上に厚い酸化シリコン膜とを形成した積層膜などを用いることができる。層間絶縁膜 I L 1 の形成後、必要に応じて、層間絶縁膜 I L 1 の上面を CMP (Chemical Mechanical Polishing) 法で研磨してもよい。

**【 0 0 8 9 】**

次に、フォトリソグラフィ法およびドライエッチング法などによって、層間絶縁膜 I L 1 内にコンタクトホールを形成し、コンタクトホール内にタンゲステンなど主体とする導電性膜を埋め込むことで、層間絶縁膜 I L 1 内に複数のプラグ P G を形成する。複数のプラグ P G は、それぞれシリサイド層 S I を介して、拡散領域 M S および拡散領域 M D に接続される。なお、メモリゲート電極 M G もプラグ P G に接続されるが、本実施の形態ではその図示を省略する。

**【 0 0 9 0 】**

次に、プラグ P G が埋め込まれた層間絶縁膜 I L 1 上に層間絶縁膜 I L 2 を形成する。その後、層間絶縁膜 I L 2 に配線用の溝を形成した後、配線用の溝内に例えば銅を主成分とする導電性膜を埋め込むことで、層間絶縁膜 I L 2 内にプラグ P G に接続される配線 M 1 を形成する。この配線 M 1 の構造は、所謂ダマシン (Damascene) 配線構造と呼ばれる。

**【 0 0 9 1 】**

その後、デュアルダマシン (Dual Damascene) 法などにより、2 層目以降の配線を形成するが、ここではそれらの説明および図示は省略する。また、配線 M 1 および配線 M 1 よりも上層の配線は、ダマシン配線構造に限定されず、例えばタンゲステン膜またはアルミニウム膜をバーニングすることで形成してもよい。

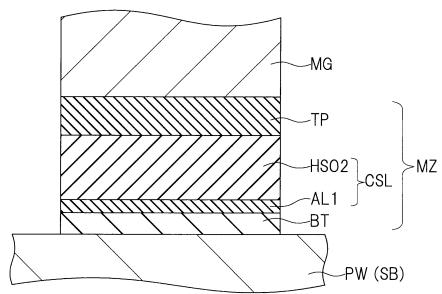

**【 0 0 9 2 】****(実施の形態 2 )**

以下に、実施の形態 2 の半導体装置を、図 14 を用いて説明する。なお、以下の説明では、実施の形態 1 との相違点を主に説明する。図 14 は、実施の形態 2 の半導体装置の要部を拡大した断面図であり、ゲート絶縁膜 M Z の詳細な構造を示す断面図である。

**【 0 0 9 3 】**

実施の形態 1 では、電荷蓄積層 C S L の内部において、ハフニウムシリケート膜 (絶縁膜 H S O 1、絶縁膜 H S O 2) の膜中に、1 層の酸化アルミニウム膜 (挿入層 A L 1) が形成されていた。すなわち、絶縁膜 H S O 1 と絶縁膜 H S O 2 との間に、挿入層 A L 1 が形成されていた。

**【 0 0 9 4 】**

図 14 に示されるように、実施の形態 2 では、電荷蓄積層 C S L は、絶縁膜 H S O 1 ~ H S O 3 を有し、絶縁膜 H S O 1 と絶縁膜 H S O 2 と間に挿入層 A L 1 を有し、絶縁膜 H S

10

20

30

40

50

O<sub>2</sub>と絶縁膜HSO<sub>3</sub>と間に挿入層AL<sub>2</sub>を有している。

【0095】

絶縁膜HSO<sub>3</sub>は、絶縁膜HOS<sub>1</sub>または絶縁膜HSO<sub>2</sub>と同じ材料からなる膜であり、ハフニウムシリケート膜などである。また、挿入層AL<sub>2</sub>は、ハフニウムと異なる金属を含む膜であり、挿入層AL<sub>1</sub>と同じ材料からなる膜であり、酸化アルミニウム膜などである。また、絶縁膜HSO<sub>3</sub>を形成する方法は、絶縁膜HSO<sub>1</sub>と同じであり、挿入層AL<sub>2</sub>を形成する方法は、挿入層AL<sub>1</sub>と同じである。

【0096】

このように、実施の形態2では、ハフニウム、シリコンおよび酸素を含む膜（絶縁膜HSO<sub>1</sub>～HSO<sub>3</sub>）の膜中に、2層のアルミニウムを含む膜（挿入層AL<sub>1</sub>、挿入層AL<sub>2</sub>）が形成されている。従って、ハフニウムシリケート膜と酸化アルミニウム膜との界面が、実施の形態1と比較して、2倍となる。このため、電荷蓄積層CSLの内部において、より多くのトラップ準位を存在させることができる。従って、メモリセルMC<sub>1</sub>のリテンション特性を更に改善させることができる。

10

【0097】

また、実施の形態2では、2層のアルミニウムを含む膜（挿入層AL<sub>1</sub>、挿入層AL<sub>2</sub>）を例示したが、3層以上のアルミニウムを含む膜を形成してもよい。

【0098】

例えば、実施の形態2のように、挿入層AL<sub>1</sub>の厚さを1nm～4nmに設定した場合、電荷蓄積層CSLは、最大で4層の酸化アルミニウム膜と、最大で5層のハフニウムシリケート膜とを有する。この場合、電荷蓄積層CSLの内部において、ハフニウムシリケート膜と酸化アルミニウム膜との界面の数は8つとなる。

20

【0099】

なお、実施の形態2の電荷蓄積層CSLは、実施の形態1よりも多くの膜を有することになるが、積層膜からなる電荷蓄積層CSLの合計の厚さが大きくなりすぎると、ゲート絶縁膜MZのEOTが増加することになる。従って、実施の形態2の電荷蓄積層CSLの厚さが、実施の形態1の電荷蓄積層CSLの厚さと同程度になるように、絶縁膜HSO<sub>1</sub>～HSO<sub>3</sub>、挿入層AL<sub>1</sub>および挿入層AL<sub>2</sub>の各々の厚さを調整することが好ましい。

【0100】

（実施の形態3）

30

以下に、実施の形態3の半導体装置を、図15および図16を用いて説明する。なお、以下の説明では、実施の形態1との相違点を主に説明する。図15は、実施の形態3の半導体装置の要部を拡大した断面図であり、ゲート絶縁膜MZの詳細な構造を示す断面図である。図16は、ゲート絶縁膜MZのうちの一部を拡大し、絶縁膜TPの詳細な構造を示す断面図である。

【0101】

実施の形態1では、トップ絶縁膜TPは、酸化アルミニウム膜などからなる単層膜であった。

【0102】

図15に示されるように、実施の形態3では、トップ絶縁膜TPは、電荷蓄積層CSL上に形成された絶縁膜TP<sub>1</sub>と、絶縁膜TP<sub>1</sub>上に形成された絶縁膜TP<sub>2</sub>と、絶縁膜TP<sub>2</sub>上に形成された絶縁膜TP<sub>3</sub>とを有する積層膜である。

40

【0103】

絶縁膜TP<sub>1</sub>は、窒化シリコン膜よりも高い誘電率を有する膜であり、絶縁膜HSO<sub>2</sub>と異なる材料からなる酸化金属膜であり、例えば2nm～5nmの厚さを有する。具体的に、絶縁膜TP<sub>1</sub>は、アルミニウム（Al）および酸素（O）を含む膜であり、好ましくは酸化アルミニウム膜、酸窒化アルミニウム膜またはアルミニウムシリケート膜であり、より好ましくはAl<sub>2</sub>O<sub>3</sub>膜である。また、絶縁膜TP<sub>1</sub>として、他の酸化金属膜を用いることもでき、例えば、チタン（Ti）、ジルコニア（Zr）、イットリウム（Y）、ランタン（La）、プラセオジム（Pr）またはルテチウム（Lu）の何れかの金属の酸化

50

物からなる酸化金属膜を、絶縁膜TP1として用いることもできる。

#### 【0104】

絶縁膜TP2は、絶縁膜TP1と異なる材料からなる膜であり、酸化シリコン膜、酸窒化シリコン膜または窒化シリコン膜であり、例えば1nm～2nmの厚さを有する。このような絶縁膜TP2は、例えばLPCVD法またはALD法によって形成することができる。

#### 【0105】

絶縁膜TP3は、絶縁膜TP1と同じ材料からなる膜であり、例えば2nm～5nmの厚さを有する。また、絶縁膜TP1および絶縁膜TP3は、実施の形態1の絶縁膜TPと同じ方法で形成することができる。

#### 【0106】

絶縁膜TP1および絶縁膜TP3は、主に、電荷蓄積層CSLの内部に蓄積された電荷が、メモリゲート電極MGへ抜けることを防止する役目を果たす。このため、絶縁膜TP1および絶縁膜TP3は、絶縁膜HSO2を構成する絶縁膜よりもバンドギャップが大きい絶縁膜であることが好ましく、挿入層AL1よりも厚い厚さを有していることが好ましい。

#### 【0107】

実施の形態3では、絶縁膜TP1と絶縁膜TP3との間に、これらと異なる材料からなる絶縁膜TP2を形成している。このため、電荷蓄積層CSLの内部に蓄積された電荷が、絶縁膜TPを介して、メモリゲート電極MGへ抜けやすくなることを防止でき、メモリセルMC1のリテンション特性を改善させることができる。以下に、このような理由について説明する。

#### 【0108】

実施の形態1では、電荷蓄積層CSLとメモリゲート電極MGとの間には、絶縁膜TPのような酸化アルミニウム膜などからなる単層膜が形成されている。このとき、絶縁膜TPの内部において、大きな結晶粒(グレイン)が形成されていると、この結晶粒の外周を構成する粒界が、電荷蓄積層CSLとメモリゲート電極MGとを繋いでしまう。このため、粒界がリーケ経路となり、電荷蓄積層CSLの内部に蓄積された電荷が、メモリゲート電極MGへリークする恐れがある。

#### 【0109】

絶縁膜TP2は、主に、上記リーケ経路を分断するために設けられている。すなわち、図16に示されるように、絶縁膜TP1を構成する複数の結晶粒GR1と、絶縁膜TP3を構成する複数の結晶粒GR2とは、絶縁膜TP2によって分離されている。絶縁膜TP1および絶縁膜TP3は、それぞれ別々に形成されるため、絶縁膜TP1の粒界GB1の位置と、絶縁膜TP3の粒界GB2の位置とをずらすことができ、絶縁膜TP1の粒界GB1と絶縁膜TP3の粒界GB2とを分断することができる。

#### 【0110】

また、実施の形態1では、図10の工程時に熱処理を行うことにより、絶縁膜TPを結晶化していた。実施の形態3でも同じ熱処理を行うことで、非晶質膜であった絶縁膜TP1および絶縁膜TP3が結晶化され、多結晶膜となるが、絶縁膜TP2は、非晶質膜として残すこともできる。絶縁膜TP2が非晶質膜であることで、絶縁膜TP1の粒界GB1と絶縁膜TP3の粒界GB2とが、絶縁膜TP2を介して繋がる恐れを、より確実に防止できる。

#### 【0111】

このように、実施の形態3では、電荷蓄積層CSLとメモリゲート電極MGとの間において、絶縁膜TPの粒界に起因したリーケが発生することを抑制できる。従って、メモリセルMC1のリテンション特性を更に向上させることができ、半導体装置の信頼性を更に向かせることができる。

#### 【0112】

また、実施の形態3に開示した技術を、実施の形態2と組み合わせて用いることもできる。

#### 【0113】

(実施の形態4)

10

20

30

40

50

以下に、実施の形態4の半導体装置を図17～図19を用いて説明し、実施の形態4の半導体装置の製造方法を図20～図25を用いて説明する。なお、以下の説明では、実施の形態1との相違点を主に説明する。

#### 【0114】

実施の形態1のメモリセルMC1は、メモリゲート電極MGを有するシングルゲート型のメモリセルであった。

#### 【0115】

実施の形態4のメモリセルMC2は、メモリゲート電極MGだけでなく、メモリゲート電極MGと隣接する位置に制御ゲート電極CGを有するスプリットゲート型のメモリセルである。以下に、実施の形態4における不揮発性メモリセルであるメモリセルMC2を備える半導体装置について説明する。図17は、メモリセルMC2の断面図を示している。

10

#### 【0116】

##### <メモリセルMC2の構造>

図17に示されるように、半導体基板SBには、p型のウェル領域PWが形成されている。ウェル領域PW上には、ゲート絶縁膜GFが形成され、ゲート絶縁膜GF上には、制御ゲート電極CGが形成されている。ゲート絶縁膜GFは、例えば酸化シリコン膜であり、例えば2nm～5nmの厚さを有する。ゲート絶縁膜GFは、酸化シリコン膜に代えて、酸化ハフニウム膜などの酸化金属膜のような高誘電率膜であってもよい。制御ゲート電極CGは、例えばn型の不純物が導入された多結晶シリコン膜である。また、制御ゲート電極CGは、例えば窒化チタン膜、アルミニウム膜若しくはタンゲステン膜のような金属膜、または、これらの金属膜の積層膜であってもよい。

20

#### 【0117】

ウェル領域PW上、および、制御ゲート電極CGの一方の側面上には、ゲート絶縁膜MZが形成されている。実施の形態4のゲート絶縁膜MZは、実施の形態1のゲート絶縁膜MZと同じ構造である。なお、図17では、図面を見易くするために、ゲート絶縁膜MZを単層膜として図示しているが、実際には、図17の破線で囲まれた領域である拡大図のように、ゲート絶縁膜MZは、絶縁膜BT、絶縁膜HSO1、挿入層AL1、絶縁膜HSO2および絶縁膜TPを有する積層膜である。

#### 【0118】

制御ゲート電極CGの一方の側面上には、ゲート絶縁膜MZを介して、メモリゲート電極MGが形成されている。すなわち、制御ゲート電極CGとメモリゲート電極MGとの間には、ゲート絶縁膜MZのような絶縁膜が形成されており、制御ゲート電極CGは、メモリゲート電極MGと絶縁分離されている。メモリゲート電極MGの2つの側面のうち、制御ゲート電極CGと反対側の側面上、および、制御ゲート電極CGの他方の側面上には、サイドウォールスペーサSWが形成されている。

30

#### 【0119】

メモリゲート電極MG側のサイドウォールスペーサSWの下部のウェル領域PWには、n型の不純物領域であるエクステンション領域EXSが形成されており、制御ゲート電極CG側のサイドウォールスペーサSWの下部のウェル領域PWには、n型の不純物領域であるエクステンション領域EXDが形成されている。エクステンション領域EXSは、メモリセルMC2のソース領域の一部を構成し、エクステンション領域EXDは、メモリセルMC2のドレイン領域の一部を構成する。

40

#### 【0120】

メモリゲート電極MG側のサイドウォールスペーサSWに整合する位置のウェル領域PWには、n型の不純物領域である拡散領域MSが形成されており、制御ゲート電極CG側のサイドウォールスペーサSWに整合する位置のウェル領域PWには、n型の不純物領域である拡散領域MDが形成されている。拡散領域MSは、エクステンション領域EXSよりも高い不純物濃度を有し、エクステンション領域EXSに接続し、メモリセルMC2のソース領域の一部を構成する。拡散領域MDは、エクステンション領域EXDよりも高い不純物濃度を有し、エクステンション領域EXDに接続し、メモリセルMC2のドレイン領域

50

域の一部を構成する。

【 0 1 2 1 】

メモリゲート電極 M G 上、制御ゲート電極 C G 上、拡散領域 M S 上および拡散領域 M D 上には、シリサイド層 S I が形成されている。

【 0 1 2 2 】

なお、メモリセル M C 2 の上方には、実施の形態 1 と同様に、層間絶縁膜 I L 1 、プラグ P G 、層間絶縁膜 I L 2 および配線 M 1 などが形成されているが、ここではこれらの図示を省略している。

【 0 1 2 3 】

<メモリセル M C 2 の動作について>

10

次に、不揮発性メモリセルであるメモリセル M C 2 の動作例について、図 1 8 および図 1 9 を参照して説明する。なお、ここで説明するメモリセル M C 2 は、半導体装置内に存在している複数のメモリセル M C 2 のうち、選択メモリセルである。

【 0 1 2 4 】

図 1 8 は、不揮発性メモリのメモリセル M C 2 の等価回路図である。図 1 9 は、「書込」、「消去」および「読出」時におけるメモリセル M C 2 の各部位への電圧の印加条件の一例を示す表である。図 1 9 の表には、「書込」、「消去」および「読出」時のそれぞれにおいて、ドレイン領域である拡散領域 M D に印加される電圧 V d 、制御ゲート電極 C G に印加される電圧 V c g 、メモリゲート電極 M G に印加される電圧 V m g 、ソース領域である拡散領域 M S に印加される電圧 V s 、および、ウェル領域 P W に印加される電圧 V b が記載されている。

20

【 0 1 2 5 】

なお、図 1 9 の表に示したものは電圧の印加条件の好適な一例であり、これに限定されるものではなく、必要に応じて種々変更可能である。また、実施の形態 4 では、電荷蓄積層 C S L への電子の注入を「書込」と定義し、電荷蓄積層 C S L へのホール(正孔)の注入を「消去」と定義する。

【 0 1 2 6 】

書込動作は、S S I (Source Side Injection : ソースサイド注入) 方式と呼ばれる、ソースサイド注入によるホットエレクトロン注入を用いた書き込み方式によって行われる。例えば図 1 9 の「書込」の欄に示されるような電圧を、書き込みを行うメモリセル M C 2 の各部位に印加し、電荷蓄積層 C S L に電子を注入することで書き込みを行う。

30

【 0 1 2 7 】

この際、ホットエレクトロンは、メモリゲート電極 M G および制御ゲート電極 C G に覆われた箇所(チャネル領域)で発生し、メモリゲート電極 M G の下部の電荷蓄積層 C S L にホットエレクトロンが注入される。注入されたホットエレクトロンは、電荷蓄積層 C S L 中のトラップ準位に捕獲され、その結果、メモリゲート電極 M G を有するメモリトランジスタのしきい値電圧が上昇する。すなわち、メモリトランジスタは書き込み状態となる。

【 0 1 2 8 】

消去動作は、B T B T (Band-To-Band Tunneling : バンド間トンネル現象) 方式と呼ばれる、B T B T によるホットホール注入を用いた消去方式によって行われる。すなわち、B T B T により発生したホールを電荷蓄積層 C S L に注入することにより消去を行う。例えば図 1 9 の「消去」の欄に示されるような電圧を、消去を行うメモリセル M C 2 の各部位に印加し、B T B T 現象によりホールを発生させ、電界加速することで電荷蓄積層 C S L 中にホールを注入する。その結果、メモリトランジスタのしきい値電圧が低下する。すなわち、メモリトランジスタは消去状態となる。

40

【 0 1 2 9 】

読出動作には、例えば図 1 9 の「読出」の欄に示されるような電圧を、読み出しを行うメモリセル M C 2 の各部位に印加する。読み出し時のメモリゲート電極 M G に印加される電圧 V m g を、書き込み状態におけるメモリトランジスタのしきい値電圧と、消去状態におけるメモリトランジスタのしきい値電圧との間の値にすることで、書き込み状態または消去状態を判別

50

することができる。

**【 0 1 3 0 】**

実施の形態 4 のメモリセル M C 2 は、実施の形態 1 のメモリセル M C 1 と同様に、ゲート絶縁膜 M Z は、絶縁膜 B T 、絶縁膜 H S O 1 、挿入層 A L 1 、絶縁膜 H S O 2 および絶縁膜 T P を有する積層膜である。このため、実施の形態 4 においても、メモリセル M C 2 のリテンション特性を改善させることができ、半導体装置の信頼性を向上させることができる。

**【 0 1 3 1 】**

< メモリセル M C 2 の製造方法 >

以下に、図 2 0 ~ 図 2 5 を用いて、実施の形態 4 の半導体装置の製造方法を説明する。

10

**【 0 1 3 2 】**

まず、図 2 0 に示されるように、フォトリソグラフィ法およびイオン注入法をもちいて、半導体基板 S B に、 p 型のウェル領域 P W を形成する。

**【 0 1 3 3 】**

次に、例えば熱酸化法または I S S G 酸化法によって、例えば酸化シリコンからなるゲート絶縁膜 G F を形成する。その後、 N O 处理またはプラズマ窒化処理を行うことで、酸化シリコン膜を窒化して、酸窒化シリコン膜としてもよい。また、ゲート絶縁膜 G F として、例えば A L D 法によって、例えば酸化ハフニウム膜などの酸化金属膜を形成してもよい。

**【 0 1 3 4 】**

次に、ゲート絶縁膜 G F 上に、例えば C V D 法を用いて、例えば多結晶シリコン膜からなる導電性膜を堆積する。また、この導電性膜は、例えば窒化チタン膜、アルミニウム膜若しくはタングステン膜のような金属膜、または、これらの金属膜の積層膜であってもよい。次に、フォトリソグラフィ法およびドライエッチング法を用いて、導電性膜をパターニングする。これにより、導電性膜が加工されて制御ゲート電極 C G が形成される。次に、制御ゲート電極 C G から露出しているゲート絶縁膜 G F を除去することで、制御ゲート電極 C G 下にゲート絶縁膜 G F が残される。

20

**【 0 1 3 5 】**

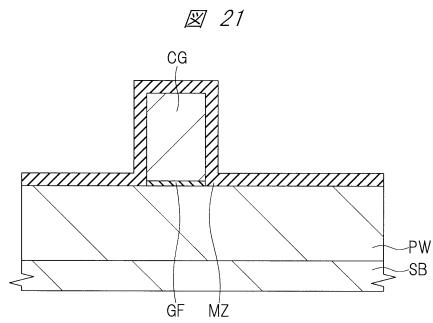

図 2 1 は、ゲート絶縁膜 M Z の形成工程を示している。

**【 0 1 3 6 】**

ウェル領域 P W 上、並びに、制御ゲート電極 C G の上面上および側面上に、絶縁膜 M Z を形成する。上述のように、ゲート絶縁膜 M Z は、絶縁膜 B T 、絶縁膜 H S O 1 、挿入層 A L 1 、絶縁膜 H S O 2 および絶縁膜 T P からなり、これらの絶縁膜の形成方法は、実施の形態 1 と同様である。

30

**【 0 1 3 7 】**

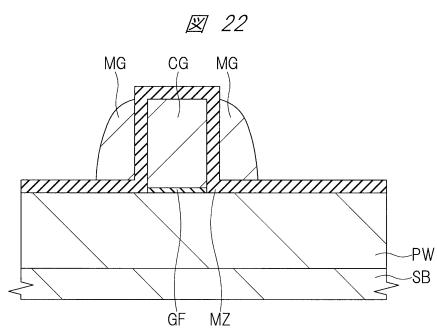

図 2 2 は、メモリゲート電極 M G の形成工程を示している。

**【 0 1 3 8 】**

まず、ゲート絶縁膜 M Z 上に、例えば C V D 法を用いて、例えば多結晶シリコンからなる導電性膜を堆積する。また、この導電性膜は、例えば窒化チタン膜、アルミニウム膜若しくはタングステン膜のような金属膜、または、これらの金属膜の積層膜であってもよい。次に、異方性エッチング処理を行い、導電性膜をサイドウォール状に加工することで、制御ゲート電極 C G の両側面に、ゲート絶縁膜 M Z を介して、導電性膜からなるメモリゲート電極 M G を形成する。

40

**【 0 1 3 9 】**

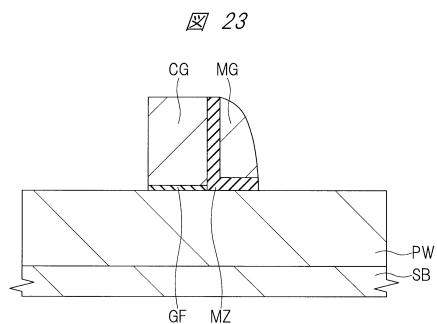

図 2 3 は、ゲート絶縁膜 M Z の一部およびメモリゲート電極 M G の一部の除去工程を示している。

**【 0 1 4 0 】**

まず、制御ゲート電極 C G の一方の側面に形成されているメモリゲート電極 M G を覆うレジストパターンを形成する。次に、このレジストパターンをマスクとして、ドライエッチング処理およびウェットエッチング処理を行うことで、レジストパターンに覆われていないゲート絶縁膜 M Z およびメモリゲート電極 M G を除去する。これにより、メモリセル M

50

C 2 のドレイン領域側のゲート絶縁膜 M Z およびメモリゲート電極 M G が除去され、メモリセル M C 2 のソース領域側のゲート絶縁膜 M Z およびメモリゲート電極 M G が残される。

【 0 1 4 1 】

図 2 4 は、エクステンション領域 E X D およびエクステンション領域 E X S の形成工程を示している。

【 0 1 4 2 】

フォトリソグラフィ法およびイオン注入法によって、例えばヒ素 ( A s ) またはリン ( P ) をウェル領域 P W 内に導入することで、n 型のエクステンション領域 E X D および n 型のエクステンション領域 E X S を形成する。エクステンション領域 E X D およびエクステンション領域 E X S は、制御ゲート電極 C G およびメモリゲート電極 M G に対して自己整合で形成される。

10

【 0 1 4 3 】

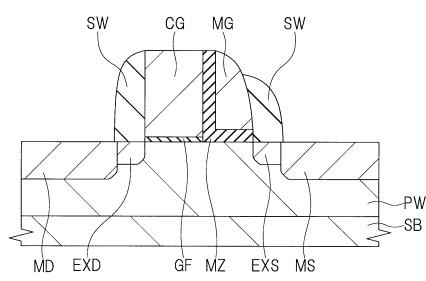

図 2 5 は、サイドウォールスペーサ S W 、拡散領域 M D および拡散領域 M S の形成工程を示している。

【 0 1 4 4 】

まず、メモリセル M C を覆うように、例えば C V D 法によって、例えば窒化シリコンからなる絶縁膜を形成する。次に、この絶縁膜に対して異方性ドライエッチング処理を行うことで、制御ゲート電極 C G の側面上およびメモリゲート電極 M G の側面上に、サイドウォールスペーサ S W が形成される。なお、サイドウォールスペーサ S W を構成する絶縁膜は、酸化シリコン膜と、酸化シリコン膜上に形成された窒化シリコン膜としてもよい。

20

【 0 1 4 5 】

次に、フォトリソグラフィ法およびイオン注入法によって、サイドウォールスペーサ S W をマスクとして例えばヒ素 ( A s ) またはリン ( P ) をウェル領域 P W 内に導入することで、n 型の拡散領域 M D および n 型の拡散領域 M S を形成する。

【 0 1 4 6 】

その後、実施の形態 1 と同様な方法によって、メモリゲート電極 M G 上、制御ゲート電極 C G 上、拡散領域 M S 上および拡散領域 M D 上に、シリサイド層 S I を形成することで、図 1 7 に示されるメモリセル M C 2 が製造される。

【 0 1 4 7 】

また、このような実施の形態 4 のメモリセル M C 2 に、実施の形態 2 および実施の形態 3 の技術を組み合わせて適用することもできる。

30

【 0 1 4 8 】

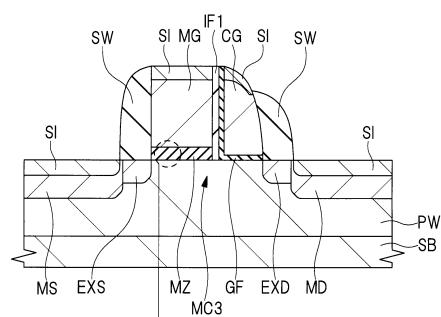

( 変形例 )

以下に、実施の形態 4 の変形例の半導体装置を、図 2 6 を用いて説明する。なお、以下の説明では、実施の形態 4 との相違点を主に説明する。

【 0 1 4 9 】

本変形例のメモリセル M C 3 は、実施の形態 4 のメモリセル M C 2 と同様に、メモリゲート電極 M G および制御ゲート電極 C G を有するスプリットゲート型のメモリセルである。実施の形態 4 では、先にゲート絶縁膜 G F および制御ゲート電極 C G を形成し、その後、ゲート絶縁膜 M Z およびメモリゲート電極 M G を形成していたが、本変形例では、これらを形成する順番が逆になっている。

40

【 0 1 5 0 】

以下に、図 2 6 を用いて、本変形例のメモリセル M C 3 を備える半導体装置について説明する。

【 0 1 5 1 】

図 2 6 に示されるように、ウェル領域 P W ( 半導体基板 S B ) 上には、ゲート絶縁膜 M Z が形成され、ゲート絶縁膜 M Z 上には、メモリゲート電極 M G が形成されている。メモリゲート電極 M G の一方の側面上には、絶縁膜 I F 1 が形成されている。絶縁膜 I F 1 は、例えば窒化シリコンまたは酸化シリコンからなる。ウェル領域 P W 上および絶縁膜 I F 1 上には、ゲート絶縁膜 G F が形成されている。絶縁膜 I F 1 が窒化シリコン膜である場合

50

には、図26に示されるように、ISSG酸化法によって形成されるゲート絶縁膜GFは、絶縁膜IF1上にも形成される。絶縁膜IF1が酸化シリコン膜である場合には、ゲート絶縁膜GFは、絶縁膜IF1上に形成されない。また、ゲート絶縁膜GFをALD法によって、酸化ハフニウム膜のような高誘電率膜で形成する場合、絶縁膜IF1が窒化シリコン膜または酸化シリコン膜の何れかであっても、ゲート絶縁膜GFは絶縁膜IF1上にも形成される。

#### 【0152】

メモリゲート電極MGの一方の側面上には、絶縁膜IF1およびゲート絶縁膜GFを介して、制御ゲート電極CGが形成されている。すなわち、制御ゲート電極CGとメモリゲート電極MGとの間には、少なくとも絶縁膜IF1のような絶縁膜が形成されており、制御ゲート電極CGは、メモリゲート電極MGと絶縁分離されている。10

#### 【0153】

ゲート絶縁膜MZ、メモリゲート電極MG、ゲート絶縁膜GFおよび制御ゲート電極CGの各々の構造および製造方法は、実施の形態4と同じである。

#### 【0154】

制御ゲート電極CGの2つの側面のうち、メモリゲート電極MGと反対側の側面上、および、メモリゲート電極MGの他方の側面上には、サイドウォールスペーサSWが形成されている。メモリゲート電極MG側のサイドウォールスペーサSWの下部のウェル領域PWには、n型の不純物領域であるエクステンション領域EXSが形成されており、制御ゲート電極CG側のサイドウォールスペーサSWの下部のウェル領域PWには、n型の不純物領域であるエクステンション領域EXDが形成されている。メモリゲート電極MG側のサイドウォールスペーサSWに整合する位置のウェル領域PWには、n型の不純物領域である拡散領域MSが形成されており、制御ゲート電極CG側のサイドウォールスペーサSWに整合する位置のウェル領域PWには、n型の不純物領域である拡散領域MDが形成されている。メモリゲート電極MG上、制御ゲート電極CG上、拡散領域MS上および拡散領域MD上には、シリサイド層SIが形成されている。20

#### 【0155】

なお、メモリセルMC3の等価回路図、並びに、「書込」、「消去」および「読出」の各動作電圧は、図18および図19と同様である。

#### 【0156】

このような本変形例においても、メモリセルMC3のリテンション特性を改善させることができ、半導体装置の信頼性を向上させることができる。30

#### 【0157】

以上、本発明者らによってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能である。

#### 【0158】

例えば、上述の実施の形態では、平坦な半導体基板SBに、メモリセルMC1～メモリセルMC3を形成する場合について説明したが、メモリセルMC1～メモリセルMC3をファイン構造としてもよい。すなわち、半導体基板SBの一部を凸状に加工して突出部を形成し、この突出部の上面および側面を覆うようにゲート絶縁膜MZを形成することで、メモリセルMC1～メモリセルMC3を設けても良い。40

#### 【符号の説明】

#### 【0159】

AL1、AL2 插入層

BT 絶縁膜(ボトム絶縁膜)

CG 制御ゲート電極

CSL 電荷蓄積層

EXD エクステンション領域

EXS エクステンション領域

10

20

30

40

50

G B 1、G B 2 粒界

G F ゲート絶縁膜

G R 1、G R 2 結晶粒

H O 絶縁膜

H S O 1 ~ H S O 3 絶縁膜

I F 1 絶縁膜

I L 1、I L 2 層間絶縁膜

M C 1 ~ M C 3 メモリセル

M D 拡散領域

M G メモリゲート電極

M S 拡散領域

M Z ゲート絶縁膜

P G プラグ

P W ウエル領域

S B 半導体基板

S I シリサイド層

S W サイドウォールスペーサ

T P 絶縁膜(トップ絶縁膜)

T P 1 ~ T P 3 絶縁膜

【図面】

【図1】

図 1

【図 2】

10

20

30

40

50

【図 3】

図 3

| 動作 | 印加電圧 | Vd  | Vmg | Vs  | Vb |

|----|------|-----|-----|-----|----|

| 書込 | -6V  | Vcc | -6V | -6V |    |

| 消去 | Vcc  | -6V | Vcc | Vcc |    |

| 読出 | Vcc  | Vcc | 0V  | 0V  |    |

Vcc = 1.5V

【図 4】

図 4

10

MC1:メモリセル MZ:ゲート絶縁膜 MG:メモリゲート電極

CSL:電荷蓄積層 HSO1:絶縁膜 HSO2:絶縁膜 AL1:挿入層

【図 5】

図 5

【図 6】

図 6

20

30

40

50

【図 7】

【図 8】

10

20

【図 9】

【図 10】

30

40

50

【図 1 1】

【図 1 2】

10

【図 1 3】

【図 1 4】

20

【図 1 5】

【図 1 6】

30

40

50

【図 17】

【図 18】

10

20

【図 19】

図 19

| 動作   | 印加電圧 | Vd   | Vcg | Vmg | Vs   | Vb |

|------|------|------|-----|-----|------|----|

| 書き込み | 0.5V | 0.5V | 1V  | 7V  | 3.5V | 0V |

| 消去   | 0V   | 0V   | 0V  | -5V | 5V   | 0V |

| 読み出し | Vcc  | Vcc  | 0V  | 0V  | 0V   | 0V |

Vcc = 1.5V

【図 20】

30

40

50

【図 2 1】

【図 2 2】

10

【図 2 3】

【図 2 4】

20

30

40

50

【図25】

図25

【図26】

図26

10

20

【図27】

図27

【図28】

図28

30

40

50

【図 2 9】

図 29

10

20

30

40

50

---

フロントページの続き

東京都千代田区丸の内一丁目6番6号 株式会社日立製作所内

審査官 小山 満

(56)参考文献 特開2015-053474 (JP, A)

特開2008-244163 (JP, A)

米国特許出願公開第2015/0060991 (US, A1)

欧州特許出願公開第02846348 (EP, A1)

米国特許出願公開第2008/0237688 (US, A1)

(58)調査した分野 (Int.Cl., DB名)

H01L 27/11568

H01L 21/336

H01L 29/788

H01L 29/792