(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4615810号

(P4615810)

(45) 発行日 平成23年1月19日(2011.1.19)

(24) 登録日 平成22年10月29日(2010.10.29)

(51) Int.Cl.

G06F 9/34 (2006.01)

F 1

G06F 9/36 330B

請求項の数 23 (全 25 頁)

(21) 出願番号 特願2001-552212 (P2001-552212)

(86) (22) 出願日 平成12年7月19日 (2000.7.19)

(65) 公表番号 特表2003-519869 (P2003-519869A)

(43) 公表日 平成15年6月24日 (2003.6.24)

(86) 國際出願番号 PCT/US2000/019770

(87) 國際公開番号 WO2001/052059

(87) 國際公開日 平成13年7月19日 (2001.7.19)

審査請求日 平成19年4月24日 (2007.4.24)

(31) 優先権主張番号 09/483,078

(32) 優先日 平成12年1月14日 (2000.1.14)

(33) 優先権主張国 米国(US)

(73) 特許権者 591016172

アドバンスト・マイクロ・ディバイシズ・

インコーポレイテッド

ADVANCED MICRO DEVICES INCORPORATED

アメリカ合衆国、94088-3453

カリフォルニア州、サンディベイル、ビィ・

オウ・ボックス・3453、ワン・エイ・

エム・ディ・ブレイス、メイル・ストップ

・68 (番地なし)

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

最終頁に続く

(54) 【発明の名称】 64ビットアドレス指定のための呼出ゲート拡張

## (57) 【特許請求の範囲】

## 【請求項1】

プロセッサであって、

セグメントセレクタを特定する分岐命令を実行するように構成される実行コアを含み、

前記プロセッサは、前記セグメントセレクタに応答してセグメント記述子テーブルから

少なくとも第1のエントリを読出るように構成され、前記第1のエントリが呼出ゲート記

述子を指示するならば、前記プロセッサは、前記第1のエントリおよび前記セグメント記

述子テーブル内の第2のエントリから、前記呼出ゲート記述子を読み出すように構成され

ており、前記第1のエントリと前記第2のエントリとの各々は別個にセグメント記述子を

記憶することが可能である、プロセッサ。

## 【請求項2】

前記プロセッサはさらに前記呼出ゲート記述子からオフセットを抽出するように構成さ

れ、前記オフセットの少なくとも第1の部分は前記第1のエントリ内に記憶され、前記オ

フセットの残りの部分は前記第2のエントリ内に記憶される、請求項1に記載のプロセッ

サ。

## 【請求項3】

前記オフセットは64ビットである、請求項2に記載のプロセッサ。

## 【請求項4】

前記プロセッサは前記呼出ゲート記述子からターゲットセグメントセレクタを抽出する

ように構成され、前記ターゲットセグメントセレクタはターゲットセグメント記述子を識

別する、請求項 1 に記載のプロセッサ。

【請求項 5】

前記ターゲットセグメント記述子は第 1 の動作モード指示を含み、前記第 1 の動作モード指示は 32 ビットよりも大きなデフォルトアドレスサイズを確立する、請求項 4 に記載のプロセッサ。

【請求項 6】

前記第 2 のエントリはタイプフィールドを含み、前記タイプフィールドは符号化されて前記第 2 のエントリが無効であることが示される、請求項 1 に記載のプロセッサ。

【請求項 7】

前記プロセッサは、前記第 2 のエントリをセグメント記述子として読出すことに応答して、前記タイプフィールドを用いて前記第 2 のエントリが無効であることを検出するよう構成される、請求項 6 に記載のプロセッサ。 10

【請求項 8】

方法であって、

プロセッサがセグメント記述子テーブルから呼出ゲート記述子を読出すステップを含み、前記呼出ゲート記述子は前記セグメント記述子テーブル内に第 1 のエントリと第 2 のエントリとを含み、前記第 1 のエントリと前記第 2 のエントリとの各々は、別個に、セグメント記述子を記憶することが可能であり、前記方法はさらに、

前記プロセッサが前記呼出ゲート記述子からオフセットを抽出するステップを含み、前記オフセットは、実行されるべき第 1 の命令をターゲットコードセグメント内に位置付ける、方法。 20

【請求項 9】

前記オフセットは 64 ビットである、請求項 8 に記載の方法。

【請求項 10】

前記プロセッサが前記セグメント記述子テーブルの第 3 のエントリのみから第 1 のセグメント記述子を読出すステップをさらに含む、請求項 8 に記載の方法。

【請求項 11】

前記プロセッサが前記呼出ゲート記述子からターゲットセグメントセレクタを抽出するステップをさらに含み、前記ターゲットセグメントセレクタはターゲットセグメント記述子を識別する、請求項 8 に記載の方法。 30

【請求項 12】

前記プロセッサが前記ターゲットセグメント記述子を読出すステップをさらに含み、前記ターゲットセグメント記述子は 32 ビットよりも大きなデフォルトアドレスサイズを確立する、請求項 11 に記載の方法。

【請求項 13】

前記第 1 のエントリと前記第 2 のエントリとの各々はタイプフィールドを有する、請求項 8 に記載の方法。

【請求項 14】

前記プロセッサが前記第 2 のエントリ内の前記タイプフィールドをセットして無効を示すステップをさらに含む、請求項 13 に記載の方法。 40

【請求項 15】

前記プロセッサが前記第 1 のエントリ内の前記タイプフィールドをセットして呼出ゲート記述子を指示するステップをさらに含む、請求項 14 に記載の方法。

【請求項 16】

前記プロセッサが前記第 2 のエントリからセグメント記述子を読出すことを試みるステップと、

前記プロセッサが前記第 2 のエントリ内の前記タイプフィールドに応答して前記セグメント記述子が無効であることを判断するステップとをさらに含む、請求項 14 に記載の方法。

【請求項 17】

50

コンピュータシステムであって、

プロセッサを含み、前記プロセッサは、

セグメントセレクタを特定する分岐命令を実行するように構成される実行コアを含み、

前記プロセッサは前記セグメントセレクタに応答してセグメント記述子テーブルから少

なくとも第1のエントリを読出すように構成され、前記第1のエントリが呼出ゲート記述

子を指示するならば、前記プロセッサは、前記第1のエントリおよび前記セグメント記述

子テーブル内の第2のエントリから、前記呼出ゲート記述子を読み出すように構成されて

おり、前記第1のエントリと前記第2のエントリとの各々は別個にセグメント記述子を記憶

することが可能であり、前記コンピュータシステムはさらに、

入力／出力（I／O）デバイスを含み、前記入力／出力（I／O）デバイスは、前記コン

ピュータシステムと、前記I／Oデバイスが結合可能な別のコンピュータシステムとの間で通信が行なわれるよう構成される、コンピュータシステム。 10

【請求項18】

前記I／Oデバイスはモデムを含む、請求項17に記載のコンピュータシステム。

【請求項19】

第2のプロセッサをさらに含み、前記第2のプロセッサは、

セグメントセレクタを特定する分岐命令を実行するように構成される実行コアを含み、

前記プロセッサは、前記セグメントセレクタに応答してセグメント記述子テーブルから少

なくとも第1のエントリを読出すように構成され、前記第1のエントリが呼出ゲート記述

子を指示するならば、前記セグメント記述子テーブル内の第2のエントリが前記呼出ゲ

ート記述子の残りの部分を記憶する、請求項17に記載のコンピュータシステム。 20

【請求項20】

セグメントセレクタに応答してセグメント記述子テーブルからセグメント記述子を読出

すように構成される回路を含むプロセッサであって、

前記セグメント記述子は、前記セグメント記述子のタイプを識別するタイプフィールド

を含み、前記セグメント記述子のタイプに応答して、前記回路は、(i)前記セグメント

記述子テーブルの第1のエントリおよび第2のエントリ、または、(ii)前記セグメン

ト記述子テーブルの第1のエントリのみ、のいずれかから前記セグメント記述子を読出

すように構成される、プロセッサ。

【請求項21】

前記タイプが呼出ゲート記述子を指示するならば、前記回路は前記第1のエントリおよ

び前記第2のエントリを読出すように構成され、前記タイプが前記呼出ゲート記述子では

ない第1のセグメント記述子を指示するならば、前記回路は前記第1のエントリのみを読

出すように構成される、請求項20に記載のプロセッサ。 30

【請求項22】

前記回路は前記セグメント記述子からオフセットを抽出するように構成され、前記セグ

メント記述子の前記タイプが、前記セグメント記述子が前記第1のエントリおよび前記第

2のエントリ内に記憶されることを指示するならば、前記オフセットの第1の部分は前記

第1のエントリにあり、前記オフセットの第2の部分は前記第2のエントリにある、請求

項20に記載のプロセッサ。 40

【請求項23】

前記タイプフィールドが前記第1のエントリにあり、前記第2のエントリにあるタイプ

フィールドと同じ位置が無効タイプにコーディングされる、請求項20に記載のプロセッ

サ。

【発明の詳細な説明】

【0001】

【発明の分野】

この発明はプロセッサの分野に関し、より具体的には、プロセッサ内のアドレスサイズお

よびオペランドサイズに関する。

【0002】

10

20

30

40

50

**【関連技術の説明】**

×86アーキテクチャ（IA-32アーキテクチャとしても知られる）は市場で広く受け入れられ、成功を享受してきた。したがって、×86アーキテクチャに従ってプロセッサを設計することが有利である。このようなプロセッサは、×86アーキテクチャに書込まれた大量のソフトウェアから利益を得ることができる（このようなプロセッサはソフトウェアを実行でき、そのプロセッサを採用するコンピュータシステムは大量の利用可能なソフトウェアのために市場でより広く受け入れられ得るからである）。

**【0003】**

コンピュータシステムは進化し続けてきたため、64ビットアドレスサイズ（時としてオペランドサイズ）が望ましいものとなった。より大きなアドレスサイズによって、より大きなメモリフットプリント（プログラムによって動作させられるデータおよびプログラム内の命令によって占有されるメモリの量）を有するプログラムがメモリースペース内で動作することが可能となる。より大きなオペランドサイズによって、より大きなオペランド上で、より正確にはオペランド内での動作が可能となる。64ビットアドレスおよび／またはオペランドサイズを用いると、より高性能なアプリケーションおよび／またはオペレーティングシステムが可能となり得る。

10

**【0004】**

残念ながら、×86アーキテクチャは最大32ビットオペランドサイズおよび32ビットアドレスサイズに限定されている。オペランドサイズとは、プロセッサによって動作させられるビットの数（たとえば、ソースまたはデスティネーションオペランド内のビット数）を指す。アドレスサイズとは、プロセッサが生成するアドレス内のビットの数を指す。したがって、×86アーキテクチャを採用するプロセッサは、64ビットアドレスサイズまたはオペランドサイズから利益を得ることができるアプリケーションのニーズを満たさないおそれがある。

20

**【0005】****【発明の概要】**

上述の問題は、ここで説明されるようなプロセッサによって大部分が解決される。そのプロセッサは、アドレスサイズが32ビットよりも大きい第1の処理モードをサポートする。アドレスサイズは公称64ビットとして示され得るが、プロセッサの種々の実施例は、32ビットよりも大きく64ビット以下のあらゆるアドレスサイズを第1の処理モードで実現し得る。第1の処理モードは、制御レジスタ内のイネーブル指示をイネーブル状態にし、さらにはセグメント記述子内の第1の動作モード指示および第2の動作モード指示を予め規定された状態にセットする(set)ことによって、確立され得る。×86プロセッサアーキテクチャとの互換ができる32ビットおよび16ビット処理のための互換モードが提供されるように、（イネーブル指示はイネーブル状態のままで）第1の動作モード指示と第2の動作モード指示との他の組合せが用いられ得る。

30

**【0006】**

イネーブル指示を介して第1の処理モードがイネーブルにされている間に互換モードは32ビットまたは16ビットコードが実行されることを可能にし得るが、第1の処理モード内で動作するコードを32ビットまたは16ビットコードから呼出すことが望ましいだろう。たとえば、アプリケーションプログラムが32ビットまたは16ビットモードで動作し得る間、オペレーティングシステムは第1の処理モードで動作し得る。セグメント記述子テーブル内で2つのエントリを占有する呼出ゲート記述子が規定される。そうでない場合には2つのエントリの各々がセグメント記述子を記憶し得る、その2つのエントリを占有することによって、呼出ゲート記述子は32ビットを超えるアドレスを記憶するのに十分なスペースを含み得る。したがって、呼出コードセグメントが呼出ゲート記述子を参照し得るが、これはターゲットコードセグメントを参照し、さらにはターゲットコードセグメントのアドレススペース内でアドレスを提供し得る。以上のことは、たとえそのアドレスが呼出コードセグメント内でのアドレスサイズを超えていたとしても行なわれ得る。さらに、呼出ゲート記述子に2つのエントリを占有させることによって、セグメント記述子

40

50

テーブルは、互換モードセグメントのためのセグメント記述子を記憶し続け得る。したがって、呼出ゲート記述子および互換モードセグメント記述子はセグメント記述子テーブル内で共存し得る。加えて、呼出ゲート記述子が占有する第2のエントリ内のタイプフィールドであり得る区域を無効タイプにコーディングしてもよく、コードセグメントのための第2のエントリを誤って用いることによって、結果としてプロセッサが例外を知らせることになり得る。

#### 【0007】

概して、プロセッサが企図される。プロセッサは、セグメントセレクタを特定する分岐命令を実行するように構成される実行コアを含む。プロセッサは、セグメントセレクタに応答してセグメント記述子テーブルから少なくとも第1のエントリを読出すように構成され

10 、第1のエントリが呼出ゲート記述子を指示する(indicate)と、セグメント記述子テーブル内の第2のエントリが呼出ゲート記述子の残りの部分を記憶する。加えて、コンピュータシステムが企図され、これは、コンピュータシステムとI/Oデバイスが結合可能な別のコンピュータシステムとの間の通信が行なわれるよう構成される入力／出力(I/O)

）デバイスおよびプロセッサを含む。

#### 【0008】

さらに、方法が企図される。呼出ゲート記述子はセグメント記述子テーブルから読出される。呼出ゲート記述子はセグメント記述子テーブル内に第1のエントリと第2のエントリとを含み、第1のエントリと第2のエントリとの各々はセグメント記述子を記憶することが可能である。オフセットが呼出ゲート記述子から抽出される。オフセットは、実行されるべき第1の命令をターゲットコードセグメント内に位置付ける。

20

#### 【0009】

以下の詳細な説明を読み、さらには添付の図を参照することによって、この発明の他の目的および利点が明らかとなるだろう。

#### 【0010】

この発明には種々の変形および代替の形が可能であるが、その具体的な実施例は図における例によって示され、ここで詳細に説明される。しかし、図およびそれに対する詳細な説明は、この発明を開示されたある特定の形に限定することを意図するものではなく、逆に、追加の請求項によって規定されるようなこの発明の思想および範囲内にあるすべての変形、均等物、および代替物を包含することが意図されることが理解されるべきである。

30

#### 【0011】

##### 【好ましい実施例の詳細な説明】

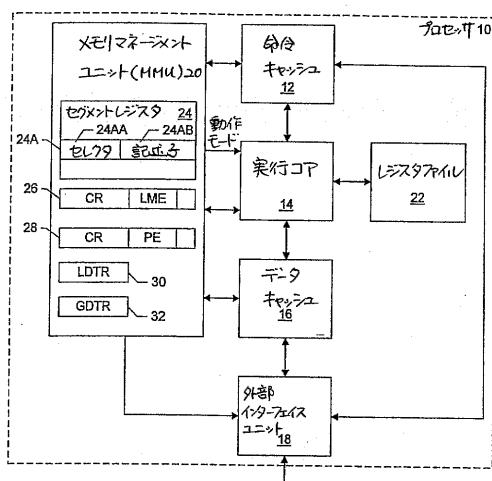

図1を参照して、プロセッサ10のある実施例を例示するブロック図が示される。他の実施例も可能であり、企図される。図1の実施例では、プロセッサ10は、命令キャッシュ12、実行コア14、データキャッシュ16、外部インターフェイスユニット18、メモリマネジメントユニット(MMU)20、およびレジスタファイル22を含む。例示される実施例では、MMU20は、1組のセグメントレジスタ24、第1の制御レジスタ26、第2の制御レジスタ28、ローカル記述子テーブルレジスタ(LDT R)30、およびグローバル記述子テーブルレジスタ(GDT R)32を含む。命令キャッシュ12は、外部インターフェイスユニット18、実行コア14、およびMMU20に結合される。実行コア14はさらに、MMU20、レジスタファイル22、およびデータキャッシュ16に結合される。データキャッシュ16はさらに、MMU20と外部インターフェイスユニット18とに結合される。外部インターフェイスユニット18はさらに、MMU20と外部インターフェイスとに結合される。

40

#### 【0012】

一般に、プロセッサ10は、×86アーキテクチャと互換性があり、かつ64ビット処理をサポートするための追加のアーキテクチャ特徴を含む、プロセッサアーキテクチャを採用する。プロセッサ10は、現在実行されているコードに対応するコードセグメント記述子内に記憶された情報に応答して、さらには1つ以上の制御レジスタ内に記憶された1つ以上のイネーブル指示に応答して、動作モードを確立するように構成される。ここで用い

50

られるように、「動作モード」はプログラム的に選択可能な種々のプロセッサ属性のためのデフォルト値を指定する。たとえば、動作モードは、デフォルトオペランドサイズとデフォルトアドレスサイズとを指定し得る。デフォルトオペランドサイズは、命令の符号化がデフォルトをオーバーライドしない限りは、命令のオペランド内のビット数を指定する。デフォルトアドレスサイズは、命令の符号化がデフォルトをオーバーライドしない限りは、命令のメモリオペランドのアドレス内のビット数を指定する。デフォルトアドレスサイズは、メモリオペランドの少なくとも仮想アドレスサイズを指定し、また物理アドレスサイズも指定し得る。代替的には、物理アドレスサイズは、デフォルトアドレスサイズから独立していてもよく、代わりに以下で説明される L M E ビットに依存し得るか(たとえば、物理アドレスは、L M E ビットがクリア(clear)ならば、3 2 ビットであり得るが、L M E ビットがセットされている(set)ならば、3 2 ビットよりも大きく6 4 ビットよりも小さい実現例によって異なるサイズであり得る)、または別の制御ビット(たとえば、別の制御レジスタ内の物理アドレス拡張ビットまたはP A E ビット)に依存し得る。ここで用いられるように、「仮想アドレス」とは、メモリにアクセスするために実際に用いられるアドレスである「物理アドレス」へとアドレス変換メカニズム(たとえば、ページングメカニズム)によって変換される前に生成されるアドレスである。加えて、ここで用いられるように、「セグメント記述子」とは、メモリのセグメントのための状況およびアクセスコントロールを規定するためにソフトウェアが作成し、かつプロセッサが用いるデータ構造である。「セグメント記述子テーブル」とは、多数のエントリを有するメモリ内のテーブルであり、各エントリはセグメント記述子を記憶することが可能である。

10

**【 0 0 1 3 】**

例示される実施例では、M M U 2 0 は動作モードを生成し、その動作モードを実行コア1 4 に伝達する。実行コア1 4 は、動作モードを用いて命令を実行する。より具体的には、実行コア1 4 は、(メモリオペランドがキャッシュ可能でデータキャッシュ1 6 でヒットするならばデータキャッシュ1 6 を通して、またはメモリオペランドがキャッシュ不可能でデータキャッシュ1 6 でミスとなるならば外部インターフェイスユニット1 8 を通して)レジスタファイル2 2 またはメモリからデフォルトオペランドサイズを有するオペランドを取出すが、以上は、ある特定の命令の符号化がデフォルトオペランドサイズをオーバーライドする場合以外のことであり、オーバーライドする場合には、オーバーライドする(overriding)オペランドサイズが用いられる。同様に、実行コア1 4 は、アドレスがデフォルトアドレスサイズを有する、メモリオペランドのアドレスを生成するが、これはある特定の命令の符号化がデフォルトアドレスサイズをオーバーライドしない限りにおいてのことであり、オーバーライドする場合には、オーバーライドするアドレスサイズが用いられる。他の実施例では、動作モードを用いるプロセッサ1 0 の部分(たとえば、実行コア1 4 )内で、動作モードを生成するために用いられる情報を局所的にバックアップ(shadow)することもでき、動作モードは局所的なシャドーコピー(shadow copies)から決定され得る。

20

**【 0 0 1 4 】**

上述のように、M M U 2 0 は、実行されているコードに対応するコードセグメント記述子に応答して、さらには制御レジスタ内の1つ以上の値に応答して、動作モードを生成する。コードセグメント記述子からの情報がセグメントレジスタ2 4 のうちの1つ(C S またはコードセグメントと呼ばれるレジスタ)の中に記憶される。加えて、制御レジスタ2 6 は、デフォルトアドレスサイズが3 2 ビットよりも大きい動作モード(「3 2 / 6 4 モード」と、3 2 ビットおよび1 6 ビット動作モードのある特定の互換モードとをイネーブルするために用いられるイネーブル指示(L M E )を記憶する。デフォルトオペランドサイズは3 2 / 6 4 モードでは3 2 ビットであり得るが、所望ならば命令が6 4 ビットオペランドサイズでデフォルト3 2 ビットオペランドサイズをオーバーライドし得る。L M E 指示がイネーブル状態ならば、3 2 ビットモードおよび1 6 ビットモードに加えて3 2 / 6 4 モードが用いられ得る。L M E 指示がディセーブル状態ならば、3 2 / 6 4 ビットはディセーブルにされる。ある実施例では、3 2 / 6 4 モードでのデフォルトアド

30

40

50

レスサイズは、実現例に依存するものであり得るが、64ビット以下のいかなる値であってもよい。さらに、仮想アドレスのサイズは、所与の実現ではその実現での物理アドレスのサイズと異なり得る。

#### 【0015】

イネーブル指示は、イネーブル状態がビットのセットされた状態であり、かつディセーブル状態がビットのクリアにされた状態であるビットとしてここで説明され得ることが注目される。しかし、多数のビットが用いられる符号化と、イネーブル状態がクリア状態でありかつディセーブル状態がセット状態である符号化とを含む、他の符号化も可能である。したがって、この説明の残りの部分は、制御レジスタ26内のLME指示をLMEビットとして呼び、ここではイネーブル状態がセットであり、ディセーブル状態がクリアであり得る。しかし、上述のように、LME指示の他の符号化も企図される。10

#### 【0016】

セグメントレジスタ24は、プロセッサ10が実行しているコードが現在使っているセグメント記述子からの情報を記憶する。上述のように、CSは、セグメントレジスタ24のうちの1つであり、メモリのコードセグメントを指定する。コードセグメントは実行されているコードを記憶する。他のセグメントレジスタが種々のデータセグメントを規定し得る（たとえば、SSセグメントレジスタが規定するスタックデータセグメント、ならびにDSセグメントレジスタと、ESセグメントレジスタと、FSセグメントレジスタと、GSセグメントレジスタとが規定する最大4つのデータセグメント）。図1は例示的なセグメントレジスタ24Aの内容を例示し、これは、セレクタフィールド24AAおよび記述子フィールド24ABを含む。セレクタフィールド24AAは、実行コア14が実行する特定のセグメントロード命令に応答してセグメントセレクタでロードされてある特定のセグメントを活動化させる。セグメントセレクタは、メモリ内のセグメント記述子テーブルの中のセグメント記述子を識別する。より具体的には、プロセッサ10は2つのセグメント記述子テーブル、すなわち、ローカル記述子テーブルとグローバル記述子テーブルとを採用し得る。ローカル記述子テーブルの基底アドレスがLDR30内に記憶される。同様に、グローバル記述子テーブルの基底アドレスがGDR32内に記憶される。セグメントセレクタ内のあるビット（テーブルインディケータビット）が記述子テーブルを選択し、セグメントセレクタの残りが、選択されたテーブルへのインデックスとして用いられる。ある命令がセグメントセレクタをセグメントレジスタ24のうちの1つにロードすると、MMU20は、対応するセグメント記述子を選択されたセグメント記述子テーブルから読み出し、セグメント記述子からの情報をセグメント記述子フィールド（たとえば、セグメントレジスタ24Aのためのセグメント記述子フィールド24AB）に記憶する。セグメント記述子フィールド内に記憶される情報は、所望ならば、すべてのセグメント記述子を含む好適なあらゆるセグメント記述子のサブセットを含み得る。加えて、所望ならば、セグメント記述子または他のソースから引き出された他の情報がセグメント記述子フィールド内に記憶され得る。たとえば、ある実施例は、コードセグメント記述子から動作モード指示を復号化することもでき、動作モード指示の元の値というよりはむしろ復号化された値を記憶し得る。ある命令によってCSがセグメントセレクタでロードされると、コードセグメントは変化して、したがってプロセッサ10の動作モードが変化し得る。セグメント記述子テーブルは以下でより詳細に説明される。203040

#### 【0017】

ある実施例では、CSセグメントレジスタのみが32/64モードで用いられる。データセグメントレジスタは無視される。16ビットモードおよび32ビットモードでは、コードセグメントおよびデータセグメントが活動状態になり得る。さらに、制御レジスタ28内の第2のイネーブル指示（PE）がMMU20の動作に影響を及ぼし得る。PEイネーブル指示を用いて保護モードをイネーブルにすることもでき、ここではセグメンテーションおよび/またはページングアドレス変換メカニズムが用いられ得る。PEイネーブル指示がディセーブル状態にある場合には、セグメンテーションおよびページングメカニズムがディセーブルにされ、プロセッサ10は「実モード」となる（ここでは、実行コア1450

が生成するアドレスは物理アドレスである)。LME指示と同様に、PE指示は、イネーブル状態はセットされたビットで、かつディセーブル状態はクリアなビットである、ビットであり得る。しかし、上述のように他の実施例も企図される。

#### 【0018】

MMU20は、所望であれば、さらなるハードウェアメカニズムを採用し得ることが注目される。たとえば、MMU20は、仮想アドレスから物理アドレスへのページングアドレス変換を実現するためのページングハードウェアを含み得る。ページングハードウェアは、ページ変換を記憶するための変換ルックアサイドバッファ(TLB)を含み得る。

#### 【0019】

制御レジスタ26および28はアーキテクトされた制御レジスタとして実現され得る(たとえば、制御レジスタ26はCR4で、制御レジスタ28はCR0であり得る)ことが注目される。代替的には、制御レジスタのうちの1つまたは両者がモデル専用レジスタとして実現されて32/64モードに干渉することなしにアーキテクトされた制御レジスタの他の用途が可能にされてもよい。

10

#### 【0020】

一般に、命令キャッシュ12は、命令バイトを記憶するための高速キャッシュメモリである。実行コア14は、実行のために命令キャッシュ12から命令を取出す。命令キャッシュ12は、直接マッピング、セットアソシエティブ、および完全にアソシエティブな構成を含む、好適なあらゆるキャッシュ機構を採用し得る。命令の取出が命令キャッシュ12内でミスとなると、命令キャッシュ12は外部インターフェイスユニット18と通信してミッシングキャッシングラインを命令キャッシュ12へと入れる(fill)こともできる。加えて、命令キャッシュ12はMMU20と通信して命令キャッシュ12から取出された仮想アドレスのための物理アドレス変換を受取り得る。

20

#### 【0021】

実行コア14は命令キャッシュ12から取出された命令を実行する。実行コア14は、レジスタファイル22からレジスタオペランドを取り出し、レジスタファイル22内のデスティネーションレジスタを更新する。レジスタオペランドのサイズは、動作モードと、ある特定の命令のための動作モードのすべてのオーバーライドとによって制御される。同様に、実行コア14は、メモリオペランドのキャッシュ性(cacheability)およびデータキャッシュ16内でのヒットを条件として、データキャッシュ16からメモリオペランドを取り出し、データキャッシュ16内のデスティネーションメモリロケーションを更新する。メモリオペランドのサイズも同様に、動作モードと、ある特定の命令のための動作モードのすべてのオーバーライドとによって制御される。さらに、実行コア14が生成するメモリオペランドのアドレスのサイズは、動作モードと、ある特定の命令のための動作モードのすべてのオーバーライドとによって制御される。

30

#### 【0022】

実行コア14は好適なあらゆる構造を採用し得る。たとえば、実行コア14は、スーパーパイプラインコア、スーパースカラコア、またはそれらの組合せであり得る。実行コア14は、設計上の選択に従って、アウトオブオーダ投機的実行またはインオーダ実行を採用し得る。

40

#### 【0023】

レジスタファイル22は64ビットレジスタを含み得るが、これは、プロセッサ10の動作モードおよびある特定の命令のためのあらゆるオーバーライドによって指示されるように64ビットレジスタ、32ビットレジスタ、16ビットレジスタ、または8ビットレジスタとしてアクセスされてもよい。ある実施例のレジスタフォーマットが以下で図7に関して説明される。レジスタファイル22内に含まれるレジスタは、L E A X レジスタ、L E B X レジスタ、L E C X レジスタ、L E D X レジスタ、L E D I レジスタ、L E S I レジスタ、L E S P レジスタ、およびL E B P レジスタを含み得る。レジスタファイル22はさらにL E I P レジスタを含み得る。代替的には、実行コア14は、レジスタファイル22内のあらゆるレジスタがアーキテクトされたレジスタにマッピングされ得るレジスタ

50

リネームの形を採用してもよい。レジスタファイル 22 内のレジスタの数は、このような実施例については実現例によって異なり得る。

#### 【0024】

データキャッシュ 16 は、データを記憶するように構成された高速キャッシュメモリである。データキャッシュ 16 は、直接マッピング、セットアソシエティブ、および完全にアソシエティブな構成を含む、好適なあらゆるキャッシュ機構を採用し得る。データの取出または更新がデータキャッシュ 16 内でミスとなると、データキャッシュ 16 は外部インターフェイスユニット 18 と通信してデータキャッシュ 16 へとミッシングキャッシングラインを入れることもできる。加えて、データキャッシュ 16 がライトバックキャッシュポリシーを採用する場合には、データキャッシュ 16 から外に出される(cast out) 更新されるキャッシュラインが外部インターフェイスユニット 18 に伝達されてメモリにライトバックされ得る。データキャッシュ 16 は MMU 20 と通信してデータキャッシュ 16 に与えられる仮想アドレスのための物理アドレス変換を受取り得る。10

#### 【0025】

外部インターフェイスユニット 18 は、プロセッサ 10 の外部のシステムの部分と通信を行なう。外部インターフェイスユニット 18 は、上述のような命令キャッシュ 12 およびデータキャッシュ 16 のためにキャッシュラインを伝達し、MMU 20 とも通信を行ない得る。たとえば、外部インターフェイスユニット 18 は、MMU 20 に代わってセグメント記述子テーブルおよび / またはページングテーブルにアクセスし得る。20

#### 【0026】

所望ならば、プロセッサ 10 は統合レベル(integrated level) 2 (L2) キャッシュを含み得ることが注目される。さらに、外部インターフェイスユニット 18 は、システムとの通信に加えてバックサイドキャッシュと通信するように構成され得る。20

#### 【0027】

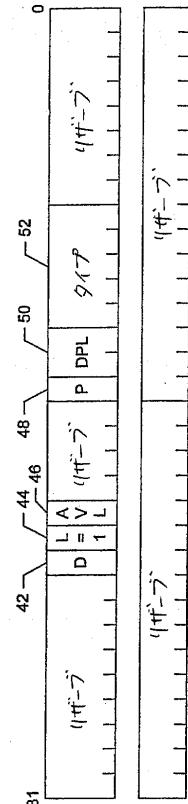

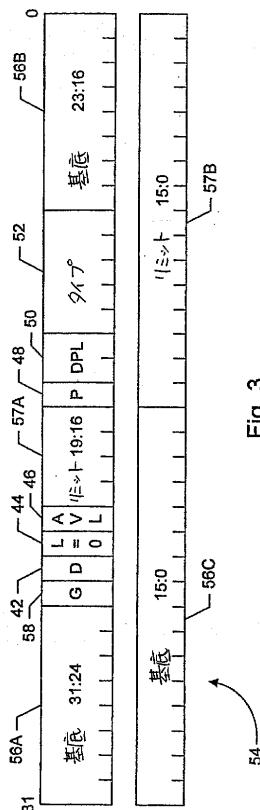

図 2 を参照して、32/64 モードのためのコードセグメント記述子 40 のある実施例のブロック図が示される。他の実施例も可能であり、企図される。図 2 の実施例では、コードセグメント記述子 40 は 8 バイトを含み、最下位 4 バイトの上方に最上位 4 バイトが例示される。最上位 4 バイトは最下位 4 バイトよりも数の上でより大きなアドレスに記憶される。4 バイトの各グループの最上位ビットは、図 2 (および以下の図 3) でビット 31 として示され、最下位ビットはビット 0 として示される。(図 2 および図 3 の両方において) 4 バイト内の短い垂直の線は各々のビットを区切り、長い垂直の線もビットを区切るが、それはまたフィールドも区切る。30

#### 【0028】

以下の図 3 で示される 32 ビットおよび 16 ビットコードセグメント記述子とは異なって、コードセグメント記述子 40 は基底アドレスまたはリミット(limit)を含まない。プロセッサ 10 は (32 ビットおよび 16 ビットモードで採用されるセグメント化されたリニアアドレススペースというよりはむしろ) 32/64 モードのためにフラット(flat)仮想アドレススペースを採用する。したがって、それ以外の場合には基底アドレスおよびリミットを記憶するであろうコードセグメント記述子 40 の部分は、セグメント記述子 40 内でリザーブされる。セグメントーションを通して提供される仮想アドレスはここで「リニアアドレス」とも呼ばれ得ることが注目される。「仮想アドレス」という用語は、セグメント化されていないアーキテクチャ内で生成される他の仮想アドレスおよびリニアアドレスを含む、メモリをアドレス指定するために実際に用いられる物理アドレスへと変換メカニズムを通して変換されるすべてのアドレスを含む。40

#### 【0029】

セグメント記述子 40 は、D ビット 42、(32/64 モードコードセグメントのために 1 にセットされる) L ビット 44、使用可能(available)ビット(AVL) 46、現在の(P)ビット 48、記述子特権レベル(DPL) 50、およびタイプフィールド 52 を含む。以下の図 5 で示されるように、D ビット 42 と L ビット 44 とはプロセッサ 10 の動作モードを決定するために用いられる。AVL ビット 46 は、システムソフトウェア(た50

とえば、動作システム)によって用いられることのために使用可能である。Pビット48が用いられてセグメントがメモリ内に存在するか否かが示される。Pビット48がセットされると、セグメントは存在し、コードがセグメントから取出され得る。Pビット48がクリアであると、セグメントは存在せず、例外が生じて(たとえば、ディスク記憶デバイスから、またはネットワーク接続を通して)セグメントがメモリへとロードされる。DPLはセグメントの特権レベルを示す。プロセッサ10は、(DPLフィールド内で0から3として符号化され、かつレベル0が最も特権を与えられたレベルである)4つの特権レベルを採用する。ある特定の命令およびプロセッサリソース(たとえば、構成レジスタおよび制御レジスタ)は、より特権を与えられたレベルでのみ実行可能またはアクセス可能であり、より低い特権レベルでこれらの命令を実行すること、またはこれらのリソースにアクセスすることを試みることによって、結果として例外が生じる。コードセグメント40からの情報がCSセグメントレジスタにロードされると、DPLがプロセッサ10の現在の特権レベル(CPL)となる。タイプフィールド52はセグメントのタイプを符号化する。コードセグメントでは、タイプフィールド52の最上位ビット2ビットがセットされ得る(最上位ビットはシステムセグメントからコードまたはデータセグメントを区別し、第2の最上位ビットはデータセグメントからコードセグメントを区別する)。残りのビットはさらなるセグメントタイプ情報(たとえば、実行専用、実行および読出、または実行および読出専用、コンフォーミング、およびコードセグメントがアクセスされたか否か)を符号化し得る。

## 【0030】

コードセグメント記述子内のいくつかの指示は、セットされた値およびクリアされた値が規定の意味を有するビットとして説明されるが、他の実施例は所望であれば反対の符号化を採用してもよく、多数のビットを用いてもよいことが注目される。したがって、たとえば、Dビット42とLビット44との各々は、上述のイネーブル指示の考察と同様に、所望であれば1つ以上のビットであり得る動作モード指示の例であり得る。

## 【0031】

図3を参照して、32および16ビット互換モードのためのコードセグメント記述子54のある実施例のブロック図が示される。他の実施例も可能であり、企図される。図2の実施例と同様に、コードセグメント記述子54も8バイトを含み、最下位4バイトの上方に最上位4バイトが示される。

## 【0032】

コードセグメント記述子54は、コードセグメント記述子40の上の説明と同様に、Dビット42、Lビット44、AVLビット46、Pビット48、DPL50、およびタイプフィールド52を含む。加えて、コードセグメント記述子54は、基底アドレスフィールド(参照番号56A、56B、および56C)、リミットフィールド(参照番号57Aおよび57B)、およびGビット58を含む。基底アドレスフィールドは、(LEIPレジスタ内に記憶される)ロジカル取出アドレスに加えられる基底アドレスを記憶してある命令のリニアアドレスを形成し、これは次に任意でページング変換メカニズムを通して物理アドレスに変換され得る。リミットフィールドは、セグメントのサイズを規定するセグメントリミットを記憶する。セグメントリミットよりも大きな論理アドレスのバイトにアクセスする試みは、認められず、例外を生じさせる。Gビット58はセグメントリミットフィールドのスケーリングを決定する。Gビット58がセットされると、リミットは4Kバイトページにスケーリングされる(たとえば、12の最下位0がリミットフィールド内のリミットに追加される)。Gビット58がクリアならば、リミットはそのまま用いられる。

## 【0033】

32/64モードが制御レジスタ26内のLMEビットを介してイネーブルにされていない時の32および16ビットモードのためのコードセグメント記述子は、Lビットがリザーブされていて0であるように規定されている以外は、コードセグメント記述子54と同様のものであり得ることが注目される。ある実施例に従った32ビットモードおよび16

10

20

30

40

50

ビットモード（ L M E ビットがセットされた互換モードと、 L M E ビットがクリアにされたモードとの両者）では、データセグメントも用いられることがさらに注目される。データセグメント記述子は、 D ビット 4 2 がセグメントの上限を指示するように規定されているか、または（スタックセグメントのための）デフォルトスタックサイズを定めるように規定されていること以外は、コードセグメント記述子 5 4 と同様のものであり得る。

#### 【 0 0 3 4 】

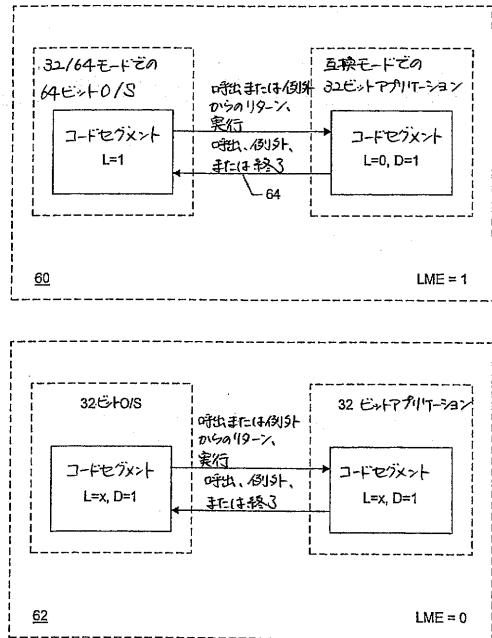

次に図 4 を参照して、制御レジスタ 2 6 内の L M E ビットと、 3 2 / 6 4 モード、ならびに 3 2 ビットモードおよび 1 6 ビットモードを実現する高度な柔軟性を可能にするための互換モードとの例示的な用途を例示する図が示される。ボックス 6 0 は L M E ビットがセットされているときの例示的な動作を示し、ボックス 6 2 は L M E ビットがクリアであるときの例示的な動作を示す。10

#### 【 0 0 3 5 】

ボックス 6 0 で示されるように、 L M E ビットがセットされているときにサポートされる互換モードは、 6 4 ビットオペレーティングシステム（つまり、 3 2 ビットを超える仮想アドレススペースおよび物理アドレススペース、および／または 6 4 ビットのデータオペランドを利用するように設計されるオペレーティングシステム）が 3 2 ビットアプリケーションプログラム（つまり、 3 2 ビットのオペランドサイズおよびアドレスサイズを用いて書込まれるアプリケーションプログラム）で動作することを可能にし得る。オペレーティングシステムのためのコードセグメントは、図 2 で示される 3 2 / 6 4 モードコードセグメント記述子 4 0 によって規定され得るため、 L ビットがセットされ得る。したがって、オペレーティングシステムは、（たとえば、セグメント記述子テーブルおよびページング変換テーブルを含む）オペレーティングシステムが維持するデータ構造およびオペレーティングシステムコードのために拡張された仮想アドレススペースおよび物理アドレススペースを利用することができます。オペレーティングシステムはまた、デフォルト 3 2 ビットオペランドサイズをオーバーライドする命令符号化を用いて 3 2 / 6 4 モードで規定される 6 4 ビットデータタイプを用いることもできる。さらに、オペレーティングシステムは、セグメント記述子テーブル内で 1 つ以上の 3 2 ビット互換モードセグメント記述子（クリアにされた L ビット、セットされた D ビット、たとえば、図 2 で示されるセグメント記述子 5 4 ）を確立し、さらには互換モードセグメントのうちの 1 つへと分岐することによって、 3 2 ビットアプリケーションプログラムを実行することもできる。同様に、オペレーティングシステムは、セグメント記述子テーブル内で 1 つ以上の 1 6 ビット互換モードセグメント記述子（クリアにされた L ビット、クリアにされた D ビット、たとえば、図 2 で示されるセグメント記述子 5 4 ）を確立させ、さらには互換モードセグメントのうちの 1 つへと分岐することによって、 1 6 ビットアプリケーションプログラムを実行することもできる。したがって、 6 4 ビットオペレーティングシステムは、互換モードで既存の 3 2 ビットアプリケーションプログラムおよび 1 6 ビットアプリケーションプログラムを実行するための能力を保持することができる。ある特定のアプリケーションプログラムは、拡張された能力がそのプログラムに望まれると 3 2 / 6 4 モードに移され得るか、または 3 2 ビットまたは 1 6 ビットのままであり得る。2030

#### 【 0 0 3 6 】

プロセッサ 1 0 が 3 2 ビットアプリケーションプログラムを実行している間、プロセッサ 1 0 の動作モードは 3 2 ビットである。したがって、アプリケーションプログラムは一般に、それが（たとえば、オペレーティングシステムも 3 2 ビットオペレーティングシステムである時） L M E ビットがクリアな状態で 3 2 ビットモードで実行されるのと同じ様で、実行され得る。しかし、アプリケーションプログラムは、オペレーティングシステムサービスを呼び出し、例外を経験するか、または終了し得る。これらの事例ごとに、プロセッサ 1 0 は（図 4 の矢印 6 4 で示されるように）オペレーティングシステムコードの実行に戻り得る。オペレーティングシステムコードは 3 2 / 6 4 モードで動作するため、オペレーティングシステムサービスルーチン、例外ハンドラ等のアドレスは 3 2 ビットを超える。したがって、プロセッサ 1 0 は、オペレーティングシステムコードに戻る前に 3 2 4050

ビットよりも大きなアドレスを生成する必要があり得る。LMEビットは、現在の動作モードがたとえ32ビットであったとしてもオペレーティングシステムは32/64モードで動作しているかもしれないという表示をプロセッサ10に提供し、このようにして、プロセッサ10は、オペレーティングシステム呼出および例外のためにより大きなアドレススペースを提供し得る。

#### 【0037】

ある実施例では、割込セグメント記述子テーブル内に記憶される割込セグメント記述子を用いて、例外が処理される。LMEビットがセットされていると、割込セグメント記述子は、例外を処理するオペレーティングシステムルーチンの64ビットアドレスを含む16バイトエントリであり得る。LMEビットがクリアであると、割込セグメント記述子は、32ビットアドレスを含む8バイトエントリであり得る。したがって、プロセッサ10はLME指示に応答して割込記述子テーブルにアクセスする(つまり、LMEビットがセットされていると16バイトエントリを読み出し、LMEビットがクリアであると8バイトエントリを読み出す)。したがって、例外は、たとえアプリケーションプログラムが32ビット互換モードで実行されても、64ビットオペレーティングシステムによって処理され得る。さらに、プロセッサ10は、LMEビットがクリアならば32ビット(または16ビット)オペレーティングシステムをサポートする。

#### 【0038】

同様に、プロセッサ10内の呼出メカニズムは、LMEビットの状態に基づいて異なった様で動作し得る。オペレーティングシステムは典型的にはアプリケーションプログラムよりもより高い特権レベルで実行されるため、アプリケーションプログラムからオペレーティングシステムへの転送(transfers)は、慎重に制御されてアプリケーションプログラムは許可されたオペレーティングシステムルーチンの実行のみ可能であることが確実にされる。より一般的には、特権レベルの変化は慎重に制御される。ある実施例では、プロセッサ10は、オペレーティングシステム呼出を行なうために少なくとも2つのメカニズムをサポートし得る。1つの方法は、(以下でより詳細に説明される)セグメント記述子テーブル内の呼出ゲートを通してのものであり得る。別の方法は、プロセッサ10がサポートするSYSCALL命令であり得るが、これはモデル専用レジスタをオペレーティングシステムルーチンのアドレスのソースとして用いる。モデル専用レジスタの更新は特権を与えられた動作であり、したがって、より高い特権レベルで実行されているコード(たとえば、オペレーティングシステムコード)のみが、SYSCALL命令によって用いられるモデル専用レジスタ内にアドレスを確立することができる。SYSCALL方法では、第2のモデル専用レジスタが、オペレーティングシステムルーチンのアドレスの最上位32ビットを記憶するように規定され得る。したがって、LMEビットがセットされていると、アドレスは2つのモデル専用レジスタから読み出され得る。LMEビットがクリアであると、アドレスは最下位32ビットを記憶するモデル専用レジスタから読み出され得る。代替的には、SYSCALL命令が用いるモデル専用レジスタは64ビットに拡張されてもよく、アドレスは、LMEビットの状態に基づいて32ビット(モデル専用レジスタの最下位32ビット)または64ビットであり得る。

#### 【0039】

上述のように、LMEビットをセットすることによって、オペレーティングシステムは64ビットであり、かつ1つ以上のアプリケーションプログラムは64ビットではない(たとえば、図示されるように32ビットまたは上の説明と同様の様態で動作する16ビットである)システムでプロセッサ10が動作することが可能となり得る。加えて、ボックス62で示されるように、LMEビットをクリアにすることによって、x86アーキテクチャと互換性がある32ビットまたは16ビットモードでプロセッサ10が動作することが可能となり得る。上述のように、例外およびオペレーティングシステム呼出を処理するためのメカニズムは、セットされたまたはクリアなLMEビットを処理するように設計され、したがって、たとえプロセッサ10が32/64モードで動作可能であっても、32ビットおよび16ビットモードは変更されずに動作し得る。さらに、LMEビットがクリア

10

20

30

40

50

なときに $\times 8$  6と互換性のある16ビットおよび32ビットモードを提供することによって(さらには、これらのモード内にリザーブされるLビットを無視することによって)、プロセッサ10は、Lビットが32/64モード以外の他のいくつかの目的のために規定されるシステムで動作し、LMEビットがセットされると依然として32/64モードをサポートし得る。したがって、32ビットオペレーティングシステムおよび32ビットまたは16ビットアプリケーションプログラムを採用するシステムは、プロセッサ10を採用することができる。続いて、システムは、プロセッサ10を変える必要なしに64ビットオペレーティングシステムへとアップグレードされ得る。

#### 【0040】

図4で例示されていないものは、LMEビットがセットされた状態で動作する64ビットオペレーティングシステムおよび64ビットアプリケーションプログラムである。64ビットオペレーティングシステムおよび32ビットアプリケーションプログラムのために上で説明されたオペレーティングシステムルーチンの呼出のためのメカニズムは、64ビットアプリケーションプログラムにも等しく当てはまり得る。加えて、(以下でより詳細に説明されるように)64ビットオフセットをサポートする呼出ゲートがサポートされる。

10

#### 【0041】

次に図5を参照して、プロセッサ10のある実施例に従った、LMEビット、コードセグメント記述子内のLビット、およびコードセグメント記述子内のDビットの状態と、プロセッサ10の対応する動作モードとを例示する表70が示される。他の実施例も可能であり、企図される。表70が示すように、LMEビットがクリアならば、Lビットはリザーブされる(0と規定される)。しかし、プロセッサ10は、LMEビットがクリアならば、Lビットをドントケアとして扱い得る。このようにして、LMEビットがクリアならば、 $\times 8$  6と互換性のある16ビットおよび32ビットモードがプロセッサ10によって提供され得る。LMEビットがセットされていてコードセグメント内のLビットがクリアならば、プロセッサ10によって互換動作モードが確立され、Dビットが16ビットまたは32ビットモードを選択する。LMEビットおよびLビットがセットされていてDビットがクリアならば、プロセッサ10のために32/64モードが選択される。最後に、LMEビット、Lビット、およびDビットがすべてセットされているならば選択されるであろうモードがリザーブされる。

20

#### 【0042】

30

上で言及され、以下の図6で例示されるように、32/64動作モードは(実現例に依存するが最大64ビットの)32ビットを超えるデフォルトアドレスサイズと、32ビットのデフォルトオペランドサイズとを含む。32ビットのデフォルトオペランドサイズは、ある特定の命令の符号化を介して64ビットへとオーバーライドされてもよい。プログラムが行なうデータ操作の多くにとって32ビットが十分であるプログラムのために平均命令長を最小にするために、32ビットのデフォルトオペランドサイズが選択される(なぜならば、64ビットへとオーバーライドすることは命令符号化に命令プレフィックスを含むことを伴い、これによって命令長が増大させられ得るためである)。(現在存在するプログラムのうちのかなりの数であり得る)このようなプログラムでは、64ビットオペランドサイズへと移ることによって、プログラムが達成する実行性能が実際に減じられるおそれがある(つまり、実行時間が増大する)。この減少は、64ビット値が記憶されるときにプログラムが用いるデータ構造のメモリサイズの倍増(doubling)にある程度起因し得る。32ビットが十分ならば、これらのデータ構造は32ビット値を記憶する。したがって、データ構造がアクセスされるときにアクセスされるバイトの数は、32ビット値が十分であり得るときに64ビット値が用いられると増大し、増大したメモリ帯域幅(および各値によって占有される増大したキャッシュスペース)によって、実行時間が増大するおそれがある。したがって、デフォルトオペランドサイズとして32ビットが選択され、ある特定の命令の符号化を介してデフォルトがオーバーライドされ得る。

40

#### 【0043】

次に図6を参照して、ある特定の命令のために動作モードをオーバーライドするための命

50

令プレフィックスの用途のある実施例を例示する表72が示される。他の実施例も可能であり、企図される。実行コア14は、表72に従ってある特定の命令のためにアドレスサイズおよびオペランドサイズを決定する。特に図6で示される実施例では、命令プレフィックスバイト(アドレスサイズオーバーライドプレフィックスバイト)が用いられてデフォルトアドレスサイズがオーバーライドされ、別の命令プレフィックスバイト(オペランドサイズオーバーライドプレフィックスバイト)が用いられてデフォルトオペランドサイズがオーバーライドされ得る。アドレスサイズオーバーライドプレフィックスバイトは(16進法では)67として符号化され、オペランドサイズオーバーライドプレフィックスバイトは(16進法では)66として符号化される。ある特定の命令でのオーバーライドプレフィックスの数によって、表の列が形成される。表の行は、動作モードおよび対応する列内のオーバーライドプレフィックスの数に基づいて、ある特定の命令のオペランドサイズおよびアドレスサイズを示す。オーバーライドプレフィックスの数は、対応するタイプのオーバーライドプレフィックスの数を指す(たとえば、アドレスサイズの行は、アドレスサイズオーバーライドプレフィックスの数に基づいたアドレスサイズであり、オペランドサイズの行は、オペランドサイズオーバーライドプレフィックスの数に基づいたオペランドサイズである)。

#### 【0044】

オーバーライドプレフィックスの数で「0」とラベル付けされる列は、各動作モードのためのデフォルトオペランドサイズおよびアドレスサイズを示す。32ビットモードの行および16ビットモードの行は、互換モード(LMEセット)と標準モード(LMEクリア)との両者を指すことが注目される。さらに、デフォルトアドレスサイズは32/64モードでは64ビットであるが、アドレスビットの実際の数は、上述のように実現例に依存したものであり得る。

#### 【0045】

表72で示されるように、32/64ビットモード内に1つのアドレスサイズオーバーライドプレフィックスを含むことによって、アドレスサイズが64ビット(所与の実現では64ビットよりも少ないものであり得るが、32ビットよりは大きい)から32ビットへと変化する。加えて、32/64ビットモード内に1つのオペランドサイズオーバーライドプレフィックスを含むことによって、オペランドサイズが32ビットから64ビットへと変化する。(たとえば、「C」プログラミング言語において短整数データ型をサポートするために)16ビットオペランドにも備えることが所望であり得る。したがって、32/64モード内に2つのオペランドサイズオーバーライドプレフィックスを含むことによって、16ビットのオペランドサイズが選択される。2つよりも多いオペランドサイズオーバーライドプレフィックスを含むことによって結果として、2つのオペランドサイズオーバーライドプレフィックスを含むときと同じオペランドサイズが得られる。同様に、1つよりも多いアドレスサイズオーバーライドプレフィックスを含むことによって結果として、1つのアドレスサイズオーバーライドプレフィックスを含むときと同じアドレスサイズが得られる。

#### 【0046】

32ビットモードでは、1つのオーバーライドプレフィックスを含むことによって、デフォルト32ビットサイズが16ビットへと切換えられ、1つよりも多いオーバーライドプレフィックスを含むことは、1つのオーバーライドプレフィックスを含むことと同じ効果を有する。同様に、16ビットモードでは、1つのオーバーライドプレフィックスを含むことによって、デフォルト16ビットサイズが32ビットに切換えられ、1つよりも多いオーバーライドプレフィックスを含むことは、1つのオーバーライドプレフィックスを含むことと同じ効果を有する。

#### 【0047】

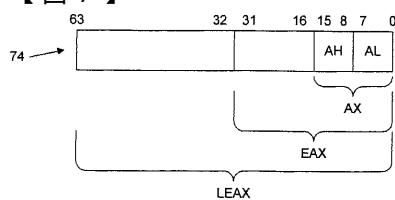

図7を参照して、LEXレジスタ74のある実施例を例示する図が示される。レジスタファイル22内の他のレジスタも同様であり得る。他の実施例も可能であり、企図される。図7の実施例では、レジスタ74は64ビットを含み、最上位ビットはビット63とし

10

20

30

40

50

てラベル付けされ、最下位ビットはビット 0 としてラベル付けされる。図 7 は、( A レジスタがオペランドとして選択された場合 ) 命令のオペランドサイズに基づいてアクセスされる L E A X レジスタの部分を示す。より具体的には、オペランドサイズが 64 ビットならば、( 図 7 で「 L E A X 」とラベル付けされたプレース(brace)によって示されるように ) レジスタ 74 全体がアクセスされる。オペランドサイズが 32 ビットならば、( 図 7 で「 E A X 」とラベル付けされたプレースによって示されるように ) レジスタ 74 のビット 31 : 0 がアクセスされる。オペランドサイズが 16 ビットならば、( 図 7 で「 A X 」とラベル付けされたプレースによって示されるように ) レジスタのビット 16 : 0 がアクセスされる。上述のオペランドサイズは、動作モードおよびオーバーライドプレフィックスのいずれかを含むことに基づいて選択され得る。しかし、8 ビットレジスタ ( 図 7 の A H または A L ) にアクセスするある特定の命令演算コードが規定される。

10

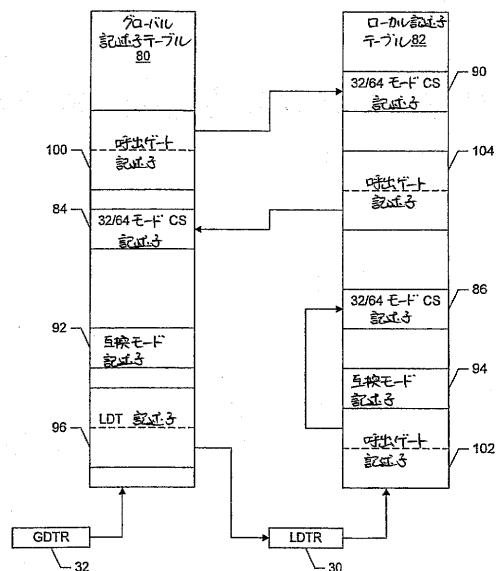

#### 【 0048 】

次に図 8 を参照して、グローバル記述子テーブル 80 およびローカル記述子テーブル 82 のある実施例を例示するロック図が示される。他の実施例も可能であり、企図される。図 8 で示され、かつ上で言及されるように、グローバル記述子テーブル 80 の基底アドレスは G D T R 32 によって提供され、ローカル記述子テーブル 82 の基底アドレスは L D T R 30 によって提供される。したがって、仮想アドレススペース内にグローバル記述子テーブル 80 とローカル記述子テーブル 82 とを恣意的に置くことをサポートするために、G D T R 32 と L D T R 30 とは 64 ビット基底アドレスを記憶し得る。L M E ビットがクリアならば、基底アドレスの最下位 32 ビットが用いられて記述子テーブルが位置付け(locate)られ得る。

20

#### 【 0049 】

グローバル記述子テーブル 80 とローカル記述子テーブル 82 との両者は、種々の種類のセグメント記述子を記憶するように構成される。たとえば、32 / 64 モードコードセグメント記述子 84 、 86 、および 90 と、互換モード記述子 92 および 94 とが図 8 で示される。記述子 84 - 94 の各々は対応する記述子テーブル内でエントリを占有し、ここではエントリは 1 つのセグメント記述子 ( たとえば、図 2 および図 3 で示される実施例では 8 バイト ) を記憶することができる。グローバル記述子テーブル 80 内の別の種類の記述子はローカル記述子テーブル記述子 96 であり、これは、ローカル記述子テーブル 82 のためにシステムセグメントを規定し、L D T R 30 内に記憶される基底アドレスを提供する。L D T R 30 は、グローバル記述子テーブル 80 内に記述子 96 を位置付けるセグメントセレクタをオペランドとして有する L L D T 命令を用いて初期設定される。グローバル記述子テーブル 80 は、所望ならば、異なったローカル記述子テーブルを位置付ける多数の L D T 記述子を記憶し得る。L M E ビットがセットされていると L D T 記述子 96 は 64 ビットオフセットを記憶し得るため、L D T 記述子 96 はグローバル記述子テーブル 80 内に 2 つのエントリを占有し得る。L M E ビットがクリアであると、L D T 記述子 96 はグローバル記述子テーブル 80 内に単一のエントリを占有し得る。同様に、各々のタスクは、記述子テーブル 80 および 82 のうちの 1 つの中にタスク状態セグメント ( T S S ) 記述子を有してタスクに関連するある特定の情報を記憶し得る。したがって、T S S 記述子は 2 つのエントリを占有して T S S 情報が 64 ビットアドレススペース内のどこにでも記憶されることを可能にし得る。

30

40

#### 【 0050 】

ローカル記述子テーブルおよびグローバル記述子テーブルはまた、呼出ゲート記述子を記憶することもできる。たとえば、図 8 は呼出ゲート記述子 100 、 102 、および 104 を示す。呼出ゲート記述子は、64 ビットオフセットもサポートし、したがって、対応する記述子テーブル内で 2 つのエントリを占有し得る。例示的な 32 / 64 呼出ゲート記述子が以下の図 9 で示される。

#### 【 0051 】

セグメント記述子テーブル 80 および 82 を 8 バイトで維持し、かつ 64 ビットオフセットを含む記述子のために 2 つのエントリを用いることによって、16 ビットモードおよび

50

32ビットモードのための記述子は、64ビットオフセットを含む記述子と同じテーブル内に記憶され得る。したがって、互換モードで動作するアプリケーションは、64ビットオペレーティングシステムと同じセグメント記述子テーブル内で適切な記述子を有することができる。

#### 【0052】

一般に、呼出ゲートが用いられてより小さい特権レベルを有するコードセグメントとより大きい特権レベルを有するコードセグメント（たとえば、オペレーティングシステムルーチンを呼出すアプリケーションプログラム）との間の遷移が管理される。より少ない特権を与えられたコードは、呼出または、ターゲットとしてセグメントセレクタ（および、この事例では無視されるが、セグメントへのオフセット）を特定する他の分岐命令を含む。

セグメントセレクタは、記述子テーブル内の呼出ゲート記述子を識別し、これは、より大きな特権レベルコードを実行するのに必要とされる最小の特権レベルを含む。プロセッサ10が呼出または他の分岐命令を実行するとき、プロセッサ10はセグメントセレクタで記述子テーブルに索引をつけ、呼出ゲートを位置付ける。プロセッサ10の現在の特権レベルと、（セグメントセレクタの一部であり、特権検査目的のために現在の特権レベルを下げるために用いられ得る）リクエスター(requestor)特権レベルとの両者が十分な特権を反映していると（たとえば、特権レベルは呼出ゲート記述子内の最小特権レベルよりも数の上において少ないかまたはそれと等しいと）、呼出が進み得る。呼出ゲート記述子は、ターゲットセグメント（より大きな特権レベルを有するコードセグメント）のためのセグメントセレクタと、コード取出がそこで開始されるターゲットセグメント内のオフセットとを含む。プロセッサ10は、呼出ゲート記述子からセグメントセレクタおよびオフセットを抽出し、ターゲットセグメント記述子を読出してより大きな特権レベルを有するコードの取出を開始する。一方で、現在の特権レベルまたはリクエスター特権レベルのいずれかが呼出ゲート記述子内の最小特権レベルよりも小さい特権レベルであるならば（たとえば、現在の特権レベルまたはリクエスター特権レベルのいずれかが最小特権レベルよりも数の上で大きいならば）、プロセッサ10は、呼出ゲート記述子にアクセスした後、かつターゲット記述子にはアクセスすることなしに、例外を知らせる。したがって、より大きな特権レベルで実行されているコードへのアクセスは慎重に制御される。

#### 【0053】

上述のように、呼出ゲート記述子は、ターゲットセグメントセレクタおよびセグメント内のオフセットを含む。ターゲットセグメント記述子への参照は、呼出ゲート記述子から別の記述子への矢印として図8で示される。たとえば、呼出ゲート記述子100はモード記述子90を参照し、呼出ゲート記述子102は32/64モード記述子86を参照し、呼出ゲート記述子104は32/64モード記述子84を参照する。図8で示されるように、呼出ゲート記述子は両方の記述子テーブル内に記憶されてもよく、他方のテーブル内または同じテーブル内の記述子を参照し得る。さらに、呼出ゲート記述子は、32/64モード記述子または互換モード記述子のいずれかを参照し得る。

#### 【0054】

一般に、プロセッサ10がセグメントセレクタを用いて記述子テーブルのうちの1つから記述子を読出すると、1つの記述子テーブルエントリが読出される。しかし、LMEビットがセットされていて、かつプロセッサ10によってエントリが呼出ゲート記述子、LDT記述子、またはTSS記述子であることが検出されると、プロセッサ10はテーブル内に続くエントリを読出して記述子の残りを得る。したがって、呼出ゲート記述子、LDT記述子、およびTSS記述子は、テーブルエントリのサイズを再定義することなしに、さらには1つのエントリを占有する記述子のためにテーブルはどのように管理されるのかを再定義することなしに、異なるサイズの互換モード記述子（または標準モード記述子）とともにテーブル内で共存し得る。さらに、TSS記述子、LDT記述子、および呼出ゲート記述子の第2の部分はセグメント記述子としてアクセスされ得るため、以下の図9で示されるように、記述子が記述子テーブルへと記憶されると、第2の部分内の記述子のタイプフィールドであり得る記述子の部分が無効タイプにセットされる。代替的には、記

10

20

30

40

50

述子テーブル読出が行なわれるたびに、プロセッサ 10 は 2 つの連続するエントリを記述子テーブルから読出すこともでき、第 1 のエントリが呼出ゲート、LDT 記述子タイプ、または TSS 記述子タイプであると第 2 のエントリが用いられ得る。

#### 【 0 0 5 5 】

いずれかの動作モード (32 / 64 モード、32 ビット互換モード、または 16 ビット互換モード) で動作しているコードは、LME ビットがセットされていると呼出ゲート記述子を参照し得ることが注目される。したがって、32 ビットまたは 16 ビットアプリケーションは、たとえルーチンのアドレスが 32 ビットまたは 16 ビットアドレススペースの外にあったとしても、呼出ゲートメカニズムを用いてオペレーティングシステムルーチンを呼出すことができる。加えて、呼出ゲート記述子は、あらゆる動作モードを有するコードセグメントを参照することができる。オペレーティングシステムは、(32 ビットターゲットセグメントのために) 呼出ゲート内のオフセットの最上位 32 ビットが 0 であるか、または (16 ビットターゲットセグメントのために) 呼出ゲート内のオフセットの最上位 48 ビットが 0 であることを保証し得る。10

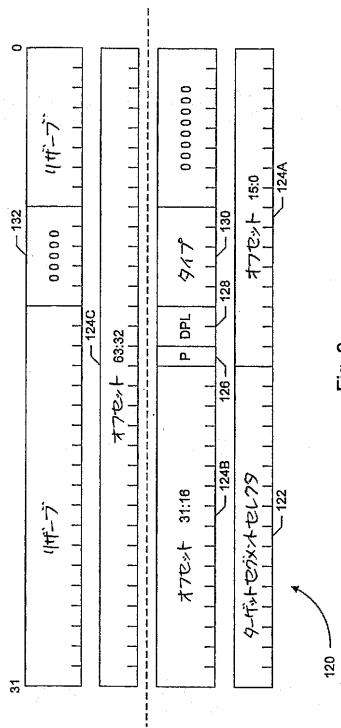

#### 【 0 0 5 6 】

図 9 を参照して、呼出ゲート記述子 120 のある実施例のブロック図が示される。他の実施例も可能であり、企図される。図 2 および図 3 と同様に、最下位バイトの上方に最上位バイトが示される。4 バイトの各グループの最上位ビットがビット 31 として示され、最下位ビットがビット 0 として示される。4 バイト内の短い垂直の線は各々のビットを区切り、長い垂直の線もビットを区切るが、それはまたフィールドも区切る。上述のように、呼出ゲート記述子は記述子テーブル内で 2 つのエントリを占有する。図 9 の水平方向の破線によって、呼出ゲート記述子 120 は (線の上の) 上部と (線の下の) 下部とに分割される。下部は、呼出ゲートのセグメントセレクタによって索引付けされるエントリ内に記憶され、上部は次に続くエントリ内に記憶される。20

#### 【 0 0 5 7 】

呼出ゲート記述子 120 は、ターゲットセグメントセレクタ (フィールド 122)、オフセット (フィールド 124A、124B、および 124C)、現在の (P) ビット 126、記述子特権レベル (DPL) 128、タイプフィールド 130、および擬似タイプフィールド 132 を含む。P ビットは上述の P ビット 48 と同様のものである。ターゲットセグメントセレクタは、(より大きな特権レベルを有する) ターゲットセグメント記述子が記憶される記述子テーブルのうちの 1 つのエントリを識別する。オフセットは、コード取出が開始されるアドレスを識別する。32 / 64 モードでは、コードセグメントは基底アドレスを有さず、さらにはフラットリニアアドレス指定が用いられるため、オフセットはコード取出が始まるアドレスである。他のモードでは、オフセットはターゲットセグメント記述子が規定するセグメントベースに加えられてコード取出が始まるアドレスが生成される。上述のように、オフセットはこの実施例では 64 ビットを含み得る。30

#### 【 0 0 5 8 】

DPL 128 は、(現在の特権レベルおよび要求された (requested) 特権レベルの両方ににおいて) 呼出ルーチンが有さなければならぬ最小特権レベルを記憶し、これは呼出ゲートをうまく通り抜け、ターゲットセグメント記述子内で特定される特権レベルにおいて呼出されたルーチンを実行し得る。40

#### 【 0 0 5 9 】

タイプフィールド 130 は呼出ゲート記述子タイプにコーディングされる。ある実施例では、このタイプは、x86 アーキテクチャ内で規定される 32 ビット呼出ゲートタイプとしてコーディングされる。代わりに、他の符号化が用いられてもよい。最後に、擬似タイプフィールド 132 が無効タイプ (たとえば、0) にコーディングされて呼出ゲート記述子 120 の上半分を記憶するセグメントテーブルエントリを識別するセグメントセレクタが与えられると (presented)、プロセッサ 10 によって例外が知らされることが保証される。

#### 【 0 0 6 0 】

50

L D T 記述子 9 6 の下半分は 3 2 ビット L D T 記述子と同様のものであり得ることと、L D T 記述子 9 6 の上半分は呼出ゲート記述子 1 2 0 の上半分と同様のものであり得ることが注目される。

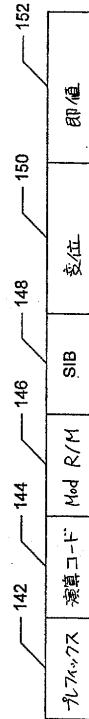

#### 【 0 0 6 1 】

次に図 1 0 を参照して、プロセッサ 1 0 が実行する命令のための命令フォーマット 1 4 0 のブロック図が示される。他の実施例も可能であり、企図される。図 1 0 の実施例では、命令フォーマット 1 4 0 は、プレフィックスフィールド 1 4 2 、演算コードフィールド 1 4 4 、 m o d R / M (レジスタ / メモリ) フィールド 1 4 6 、 S I B (スケールインデックスベース) フィールド 1 4 8 、変位フィールド 1 5 0 、および即値フィールド 1 5 2 を含む。演算コードフィールド 1 4 4 以外の各フィールドは任意である。したがって、命令フォーマット 1 4 0 によって、可変長命令が規定され得る。10

#### 【 0 0 6 2 】

プレフィックスフィールド 1 4 2 は、命令のためのいかなる命令プレフィックスのためにも用いられる。上述のように、オペランドサイズオーバーライドプレフィックスおよびアドレスサイズオーバーライドプレフィックスはある命令へと符号化されてプロセッサ 1 0 の動作モードをオーバーライドし得る。これらのオーバーライドプレフィックスがプレフィックスフィールド 1 4 2 内に含まれる。上述のように、オペランドサイズオーバーライドプレフィックスおよびアドレスサイズオーバーライドプレフィックスの各々は、バイト単位で (by bytes) プレフィックスフィールド 1 4 2 内に含まれ得る。20

#### 【 0 0 6 3 】

演算コードフィールド 1 4 4 は、命令の演算コード (つまり、命令セット内のどの命令が実行されているのか) を含む。いくつかの命令では、オペランドは演算コードフィールド 1 4 4 内で特定され得る。他の命令では、演算コードの一部が m o d R / M フィールド 1 4 6 内に含まれ得る。さらに、ある特定の演算コードは、オペランドとして 8 ビットまたは 1 6 ビットレジスタを特定する。したがって、演算コード符号化はまた、プロセッサ 1 0 の動作モードによって示されるデフォルトをオーバーライドするように働き得る。20

#### 【 0 0 6 4 】

M o d R / M フィールド 1 4 6 および S I B フィールド 1 4 8 は、命令のオペランドを示す。変位フィールド 1 5 0 はいかなる変位情報をも含み、即値フィールド 1 5 2 は即値オペランドを含む。30

#### 【 0 0 6 5 】

##### コンピュータシステム

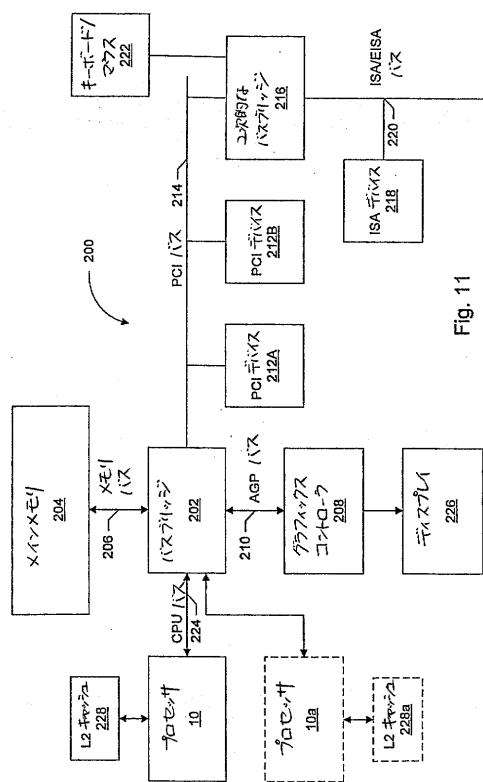

図 1 1 を参照して、バスブリッジ 2 0 2 を通して種々のシステム構成要素に結合されるプロセッサ 1 0 を含むコンピュータシステム 2 0 0 のある実施例のブロック図が示される。他の実施例も可能であり、企図される。示されるシステムでは、メモリバス 2 0 6 を通してメインメモリ 2 0 4 がバスブリッジ 2 0 2 に結合され、A G P バス 2 1 0 を通してグラフィックスコントローラ 2 0 8 がバスブリッジ 2 0 2 に結合される。最後に、P C I バス 2 1 4 を通して複数の P C I デバイス 2 1 2 A - 2 1 2 B がバスブリッジ 2 0 2 に結合される。E I S A / I S A バス 2 2 0 を通した 1 つ以上の E I S A または I S A デバイス 2 1 8 への電気的インターフェイスに対応する (accommodate) ように、2 次的なバスブリッジ 2 1 6 がさらに設けられ得る。プロセッサ 1 0 は、C P U バス 2 2 4 を通してバスブリッジ 2 0 2 に結合され、任意の L 2 キャッシュ 2 2 8 にも結合される。C P U バス 2 2 4 と L 2 キャッシュ 2 2 8 に対するインターフェイスとは共に、外部インターフェイスユニット 1 8 が結合し得る外部インターフェースを含み得る。40

#### 【 0 0 6 6 】

バスブリッジ 2 0 2 は、プロセッサ 1 0 、メインメモリ 2 0 4 、グラフィックスコントローラ 2 0 8 、および P C I バス 2 1 4 に接続されるデバイスの間のインターフェイスを提供する。バスブリッジ 2 0 2 に接続されるデバイスのうちの 1 つからある動作が受取られると、バスブリッジ 2 0 2 は動作のターゲット (たとえば、ある特定のデバイスまたは、P C I バス 2 1 4 の場合には、ターゲットは P C I バス 2 1 4 上にあること) を識別する50

。バスブリッジ 202 は動作をターゲットのデバイスへと経路付ける。バスブリッジ 202 は一般に、ソースデバイスまたはバスが用いるプロトコルからターゲットデバイスまたはバスが用いるプロトコルへと動作を変換する。

#### 【0067】

I S A / E I S A バスに対するインターフェイスを P C I バス 214 に提供することに加えて、所望ならば、2 次的なバスブリッジ 216 はさらに付加的な機能を組込んでもよい。2 次的なバスブリッジ 216 の外側にあるか、またはそれと一体化されている入力 / 出力コントローラ（図示せず）もコンピュータシステム 200 内に含まれてもよく、所望ならば、キーボードおよびマウス 222、ならびに種々のシリアルポートおよびパラレルポートに動作サポートを提供し得る。他の実施例では、外部キャッシュユニット（図示せず）がさらにプロセッサ 10 とバスブリッジ 202 との間の C P U バス 224 に結合され得る。代替的には、外部キャッシュはバスブリッジ 202 に結合されてもよく、外部キャッシュのためのキャッシュ制御ロジックはバスブリッジ 202 と一体化され得る。L 2 キャッシュ 228 がさらに、プロセッサ 10 に対する後方構成で示される。L 2 キャッシュ 228 は、プロセッサ 10 から分離されてもよく、プロセッサ 10 を備えるカートリッジ（たとえば、スロット 1 またはスロット A）と一体化されてもよく、またはプロセッサ 10 を備える半導体基板とさえ一体化されていてもよいことが注目される。10

#### 【0068】

メインメモリ 204 は、アプリケーションプログラムが記憶され、さらにはそこからプロセッサ 10 が主に実行されるメモリである。好適なメインメモリ 204 は D R A M ( ダイナミックランダムアクセスメモリ ) を含む。たとえば、S D R A M ( 同期 D R A M ) またはランバス D R A M ( R D R A M ) の複数のバンクも好適であり得る。20

#### 【0069】

P C I デバイス 212A - 212B は、たとえば、ネットワークインターフェイスカード、ビデオアクセラレータ、オーディオカード、ハードディスクドライブまたはハードドライブコントローラ、フロッピー ( R ) ディスクドライブまたはフロッピー ( R ) ドライブコントローラ、S C S I ( 小型コンピュータシステムインターフェイス ) アダプタ、および電話カード等の種々の周辺デバイスを例証する。同様に、I S A デバイス 218 は、モデム、サウンドカード、ならびに G P I B またはフィールドバスインターフェイスカード等の種々のデータ収集カード等の種々の種類の周辺デバイスを例証する。30

#### 【0070】

グラフィックスコントローラ 208 が設けられてディスプレイ 226 上のテキストおよび画像のレンダリングが制御される。グラフィックスコントローラ 208 は、メインメモリ 204 へと、さらにはそこから効果的にシフトされ得る三次元データ構造をレンダリングするような、当該技術分野で一般に公知の典型的なグラフィックスアクセラレータを具体化し得る。したがって、グラフィックスコントローラ 208 は、バスブリッジ 202 内のターゲットインターフェイスへのアクセスを要求し、かつそれを受取ってメインメモリ 204 へのアクセスを得ることができるという点で、A G P バス 210 のマスターであり得る。専用グラフィックスバスは、メインメモリ 204 からのデータの迅速な検索に対応する。ある特定の動作では、グラフィックスコントローラ 208 はさらに、A G P バス 210 上で P C I プロトコルトランザクションを生成するように構成され得る。したがって、バスブリッジ 202 の A G P インターフェイスは、A G P プロトコルトランザクションならびに P C I プロトコルターゲットとイニシエータトランザクションとの両者をサポートするための機能を含む。ディスプレイ 226 は、画像またはテキストが示され得るすべての電子ディスプレイである。好適なディスプレイ 226 は、陰極線管 ( “ C R T ” ) 、液晶ディスプレイ ( “ L C D ” ) 等を含む。40

#### 【0071】

A G P 、 P C I 、および I S A または E I S A バスが上の説明で例として用いられてきたが、所望であればいかなるバスアーキテクチャも代わりになり得ることが注目される。コンピュータシステム 200 は、追加のプロセッサ（たとえば、コンピュータシステム 20

0の任意の構成要素として示されるプロセッサ10a)を含む多重処理コンピュータシステムであってもよいことがさらに注目される。プロセッサ10aはプロセッサ10と同様のものであり得る。より具体的には、プロセッサ10aはプロセッサ10の同一コピーでもあり得る。プロセッサ10aは、(図11で示されるように)独立したバスを介してバスブリッジ202に接続されてもよく、またはプロセッサ10とともにCPUバス224を共有してもよい。さらに、プロセッサ10aは、L2キャッシュ228と同様の任意のL2キャッシュ228aに結合され得る。

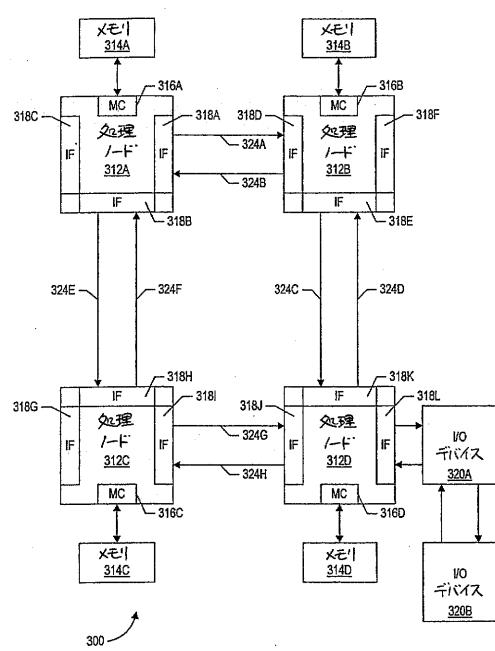

#### 【0072】

図12を参照して、コンピュータシステム300の別の実施例が示される。他の実施例も可能であり、企図される。図12の実施例では、コンピュータシステム300は、いくつかの処理ノード312A、312B、312C、および312Dを含む。各処理ノードは、それぞれの処理ノード312A-312D内に含まれるメモリコントローラ316A-316Dを介してそれぞれのメモリ314A-314Dに結合される。加えて、処理ノード312A-312Dは、処理ノード312A-312D間の通信のために用いられるインターフェイスロジックを含む。たとえば、処理ノード312Aは、処理ノード312Bと通信を行なうためのインターフェイスロジック318A、処理ノード312Cと通信を行なうためのインターフェイスロジック318B、およびさらなる別の処理ノード(図示せず)と通信を行なうための第3のインターフェイスロジック318Cを含む。同様に、処理ノード312Bは、インターフェイスロジック318D、318E、および318Fを含み、処理ノード312Cは、インターフェイスロジック318G、318H、および318Iを含み、処理ノード312Dは、インターフェイスロジック318J、318K、および318Lを含む。処理ノード312Dは、インターフェイスロジック318Lを介して複数の入力/出力デバイス(たとえば、ディジーチェーン構成のデバイス320A-320B)と通信するように結合される。他の処理ノードも同様の態様で他のI/Oデバイスと通信し得る。

#### 【0073】

処理ノード312A-312Dは、処理ノード間の通信のためにパケットベースリンクを実現する。この実施例では、リンクは何組かの単方向ラインとして実現される(たとえば、ライン324Aが用いられて処理ノード312Aから処理ノード312Bへとパケットが伝送され、ライン324Bが用いられて処理ノード312Bから処理ノード312Aへとパケットが伝送される)。図12で示されるように、他の組のライン324C-324Hが用いられて他の処理ノード間でパケットが伝送される。一般に、ライン324の各々の組は、1つ以上のデータラインと、データラインに対応する1つの以上のクロックラインと、伝達されているパケットの種類を示す1つ以上のコントロールラインを含み得る。リンクは、処理ノード間の通信のためにキャッシュコヒーレント態様で動作され得るか、または処理ノードとI/Oデバイス(または、PCIバスまたはISAバス等の従来の構造のI/Oバスへのバスブリッジ)との間の通信のために非コヒーレント態様で動作され得る。さらに、リンクは、図示されるようなI/Oデバイス間のディジーチェーン構造を用いて非コヒーレント態様で動作され得る。ある処理ノードから別のものへと伝送されるパケットは1つ以上の中間ノードを通り抜け得ることが注目される。たとえば、図12で示されるように、処理ノード312Aによって処理ノード312Dへと伝送されるパケットは、処理ノード312Bまたは処理ノード312Cのいずれかを通り抜け得る。好適なあらゆる配線アルゴリズムが用いられ得る。コンピュータシステム300の他の実施例は、図12で示される実施例よりも多くの、またはより少ない処理ノードを含み得る。

#### 【0074】

一般に、パケットは、ノード間のライン324上の1つ以上のビットタイム(bit times)として伝送され得る。ビットタイムは、対応するクロックライン上のクロック信号の立上がり端縁または立下がり端縁であり得る。パケットは、トランザクションを開始するためのコマンドパケット、キャッシングコヒーレンシを維持するためのプロープパケット、およびプロープとコマンドとに応答するための応答パケットを含み得る。

10

20

30

40

50

## 【0075】

メモリコントローラおよびインターフェイスロジックに加えて、処理ノード312A-312Dは1つ以上のプロセッサを含み得る。概して、処理ノードは、少なくとも1つのプロセッサを含み、所望であればメモリと通信するためのメモリコントローラおよび他のロジックを任意で含み得る。より具体的には、各処理ノード312A-312Dは、プロセッサ10の1つ以上のコピーを含み得る。外部インターフェイスユニット18は、ノード内にインターフェイスロジック318およびメモリコントローラ316を含み得る。

## 【0076】

メモリ314A-314Dは、好適なあらゆるメモリデバイスを含み得る。たとえば、メモリ314A-314Dは、1つ以上のRAMBUS DRAM(RDRAM)、同期DRAM(SDRAM)、スタティックRAM等を含み得る。コンピュータシステム300のアドレススペースはメモリ314A-314D内で分割される。処理ノード312A-312Dの各々は、どのアドレスがどのメモリ314A-314Dにマッピングされ、したがってどの処理ノード312A-312Dにある特定のアドレスのためのメモリ要求が経路付けされるべきなのかを判断するために用いられるメモリマップを含み得る。ある実施例では、コンピュータシステム300内のアドレスのためのコヒーレンシポイントは、アドレスに対応するメモリ記憶バイトに結合されたメモリコントローラ316A-316Dである。言換えると、メモリコントローラ316A-316Dは、対応するメモリ314A-314Dへのメモリアクセスの各々がキャッシュコヒーレント態様で起こることを保証することを担当する。メモリコントローラ316A-316Dは、メモリ314A-314Dとインターフェイスをとるための制御回路を含み得る。加えて、メモリコントローラ316A-316Dは、メモリ要求を列に並ばせるための要求待ち行列を含み得る。

## 【0077】

一般に、インターフェイスロジック318A-318Lは、リンクからパケットを受信し、さらにはリンク上で伝送されるべきパケットをバッファリングするための種々のバッファを含み得る。コンピュータシステム300は、パケットを伝送するための好適なあらゆるフロー制御メカニズムを採用し得る。たとえば、ある実施例では、各インターフェイスロジック318は、そのインターフェイスロジックが接続されるリンクの他端のレシーバ内に各々の種類のバッファの数のカウントを記憶する。インターフェイスロジックは、受信インターフェイスロジックがパケットを記憶するための解放されたバッファを有さない限りは、パケットを传送しない。パケットを前方に(onward)経路付けることによって受信バッファが解放されると、受信インターフェイスロジックは送信インターフェイスロジックへとメッセージを传送してバッファが解放されたことを示す。このようなメカニズムは「クーポンベース」システムと呼ばれ得る。

## 【0078】

I/Oデバイス320A-320Bは、好適なあらゆるI/Oデバイスであり得る。たとえば、I/Oデバイス320A-320Bは、ネットワークインターフェイスカード、ビデオアクセラレータ、オーディオカード、ハードディスクドライブまたはハードドライブコントローラ、フロッピー(R)ディスクドライブまたはフロッピー(R)ドライブコントローラ、SCSI(小型コンピュータシステムインターフェイス)アダプタおよび電話カード、モデム、サウンドカード、およびGPIBまたはフィールドバスインターフェイスカード等の種々のデータ収集カードを含み得る。

## 【0079】

上述の開示が完全に理解されると、多くの変更および変形が当業者に明らかとなるだろう。前掲の請求項はこのようなすべての変更および変形を包含すると解釈されることが意図される。

## 【図面の簡単な説明】

【図1】 プロセッサのある実施例のブロック図である。

【図2】 32/64モードのためのセグメント記述子のある実施例のブロック図である。

【図3】 互換モードのためのセグメント記述子のある実施例のブロック図である。

【図4】 図1で示されるプロセッサのある実施例に従った、互換モードおよびレガシーモードにおける動作を示すブロック図である。

【図5】 セグメント記述子および制御レジスタ値の関数としての動作モードの1つの実施例を例示する表である。

【図6】 デフォルト動作モードをオーバーライドするための命令プレフィックスの用途のある実施例を例示する表である。

【図7】 レジスタのある実施例を示すブロック図である。

【図8】 グローバル記述子テーブルおよびローカル記述子テーブルのある実施例を例示する図である。 10

【図9】 32 / 64 呼出ゲート記述子のある実施例のブロック図である。

【図10】 命令フォーマットのブロック図である。

【図11】 図1で示されるプロセッサを含むコンピュータシステムのある実施例のブロック図である。

【図12】 図1で示されるプロセッサを含むコンピュータシステムの別の実施例のブロック図である。

【図1】

Fig. 1

【図2】

Fig. 2

40

【図3】

Fig. 3

【図4】

Fig. 4

【図5】

| LME | CS Lビット | CS Dビット | 動作モード      |

|-----|---------|---------|------------|

| 0   | x       | 0       | 16ビットモード   |

| 0   | x       | 1       | 32ビットモード   |

| 1   | 0       | 0       | 16ビット互換モード |

| 1   | 0       | 1       | 32ビット互換モード |

| 1   | 1       | 0       | 32/64モード   |

| 1   | 1       | 1       | 1/1モード     |

70

Fig. 5

【図6】

| オペレーライドフレームの数(66H<br>オペランド、67H アドレス) |          | 0     | 1     | 2+    |

|--------------------------------------|----------|-------|-------|-------|

| 32/64 モード                            | オペランドサイズ | 32ビット | 64ビット | 16ビット |

|                                      | アドレスサイズ  | 64ビット | 32ビット | 32ビット |

| 互換モードを含む<br>32ビットモード                 | オペランドサイズ | 32ビット | 16ビット | 16ビット |

|                                      | アドレスサイズ  | 32ビット | 16ビット | 16ビット |

| 互換モードを含む<br>16ビットモード                 | オペランドサイズ | 16ビット | 32ビット | 32ビット |

|                                      | アドレスサイズ  | 16ビット | 32ビット | 32ビット |

72

Fig. 6

【図7】

Fig. 7

【図8】

Fig. 8

【図 9】

Fig. 9

【図 10】

Fig. 10

【図 11】

Fig. 11

【図 12】

Fig. 12

---

フロントページの続き

(74)代理人 100083703

弁理士 仲村 義平

(74)代理人 100096781

弁理士 堀井 豊

(74)代理人 100098316

弁理士 野田 久登

(74)代理人 100109162

弁理士 酒井 將行

(72)発明者 マクグラス, ケビン・ジェイ

アメリカ合衆国、95033 カリフォルニア州、ロス・ガトス、ハチンソン・ロード、2287

6

審査官 三坂 敏夫

(56)参考文献 米国特許第05481684(US, A)

特開平06-202945(JP, A)

(58)調査した分野(Int.Cl., DB名)

G06F 9/34