(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 699 08 293 T2 2004.03.25

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 044 508 B1

(51) Int Cl.<sup>7</sup>: H03M 13/27

(21) Deutsches Aktenzeichen: 699 08 293.5

(86) PCT-Aktenzeichen: PCT/EP99/04707

(96) Europäisches Aktenzeichen: 99 936 484.7

(87) PCT-Veröffentlichungs-Nr.: WO 00/03486

(86) PCT-Anmeldetag: 02.07.1999

(87) Veröffentlichungstag

der PCT-Anmeldung: 20.01.2000

(97) Erstveröffentlichung durch das EPA: 18.10.2000

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 28.05.2003

(47) Veröffentlichungstag im Patentblatt: 25.03.2004

(30) Unionspriorität:

9814960 10.07.1998 GB

(84) Benannte Vertragsstaaten:

DE, FR, GB, IT

(73) Patentinhaber:

Koninklijke Philips Electronics N.V., Eindhoven,

NL

(72) Erfinder:

MOULSLEY, J., Timothy, NL-5656 AA Eindhoven,

NL

(74) Vertreter:

Meyer, M., Dipl.-Ing., Pat.-Ass., 52076 Aachen

(54) Bezeichnung: CODIER- UND DECODIERVORRICHTUNG ZUR RATEANPASSUNG BEI DATENÜBERTRAGUNG

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingereicht, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

**Beschreibung****Technischer Bereich**

[0001] Die vorliegende Erfindung bezieht sich im Allgemeinen auf ein digitales Kommunikationssystem und insbesondere auf ein Kommunikationssystem, wobei Codierung des digitalen Eingangs angewandt wird zum Erzeugen eines codierten Eingangs mit einer größeren Anzahl Bits als der digitale Eingang. Vorwärts Fehler Korrektur ("Forward Error Correction") (FEC) funktioniert auf diese Weise und Faltungscodierung ist ein Beispiel des Vorwärts Fehler Korrektursystems.

**Stand der Technik**

[0002] Bei einem Faltungscodierungssystem wird ein digitaler Eingang durch eine Faltungscodierungsschaltung derart codiert, dass für jede Anzahl  $k$  Bits, die in die Faltungscodierungsschaltung eingegeben wird, eine größere Anzahl  $n$  Bits als Ausgang geliefert wird. Eine Codierungsrate für die Faltungscodierungsschaltung wird definiert als das Verhältnis der Anzahl  $k$  Eingangsbits zu der Anzahl  $n$  codierter Ausgangsbits. Auf diese Weise ist beispielsweise die Codierungsrate  $\frac{1}{2}$ , wenn für jedes in die Faltungscodierungsschaltung eingegebene Bit zwei Ausgangsbits geliefert werden. Diese Zunehme der Anzahl Bits führt zu einer Abnahme der Signalbitrate.

[0003] Es sind mehrere herkömmliche Faltungscodierungsalgorithmen verfügbar, mit je einer spezifischen Codierungsrate. Es kann erwünscht sein, die Codierungsrate derart einzustellen, dass die Datenrate für den Ausgang der Schaltungsanordnung den Anforderungen für den restlichen Teil der Kommunikationsschaltung einschließlich des Kommunikationskanals entspricht. So ist es beispielsweise zur Steigerung der Codierungsrate bekannt, den faltungscodierten Ausgang durch eine Durchschlagschaltung hindurch zu führen, die ein Löschmuster aufweist zum Entfernen selektierter Bits aus dem faltungscodierten Ausgang. Auf alternative Weise ist es zum Reduzieren der Codierungsrate möglich, den Ausgang durch eine Wiederholungsschaltung hindurch zu führen zum Wiederholen selektierter Bits des Ausgangs.

[0004] In US 5.668.820 und US 5.511.082 wird ein digitales Kommunikationssystem mit einem durchgeschlagenen Faltungscodierungssystem der oben beschriebenen Art beschrieben.

[0005] Die vorliegende Erfindung bezieht sich insbesondere auf eine Codierungsanordnung mit einem codierten Ausgang, wobei eine Anzahl Worte des codierten Ausgangssignals verschachtelt sind. Verschachtelung ist eine durchaus bekannte Technik, die angewandt wird zum Verbessern der Fehlerleistung eines Übertragungssystems. Ein Beispiel eines derartigen Systems ist in der UK Patentanmeldung GB-A-2 296 165 beschrieben, worin eine Übertra-

gungskette mit einem Reed-Salomon-Codierer, einem Verschachtler und einer Füll/Durchschlaganordnung beschrieben wird. Es gibt eine wachsende Nachfrage nach Flexibilität bei Kommunikationssystemen, beispielsweise die Möglichkeit, Daten mit verschiedenen Charakteristiken, wie Bitrate, Verschachtelungstiefe, variable Datenrate usw. zu verarbeiten. Die Verwendung einer herkömmlichen Faltungscodierungsschaltung mit variabler Rate (oder einer anderen FEC-Codierungsschaltung) in einer Codierungsanordnung mit Verschachtelung des codierten Ausgang erfordert, dass die Verschachtelungsschaltung adaptiv ist zu der Ausgangsbitrate des Faltungscodierers. Die Anmelderin hat deswegen erkannt, dass die Verschachtelung von Daten nach der Codierung aber vor der Ratenanpassung des Datenstroms durchgeführt werden soll, d. h. vor dem Durchschlag oder der Bitwiederholung). Dies bringt aber das Problem mit sich, dass der Durchschlag oder die Bitwiederholung, durchgeführt durch die Ratenanpassschaltung nicht geeignet sein kann für die von der Verschachtelungsschaltung erzeugte Bitstruktur. So gibt es beispielsweise die Möglichkeit, dass die für Durchschlagbit selektierten Bits Information in Bezug auf dieselben oder angrenzenden Bits in dem digitalen Eingang liefern. Dies steigert die Wahrscheinlichkeit eines Fehlers in der Übertragung in Bezug auf diesen Teil des Eingangssignals.

**Beschreibung der vorliegenden Erfindung**

[0006] Nach einem ersten Aspekt der vorliegenden Erfindung wird eine Ratenanpassungsschaltung geschaffen zum Einstellen der Anzahl Bits in einem Datenblock, wobei der Datenblock eine Anzahl verschachtelter Worte aufweist, die durch die Wirkung einer Verschachtelungsschaltung an einem codierten Ausgang erzeugt worden sind, wobei dieser Ausgang durch die Wirkung einer Codierungsschaltung an einem digitalen Eingang erzeugt worden ist, wobei der codierte Ausgang eine größere Anzahl Bits aufweist als der digitale Eingang, wobei die Ratenanpassungsschaltung Mittel umfasst zum Einstellen der Anzahl Bits in dem Datenblock, wobei ein Ratenanpassungsmuster verwendet wird zum Schaffen von Datenbits zur Übertragung während betreffender Frames eines Übertragungskanals, mit dem Kennzeichen, dass Mittel vorgesehen sind zum Selektieren des Ratenanpassungsmusters je nach den Kennzeichen der Codierungsschaltung und der Verschachtelungsschaltung.

[0007] Mit dem Ausdruck "Ratenanpassungsmuster" ist ein Muster (von Einsen und Nullen) gemeint, das angibt, welche Bits innerhalb einer betreffenden Datenblocks wiederholt oder durchgeschlagen werden sollen.

[0008] Nach der vorliegenden Erfindung braucht die Verschachtelungsschaltung nicht adaptiv zu sein, weil sie selektiert wird als Schnittstelle mit einer Codierungsschaltung mit einer festen Codierungsrate

oder einer beschränkten Anzahl Raten für eine Datenquelle mit einer variablen Datenrate. Die Durchschlagschaltung oder Wiederholungsschaltung arbeitet dann an den verschachtelten Worten um sie derart einzustellen, dass die Ausgangsbitrate geeignet ist für Übertragung über den Übertragungskanal. Das Lösch- oder Wiederholungsmuster wird danach derart selektiert, dass (i) im Falle von Löschung von Bits der Durchbruch den geringsten störenden Effekt auf den digitalen Eingang hat (der vor der Eingang in die Durchschlagschaltung codiert und verschachtelt worden ist) oder (ii) im Falle einer Wiederholung von Bits die Wiederholung den günstigsten Effekt für den Ausgang hat zum Übertragen und nicht auf nur einen Teil des digitalen Eingangs konzentriert ist.

[0009] Auch kann nach der vorliegenden Erfindung die einfache Durchschlagoder Wiederholungsstufe, welche die Ratenanpassung des Eingangssignals beeinflusst, benutzt werden zum Steuern der Übertragungsqualität des Eingangssignals (durch Änderung der Vorwärts-Fehlerkonekturmerkmale) sowie zum Manipulieren der Ausgangsbitrate derart, dass diese geeignet ist zur nachfolgenden Übertragung, beispielsweise zum Anpassen der maximalen Bitrate des Übertragungskanals. Dies vermeidet die Notwendigkeit separater Ratenanpassungsstufen für Qualität von Dienstanforderungen und für Kanalkapazitätsbetrachtung.

[0010] Das Muster für jedes verschachtelte Wort innerhalb des Datenblocks kann gegenüber dem benachbarten verschachtelten Wort oder Worten innerhalb des Blocks versetzt sein. Für eine Blockverschachtelungsschaltung ist das Abzielen verschiedener Bits innerhalb benachbarter Worte des verschachtelten Blocks eine Art und Weise um zu vermeiden, dass benachbarte Bits des codierten Ausgangswortes durch das Wiederholungs/Löschmuster abgezielt werden.

[0011] Das Muster kann als Funktion der Verschachtelungstiefe der Verschachtelungsschaltung selektiert werden.

[0012] Die Codierung umfasst vorzugsweise Faltungscodierung und das Lösch- oder Wiederholungsmuster wird beispielsweise die bedingte Länge der Faltungscodierungsschaltung berücksichtigen.

[0013] Die Ratenanpassungsschaltung ermöglicht es, dass die Ausgangsbitrate gesteuert wird und dies wird insbesondere angewandt, wenn eine Anzahl digitaler Eingänge auf einem einzigen Träger gemultiplext werden soll. Dazu kann ein Kommunikationssystem eine Anzahl Codierungsanordnungen umfassen, je zum Codieren eines betreffenden digitalen Eingangs, und einen Multiplexer zum Kombinieren von Ausgangsdatenworten der Codierungsanordnungen zur nachfolgenden Übertragung durch das Übertragungssystem über den einzelnen Übertragungskanal. Die Ausgänge der verschiedenen Codierungsanordnungen können derart selektiert werden, dass sie verschiedene Datenraten haben, wobei die kombinierte Datenrate der Kanalkapazität des Übertra-

gungskanals entspricht.

[0014] Nach einem zweiten Aspekt der vorliegenden Erfindung wird eine Codierungsanordnung geschaffen, die eine Ratenanpassungsschaltung aufweist, die nach der vorliegenden Erfindung geschaffen ist, und die weiterhin eine Verschachtelungsschaltung und eine Codierschaltung umfasst.

[0015] Nach einem dritten Aspekt der vorliegenden Erfindung wird eine Decodierschaltung geschaffen zum Decodieren eines codierten digitalen Signals mit einem empfangenen Datenblock mit einer Anzahl verschachtelter Worte, wobei der Datenblock von einer Ratenanpassungsschaltung verarbeitet worden ist zum Einstellen der Anzahl Bits in dem Datenblock, wobei die Decodieranordnung eine Rekonstruktionschaltung mit Mitteln aufweist zum Einstellen der Anzahl Bits in dem Datenblock um die Wirkung der Ratenanpassungsschaltung umzukehren, wodurch die verschachtelten Worte rekonstruiert werden, und eine Entschachtelungsschaltung aufweist mit Mitteln zum Erzeugen jeder der Anzahl verschachtelter Worte, sowie einen Kanaldecoder.

#### Kurze Beschreibung der Zeichnung

[0016] Ausführungsbeispiele der vorliegenden Erfindung sind in der Zeichnung dargestellt und werden im Folgenden näher beschrieben. Es zeigen:

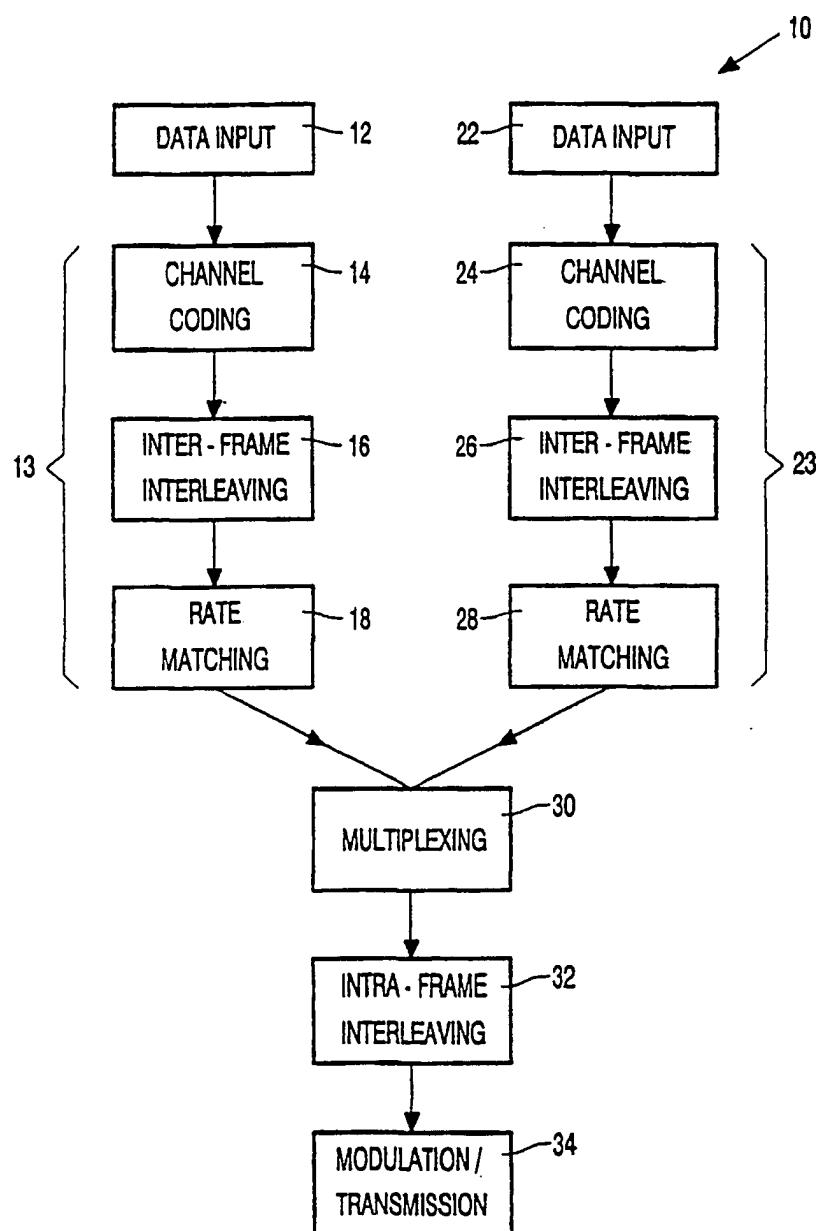

[0017] **Fig. 1** eine schematische Darstellung der Bauteile erforderlich zum Implementieren eines Übertragungssystems unter Verwendung einer Codieranordnung,

[0018] **Fig. 2** eine schematische Darstellung eines Bitstroms, der durch die Codieranordnung hindurchgeht,

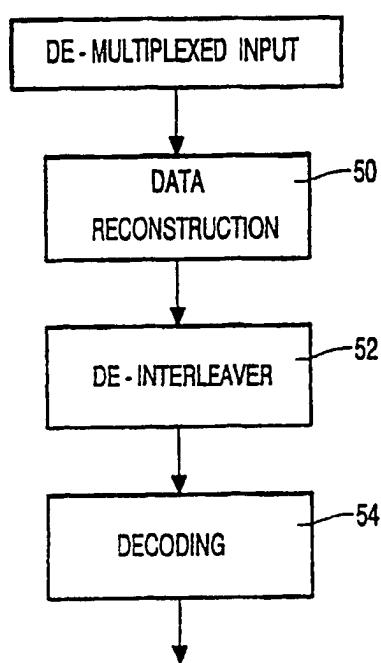

[0019] **Fig. 3** eine schematische Darstellung der Bauteile erforderlich zum Implementieren einer Decodieranordnung nach der vorliegenden Erfindung.

#### Moden zum Durchführen der vorliegenden Erfindung

[0020] **Fig. 1** zeigt eine Ausführungsform einer Codieranordnung zum Codieren eines digitalen Eingang derart, dass die Anzahl Bits zunimmt. Dies ist eine Standard-Annäherung zum Schaffen einer Vorwärts-Fehlerkonekturmöglichkeit und Faltungscodierung ist ein übliches Beispiel. Wie in **Fig. 1** dargestellt, folgt einer Kanalcodierungsstufe (beispielsweise Faltungscodierung) Interframe-Verschachtelung, wobei der verschachtelte Ausgang einer Ratenanpassung ausgesetzt wird, wobei es sich um Durchschlag oder um Bitwiederholung handelt. Der Durchschlag oder die Bitwiederholung erfolgt unter Anwendung eines Lösch-/Wiederholungsmusters, das auf eine Anzahl Bits von der Matrix der Verschachtelungsschaltung **16** zielt. Das Muster wird als eine Funktion der Codierungs- und Verschachtelungsvorgänge selektiert, und zwar derart, dass alle Bits des digitalen Eingangs von nicht-gezielten Bits des Ausgangs der Verschachtelungsschaltung **16** hergeleitet

werden können.

[0021] **Fig. 1** zeigt ein Kommunikationssystem **10** zur Übertragung von Daten von zwei Dateneingängen **12, 22** über einen einzigen Kanal. Jeder Dateneingang ist mit einer betreffenden Codierungsanordnung **13, 23** assoziiert, die eine Faltungscodierung des Eingangs durchführt und ebenfalls Ratenanpassung durchführt, so dass die codierten Daten dem verfügbaren Übertragungskanal aufmoduliert werden können, der eine maximale Kanalkapazität hat.

[0022] Jede Codierungsanordnung **13, 23** umfasst eine betreffenden Kanalcodierungsschaltung **14, 24**. Die Kanalcodierungsschaltung in dem Beispiel nach **Fig. 1** führt eine Faltungscodierung des Dateneingangs durch. Es ist eine Standard-Faltungscodierungsschaltung verfügbar, die eine Anzahl  $k$  Eingangsbits in eine größere Anzahl  $n$  Ausgangsbits umwandelt, mit dem Vorteil, dass Vorwärts-Fehlerkennung implementiert werden kann. Die Codierungsrate wird als ein Verhältnis der Anzahl Eingangsbits zu der Anzahl Ausgangsbits der Codierungsschaltung ausgedrückt und es sind Standard-Faltungscodierungsschaltungen mit Codierungsrationen von beispielsweise  $\frac{1}{2}, \frac{1}{3}, \frac{1}{4}$  verfügbar.

[0023] Faltungscodierungsschaltungen umfassen im Allgemeinen Schieberegister, Funktionsgeneratoren, einen Speicher und einen Multiplexer. Jedes Ausgangsbit der Faltungscodierungsschaltung umfasst eine bekannte Funktion, durchgeführt an einer bestimmten vorhergehenden Anzahl Bits des Eingangssignals, abhängig von der bedingten Länge (der Speicherlänge) der Codierungsschaltung. Es kann eine direkte Darstellung der Eingangsbits zu dem Ausgang geben, sowie einige funktionelle Transformationen, durchgeführt an den Eingangsbits zum Schaffen der zusätzlichen Fehlerkennungsmöglichkeit. Auf alternative Weise kann es auch keine direkte Darstellung von Eingangsbits geben. Der Ausgang der Codierungsschaltung kann durch eine entsprechende Decodierungsschaltung decodiert werden zum Regenerieren des ursprünglichen Dateneingangs sowie von zusätzlichen Daten, geeignet für Datenkorrekturvorgänge.

[0024] Das faltungscodierte Ausgangswort wird einer Verschachtelungsschaltung **16, 26** zugeführt zum Kombinieren einer Anzahl Faltungsausgangsworte und zum Erzeugen eines Datenblocks mit einer entsprechenden Anzahl verschachtelter Worte. Die einfachste Form einer Verschachtelungsschaltung umfasst einen Blockverschachtler, der eine Verschachtelungsmatrix reihenweise mit einer Anzahl Eingangsworte (entsprechend der Verschachtelungstiefe) füllt und die Daten spaltenweise ausliefert. Andere Verschachtelungsschemen sind ebenfalls bekannt. Dieser Prozess macht die Übertragung von Daten weniger empfindlich für Fehler, verursacht durch Zerbrechungen zu dem Übertragungskanal.

[0025] Der verschachtelte Ausgang wird einer Ratenanpassungsschaltung **18, 28** zugeführt, die auf effektive Weise die Codierungsrate der Faltungscodie-

rungsschaltung ändert, so dass die Ausgangsbitrate genauer steuerbar ist. Diese Ratenanpassung kann Durchschlag des verschachtelten Datenblocks (nämlich das Entfernen von Bits) umfassen oder kann Bitwiederholung umfassen. Es ist bekannt, einen faltungscodierten Ausgang durchzuschlagen, damit die Codierungsrate zunimmt, und Beispiele davon sind in UA 5.511.082 gegeben.

[0026] Ein Vorteil der Struktur der oben beschriebenen Codierungsanordnung ist, dass der Ratenanpassungsvorgang dem Codierungsvorgang folgt, mit dem Ergebnis, dass die Verschachtelungsschaltung **16, 26** eine konstante Eingangsbitrate hat, gesteuert durch die Bitrate der Datenquelle und wobei die Reduktion der Bitrate herrührt aus der Faltungscodierungsschaltung **14, 24**. Folglich wird die Notwendigkeit einer adaptiven Verschachtelungsschaltung vermieden.

[0027] Das Ratenanpassungsmuster wird nach der vorliegenden Erfindung abhängig von der Wirkung der Verschachtelungsschaltung und der Codierungsschaltung selektiert. Dies wird nachstehend anhand der **Fig. 2** näher beschrieben.

[0028] Die Ratenanpassungsschaltung **18, 28** ermöglicht auch die Kanalcodierung, damit ein spezieller Dateneingang derart eingestellt wird, dass er einer bestimmten Qualität der Dienstanforderung entspricht, beispielsweise in Bezug auf die Fehlerleistung des Übertragungskanals. Die kombinierten Ratenanpassungsschaltungen **18, 28** werden ebenfalls dazu verwendet, zu gewährleisten, dass die Gesamtbirate der Signale, wenn sie einmal gemultiplext sind, die Übertragungskanalkapazität nicht übersteigt. Auf diese Weise kann ein einziger Ratenanpassungsvorgang benutzt werden um spezifische Anforderungen eines Übertragungskanals in Bezug auf einen einzelnen Dateneingang zu erzielen, sowie um zu gewährleisten, dass die kombinierte Dateninformation erfolgreich übertragen werden kann. Es wird zwischen der erzielbaren Fehlerleistung der einzelnen Datenkanäle und der kombinierten Datenrate ein Kompromiss geben, aber diese Erwägungen werden mit einer einzelnen Ratenanpassungsschaltung für jede Codierungsanordnung erzielt.

[0029] Die Ausgänge der beiden Codierungsanordnungen **13, 23** werden zusammen durch eine Multiplexschaltung **30** gemultiplext um eine Übertragung über den einzigen Kanal zu ermöglichen. Der Ausgang der Multiplexschaltung ist effektiv ein Datenframe zur Übertragung über den Kanal und das Frame kann in seiner Größe einem Block verschachtelter Daten entsprechen. Die Framedaten können durch eine Intra-Frame-Verschachtelungsschaltung **32** verschachtelt werden zur nachfolgenden Übertragung durch eine Faltungsmodulations- und -übertragungsschaltung **34**.

[0030] Die Wirkungsweise der Codierungsanordnung **13, 23** aus **Fig. 1** ist in **Fig. 2** detailliert dargestellt.

[0031] In **Fig. 2** zeigt Teil A deutlichkeitshalber eine

Sequenz von Eingangsdatenbits, die der Codierungsanordnung zugeführt werden. Diese können als Worte einer vorbestimmten Anzahl Bits oder als ein kontinuierlicher Datenstrom, wie dargestellt, gegliedert werden.

[0032] Die Kanalcodierungsschaltung **14, 24** führt eine Faltungscodierung an dem Eingangsdatenstrom durch und erzeugt einen Bitstrom mit einer größeren Anzahl Bits. In dem in **Fig. 2** dargestellten Beispiel verwandelt die Faltungscodierungsschaltung einen Datenstrom mit der Länge  $k$  in einen Strom mit der Länge  $n$ , wie dargestellt, was effektiv die Anzahl Bits zur Übertragung um  $n/k$  steigert. Verschachtelung wird an den codierten Datenworten durchgeführt und in dem in **Fig. 2** dargestellten Beispiel arbeitet die Inter-Frame-Verschachtelungsschaltung **16** an 8-Bit-Worten von dem codierten Datenstrom und wendet einen Blockverschachtelungsalgorithmus mit einer Tiefe 4 an. Auf diese Weise füllt die Verschachtelungsschaltung eine Verschachtelungsmatrix von 4 Spalten und 8 Reihen reihenweise, bitweise.

[0033] Der in **Fig. 2** Teil C dargestellte Datenblock wird einem Löschenmuster oder einem Wiederholungsmuster ausgesetzt um die Bitrate derart zu ändern, dass alle Signale, wenn sie gemultiplext sind, zusammen einen Datenstrom erzeugen, der durch den verfügbaren Übertragungskanal verarbeitet werden kann.

[0034] Die Anmelderin hat erkannt, dass das Löschen- oder Wiederholungsmuster derart selektiert werden soll, dass es nicht erforderlich ist, dass die gelöschten oder wiederholten Bits es ermöglichen, dass alle Bits von dem digitalen Eingang rekonstruiert werden.

[0035] So kann beispielsweise vorausgesetzt werden, dass eine Faltungscodierungsschaltung mit geringer bedingter Länge benutzt wird. Der Effekt dabei ist, dass es zwischen den codierten Daten und den Eingangsdaten eine direkte Darstellung gibt, so dass benachbarte codierte Datenbits Information über benachbarte Bits des digitalen Eingangssignals liefern werden. Das Löschen oder Wiederholen benachbarter Eingangsbits soll vermieden werden, weil (i) im Falle von Lösung von Bits die Wahrscheinlichkeit eines Fehlers in der Übertragung in Bezug auf diesen Teil der Eingangsdaten vergrößert wird, und (ii) im Falle einer Wiederholung von Bits die zusätzliche Kapazität gleichmäßig über den Eingangsdatenstrom verteilt wird, damit die Wiederholung die Gesamtfehlerleistung der Übertragung verbessert. Es wird möglich sein, eine Lösung benachbarter Bits in dem digitalen Eingang für niedrige Durchschlagraten zu vermeiden.

[0036] Eine einfache Anwendung von Lösung oder Wiederholung an dem Ausgang der Verschachtelungsschaltung **16, 26** kann schlechte Resultate in der Verschachtelungstiefe (Anzahl Spalten) und in der Löschen-/Wiederholungsrate ergeben. Wenn beispielsweise jedes vierte Bit gelöscht oder wiederholt wird, wenn der durch **Fig. 2** Teil C dargestellte Datenblock (spaltenweise) ausgelesen wird, wird das Er-

gebnis sein, vier benachbarte Bits in der ersten Reihe ( $A_{11}$  bis  $A_{14}$ ) und in der fünften Reihe ( $A_{31}$ , bis  $A_{34}$ ) zu löschen oder zu wiederholen.

[0037] Folglich sind in dem in **Fig. 2** Teil D dargestellten Löschen-/Wiederholungsmuster die Bits zur Lösung oder Wiederholung mit maximal einem solchen Bit in jeder Reihe der Verschachtelungsmatrix selektiert worden. In dem in **Fig. 2** dargestellten be treffenden Beispiel wird das Löschenmuster für jedes verschachtelte Wort **44** gegenüber dem benachbarten verschachtelten Wort oder Worte innerhalb des Blocks versetzt. So hat beispielsweise das verschachtelte Wort **44a** ein darauf angewandtes Löschen-/Wiederholungsmuster (100000100), während das verschachtelte Wort **44b** ein darauf angewandtes Löschen-/Wiederholungsmuster (01000010), usw. Durch Versatz des Musters in benachbarten Spalten wird das Problem der Lösung oder der Wiederholung benachbarter Bits vermieden und das Muster lässt sich auf einfache Art und Weise implementieren.

[0038] In einem allgemeineren Fall werden die Einzelheiten des gewählten Löschen-/Wiederholungsmusters abhängig sein von der Größe der Verschachtelungsmatrix und von dem Ausmaß der Lösung oder Wiederholung. Insbesondere kann die Verschachtelungsmatrix ziemlich größer sein als das einfache Beispiel aus **Fig. 2**. Für eine Matrix mit  $N$  Spalten kann ein geeignetes Löschen-/Wiederholungsmuster dadurch erhalten werden, dass in allen  $P$  Bits ein Bit gewählt wird, das sich reihe für Reihe durch die Matrix fortsetzt. Wenn beispielsweise  $P$  gleich  $N + 1$  ist, wird ein Muster gleich dem aus **Fig. 2** Teil D mit benachbartem Spaltenversatz um eine Reihe das Resultat sein.

[0039] Auch die Verschachtelungsschaltung **16, 26** kann komplexer sein als die aus dem oben gegebenen Beispiel. Dem Fachmann sind viele alternative Verschachtelungsschaltungen, geeignet zum Gebrauch in einer Codierungsanordnung nach der vorliegenden Erfindung bekannt, beispielsweise Neu gliederung der Spalten der Verschachtelungsmatrix vor dem Auslesen. Folglich wird es notwendig sein, dass das Löschen-/Wiederholungsmuster geändert werden soll um die Merkmale der Verschachtelungsschaltung zu berücksichtigen. Eine Methode dies zu machen ist, die maximale Löschen-/Wiederholungsrate (sagen wir ein Bit in jedem  $P$ ) zu ermitteln und der Verschachtelungsschaltung, in der jedes  $P$  Bit gesetzt wird, einen Eingangsdatenstrom zuzuführen. Der Ausgang der Verschachtelungsschaltung ist dann ein geeignetes Löschen-/Wiederholungsmuster. Es dürfte einleuchten, dass das Löschen-/Wiederholungsmuster nach **Fig. 2** Teil D dadurch hätte erhalten werden können, dass der Verschachtelungsschaltung **16, 26** ein Datenstrom zugeführt wird, in das jedes fünfte Bit gesetzt wurde.

[0040] Das Muster aus **Fig. 2** Teil D kann ein maximales Ausmaß an erlaubtem Durchschlag oder an erlaubter Bitwiederholung darstellen. In diesem Fall

wäre es für geringere Durchschlag- oder Wiederholungsraten möglich, nur einen Teil der Lösch- oder Wiederholungsbits zu selektieren, damit die gewünschte End-Bitrate erzielt wird.

[0041] Eine Durchschlaggrenze kann als allgemeine Grenze gesetzt werden oder kann für jeden Dateneingangskanal gesetzt werden, sogar dynamisch. In diesem Fall können deterministische Algorithmen oder Darstellungen zum genauen Durchschlagen entworfen werden um jede bestimmte Durchschlagrate zu erzielen. Nicht einheitliche Durchschlaggitter können ebenfalls betrachtet werden.

[0042] Ein Durchschlag- oder Wiederholungsmuster kann für die maximale Verschachtelungstiefe bestimmt werden und das Muster für eine verschiedene Codierungsanordnung innerhalb des Kommunikationssystems und mit einer anderen Verschachtelungstiefe kann als eine reduzierte Anzahl Spalten der größeren Musters definiert werden. Jedes Frame zur Übertragung kann dann mit einer der möglichen Durchschlagspalten (beispielsweise 44a, 44b) assoziiert werden, abhängig von der Verschachtelungstiefe und der spezielle Durchschlag oder die spezielle Wiederholung für jedes Frame kann auf einfache Weise durch empfangende Schaltungsanordnung bestimmt werden, und zwar aus den Kenntnissen der Verschachtelungstiefe der betreffenden Codierungsanordnung. Ohne zusätzliche Signalisierung.

[0043] Obschon zwei Eingangskanäle in den Figuren dargestellt sind als seien sie gemultiplext um gemeinsam über einen einzigen Kanal übertragen zu werden, ist es selbstverständlich möglich, gemeinsam eine viel größere Anzahl Eingangskanäle zu multiplexen.

[0044] Faltungscodierung ist beschrieben worden als eine bestimmte Möglichkeit einer Codierungs-technik, aber es dürfte dem Fachmann einleuchten, dass andere FEC-Schemen, wie Blockcodierungsschemen oder Turbo-Codierung angewandt werden können.

[0045] Eine besondere Anwendung der vorliegenden Erfindung ist für das Aufwärtssignal von einer mobilen Telekommunikationsstation zu einer Basisstation und wobei die mobile Station verschiedene Typen von Datenquellen unterstützen kann. Eine Vorwärtsblockverschachtler ist beschrieben worden, obschon dem Fachmann mehrere andere Verschachtelungsoptionen bekannt sein dürften. Welche Verschachtelungsmethode gewählt worden ist, das durch die vorliegende Erfindung implementierte Wiederholungs- oder Löschmuster berücksichtigt den Effekt des Verschachtelungsvorgangs, so dass das Lösch-/Wiederholungsmuster selektiert wird unter Berücksichtigung der ursprünglichen Datensequenz. Eine Decodierungsanordnung wird ebenfalls erforderlich sein als Teil eines Empfangssystems zum Bilden eines kompletten Kommunikationssystems. Ein Beispiel der Decodierungsanordnung ist in **Fig. 3** schematisch dargestellt und umfasst eine Datenrekonstruktionsschaltung 50, die einen gedemultiplex-

ten Eingang erhält.

[0046] Die rekonstruierten Daten werden einer Entschachtelungsschaltung 52 sowie einem Kanaldecoder 54 zugeführt.

[0047] Für eine durchgeschlagene Übertragung füllt die Datenrekonstruktionsschaltung 50 die durchgeschlagenen Bits mit Dummybits. Dies ermöglicht es, dass die Entschachtelung durchgeführt wird zum Rekonstruieren der codierten Eingangssequenz, aber mit einigen Dummybits. Die Decodierungsschaltung kann die Stelle der Dummybits aus der bekannten Verschachtelungsmatrix und dem bekannten Durchschlagmuster herleiten und kann dadurch die Dummybits während der Rekonstruktion der ursprünglichen Datensequenz vermeiden.

[0048] Für eine Übertragung mit wiederholten Bits wird die Datenrekonstruktionsschaltung 50 die Bitwiederholungen entfernen, wird aber auch die Wiederholungen benutzen zum Schaffen einer Schätzung des Wertes des betreffenden Bits mit einer niedrigeren Fehlerwahrscheinlichkeit. Eine weiche Kombinationstechnik kann angewandt werden zum Herleiten des wahrscheinlichsten Wertes für das betreffende Bit aus der Anzahl empfangener Wiederholungen.

[0049] Das beschriebene Codierungssystem kann nur für eine Aufwärtsübertragung in einem zellularen drahtlosen Telephonnetzwerk benutzt werden, oder es kann für die Aufwärts- sowie Abwärtsübertragungskanäle in einem derartigen Netzwerk benutzt werden. Das System kann in dem UMTS-Drahtlos-Kommunikationsnetzwerk implementiert werden.

### Industrielle Anwendbarkeit

[0050] Die vorliegende Erfindung kann bei Funk-Kommunikationssystemen wie UMTS angewandt werden.

### Text in der Zeichnung

### Bezugszeichenliste

Fig. 1

|    |                            |

|----|----------------------------|

| 12 | Dateneingang               |

| 14 | Kanalcodierung             |

| 16 | Interframe-Verschachtelung |

| 18 | Ratenanpassung             |

| 22 | Dateneingang               |

| 24 | Kanalcodierung             |

| 26 | Interframe-Verschachtelung |

| 28 | Ratenanpassung             |

| 30 | Multiplexen                |

| 32 | Intraframe-Verschachtelung |

| 34 | Modulation/Übertragung     |

Fig. 2A

Dateneingang

Fig. 2B

Dateneingang

Fig. 2C

Verschachtelungsmatrix

Fig. 2D

Lösch-/Wiederholungsmuster

Fig. 3

Gedemultiplexer Eingang

50 Datenrekonstruktion

52 Entschachtlung

54 Decodierung

**Patentansprüche**

1. Ratenanpassungsschaltung zum Einstellen der Anzahl Bits in einem Datenblock, wobei dieser Datenblock eine Anzahl verschachtelter Worte enthält, erzeugt durch die Wirkung einer Verschachtelungsschaltung (16, 26) an einem codierten Ausgang, erzeugt durch die Wirkung einer Codierungsschaltung (14, 24) an einem digitalen Eingang (12, 25), wobei der codierte Ausgang eine größere Anzahl Bits hat als der digitale Eingang, wobei die Ratenanpassungsschaltung (18, 28) Mittel aufweist zum Einstellen der Anzahl Bits in dem Datenblock unter Verwendung eines Ratenanpassungsmusters zum Schaffen von Datenbits zur Übertragung während der betreffenden Frames eines Übertragungskanals, **dadurch gekennzeichnet**, dass Mittel vorgesehen sind zum Selektieren des Ratenanpassungsmusters (44) je nach den Merkmalen der Codierungsschaltung (14, 24) und der Verschachtelungsschaltung (16, 26).

2. Ratenanpassungsschaltung nach Anspruch 1, dadurch gekennzeichnet, dass das Ratenanpassungsmuster derart selektiert wird, dass alle Bits des digitalen Eingangs von dem restlichen Teil der Bits in aufeinander folgenden verschachtelten Blöcken hergeleitet werden können.

3. Ratenanpassungsschaltung nach Anspruch 1 oder 2, dadurch gekennzeichnet, dass das Ratenanpassungsmuster (44a, 44b) für jedes verschachtelte Wort innerhalb des Datenblocks gegenüber dem (den) angrenzenden verschachtelten Wort oder Wörtern innerhalb des Blocks versetzt ist.

4. Ratenanpassungsschaltung nach einem der Ansprüche 1 bis 3, dadurch gekennzeichnet, dass das Ratenanpassungsmuster (44) als eine Funktion der Verschachtelungstiefe der Verschachtelungsschaltung (16, 26) selektiert wird.

5. Codierungsanordnung mit einer Ratenanpassungsschaltung (18, 28) nach einem der Ansprüche 1 bis 4, weiterhin mit einer Verschachtelungsschaltung (16, 26) und einer Codierungsschaltung (14, 24).

6. Decodierungsanordnung zum Decodieren eines codierten digitalen Signals mit einem empfangenen Datenblock mit einer Anzahl verschachtelter Worte, wobei der Datenblock durch eine Codierungsanordnung verarbeitet worden ist zum Einstellen der Anzahl Bits in dem Datenblock, wobei die Decodierungsanordnung eine Datenrekonstruktionsschaltung (50) aufweist mit Mitteln zum Einstellen der Anzahl Bits in dem Datenblock entsprechend einem Ratenanpassungsmuster um die Wirkung der Datenanpassungsschaltung (18, 28) umzukehren, wodurch die verschachtelten Worte rekonstruiert werden, wobei eine Entschachtelungsschaltung (52) Mittel aufweist zum Erzeugen jedes der Anzahl verschachtelter Worte und einen Kanaldecoder (54), dadurch gekennzeichnet, dass Mittel vorgesehen sind zum Selektieren des Ratenanpassungsmusters in Abhängigkeit von den Merkmalen der Codierungsanordnung.

Es folgen 3 Blatt Zeichnungen

FIG. 1

DATA INPUT:  $a_{11} a_{12} \dots a_{1k} a_{21} a_{22} \dots a_{2k} a_{31} a_{32} \dots a_{3k} \dots$

FIG. 2A

DATA INPUT:  $A_{11} A_{12} \dots A_{1n} A_{21} A_{22} \dots A_{2n} A_{31} A_{32} \dots A_{3n} \dots$

FIG. 2B

INTERLEAVING MATRIX

|          |          |          |          |

|----------|----------|----------|----------|

| $A_{11}$ | $A_{12}$ | $A_{13}$ | $A_{14}$ |

| $A_{15}$ | $A_{16}$ | $A_{17}$ | $A_{18}$ |

| $A_{21}$ | $A_{22}$ | $A_{23}$ | $A_{24}$ |

| $A_{25}$ | $A_{26}$ | $A_{27}$ | $A_{28}$ |

| $A_{31}$ | $A_{32}$ | $A_{33}$ | $A_{34}$ |

| $A_{35}$ | $A_{36}$ | $A_{37}$ | $A_{38}$ |

| $A_{41}$ | $A_{42}$ | $A_{43}$ | $A_{44}$ |

| $A_{45}$ | $A_{46}$ | $A_{47}$ | $A_{48}$ |

FIG. 2C

DELETION / REPETITION PATTERN

|     |     |    |    |

|-----|-----|----|----|

| 44a | 44b | 44 | 44 |

| 1   | 0   | 0  | 0  |

| 0   | 1   | 0  | 0  |

| 0   | 0   | 1  | 0  |

| 0   | 0   | 0  | 1  |

| 0   | 0   | 0  | 0  |

| 1   | 0   | 0  | 0  |

| 0   | 1   | 0  | 0  |

| 0   | 0   | 1  | 0  |

FIG. 2D

FIG. 3