(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5917285号

(P5917285)

(45) 発行日 平成28年5月11日(2016.5.11)

(24) 登録日 平成28年4月15日(2016.4.15)

(51) Int.Cl.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO3K 3/356   | (2006.01) | HO3K 3/356 | D    |

| HO1L 21/8242 | (2006.01) | HO1L 27/10 | 621Z |

| HO1L 27/108  | (2006.01) | HO1L 27/10 | 671C |

| HO1L 27/105  | (2006.01) | HO1L 27/10 | 671Z |

| HO1L 27/10   | (2006.01) | HO1L 27/10 | 441  |

請求項の数 6 (全 21 頁) 最終頁に続く

(21) 出願番号

特願2012-109004 (P2012-109004)

(22) 出願日

平成24年5月11日(2012.5.11)

(65) 公開番号

特開2013-236344 (P2013-236344A)

(43) 公開日

平成25年11月21日(2013.11.21)

審査請求日

平成27年5月1日(2015.5.1)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 福留 貴浩

栃木県栃木市都賀町升塚161-2 アド

バンスト フィルム ディバイス インク

株式会社内

審査官 柳下 勝幸

最終頁に続く

(54) 【発明の名称】半導体装置の駆動方法

(57) 【特許請求の範囲】

【請求項 1】

データを保持することが可能な揮発性の保持ノードと、

パワーゲーティング期間中に前記データを保持するキャパシタと、

前記保持ノードと前記キャパシタを電気的に接続させるか否かを選択する、チャネルが酸化物半導体層に形成されるトランジスタと、を有し、

前記トランジスタは、

前記パワーゲーティング期間が開始される前にオフ状態となってから前記パワーゲーティング期間中に渡ってオフ状態を維持し、

前記パワーゲーティング期間経過後にオン状態となってから再度パワーゲーティング期間が開始される前までに渡ってオン状態を維持する、ことを繰り返す半導体装置の駆動方法。

【請求項 2】

データを保持することが可能な揮発性の保持ノードと、

パワーゲーティング期間中に前記データを保持するキャパシタと、

前記保持ノードと前記キャパシタを電気的に接続させるか否かを選択する、チャネルが酸化物半導体層に形成されるトランジスタと、を有し、

前記トランジスタは、

前記パワーゲーティング期間が開始される際にオフ状態となってから前記パワーゲーティング期間中に渡ってオフ状態を維持し、

10

20

前記パワーゲーティング期間経過後にオン状態となってから再度パワーゲーティング期間が開始されるまでに渡ってオン状態を維持する、ことを繰り返す半導体装置の駆動方法

【請求項3】

請求項1又は請求項2において、

前記パワーゲーティング期間経過後に前記トランジスタがオン状態となる際に前記保持ノードを浮遊状態とする半導体装置の駆動方法。

【請求項4】

それぞれにおいて同一のデータを保持することが可能な揮発性の第1の保持ノード及び第2の保持ノードと、

パワーゲーティング期間中に前記データを保持するキャパシタと、

前記第1の保持ノードと前記キャパシタを電気的に接続させるか否かを選択する、チャネルが酸化物半導体層に形成される第1のトランジスタと、

前記第2の保持ノードと前記キャパシタを電気的に接続させるか否かを選択する、チャネルが酸化物半導体層に形成される第2のトランジスタと、を有し、

前記第1のトランジスタは、

前記パワーゲーティング期間が開始される前にオフ状態となってから前記パワーゲーティング期間中に渡ってオフ状態を維持し、

前記パワーゲーティング期間経過後にオン状態となってから再度パワーゲーティング期間が開始される前までに渡ってオン状態を維持する、ことを繰り返し、

前記第2のトランジスタは、

前記パワーゲーティング期間が開始される前にオフ状態となってから前記パワーゲーティング期間中に渡ってオフ状態を維持し、

前記第1のトランジスタのゲートには、前記パワーゲーティング期間以外の期間に渡って前記第2のトランジスタのゲートに供給される信号の反転信号が供給される半導体装置の駆動方法。

【請求項5】

それぞれにおいて同一のデータを保持することが可能な揮発性の第1の保持ノード及び第2の保持ノードと、

パワーゲーティング期間中に前記データを保持するキャパシタと、

前記第1の保持ノードと前記キャパシタを電気的に接続させるか否かを選択する、チャネルが酸化物半導体層に形成される第1のトランジスタと、

前記第2の保持ノードと前記キャパシタを電気的に接続させるか否かを選択する、チャネルが酸化物半導体層に形成される第2のトランジスタと、を有し、

前記第1のトランジスタは、

前記パワーゲーティング期間が開始される際にオフ状態となってから前記パワーゲーティング期間中に渡ってオフ状態を維持し、

前記パワーゲーティング期間経過後にオン状態となってから再度パワーゲーティング期間が開始されるまでに渡ってオン状態を維持する、ことを繰り返し、

前記第2のトランジスタは、

前記パワーゲーティング期間が開始される前にオフ状態となってから前記パワーゲーティング期間中に渡ってオフ状態を維持し、

前記第1のトランジスタのゲートには、前記パワーゲーティング期間以外の期間に渡って前記第2のトランジスタのゲートに供給される信号の反転信号が供給される半導体装置の駆動方法。

【請求項6】

請求項4又は請求項5において、

前記パワーゲーティング期間経過後に前記第2のトランジスタがオン状態となる際に前記第2の保持ノードを浮遊状態とする半導体装置の駆動方法。

【発明の詳細な説明】

10

20

30

40

50

## 【技術分野】

## 【0001】

本発明は、半導体装置及びその駆動方法に関する。特に、パワーゲーティングが行われる半導体装置及びその駆動方法に関する。なお、本明細書において半導体装置とは、半導体特性を利用することで機能しうる装置を指すこととする。

## 【背景技術】

## 【0002】

Central Processing Unit (CPU) 等の消費電力を低減する技術として、パワーゲーティングが注目されている。パワーゲーティングは、当該CPUの一部又は全部が動作しない場合に、その一部又は全部に対する電源電圧の供給を停止する技術である。これにより、静的な消費電力 (CPUの一部又は全部の状態を維持するために消費される電力) の抑制を図ることが可能である。

10

## 【0003】

ただし、パワーゲーティングを行った場合には、各種のノードにおける論理状態の消失及び各種のメモリに保持されているデータ (以下、単に「データ」という) の消失などが生じることになる。そのため、パワーゲーティングが終了 (電源電圧の供給を再開) した後、即座に動作を再開することはできない。この場合には、動作の再開に先だって、消失されたデータを復元することが必要となるからである。よって、各種の半導体装置に対してパワーゲーティングを行う場合、当該半導体装置の動作遅延が生じることになる。

## 【0004】

20

これに対して、パワーゲーティング前に各種のノードに保持されているデータを不揮発性のメモリに退避させ、そして、当該パワーゲーティング後にそれらを復元することで動作遅延の発生を抑制する技術が開発されている。例えば、特許文献1では、Static

Random Access Memory (SRAM) に保持されているデータを不揮発性のメモリに退避する技術が開示されている。なお、特許文献1では、チャネルが酸化物半導体層に形成されるトランジスタ (容量用スイッチング素子) と、当該トランジスタがオフ状態となることによって一方の端子が電気的に接続するノードが浮遊状態となるキャパシタ (容量素子) とによって当該メモリが構成されている。

## 【先行技術文献】

## 【特許文献】

30

## 【0005】

## 【特許文献1】特開2011-171723号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0006】

本発明の一態様は、パワーゲーティングを行う際の処理の簡便化を図ることを目的のとする。

## 【課題を解決するための手段】

## 【0007】

本発明の一態様の半導体装置では、データを保持することが可能な揮発性の保持ノードと、キャパシタと、当該保持ノードと当該キャパシタを電気的に接続させるか否かを選択するチャネルが酸化物半導体層に形成されるトランジスタとを設ける。そして、当該トランジスタが、半導体装置に対するパワーゲーティングが行われる期間以外のほぼ全ての期間においてオン状態を維持することを要旨とする。

40

## 【0008】

例えば、本発明の一態様は、データを保持することが可能な揮発性の保持ノードと、パワーゲーティング期間中にデータを保持するキャパシタと、保持ノードとキャパシタを電気的に接続させるか否かを選択する、チャネルが酸化物半導体層に形成されるトランジスタと、を有し、トランジスタが、パワーゲーティング期間以前にオフ状態となってからパワーゲーティング期間中に渡ってオフ状態を維持する第1の行程と、パワーゲーティング

50

期間後にオン状態となってからパワーゲーティング期間前までに渡ってオン状態を維持する第2の行程と、を繰り返す半導体装置の駆動方法である。

【発明の効果】

【0009】

本発明の一態様の半導体装置の駆動方法では、半導体装置が動作中のほぼ全ての期間において、保持ノードとキャパシタの間に設けられているトランジスタがオン状態を維持する。よって、キャパシタが常時保持ノードのデータと対応するデータを有することになるとともに、当該トランジスタをオフ状態とすることのみによって当該保持ノードから当該キャパシタへのデータの退避が完了する。すなわち、簡便な処理（当該トランジスタをオフ状態とすること）によってパワーゲーティングを行うための準備を完了させることができとなる。

10

【図面の簡単な説明】

【0010】

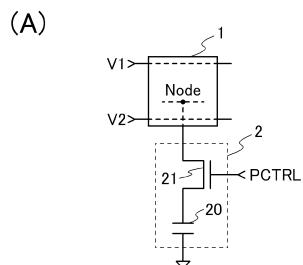

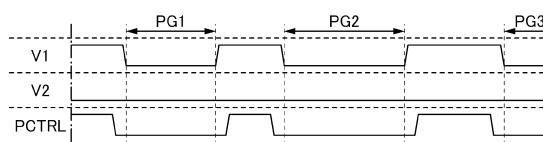

【図1】半導体装置の（A）構成例を示す図、（B）、（C）動作例を示すタイミングチャート。

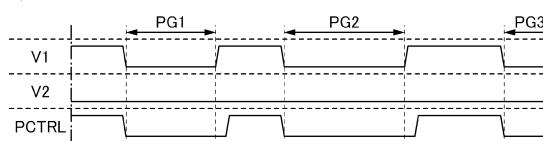

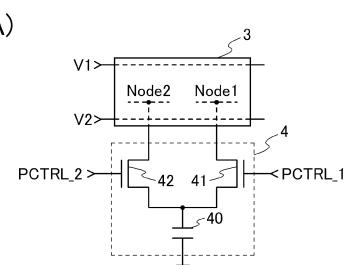

【図2】半導体装置の（A）構成例を示す図、（B）、（C）動作例を示すタイミングチャート。

【図3】（A）、（B）半導体装置の具体例を示す回路図。

【図4】（A）、（B）半導体装置の具体例を示す回路図。

【図5】（A）、（B）半導体装置の具体例を示す回路図。

20

【図6】（A）、（B）半導体装置の具体例を示す回路図。

【図7】半導体装置の構造例を示す図。

【図8】半導体装置の構造例を示す図。

【図9】半導体装置の構造例を示す図。

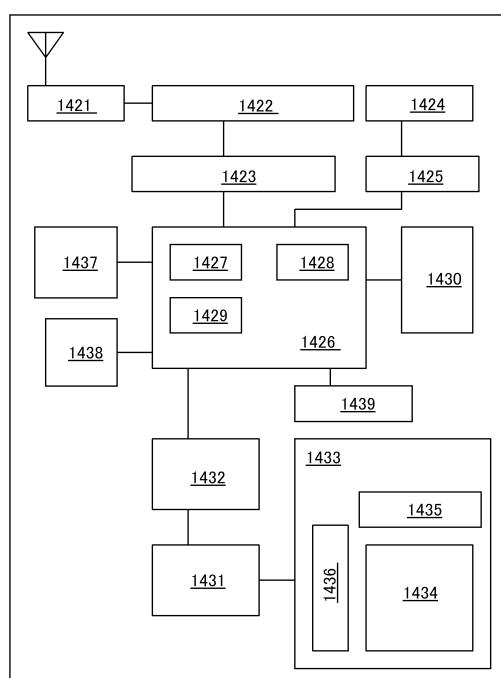

【図10】携帯用の電子機器のブロック図。

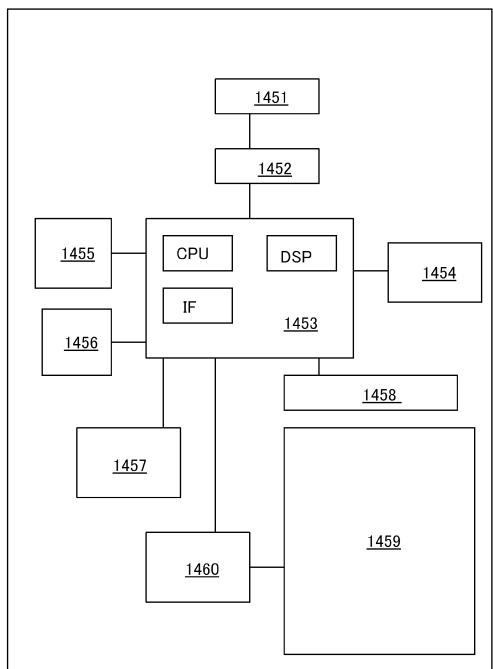

【図11】電子書籍のブロック図。

【発明を実施するための形態】

【0011】

以下では、本発明の一態様について詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態を々々に変更し得る。したがって、本発明は以下に示す記載内容に限定して解釈されるものではない。

30

【0012】

<半導体装置>

図1、2を参照して半導体装置の構成例及び動作例について説明する。

【0013】

<構成例1：図1（A）>

図1（A）は、本発明の一態様に係る半導体装置の構成例を示す図である。図1（A）に示す半導体装置は、特定のノード（Node）においてデータを保持することが可能な揮発性の回路1と、パワーゲーティング期間中に当該データを保持する不揮発性のメモリ2とを有する。具体的には、図1（A）に示す半導体装置では、パワーゲーティング期間以前に回路1がノード（Node）において保持するデータをメモリ2に退避させ、当該パワーゲーティング期間後にメモリ2に退避されているデータを用いて回路1のノード（Node）におけるデータを復元することが可能な半導体装置である。

40

【0014】

なお、回路1には、電源電位V1を供給する配線及び電源電位V2を供給する配線が設けられている。電源電位V1は、高電源電位（VDD）とパワーゲーティング電位のいずれかの電位となる電圧であり、電源電位V2は、低電源電位（VSS）と当該パワーゲーティング電位のいずれかの電位となる電圧である。なお、本明細書において、パワーゲーティング電位とは、パワーゲーティング期間において電源電位V1及び電源電位V2がとる電位である。例えば、パワーゲーティング電位として、接地電位、0（V）、任意の値

50

の固定電位を適用することが可能である。図1(A)に示す半導体装置においては、当該パワーゲーティング電位として低電源電位(VSS)を適用することとする。また、回路1には、データの復元が行われる際にノード(Node)を浮遊状態とする手段を設けられていることが好ましい。仮に、論理ゲートの出力がノード(Node)と電気的に接続されている場合には、データの復元時にメモリ2に保持されているデータ(電荷)が消失する可能性があるためである。

#### 【0015】

また、メモリ2には、パワーゲーティング期間中にデータを保持するキャパシタ20と、ノード(Node)とキャパシタ20を電気的に接続させるか否かを選択するトランジスタ21とが設けられている。なお、トランジスタ21は、チャネルが酸化物半導体層に形成されるトランジスタである。さらに、トランジスタ21のスイッチングは、ゲートに入力されるパワーゲーティング制御信号(PCTRL)によって制御されている。なお、パワーゲーティング制御信号(PCTRL)は、高電源電位(VDD)及び低電源電位(VSS)並びにパワーゲーティング電位のいずれかの電位となる信号である。そして、これらの電位の具体的な値は、トランジスタ21のゲートに高電源電位(VDD)が供給される際にトランジスタ21がオン状態となり、低電源電位(VSS)又はパワーゲーティング電位が供給される際にトランジスタ21がオフ状態になるように設定されている。

#### 【0016】

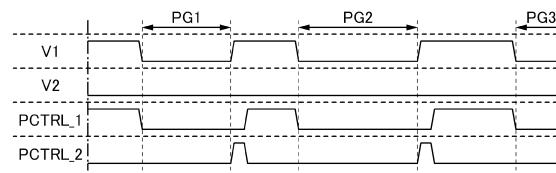

<構成例1の動作例1：図1(B)>

図1(B)は、図1(A)に示す半導体装置の動作例を示すタイミングチャートである。図1(B)に示すタイミングチャートでは、パワーゲーティング期間(PG1、PG2、PG3)において電源電位V1及び電源電位V2並びにパワーゲーティング制御信号(PCTRL)が共にパワーゲーティング電位(ここでは、低電源電位VSSとする)となる。また、パワーゲーティング期間(PG1、PG2、PG3)以外の期間において電源電位V1が高電源電位(VDD)となり、電源電位V2が低電源電位(VSS)となり、パワーゲーティング制御信号(PCTRL)が高電源電位(VDD)又は低電源電位(VSS)となる。

#### 【0017】

以下、図1(B)に示すタイミングチャートにおけるパワーゲーティング制御信号(PCTRL)について詳細に述べる。パワーゲーティング制御信号(PCTRL)は、パワーゲーティングが開始される前に低電源電位(VSS)となる。そして、パワーゲーティングが終了後も一定期間に渡って低電源電位(VSS)となる。なお、当該一定期間が経過した後に高電源電位(VDD)となる。この状態は、再度パワーゲーティングが行われる前まで維持される。

#### 【0018】

これにより、トランジスタ21は、パワーゲーティング前にオフ状態となってからパワーゲーティング終了後一定期間が経過するまでに渡ってオフ状態を維持することになる。そして、トランジスタ21がオフ状態となる期間に渡って、キャパシタ20に蓄積されている電荷(データ)も保持されることになる。チャネルが酸化物半導体層に形成されるトランジスタ21は、オフ電流値が極めて小さいからである。また、トランジスタ21は、当該期間経過後にオン状態となってから再度パワーゲーティングが開始される前までに渡ってオン状態を維持することになる。なお、図1(B)に示すタイミングチャートに従つて図1(A)に示す半導体装置が動作する場合、パワーゲーティング前にトランジスタ21がオフ状態となることによってデータの退避が行われ、パワーゲーティング後にトランジスタ21がオン状態になることによってデータの復元が行われることになる。よって、この場合には、簡便な処理によってパワーゲーティングを行う際にデータの退避を行うことが可能である。

#### 【0019】

<構成例1の動作例2：図1(C)>

図1(C)は、図1(A)に示す半導体装置の動作例を示すタイミングチャートである

10

20

30

40

50

。図1(C)に示すタイミングチャートは、パワーゲーティング期間(PG1、PG2、PG3)の間の期間において、パワーゲーティング制御信号(CTRL)が高電源電位(VDD)となった後に低電源電位(VSS)とならない(パワーゲーティング期間(PG1、PG2、PG3)が開始する際に、高電源電位(VDD)から直接的にパワーゲーティング電位へと変化する)点を除き、図1(B)に示すタイミングチャートと同様のタイミングチャートである。

【0020】

図1(C)に示すタイミングチャートに従って図1(A)に示す半導体装置が動作する場合、パワーゲーティングを行うための準備を行うことなくパワーゲーティングが開始されることになる。よって、図1(B)に示すタイミングチャートに従って図1(A)に示す半導体装置が動作する場合よりも簡便な処理によってパワーゲーティングを行うことが可能となる。他方、図1(B)に示すタイミングチャートに従って図1(A)に示す半導体装置が動作する場合には、データの退避を確実に行うことが可能である。

10

【0021】

<構成例2：図2(A)>

図2(A)は、図1(A)とは異なる半導体装置の構成例を示す図である。図2(A)に示す半導体装置は、2種のノード(Node1、Node2)において同一のデータを保持することが可能な揮発性の回路3と、パワーゲーティング期間中に当該データを保持する不揮発性のメモリ4とを有する。具体的には、図2(A)に示す半導体装置では、パワーゲーティング期間以前に回路3が第1のノード(Node1)において保持するデータをメモリ2に退避させ、当該パワーゲーティング期間後にメモリ2に退避されているデータを用いて回路3の第2のノード(Node2)におけるデータを復元することが可能な半導体装置である。

20

【0022】

なお、回路3には、図1(A)に示す半導体装置における回路1と同様に、電源電位V1を供給する配線及び電源電位V2を供給する配線が設けられている。また、回路3には、図1(A)に示す半導体装置における回路1と同様に、データの復元が行われる際に第2のノード(Node2)を浮遊状態とする手段を設けられていることが好ましい。

【0023】

また、メモリ4には、パワーゲーティング期間中にデータを保持するキャパシタ40と、第1のノード(Node1)とキャパシタ40を電気的に接続させるか否かを選択するトランジスタ41と、第2のノード(Node2)とキャパシタ40を電気的に接続させるか否かを選択するトランジスタ42とが設けられている。なお、トランジスタ41、42は、チャネルが酸化物半導体層に形成されるトランジスタである。さらに、トランジスタ41のスイッチングは、ゲートに入力される第1のパワーゲーティング制御信号(CTRL\_1)によって制御され、トランジスタ42のスイッチングは、ゲートに入力される第2のパワーゲーティング制御信号(CTRL\_2)によって制御されている。なお、第1及び第2のパワーゲーティング制御信号(CTRL\_1、CTRL\_2)は、高電源電位(VDD)及び低電源電位(VSS)並びにパワーゲーティング電位のいずれかの電位となる信号である。そして、これらの電位の具体的な値は、トランジスタ41、42のゲートに高電源電位(VDD)が供給される際にトランジスタ41、42がオン状態となり、低電源電位(VSS)又はパワーゲーティング電位が供給される際にトランジスタ41、42がオフ状態になるように設定されている。

30

【0024】

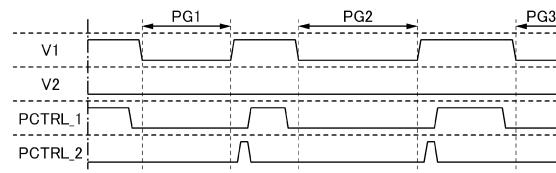

<構成例2の動作例1：図2(B)>

図2(B)は、図2(A)に示す半導体装置の動作例を示すタイミングチャートである。図2(B)に示すタイミングチャートでは、パワーゲーティング期間(PG1、PG2、PG3)において電源電位V1及び電源電位V2並びに第1及び第2のパワーゲーティング制御信号(CTRL\_1、CTRL\_2)が共にパワーゲーティング電位(ここでは、低電源電位VSSとする)となる。また、パワーゲーティング期間(PG1、PG

40

50

2、PG3)以外の期間において電源電位V1が高電源電位(VDD)となり、電源電位V2が低電源電位(VSS)となり、第1及び第2のパワーゲーティング制御信号(PCTR1、PCTR2)が高電源電位(VDD)又は低電源電位(VSS)となる。

【0025】

以下、第1及び第2のパワーゲーティング制御信号(PCTR1、PCTR2)について詳細に述べる。第1のパワーゲーティング制御信号(PCTR1)は、パワーゲーティングが開始される前に低電源電位(VSS)となる。そして、パワーゲーティング終了後も一定期間に渡って低電源電位(VSS)となる。なお、当該一定期間が経過した後に高電源電位(VDD)となる。この状態は、再度パワーゲーティングが行われる前まで維持される。また、第2のパワーゲーティング制御信号(PCTR2)は、パワーゲーティング終了後の一定期間に渡って低電源電位(VSS)となる。そして、当該一定期間が経過した後に高電源電位(VDD)となる。その後、第1のパワーゲーティング制御信号(PCTR1)が高電源電位(VDD)となる際に第2のパワーゲーティング制御信号(PCTR2)は低電源電位(VSS)となる。この状態は、再度パワーゲーティングが行われるまで維持される。

【0026】

これにより、トランジスタ41、42は、パワーゲーティング前にトランジスタ41がオフ状態となってからパワーゲーティング終了後一定期間が経過する(トランジスタ42がオン状態となる)までに渡ってオフ状態を維持することになる。そして、トランジスタ41、42がオフ状態となる期間に渡って、キャパシタ40に蓄積されている電荷(データ)も保持されることになる。チャネルが酸化物半導体層に形成されるトランジスタ41、42は、オフ電流値が極めて小さいからである。また、トランジスタ41は、当該期間経過後にオン状態となってから再度パワーゲーティングが開始される前までに渡ってオン状態を維持することになる。なお、図2(B)に示すタイミングチャートに従って図2(A)に示す半導体装置が動作する場合、パワーゲーティング前にトランジスタ41がオフ状態となることによって第1のノード(Node1)に保持されていたデータの退避が行われ、パワーゲーティング後にトランジスタ42がオン状態になることによって第2のノードに対してデータの復元が行われることになる。よって、この場合には、簡便な処理によってパワーゲーティングを行う際にデータの退避を行うことが可能である。

【0027】

<構成例2の動作例2：図2(C)>

図2(C)は、図2(A)に示す半導体装置の動作例を示すタイミングチャートである。図2(C)に示すタイミングチャートは、パワーゲーティング期間(PG1、PG2、PG3)の間の期間において、第1のパワーゲーティング制御信号(PCTR1)が高電源電位(VDD)となった後に低電源電位(VSS)とならない(パワーゲーティング期間(PG1、PG2、PG3)が開始する際に、高電源電位(VDD)から直接的にパワーゲーティング電位へと変化する)点、及び、第2のパワーゲーティング制御信号(PCTR2)が高電源電位(VDD)となる前に低電源電位(VSS)とならない(パワーゲーティング期間(PG1、PG2、PG3)が終了する際に、パワーゲーティング電位から直接的に高電源電位(VDD)へと変化する)点を除き、図2(B)に示すタイミングチャートと同様のタイミングチャートである。

【0028】

図2(C)に示すタイミングチャートに従って図2(A)に示す半導体装置が動作する場合、パワーゲーティングを行うための準備を行うことなくパワーゲーティングが開始されることになる。よって、図2(B)に示すタイミングチャートに従って図2(A)に示す半導体装置が動作する場合よりも簡便な処理によってパワーゲーティングを行うことが可能となる。他方、図2(B)に示すタイミングチャートに従って図2(A)に示す半導体装置が動作する場合には、データの退避を確実に行うことが可能である。

【0029】

10

20

30

40

50

また、図2(C)に示す第1のパワーゲーティング制御信号(PCTRL\_1)は、第2のパワーゲーティング制御信号(PCTRL\_2)の反転信号となる。よって、図2(B)に示すタイミングチャートに従って図2(A)に示す半導体装置が動作する場合、回路動作に必要な信号の生成が容易である。

【実施例1】

【0030】

本実施例においては、図1を参照して説明した半導体装置の具体例について図3、4を参考して説明する。なお、図3、4は、図1(A)に示す回路1としてStatic Random Access Memory(SRAM)を適用した場合の半導体装置の回路構成例を示す図である。

10

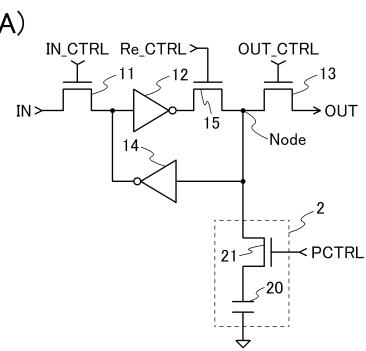

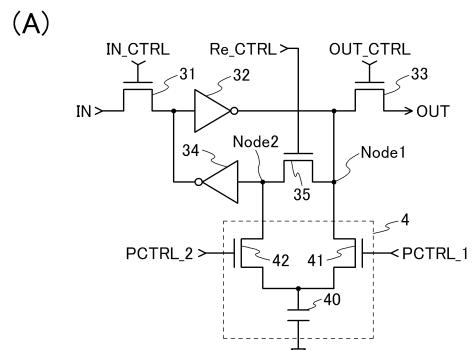

【0031】

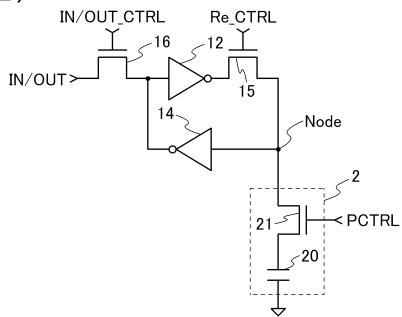

<具体例1：図3(A)>

図3(A)に示す半導体装置は、入力信号(IN)をノード(Node)に入力するか否かを選択するトランジスタ11と、ノード(Node)の電位が入力されるインバータ12と、インバータ12の出力信号を半導体装置の出力信号(OUT)として出力するか否かを選択するトランジスタ13と、インバータ12の出力信号が入力されるインバータ14と、インバータ14の出力信号をノード(Node)に出力するか否かを選択するトランジスタ15と、図1(A)に示すメモリ2とを有する。なお、図1(A)に示す電源電位V1及び電源電位V2は、インバータ12、14に供給されている(図示しない)。

【0032】

20

なお、トランジスタ11のスイッチングはゲートに入力される入力制御信号(IN\_CTRL)によって制御され、トランジスタ13のスイッチングはゲートに入力される出力制御信号(OUT\_CTRL)によって制御され、トランジスタ15のスイッチングはゲートに入力される復元制御信号(Re\_CTRL)によって制御されている。具体的には、トランジスタ11は、入力信号(IN)をノード(Node)に入力する場合にオン状態となり、それ以外の期間においてはオフ状態となる。また、トランジスタ13は、インバータ12の出力信号を半導体装置の出力信号(OUT)として出力する場合にオン状態となり、それ以外の期間においてはオフ状態となる。また、トランジスタ15は、メモリ2に退避されているデータを用いてノード(Node)におけるデータを復元する際にオフ状態となり、それ以外の期間(パワーゲーティング期間は除く)においてはオン状態となる。また、トランジスタ15をノード(Node)におけるデータを復元する際のみならず入力信号(IN)をノード(Node)に入力する際にもオフ状態としてもよい。

30

【0033】

図3(A)に示す半導体装置においては、図1(A)、(B)に示すタイミングチャートに従って動作させることでパワーゲーティングによって消失するノード(Node)のデータを簡便に復元することが可能である。

【0034】

なお、図3(A)では、トランジスタ11、13、15としてNチャネル型のトランジスタを適用する例について示したが、これらのトランジスタの一部又は全部をPチャネル型のトランジスタとすることも可能である。また、図3(A)に示す構成からトランジスタ15を削除した構成とすることも可能である。この場合には、回路面積の縮小を図ることが可能である。他方、図3(A)に示すようにトランジスタ15を設けることによって、データの復元時にノード(Node)を浮遊状態とすることが可能となる。これにより、インバータ14の状態に依存することなくデータの復元を行うことが可能となる。すなわち、データの復元時にメモリ2に保持されているデータ(電荷)が消失する蓋然性を低減することが可能である。

40

【0035】

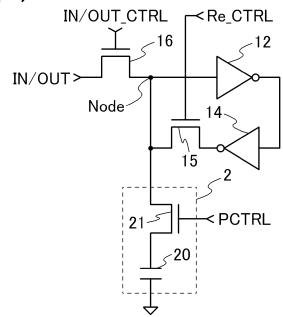

<具体例2：図3(B)>

図3(B)に示す半導体装置は、入力信号(IN)及び出力信号(OUT)が供給される配線が共通化されている点を除き、図3(A)に示す半導体装置と同様の構成を有する

50

。具体的には、図3(B)に示す半導体装置は、図3(A)に示すトランジスタ11、13を、入力信号(IN)をノード(Node)に入力するか否か、及びインバータ14の出力信号を半導体装置の出力信号(OUT)として出力するか否かを選択するトランジスタ16に置換した構成を有する。

【0036】

なお、トランジスタ16のスイッチングはゲートに入力される入出力制御信号(IN/OUT\_CTRL)によって制御されている。具体的には、トランジスタ16は、入力信号(IN)をノード(Node)に入力する場合及びインバータ14の出力信号を半導体装置の出力信号(OUT)として出力する場合にオン状態となり、それ以外の期間においてはオフ状態となる。

10

【0037】

図3(B)に示す半導体装置においても図3(A)に示す半導体装置と同様にノード(Node)のデータを簡便に復元することが可能である。

【0038】

なお、図3(B)では、トランジスタ16としてNチャネル型のトランジスタを適用する例について示したが、トランジスタ16をPチャネル型のトランジスタとすることも可能である。また、図3(B)に示す構成からトランジスタ15を削除した構成とすることも可能である。

【0039】

<具体例3：図4(A)>

20

図4(A)に示す半導体装置は、トランジスタ15及びメモリ2がインバータ14の出力側ではなくインバータ12の出力側に電気的に接続されている点を除き、図3(A)に示す半導体装置と同様の構成を有する。

【0040】

図4(A)に示す半導体装置においても図3(A)、(B)に示す半導体装置と同様にノード(Node)のデータを簡便に復元することが可能である。また、図4(A)に示す構成からトランジスタ15を削除した構成とすることも可能である。

【0041】

<具体例4：図4(B)>

30

図4(B)に示す半導体装置は、トランジスタ15及びメモリ2がインバータ14の出力側ではなくインバータ12の出力側のノード(Node)に電気的に接続されている点を除き、図3(B)に示す半導体装置と同様の構成を有する。

【0042】

図4(B)に示す半導体装置においても図3(A)、(B)、図4(A)に示す半導体装置と同様にノード(Node)のデータを簡便に復元することが可能である。また、図4(B)に示す構成からトランジスタ15を削除した構成とすることも可能である。

【0043】

<付記>

なお、本実施例においては、図1(A)に示す回路1としてSRAMが適用された半導体装置について示したが、回路1としてフリップフロップ又はレジスタなどを適用することも可能である。

40

【実施例2】

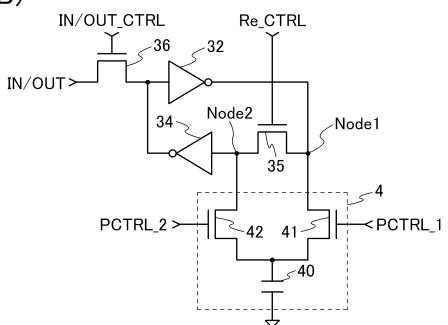

【0044】

本実施例においては、図2を参照して説明した半導体装置の具体例について図5、6を参照して説明する。なお、図5、6は、図2(A)に示す回路3としてSRAMを適用した場合の半導体装置の回路構成例を示す図である。

【0045】

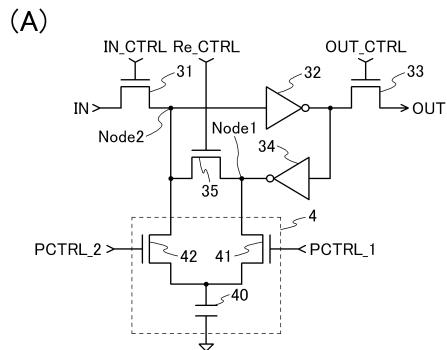

<具体例5：図5(A)>

図5(A)に示す半導体装置は、入力信号(IN)を第2のノード(Node2)に入力するか否かを選択するトランジスタ31と、第2のノード(Node2)の電位が入力

50

されるインバータ32と、インバータ32の出力信号を半導体装置の出力信号(OUT)として出力するか否かを選択するトランジスタ33と、インバータ32の出力信号が入力されるインバータ34と、第1のノード(Node1)と第2のノード(Node2)を電気的に接続するか否かを選択するトランジスタ35と、図2(A)に示すメモリ4とを有する。なお、図1(A)に示す電源電位V1及び電源電位V2は、インバータ32、34に供給されている。

【0046】

なお、トランジスタ31のスイッチングはゲートに入力される入力制御信号(IN\_CTRL)によって制御され、トランジスタ33のスイッチングはゲートに入力される出力制御信号(OUT\_CTRL)によって制御され、トランジスタ35のスイッチングはゲートに入力される復元制御信号(Re\_CTRL)によって制御されている。具体的には、トランジスタ31は、入力信号(IN)を第2のノード(Node2)に入力する場合にオン状態となり、それ以外の期間においてはオフ状態となる。また、トランジスタ33は、インバータ32の出力信号を半導体装置の出力信号(OUT)として出力する場合にオン状態となり、それ以外の期間においてはオフ状態となる。また、トランジスタ35は、メモリ2に退避されているデータを用いて第2のノード(Node2)におけるデータを復元する際にオフ状態となり、それ以外の期間(パワーゲーティング期間は除く)においてはオン状態となる。また、トランジスタ35を第2のノード(Node2)におけるデータを復元する際のみならず入力信号(IN)を第2のノード(Node2)に入力する際にもオフ状態としてもよい。

10

20

【0047】

また、復元制御信号(Re\_CTRL)として、第1のパワーゲーティング制御信号(CTRL\_1)を適用することも可能である。この場合、回路動作に必要な信号数を削減することが可能である。

【0048】

図5(A)に示す半導体装置においては、図2(A)、(B)に示すタイミングチャートに従って動作させることでパワーゲーティングによって消失する第2のノード(Node2)のデータを簡便に復元することが可能である。

【0049】

なお、図5(A)では、トランジスタ31、33、35としてNチャネル型のトランジスタを適用する例について示したが、これらのトランジスタの一部又は全部をPチャネル型のトランジスタとすることも可能である。さらに、トランジスタ35としてPチャネル型のトランジスタを適用する場合には、復元制御信号(Re\_CTRL)として、第2のパワーゲーティング制御信号(CTRL\_2)を適用することも可能である。

30

【0050】

<具体例6：図5(B)>

図5(B)に示す半導体装置は、入力信号(IN)及び出力信号(OUT)が供給される配線が共通化されている点を除き、図5(A)に示す半導体装置と同様の構成を有する。具体的には、図5(B)に示す半導体装置は、図5(A)に示すトランジスタ31、33を、入力信号(IN)を第2のノード(Node2)に入力するか否か、及びインバータ34の出力信号を半導体装置の出力信号(OUT)として出力するか否かを選択するトランジスタ36に置換した構成を有する。

40

【0051】

なお、トランジスタ36のスイッチングはゲートに入力される入出力制御信号(IN/OUT\_CTRL)によって制御されている。具体的には、トランジスタ36は、入力信号(IN)を第2のノード(Node2)に入力する場合及びインバータ34の出力信号を半導体装置の出力信号(OUT)として出力する場合にオン状態となり、それ以外の期間においてはオフ状態となる。

【0052】

図5(B)に示す半導体装置においても図5(A)に示す半導体装置と同様に第2のノ

50

ード (Node 2) のデータを簡便に復元することが可能である。

【0053】

なお、図5(B)では、トランジスタ36としてNチャネル型のトランジスタを適用する例について示したが、トランジスタ36をPチャネル型のトランジスタとすることも可能である。

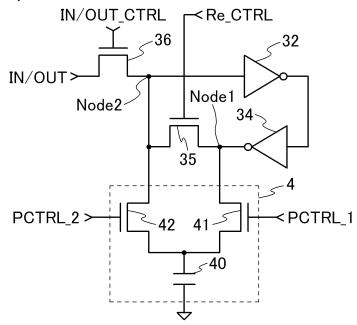

【0054】

<具体例7：図6(A)>

図6(A)に示す半導体装置は、トランジスタ35及びメモリ4がインバータ34の出力側ではなくインバータ32の出力側に電気的に接続されている点を除き、図5(A)に示す半導体装置と同様の構成を有する。

10

【0055】

図6(A)に示す半導体装置においても図5(A)、(B)に示す半導体装置と同様に第2のノード(Node 2)のデータを簡便に復元することが可能である。

【0056】

<具体例8：図6(B)>

図6(B)に示す半導体装置は、トランジスタ35及びメモリ4がインバータ34の出力側ではなくインバータ32の出力側に電気的に接続されている点を除き、図5(B)に示す半導体装置と同様の構成を有する。

【0057】

図6(B)に示す半導体装置においても図5(A)、(B)、図6(A)に示す半導体装置と同様に第2のノード(Node 2)のデータを簡便に復元することが可能である。

20

【0058】

<付記>

なお、本実施例においては、図2(A)に示す回路3としてSRAMが適用された半導体装置について示したが、回路3としてフリップフロップ又はレジスタなどを適用することも可能である。

【実施例3】

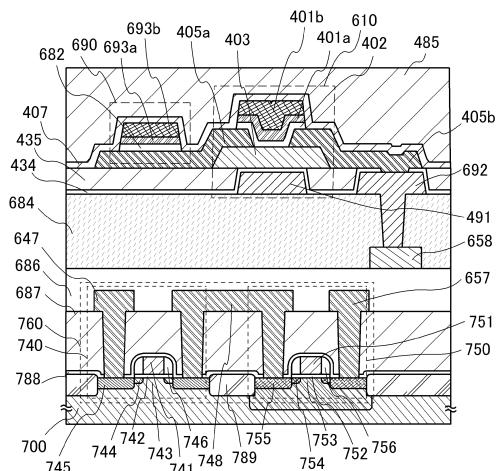

【0059】

本実施例においては、上述した半導体装置の構造例について図7～9を参照して説明する。具体的には、図7～9は、図1(A)、図2(A)に示す回路1、3に含まれるインバータと、メモリ2、4に含まれるチャネルが酸化物半導体層に形成されるトランジスタ及びキャパシタとが重畳して設けられる場合の構造例を示す図である。なお、図7に示すインバータは回路1、3に含まれる論理ゲートの一例であり、回路1、3がインバータを含む回路に限定される訳ではない。

30

【0060】

図7に示す半導体装置は、下部に第1の半導体材料を用いたトランジスタ740、750を有し、上部に第2の半導体材料を用いたトランジスタ610を有する。

【0061】

ここで、第1の半導体材料と第2の半導体材料は異なるバンドギャップを持つ材料とすることが望ましい。例えば、第1の半導体材料を酸化物半導体以外の半導体材料(シリコンなど)とし、第2の半導体材料を酸化物半導体とすることができます。シリコンなどの材料を用いたトランジスタは、高速動作が容易である。一方で、酸化物半導体を用いたトランジスタは、その特性により長時間の電荷保持を可能とする。

40

【0062】

半導体装置に用いる基板は、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI(Silicon on Insulator)基板などを用いることができ、トランジスタのチャネル形成領域は、半導体基板中、又は半導体基板上に形成することができる。図7に示す半導体装置は、半導体基板中にチャネル形成領域を形成して下部のトランジスタを作製する例である。

50

## 【0063】

図7に示す半導体装置においては、基板700に単結晶シリコン基板を用いて、該単結晶シリコン基板にトランジスタ740、トランジスタ750を形成しており、第1の半導体材料として単結晶シリコンを用いている。トランジスタ740はnチャネル型トランジスタ、トランジスタ750はpチャネル型トランジスタであり、トランジスタ740及びトランジスタ750によってインバータ760が構成されている。

## 【0064】

なお、ここでは、基板700としてp型の導電型を有する単結晶シリコン基板を用いているため、pチャネル型トランジスタであるトランジスタ750の形成領域に、n型を付与する不純物元素を添加し、nウェルを形成する。トランジスタ750のチャネル形成領域753はnウェルに形成される。n型を付与する不純物元素としては、リン(P)やヒ素(As)等を用いることができる。

10

## 【0065】

よって、nチャネル型トランジスタであるトランジスタ740の形成領域に、p型の導電型を付与する不純物元素の添加を行っていないが、p型を付与する不純物元素を添加することによりpウェルを形成してもよい。p型を付与する不純物元素としては、ボロン(B)やアルミニウム(Al)やガリウム(Ga)等を用いることができる。

## 【0066】

一方、n型の導電型を有する単結晶シリコン基板を用いる場合には、p型を付与する不純物元素を添加してpウェルを形成してもよい。

20

## 【0067】

トランジスタ740は、チャネル形成領域743、LDD(Lightly Doped Drain)領域やエクステンション領域として機能するn型不純物領域744、ソース領域又はドレイン領域として機能するn型不純物領域745、ゲート絶縁膜742、ゲート電極層741を有している。なお、n型不純物領域745の不純物濃度は、n型不純物領域744よりも高い。ゲート電極層741の側面には側壁絶縁層746が設けられており、ゲート電極層741及び側壁絶縁層746をマスクとして用いて、不純物濃度が異なるn型不純物領域744、n型不純物領域745を自己整合的に形成することができる。

## 【0068】

30

トランジスタ750は、チャネル形成領域753、LDD領域やエクステンション領域として機能するp型不純物領域754、ソース領域又はドレイン領域として機能するp型不純物領域755、ゲート絶縁膜752、ゲート電極層751を有している。なお、p型不純物領域755の不純物濃度は、p型不純物領域754よりも高い。ゲート電極層751の側面には側壁絶縁層756が設けられており、ゲート電極層751及び側壁絶縁層756をマスクとして用いて、不純物濃度が異なるp型不純物領域754、p型不純物領域755を自己整合的に形成することができる。

## 【0069】

基板700において、トランジスタ740及びトランジスタ750は素子分離領域789により分離されており、トランジスタ740及びトランジスタ750上に絶縁膜788、及び絶縁膜687が積層されている。絶縁膜687上には、絶縁膜788及び絶縁膜687に形成された開口においてn型不純物領域745に接する配線層647と、絶縁膜788及び絶縁膜687に形成された開口においてp型不純物領域755に接する配線層657とを有する。また、絶縁膜687上には、トランジスタ740及びトランジスタ750を電気的に接続させる配線層748が形成されている。配線層748は、絶縁膜788及び絶縁膜687に形成された一対の開口の一方においてn型不純物領域745に接し、他方においてp型不純物領域755と接する。

40

## 【0070】

また、絶縁膜687、配線層647、配線層748、配線層657上に絶縁膜686が設けられている。また、絶縁膜686上に配線層658が形成されている。なお、配線層

50

658は、絶縁膜788、絶縁膜687、絶縁膜686に形成された開口においてゲート配線と電気的に接続されている。そして、ゲート配線は、ゲート絶縁膜742上に形成されており、ゲート配線がそれぞれ分岐してゲート電極層741及びゲート電極層751となっている。

【0071】

なお、本発明の半導体装置の構造は図7に示す構成に限定されず、トランジスタ740、750として、シリサイド(サリサイド)を有するトランジスタ、又は側壁絶縁層を有さないトランジスタを適用してもよい。シリサイド(サリサイド)を有する構造であると、ソース領域及びドレイン領域がより低抵抗化でき、半導体装置の動作の高速化を図ることが可能である。また、低電圧で動作できるため、半導体装置の消費電力の低減を図ることが可能である。

10

【0072】

次に、図7の半導体装置における下部のトランジスタ上に設けられる上部の素子構成を説明する。

【0073】

絶縁膜686及び配線層658上に絶縁膜684が設けられている。また、絶縁膜684上に、導電層491及び配線層692が形成されている。なお、配線層692は、絶縁膜684に形成された開口において配線層658と接する。さらに、導電層491及び配線層692上に絶縁膜434が設けられ、その上に絶縁膜435が設けられている。

【0074】

絶縁膜435上には、酸化物半導体層403が設けられている。そして、酸化物半導体層403上に、ドレイン電極層405a、及びソース電極層405bが設けられている。酸化物半導体層403のうち、ドレイン電極層405a及びソース電極層405bと重なっていない領域(チャネル形成領域)上に接してゲート絶縁膜402が設けられ、その上にゲート電極層401a、401bが設けられている。

20

【0075】

また、キャパシタ690もトランジスタ610と同一の絶縁膜435上に工程を増やすことなく形成されており、キャパシタ690は、ドレイン電極層405aを一方の電極とし、電極層693a、693bをもう一方の電極とし、それらの間に設けられたゲート絶縁膜402と同じ工程で形成される絶縁膜682を誘電体とするキャパシタである。なお、電極層693a、693bはゲート電極層401a、401bと同じ工程で形成される。

30

【0076】

また、トランジスタ610及びキャパシタ690上に絶縁膜407及び層間絶縁膜485が設けられている。さらに、層間絶縁膜485に埋め込み配線を形成し、埋め込み配線上方に他の半導体素子や配線などを形成して多層構造を有する半導体装置を作製してもよい。

【0077】

導電層491は、電位をGND(または固定電位)とすることでトランジスタ610の電気的特性を制御するバッゲートとして機能する。なお、導電層491は静電気に対する静電遮蔽機能も有する。ただし、導電層491を用いずともトランジスタ610をノーマリーオフのトランジスタとできる場合、又は、トランジスタ610をノーマリーオフのトランジスタとする必要がない場合には、導電層491を設けなくともよい。また、ある特定の回路の一部にトランジスタ610を用いる場合に導電層491を設けると支障がでる恐れがある場合には、その回路には設けなくともよい。

40

【0078】

絶縁膜434は半導体装置において下部と上部の間に設けられており、上部のトランジスタ610の電気的特性の劣化や変動を招く水素等の不純物が、下部から上部へ侵入しないように、バリア膜として機能する。よって、不純物等の遮断機能の高い、緻密な無機絶縁膜(例えば、酸化アルミニウム膜、窒化シリコン膜など)を用いることが好ましい。ま

50

た、同様の理由から、ゲート絶縁膜 402 及び絶縁膜 407 としてもこれらの膜を用いることが好ましい。

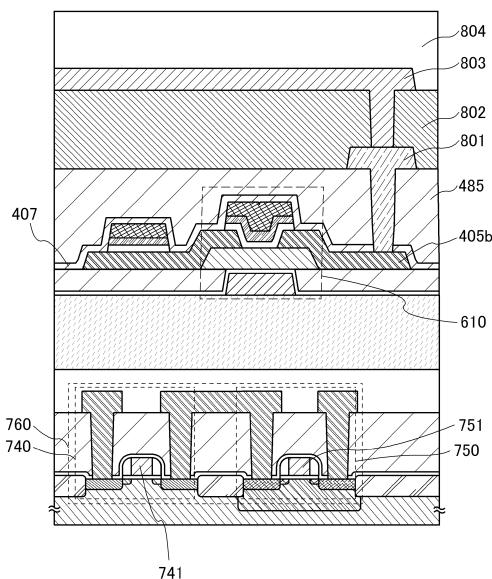

【0079】

また、上述した半導体装置の構造として図 8、9 に示す構造を適用することも可能である。

【0080】

図 8 に示す半導体装置の構造は、トランジスタ 610 が設けられている層上に配線層が設けられている点で図 7 に示す構造と異なる。具体的には、図 8 に示す半導体装置は、トランジスタ 610 が設けられている層上に設けられている配線層 801 と、層間絶縁膜 485 及び配線層 801 上に設けられている層間絶縁膜 802 と、層間絶縁膜 802 上に設けられている配線層 803 と、層間絶縁膜 802 及び配線層 803 上に設けられている層間絶縁膜 804 とを有する。なお、配線層 801 は、層間絶縁膜 485 及び絶縁膜 407 に形成された開口においてトランジスタ 610 のソース電極層 405b と接する。また、配線層 803 は、層間絶縁膜 802 に形成された開口において配線層 801 と接する。そして、図 8 に示す半導体装置においては、トランジスタ 610 のソース電極層 405b と、インバータ 760 を構成するトランジスタ 740 のゲート電極層 741 及びトランジスタ 750 のゲート電極層 751 とが配線層 801 及び配線層 803 並びに層間絶縁膜 485、802 などに形成される開口に設けられる配線層（図示しない）を介して電気的に接続させることが可能である。なお、図 8 においては、トランジスタ 610 が設けられている層上に 2 つの配線層が設けられている構造を示したが、当該配線層を 1 つ又は 3 つ以上としてもよい。

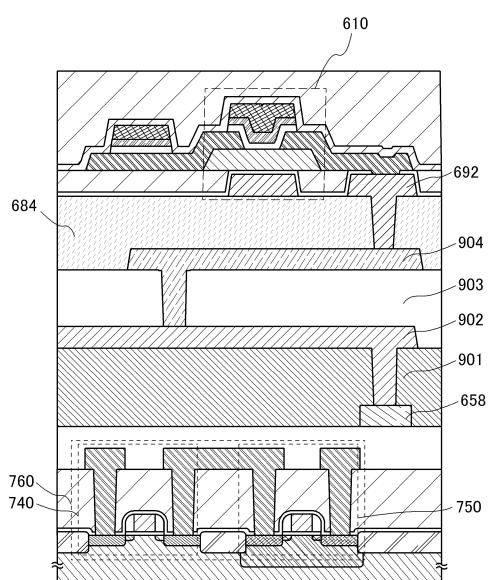

【0081】

図 9 に示す半導体装置の構造は、トランジスタ 610 が設けられている層と、インバータ 760（トランジスタ 740 及びトランジスタ 750）が設けられている層との間に配線層が設けられている点で図 7 に示す構造と異なる。具体的には、図 8 に示す半導体装置は、配線層 658 上に設けられている層間絶縁膜 901 と、層間絶縁膜 901 上に設けられている配線層 902 と、層間絶縁膜 901 及び配線層 902 上に設けられている層間絶縁膜 903 と、層間絶縁膜 903 上に設けられている配線層 904 とを有する。なお、配線層 902 は、層間絶縁膜 901 に形成された開口において配線層 658 と接する。また、配線層 904 は、層間絶縁膜 903 に形成された開口において配線層 902 と接し、且つ絶縁膜 684 に形成された開口において配線層 692 と接する。なお、図 9 においては、トランジスタ 610 が設けられている層と、インバータ 760（トランジスタ 740 及びトランジスタ 750）が設けられている層との間に 2 つの配線層が設けられている構造を示したが、当該配線層を 1 つ又は 3 つ以上としてもよい。

【実施例 4】

【0082】

本実施例においては、上述した半導体装置を、携帯電話、スマートフォン、電子書籍などの携帯用の電子機器に応用した場合について説明する。

【0083】

図 10 は、携帯用の電子機器のブロック図である。図 10 に示す携帯用の電子機器は RF 回路 1421、アナログベースバンド回路 1422、デジタルベースバンド回路 1423、バッテリー 1424、電源回路 1425、アプリケーションプロセッサ 1426、フラッシュメモリ 1430、ディスプレイコントローラ 1431、メモリ回路 1432、ディスプレイ 1433、タッチセンサ 1439、音声回路 1437、キーボード 1438 などより構成されている。ディスプレイ 1433 は表示部 1434、ソースドライバ 1435、ゲートドライバ 1436 によって構成されている。アプリケーションプロセッサ 1426 は CPU 1427、DSP 1428、インターフェース 1429 を有している。図 10 に示す電子機器においては、CPU 1427 が上述した半導体装置を有する構成とすることが可能である。

【0084】

10

20

30

40

50

図11は電子書籍のブロック図である。電子書籍はバッテリー1451、電源回路1452、マイクロプロセッサ1453、フラッシュメモリ1454、音声回路1455、キーボード1456、メモリ回路1457、タッチパネル1458、ディスプレイ1459、ディスプレイコントローラ1460によって構成される。図11に示す電子機器においては、マイクロプロセッサ1453が上述した半導体装置を有する構成とすることが可能である。

## 【符号の説明】

## 【0085】

|         |         |    |

|---------|---------|----|

| 1       | 回路      | 10 |

| 2       | メモリ     |    |

| 3       | 回路      |    |

| 4       | メモリ     |    |

| 1 1     | トランジスタ  |    |

| 1 2     | インバータ   |    |

| 1 3     | トランジスタ  |    |

| 1 4     | インバータ   |    |

| 1 5     | トランジスタ  |    |

| 1 6     | トランジスタ  |    |

| 2 0     | キャパシタ   |    |

| 2 1     | トランジスタ  | 20 |

| 3 1     | トランジスタ  |    |

| 3 2     | インバータ   |    |

| 3 3     | トランジスタ  |    |

| 3 4     | インバータ   |    |

| 3 5     | トランジスタ  |    |

| 3 6     | トランジスタ  |    |

| 4 0     | キャパシタ   |    |

| 4 1     | トランジスタ  |    |

| 4 2     | トランジスタ  |    |

| 4 0 1 a | ゲート電極層  | 30 |

| 4 0 1 b | ゲート電極層  |    |

| 4 0 2   | ゲート絶縁膜  |    |

| 4 0 3   | 酸化物半導体層 |    |

| 4 0 5 a | ドレイン電極層 |    |

| 4 0 5 b | ソース電極層  |    |

| 4 0 7   | 絶縁膜     |    |

| 4 3 4   | 絶縁膜     |    |

| 4 3 5   | 絶縁膜     |    |

| 4 8 5   | 層間絶縁膜   |    |

| 4 9 1   | 導電層     | 40 |

| 6 1 0   | トランジスタ  |    |

| 6 4 7   | 配線層     |    |

| 6 5 7   | 配線層     |    |

| 6 5 8   | 配線層     |    |

| 6 8 2   | 絶縁膜     |    |

| 6 8 4   | 絶縁膜     |    |

| 6 8 6   | 絶縁膜     |    |

| 6 8 7   | 絶縁膜     |    |

| 6 9 0   | キャパシタ   |    |

| 6 9 2   | 配線層     | 50 |

|         |               |    |

|---------|---------------|----|

| 6 9 3 a | 電極層           |    |

| 6 9 3 b | 電極層           |    |

| 7 0 0   | 基板            |    |

| 7 4 0   | トランジスタ        |    |

| 7 4 1   | ゲート電極層        |    |

| 7 4 2   | ゲート絶縁膜        |    |

| 7 4 3   | チャネル形成領域      |    |

| 7 4 4   | n型不純物領域       |    |

| 7 4 5   | n型不純物領域       |    |

| 7 4 6   | 側壁絶縁層         | 10 |

| 7 4 8   | 配線層           |    |

| 7 5 0   | トランジスタ        |    |

| 7 5 1   | ゲート電極層        |    |

| 7 5 2   | ゲート絶縁膜        |    |

| 7 5 3   | チャネル形成領域      |    |

| 7 5 4   | p型不純物領域       |    |

| 7 5 5   | p型不純物領域       |    |

| 7 5 6   | 側壁絶縁層         |    |

| 7 6 0   | インバータ         |    |

| 7 8 8   | 絶縁膜           | 20 |

| 7 8 9   | 素子分離領域        |    |

| 8 0 1   | 配線層           |    |

| 8 0 2   | 層間絶縁膜         |    |

| 8 0 3   | 配線層           |    |

| 8 0 4   | 層間絶縁膜         |    |

| 9 0 1   | 層間絶縁膜         |    |

| 9 0 2   | 配線層           |    |

| 9 0 3   | 層間絶縁膜         |    |

| 9 0 4   | 配線層           |    |

| 1 4 2 1 | R F 回路        | 30 |

| 1 4 2 2 | アナログベースバンド回路  |    |

| 1 4 2 3 | デジタルベースバンド回路  |    |

| 1 4 2 4 | バッテリー         |    |

| 1 4 2 5 | 電源回路          |    |

| 1 4 2 6 | アプリケーションプロセッサ |    |

| 1 4 2 7 | C P U         |    |

| 1 4 2 8 | D S P         |    |

| 1 4 2 9 | インターフェース      |    |

| 1 4 3 0 | フラッシュメモリ      |    |

| 1 4 3 1 | ディスプレイコントローラ  | 40 |

| 1 4 3 2 | メモリ回路         |    |

| 1 4 3 3 | ディスプレイ        |    |

| 1 4 3 4 | 表示部           |    |

| 1 4 3 5 | ソースドライバ       |    |

| 1 4 3 6 | ゲートドライバ       |    |

| 1 4 3 7 | 音声回路          |    |

| 1 4 3 8 | キーボード         |    |

| 1 4 3 9 | タッチセンサ        |    |

| 1 4 5 1 | バッテリー         |    |

| 1 4 5 2 | 電源回路          | 50 |

- 1 4 5 3 マイクロプロセッサ

1 4 5 4 フラッシュメモリ

1 4 5 5 音声回路

1 4 5 6 キーボード

1 4 5 7 メモリ回路

1 4 5 8 タッチパネル

1 4 5 9 ディスプレイ

1 4 6 0 ディスプレイコントローラ

【図1】

(B)

(C)

【図2】

(B)

(C)

【図3】

(B)

【図4】

(B)

【図5】

(B)

【図6】

(B)

【図7】

【図8】

【図9】

【図10】

【図 1 1】

## フロントページの続き

| (51)Int.Cl.  |                | F I              |                            |

|--------------|----------------|------------------|----------------------------|

| <i>H 01L</i> | <i>21/8244</i> | <i>(2006.01)</i> | <i>H 01L</i> 27/10 4 6 1   |

| <i>H 01L</i> | <i>27/11</i>   | <i>(2006.01)</i> | <i>H 01L</i> 27/10 3 8 1   |

| <i>H 01L</i> | <i>29/786</i>  | <i>(2006.01)</i> | <i>H 01L</i> 29/78 6 1 8 B |

| <i>G 11C</i> | <i>11/412</i>  | <i>(2006.01)</i> | <i>H 01L</i> 29/78 6 1 3 B |

| <i>G 11C</i> | <i>11/41</i>   | <i>(2006.01)</i> | <i>G 11C</i> 11/40 3 0 1   |

|              |                |                  | <i>H 03K</i> 3/356 B       |

|              |                |                  | <i>G 11C</i> 11/40 Z       |

- (56)参考文献 特開2011-151796 (JP, A)

特開2011-142621 (JP, A)

国際公開第2009/063542 (WO, A1)

特開2006-50208 (JP, A)

特開2000-77982 (JP, A)

特開平5-110392 (JP, A)

特開2012-160708 (JP, A)

## (58)調査した分野(Int.Cl., DB名)

|              |                   |

|--------------|-------------------|

| <i>H 03K</i> | 3 / 2 6 - 3 / 3 6 |

| <i>G 11C</i> | 1 1 / 4 1         |

| <i>G 11C</i> | 1 1 / 4 1 2       |

| <i>H 01L</i> | 2 1 / 8 2 4 2     |

| <i>H 01L</i> | 2 1 / 8 2 4 4     |

| <i>H 01L</i> | 2 7 / 1 0         |

| <i>H 01L</i> | 2 7 / 1 0 5       |

| <i>H 01L</i> | 2 7 / 1 0 8       |

| <i>H 01L</i> | 2 7 / 1 1         |

| <i>H 01L</i> | 2 9 / 7 8 6       |