(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2014-175518

(P2014-175518A)

(43) 公開日 平成26年9月22日(2014.9.22)

| (51) Int.Cl.                 | F 1        | テーマコード (参考) |

|------------------------------|------------|-------------|

| <b>H01L 29/78</b> (2006.01)  | H01L 29/78 | 652J        |

| <b>H01L 29/12</b> (2006.01)  | H01L 29/78 | 652T        |

| <b>H01L 21/336</b> (2006.01) | H01L 29/78 | 653A        |

|                              | H01L 29/78 | 652H        |

|                              | H01L 29/78 | 652S        |

審査請求 未請求 請求項の数 7 O L (全 22 頁) 最終頁に続く

|           |                            |          |                                                |

|-----------|----------------------------|----------|------------------------------------------------|

| (21) 出願番号 | 特願2013-47790 (P2013-47790) | (71) 出願人 | 000002130<br>住友電気工業株式会社<br>大阪府大阪市中央区北浜四丁目5番33号 |

| (22) 出願日  | 平成25年3月11日 (2013.3.11)     | (74) 代理人 | 110001195<br>特許業務法人深見特許事務所                     |

|           |                            | (72) 発明者 | 和田 圭司<br>大阪市此花区島屋一丁目1番3号 住友電<br>気工業株式会社大阪製作所内  |

|           |                            | (72) 発明者 | 増田 健良<br>大阪市此花区島屋一丁目1番3号 住友電<br>気工業株式会社大阪製作所内  |

|           |                            | (72) 発明者 | 日吉 透<br>大阪市此花区島屋一丁目1番3号 住友電<br>気工業株式会社大阪製作所内   |

## (54) 【発明の名称】炭化珪素半導体装置

## (57) 【要約】

【課題】高い耐圧と低いオン抵抗とを有する炭化珪素半導体装置を提供する。

【解決手段】第1のドリフト層81aは、第1の電極98に面しかつ第1の電極98に電気的に接続された第1の面P1と、第1の面P1と反対の第2の面P2とを有する。第1のドリフト層81aは、不純物濃度N<sub>A</sub>を有する。緩和領域71は、第1のドリフト層81aの第2の面P2に部分的に設けられている。第1のドリフト層81aおよび第2のドリフト層81bは、緩和領域71を埋め込むドリフト領域81を構成している。第2のドリフト層81bは不純物濃度N<sub>B</sub>を有し、N<sub>B</sub> > N<sub>A</sub>が満たされている。ボディ領域82、ソース領域83および第2の電極94は第2のドリフト層81b上に設けられている。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

炭化珪素半導体装置であつて、

第 1 の電極と、

前記第 1 の電極に面しあつ前記第 1 の電極に電気的に接続された第 1 の面と前記第 1 の面と反対の第 2 の面とを有し、第 1 の導電型を有し、不純物濃度  $N_A$  を有する第 1 のドリフト層と、

前記第 1 のドリフト層の前記第 2 の面に部分的に設けられ、前記第 1 の面から距離  $L_A$  を有し、第 2 の導電型を有する緩和領域と、

前記第 2 の面に接する第 3 の面と前記第 3 の面と反対の第 4 の面とを有し、前記第 1 の導電型を有する第 2 のドリフト層とを備え、前記第 1 のドリフト層および前記第 2 のドリフト層は、前記緩和領域を埋め込むドリフト領域を構成しており、前記第 2 のドリフト層は不純物濃度  $N_B$  を有し、 $N_B > N_A$  が満たされ、前記炭化珪素半導体装置はさらに

前記第 2 のドリフト層の前記第 4 の面上に設けられ、前記第 2 の導電型を有するボディ領域と、

前記ボディ領域上に設けられ、前記ボディ領域によって前記ドリフト領域から隔てられ、前記第 1 の導電型を有するソース領域と、

前記ソース領域に電気的に接続された第 2 の電極と、

前記ソース領域および前記第 2 のドリフト層をつなぐように前記ボディ領域上に位置する部分を含むゲート絶縁膜と、

前記ゲート絶縁膜上に設けられたゲート電極とを備える、炭化珪素半導体装置。

## 【請求項 2】

前記第 3 の面は前記第 4 の面から距離  $L_B$  を有し、 $L_A > L_B$  が満たされている、請求項 1 に記載の炭化珪素半導体装置。

## 【請求項 3】

$L_A > 2 \cdot L_B$  が満たされている、請求項 2 に記載の炭化珪素半導体装置。

## 【請求項 4】

$L_A > 5 \mu m$  が満たされている、請求項 1 ~ 3 のいずれか 1 項に記載の炭化珪素半導体装置。

## 【請求項 5】

前記緩和領域はドーズ量  $D_R$  を有し、 $L_A \cdot N_A < D_R$  が満たされている、請求項 1 ~ 4 のいずれか 1 項に記載の炭化珪素半導体装置。

## 【請求項 6】

前記ソース領域および前記ボディ領域を貫通して前記第 2 のドリフト層に至りかつ前記第 1 のドリフト層から離れた側壁面を有するトレンチが設けられており、

前記ゲート電極は前記ゲート絶縁膜を介して前記側壁面上に位置している、請求項 1 ~ 5 のいずれか 1 項に記載の炭化珪素半導体装置。

## 【請求項 7】

前記ソース領域、前記ボディ領域および前記第 2 のドリフト層の各々からなる部分を有しあつ前記第 2 のドリフト層の前記第 4 の面と平行な平坦面が設けられており、

前記ゲート電極は前記ゲート絶縁膜を介して前記平坦面上に位置している、請求項 1 ~ 5 のいずれか 1 項に記載の炭化珪素半導体装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0 0 0 1】

この発明は、炭化珪素半導体装置に関するものであり、特に、ドリフト領域を有する炭化珪素半導体装置に関するものである。

## 【背景技術】

## 【0 0 0 2】

広く用いられている電力用半導体装置である Si (シリコン) MOSFET (Metal Oxide Semiconductor Field-Effect Transistor) は、

10

20

30

40

50

xide Semiconductor Field Effect Transistor) に関して、耐圧の主な決定要因は、耐圧保持領域をなすドリフト層が耐え得る電界強度の上限である。Si から作られたドリフト層は、0.3 MV/cm 程度以上の電界が印加された箇所で破壊し得る。このため MOSFET のドリフト層全体において電界強度を所定の値未満に抑えることが必要である。最も単純な方法はドリフト層の不純物濃度を低くすることである。しかしながらこの方法では MOSFET のオン抵抗が大きくなるという短所がある。すなわちオン抵抗と耐圧との間にトレードオフ関係が存在する。

【 0 0 0 3 】

特開平9-191109号公報において、典型的なSi-MOSFETについて、Siの物性値から得られる理論限界を考慮しつつ、オン抵抗と耐圧との間のトレードオフ関係の説明がなされている。そしてこのトレードオフを解消するために、ドレイン電極上のn型基板の上のnベース層中において、下側のp型埋込層と、上側のp型埋込層とを附加することが開示されている。下側のp型埋込層および上側の埋込層によってnベース層は、各々等しい厚さを有する下段と中段と上段とに区分される。この公報に記載の一実施の形態によれば、印加電圧が200Vに達した時点でまず上段にパンチスルーポートが生じ、印加電圧が400Vに達した時点でさらに中段にパンチスルーポートが生じ、印加電圧が600Vに達した時点でさらに下段にパンチスルーポートが生じる。パンチスルーポートが生じた各段は等しい電圧を分担し、各段の最大電界が限界電界強度以下に保たれる。

【先行技術文献】

【特許文献】

〔 0 0 0 4 〕

【特許文献1】特開平9-191109号公報

## 【発明の概要】

#### 【発明が解決しようとする課題】

【 0 0 0 5 】

上述したトレードオフをより大きく改善するための方法として、近年、Siに代わりSiC（炭化珪素）を用いることが活発に検討されている。SiCはSiと異なり0.4M V/cm以上の電界強度にも十分に耐え得る材料である。

( 0 0 0 6 )

このように高い電界が印加され得る場合は、MOSFET構造における特定位置での電界集中に起因した破壊が問題となる。たとえばトレンチ型MOSFETの場合、トレンチの底部、特に角部、における、ゲート絶縁膜中での電界集中に起因したゲート絶縁膜の破壊現象が、耐圧の主な決定要因である。このように耐圧の決定要因がSi半導体装置とSiC半導体装置との間で異なる。このため、Siの使用を前提としていると考えられる上記公報の技術をSiC半導体装置の耐圧を向上させるために単純に適用したとすると、SiCの物性上の利点を十分に利用した耐圧の改善を行うことができない。

【 0 0 0 7 】

本発明は、上記のような課題を解決するために成されたものであり、この発明の目的は、高い耐圧と低いオン抵抗とを有する炭化珪素半導体装置を提供することである。

#### 【課題を解決するための手段】

[ 0 0 0 8 ]

本発明の炭化珪素半導体装置は、第1の電極と、第1のドリフト層と、緩和領域と、第2のドリフト層と、ボディ領域と、ソース領域と、第2の電極と、ゲート絶縁膜と、ゲート電極とを有する。第1のドリフト層は、第1の電極に面しつつ第1の電極に電気的に接続された第1の面と、第1の面と反対の第2の面とを有する。第1のドリフト層は、第1の導電型を有し、不純物濃度 $N_A$ を有する。緩和領域は、第1のドリフト層の第2の面に部分的に設けられており、第1の面から距離 $L_A$ を有する。緩和領域は第2の導電型を有する。第2のドリフト層は、第2の面に接する第3の面と、第3の面と反対の第4の面とを有する。第2のドリフト層は第1の導電型を有する。第1のドリフト層および第2のドリフト層は、緩和領域を埋め込むドリフト領域を構成している。第2のドリフト層は不純物濃度 $N_B$ を有する。

物濃度  $N_B$  を有し、 $N_B > N_A$  が満たされている。ボディ領域は第2のドリフト層の第4の面上に設けられている。ボディ領域は第2の導電型を有する。ソース領域は、ボディ領域上に設けられており、ボディ領域によってドリフト領域から隔てられている。ソース領域は第1の導電型を有する。第2の電極はソース領域に電気的に接続されている。ゲート絶縁膜は、ソース領域および第2のドリフト層をつなぐようにボディ領域上に位置する部分を含む。ゲート電極はゲート絶縁膜上に設けられている。

## 【発明の効果】

## 【0009】

本発明によれば、高い耐圧と低いオン抵抗とを有する炭化珪素半導体装置が得られる。

## 【図面の簡単な説明】

## 【0010】

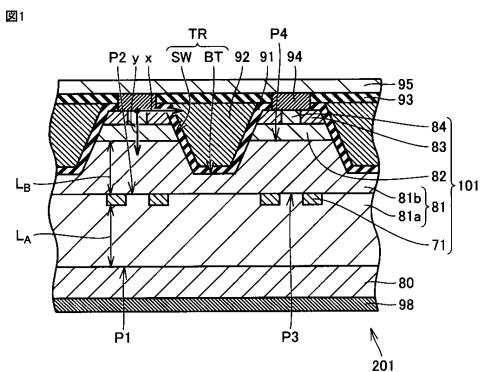

【図1】本発明の実施の形態1における炭化珪素半導体装置の構成を概略的に示す部分断面図である。

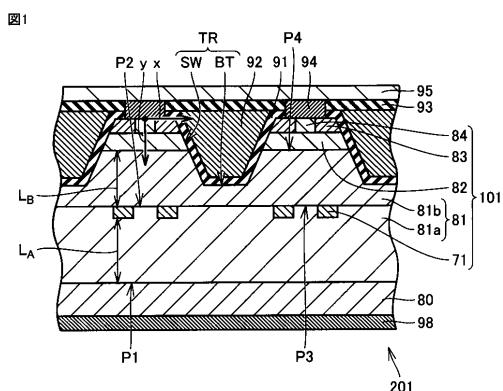

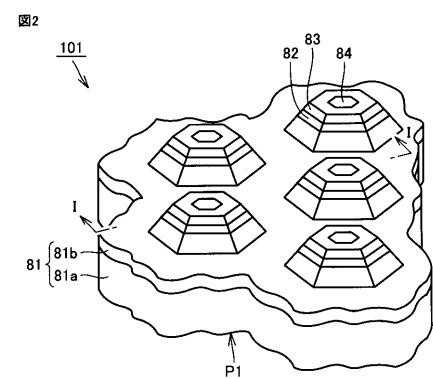

【図2】図1の炭化珪素半導体装置が有する炭化珪素層の形状を概略的に示す部分斜視図である。

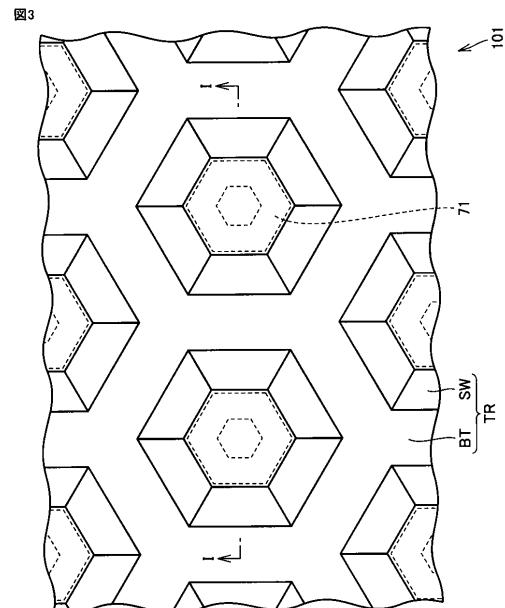

【図3】図1の炭化珪素半導体装置が有する炭化珪素層の形状を概略的に示す部分上面図である。

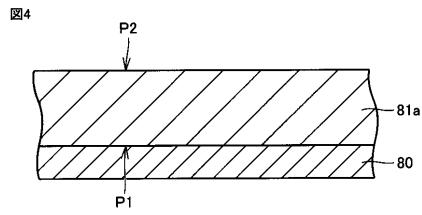

【図4】図1の炭化珪素半導体装置の製造方法の第1工程を概略的に示す部分断面図である。

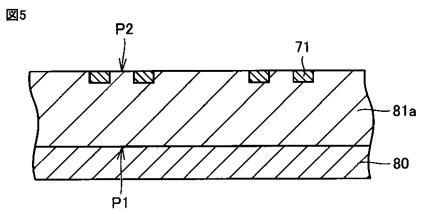

【図5】図1の炭化珪素半導体装置の製造方法の第2工程を概略的に示す部分断面図である。

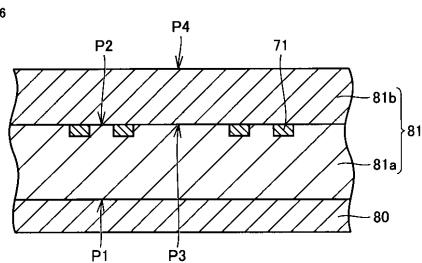

【図6】図1の炭化珪素半導体装置の製造方法の第3工程を概略的に示す部分断面図である。

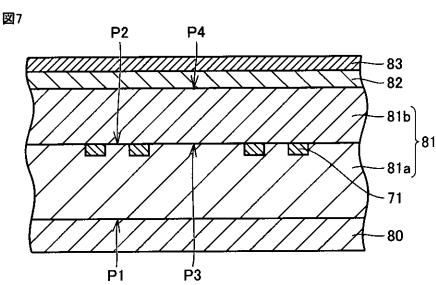

【図7】図1の炭化珪素半導体装置の製造方法の第4工程を概略的に示す部分断面図である。

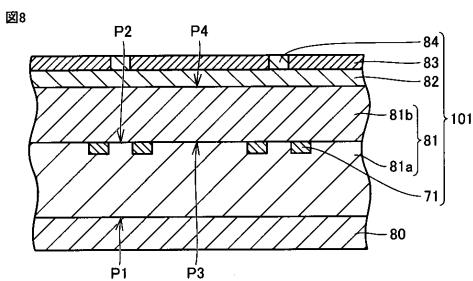

【図8】図1の炭化珪素半導体装置の製造方法の第5工程を概略的に示す部分断面図である。

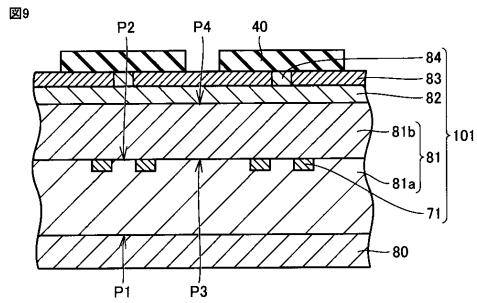

【図9】図1の炭化珪素半導体装置の製造方法の第6工程を概略的に示す部分断面図である。

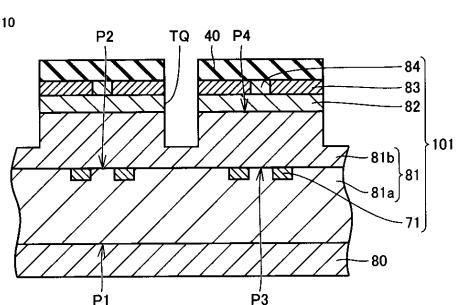

【図10】図1の炭化珪素半導体装置の製造方法の第7工程を概略的に示す部分断面図である。

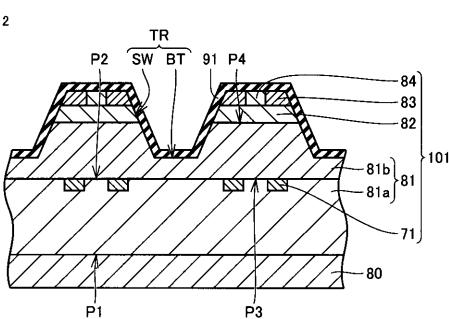

【図11】図1の炭化珪素半導体装置の製造方法の第8工程を概略的に示す部分断面図である。

【図12】図1の炭化珪素半導体装置の製造方法の第9工程を概略的に示す部分断面図である。

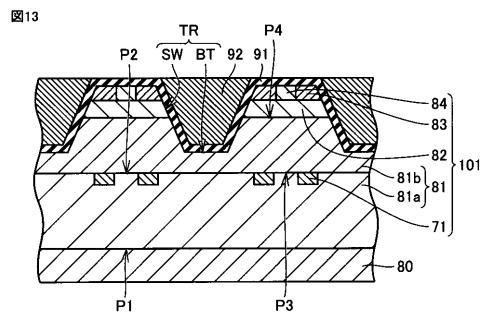

【図13】図1の炭化珪素半導体装置の製造方法の第10工程を概略的に示す部分断面図である。

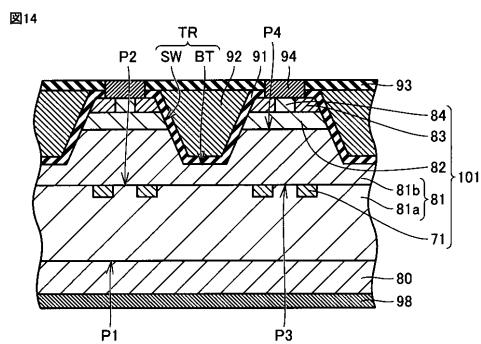

【図14】図1の炭化珪素半導体装置の製造方法の第11工程を概略的に示す部分断面図である。

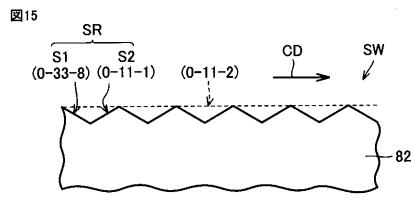

【図15】炭化珪素半導体装置が有する炭化珪素層の表面の微細構造を概略的に示す部分断面図である。

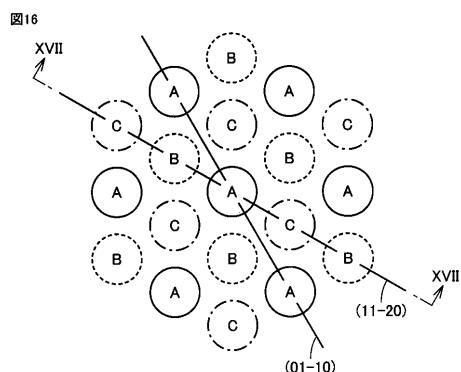

【図16】ポリタイプ4Hの六方晶における(000-1)面の結晶構造を示す図である。

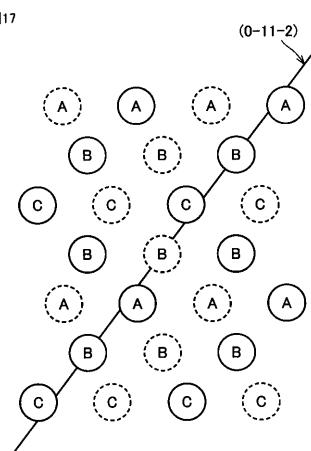

【図17】図16の線XVII-XVIIに沿う(11-20)面の結晶構造を示す図である。

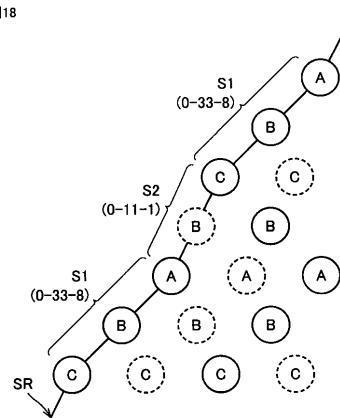

【図18】図15の複合面の表面近傍における結晶構造を(11-20)面内において示す図である。

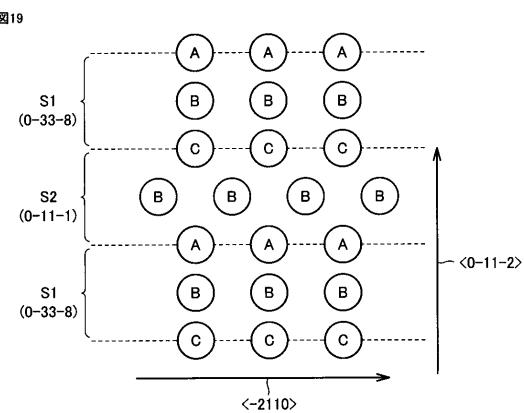

【図19】図15の複合面を(01-10)面から見た図である。

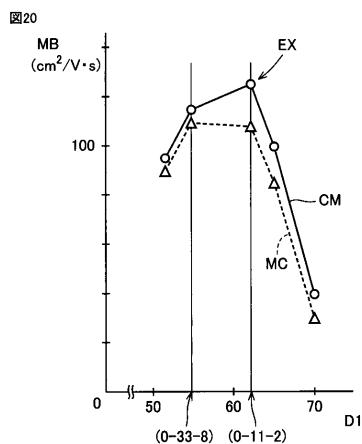

【図20】巨視的に見たチャネル面および(000-1)面の間の角度と、チャネル移動度との関係の一例を、熱エッチングが行われた場合と行われなかつた場合との各々につい

10

20

30

40

50

て示すグラフ図である。

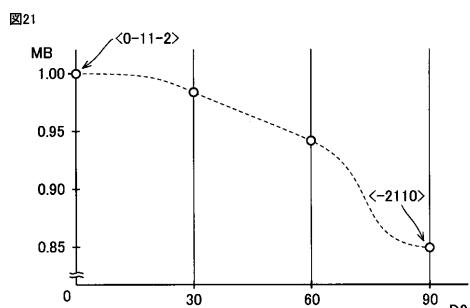

【図21】チャネル方向および<0-11-2>方向の間の角度と、チャネル移動度との関係の一例を示すグラフ図である。

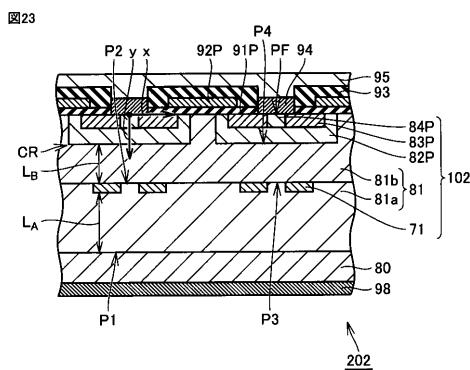

【図22】図15の変形例を示す図である。

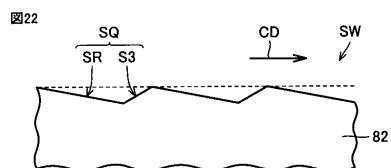

【図23】本発明の実施の形態2における炭化珪素半導体装置の構成を概略的に示す部分断面図である。

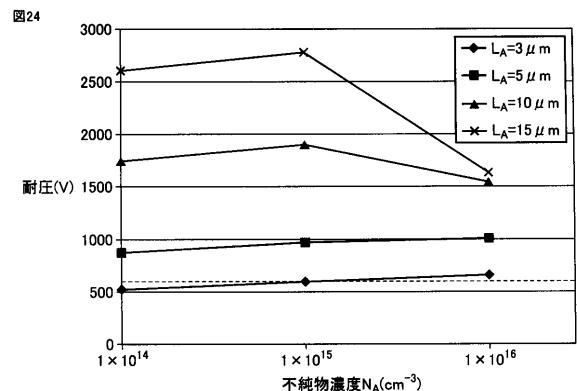

【図24】距離 $L_A = 3 \mu m$ 、 $5 \mu m$ 、 $10 \mu m$ および $15 \mu m$ の各々の場合における、下部ドリフト層の不純物濃度 $N_A$ と、耐圧との関係を例示するグラフ図である。

【発明を実施するための形態】

【0011】

以下、本発明の実施の形態について図に基づいて説明する。なお、以下の図面において、同一または相当する部分には同一の参照番号を付し、その説明は繰り返さない。また、本明細書中の結晶学的記載においては、個別方位を[ ]、集合方位を<>、個別面を( )、集合面を{ }でそれぞれ示している。また結晶学上の指数が負であることには、通常、"-"(バー)を数字の上に付すことによって表現されるが、本明細書中では数字の前に負の符号を付している。

【0012】

はじめに、実施の形態の概要について、以下の(i)~(vii)に記す。

(i) 炭化珪素半導体装置201, 202は、第1の電極98と、第1のドリフト層81aと、緩和領域71と、第2のドリフト層81bと、ボディ領域82と、ソース領域83と、第2の電極94と、ゲート絶縁膜91と、ゲート電極92とを有する。第1のドリフト層81aは、第1の電極98に面しあつ第1の電極98に電気的に接続された第1の面P1と、第1の面P1と反対の第2の面P2とを有する。第1のドリフト層81aは、第1の導電型を有し、不純物濃度 $N_A$ を有する。緩和領域71は、第1のドリフト層81aの第2の面P2に部分的に設けられており、第1の面P1から距離 $L_A$ を有する。緩和領域71は第2の導電型を有する。第2のドリフト層81bは、第2の面P2に接する第3の面P3と、第3の面P3と反対の第4の面P4とを有する。第2のドリフト層81bは第1の導電型を有する。第1のドリフト層81aおよび第2のドリフト層81bは、緩和領域71を埋め込むドリフト領域81を構成している。第2のドリフト層81bは不純物濃度 $N_B$ を有し、 $N_B > N_A$ が満たされている。ボディ領域82は第2のドリフト層81bの第4の面P4上に設けられている。ボディ領域は第2の導電型を有する。ソース領域83は、ボディ領域82上に設けられており、ボディ領域82によってドリフト領域から隔てられている。ソース領域83は第1の導電型を有する。第2の電極94はソース領域83に電気的に接続されている。ゲート絶縁膜91は、ソース領域83および第2のドリフト層81bをつなぐようにボディ領域82上に位置する部分を含む。ゲート電極92はゲート絶縁膜91上に設けられている。

【0013】

この炭化珪素半導体装置201, 202によれば、 $N_B > N_A$ が満たされる。これにより、第1の電極98および第2の電極94の間に電圧が印加された際に、ボディ領域82から第2のドリフト層81bへの空乏層の伸展に比して、緩和領域71から第1のドリフト層81aへの空乏層の伸展の方が、より促進される。よって、印加電圧のうち大きな割合が第1のドリフト層81aで負担される。よって、第2のドリフト層81bにおいて電界強度を抑制することができる。炭化珪素半導体装置の破壊は第2のドリフト層またはその上に設けられた構造において生じやすい。よって上述したように第2のドリフト層81bにおいて電界強度を抑制することで、炭化珪素半導体装置201, 202の耐圧を高めることができる。

【0014】

また $N_B > N_A$ の場合に比して第2のドリフト層81bの不純物濃度が高いので、第2のドリフト層81bの電気抵抗を低くすることができる。よって炭化珪素半導体装置201, 202のオン抵抗を低くすることができる。

10

20

30

40

50

## 【0015】

以上のように、高い耐圧と低いオン抵抗とを有する炭化珪素半導体装置 201, 202 が得られる。

## 【0016】

(ii) 第3の面 P3 が第4の面 P4 から距離  $L_B$  を有し、 $L_A > L_B$  が満たされていてもよい。

## 【0017】

これにより第1のドリフト層により負担される電圧の割合を、より高めることができる。よって耐圧をより高めることができる。

## 【0018】

(iii) 上記(ii)において、 $L_A > 2 \cdot L_B$  が満たされていてもよい。

これにより第1のドリフト層 81a により負担される電圧の割合を、さらにより高めることができる。よって耐圧をより高めることができる。

## 【0019】

(iv)  $L_A > 5 \mu m$  が満たされていてもよい。

これにより、緩和領域 71 と第1の面 P1との間に、最大で  $5 \mu m$  の長さを有する空乏層が形成され得る。言い換えれば、緩和領域 71 と第1の面 P1との間に、十分な長さを有する空乏層が、より確実に形成され得る。よって炭化珪素半導体装置 201, 202 の耐圧をより高め得る。

## 【0020】

(v) 緩和領域 71 はドーズ量  $D_R$  を有し、 $L_A \cdot N_A < D_R$  が満たされていてもよい。ここで「ドーズ量」とは単位面積当たりの不純物量を意味する。単位面積は、厚さ方向に垂直な面におけるものである。

## 【0021】

これにより、炭化珪素半導体装置 201, 202 がオフ状態とされることで第1の電極 98 と第2の電極 94 との間の電圧が高まった際に、緩和領域 71 から第1の面 P1 に向かって空乏層が十分に延びる前に緩和領域 71 が完全に空乏化してしまうことが防止される。これにより緩和領域 71 と第1の面 P1との間で第1のドリフト層 81a 中に、十分な長さを有する空乏層が形成され得る。よって、第1の電極 98 と第2の電極 94 との間の電圧について、第1のドリフト層 81a で負担される割合が高められる。言い換えれば、第2のドリフト層 81b で負担される電圧が軽減される。これにより、電界集中によつて破壊が生じやすい部分での電界強度をより抑制することができる。これにより炭化珪素半導体装置の耐圧がより高められる。

## 【0022】

(vi) 炭化珪素半導体装置 201 には、側壁面 SW を有するトレンチ TR が設けられていてもよい。側壁面 SW は、ソース領域 83 およびボディ領域 82 を貫通して第2のドリフト層 81b に至っている。また側壁面 SW は第1のドリフト層 81a から離れている。ゲート電極 92 はゲート絶縁膜 91 を介して側壁面 SW 上に位置している。

## 【0023】

このようなトレンチ型の炭化珪素半導体装置においては、第2のドリフト層中に至る側壁面 SW 端部の近傍でのゲート絶縁膜の破壊が、炭化珪素半導体装置の耐圧の決定要因となりやすい。このような場合であっても、上記(i)の特徴を有することで、オン抵抗を抑制しつつ、十分な耐圧を確保することができる。

## 【0024】

(vii) 炭化珪素半導体装置 202 には、ソース領域 83P、ボディ領域 82P および第2のドリフト層 81b の各々からなる部分を有しあつ第2のドリフト層 81b の第4の面 P4 と平行な平坦面 PF が設けられていてもよい。ゲート電極 92P はゲート絶縁膜 91P を介して平坦面 PF 上に位置している。

## 【0025】

このようなプレーナ型の炭化珪素半導体装置 202 においては、第2のドリフト層 81

10

20

30

40

50

bとボディ領域82Pとの界面近傍での破壊が、炭化珪素半導体装置202の耐圧の決定要因となりやすい。このような場合であっても、上記(i)の特徴を有することで、オン抵抗を抑制しつつ、十分な耐圧を確保することができる。

#### 【0026】

次に、本願発明の実施の形態のより詳細な説明として、以下に実施の形態1および2と補足事項とについて説明する。

#### 【0027】

##### (実施の形態1)

図1～図3に示すように、本実施の形態のMOSFET201(炭化珪素半導体装置)は、単結晶基板80と、エピタキシャル層101(炭化珪素層)と、ゲート酸化膜91(ゲート絶縁膜)と、ゲート電極92と、層間絶縁膜93と、ソース電極94(第2の電極)と、ソース配線層95と、ドレイン電極98(第1の電極)とを有する。MOSFET201は、ドレイン電極98およびソース電極94の間で600V以上の耐圧を有することが好ましい。言い換ればMOSFET201は、高耐圧を有する電力用半導体装置であることが好ましい。

10

#### 【0028】

単結晶基板80は、炭化珪素からなり、n型(第1の導電型)を有する。単結晶基板80の一方の面(図中、上面)上にはエピタキシャル層101が設けられ、他方の面(図中、下面)上にはオーミック電極としてのドレイン電極98が設けられている。単結晶基板80は、ポリタイプ4Hの六方晶の結晶構造を有することが好ましい。

20

#### 【0029】

エピタキシャル層101は、単結晶基板80上にエピタキシャルに成長させられた炭化珪素層である。エピタキシャル層101は、ポリタイプ4Hの六方晶の結晶構造を有することが好ましい。エピタキシャル層101は、緩和領域71と、ドリフト領域81と、ボディ領域82と、ソース領域83と、コンタクト領域84を有する。

#### 【0030】

ドリフト領域81はn型を有する。ドリフト領域81は下部ドリフト層81a(第1のドリフト層)および上部ドリフト層81b(第2のドリフト層)を有する。下部ドリフト層81aは、第1の面P1と、第1の面P1と反対の第2の面P2とを有する。第1の面P1は、ドレイン電極98に面しており、単結晶基板80を介してドレイン電極98に電気的に接続されている。下部ドリフト層81aは、n型を有し、不純物濃度N<sub>A</sub>を有する。

30

#### 【0031】

緩和領域71は、下部ドリフト層81aの第2の面P2に部分的に設けられており、第1の面P1から距離L<sub>A</sub>を有する。好ましくはL<sub>A</sub>>5μmが満たされている。緩和領域71は、p型(第2の導電型)を有し、不純物として、たとえばアルミニウムが添加されている。緩和領域71はドーズ量D<sub>R</sub>を有する。ここで「ドーズ量」とは単位面積当たりの不純物量を意味する。単位面積は、厚さ方向(図1における縦方向)に垂直な面におけるものである。言い換れば、ドース量とは、単位体積当たりの不純物濃度を厚さ方向に積分した値である。好ましくは、L<sub>A</sub>·N<sub>A</sub><D<sub>R</sub>が満たされている。緩和領域71のドース量は、好ましくは1×10<sup>12</sup>c m<sup>-2</sup>以上であり、より好ましくは1×10<sup>13</sup>c m<sup>-2</sup>以上である。またこのドーズ量は、好ましくは1×10<sup>15</sup>c m<sup>-2</sup>以下である。このドーズ量は、たとえば3×10<sup>13</sup>c m<sup>-2</sup>である。

40

#### 【0032】

上部ドリフト層81bは、下部ドリフト層81aの第2の面P2上に設けられている。上部ドリフト層81bは、第2の面P2に接する第3の面P3と、第3の面P3と反対の第4の面P4とを有する。第3の面P3は第4の面P4から距離L<sub>B</sub>を有する。言い換れば、上部ドリフト層81bは厚さL<sub>B</sub>を有する。緩和領域71および第1の面P1の間の距離L<sub>A</sub>と、第3の面P3および第4の面P4の間の距離L<sub>B</sub>との間で、好ましくはL<sub>A</sub>>L<sub>B</sub>が満たされており、より好ましくはL<sub>A</sub>>2·L<sub>B</sub>が満たされている。下部ドリフト

50

層 8 1 a および上部ドリフト層 8 1 b は、緩和領域 7 1 を埋め込むドリフト領域 8 1 を構成している。言い換えれば上部ドリフト層 8 1 b は緩和領域 7 1 を覆っている。上部ドリフト層 8 1 b は、n 型を有し、不純物濃度  $N_B$  を有する。

#### 【 0 0 3 3 】

下部ドリフト層 8 1 a の不純物濃度  $N_A$  と上部ドリフト層 8 1 b の不純物濃度  $N_B$  との間では、 $N_B > N_A$  の関係が満たされている。不純物濃度  $N_A$  は、好ましくは  $3 \times 10^{15} \text{ cm}^{-3}$  以上  $1 \times 10^{16} \text{ cm}^{-3}$  以下であり、たとえば  $4 \times 10^{15} \text{ cm}^{-3}$  である。不純物濃度  $N_B$  は、好ましくは  $7 \times 10^{15} \text{ cm}^{-3}$  以上  $5 \times 10^{16} \text{ cm}^{-3}$  以下であり、たとえば  $7.5 \times 10^{15} \text{ cm}^{-3}$  である。単結晶基板 8 0 の不純物濃度は、不純物濃度  $N_A$  よりも十分に大きいことが好ましく、たとえば 50 倍以上である。このような場合、単結晶基板 8 0 はドリフト領域としての機能、すなわち耐圧保持機能を実質的に有しない。10

#### 【 0 0 3 4 】

ボディ領域 8 2 は上部ドリフト層 8 1 b の第 4 の面 P 4 上に設けられている。ボディ領域は p 型を有する。ボディ領域 8 2 は上部ドリフト層 8 1 b によって緩和領域 7 1 から隔てられている。ボディ領域 8 2 の不純物濃度は、好ましくは  $1 \times 10^{17} \text{ cm}^{-3}$  以上  $5 \times 10^{18} \text{ cm}^{-3}$  以下であり、たとえば  $1 \times 10^{18} \text{ cm}^{-3}$  である。

#### 【 0 0 3 5 】

ソース領域 8 3 は、ボディ領域 8 2 上に設けられており、ボディ領域 8 2 によってドリフト領域から隔てられている。ソース領域は n 型を有する。ソース領域 8 3 はコンタクト領域 8 4 と共にエピタキシャル層 1 0 1 の上面をなしている。コンタクト領域 8 4 は p 型を有する。コンタクト領域 8 4 はボディ領域 8 2 につながっている。20

#### 【 0 0 3 6 】

MOSFET には、エピタキシャル層 1 0 1 の上面にトレンチ TR が設けられている。トレンチ TR は側壁面 SW および底面 BT を有する。側壁面 SW は、ソース領域 8 3 およびボディ領域 8 2 を貫通して上部ドリフト層 8 1 b に至っている。これにより側壁面 SW は、ボディ領域 8 2 上において MOSFET 2 0 1 のチャネル面を含む。側壁面 SW は下部ドリフト層 8 1 a から離れている。底面 BT は上部ドリフト層 8 1 b 上に位置している。本実施の形態においては底面 BT は上面とほぼ平行な平坦な形状を有する。底面 BT と側壁面 SW とがつながる部分はトレンチ TR の角部を構成している。本実施の形態においてはトレンチ TR は、平面視（図 3）において、ハニカム構造を有する網目を構成するように延びている。これによりエピタキシャル層 1 0 1 は、トレンチ TR によって囲まれた、六角形状を有する上面を有する。側壁面 SW はエピタキシャル層 1 0 1 の上面に対して傾斜しており、これによりトレンチ TR は開口に向かってテーパ状に拡がっている。側壁面 SW の面方位は、{0 0 0 1} 面に対して  $50^\circ$  以上  $65^\circ$  以下傾斜していることが好ましく、(0 0 0 - 1) 面に対して  $50^\circ$  以上  $65^\circ$  以下傾斜していることがより好ましい。好ましくは側壁面 SW は、特にボディ領域 8 2 上の部分において、所定の結晶面（特殊面とも称する）を有する。特殊面の詳細については後述する。30

#### 【 0 0 3 7 】

好ましくは緩和領域 7 1 は、図 3 に示すように、平面視においてトレンチ TR の底面 BT の外にのみ配置されている。本実施の形態においては、緩和領域 7 1 は、平面視において、開口部を有している。具体的には緩和領域 7 1 は、六角形状を有する上面とほぼ相似の外縁および開口部を有する。40

#### 【 0 0 3 8 】

ゲート酸化膜 9 1 は、トレンチ TR の側壁面 SW および底面 BT の各々を覆っている。これによりゲート酸化膜 9 1 は、ソース領域 8 3 および上部ドリフト層 8 1 b をつなぐようにボディ領域 8 2 上に位置する部分を含む。ゲート電極 9 2 はゲート酸化膜 9 1 上に設けられている。これによりゲート電極 9 2 はゲート酸化膜 9 1 を介して側壁面 SW 上に位置する部分を有する。

#### 【 0 0 3 9 】

ソース電極 9 4 は、ソース領域 8 3 およびコンタクト領域 8 4 の各々に接することによ50

り各々に電気的に接続されている。ソース配線層 9 5 はソース電極 9 4 に接している。ソース配線層 9 5 は、たとえばアルミニウム層である。層間絶縁膜 9 3 はゲート電極 9 2 とソース配線層 9 5 との間を絶縁している。

#### 【0040】

本実施の形態によれば、MOSFET 201 には、側壁面 SW を有するトレンチ TR が設けられている。側壁面 SW は、ソース領域 8 3 およびボディ領域 8 2 を貫通して上部ドリフト層 8 1 b に至っており、かつ下部ドリフト層 8 1 a から離れている。ゲート電極 9 2 はゲート酸化膜 9 1 を介して側壁面 SW 上に位置している。このようなトレンチ型の MOSFET 201 においては、下部ドリフト層 8 1 b 中に至る側壁面 SW 端部（トレンチ TR の角部）の近傍でのゲート絶縁膜 9 1 の破壊が、MOSFET 201 の耐圧の決定要因となりやすい。10

#### 【0041】

ここで下部ドリフト層 8 1 a の不純物濃度  $N_A$  と上部ドリフト層 8 1 b の不純物濃度  $N_B$  との間で  $N_B > N_A$  が満たされていることにより、ドレイン電極 9 8 およびソース電極 9 4 の間に電圧が印加された際に、ボディ領域 8 2 から上部ドリフト層 8 1 b への空乏層の伸展に比して、緩和領域 7 1 から下部ドリフト層 8 1 a への空乏層の伸展の方が、より促進される。よって、印加電圧のうち大きな割合が下部ドリフト層 8 1 a で負担される。よって、上部ドリフト層 8 1 b において電界強度を抑制することができる。上述したように MOSFET 201 の破壊は下部ドリフト層 8 1 b 上のゲート絶縁膜 9 1 において生じやすい。よって上部ドリフト層 8 1 b において電界強度を抑制することで、MOSFET 201 の耐圧を高めることができる。20

#### 【0042】

また  $N_B > N_A$  の場合に比して上部ドリフト層 8 1 b の不純物濃度が高いので、上部ドリフト層 8 1 b の電気抵抗を低くすることができる。よって MOSFET 201 のオン抵抗を低くすることができる。

#### 【0043】

以上のように、高い耐圧と低いオン抵抗とを有する MOSFET 201 が得られる。

距離  $L_A$  および  $L_B$ （図 1）の間で  $L_A > L_B$  が満たされている場合、特には  $L_A > 2 \cdot L_B$  が満たされている場合、下部ドリフト層 8 1 a により負担される電圧の割合を、より高めることができます。よって耐圧をより高めることができます。30

#### 【0044】

$L_A > 5 \mu m$  が満たされている場合、緩和領域 7 1 と第 1 の面 P 1 との間に、最大で 5  $\mu m$  の長さを有する空乏層が形成され得る。言い換えれば、緩和領域 7 1 と第 1 の面 P 1 との間に、十分な長さを有する空乏層が、より確実に形成され得る。よって MOSFET 201 の耐圧をより高め得る。

#### 【0045】

$L_A \cdot N_A < D_R$  が満たされている場合、MOSFET 201 がオフ状態とされることでドレイン電極 9 8 とソース電極 9 4 との間の電圧が高まった際に、緩和領域 7 1 から第 1 の面 P 1 に向かって空乏層が十分に延びる前に緩和領域 7 1 が完全に空乏化してしまうことが防止される。これにより緩和領域 7 1 と第 1 の面 P 1 との間で下部ドリフト層 8 1 a 中に、十分な長さを有する空乏層が形成され得る。よって、ドレイン電極 9 8 とソース電極 9 4 との間の電圧について、下部ドリフト層 8 1 a で負担される割合が高められる。言い換えれば、上部ドリフト層 8 1 b で負担される電圧が軽減される。これにより、電界集中によって破壊が生じやすい部分での電界強度をより抑制することができる。これにより MOSFET 201 の耐圧がより高められる。40

#### 【0046】

また下部ドリフト層 8 1 a とドレイン電極 9 8 との電気的接続が、不純物濃度  $N_A$  より高い不純物濃度を有する単結晶基板 8 0 を介して行なわれる。よってドレイン電極 9 8 の接触抵抗を小さくすることができる。よってその分だけドリフト領域 8 1 の電気抵抗を大きくし得る。よってドリフト領域 8 1 の不純物濃度をより低くし得る。よって MOSFE50

T 2 0 1 の耐圧をより高め得る。

【 0 0 4 7 】

緩和領域 7 1 が平面視（図 3）においてトレンチ TR の底面 BT の外に配置されている場合、MOSFET 2 0 1 がオフ状態にある場合に、トレンチ TR の底面 BT の縁に位置するトレンチ TR の角部に向かって、緩和領域 7 1 から空乏層が延びる。よって電界緩和構造の効果をより高めることができる。

【 0 0 4 8 】

次に MOSFET 2 0 1（図 1）の製造方法について、以下に説明する。

図 4 に示すように、下部ドリフト層 8 1 a が単結晶基板 8 0 上に形成される。具体的には、単結晶基板 8 0 上におけるエピタキシャル成長によって下部ドリフト層 8 1 a が形成される。このエピタキシャル成長は、たとえば原料ガスとしてシラン ( $\text{SiH}_4$ ) とプロパン ( $\text{C}_3\text{H}_8$ ) との混合ガスを用い、キャリアガスとしてたとえば水素ガス ( $\text{H}_2$ ) を用いた CVD (Chemical Vapor Deposition) 法により行うことができる。この際、不純物として、たとえば窒素 (N) やリン (P) を導入することが好ましい。

10

【 0 0 4 9 】

図 5 に示すように、下部ドリフト層 8 1 a の第 2 の面 P 2 の一部の上に、p 型を有する緩和領域 7 1 が形成される。具体的には、第 2 の面 P 2 上において、注入マスク（図示せず）を用いたアクセプタイオン（第 2 の導電型を付与するための不純物イオン）の注入が行われる。

20

【 0 0 5 0 】

図 6 に示すように、緩和領域 7 1 が形成された後に第 2 の面 P 2 上に、n 型を有する上部ドリフト層 8 1 b が形成される。これにより緩和領域 7 1 は、下部ドリフト層 8 1 a および上部ドリフト層 8 1 b によって構成されるドリフト領域 8 1 に埋め込まれる。上部ドリフト層 8 1 b は下部ドリフト層 8 1 a の形成方法と同様の方法によって形成され得る。

30

【 0 0 5 1 】

図 7 に示すように、上部ドリフト層 8 1 b の第 4 の面 P 4 上にボディ領域 8 2 およびソース領域 8 3 が形成される。図 8 に示すように、ボディ領域 8 2 上にコンタクト領域 8 4 が形成される。これらの形成は、たとえば上部ドリフト層 8 1 b の第 4 の面（図 6）上へのイオン注入により行い得る。ボディ領域 8 2 およびコンタクト領域 8 4 を形成するためのイオン注入においては、たとえばアルミニウム (Al) などの、p 型を付与するための不純物がイオン注入される。またソース領域 8 3 を形成するためのイオン注入においては、たとえばリン (P) などの、n 型を付与するための不純物がイオン注入される。なおイオン注入の代わり、不純物の添加をともなうにエピタキシャル成長が用いられてもよい。

30

【 0 0 5 2 】

次に、不純物を活性化するための熱処理が行われる。この熱処理の温度は、好ましくは 1 5 0 0 以上 1 9 0 0 以下であり、たとえば 1 7 0 0 程度である。熱処理の時間は、たとえば 3 0 分程度である。熱処理の雰囲気は、好ましくは不活性ガス雰囲気であり、たとえば Ar 雰囲気である。

40

【 0 0 5 3 】

図 9 に示すように、ソース領域 8 3 およびコンタクト領域 8 4 からなる面上に、開口部を有するマスク層 4 0 が形成される。マスク層 4 0 として、たとえばシリコン酸化膜などを用いることができる。開口部はトレンチ TR（図 1）の位置に対応して形成される。

40

【 0 0 5 4 】

図 10 に示すように、マスク層 4 0 の開口部において、ソース領域 8 3 と、ボディ領域 8 2 と、上部ドリフト層 8 1 b の一部とがエッティングにより除去される。エッティングの方法としては、たとえば反応性イオンエッティング (RIE)、特に誘導結合プラズマ (ICP) RIE を用いることができる。具体的には、たとえば反応ガスとして  $\text{SF}_6$  または  $\text{SF}_6$  と  $\text{O}_2$  との混合ガスを用いた ICP - RIE を用いることができる。このようなエッティングにより、トレンチ TR（図 1）が形成されるべき領域に、上面に対してほぼ垂直な側壁を有する凹部 TQ が形成される。

50

## 【0055】

次に、凹部TQにおいて熱エッティングが行われる。熱エッティングは、たとえば、少なくとも1種類以上のハロゲン原子を有する反応性ガスを含む雰囲気中の加熱によって行い得る。少なくとも1種類以上のハロゲン原子は、塩素(C1)原子およびフッ素(F)原子の少なくともいずれかを含む。この雰囲気は、たとえば、 $\text{Cl}_2$ 、 $\text{BCl}_3$ 、 $\text{SF}_6$ 、または $\text{CF}_4$ である。たとえば、塩素ガスと酸素ガスとの混合ガスを反応ガスとして用い、熱処理温度を、たとえば700以上1000以下として、熱エッティングが行われる。

## 【0056】

なお、反応ガスは、上述した塩素ガスと酸素ガスとに加えて、キャリアガスを含んでいてもよい。キャリアガスとしては、たとえば窒素( $\text{N}_2$ )ガス、アルゴンガス、ヘリウムガスなどを用いることができる。そして、上述のように熱処理温度を700以上1000以下とした場合、SiCのエッティング速度はたとえば約 $70\text{ }\mu\text{m}/\text{時}$ になる。また、この場合に、酸化珪素から作られたマスク層40は、SiCに対する選択比が極めて大きいので、SiCのエッティング中に実質的にエッティングされない。

10

## 【0057】

図11に示すように、上記の熱エッティングにより、エピタキシャル層101の上面にトレンチTRが形成される。好ましくは、トレンチTRの形成時、側壁面SW上、特にボディ領域82上において、特殊面が自己形成される。次にマスク層40がエッティングなど任意の方法により除去される。

20

## 【0058】

図12に示すように、トレンチTRの側壁面SWおよび底面BTの各々を覆うゲート酸化膜91が形成される。ゲート酸化膜91は、たとえば熱酸化により形成され得る。この後に、雰囲気ガスとして一酸化窒素(NO)ガスを用いるNOアニールが行わってもよい。温度プロファイルは、たとえば、温度1100以上1300以下、保持時間1時間程度の条件を有する。これにより、ゲート酸化膜91とボディ領域82との界面領域に窒素原子が導入される。その結果、界面領域における界面準位の形成が抑制されることで、チャネル移動度を向上させることができる。なお、このような窒素原子の導入が可能であれば、NOガス以外のガスが雰囲気ガスとして用いられてもよい。このNOアニールの後にさらに、雰囲気ガスとしてアルゴン(Ar)を用いるArアニールが行わってもよい。Arアニールの加熱温度は、上記NOアニールの加熱温度よりも高く、ゲート酸化膜91の融点よりも低いことが好ましい。この加熱温度が保持される時間は、たとえば1時間程度である。これにより、ゲート酸化膜91とボディ領域82との界面領域における界面準位の形成がさらに抑制される。なお、雰囲気ガスとして、Arガスに代えて窒素ガスなどの他の不活性ガスが用いられてもよい。

30

## 【0059】

図13に示すように、ゲート酸化膜91上にゲート電極92が形成される。具体的には、トレンチTRの内部の領域をゲート酸化膜91を介して埋めるように、ゲート酸化膜91上にゲート電極92が形成される。ゲート電極92の形成方法は、たとえば、導体またはドープトポリシリコンの成膜とCMP(Chemical Mechanical Polishing)とによって行い得る。

40

## 【0060】

図14を参照して、ゲート電極92の露出面を覆うように、ゲート電極92およびゲート酸化膜91上に層間絶縁膜93が形成される。層間絶縁膜93およびゲート酸化膜91に開口部が形成されるようにエッティングが行われる。この開口部により上面においてソース領域83およびコンタクト領域84の各々が露出される。次に上面においてソース領域83およびコンタクト領域84の各々に接するソース電極94が形成される。ドリフト領域81からなる第1の面P1上に、単結晶基板80を介して、ドレイン電極98が形成される。

## 【0061】

再び図1を参照して、ソース配線層95が形成される。これにより、MOSFET20

50

1が得られる。

**【0062】**

(特殊面)

上述した側壁面SWは、特にボディ領域82上の部分において、特殊面を有する。特殊面を有する側壁面SWは、図15に示すように、面方位{0-33-8}を有する面S1を含む。言い換えれば、トレーナーTRの側壁面SW上においてボディ領域82には、面S1を含む表面が設けられている。面S1は好ましくは面方位(0-33-8)を有する。

**【0063】**

より好ましくは、側壁面SWは面S1を微視的に含み、側壁面SWはさらに、面方位{0-11-1}を有する面S2を微視的に含む。ここで「微視的」とは、原子間隔の2倍程度の寸法を少なくとも考慮する程度に詳細に、ということを意味する。このように微視的な構造の観察方法としては、たとえばTEM(Transmission Electron Microscope)を用いることができる。面S2は好ましくは面方位(0-11-1)を有する。

10

**【0064】**

好ましくは、側壁面SWの面S1および面S2は、面方位{0-11-2}を有する複合面SRを構成している。すなわち複合面SRは、面S1およびS2が周期的に繰り返されることによって構成されている。このような周期的構造は、たとえば、TEMまたはAFM(Atomic Force Microscopy)により観察し得る。この場合、複合面SRは{000-1}面に対して巨視的に62°のオフ角を有する。ここで「巨視的」とは、原子間隔程度の寸法を有する微細構造を無視することを意味する。このように巨視的なオフ角の測定としては、たとえば、一般的なX線回折を用いた方法を用い得る。好ましくは複合面SRは面方位(0-11-2)を有する。この場合、複合面SRは(000-1)面に対して巨視的に62°のオフ角を有する。

20

**【0065】**

好ましくは、チャネル面上においてキャリアが流れる方向(すなわちMOSFETの厚さ方向(図1などにおける縦方向))であるチャネル方向CDは、上述した周期的繰り返しが行われる方向に沿っている。

**【0066】**

次に複合面SRの詳細な構造について説明する。

一般に、ポリタイプ4Hの炭化珪素単結晶を(000-1)面から見ると、図16に示すように、Si原子(またはC原子)は、A層の原子(図中の実線)と、この下に位置するB層の原子(図中の破線)と、この下に位置するC層の原子(図中的一点鎖線)と、この下に位置するB層の原子(図示せず)とが繰り返し設けられている。つまり4つの層ABCBA周期としてABCBAABCBA...のような周期的な積層構造が設けられている。

30

**【0067】**

図17に示すように、(11-20)面(図16の線XVII-XVIIの断面)において、上述した1周期を構成する4つの層ABCBAの各層の原子は、(0-11-2)面に完全に沿うようには配列されていない。図17においてはB層の原子の位置を通るように(0-11-2)面が示されており、この場合、A層およびC層の各々の原子は(0-11-2)面からずれていることがわかる。このため、炭化珪素単結晶の表面の巨視的な面方位、すなわち原子レベルの構造を無視した場合の面方位が(0-11-2)に限定されたとしても、この表面は、微視的には様々な構造をとり得る。

40

**【0068】**

図18に示すように、複合面SRは、面方位(0-33-8)を有する面S1と、面S1につながりかつ面S1の面方位と異なる面方位を有する面S2とが交互に設けられることによって構成されている。面S1および面S2の各々の長さは、Si原子(またはC原子)の原子間隔の2倍である。なお面S1および面S2が平均化された面は、(0-11-2)面(図17)に対応する。

**【0069】**

50

図19に示すように、複合面SRを(01-10)面から見て単結晶構造は、部分的に見て立方晶と等価な構造(面S1の部分)を周期的に含んでいる。具体的には複合面SRは、上述した立方晶と等価な構造における面方位(001)を有する面S1と、面S1につながりかつ面S1の面方位と異なる面方位を有する面S2とが交互に設けられることによって構成されている。このように、立方晶と等価な構造における面方位(001)を有する面(図24においては面S1)と、この面につながりかつこの面方位と異なる面方位を有する面(図16においては面S2)とによって表面を構成することは4H以外のポリタイプにおいても可能である。ポリタイプは、たとえば6Hまたは15Rであってもよい。

#### 【0070】

次に図20を参照して、側壁面SWの結晶面と、チャネル面の移動度MBとの関係について説明する。図20のグラフにおいて、横軸は、チャネル面を有する側壁面SWの巨視的な面方位と(000-1)面とのなす角度D1を示し、縦軸は移動度MBを示す。プロット群CMは側壁面SWが熱エッチングによる特殊面として仕上げられた場合に対応し、プロット群MCはそのような熱エッチングがなされない場合に対応する。

#### 【0071】

プロット群MCにおける移動度MBは、チャネル面の表面の巨視的な面方位が(0-33-8)のときに最大となった。この理由は、熱エッチングが行われない場合、すなわち、チャネル表面の微視的な構造が特に制御されない場合においては、巨視的な面方位が(0-33-8)とされることによって、微視的な面方位(0-33-8)、つまり原子レベルまで考慮した場合の面方位(0-33-8)が形成される割合が確率的に高くなつたためと考えられる。

#### 【0072】

一方、プロット群CMにおける移動度MBは、チャネル面の表面の巨視的な面方位が(0-11-2)のとき(矢印EX)に最大となった。この理由は、図18および図19に示すように、面方位(0-33-8)を有する多数の面S1が面S2を介して規則正しく稠密に配置されることで、チャネル面の表面において微視的な面方位(0-33-8)が占める割合が高くなつたためと考えられる。

#### 【0073】

なお移動度MBは複合面SR上において方位依存性を有する。図21に示すグラフにおいて、横軸はチャネル方向と<0-11-2>方向との間の角度D2を示し、縦軸はチャネル面の移動度MB(任意単位)を示す。破線はグラフを見やすくするために補助的に付してある。このグラフから、チャネル移動度MBを大きくするには、チャネル方向CD(図15)が有する角度D2は、0°以上60°以下であることが好ましく、ほぼ0°であることがより好ましいことがわかった。

#### 【0074】

図22に示すように、側壁面SWは複合面SRに加えてさらに面S3を含んでもよい。より具体的には、面S3および複合面SRが周期的に繰り返されることによって構成された複合面SQを側壁面SWが含んでもよい。この場合、側壁面SWの{000-1}面に対するオフ角は、理想的な複合面SRのオフ角である62°からずれる。このずれは小さいことが好ましく、±10°の範囲内であることが好ましい。このような角度範囲に含まれる表面としては、たとえば、巨視的な面方位が{0-33-8}面となる表面がある。より好ましくは、側壁面SWの(000-1)面に対するオフ角は、理想的な複合面SRのオフ角である62°からずれる。このずれは小さいことが好ましく、±10°の範囲内であることが好ましい。このような角度範囲に含まれる表面としては、たとえば、巨視的な面方位が(0-33-8)面となる表面がある。

#### 【0075】

このような周期的構造は、たとえば、TEMまたはAFMにより観察し得る。

(実施の形態2)

図23に示すように、本実施の形態のMOSFET202は、いわゆるプレーナ型であ

10

20

30

40

50

る。エピタキシャル層 102 は、ボディ領域 82P、ソース領域 83P およびコンタクト領域 84P を含む。MOSFET202 には平坦面 PF が設けられている。平坦面 PF は、ソース領域 83P、ボディ領域 82P および上部ドリフト層 81b の各々からなる部分を有し、かつ上部ドリフト層 81b の第 4 の面 P4 と平行である。ゲート電極 92P はゲート酸化膜 91P を介して平坦面 PF 上に位置している。なお、上記以外の構成については、上述した実施の形態 1 の構成とほぼ同じであるため、同一または対応する要素について同一の符号を付し、その説明を繰り返さない。

#### 【0076】

本実施の形態においては、下部ドリフト層 81b とボディ領域 82P との界面（特に角部 CR）の近傍での破壊が、MOSFET202 の耐圧の決定要因となりやすい。このような場合であっても、実施の形態 1 とほぼ同様の理由により、オン抵抗を抑制しつつ、十分な耐圧を確保することができる。

10

#### 【0077】

（不純物濃度  $N_A$  および距離  $L_d$  と、耐圧との関係について）

図 24 のシミュレーション結果に示すように、緩和領域 71 の完全空乏化が生じない程度に緩和領域の不純物ドーズ量が十分に高い場合、緩和領域 71 および下部ドリフト層 81a の界面の耐圧は主に、下部ドリフト層 81a の不純物濃度  $N_A$ 、および緩和領域 71 と第 1 の面 P1 との間の距離  $L_A$  によって決まる。この耐圧は、シリコン半導体装置においては 600V 程度（図中、破線参照）が上限となる。炭化珪素半導体装置においては、 $L_A = 5 \mu m$  の場合、600V 以上の耐圧が得られた。

20

#### 【0078】

（実施例 1）

MOSFET201（図 1）について、不純物濃度  $N_A$ 、 $N_B$  と、距離  $L_A$ 、 $L_B$  とを変化させて、電界強度およびオン抵抗  $R_{ON}$  のシミュレーション 1～5 を行なった。なおシミュレーション 1 は、不純物濃度  $N_A$ 、 $N_B$  が互いに同一とされた比較例である。結果を以下に示す。

#### 【0079】

【表1】

| # | $N_A$<br>[cm $^{-3}$ ] | $L_A$<br>[μm] | $N_B$<br>[cm $^{-3}$ ] | $L_B$<br>[μm] | $E_{fp/n}$<br>[MV/cm] | $E_{trench}$<br>[MV/cm] | $E_{ox}$<br>[MV/cm] | $E_{pn}$<br>[MV/cm] | $R_{on}$<br>[mohm·cm $^2$ ] |

|---|------------------------|---------------|------------------------|---------------|-----------------------|-------------------------|---------------------|---------------------|-----------------------------|

| 1 | $4.5 \times 10^{15}$   | 9             | $4.5 \times 10^{15}$   | 9             | 2.5                   | 1.07                    | 3.53                | 0.16                | 9.27                        |

| 2 | $4.5 \times 10^{15}$   | 9             | $5.5 \times 10^{15}$   | 3             | 2.5                   | 1.12                    | 3.73                | 0.16                | 3.25                        |

| 3 | $4.5 \times 10^{15}$   | 9             | $7.0 \times 10^{15}$   | 3             | 2.55                  | 1.16                    | 3.9                 | 0.17                | 2.95                        |

| 4 | $4.5 \times 10^{15}$   | 9             | $1.0 \times 10^{16}$   | 3             | 2.6                   | 1.22                    | 4.04                | 0.17                | 2.75                        |

| 5 | $4.5 \times 10^{15}$   | 9             | $2.0 \times 10^{16}$   | 3             | 2.7                   | 1.5                     | 4.4                 | 0.18                | 2.50                        |

## 【0080】

ここで、「 $E_{fp/n}$ 」は緩和領域71と下部ドリフト層81aとの界面近傍の最大電界強度、「 $E_{trench}$ 」はトレンチTRにおける最大電界強度、「 $E_{ox}$ 」はゲート酸化膜91での最大電界強度、「 $E_{pn}$ 」はボディ領域82と上部ドリフト層81bとの界面近傍の最大電界強度である。

## 【0081】

MOSFET201においては、緩和領域71が設けられることで $E_{ox}$ が効果的に抑制される一方で、 $E_{fp/n}$ が過度に高くならないように留意する必要がある。シミュレーション1（比較例）とシミュレーション2（実施例）との間では、 $E_{fp/n}$ を同程度に抑えつつ、後者（実施例）の方がオン抵抗 $R_{on}$ が抑制されていた。シミュレーション3～5に示すように、不純物濃度 $N_B$ を高めたところ、オン抵抗 $R_{on}$ はさらに抑制された。

## 【0082】

(実施例2)

上記と同様のシミュレーションをMOSFET202(図23)についても行なった。

その結果を以下に示す。

## 【0083】

## 【表2】

| # | $N_A$<br>[cm <sup>-3</sup> ] | $L_A$<br>[μm] | $N_B$<br>[cm <sup>-3</sup> ] | $L_B$<br>[μm] | $E_{fp}/n$<br>[MV/cm] | $E_{pn}$<br>[MV/cm] | $R_{on}$<br>[mohm·cm <sup>2</sup> ] |

|---|------------------------------|---------------|------------------------------|---------------|-----------------------|---------------------|-------------------------------------|

| 1 | $4.5 \times 10^{15}$         | 9             | $4.5 \times 10^{15}$         | 9             | 1.67                  | 1.28                | 7.66                                |

| 2 | $4.5 \times 10^{15}$         | 9             | $7.0 \times 10^{15}$         | 3             | 1.98                  | 1.32                | 4.06                                |

## 【0084】

シミュレーション1(比較例)とシミュレーション2(実施例)との間では、後者(実施例)の方がオン抵抗 $R_{on}$ が抑制されていた。

## 【0085】

今回開示された実施の形態および実施例はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。たとえば、トレンチは平坦な底面を有するものに限定されるものではなく、その断面形状がU字状またはV字状であってもよい。また炭化珪素半導体装置はMOSFETに限定されるものではなく、たとえばIGBT(Insulated Gate Bipolar Transistor)であってもよい。この場合、上述したソース電極、ソース領域およびドレイン電極のそれぞれは、エミッタ電極、エミッタ領域およびコレクタ電極としての機能を有する。また上記各実施の形態においては第1の導電型がn型であり第2の導電型がp型であるが、これらの導電型が入れ替えられてもよい。この場合、上記説明におけるドナーおよびアクセプタも入れ替えられる。なお、より高いチャネル移動度を得るために、第1導電型がn型であることが好ましい。また炭化珪素半導体装置は、必ずしも単結晶基板を有する必要はなく、単結晶基板が省略されてもよい。

## 【符号の説明】

## 【0086】

71 緩和領域

80 単結晶基板

81 ドリフト領域

81a 上部ドリフト層(第1のドリフト層)

81b 下部ドリフト層(第2のドリフト層)

82, 82P ボディ領域

83, 83P ソース領域

84, 84P コンタクト領域

91, 91P ゲート酸化膜(ゲート絶縁膜)

92, 92P ゲート電極

93 層間絶縁膜

94 ソース電極

95 ソース配線層

98 ドレイン電極(第1の電極)

94 ソース電極(第2の電極)

101, 102 エピタキシャル層

201, 202 MOSFET(炭化珪素半導体装置)

BT 底面

10

20

30

40

50

C D チャネル方向

C R 角部

P 1 ~ P 4 第 1 ~ 第 4 の面

S W 側壁面

T R トレンチ

【図 1】

【図 3】

【図 2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【 図 1 4 】

【 図 15 】

【 図 1 6 】

【図 17】

【 図 1 8 】

【図19】

【図20】

【図21】

【図23】

【図22】

【図24】

---

フロントページの続き

| (51) Int.Cl. | F I          | テーマコード(参考) |

|--------------|--------------|------------|

|              | H 01 L 29/78 | 6 5 2 F    |

|              | H 01 L 29/78 | 6 5 8 G    |

|              | H 01 L 29/78 | 6 5 8 F    |