### (19) United States

### (12) Patent Application Publication (10) Pub. No.: US 2002/0033360 A1 Beffa

### (54) METHOD FOR SORTING INTEGRATED **CIRCUIT DEVICES**

(76) Inventor: Raymond J. Beffa, Boise, ID (US)

Correspondence Address: TRASK BRITT P.O. BOX 2550 SALT LAKE CITY, UT 84110 (US)

(21) Appl. No.: 09/944,567

(22) Filed: Aug. 30, 2001

### Related U.S. Application Data

(60) Continuation of application No. 09/653,101, filed on Aug. 31, 2000, now Pat. No. 6,307,171, which is a

Mar. 21, 2002 (43) Pub. Date:

continuation of application No. 09/133,336, filed on Aug. 13, 1998, now Pat. No. 6,147,316, which is a division of application No. 08/785,353, filed on Jan.

#### Publication Classification

17, 1997, now Pat. No. 5,927,512.

- (51)

- 324/765

#### (57) ABSTRACT

A method for sorting integrated circuit (IC) devices of the type having a substantially unique identification (ID) code, such as a fuse ID, includes automatically reading the ID code of each of the IC devices and sorting the IC devices in accordance with their automatically read ID codes.

Fig. 1 (PRIOR ART)

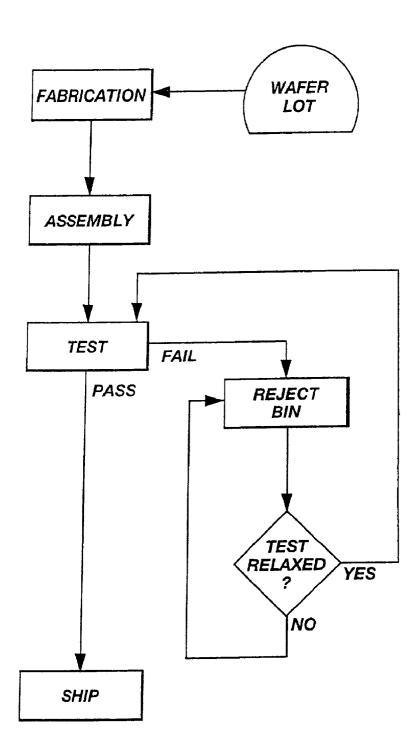

Fig. 2 (PRIOR ART)

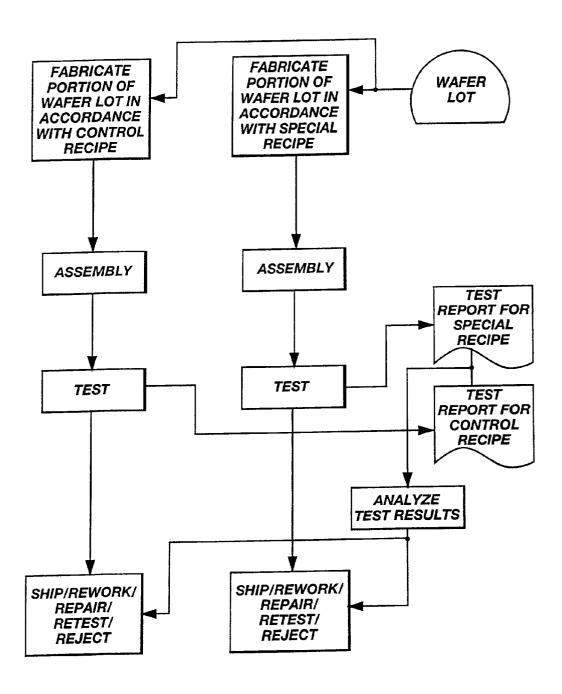

FIG. 3 (PRIOR ART)

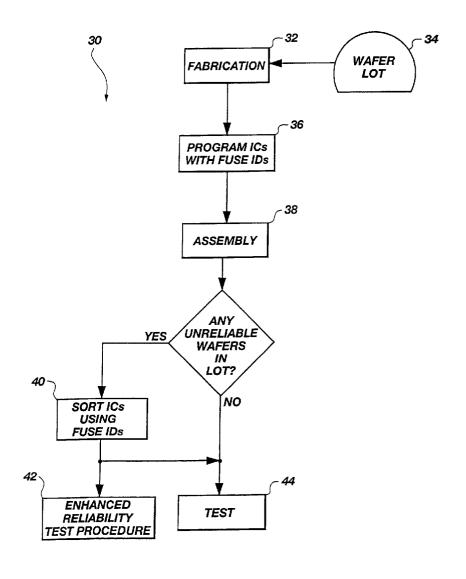

Fig. 5

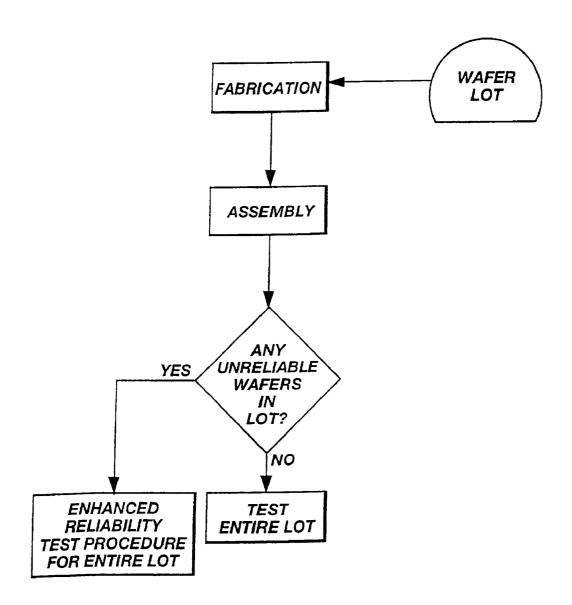

Fig. 6

Fig. 7

### METHOD FOR SORTING INTEGRATED CIRCUIT DEVICES

# CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application is a continuation of application Ser. No. 09/653,101, filed Aug. 31, 2000, pending, which is a continuation of application Ser. No. 09/133,336, filed Aug. 13, 1998, now U.S. Pat. No. 6,147,316, issued Nov. 14, 2000, which is a divisional of application Ser. No. 08/785, 353 entitled "METHOD FOR SORTING INTEGRATED CIRCUIT DEVICES," and filed Jan. 17, 1997, now U.S. Pat. No. 5,927,512, issued Jul. 27, 1999.

[0002] The present application is also related to: a application having Ser. No. 08/591,238, entitled "METHOD AND APPARATUS [sic] FOR STORAGE OF TEST RESULTS WITHIN AN INTEGRATED CIRCUIT," and filed Jan. 17, 1996 now U.S. Pat. No. 5,895,962, issued Apr. 20, 1999; a application having Ser. No. 08/664,109, entitled "A STRUCTURE AND A METHOD FOR STORING INFORMATION IN A SEMICONDUCTOR DEVICE," and filed Jun. 13, 1996 now U.S. Pat. No. 5,895,962, issued Apr. 20, 1999; a divisional application having Ser. No. 09/133, 338, entitled "METHOD FOR SORTING INTEGRATED CIRCUIT DEVICES" and filed Aug. 13, 1998, now U.S. Pat. No. 6,100,436, issued Aug. 8, 2000; a application having Ser. No. 08/822,731, entitled "METHOD FOR CONTINUOUS, NON LOT-BASED INTEGRATED CIR-CUIT MANUFACTURING," and filed Mar. 24, 1997, now U.S. Pat. No. 5,856,923, issued Jan. 5, 1999; a application having Ser. No. 08/806,442, entitled "METHOD IN AN INTEGRATED CIRCUIT (IC) MANUFACTURING PRO-CESS FOR IDENTIFYING AND RE-DIRECTING ICS MIS-PROCESSED DURING THEIR MANUFACTURE," and filed Feb. 26, 1997, now U.S. Pat. No. 5,915,231, issued Jun. 22, 1999; a application having Ser. No. 08/871,015, entitled "METHOD FOR USING DATA REGARDING MANUFACTURING PROCEDURES INTEGRATED CIRCUITS (ICS) HAVE UNDERGONE, SUCH AS REPAIRS, TO SELECT PROCEDURES THE ICS WILL UNDERGO, SUCH AS ADDITIONAL REPAIRS," and filed Jun. 6, 1997, now U.S. Pat. No. 5,907,492, issued May 25, 1999; and a application having Ser. No. 08/801,565 entitled "METHOD OF SORTING A GROUP OF INTE-GRATED CIRCUIT DEVICES FOR THOSE DEVICES REQUIRING SPECIAL TESTING," and filed Feb. 17, 1997, now U.S. Pat. No. 5,844,803, issued Dec. 1, 1998.

### BACKGROUND OF THE INVENTION

[0003] 1. Field of the Invention

[0004] The present invention relates in general to integrated circuit (IC) manufacturing and, more specifically, to methods in IC manufacturing processes for sorting IC devices using identification (ID) codes, such as fuse IDs, in the devices.

[0005] 2. State of the Art

[0006] Integrated circuits (ICs) are small electronic circuits formed on the surface of a wafer of semiconductor material, such as silicon, in an IC manufacturing process referred to as "fabrication." Once fabricated, ICs are electronically probed to evaluate a variety of their electronic

characteristics, cut from the wafer on which they were formed into discrete IC dice or "chips," and then assembled for customer use using various well-known IC packaging techniques, including lead frame packaging, Chip-On-Board (COB) packaging, and flip-chip packaging.

[0007] Before being shipped to customers, packaged ICs are generally tested to ensure they will function properly once shipped. Testing typically involves a variety of known test steps, such as pre-grade, bum-in, and final, which test ICs for defects and functionality and grade ICs for speed. As shown in FIG. 1, ICs that pass the described testing are generally shipped to customers, while ICs that fail the testing are typically rejected.

[0008] The testing standards for a particular IC product are sometimes relaxed as the product "matures" such that ICs previously rejected under strict testing standards may pass the relaxed testing standards. Consequently, reject bins containing previously rejected ICs are sometimes "culled" for ICs that are shippable under relaxed testing standards by testing the rejected ICs again using the relaxed testing standards. Unfortunately, while this "culling" process does retrieve shippable ICs from reject bins, it makes inefficient use of expensive and often limited testing resources by diverting those resources away from testing untested ICs in order to retest previously rejected ICs. Therefore, there is a need in the art for an improved method of "culling" or sorting such reject bins for shippable ICs.

[0009] Similarly, as shown in FIG. 2, all the ICs from the wafers in a wafer lot typically undergo enhanced reliability testing that is more extensive and strict than normal testing when any of the wafers in the lot are deemed to be unreliable because of fabrication or other process errors. Since a wafer lot typically consists of fifty or more wafers, many of the ICs that undergo the enhanced reliability testing do not require it because they come from wafers that are not deemed unreliable. Performing enhanced reliability testing on ICs that do not need it is inefficient because such testing is typically more time-consuming and uses more resources than normal testing. Therefore, there is a need in the art for a method of sorting ICs from a wafer lot into those ICs that require enhanced reliability testing and those that do not.

[0010] Likewise, as shown in FIG. 3, a new or special "recipe" for fabricating ICs on wafers is sometimes tested by fabricating some wafers from a wafer lot using the special recipe and other wafers from the wafer lot using a control recipe. ICs from the wafers then typically undergo separate assembly and test procedures so that the test results of ICs fabricated using the special recipe are not mixed with the test results of ICs fabricated using the control recipe, and vice versa. Test reports from the separate test procedures are then used to evaluate the special recipe and to determine whether the ICs are to be shipped to customers, reworked, repaired, retested, or rejected. Unfortunately, because the ICs undergo separate test and assembly procedures, undesirable variables, such as differences in assembly and test equipment, are introduced into the testing of the special recipe. It would be desirable, instead, to be able to assemble and test the ICs using the same assembly and test procedures, and to then sort the ICs and their test results into those ICs fabricated using the special recipe and those ICs fabricated using the control recipe. Therefore, there is a need in the art for a

method of identifying individual ICs fabricated using a special or control recipe and sorting the ICs based on their fabrication recipe.

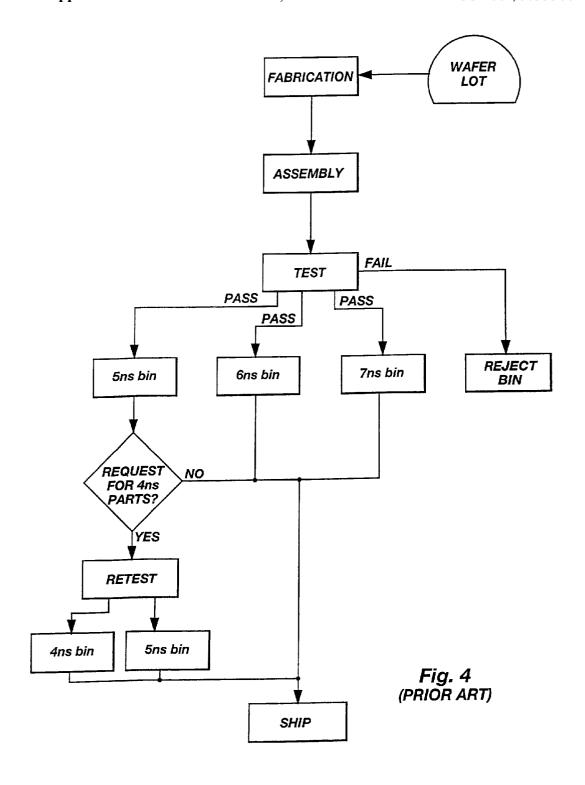

[0011] As described above, ICs are typically tested for various characteristics before being shipped to customers. For example, as shown in FIG. 4, ICs may be graded in test for speed and placed in various bins (e.g., 5 nanoseconds (ns), 6 ns, and 7 ns bins) according to their grading. If a customer subsequently requests a more stringent speed grade (e.g., 4 ns), ICs in one of the bins (e.g., a 5 ns bin) are re-tested and thereby sorted into ICs that meet the more stringent speed grade (e.g., 4 ns bin) and those that do not (e.g., 5 ns bin). While this conventional process sorts the ICs into separate speed grades, it makes inefficient use of expensive and often limited testing resources by diverting those resources away from testing untested ICs in order to retest previously tested ICs. Therefore, there is a need in the art for an improved method of "culling" or sorting bins for ICs that meet more stringent standards, such as a higher speed grading.

[0012] As described in U.S. Pat. Nos. 5,301,143, 5,294, 812, and 5,103,166, some methods have been devised to electronically identify individual ICs. Such methods take place "off" the manufacturing line and involve the use of electrically retrievable ID codes, such as so-called "fuse IDs," programmed into individual ICs to identify the ICs. The programming of a fuse ID typically involves selectively blowing an arrangement of fuses and anti-fuses in an IC so that when the fuses or anti-fuses are accessed, they output a selected ID code. Unfortunately, none of these methods addresses the problem of identifying and sorting ICs "on" a manufacturing line.

### BRIEF SUMMARY OF THE INVENTION

[0013] An inventive method for sorting integrated circuit (IC) devices of the type to have a substantially unique identification (ID) code, such as a fuse ID, includes automatically reading the ID code of each of the IC devices and sorting the IC devices according to their automatically read ID codes. The inventive method can be used in conjunction with an IC manufacturing process that includes providing semiconductor wafers, fabricating the ICs on each of the wafers, causing each of the ICs to store its ID code, separating each of the ICs from its wafer to form an IC die, assembling the IC dice into IC devices, and testing the IC devices. The method can also be used in conjunction with Single In-line Memory Module (SIMM), Dual In-line Memory Module (DIMM), and other multi-chip module (MCM) manufacturing processes.

[0014] In another embodiment, an inventive method for recovering IC devices from a group of IC devices that have previously been rejected in accordance with a test standard that has since been relaxed includes: storing test results that caused each of the IC devices in the group to be rejected in connection with an ID code, such as a fuse ID, associated with each device; automatically reading the ID code from each of the IC devices; accessing the test results stored in connection with each of the automatically read ID codes; comparing the accessed test results for each of the IC devices with the relaxed test standard; and sorting the IC devices according to whether their accessed test results pass the relaxed test standard in order to recover any of the IC devices having test results that pass the relaxed test standard.

[0015] By sorting the IC devices in accordance with their previously stored test results and their ID codes, the above-described inventive method eliminates the need to retest the IC devices after the test standard is relaxed in order to cull shippable IC devices from the rejected devices.

[0016] In still another embodiment, a method for sorting a group of IC devices in accordance with a first IC standard, such as a speed standard, that have previously been sorted in accordance with a second IC standard, such as a speed standard that is less stringent than the first IC standard, includes storing test results that caused each of the IC devices in the group to be sorted into the group in connection with ID codes, such as fuse IDs, of the devices, automatically reading the ID code from each of the IC devices, accessing the test results stored in connection with each of the automatically read ID codes, comparing the accessed test results for each of the IC devices with the first IC standard, and sorting the IC devices according to whether their test results pass the first IC standard.

[0017] In a further embodiment, an inventive back-end test method for separating IC devices in need of enhanced reliability testing from a group of IC devices undergoing back-end test procedures includes: storing a flag in connection with an ID code, such as a fuse ID, associated with each of the IC devices in the group indicating whether each IC device is in need of enhanced reliability testing; automatically reading the ID code of each of the IC devices in the group; accessing the enhanced reliability testing flag stored in connection with each of the automatically read ID codes; and sorting the IC devices in accordance with whether their enhanced reliability testing flag indicates they are in need of enhanced reliability testing.

[0018] Thus, the inventive method described above provides an advantageous method for sorting ICs from the same wafer lot into those ICs that require enhanced reliability testing and those that do not.

[0019] In a still further embodiment, an inventive method in an IC manufacturing process for testing different fabrication process recipes includes the following: providing first and second pluralities of semiconductor wafers; fabricating a first plurality of ICs on each of the first plurality of wafers in accordance with a control recipe; fabricating a second plurality of ICs on each of the second plurality of wafers in accordance with a test recipe; causing each of the ICs on each of the wafers to permanently store a substantially unique ID code, such as a fuse ID; separating each of the ICs on each of the wafers from its wafer to form one of a plurality of IC dice; assembling each of the IC dice into an IC device; automatically reading the ID code from the IC in each of the IC devices; testing each of the IC devices; and sorting each of the IC devices in accordance with the automatically read ID code from the IC in each of the IC devices indicating the IC is from one of the first and second pluralities of ICs.

## BRIEF DESCRIPTION OF THE SEVERAL VIEWS OF THE DRAWINGS

[0020] FIG. 1 is a flow diagram illustrating a conventional procedure in an integrated circuit (IC) manufacturing process for culling shippable ICs from a reject bin;

[0021] FIG. 2 is a flow diagram illustrating a conventional procedure in an IC manufacturing process for directing ICs to enhanced reliability testing;

[0022] FIG. 3 is a flow diagram illustrating a conventional procedure in an IC manufacturing process for testing a new or special fabrication process recipe;

[0023] FIG. 4 is a flow diagram illustrating a conventional procedure in an IC manufacturing process for speed-sorting ICs:

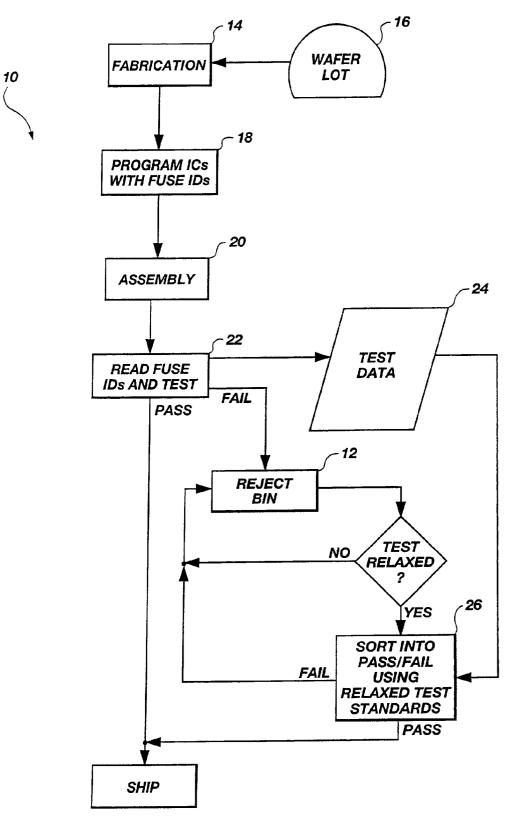

[0024] FIG. 5 is a flow diagram illustrating a procedure in an integrated circuit (IC) manufacturing process for culling shippable ICs from a reject bin in accordance with the present invention;

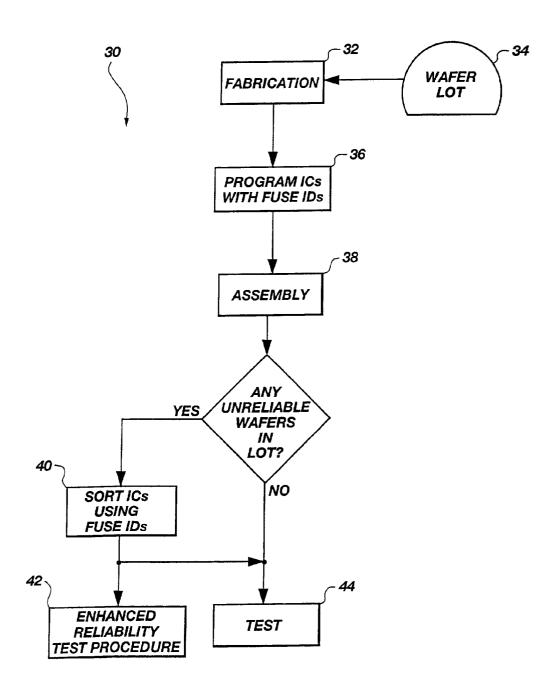

[0025] FIG. 6 is a flow diagram illustrating a procedure in an IC manufacturing process for directing ICs to enhanced reliability testing in accordance with another embodiment of the present invention;

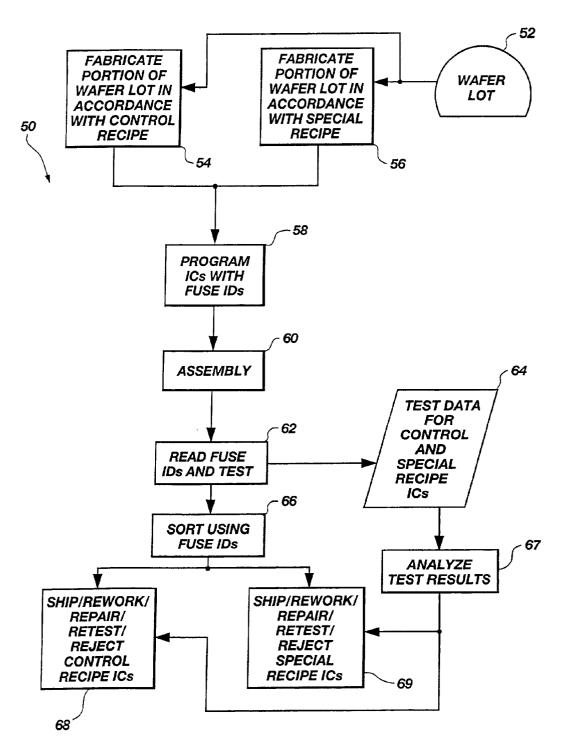

[0026] FIG. 7 is a flow diagram illustrating a procedure in an IC manufacturing process for testing a new or special fabrication process recipe in accordance with still another embodiment of the present invention; and

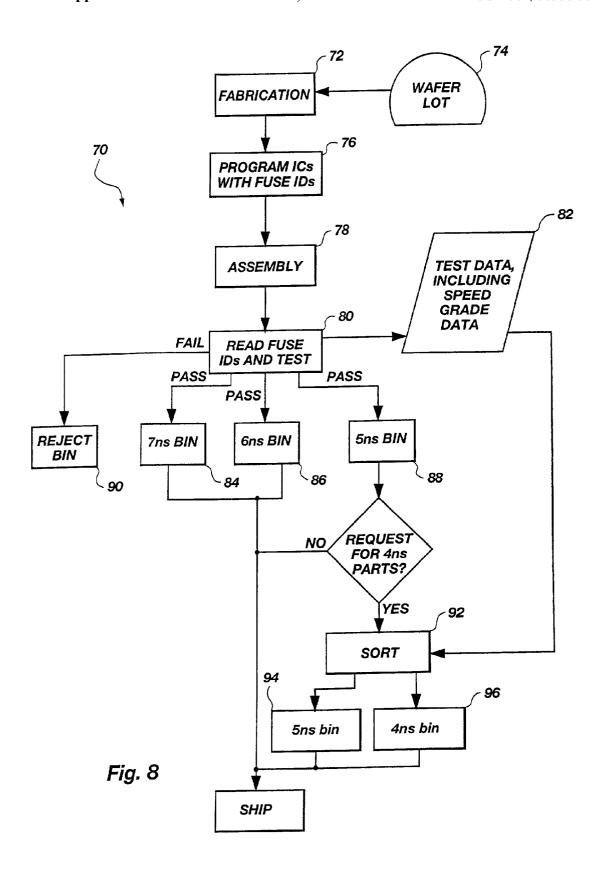

[0027] FIG. 8 is a flow diagram illustrating a procedure in an IC manufacturing process for speed-sorting ICs in accordance with a further embodiment of the present invention.

## DETAILED DESCRIPTION OF THE INVENTION

[0028] As shown in FIG. 5, an inventive method for sorting integrated circuit (IC) devices is embodied in a method 10 in an IC manufacturing process for culling shippable ICs from a reject bin 12. It will be understood by those having skill in the field of this invention that the present invention is applicable to sorting any IC devices, including Dynamic Random Access Memory (DRAM) ICs, Static Random Access Memory (SRAM) ICs, Synchronous DRAM (SDRAM) ICs, processor ICs, Single In-line Memory Modules (SIMMs), Dual In-line Memory Modules (DIMMs), and other Multi-Chip Modules (MCMs).

[0029] The method 10 includes the step 14 of fabricating ICs on wafers from a wafer lot 16. ICs fabricated on the wafers are then programmed in a program step 18 in the manner described above with a fuse identification (ID) unique to each IC. The fuse ID may identify a wafer lot ID, the week the ICs were fabricated, a wafer ID, a die location on the wafer, and a fabrication facility ID. It will be understood, of course, that the present invention includes within its scope ICs having any ID code, including those having fuse IDs. It will also be understood that the ID code for each IC need not be unique, but instead may only specify the wafer the IC comes from, for example.

[0030] Once programmed, the ICs proceed through an assembly step 20 to a test step 22 where the fuse IDs are automatically read and stored in association with test data 24 generated in the test step 22. Although the fuse IDs are typically read electronically, it will be understood that they may also be read optically if the fuse ID consists of "blown" laser fuses that are optically accessible. It will also be understood that the test data 24 may include data such as the following: data identifying the testing equipment that tested the ICs, operating personnel who operated the testing equipment, and the set-up of the equipment when the ICs were tested; and data indicating the time and date the ICs were

tested, the yield of shippable ICs through the test step 22, and test results for the ICs from the various stages of the test step 22.

[0031] ICs that pass the test step 22 are typically shipped to customers, while those that fail the test step 22 are directed to the reject bin 12. At a point in time when test standards of the test step 22 have been relaxed as described above, the ICs in the reject bin 12 are sorted in a sort step 26 by reading the fuse ID of each IC, accessing the test data 24 associated with the fuse ID, and comparing the accessed test data 24 with the relaxed test standards. Those ICs that fail even the relaxed test standards are directed back to the reject bin 12, while those ICs that pass the relaxed test standards are typically shipped to customers. The method 10 thus successfully culls shippable ICs from the reject bin 12 without retesting the ICs.

[0032] As shown in FIG. 6, the inventive sorting method is also embodied in a backend (i.e., after fabrication) test method 30 for separating ICs in need of enhanced reliability testing from a group of ICs undergoing back-end test procedures. ICs typically require enhanced reliability testing because the wafer they come from is unreliable as a result of fabrication errors and other unintended manufacturing process deviations.

[0033] The method 30 includes the step 32 of fabricating ICs on wafers from a wafer lot 34. ICs fabricated on the wafers are then programmed in a program step 36 in the manner described above with a fuse identification (ID) unique to each IC. The fuse ID may identify a wafer lot ID, the week the ICs were fabricated, a wafer ID, a die location on the wafer, and a fabrication facility ID. It will be understood, of course, that the present invention includes within its scope ICs having any ID code, including those having fuse IDs. It will also be understood that the ID code for each IC need not be unique, but instead may only specify the wafer the IC comes from, for example.

[0034] Once programmed, the ICs proceed through an assembly step 38. At this point in the IC manufacturing process, it is not uncommon for a number of wafers to have been identified as being unreliable for the reasons stated above. The fuse IDs of the ICs that come from these unreliable wafers may then be associated with a stored flag indicating the ICs come from unreliable wafers. If any wafers in the wafer lot 34 have been identified as being unreliable, the ICs proceed to a sort step 40, where their fuse IDs are automatically read so the ICs can be sorted into those flagged as coming from the unreliable wafers that require processing through an enhanced reliability testing step 42 and those not flagged as coming from the unreliable wafers that may proceed through a standard test step 44. Of course, those ICs that pass either the standard test step 44 or the enhanced reliability testing step 42 are typically shipped to customers, while those that fail these steps are directed to a reject bin (not shown).

[0035] Thus, the present invention provides a method 30 that directs those ICs needing enhanced reliability testing to the enhanced reliability testing step 42 while allowing those that do not require enhanced reliability testing to proceed through the standard testing step 44.

[0036] As shown in FIG. 7, the inventive sorting method is further embodied in a method 50 for testing different

fabrication process recipes. Such testing is typically done in accordance with a Special Work Request (SWR) from an engineer or technician.

[0037] The method 50 includes fabricating some of the wafers from a wafer lot 52 in a fabrication step 54 in accordance with a control process recipe that is typically the normal process recipe in use in the IC manufacturing process at the time. The remainder of the wafers from the wafer lot 52 are fabricated in another fabrication step 56 in accordance with a special or test process recipe. The special or test process recipe may change a variety of variables in the fabrication process, including doping, the thickness of IC layers, etc.

[0038] Once the ICs are fabricated in the fabrication steps 54 and 56, the ICs are then programmed in a program step 58 in the manner described above with a fuse identification (ID) unique to each IC. The fuse ID may identify a wafer lot ID, the week the ICs were fabricated, a wafer ID, a die location on the wafer, and a fabrication facility ID. It will be understood, of course, that the present invention includes within its scope ICs having any ID code, including those having fuse IDs. It will also be understood that the ID code for each IC need not be unique, but instead may only specify the wafer the IC comes from, for example.

[0039] Once programmed, the ICs proceed through an assembly step 60 to a test step 62 where the fuse IDs are automatically read and stored in association with test data 64 generated for both the control recipe ICs and the special or test recipe ICs in the test step 62. Although the fuse IDs are typically read electronically, it will be understood that they may also be read optically if the fuse ID consists of "blown" laser fuses that are optically accessible. It will also be understood that the test data 64 may include data such as the following: data identifying the testing equipment that tested the ICs, operating personnel who operated the testing equipment, and the set-up of the equipment when the ICs were tested; and data indicating the time and date the ICs were tested, the yield of shippable ICs through the test step 62, and test results for the ICs from the various stages of the test step 62.

[0040] Once the test data 64 is generated, the data 64 may be analyzed 67 to determine those ICs that are shippable and those that are not, and to determine any differences in test results between the control recipe ICs and the special or test recipe ICs. The ICs are sorted in a sort step 66 so they may be shipped, reworked, repaired, retested, or rejected in accordance with the analysis of the test results.

[0041] By sorting the control recipe 68 and special or test recipe 69 ICs at the end of the IC manufacturing process, the method 50 is able to assemble and test the ICs together and thus eliminate unintended variables introduced into the process of testing the special or test recipe by the conventional method of assembling and testing the ICs separately. The inventive method 50 thus provides more reliable test results.

[0042] As shown in FIG. 8, the inventive method for sorting IC devices is also embodied in a method 70 in an IC manufacturing process for sorting IC devices in accordance with an IC standard, such as speed, that is more stringent than an IC standard that the devices were previously sorted in accordance with. It will be understood that although the

method of FIG. 8 will be described with respect to speedsorting, the method is applicable to all situations in which ICs previously sorted in accordance with an IC standard, such as speed, need to be sorted in accordance with another, more stringent IC standard. Such IC standards may include, for example, access time, data setup time, data hold time, standby current, refresh current, and operating current.

[0043] The method 70 includes the step 72 of fabricating ICs on wafers from a wafer lot 74. ICs fabricated on the wafers are then programmed in a program step 76 in the manner described above with a fuse identification (ID) unique to each IC. The fuse ID may identify a wafer lot ID, the week the ICs were fabricated, a wafer ID, a die location on the wafer, and a fabrication facility ID. It will be understood, of course, that the present invention includes within its scope ICs having any ID code, including those having fuse IDs.

[0044] Once programmed, the ICs proceed through an assembly step 78 to a test step 80 where the fuse IDs are automatically read and stored in association with test data 82 generated in the test step 80. Although the fuse IDs are typically read electronically, it will be understood that they may also be read optically if the fuse ID consists of "blown" laser fuses that are optically accessible. It will also be understood that the test data 82 includes speed grading data for each IC, as described above, and may include data such as the following: data identifying the testing equipment that tested the ICs, operating personnel who operated the testing equipment, and the set-up of the equipment when the ICs were tested; and data indicating the time and date the ICs were tested, the yield of shippable ICs through the test step 80, and test results for the ICs from the various stages of the test step 80.

[0045] ICs that pass the test step 80 are typically directed to speed graded bins 84, 86, and 88, while those that fail the test step 80 are directed to a reject bin 90. The speed graded bins 84, 86, and 88 typically each contain ICs of varying speeds. For example, the bin 88 may contain a variety of 5.0 ns, 4.5 ns, 4.0 ns, 3.5 ns, etc. parts, the bin 86 may contain a variety of 6.0 ns, 5.5 ns, 5.1 ns, etc. parts, and the bin 84 may contain a variety of 7.0 ns, 6.5 ns, 6.1 ns, etc. parts.

[0046] On occasion, customers request ICs that meet a more stringent speed standard (e.g., 4 nanoseconds (ns)) than any of the ICs in the various bins 84, 86, and 88 have been graded for. While bin 88, for example, may contain ICs that will meet the more stringent speed standard, the bin 88 cannot be used to supply the customer's request because the ICs in the bin 88 have only been graded (i.e., are guaranteed to meet or exceed) a lower speed standard (e.g., 5 ns). Therefore, the present inventive method 70 sorts the ICs in a sort step 92 by reading the fuse ID of each IC, accessing the test data 82, including the speed-grading data, associated with the fuse ID, and comparing the accessed speed-grading data with the more stringent speed standard (e.g., 4 ns). Those ICs that fail the more stringent speed standard are directed to a speed graded bin 94, while those ICs that pass the more stringent speed standard are directed to another speed graded bin 96 where they can be used to fill the customer's request. The inventive method 70 thus sorts the ICs in accordance with a more stringent IC standard, such as speed, than they were previously sorted in accordance with without having to retest the ICs, and thus without reusing valuable testing resources to retest ICs.

[0047] Although the present invention has been described with reference to particular embodiments, the invention is not limited to these described embodiments. For example, while the various steps of the embodiments of the inventive sorting method have been described as occurring in a particular order, it will be understood that these steps need not necessarily occur in the described order to fall within the scope of the present invention. Thus, the invention is limited only by the appended claims, which include within their scope all equivalent methods that operate according to the principles of the invention as described.

#### What is claimed is:

- 1. A test method in an integrated circuit (IC) manufacturing process for determining IC devices in need of enhanced reliability testing from a group of IC devices undergoing test procedures, the IC devices each having a substantially unique identification (ID) code, the method comprising:

- storing an enhanced reliability testing flag in connection with the ID code of each IC device of the IC devices in the group indicating whether each IC device is in need of enhanced reliability testing;

- automatically reading the ID code of each IC device of the IC devices in the group;

- accessing the enhanced reliability testing flag stored in connection with each of the automatically read ID codes of each IC device having the ID code thereof read; and

- sorting the IC devices in accordance with whether their enhanced reliability testing flag indicates they are in need of enhanced reliability testing.

- 2. A test method in an integrated circuit (IC) manufacturing process for separating IC devices manufactured on one or more semiconductor wafers to determine the need of enhanced reliability testing from a group of IC devices undergoing test procedures, the IC devices each having a substantially unique identification (ID) code, the method comprising:

- storing an enhanced reliability testing flag in connection with the ID code of each IC device of the IC devices in the group indicating whether each IC device is needing enhanced reliability testing;

- automatically reading the ID code of each IC device of the IC devices in the group;

- accessing the enhanced reliability testing flag stored in connection with each of the automatically read ID codes of each IC device having the ID code thereof read; and

- sorting the IC devices in accordance with whether their enhanced reliability testing flag indicates the IC device comes from a semiconductor wafer which is known as an unreliable semiconductor wafer.

\* \* \* \* \*