(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4637390号

(P4637390)

(45) 発行日 平成23年2月23日(2011.2.23)

(24) 登録日 平成22年12月3日(2010.12.3)

|              |                      |

|--------------|----------------------|

| (51) Int.Cl. | F 1                  |

| H05B 33/10   | (2006.01) H05B 33/10 |

| H05B 33/12   | (2006.01) H05B 33/12 |

| H01L 51/50   | (2006.01) H05B 33/14 |

| H05B 33/22   | (2006.01) H05B 33/22 |

請求項の数 9 (全 26 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2001-86501 (P2001-86501)    |

| (22) 出願日     | 平成13年3月26日 (2001.3.26)        |

| (65) 公開番号    | 特開2001-345178 (P2001-345178A) |

| (43) 公開日     | 平成13年12月14日 (2001.12.14)      |

| 審査請求日        | 平成20年2月27日 (2008.2.27)        |

| (31) 優先権主張番号 | 特願2000-85894 (P2000-85894)    |

| (32) 優先日     | 平成12年3月27日 (2000.3.27)        |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                                                 |

|-----------|-------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地  |

| (72) 発明者  | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

| (72) 発明者  | ▲ひろ▼木 正明<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内 |

| (72) 発明者  | 福永 健司<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

審査官 濱野 隆

最終頁に続く

(54) 【発明の名称】発光装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

絶縁体の上に電極を形成し、

前記電極の上に金属膜を含むバンクを複数形成し、

前記金属膜を正または負の極性に帯電させ、前記金属膜と同一の極性に前記複数のバンクの上方に配置したシャドーマスク、及び発光材料を帯電させ、且つ前記金属膜と逆の極性に前記電極を帯電させながら、前記複数のバンクの間に発光材料を含む層を形成することを特徴とする発光装置の作製方法。

## 【請求項 2】

絶縁体の上に電極を形成し、

前記電極の上に絶縁膜及び金属膜を積層してなるバンクを複数形成し、

前記金属膜を正または負の極性に帯電させ、前記金属膜と同一の極性に前記複数のバンクの上方に配置したシャドーマスク、及び発光材料を帯電させ、且つ前記金属膜と逆の極性に前記電極を帯電させながら、前記複数のバンクの間に発光材料を含む層を形成することを特徴とする発光装置の作製方法。

## 【請求項 3】

絶縁体の上にストライプ状に配置されるように第1の線状電極を形成し、

前記第1の線状電極と交差し、且つストライプ状に配置されるように絶縁膜及び金属膜を積層してなるバンクを複数形成し、

前記金属膜を正または負の極性に帯電させ、前記金属膜と同一の極性に前記複数のバン

10

20

クの上方に配置したシャドーマスク、及び発光材料を帯電させ、且つ前記金属膜と逆の極性に前記第1の線状電極を帯電させながら、前記複数のバンクの間に発光材料を含む層を形成し、

前記第1の線状電極と交差し、且つ前記複数のバンクの間にストライプ状に配置されるように、前記発光材料を含む層の上に第2の線状電極を形成することを特徴とする発光装置の作製方法。

**【請求項4】**

絶縁体の上に電極を形成し、

前記電極の上に金属膜を含むバンクを複数形成し、

前記金属膜を正または負の極性に帯電させ、前記金属膜と同一の極性に蒸着室の隔壁、

及び発光材料を帯電させ、且つ前記金属膜と逆の極性に前記電極を帯電させながら、前記複数のバンクの間に発光材料を含む層を蒸着法により前記蒸着室で形成し、

前記発光材料を備えた蒸着ポートに設けられた孔の外に配置されたリング状電極の内側に電場を形成し、前記孔から前記発光材料が飛散する際に前記リング状電極の内側を通過させることにより、前記金属膜と同一の極性に前記発光材料を帯電させることを特徴とする発光装置の作製方法。

**【請求項5】**

絶縁体の上に電極を形成し、

前記電極の上に絶縁膜及び金属膜を積層してなるバンクを複数形成し、

前記金属膜を正または負の極性に帯電させ、前記金属膜と同一の極性に蒸着室の隔壁、

及び発光材料を帯電させ、且つ前記金属膜と逆の極性に前記電極を帯電させながら、前記複数のバンクの間に発光材料を含む層を蒸着法により前記蒸着室で形成し、

前記発光材料を備えた蒸着ポートに設けられた孔の外に配置されたリング状電極の内側に電場を形成し、前記孔から前記発光材料が飛散する際に前記リング状電極の内側を通過させることにより、前記金属膜と同一の極性に前記発光材料を帯電させることを特徴とする発光装置の作製方法。

**【請求項6】**

絶縁体の上にストライプ状に配置されるように第1の線状電極を形成し、

前記第1の線状電極と交差し、且つストライプ状に配置されるように絶縁膜及び金属膜を積層してなるバンクを複数形成し、

前記金属膜を正または負の極性に帯電させ、前記金属膜と同一の極性に蒸着室の隔壁、

及び発光材料を帯電させ、且つ前記金属膜と逆の極性に前記第1の線状電極を帯電させながら、前記複数のバンクの間に発光材料を含む層を蒸着法により前記蒸着室で形成し、

前記第1の線状電極と交差し、且つ前記複数のバンクの間にストライプ状に配置されるように、前記発光材料を含む層の上に第2の線状電極を形成し、

前記発光材料を備えた蒸着ポートに設けられた孔の外に配置されたリング状電極の内側に電場を形成し、前記孔から前記発光材料が飛散する際に前記リング状電極の内側を通過させることにより、前記金属膜と同一の極性に前記発光材料を帯電させることを特徴とする発光装置の作製方法。

**【請求項7】**

請求項2、3、5、6のいずれか一において、前記複数のバンクを形成する際に、等方性エッチングによって前記絶縁膜の線幅が前記金属膜の線幅よりも狭くなるように形成することを特徴とする発光装置の作製方法。

**【請求項8】**

請求項2、3、5、6、7のいずれか一において、前記絶縁膜は珪素化合物膜または樹脂膜からなることを特徴とする発光装置の作製方法。

**【請求項9】**

請求項1乃至3のいずれか一において、蒸着法、イオンプレーティング法、またはインクジェット法により前記発光材料を含む層を形成することを特徴とする発光装置の作製方法。

10

20

30

40

50

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、電極間に発光性材料を挟んだ素子（以下、発光素子という）を有する装置（以下、発光装置という）およびその作製方法に関する。特に発光性材料としてEL（Electro Luminescence）が得られる発光性材料（以下、EL材料という）を利用した発光素子（以下、EL素子という）を用いた発光装置（以下、EL発光装置）に関する。なお、有機ELディスプレイや有機発光ダイオード（OLED：Organic Light Emitting Diode）は本発明の発光装置に含まれる。

**【0002】**

10

また、本発明に用いることのできるEL材料は、一重項励起もしくは三重項励起または両者の励起を経由して発光（燐光および／または蛍光）するすべての発光性材料を含む。

**【0003】****【従来の技術】**

EL発光装置は、陽極と陰極との間にEL材料を挟んだ構造のEL素子を有した構造からなる。この陽極と陰極との間に電圧を加えてEL材料中に電流を流すことによりキャリアを再結合させて発光させる。即ち、EL発光装置は発光素子自体に発光能力があるため、液晶表示装置に用いるようなバックライトが不要である。さらに視野角が広く、軽量であるという利点をもつ。

**【0004】**

20

このときEL材料を成膜してEL層を形成するには、様々な成膜方法が採用されている。特に、低分子系有機EL材料の成膜には蒸着法が用いられ、高分子系有機EL材料の成膜にはスピンドルコート法もしくはインクジェット法が用いられている。

**【0005】**

いずれの成膜方法にも一長一短があるが、蒸着法の場合はEL材料の利用効率が悪いという問題がある。蒸着法の場合、抵抗加熱や電子ビーム加熱により気化したEL材料を飛散させて成膜するが、被膜形成面に成膜される分以外にもシャドーマスクや蒸着室内壁に成膜されてしまう分の損失が大きかった。現状ではEL材料の単価が高いため、このような問題は製造コストの増大を招く結果となってしまう。

**【0006】**

30

また、インクジェット法の場合、ノズル先端から吐出されたEL材料を含む液滴の軌道の制御が難しく、液滴の着弾点（EL層を成膜する部分）を正確に制御することが難しかった。この着弾点がずれてしまうと、となりの画素に液滴が混入されてしまうといった問題が起こり得た。この問題は高精細な画素部を有する発光装置を作製する上で特に顕著な問題となる。

**【0007】****【発明が解決しようとする課題】**

本発明は、EL材料を成膜するにあたって成膜位置を精密に制御するための技術を提供することを課題とする。そして、高精細な画素部を有する発光装置を得ることを課題とする。さらに、その発光装置を表示部として用いた表示品質の高い電気器具を提供することを課題とする。

40

**【0008】****【課題を解決するための手段】**

本発明では、画素を区分するバンクの一部に金属膜を用い、該金属膜に電圧をかける（負もしくは正に帯電させる）ことで電界を形成し、その電界によりEL材料の軌道を制御することを特徴としている。従って、本明細書において「電界を加える」とは、「荷電粒子の向きを制御する」と同義である。

**【0009】**

これにより蒸着法、イオンプレーティング法もしくはインクジェット法のように皮膜形成面の上方もしくは下方からEL材料が飛んできて付着するような成膜方法において、EL

50

材料の成膜位置を精密に制御することが可能となり、高精細な画素部を有する発光装置を得ることができる。

#### 【0010】

なお、本明細書中においてバンクとは、陽極もしくは陰極をストライプ状に複数本形成するにあたって、個々の配線を電気的に絶縁するための絶縁膜であり、珪素化合物膜もしくは樹脂膜などを用いることができる。

#### 【0011】

##### 【発明の実施の形態】

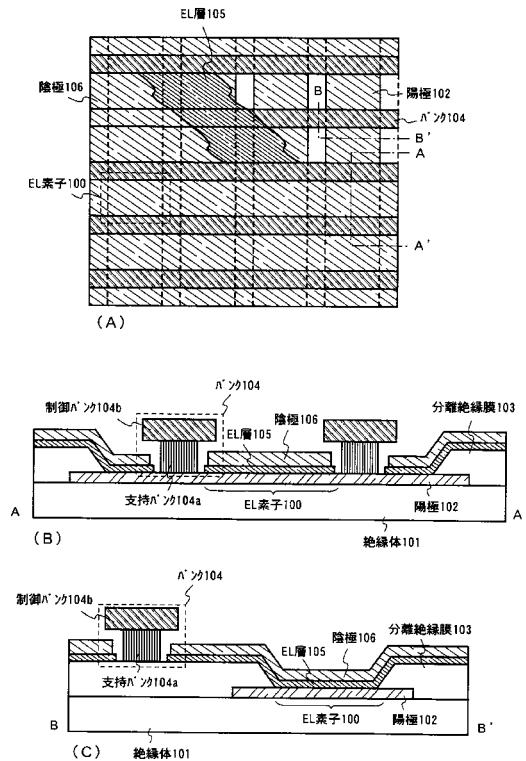

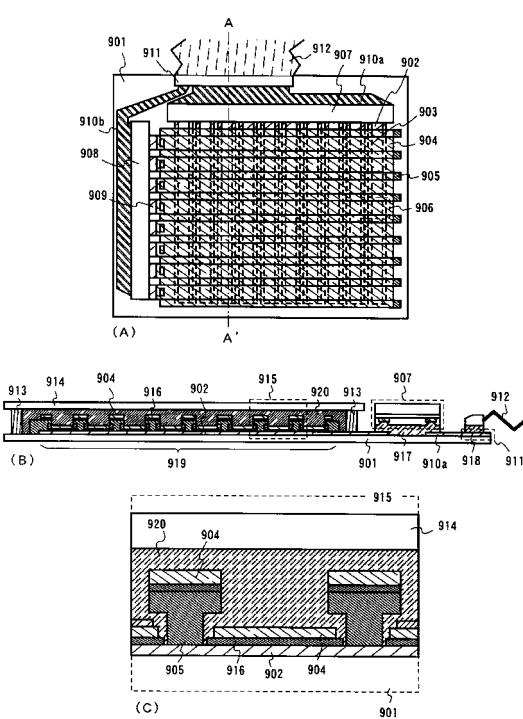

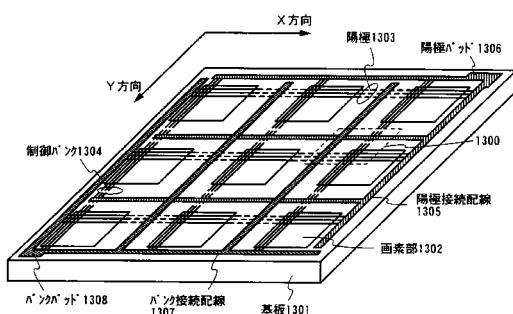

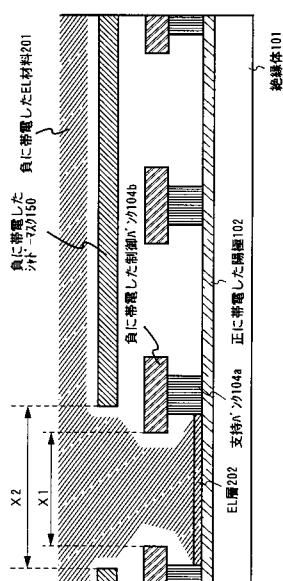

本発明の発光装置の構造について図1(A)～(C)を用いて説明する。なお、図1(A)は画素部の上面図であり、図1(B)は図1(A)をA-A'で切断した断面図、図1(C)は図1(A)をB-B'で切断した断面図である。但し、ここで示す発光装置は発光素子を封止する前の状態である。10

#### 【0012】

本発明の発光装置は、まず絶縁体101上に陽極102が設けられている。絶縁体101はガラス基板、プラスチック基板(プラスチックフィルムを含む)、金属基板もしくはセラミックス基板の上に絶縁膜を設けたものを用いても良いし、石英基板をそのまま用いても良い。

#### 【0013】

陽極102は帯状(線状といつても良い)に複数並べられ、全体として縞状(ストライプ状)に配置されている。また、陽極102としては仕事関数の大きい導電膜が用いられ、典型的には可視光に対して透明な酸化物導電膜が用いられる。酸化物導電膜としては、酸化インジウム、酸化スズ、酸化亜鉛もしくはこれらの化合物からなる導電膜を用いることができる。さらに、これらの酸化物導電膜にガリウムを添加したものであっても良い。20

#### 【0014】

また、分離絶縁膜103は、隣接する陽極間に設けられ、陽極102の端部にEL層105が形成されないように分離する役割を担う絶縁膜である。分離絶縁膜103としては珪素を含む絶縁膜、代表的には酸化珪素膜、窒化珪素膜、窒化酸化珪素膜もしくは炭化珪素膜を用いることができる。

#### 【0015】

また、陽極102と直交するようにバンク104が設けられている。バンク104はこの上に形成されるEL層105および陰極106をパターニングするためのマスク材として用いられる絶縁膜である。バンク104は絶縁膜を用いて形成した支持バンク104aとその上に設けられた金属膜からなる制御バンク104bを含む。30

#### 【0016】

このとき、支持バンク104aの線幅は制御バンク104bの線幅よりも細くなっている。このような構造は制御バンク104bをマスクとして支持バンク104aに対して等方的なエッティングを施せば得ることができる。本発明では制御バンク104bに電圧をかけて負もしくは正に帯電させ、EL材料に電界を加えることによりEL材料の軌道を制御することが可能となる。

#### 【0017】

さらに、バンク104と平行に(陽極102と直交するように)EL層105および陰極106が設けられる。これらはバンク104によって帯状に分離され、全体としてストライプ状に設けられている。もちろん、帯状に分離された個々の陰極は電気的に絶縁されている。

#### 【0018】

なお、本明細書においてEL層とは、EL素子において陽極と陰極との間に設けられた絶縁層を指し、様々な有機膜もしくは無機膜を組み合わせて形成される層である。典型的には、EL層は少なくとも発光層を含み、発光層に電荷注入層や電荷輸送層を組み合わせて用いられる。また、EL層105としては、有機EL材料、無機EL材料もしくはそれらを組み合わせたEL材料を用いる。また、有機EL材料を用いる場合、低分子材料を用い4050

ても高分子材料を用いても良く、公知の如何なる材料を用いても良い。

【0019】

また、陰極106は仕事関数の小さい導電膜が用いられ、典型的には周期表の1族もしくは2族に属する元素を含む導電膜が用いられる。代表的にはマグネシウム、リチウム、セシウム、ベリリウム、カリウムもしくはカルシウムを含む合金膜が用いられる。また、ビスマス膜を用いることもできる。

【0020】

以上の陽極102、EL層105および陰極106がEL素子100を形成する。実際には、EL素子100の上に樹脂膜を封止材として設けるか、EL素子100の上に密閉空間を作るかして、EL素子100を外気から保護する。これはEL層105や陰極106が酸化することで劣化してしまうため、酸素および水に極力触れないようにするためである。10

【0021】

以上のような構造を含む本発明の発光装置は、蒸着法、イオンプレーティング法もしくはインクジェット法のように、上方もしくは下方からEL材料が飛んできて付着することにより成膜される手法を用いる場合において、バンクの一部である金属膜を用いてEL材料に電界を加え、その電界により成膜位置の制御を行うことを特徴とするものである。

【0022】

本発明を実施することで、精密な位置制御を行いながらEL材料を成膜することが可能となり、高精細な画素部を有する発光装置を実現することができる。20

【0023】

【実施例】

【実施例1】

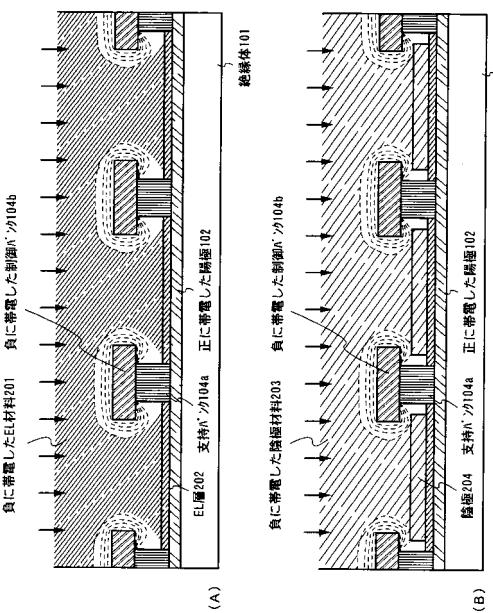

図1に示した構造の発光装置を作製する際のEL層の成膜過程について図2を用いて説明する。なお、一部図1の符号を参照して説明する。

【0024】

図2(A)において、絶縁体101の上には陽極102が形成され、その上には支持バンク104aおよび制御バンク104bを含むバンク104が形成されている。

【0025】

そして、この状態でまず陽極102を正に帯電させる。これは陽極102に正電圧を印加しても良いし、正に帯電したイオンシャワーを浴びせることで帯電させることも可能である。そして、制御バンク104bは負に帯電させる。これは制御バンク104bに負電圧を印加することで可能である。負電圧の大きさは実施者が適宜決定すれば良い。30

【0026】

この状態でEL材料201を蒸着法、イオンプレーティング法もしくはインクジェット法により積層する。このとき、本発明ではEL材料201を、制御バンク104bと同一極性に帯電させる点に特徴がある。即ち、本実施例の場合は、制御バンク104bが負に帯電しているため、EL材料201も負に帯電させる。これによりEL材料201は制御バンク104bの周囲に形成された電界に反発し、制御バンク104bを避けるような軌道を描く。40

【0027】

さらに、本実施例では陽極102が正に帯電しているため、負に帯電したEL材料201を引き寄せる方向に働く。

【0028】

以上のように、EL材料201はバンク104を避けて陽極102へ積層される。こうして画素の部分にEL層202が形成される。即ち、特にシャドーマスク等を設けることなく、EL材料を集中的に画素に成膜することができ、EL材料の利用効率を大幅に向上させることが可能となる。また、本発明は画素ピッチが数十μmといった非常に微細な画素部においても何ら問題なく実施することが可能である。

【0029】

50

また、同様に図2(B)に示すように、陰極を形成する材料(陰極材料)203を負に帯電させて蒸着法もしくはイオンプレーティング法により成膜することで上記と同様の効果を得ることができる。即ち、バンク104を避けて画素の部分に陰極204を形成することができる。

**【0030】**

**[実施例2]**

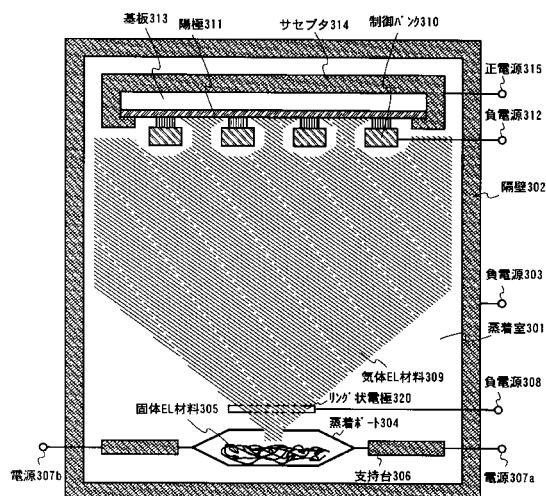

本実施例では、蒸着法によりEL材料を成膜する際に本発明を実施する場合について図3に示す。

**【0031】**

図3において、301は蒸着室であり、蒸着室の隔壁302は負の電圧が印加される負電源303に接続されている。また、蒸着室301の内部には蒸着ポート304が設置され、その中には固体EL材料305が備えられている。この蒸着ポート304は支持台306に接続された電源307a、307bを用いて加熱される。即ち、本実施例では抵抗加熱による蒸着源を用いている。10

**【0032】**

また、蒸着ポート304に設けられた孔(気体となったEL材料が蒸着ポート外に出るための孔)のすぐ外に、孔から出た気体となったEL材料(以下、気体EL材料という)を取り囲むように配置されたリング状電極320が設けられている。このリング状電極320は負電源308に接続され、リング状電極320の内側に電場を形成して、気体EL材料を負に帯電させる。即ち、蒸着ポート304から飛び出した気体EL材料は、飛散中に電場を通過させることで帯電する。このとき、蒸着室の隔壁302は負に帯電しているため、隔壁302に付着するEL材料を最小限に抑えることができる。20

**【0033】**

こうして飛散した気体EL材料309は制御バンク310が形成する電界を避けるようにして陽極311に積層される。制御バンク310には負電源312が接続され、これにより電界が形成される。なお、図示されていないが全ての制御バンクは同電位となるように電気的に接続されている。

**【0034】**

また、このとき陽極311が形成された基板313を保持するサセプタ314には正電源315が接続され、サセプタ314を正に帯電させている。このサセプタ314は陽極311と電気的に接続されており、陽極311を正に帯電させる。30

**【0035】**

以上のような構成とすることで、蒸着する気体EL材料309の利用効率を高め、必要最小限の量で所望のEL層を形成することが可能となる。従って、EL材料の消費量が大幅に削減されるため、製造コストを低減することができる。

**【0036】**

なお、本実施例では蒸着ポート304に電源308を接続して気体EL材料309を負に帯電させる方法としたが、蒸着ポート304から飛び出した後、飛散中に電場を通過させることにより帯電させることも可能である。また、蒸着源として抵抗加熱を例にとったが、電子ビーム(EB)加熱であっても構わない。40

**【0037】**

また、本実施例では気体EL材料を負に帯電させる例を示しているが、正に帯電させることも可能である。その場合、隔壁302、蒸着ポート304および制御バンク310を正に帯電させ、陽極311を負に帯電させれば良い。

**【0038】**

**[実施例3]**

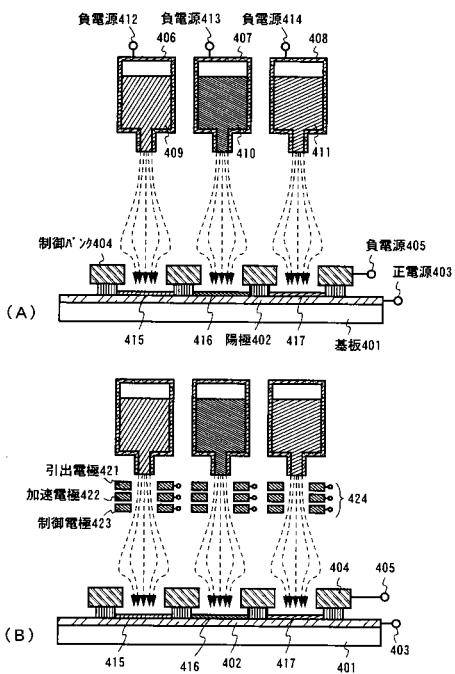

本実施例では、インクジェット法によりEL材料を塗布する際に本発明を実施する場合について図4に示す。なお、図4(A)、(B)はいずれも不活性雰囲気中(窒素ガスもしくは希ガス中)で行われる。

**【0039】**

10

20

30

40

50

図4(A)において、401はガラス基板、402は陽極であり、陽極402には負電源403が接続されている。また、本実施例では制御バンク404に負電源405を接続する。この場合、図示されないが全ての制御バンクは同電位となるように電気的に接続されている。

#### 【0040】

また、基板401の上方にはインクジェット方式でEL層を成膜するための薄膜形成装置のヘッド406～408が配置されている。ヘッド406の中には赤色発光のためのEL材料を含む溶液409が備えられ、ヘッド407の中には緑色発光のためのEL材料を含む溶液410が備えられ、ヘッド408の中には青色発光のためのEL材料を含む溶液411が備えられている。これらのEL材料を含む溶液はピエゾ素子を用いて吐出される。10

もちろん、バブルジェット方式を用いても良い。

#### 【0041】

本実施例では、ヘッド406～408の各々に負電源412～414を接続し、EL材料409～411を負に帯電させている。この状態で吐出されたEL材料を含む溶液は点線で示される軌道に沿って落下し、バンクの間に露出した陽極402上に塗布される。即ち、負に帯電したEL材料を含む溶液409～411は、やはり負に帯電した制御バンク404を避けて画素内に塗布される。

#### 【0042】

こうして画素内には赤色発光に対応するEL層415、緑色発光に対応するEL層416および青色発光に対応するEL層417が形成される。なお、ここでは三つの画素しか図示されないが、一画素ずつ成膜しても良いし、三つ以上の複数の画素に同時に成膜することも可能である。20

#### 【0043】

また、図4(B)に示したのは、ヘッド406～408の吐出口付近にEL材料を含む溶液を帯電させるための電極を設けた例である。本実施例では、引出電極421、加速電極422および制御電極423を設けている。また、各々には電源424が接続されている。

#### 【0044】

引出電極421はヘッド406～408からEL材料を含む溶液を引き出すための電界を形成する電極である。また、加速電極422は引き出されたEL材料を加速させるための電界を形成する電極であり、制御電極423は最終的にEL材料の落下する位置を制御するための電界を形成する電極である。もちろん、これら三つを常に用いる必要はなく、この組み合わせに限定する必要はない。30

#### 【0045】

図4(B)に示す構成の場合、これら三つの電極のいずれかを用いてEL材料を含む溶液を負に帯電させている。従って、ヘッド406～408に特に電源を設ける必要がなく、吐出されたEL材料を含む溶液自体を直接帯電させることができる。この場合も、図4(A)の場合と同様にEL材料を含む溶液は点線で示される軌道に沿って落下し、バンクの間に露出した陽極402上に塗布される。即ち、負に帯電したEL材料409～411は、やはり負に帯電した制御バンク404を避けて画素内に塗布される。40

#### 【0046】

以上のような構成とすることで、インクジェット法によりEL材料を塗布する際に軌道がずれてしまう可能性が大幅に減り、歩留まりを向上させることが可能となる。そのため製造コストを低減することができる。

#### 【0047】

なお、本実施例ではEL材料を含む溶液を負に帯電させる例を示しているが、正に帯電させることも可能である。その場合、制御バンク404およびEL材料を含む溶液409～411を正に帯電させ、陽極402を負に帯電させれば良い。

#### 【0048】

〔実施例4〕

10

20

30

40

50

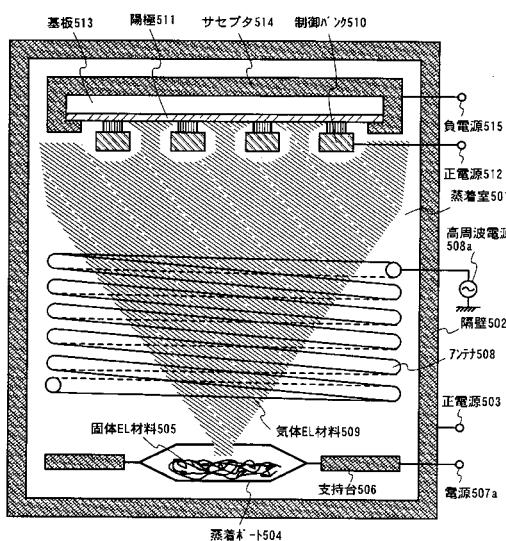

本実施例では、イオンプレーティング法により E L 層を成膜する際に本発明を実施する場合について図 5 に示す。

#### 【 0 0 4 9 】

図 5において、5 0 1は蒸着室であり、蒸着室の隔壁 5 0 2は正の電圧が印加される正電源 5 0 3に接続されている。また、蒸着室 5 0 1の内部には蒸着ポート 5 0 4が設置され、その中には固体 E L 材料 5 0 5が備えられている。この蒸着ポート 5 0 4は支持台 5 0 6に接続された電源 5 0 7a、5 0 7bを用いて加熱される。即ち、本実施例では抵抗加熱による蒸着源を用いている。

#### 【 0 0 5 0 】

また、蒸着ポート 5 0 4の上には導体をらせん状に巻いたアンテナ 5 0 8が設けられている。アンテナ 5 0 8には高周波電源 5 0 8aが接続されており、高真空中にて高周波が印加され、電波（典型的にはマイクロ波）を発生させることができる。本実施例ではこの電波を気化した気体 E L 材料 5 0 9に加えて正に帯電させる。このとき、アンテナ 5 0 8の間にプラズマを発生させても良い。このプラズマはアルゴンガスもしくはネオンガスといった希ガスを用いて形成すれば良い。このとき、蒸着室の隔壁 5 0 2は正に帯電しているため、隔壁 5 0 2に付着する E L 材料を最小限に抑えることができる。10

#### 【 0 0 5 1 】

こうして飛散した気体 E L 材料 5 0 9は、制御バンク 5 1 0が形成する電界を避けるようにして陽極 5 1 1に積層される。制御バンク 5 1 0には正電源 5 1 2が接続され、これにより電界が形成される。なお、図示されていないが全ての制御バンクは同電位となるように電気的に接続されている。また、このとき陽極 5 1 1が形成された基板 5 1 3を保持するサセプタ 5 1 4には負電源 5 1 5が接続され、サセプタ 5 1 4を負に帯電させている。このサセプタ 5 1 4は陽極 5 1 1と電気的に接続されており、陽極 5 1 1を負に帯電させる。20

#### 【 0 0 5 2 】

以上のような構成とすることで、蒸着する気体 E L 材料 5 0 9の利用効率を高め、必要最小限の量で所望の E L 層を形成することが可能となる。従って、E L 材料の消費量が大幅に削減されるため、製造コストを低減することができる。

#### 【 0 0 5 3 】

なお、本実施例では電極 5 0 8aと 5 0 8bとの間に形成された電界を気体 E L 材料 5 0 9に加えて正に帯電させる方法としたが、陽極 5 1 1と蒸着ポート 5 0 4との間にバイアス電圧をかけて正に帯電させることもできる。30

#### 【 0 0 5 4 】

また、本実施例では気体 E L 材料を正に帯電させる例を示しているが、負に帯電させることも可能である。その場合、隔壁 5 0 2、蒸着ポート 5 0 4および制御バンク 5 1 0を負に帯電させ、陽極 5 1 1を正に帯電させれば良い。

#### 【 0 0 5 5 】

##### 〔実施例 5〕

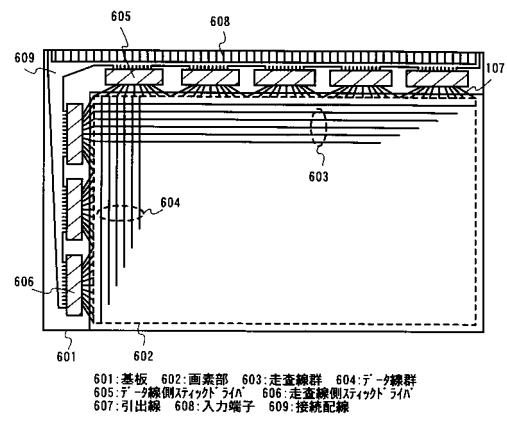

本発明の発光装置の一実施例を図 6 に示す。発光素子を形成するための基板 6 0 1上には画素部 6 0 2が形成されている。画素部 6 0 2は走査線（ここでは陽極および補助配線を含む積層配線）群 6 0 3とデータ線（ここでは陰極）群 6 0 4が互いに直交するように交差している。このとき交差した部分（以下、交差部という）は走査線とデータ線とに E L 材料が挟まれた E L 素子が形成される。このとき画素部 6 0 2は図 1 に示した構造の画素部である。40

#### 【 0 0 5 6 】

また、画素部 6 0 2の周辺（外側）の領域には、画素部 6 0 2へ各信号を伝送する駆動回路が形成された I C が COG 方式により実装されている。本実施例ではこの I C が、ガラス基板、石英基板もしくはプラスチック基板上に TFT で駆動回路を形成したものである点に特徴がある。本明細書ではこのような特徴を有する I C をスティックドライバと呼ぶ。もちろん、シリコン基板上に公知の I C 技術により駆動回路を形成した I C チップを用50

いることも可能である。

**【0057】**

図6において、605はデータ線側のスティックドライバであり、606は走査線側のスティックドライバである。なお、ここでは複数個に分割して実装した例を示しているが、各1個づつとしても良い。また、カラー表示に対応した画素部を形成するためには、XGAクラスでデータ線の本数が3072本であり走査線側が768本必要となる。このような数で形成されたデータ線及び走査線は画素部602の端部で数ブロック毎に区分して引出線607を形成し、スティックドライバ605、606の出力端子のピッチに合わせて集められている。

**【0058】**

一方、基板601の端部には入力端子608が形成され、この部分で外部回路と接続するFPC（フレキシブルプリント配線板：Flexible Printed Circuit）を貼り合わせる。そして、外部入力端子608とスティックドライバとの間は基板601上に形成した接続配線609によって結ばれ、最終的にはスティックドライバの入力端子のピッチに合わせて集められる。

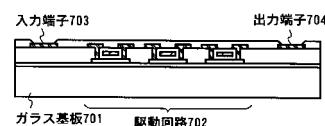

**【0059】**

駆動回路が形成されたスティックドライバは図7に示すように、駆動回路を形成するための基板（ここではガラス基板）701上に形成され、TFTで形成された駆動回路702と、入力端子703および出力端子704が設けられている。基板701の材料としては、図6の基板601と熱膨張係数の近い材料を用いることが望ましく、ガラス、石英ガラスもしくはプラスチックを用いることが望ましい。熱膨張係数の近い材料を用いると、熱を加えた際に応力の発生を最小限に抑制することができ、応力に起因する接続不良や動作不良を回避できる。

**【0060】**

また、駆動回路702のTFTは、活性層（能動層）、特にチャネル形成領域が多結晶半導体膜もしくは単結晶半導体膜で形成されている。多結晶半導体膜および単結晶半導体膜はいずれも公知の技術で形成されたもので良い。また、TFT構造にも特に限定はない。

**【0061】**

図7に示すようなスティックドライバを基板601上に実装する方法は異方導電性材料もしくはメタルバンプを用いた接続方法またはワイヤボンディング方式を採用することができる。特に、ITO（酸化インジウムと酸化スズとの化合物からなる酸化物）からなる配線上にスティックドライバを形成する場合は異方導電性材料を用いた接続方法が好ましい。

**【0062】**

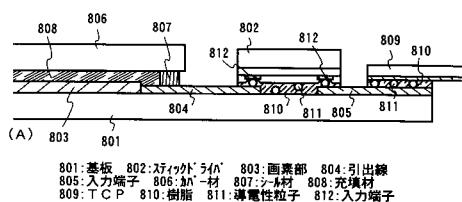

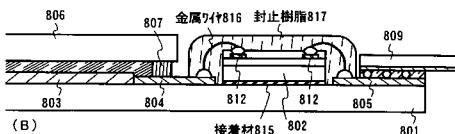

図8にその一例を示す。図8(A)は基板801にスティックドライバ802が異方導電性材料を用いて実装された例を示している。基板801上には画素部803、引出線804、入力端子805、接続配線（図示せず）が設けられている。なお、画素部803はカバー材806およびシール材807により密閉空間808に封入され外気から保護されている。

**【0063】**

また、入力端子805の一方の端にはTCP809が異方導電性材料で接着されている。異方導電性材料は樹脂810と表面が金属メッキされた直径数十～数百μmの導電性粒子811からなり、導電性粒子811によりスティックドライバ側の入力端子812もしくはTCP809と引出線804もしくは入力端子805とが電気的に接続されている。

**【0064】**

また、図8(B)で示すように基板801にスティックドライバを接着材815で固定して、金属ワイヤ816によりスティックドライバ802の入力端子812と引出線804もしくは入力端子805とを電気的に接続しても良い。この場合、接続したスティックドライバ802は樹脂膜817で封入する。

**【0065】**

10

20

30

40

50

なお、スティックドライバの実装方法は図8に示した方法に限定されるものではなく、公知の実装方法を用いることが可能である。

【0066】

〔実施例6〕

本発明の発光装置の一実施例を図9に示す。図9(A)は本発明の発光装置の上面図であり、図9(B)は図8(A)をA-A'で切断した断面図に相当する。まず、図9(A)の上面図について説明する。

【0067】

図9(A)において、901は基板であり、ここではプラスチック材を用いる。プラスチック材としては、ポリイミド、ポリアミド、アクリル樹脂、エポキシ樹脂、PES(ポリエチレンサルファイル)、PC(ポリカーボネート)、PET(ポリエチレンテレフタレート)もしくはPEN(ポリエチレンナフタレート)を板状もしくはフィルム状にして用いることができる。10

【0068】

902は酸化物導電膜からなる走査線(陽極)であり、本実施例では酸化亜鉛に酸化ガリウムを添加した酸化物導電膜を用いる。このとき走査線902の上にニッケル配線903が設けられている(図9(A)参照)。

【0069】

また、904は金属膜からなるデータ線(陰極)であり、本実施例ではビスマス膜を用いる。また、905はアクリル樹脂からなるバンクであり、データ線904を分断するための隔壁として機能する。走査線902とデータ線904は両方ともストライプ状に複数本形成されており、互いに直交するように設けられる。なお、図9(A)では図示されないが、走査線902とデータ線904の間にはEL層が挟まれてあり、906で示される交差部が画素となる。20

【0070】

907は走査線側スティックドライバであり、TFTで形成された駆動回路を含んでいる。ここでは駆動回路をプラスチック基板上に形成しているが、ガラス基板上に形成しても構わない。なお、スティックドライバ907の構造は図7で説明した通りである。また、一つのスティックドライバを設けた例を示しているが、複数個に分割して設けても構わない。30

【0071】

908はデータ線側スティックドライバであり、TFTで形成された駆動回路を含んでいる。ここでも駆動回路をプラスチック基板上に形成している。また、スティックドライバ908も図7で説明した構造である。また、一つのスティックドライバを設けた例を示しているが、複数個に分割して設けても構わない。

【0072】

なお、データ線904は配線端で接続配線909と電気的に接続され、接続配線909がスティックドライバ908と接続される。これはスティックドライバ908をバンク905上に設けることが困難だからである。

【0073】

以上のような構成で設けられた走査線側スティックドライバ907は接続配線910aおよび入力端子911を介してFPC912に接続される。また、データ線側スティックドライバ908は接続配線910bおよび入力端子911を介してFPC912に接続される。40

【0074】

また、913はシール材、914はシール材913によりプラスチック材901に貼り合わせたカバー材である。シール材913としては光硬化樹脂を用いれば良く、脱ガスが少なく、吸湿性の低い材料が好ましい。また、カバー材としては基板901と同一の材料が好ましく、ガラス(石英ガラスを含む)もしくはプラスチックを用いることができる。ここではプラスチック材を用いる。50

**【 0 0 7 5 】**

次に、図9（B）の断面図について説明する。なお、図9（A）と同一の部分は同一の符号を用いて説明する。

**【 0 0 7 6 】**

図9（B）において、915で示された領域は画素の構造を示しており、この拡大図を図9（C）に示す。916はEL層であり、正孔注入層、正孔輸送層、発光層、電子輸送層もしくは電子注入層を適宜組み合わせて形成する。勿論、発光層を単層で用いても良い。EL層916を形成する構造および材料は公知のものを用いれば良い。

**【 0 0 7 7 】**

なお、図9（C）に示すようにバンク905は下層の幅が上層の幅よりも狭い形状となつており、データ線904を物理的に分断する。

10

**【 0 0 7 8 】**

また、図9（B）に示すように、走査線側スティックドライバ907は異方導電性材料917を用いて走査線902および接続配線910aに電気的に接続されている。また同様にFPC912も異方導電性材料918を用いて接続配線910aに電気的に接続されている。

**【 0 0 7 9 】**

また、シール材913で囲まれた画素部919は、樹脂からなる封止材920により外気から遮断され、EL層の劣化を防ぐ構造となっている。

20

**【 0 0 8 0 】**

以上のような構成を含む本発明の発光装置は、画素部919が走査線902、補助配線903、データ線904、バンク905およびEL層916で形成されるため、非常に簡単なプロセスで作製することができる。さらに、補助配線903を設けたことで走査線902の配線抵抗を低減することができ、表示品質の高い発光装置とすることができます。

**【 0 0 8 1 】**

また、本実施例に示した発光装置の表示面（画像を観測する面）に偏光板を設けても良い。この偏光板は、外部から入射した光の反射を抑え、観測者が表示面に映り込むことを防ぐ効果を有する。一般的には円偏光板が用いられている。但し、EL層から発した光が偏光板により反射されて内部に戻されることを防ぐため、屈折率を調節して内部反射の少ない構造とすることが望ましい。

30

**【 0 0 8 2 】**

また、駆動回路となるスティックドライバ907、908を別工程で作製して実装する。その結果、特に煩雑なプロセスを必要とせずに発光装置を作製することができるため歩留まりが高く、製造コストを下げることができる。

**【 0 0 8 3 】****〔 実施例 7 〕**

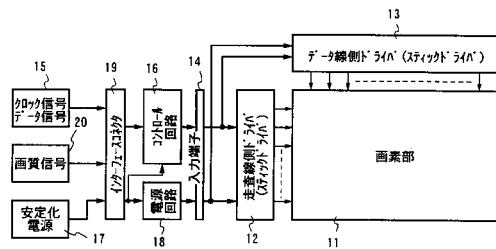

本実施例では、本発明の発光装置における回路構成の一実施例を図10に示す。画素部11は複数の走査線とデータ線で形成され、複数のEL素子が形成される。その周辺の領域には走査線側ドライバ12及びデータ線側ドライバ13が設けられ、これらのドライバ（駆動回路）にスティックドライバが用いられる。このスティックドライバの構造は図7、図8を用いて説明した通りである。

40

**【 0 0 8 4 】**

これらのスティックドライバは入力端子14と接続されている。このように、画素部11が形成された基板上には、走査線側ドライバ12、データ線側ドライバ13および入力端子14が形成されている。

**【 0 0 8 5 】**

また、コントロール回路16、安定化電源17、オペアンプを含む電源回路18のうちコントロール回路16と電源回路18はプリント配線板に実装し、FPCを用いて入力端子14に接続される。また、FPCの一方の端にはインターフェースコネクタ19が設けられ、これを介してクロック信号及びデータ信号15、画質信号20が上記プリント配線板

50

に入力される。また、安定化電源 17 からの電源信号もインターフェースコネクタ 19 を介して上記プリント配線板に入力される。

**【 0 0 8 6 】**

なお、外部から入力されるクロック信号及びデータ信号 15 は、スティックドライバの入力仕様に変換するためのコントロール回路 16 に入力され、それぞれのタイミング仕様に変換される。

**【 0 0 8 7 】**

**[ 実施例 8 ]**

実施例 1 ~ 7 では、絶縁体の上に陽極、EL 層、陰極の順に積層していく場合について説明したが、陰極、EL 層、陽極および補助配線の順に積層していくことも可能である。

10

**【 0 0 8 8 】**

前者は絶縁体を通過した光を観測することになるのに対して、後者は絶縁体から離れる方向に光が放射される。

**【 0 0 8 9 】**

なお、本実施例の構成は実施例 1 ~ 7 のいずれの構成とも自由に組み合わせて実施することが可能である。

**【 0 0 9 0 】**

**[ 実施例 9 ]**

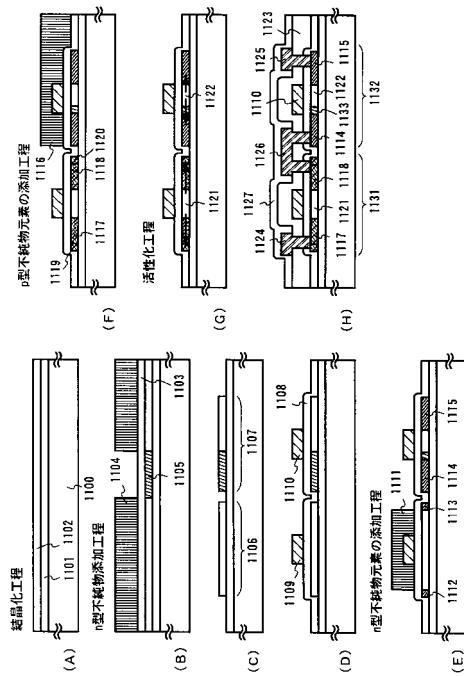

実施例 5 ~ 7 で用いるスティックドライバの作製方法について図 11 を用いて説明する。ここでは駆動回路を形成する基本単位として CMOS 回路を作製する場合の例について説明する。

20

**【 0 0 9 1 】**

まず、図 11 (A) に示すように、ガラス基板 1100 上に下地膜 1101 を 300 nm の厚さに形成する。本実施例では下地膜 1102 として窒化酸化珪素膜を積層して用いる。この時、ガラス基板 1100 に接する方の窒素濃度を 10 ~ 25 wt % としておくと良い。

**【 0 0 9 2 】**

次に下地膜 1101 の上に 50 nm の厚さの非晶質珪素膜 ( 図示せず ) ) を公知の成膜法で形成する。なお、非晶質珪素膜に限定する必要はなく、非晶質構造を含む半導体膜 ( 微結晶半導体膜を含む ) であれば良い。さらに非晶質シリコンゲルマニウム膜などの非晶質構造を含む化合物半導体膜でも良い。また、膜厚は 20 ~ 100 nm の厚さであれば良い。

30

**【 0 0 9 3 】**

そして、公知の技術により非晶質珪素膜を結晶化し、結晶質珪素膜 ( 多結晶シリコン膜若しくはポリシリコン膜ともいう ) 1102 を形成する。公知の結晶化方法としては、電熱炉を使用した熱結晶化方法、レーザー光を用いたレーザーアニール結晶化法、赤外光を用いたランプアニール結晶化法がある。

**【 0 0 9 4 】**

本実施例では特開平 7 - 130652 号公報に記載された技術を用い、非晶質珪素膜にニッケルを添加し、ファーネスアニールを行って結晶化させる。ニッケルは結晶化を促進させる触媒として用いられる。

40

**【 0 0 9 5 】**

なお、本実施例では結晶質珪素膜を TFT の活性層として用いるが、非晶質珪素膜を用いること也可能である。また、オフ電流を低減する必要のあるスイッチング用 TFT の活性層を非晶質珪素膜で形成し、電流制御用 TFT の活性層を結晶質珪素膜で形成すること也可能である。非晶質珪素膜はキャリア移動度が低いため電流を流しにくくオフ電流が流れにくい。即ち、電流を流しにくい非晶質珪素膜と電流を流しやすい結晶質珪素膜の両者の利点を生かすことができる。

**【 0 0 9 6 】**

次に、図 11 (B) に示すように、結晶質珪素膜 1102 上に酸化珪素膜でなる保護膜 1

50

103を130nmの厚さに形成する。この厚さは100~200nm(好ましくは130~170nm)の範囲で選べば良い。また、珪素を含む絶縁膜であれば他の膜でも良い。この保護膜1103は不純物を添加する際に結晶質珪素膜が直接プラズマに曝されないようにするために、微妙な濃度制御を可能にするために設ける。

#### 【0097】

そして、その上にレジストマスク1104を形成し、保護膜1103を介してn型を付与する不純物元素(以下、n型不純物元素という)を添加する。なお、n型不純物元素としては、代表的には周期表の15族に属する元素、典型的にはリン又は砒素を用いることができる。なお、本実施例ではフォスフィン( $\text{PH}_3$ )を質量分離しないでプラズマ励起したプラズマドーピング法を用い、リンを $1 \times 10^{18}\text{atoms/cm}^3$ の濃度で添加する。勿論、質量分離を行うイオンインプランテーション法を用いても良い。

10

#### 【0098】

この工程により形成されるn型不純物領域1105には、n型不純物元素が $2 \times 10^{16} \sim 5 \times 10^{19}\text{atoms/cm}^3$ (代表的には $5 \times 10^{17} \sim 5 \times 10^{18}\text{atoms/cm}^3$ )の濃度で含まれるようにドーズ量を調節する。

#### 【0099】

次に、図11(C)に示すように、結晶質珪素膜の不要な部分を除去して、後にpチャネル型TFTの活性層となる半導体膜1106および後にnチャネル型TFTの活性層となる半導体膜1107を形成する。

#### 【0100】

20

次に、図11(D)に示すように、半導体膜1106、1107を覆ってゲート絶縁膜1108を形成する。ゲート絶縁膜1108としては、10~200nm、好ましくは50~150nmの厚さの珪素を含む絶縁膜を用いれば良い。これは単層構造でも積層構造でも良い。

#### 【0101】

次に、200~400nm厚の導電膜を形成し、パターニングしてゲート電極1109、1110を形成する。このゲート電極1109、1110の端部をテーパー状にすることもできる。また、ゲート電極は単層の導電膜で形成しても良いが、必要に応じて二層、三層といった積層膜とすることが好ましい。ゲート電極の材料としては公知のあらゆる導電膜を用いることができる。

30

#### 【0102】

代表的には、タンタル(Ta)、チタン(Ti)、モリブデン(Mo)、タングステン(W)、クロム(Cr)、シリコン(Si)から選ばれた元素でなる膜、または前記元素の窒化物膜(代表的には窒化タンタル膜、窒化タングステン膜、窒化チタン膜)、または前記元素を組み合わせた合金膜(代表的にはMo-W合金、Mo-Ta合金)、または前記元素のシリサイド膜(代表的にはタングステンシリサイド膜、チタンシリサイド膜)を用いることができる。勿論、単層で用いても積層して用いても良い。

#### 【0103】

本実施例では、50nm厚の窒化タンゲステン(WN)膜と、350nm厚のタンゲステン(W)膜とでなる積層膜を用いる。これはスパッタ法で形成すれば良い。また、スパッタガスとしてXe、Ne等の不活性ガスを添加すると応力による膜はがれを防止することができる。

40

#### 【0104】

またこの時、ゲート電極1110はn型不純物領域1105の一部とゲート絶縁膜1108を挟んで重なるように形成する。この重なった部分が後にゲート電極と重なったLDD領域となる。

#### 【0105】

次に、図11(E)に示すように、レジスト1111を形成し、n型不純物元素(本実施例ではリン)を添加して高濃度にリンを含む不純物領域1112~1115を形成する。ここでもフォスフィン( $\text{PH}_3$ )を用いたイオンドープ法で行い、この領域のリンの濃度

50

は  $1 \times 10^{20} \sim 1 \times 10^{21}$  atoms/cm<sup>3</sup> (代表的には  $2 \times 10^{20} \sim 5 \times 10^{21}$  atoms/cm<sup>3</sup>) となるように調節する。この工程によって n チャネル型 TFT のソース領域若しくはドレイン領域が形成される。

#### 【0106】

この工程では、p チャネル型 TFT の活性層となる半導体膜 1106 にも n 型不純物領域 1112、1113 を形成する点に特徴がある。この領域は非晶質珪素膜の結晶化に用いたニッケルをゲッタリングするために後工程で必要となる。

#### 【0107】

次に、図 11 (F) に示すように、レジストマスク 911 を除去し、新たにレジスト 1116 を形成する。そして、p 型不純物元素（本実施例ではボロン）を添加し、高濃度にボロンを含む不純物領域 1117、1118 を形成する。ここではジボラン（B<sub>2</sub>H<sub>6</sub>）を用いたイオンドープ法により  $3 \times 10^{20} \sim 3 \times 10^{21}$  atoms/cm<sup>3</sup> (代表的には  $5 \times 10^{20} \sim 1 \times 10^{21}$  atoms/cm<sup>3</sup>) の濃度となるようにボロンを添加する。

10

#### 【0108】

なお、1119、1120 で示される領域には既に  $1 \times 10^{20} \sim 1 \times 10^{21}$  atoms/cm<sup>3</sup> の濃度でリンが添加されているが、ここで添加されるボロンはその少なくとも 3 倍以上の濃度で添加される。そのため、予め形成されていた n 型の不純物領域は完全に P 型に反転し、P 型の不純物領域として機能する。

#### 【0109】

次に、レジストマスク 1116 を除去した後、図 11 (G) に示すように、それぞれの濃度で添加された n 型または p 型不純物元素を活性化する。活性化手段としては、ファーネスアニール法、レーザーアニール法、またはランプアニール法で行うことができる。本実施例では電熱炉において窒素雰囲気中、550、4 時間の熱処理を行う。

20

#### 【0110】

このとき、結晶化の際に用いたニッケルがチャネル形成領域 1121、1122 から n 型不純物領域 1114、1115 および p 型不純物領域 1119、1120 の方へ移動してゲッタリング（捕獲）される。即ち、n 型不純物領域 1114、1115 および p 型不純物領域 1119、1120 に含まれたリンによりニッケルがゲッタリングされる。この工程によりチャネル形成領域 1121、1122 のニッケル濃度を  $1 \times 10^{17}$  atoms/cm<sup>3</sup> 以下（好ましくは  $1 \times 10^{16}$  atoms/cm<sup>3</sup> 以下）とすることができます。また逆に、n 型不純物領域 1114、1115 および p 型不純物領域 1119、1120 にはニッケルが偏析して  $5 \times 10^{18}$  atoms/cm<sup>3</sup> 以上（代表的には  $1 \times 10^{19} \sim 5 \times 10^{20}$  atoms/cm<sup>3</sup> ) 濃度で存在するようになる。

30

#### 【0111】

次に、図 11 (A) に示すように、層間絶縁膜 1123 を形成する。層間絶縁膜 1123 としては、珪素を含む絶縁膜を単層で用いるか、その上で組み合わせた積層膜を用いれば良い。また、膜厚は 400 nm ~ 1.5 μm とすれば良い。本実施例では、200 nm 厚の窒化酸化珪素膜の上に 800 nm 厚の酸化珪素膜を積層した構造とする。

#### 【0112】

さらに、3 ~ 100 % の水素を含む雰囲気中で、300 ~ 450 で 1 ~ 12 時間の熱処理を行い水素化処理を行う。この工程は熱的に励起された水素により半導体膜の不対結合手を水素終端する工程である。水素化の他の手段として、プラズマ水素化（プラズマにより励起された水素を用いる）を行っても良い。

40

#### 【0113】

なお、水素化処理は層間絶縁膜 623 を形成する間に入れても良い。即ち、200 nm 厚の窒化酸化珪素膜を形成した後で上記のように水素化処理を行い、その後で残り 800 nm 厚の酸化珪素膜を形成しても構わない。

#### 【0114】

次に、第 1 層間絶縁膜 1123 に対してコンタクトホールを形成し、ソース配線 1124、1125 と、ドレイン配線 1126 を形成する。このとき同時に図 7 に示す入力端子 7

50

03および出力端子704を形成すれば良い。なお、本実施例ではこの電極を、Ti(チタン)膜を100nm、Tiを含むアルミニウム膜を300nmおよびTi膜150nmをスパッタ法で連続形成した3層構造の積層膜とする。勿論、他の導電膜でも良い。

#### 【0115】

次に、50~500nm(代表的には200~300nm)の厚さでパッシベーション膜1127を形成する。本実施例ではパッシベーション膜1127として300nm厚の窒化酸化珪素膜を用いる。これは窒化珪素膜で代用しても良い。

#### 【0116】

なお、窒化酸化珪素膜の形成に先立ってH<sub>2</sub>、NH<sub>3</sub>等水素を含むガスを用いてプラズマ処理を行うことは有効である。10 この前処理により励起された水素が層間絶縁膜1123に供給され、熱処理を行うことで、パッシベーション膜1127の膜質が改善される。それと同時に、層間絶縁膜1123に添加された水素が下層側に拡散するため、効果的に活性層を水素化することができる。

#### 【0117】

こうして図11(H)に示す構造のpチャネル型TFT1131およびnチャネル型TFT1132を相補的に組み合わせたCMOS回路が完成する。本実施例の場合、pチャネル型TFT1131の活性層はソース領域1117、ドレイン領域1118およびチャネル形成領域1121で形成される。

#### 【0118】

また、nチャネル型1132の活性層は、ソース領域1115、ドレイン領域1114、20 LDD領域1133およびチャネル形成領域1122を含み、LDD領域1133はゲート絶縁膜1108を挟んでゲート電極1110と重なっている。このLDD領域1133のうち、ゲート電極1110と重なっている領域のチャネル長方向の長さは0.5~3.0μm、好ましくは1.0~2.0μmとする。

#### 【0119】

このような構造はホットキャリア効果による劣化を抑制する上で非常に有効である。但し、ドレイン領域1114側のみにLDD領域1133を形成しているのは、動作速度を落とさないための配慮である。ホットキャリア効果はドレイン領域とチャネル形成領域の接合部付近で問題となるため、ドレイン領域側に設けられていれば十分に効果が得られる。30 勿論、ソース領域側に同様に設けても良い。

#### 【0120】

本実施例はCMOS回路の作製方法を説明しているが、実際にはCMOS回路、NMOS回路もしくはPMOS回路を組み合わせて駆動回路を形成する。その際、PMOS回路の作製にはpチャネル型TFT1131の作製方法を、NMOS回路の作製にはnチャネル型TFT1132の作製方法を参照すれば良い。

#### 【0121】

なお、本実施例の構成は実施例5~8のいずれの構成とも自由に組み合わせて実施することが可能である。

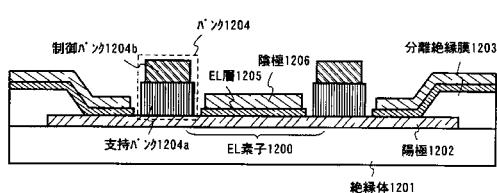

#### 【0122】

(実施例10)40

本実施例では、図1(B)、(C)とは異なる形状のバンクを用いた場合について図12を用いて説明する。図12(A)において、絶縁体1201上には陽極1202が設けられ、その上に分離絶縁膜1203が設けられる。さらに、支持バンク1204aおよび制御バンク1204bからなるバンク1204が設けられる。

#### 【0123】

本実施例では、支持バンク1204aを形成した後、その上に改めて制御バンク1204bを設けている。従って、制御バンク1204bの線幅は支持バンク1204aの線幅よりも狭くなっている。

#### 【0124】

また、陽極1202上において、バンク1204の間(画素に相当する部分)にはEL層50

1205および陰極1206が設けられる。こうして、陽極1202、EL層1205および陰極1206からなるEL素子1200が形成されている。

#### 【0125】

なお、本実施例の構造を含むバンクは、実施例1～4のいずれの構成においてもバンクとして用いることが可能であり、実施例5～9のいずれの構成とも自由に組み合わせて実施することが可能である。

#### 【0126】

##### 〔実施例11〕

本実施例では、多面取りにより1枚の基板から複数の発光装置を作製する場合に本発明を実施する例について説明する。説明には図13を用いる。

10

#### 【0127】

ガラス基板1301上には複数の画素部1302が形成されている。本実施例では1枚のガラス基板上に九つの画素部、即ち、九つの発光装置が形成されることになる。また、各画素は図1に示すような構造からなり、図中のX方向に陽極1303が形成され、Y方向に制御バンク1304が形成されている。

#### 【0128】

本実施例では、陽極1303が全て同電位となるように個々の陽極を接続するための配線（以下、陽極接続配線という）1305が形成され、陽極パッド1306に電圧を加えればその電圧が全て陽極に伝わるようになっている。また、制御バンク1304が全て同電位となるように個々の制御バンクを接続するための配線（以下、バンク接続配線という）1307が形成され、バンクパッド1308に電圧を加えればその電圧が全て制御バンクに伝わるようになっている。

20

#### 【0129】

本実施例では、これらの陽極接続配線1305およびバンク接続配線1307を静電対策に活用する点に特徴がある。即ち、全てが同電位になつていれば突発的に大きな電圧が配線間に加わることもないため、絶縁破壊等を効果的に抑制することができる。

#### 【0130】

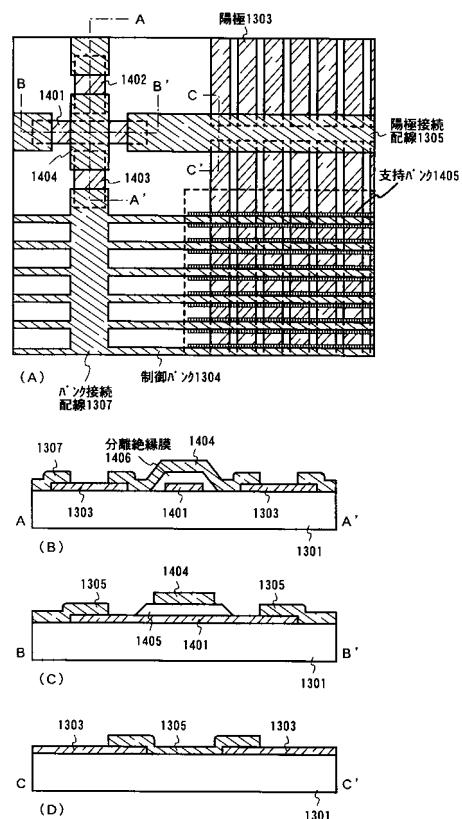

ここで、点線で囲まれた領域1300の拡大図を図14(A)に示す。なお、本実施例では実施例10に示したバンク構造を用いている。

30

#### 【0131】

図14(A)に示すように、陽極接続配線1305とバンク接続配線1307とは同時に形成されている。即ち、両者は同一の金属膜で同一の層に形成されている。このとき、陽極接続配線1305は陽極1303と同時に形成されたバッファ配線1401で連結された部分を有する。また、バンク接続配線1307は陽極1303と同時に形成されたバッファ配線1402、1403および制御バンク1307と同時に形成されたバッファ配線1404で連結された部分を有する。

#### 【0132】

ここで図14(A)をA-A'で切断した断面図を図14(B)に、B-B'で切断した断面図を図14(C)に、C-C'で切断した断面図を図14(D)に示す。なお、1405は支持バンク、1406は分離絶縁膜である。

40

#### 【0133】

バッファ配線1401～1403は、陽極と同一材料からなる配線であり、典型的には酸化物導電膜からなる配線である。酸化物導電膜は金属膜に比べて抵抗値が高いため、バッファ配線は一種の抵抗体として機能することになる。そのため、陽極接続配線1305もしくは陰極接続配線1307に大電流が流れたとしても、バッファ配線で緩衝され、複数の発光装置に被害が及ぶのを防ぐことが可能となる。

#### 【0134】

本実施例の構成とすることで、多面取りプロセスにより一度に複数の発光装置を作製する場合にも、複雑な配線を施すことなく、本発明を実施することが可能となる。

#### 【0135】

50

また、発光装置が完成したら、ダイサーもしくはスクライバーを用いて基板 1301 を分断し、発光装置を個々に分離すれば良い。このとき、陽極接続配線 1305 やバンク接続配線 1307 も分断してしまえば、各発光装置は電気的に孤立した状態となる。

#### 【0136】

なお、基板 1301 を分断する前もしくは分断した後に、必要に応じて実施例 5 ~ 9 に示したスティックドライバを設けることも可能である。また、本実施例の構成は実施例 1 ~ 4 もしくは 10 のいずれの構成とも自由に組み合わせて実施することが可能である。

#### 【0137】

##### 〔実施例 12〕

本実施例では、本発明とシャドーマスクとを組み合わせて用いる場合について説明する。

説明には図 15 を用いる。なお、図 2 (A) に示した構造と同一の部分は同一の符号を用いて説明する。

#### 【0138】

図 15 では、バンク 104 の上方に、さらにシャドーマスク 1501 を設け、シャドーマスク 1501 を負に帯電させておく。即ち、シャドーマスク 1501 と制御バンク 104 b を同じ極性に帯電させておく。

#### 【0139】

このとき、制御バンク 104 b 間の距離を  $X_1$  とし、シャドーマスク 1501 に設けられた開口部の距離を  $X_2$  とすると、 $X_1 < X_2$  の関係とすることが好みしい。このようにすると、シャドーマスク 1501 の上方から飛んできた EL 材料（もしくは EL 材料を含む溶液）201 は、まずシャドーマスク 1501 が形成する電界によりシャドーマスク 1501 の開口部付近に導かれる。さらに、制御バンク 104 b が形成する電界により画素内へと導かれる。こうして EL 層 202 が成膜される。

#### 【0140】

本実施例の構成は、特に赤色発光用の EL 材料、緑色発光用の EL 材料および青色発光用の EL 材料を分けて成膜する場合のように、異なる種類の EL 材料を複数回に分けて成膜する場合に有効である。

#### 【0141】

なお、本実施例の構成は実施例 1 ~ 11 のいずれの構成とも自由に組み合わせて実施することが可能である。

#### 【0142】

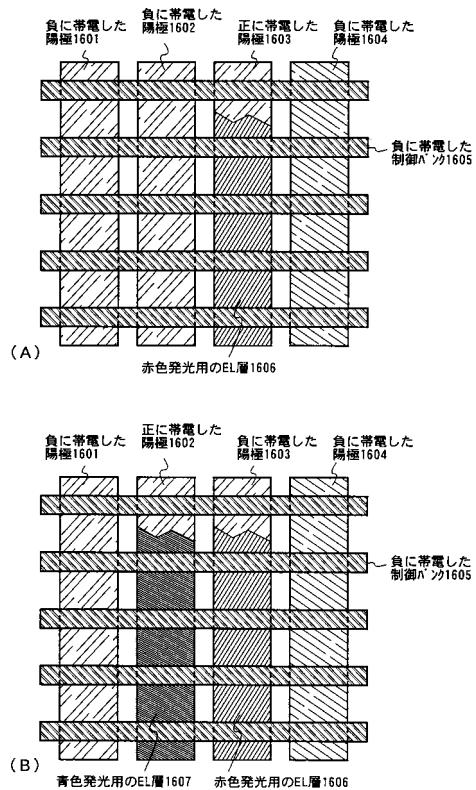

##### 〔実施例 13〕

本実施例では、シャドーマスクを用いることなく、本発明の電界制御により赤色発光用の EL 材料、緑色発光用の EL 材料および青色発光用の EL 材料を分けて成膜する場合について説明する。

#### 【0143】

本実施例の概念を図 16 (A)、(B) に示す。図 16 (A)、(B) では、図示しない絶縁体上に陽極 1601 ~ 1604 が形成され、それらと直交するように制御バンク 1605 が形成されている。

#### 【0144】

本実施例では、まず図 16 (A) に示すように、陽極 1603 のみ正に帯電させ、他の陽極 1601、1602、1604 を負に帯電させる。さらに制御バンク 1605 を負に帯電させ、この状態で負に帯電させた赤色発光用の EL 材料を蒸着法により成膜する。このとき、負に帯電した陽極上では EL 材料が反発され、殆どが正に帯電した陽極 1603 上に成膜される。こうして赤色発光用の EL 層 1606 が成膜される。

#### 【0145】

次に、図 16 (B) に示すように、陽極 1602 のみ正に帯電させ、他の陽極 1601、1603、1604 を負に帯電させる。さらに制御バンク 1605 を負に帯電させ、この状態で負に帯電させた緑色発光用の EL 材料を蒸着法により成膜する。このとき、負に帯電した陽極上では EL 材料が反発され、殆どが正に帯電した陽極 1602 上に成膜される

10

20

30

40

50

。こうして緑色発光用のEL層1607が成膜される。

【0146】

さらに、図示しないが、青色発光用のEL層も同様に陽極1601、1604のみを正に帯電させ、他の陽極1602、1603を負に帯電させて青色発光用のEL材料を成膜すれば良い。

【0147】

本実施例の構成では、制御バンク1605が形成する電界および陽極1601～1604が形成する電界により、EL材料の軌道を決定し、シャドーマスクを用いずに選択的な成膜を可能とするものである。

【0148】

なお、本実施例の構成は実施例1～11のいずれの構成とも自由に組み合わせて実施することが可能である。

【0149】

〔実施例14〕

本発明において、三重項励起子からの燐光を発光に利用できるEL材料を用いることで、外部発光量子効率を飛躍的に向上させることができる。これにより、EL素子の低消費電力化、長寿命化、および軽量化が可能になる。

ここで、三重項励起子を利用し、外部発光量子効率を向上させた報告を示す。

(T.Tsutsui, C.Adachi, S.Saito, Photochemical Processes in Organized Molecular Systems, ed.K.Honda, (Elsevier Sci.Pub., Tokyo,1991) p.437.)

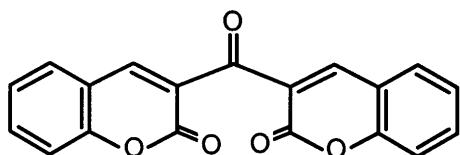

上記論文に報告されたEL材料(クマリン色素)の分子式を以下に示す。

【0150】

【化1】

10

20

30

【0151】

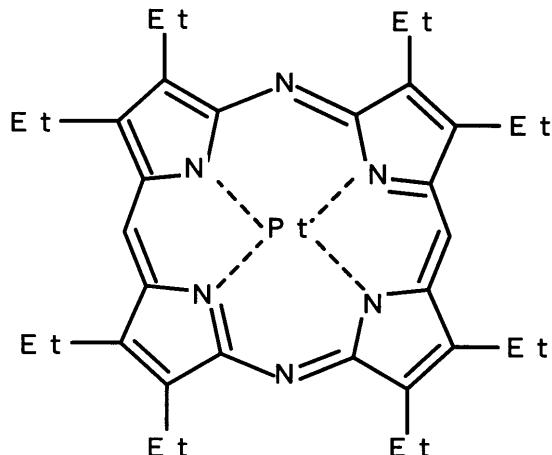

(M.A.Baldo, D.F.O'Brien, Y.You, A.Shoustikov, S.Sibley, M.E.Thompson, S.R.Forrest, Nature 395 (1998) p.151.)

上記論文に報告されたEL材料(Pt錯体)の分子式を以下に示す。

【0152】

【化2】

10

## 【0153】

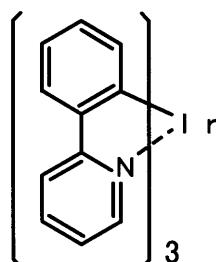

(M.A.Baldo, S.Lamansky, P.E.Burrows, M.E.Thompson, S.R.Forrest, Appl.Phys.Lett., 75 (1999) p.4.)

(T.Tsutsui, M.-J.Yang, M.Yahiro, K.Nakamura, T.Watanabe, T.tsuji, Y.Fukuda, T.Wakimoto, S.Mayaguchi, Jpn.Appl.Phys., 38 (12B) (1999) L1502.) 20

上記論文に報告されたEL材料(Ir錯体)の分子式を以下に示す。

## 【0154】

## 【化3】

30

## 【0155】

以上のように三重項励起子からの発光を利用できれば原理的には一重項励起子からの蛍光発光を用いる場合より3~4倍の高い外部発光量子効率の実現が可能となる。なお、本実施例の構成は、実施例1~実施例13のいずれの構成とも自由に組み合わせて実施することができる。

40

## 【0156】

## 【実施例15】

本発明を実施して形成された発光装置は、自発光型であるため液晶表示装置に比べて明るい場所での視認性に優れ、しかも視野角が広い。従って、様々な電気器具の表示部として用いることができる。その際、本発明の発光装置はパッシブ型の発光装置でありながらも配線抵抗を減らすことで大画面化を可能としているため、用途も幅広いものとすることができます。

## 【0157】

本発明の電気器具としては、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ(

50

ヘッドマウントディスプレイ)、カーナビゲーションシステム、カーオーディオ、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍)、記録媒体を備えた画像再生装置(具体的にはコンパクトディスク(CD)、レーザーディスク(LD)又はデジタルバーサタイルディスク(DVD)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などが挙げられる。それら電気器具の具体例を図17に示す。

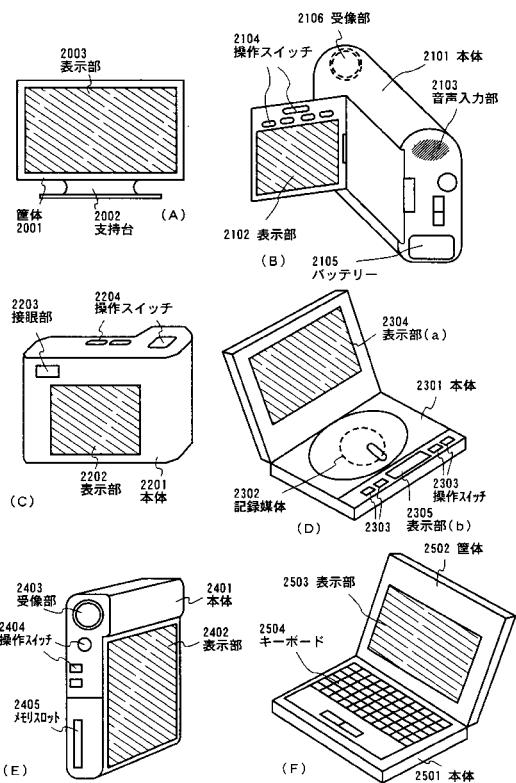

#### 【0158】

図17(A)はELディスプレイであり、筐体2001、支持台2002、表示部2003を含む。本発明の発光装置は表示部2003に用いることができる。ELディスプレイは自発光型であるためバックライトが必要なく、液晶ディスプレイよりも薄い表示部とすることができる。なお、表示部2003に用いる発光装置にスティックドライバを設ける場合は、数十個に分割して設けることが好ましい。10

#### 【0159】

図17(B)はビデオカメラであり、本体2101、表示部2102、音声入力部2103、操作スイッチ2104、バッテリー2105、受像部2106を含む。本発明の発光装置は表示部2102に用いることができる。なお、表示部2102に用いる発光装置にスティックドライバを設ける場合は、数個に分割して設けることが好ましい。

#### 【0160】

図17(C)はデジタルカメラであり、本体2201、表示部2202、接眼部部2203、操作スイッチ2204を含む。本発明の発光装置は表示部2202に用いることができる。なお、表示部2202に用いる発光装置にスティックドライバを設ける場合は、数個に分割して設けることが好ましい。20

#### 【0161】

図17(D)は記録媒体を備えた画像再生装置(具体的にはDVD再生装置)であり、本体2301、記録媒体(CD、LDまたはDVD等)2302、操作スイッチ2303、表示部(a)2304、表示部(b)2305を含む。表示部(a)は主として画像情報を表示し、表示部(b)は主として文字情報を表示するが、本発明の発光装置はこれら表示部(a)、(b)に用いることができる。なお、記録媒体を備えた画像再生装置には、CD再生装置、ゲーム機器なども含まれうる。なお、表示部(a)2304、表示部(b)2305に用いる発光装置にスティックドライバを設ける場合は、数十個に分割して設けることが好ましい。30

#### 【0162】

図17(E)は携帯型(モバイル)コンピュータであり、本体2401、表示部2402、受像部2403、操作スイッチ2404、メモリスロット2405を含む。本発明の電気光学装置は表示部2402に用いることができる。この携帯型コンピュータはフラッシュメモリや不揮発性メモリを集積化した記録媒体に情報を記録したり、それを再生したりすることができる。なお、表示部2402に用いる発光装置にスティックドライバを設ける場合は、数個に分割して設けることが好ましい。

#### 【0163】

図17(F)はパーソナルコンピュータであり、本体2501、筐体2502、表示部2503、キーボード2504を含む。本発明の発光装置は表示部2503に用いることができる。なお、表示部2503に用いる発光装置にスティックドライバを設ける場合は、数十個に分割して設けることが好ましい。40

#### 【0164】

なお、将来的にEL材料の発光輝度が高くなれば、出力した画像情報を含む光をレンズ等で拡大投影してフロント型若しくはリア型のプロジェクターに用いることも可能となる。

#### 【0165】

また、上記電子装置はインターネットやCATV(ケーブルテレビ)などの電子通信回線を通じて配信された情報を表示するが多くなり、特に動画情報を表示する機会が増してきている。EL材料の応答速度は非常に高いため、そのような動画表示を行うに適して50

いる。

#### 【0166】

また、発光装置は発光している部分が電力を消費するため、発光部分が極力少なくなるように情報を表示することが望ましい。従って、携帯情報端末、特に携帯電話やカーオーディオのような文字情報を主とする表示部に発光装置を用いる場合には、非発光部分を背景として文字情報を発光部分で形成するように駆動することが望ましい。

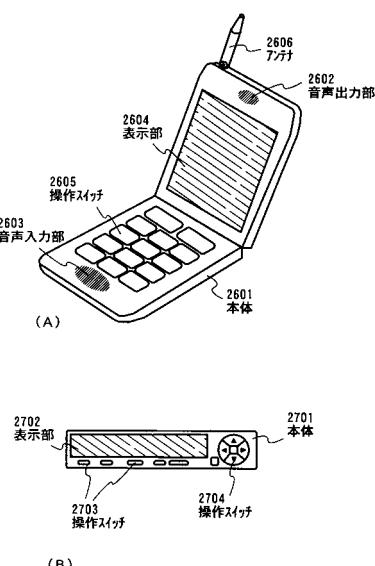

#### 【0167】

ここで図18(A)は携帯電話であり、本体2601、音声出力部2602、音声入力部2603、表示部2604、操作スイッチ2605、アンテナ2606を含む。本発明の発光装置は表示部2604に用いることができる。なお、表示部2604は黒色の背景に白色の文字を表示することで携帯電話の消費電力を抑えることができる。10

#### 【0168】

また、図18(B)はカーオーディオ(車載用オーディオ)であり、本体2701、表示部2702、操作スイッチ2703、2704を含む。本発明の発光装置は表示部2702に用いることができる。また、本実施例では車載用オーディオを示すが、据え置き型(家庭用)オーディオに用いても良い。なお、表示部2704は黒色の背景に白色の文字を表示することで消費電力を抑えられる。なお、表示部2704に用いる発光装置にステイックドライバを設ける場合は、数個に分割して設けることが好ましい。

#### 【0169】

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電気器具に用いることが可能である。また、本実施例の電気器具は実施例1~14の構成を自由に組み合わせた発光装置を用いることで得ることができる。20

#### 【0170】

##### 【発明の効果】

本発明を実施することでEL材料を成膜するにあたって成膜位置を精密に制御することができる。そのため高精細な画素部を有する発光装置を作製することができる。また、必要な部分に優先的にEL材料を成膜することができるため、EL材料の利用効率が高まり、製造コストを低減することができる。さらに、本発明の発光装置を表示部として用いることで高精細な表示部を有した電気器具を得ることができる。

##### 【図面の簡単な説明】

- 【図1】 発光装置の上面構造および断面構造を示す図。

- 【図2】 EL材料の成膜工程を説明するための図。

- 【図3】 蒸着法によるEL材料の成膜工程を説明するための図。

- 【図4】 インクジェット法によるEL材料の成膜工程を説明するための図。

- 【図5】 イオンプレーティング法によるEL材料の成膜工程を説明するための図。

- 【図6】 発光装置の上面構造を示す図。

- 【図7】 スティックドライバの断面構造を示す図。

- 【図8】 スティックドライバの接続例を示す図。

- 【図9】 発光装置の上面構造および断面構造を示す図。

- 【図10】 発光装置および発光装置に入力される信号の構成を示す図。

- 【図11】 スティックドライバの作製工程を示す図。

- 【図12】 発光装置の断面構造を示す図。

- 【図13】 多面取りプロセスを説明するための図。

- 【図14】 多面取りプロセスを説明するための図。

- 【図15】 EL材料の成膜工程を説明するための図。

- 【図16】 EL材料の成膜工程を説明するための図。

- 【図17】 電気器具の一例を示す図。

- 【図18】 電気器具の一例を示す図。

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

〔四七〕

【 図 8 】

801:基板 802:ステップ・ライア 803:画素部 804:引出線

805:入力端子 806:加一材 807:シール材 808:充填材

809:T C P 810:樹脂 811:導電性粒子 812:入力端子

803                  804                  612                  612

(6)                                                    600

【 図 9 】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

---

フロントページの続き

(56)参考文献 特開平10-335068(JP,A)

国際公開第98/012689(WO,A1)

特開平09-102393(JP,A)

特公昭47-035690(JP,B1)

特開平09-234870(JP,A)

特開平10-321372(JP,A)

(58)調査した分野(Int.Cl., DB名)

H05B 33/10

H01L 51/50

H05B 33/12

H05B 33/22