(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6357099号

(P6357099)

(45) 発行日 平成30年7月11日(2018.7.11)

(24) 登録日 平成30年6月22日(2018.6.22)

|                         |                   |

|-------------------------|-------------------|

| (51) Int.Cl.            | F 1               |

| HO 1 L 21/301 (2006.01) | HO 1 L 21/78 S    |

| B23K 26/364 (2014.01)   | HO 1 L 21/78 B    |

| HO 1 L 21/304 (2006.01) | B23K 26/364       |

|                         | HO 1 L 21/304 631 |

請求項の数 12 (全 17 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2014-515843 (P2014-515843)  |

| (86) (22) 出願日 | 平成24年5月25日 (2012.5.25)        |

| (65) 公表番号     | 特表2014-523112 (P2014-523112A) |

| (43) 公表日      | 平成26年9月8日 (2014.9.8)          |

| (86) 国際出願番号   | PCT/US2012/039746             |

| (87) 国際公開番号   | W02012/173768                 |

| (87) 国際公開日    | 平成24年12月20日 (2012.12.20)      |

| 審査請求日         | 平成27年1月21日 (2015.1.21)        |

| 審判番号          | 不服2016-5329 (P2016-5329/J1)   |

| 審判請求日         | 平成28年4月11日 (2016.4.11)        |

| (31) 優先権主張番号  | 13/160,891                    |

| (32) 優先日      | 平成23年6月15日 (2011.6.15)        |

| (33) 優先権主張国   | 米国(US)                        |

早期審査対象出願

|           |                                                                                                                                                                |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 390040660<br>アプライド マテリアルズ インコーポレイテッド<br>A P P L I E D M A T E R I A L S, I<br>N C O R P O R A T E D<br>アメリカ合衆国 カリフォルニア州 95<br>054 サンタ クララ バウアーズ ア<br>ベニュー 3050 |

| (74) 代理人  | 100101502<br>弁理士 安齋 嘉章                                                                                                                                         |

| (72) 発明者  | リ ウェイシェン<br>アメリカ合衆国 カリフォルニア州 95<br>130 サン ノゼ デュバル ドライブ<br>1786                                                                                                 |

最終頁に続く

(54) 【発明の名称】レーザ・プラズマエッティングによる基板のダイシング用水溶性マスク

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の IC を含む基板をダイシングする方法であって、

基板上に IC を被覆し保護するマスクを形成する工程であって、マスクは IC の上面と

接触する水溶性材料の層を含む工程と、

レーザスクライピングプロセスによってマスク及び基板の一部をパターニングして、ギャップを有するパターニングされたマスクを提供し、IC 間の基板の領域を露出させる工程であって、530 ナノメートル以下の波長と 500 フェムト秒以下のレーザパルス幅を有するフェムト秒レーザでギャップを形成する工程を含み、各々のギャップは基板内にある幅を有する工程と、

ギャップを貫通してプラズマエッティングして、これによって基板内にトレンチを形成し、IC を個片化する工程であって、各々のトレンチは前記幅を有する工程を含み、

前記方法は、プロセスツールによって実行され、前記プロセスツールは、

レーザスクライプ装置と、

クラスタツールとを含み、クラスタツールは、

ロボットアームを収容し、ファクトリーインターフェースを介してレーザスクライプ装置に結合されたロボット搬送チャンバと、

ロボット搬送チャンバに結合された 1 以上のプラズマエッティングチャンバとを含み

前記パターニングは、前記レーザスクライプ装置によって実行され、

10

20

前記プラズマエッティングは、前記プラズマエッティングチャンバ内で実行される方法。

**【請求項 2】**

レーザスクライビングプロセスによってマスクをパターニングする工程が、水溶性材料が、水溶性ポリマーを含み、半導体基板をエッティングする工程が、水溶性材料を100未満に維持しながら、ディープトレンチエッティングプロセスでトレンチをエッティングする工程を含む請求項1記載の方法。

**【請求項 3】**

マスクを形成する工程が、IC間のストリートの上で20μm以下、ICの上部バンプ上に少なくとも10μmの厚さに水溶性材料層を形成する工程を含む請求項1記載の方法。

10

**【請求項 4】**

マスクを形成する工程が、ポリ(ビニルアルコール)、ポリ(アクリル酸)、ポリ(メタクリル酸)、ポリ(アクリルアミド)、又はポリ(エチレンオキシド)のうちの少なくとも1つをICの上面に接触して塗布する工程を含む請求項1記載の方法。

**【請求項 5】**

マスクを形成する工程が、ポリ(ビニルアルコール)をICの上面に接触して塗布する工程を含む請求項4記載の方法。

**【請求項 6】**

マスクを形成する工程が、

ICの上面の上に水溶性ポリマーの水溶液をスピンドルコートする工程と、

水溶液を乾燥させる工程を含む請求項1記載の方法。

20

**【請求項 7】**

裏面研削プロセスによって基板を薄くする工程を含み、スピンドルコートは裏面研削の後に実行される請求項6記載の方法。

**【請求項 8】**

マスクを形成する工程が、ICの上面の上に水溶性材料のドライフィルムを真空ラミネートする工程を含む請求項1記載の方法。

**【請求項 9】**

裏面研削プロセスで基板を薄くする工程を含み、真空ラミネートは裏面研削の後に実行される請求項1記載の方法。

30

**【請求項 10】**

基板をプラズマエッティングした後の水溶性マスクを水溶液で除去する工程を含む請求項1記載の方法。

**【請求項 11】**

除去する工程は、水溶性マスクを水の加圧されたジェットで洗い流す工程を含む請求項10記載の方法。

**【請求項 12】**

複数のICを含む半導体基板をダイシングする方法であって、

シリコン基板の上に水溶性マスクを形成する工程であって、水溶性マスクは、シリコン基板上に配置されたICを覆い保護し、ICは、二酸化ケイ素の層、低k材料の層、及び銅の層を含む薄膜スタックを含む工程と、

40

水溶性マスク、低k材料の層、銅の層、及びシリコン基板の一部を、530ナノメートル以下の波長と500フェムト秒以下のレーザパルス幅を有するフェムト秒レーザでパターニングし、これによって内部にギャップを生成し、IC間のシリコン基板の領域を露出させる工程であって、各々のギャップはシリコン基板内にある幅を有する工程と、

ギャップを貫通してシリコン基板をプラズマエッティングし、これによってシリコン基板内にトレンチを形成し、ICを個片化する工程であって、各々のトレンチは、シリコン基板内に前記幅を有する工程を含み、

前記方法は、プロセスツールによって実行され、前記プロセスツールは、

レーザスクライブ装置と、

50

クラスタツールとを含み、クラスタツールは、

ロボットアームを収容し、ファクトリーインターフェースを介してレーザスクライ

ブ装置に結合されたロボット搬送チャンバと、

ロボット搬送チャンバに結合された1以上のプラズマエッチングチャンバとを含み

、

前記パターニングは、前記レーザスクライブ装置によって実行され、

前記プラズマエッチングは、前記プラズマエッチングチャンバ内で実行される方法。

## 【発明の詳細な説明】

10

## 【技術分野】

## 【0001】

本発明の実施形態は、半導体処理の分野に関し、特に、各基板がICを上に有する基板をダイシングするためのマスキング方法に関する。

## 【関連技術の背景説明】

## 【0002】

半導体基板の処理において、典型的にはシリコン又は他の半導体材料からなる基板（ウェハとも呼ばれる）上にICが形成される。一般的には、半導体、導体又は絶縁体のうちのいずれかである種々の材料の薄膜層が、ICを形成するために使用される。これらの材料は、様々な周知のプロセスを用いてドープされ、蒸着（堆積）され、エッチングされ、これによって同時に複数のIC（例えば、メモリデバイス、論理デバイス、光起電デバイス等）を同一基板上に同時に形成する。

20

## 【0003】

デバイス形成に続いて、基板は、支持部材（例えば、フィルムフレーム全域に亘って引き伸ばされた接着フィルム）に載置され、基板は梱包等のために互いに各々個々のデバイス又は「ダイ」に分離するために「ダイシング」される。現在、最も人気のある2つのダイシング技術は、スクライビングとソーイングである。スクライビングの場合、ダイヤモンドを先端に付けたスクライブが、予め形成されたスクライブラインに沿って基板表面を横切って移動する。例えば、ローラによって圧力を印加すると、基板はスクライブラインに沿って分離する。ソーイングの場合は、ダイヤモンドを先端に付けたこぎりがストリートに沿って基板を切断する。50～150 μm厚のバルクシリコンの個片化等の薄い基板の個片化の場合、従来のアプローチでは、悪いプロセス品質のみが得られている。薄い基板からダイを個片化する際に直面する可能性のある課題のいくつかは、異なる層間における微小亀裂の形成又は剥離、無機誘電体層のチッピング、厳密な切り口幅制御の保持、又は正確なアブレーション深さの制御を含めることができる。

30

## 【0004】

プラズマダイシングも考えられるが、レジストのパターニングのための標準的なリソグラフィ操作は、実行コストが桁違いに高くなる可能性がある。プラズマダイシングの実施を妨げる可能性のあるもう一つの制限は、一般的に発生する金属（例えば、銅）のプラズマ処理は、ストリートに沿ってダイシングする際に、生産の問題やスループットの限界を作る可能性があることである。最後に、プラズマダイシングプロセスのマスキングは、とりわけ、基板の厚さ及び上面のトポグラフィー、プラズマエッチングの選択性、及び基板の上面に存在する材料に応じて、問題となる可能性がある。

40

## 【概要】

## 【0005】

本発明の実施形態は、レーザスクライビング及びプラズマエッチングの両方を含むハイブリッドダイシングプロセスのための半導体基板をマスキングする方法を含む。

## 【0006】

一実施形態では、複数のICを有する基板をダイシングする方法は、半導体基板上にICを被覆し保護する水溶性材料を含むマスクを形成する工程を含む。マスクは、レーザス

50

クライピングプロセスによってパターニングされ、ギャップを有するパターニングされたマスクを提供し、IC間の基板の領域を露出させる。その後、パターニングされたマスク内のギャップを貫通して基板をプラズマエッチングして、ICを個片化してチップにする。

【0007】

別の一実施形態では、半導体基板をダイシングするシステムは、同じプラットフォームに結合されたフェムト秒レーザと、プラズマエッチングチャンバと、ウェットステーションを含む。

【0008】

別の一実施形態では、複数のICを有する基板をダイシングする方法は、シリコン基板の表側の上にポリビニルアルコール(PVA)の水溶性マスク層を形成する工程を含む。マスクは、基板の表側の上に配置されたICを被覆し保護する。ICは、パッシベーション層(ポリイミド(PI)等)によって取り囲まれたバンプを有する銅でバンプ形成された上面を含む。バンプ及びパッシベーションの下の表面下の薄膜は、低の層間誘電体(ILD)層及び銅配線の層を含む。水溶性材料、パッシベーション層、及び表面下の薄膜は、フェムト秒レーザクライピングプロセスでパターニングされ、これによってIC間のシリコン基板の領域を露出させる。シリコン基板は、ディープシリコンプラズマエッチングプロセスによってギャップを貫通してエッチングされ、これによってIC及びPVA層を個片化し、その後、水中で洗い流される。

【図面の簡単な説明】

【0009】

本発明の実施形態は、添付図面の図において、限定ではなく例として示されている。

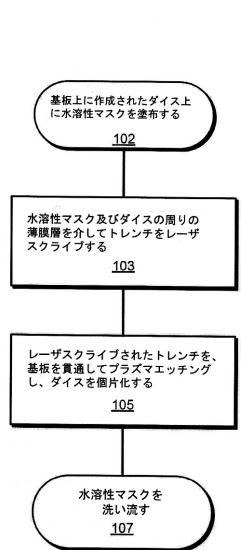

【図1】本発明の実施形態に係るハイブリッドレーザアブレーションプラズマエッチング個片化法を示すフロー図である。

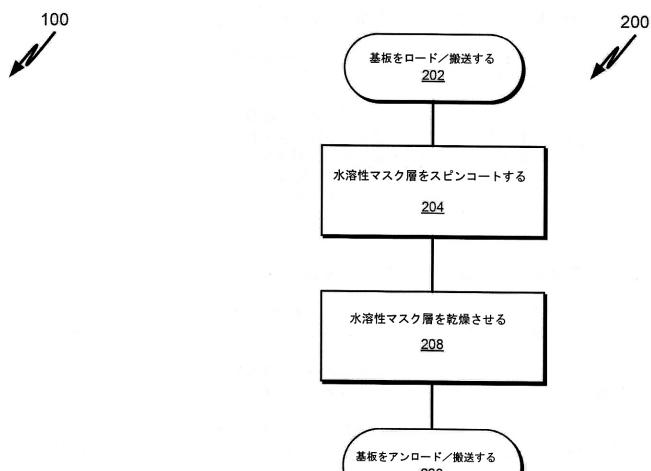

【図2A】本発明の実施形態に係る、ダイシングされる基板上に水溶性マスク層をスピンドルコートする方法を示すフロー図である。

【図2B】本発明の実施形態に係る、ダイシングされる基板に水溶性マスク層を塗布するドライフィルムラミネーション法を示すフロー図である。

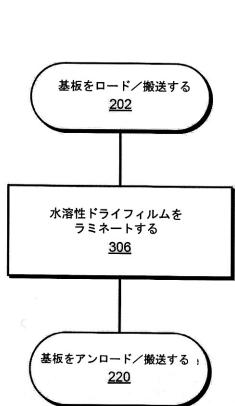

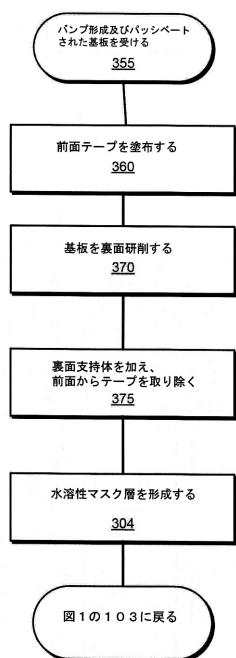

【図3A】本発明の実施形態に係る、ウェハを薄くする前にダイシングされる基板に水溶性マスク層を塗布する方法を示すフロー図である。

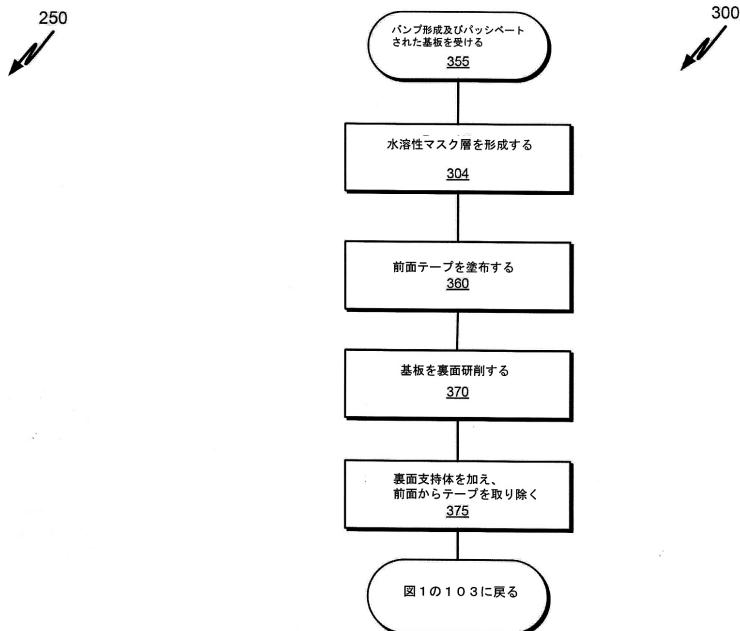

【図3B】本発明の実施形態に係る、ウェハを薄くした後にダイシングされる基板に水溶性マスク層を塗布する方法を示すフロー図である。

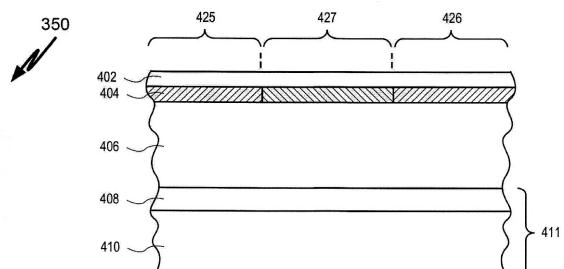

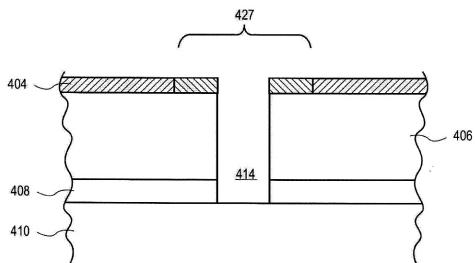

【図4A】本発明の実施形態に係る、図1に示されるダイシング方法の操作102に対応する、複数のICを含む半導体基板の断面図である。

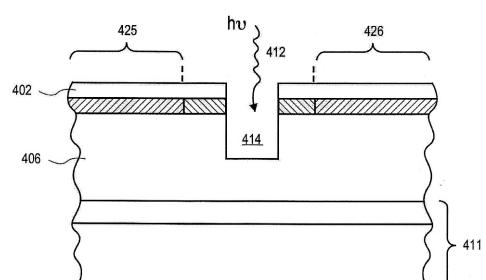

【図4B】本発明の実施形態に係る、図1に示されるダイシング方法の操作103に対応する、複数のICを含む半導体基板の断面図である。

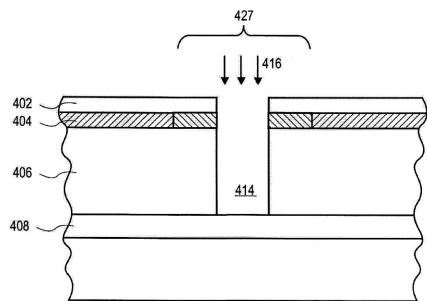

【図4C】本発明の実施形態に係る、図1に示されるダイシング方法の操作105に対応する、複数のICを含む半導体基板の断面図である。

【図4D】本発明の実施形態に係る、図1に示されるダイシング方法の操作107に対応する、複数のICを含む半導体基板の断面図である。

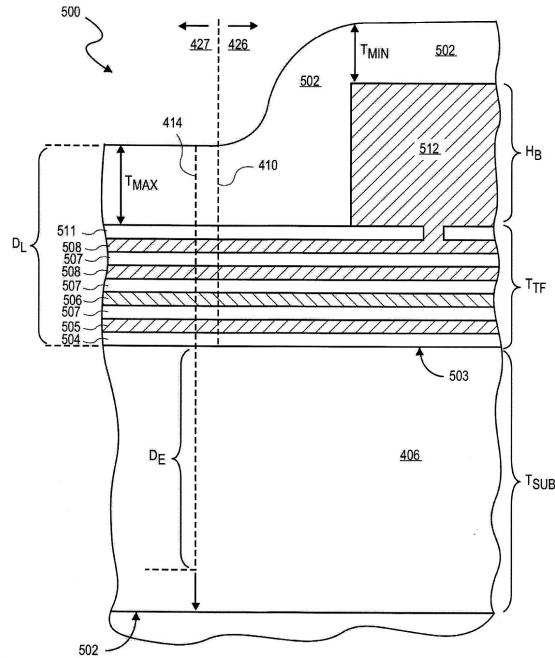

【図5】本発明の実施形態に係る、複数のICを含む基板の上面及び表面下の薄膜の上に塗布される水溶性マスクの断面図を示す。

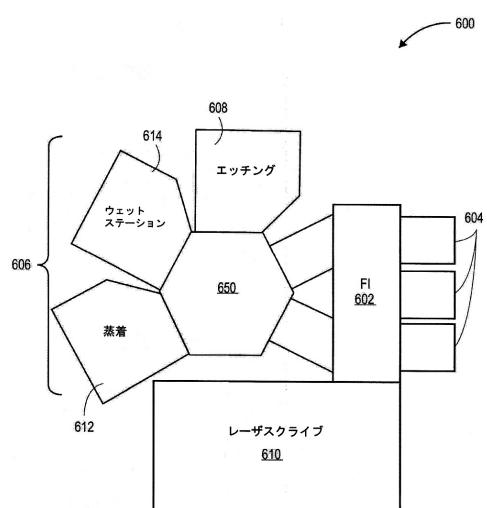

【図6】本発明の実施形態に係る、マスク除去用統合化ウェットステーションを備えた基板のレーザ・プラズマダイシング用ツールレイアウトのブロック図を示す。

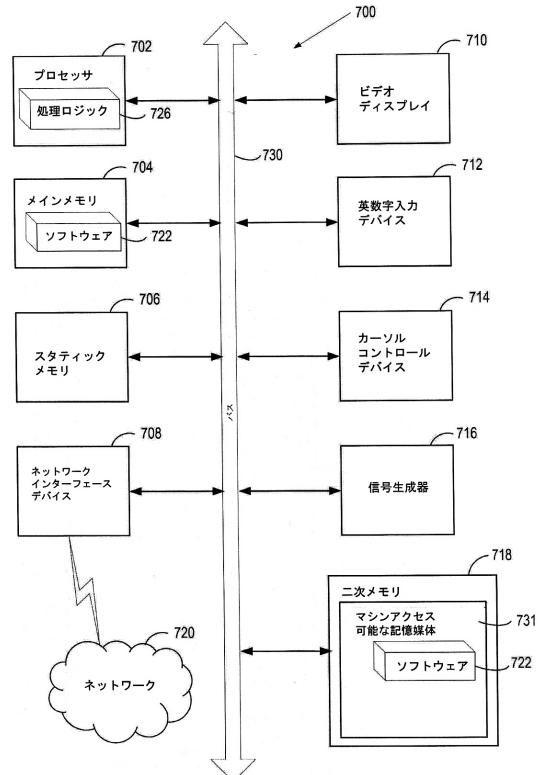

【図7】本発明の実施形態に係る、本明細書に記載されるマスキング法、レーザクライピング法、プラズマダイシング法において、1以上の操作の自動実行を制御する例示的コンピュータシステムのブロック図を示す。

【詳細な説明】

【0010】

各基板が複数のICを上に有する基板をダイシングする方法を説明する。以下の説明で

10

20

30

40

50

は、本発明の例示的な実施形態を説明するために、多数の特定の詳細（例えば、フェムト秒レーザスクライビング条件及びディープシリコンプラズマエッチング条件）が記載されている。しかしながら、本発明の実施形態は、これらの特定の詳細なしに実施できることは当業者には明らかであろう。他の例において、周知の態様（例えば、IC製造、基板薄化、テーピング等）は、本発明の実施形態を必要に不明瞭にしないために、詳細には説明されない。本明細書全体を通して、「一実施形態」は、その実施形態に関連して記載された特定の構成、構造、材料、又は特性が、本発明の少なくとも1つの実施形態に含まれることを意味する。従って、本明細書全体を通して様々な箇所で「一実施形態では」というフレーズが出現するが、必ずしも本発明の同じ実施形態に言及しているわけではない。更に、特定の構成、構造、材料、又は特性は、1以上の実施形態において任意の適切な方法で組み合わせができる。また、図に示される様々な例示的実施形態は単なる例示表現であり、必ずしも一定の縮尺で描かれていないと理解されるべきである。

#### 【0011】

用語「結合される」、「接続される」及びそれらの派生語は、本明細書内では構成要素間の構造的関係を記述するために使用することができる。これらの用語は互いに同義語として意図されるものではないことを理解すべきである。むしろ、特定の実施形態では、「接続される」は、2以上の要素が互いに直接物理的又は電気的に接觸していることを示すために使用される場合がある。「結合される」は、2以上の要素が互いに直接的又は間接的に（それらの間に他の介在要素を有して）物理的又は電気的に接觸していること、及び/又は2以上の要素が（例えば、因果関係のように）互いに協働又は相互作用することを示すために使用される場合がある。

#### 【0012】

本明細書内で使用される用語「上に」、「下に」、「間に」、「表面に」は、1つの材料層の他の材料層に対する相対位置を表す。このように、例えば、1つの層が別の層の上に又は下に配置されるというのは、直接別の層に接觸していてもよく、又は1以上の介在層を有していてもよい。更に、2つの層の間に配置された1つの層は、2つの層と直接接觸していてもよく、又は1以上の介在層を有していてもよい。対照的に、「第1層」が「第2層」の「表面に」ある場合は、第2層に接觸している。また、1つの層の他の層に対する相対位置は、基板の絶対的な姿勢を考慮することなく、基板に対して操作が相対的に行われると仮定して設けられている。

#### 【0013】

一般的には、初期のレーザスクライプ及びその後のプラズマエッチングを含むハイブリッド基板又は基板のダイシングプロセスは、ダイの個片化用の水溶性マスクと共に実施される。レーザスクライププロセスは、パターニングされていない（即ち、プランケット）マスク層、パッシベーション層、及び表面下の薄膜デバイス層をきれいに除去するために使用することができる。レーザエッチングプロセスは、その後の基板の露出又は基板の部分的なアブレーション時に終了することができる。ハイブリッドダイシングプロセスのプラズマエッチングの部分は、その後、チップの個片化又はダイシングするために、基板のバルクを貫通して（例えば、バルクの単結晶シリコンを貫通して）エッチングするために用いることができる。

#### 【0014】

本発明の一実施形態によると、フェムト秒レーザとプラズマエッチングの組み合わせが使用され、これによって半導体基板を個別化された又は個片化されたICにダイシングする。一実施形態では、フェムト秒レーザスクライビングは、もしも完全でないならば、本質的に非平衡プロセスである。例えば、フェムト秒ベースのレーザスクライビングは、無視できる程度の熱損傷領域に局所化することができる。一実施形態では、レーザスクライビングは、超低 膜を有する（即ち、3.0未満の誘電率を有する）個片化されたICに使用される。一実施形態では、レーザによる直接描画は、リソグラフィのパターニング操作を削減し、マスキング材料が非感光性であることを可能にし、非常に少ないコストで実施されるプラズマエッチングベースのダイシング処理によって、基板の分割が可能となる

10

20

30

40

50

。一実施形態では、プラズマエッティングチャンバ内でダイシングプロセスを完了するために、スルーシリコンビア（ T S V ）型のエッティングが使用される。

【 0 0 1 5 】

図 1 は、本発明の実施形態に係るハイブリッドレーザアブレーションプラズマエッティング個片化プロセス 1 0 0 を示すフロー図である。図 4 A ~ 図 4 D は、本発明の一実施形態に係る方法 1 0 0 の操作に対応する第 1 及び第 2 の I C 4 2 5 、 4 2 6 を含む基板 4 0 6 の断面図を示す。

【 0 0 1 6 】

図 1 の操作 1 0 2 及び対応する図 4 A を参照すると、マスク層 4 0 2 が、基板 4 0 6 の上に形成される。一般的に、基板 4 0 6 は、その上に形成される薄膜デバイス層の製造プロセスに耐えるのに適した任意の材料から構成される。例えば、一実施形態では、基板 4 0 6 は、 I V 族系材料（例えば、単結晶シリコン、ゲルマニウム又はシリコン / ゲルマニウムが挙げられるが、これらに限定されない）である。別の一実施形態では、基板 4 0 6 は、 I I I - V 族材料（例えば、発光ダイオード（ L E D ）の製造に使用される I I I - V 族材料基板等）である。デバイス製造中に、基板 4 0 6 は、典型的には  $600 \mu m$  ~  $800 \mu m$  の厚さであるが、図 4 A に示されるように、キャリア（例えば、フレーム（図示せず）全域に亘って引き伸ばされ、ダイ取り付け膜（ D A F ） 4 0 8 によって基板の裏面に付けられたバックティングテープ 4 1 0 ）によって薄化された基板を今支持しながら、  $50 \mu m$  ~  $100 \mu m$  まで薄くされている。

【 0 0 1 7 】

実施形態では、第 1 及び第 2 の I C 4 2 5 、 4 2 6 は、シリコン基板 4 0 6 内で製造され、誘電体スタック内に入れられたメモリデバイス又は相補型金属酸化膜半導体（ C M O S ）トランジスタを含む。複数の金属相互接続をデバイス又はトランジスタの上方かつ取り囲む誘電体層内に形成することができ、 I C 4 2 5 、 4 2 6 を形成するためにデバイス又はトランジスタを電気的に結合するために使用することができる。ストリート（通り） 4 2 7 を構成する材料は、 I C 4 2 5 、 4 2 6 を形成するために用いる材料と類似又は同一であることができる。例えば、ストリート 4 2 7 は、誘電材料、半導体材料、及びメタライゼーションの薄膜層を含むことができる。一実施形態では、ストリート 4 2 7 は、 I C 4 2 5 、 4 2 6 と同様のテストデバイスを含む。ストリート 4 2 7 の幅は、どこでも  $10 \mu m$  ~  $100 \mu m$  の間である。

【 0 0 1 8 】

実施形態では、マスク層 4 0 2 は、 I C 4 2 5 、 4 2 6 の上面を覆う水溶性材料層を含む。マスク層 4 0 2 は、 I C 4 2 5 、 4 2 6 の間に介在しているストリート 4 2 7 も覆う。水溶性材料層は、ハイブリッドレーザスクライビング・プラズマエッティングダイシング法 1 0 0 （図 1 ）の間、 I C 4 2 5 、 5 2 6 の上面に保護を提供することができる。マスク層 4 0 2 は、ストリート 4 2 7 の上に配置されたマスク層 4 0 2 の一部を除去することによってスクライブラインの直接描画を行うレーザスクライブによるレーザスクライビング操作 1 0 3 の前にはパターン化されていない。

【 0 0 1 9 】

図 5 は、本発明の実施形態に係る、 I C 4 2 6 及びストリート 4 2 7 の上面と接触している水溶性層 5 0 2 を含む例示的な一実施形態の拡大断面図 5 0 0 を示す。図 5 に示されるように、基板 4 0 6 は、薄膜デバイス層が上に配置され、 D A F 4 0 8 （図 4 A ）とインターフェース接続する底面 5 0 1 の反対側にある上面 5 0 3 を有する。一般に、薄膜デバイス層材料としては、有機材料（例えば、ポリマー）、金属、又は無機誘電体（例えば、二酸化ケイ素、窒化ケイ素）を含むことができるが、これらに限定されない。図 5 に示される例示的な薄膜デバイス層は、二酸化ケイ素層 5 0 4 、窒化ケイ素層 5 0 5 、銅配線層 5 0 8 と共に、それらの間に配置される低（例えば、  $3.5$  未満）又は超低（例えば、  $3.0$  未満）の層間誘電体層（ I L D ）（例えば、炭素ドープ酸化物（ C D O ））を含む。 I C 4 2 6 の上面は、パッシベーション層 5 1 1 （典型的には、ポリイミド（ P I ）又は類似のポリマー）によって囲まれたバンプ 5 1 2 （典型的には、銅）を含む。従つ

10

20

30

40

50

て、バンプ 512 及びパッシベーション層 511 は、表面下の IC 層を形成する薄膜デバイス層で IC の上面を構成している。バンプ 512 は、パッシベーション層 511 の上面からバンプ高さ  $H_B$  延びており、例示的な実施形態では  $10 \mu m \sim 50 \mu m$  の間の範囲である。

#### 【0020】

一実施形態では、水溶性層 502 は、他の材料層を含まないようなマスク層 402 である。他のより従来型のマスキング材料（例えば、フォトレジスト）、無機誘電体ハードマスク（例えば、二酸化ケイ素）、又はシリセスキオキサンとは異なり、水溶性層 502 を含むマスクは、下地のパッシベーション層 511 及び / 又はバンプ 512 に損傷を与えることなく容易に除去することができる。水溶性層 502 がマスク層 402 である場合には、水溶性層 502 は、従来のスクライビングプロセス中に利用される単なる汚染保護層を超えたものであり、その代わりに後続のストリートのプラズマエッチングの際に保護を提供する。このように、水溶性層 502 は、プラズマにさらされたときに、損傷を受け、酸化され、又はそうでなくとも汚染される可能性のある銅であるバンプ 512 でさえも保護して、プラズマエッチングプロセスに耐えるのに十分な厚さである必要がある。水溶性層 502 の最小厚さは、後続のプラズマエッチング（例えば、図 1 の操作 105）によって達成される選択性の関数である。プラズマエッチングの選択性は、水溶性層 502 の材料 / 組成及び採用されるエッチングプロセスの少なくとももの両方に依存する。

#### 【0021】

一実施形態では、水溶性材料は、水溶性ポリマーを含む。多くのこのようなポリマーは、洗濯物及び買い物袋、刺繡、グリーンパッケージング等の用途のために市販されている。しかしながら、本発明用の水溶性材料の選択は、最大膜厚、耐エッチング性、熱安定性、基板への材料の塗布及び基板からの材料の除去機構、及び微視的な汚染（マイクロコンタミネーション）の厳しい要求によって複雑である。ストリート内において、水溶性層 502 の最大厚さ  $T_{max}$  は、レーザがアブレーションによってマスクを通してパターニングする能力によって制限される。水溶性層 502 は、IC 425、426 及び又はストリートパターンが形成されないストリート 427 の縁部に対してはるかに厚い可能性がある。このように、 $T_{max}$  は一般的に、レーザ波長に関連する光変換効率の関数である。 $T_{max}$  は、ストリート 427 に関連しているので、ストリートの構造トポグラフィー、ストリート幅、及び水溶性層 502 を塗布する方法は、所望の  $T_{max}$  を達成するように選択することができる。特定の実施形態では、複数のレーザパスを要求するより厚いマスクと共に、水溶性層 502 は、 $30 \mu m$  未満、有利には  $20 \mu m$  未満の厚さ  $T_{max}$  を有する。

#### 【0022】

一実施形態では、水溶性層 502 は、材料の温度が上昇されたときに、その後のプラズマエッチングプロセスの間の過度の架橋を避けるために、少なくとも 60 で熱的に安定であり、好ましくは 100 で安定であり、理想的には 120 で安定である。一般的に、過度の架橋は、材料の溶解性に悪影響を与え、エッチング後の除去がより困難になる。実施形態によって、水溶性層 502 は、ウェットパッシベーション層 511 及びバンプ 512 を覆うために基板 406 上に塗布される湿式のもの、あるいはドライフィルムラミネートとして塗布されるもののいずれかが可能である。塗布の両モードに対して、例示的な材料は、ポリ（ビニルアルコール）、ポリ（アクリル酸）、ポリ（メタクリル酸）、ポリ（アクリルアミド）、又はポリ（エチレンオキシド）の少なくとも 1 つを含み、多数の他の水溶性材料もまた、（特に、ドライフィルムラミネートとして）容易に利用可能である。ラミネート用のドライフィルムは、水溶性物質のみを含むことが可能であり、更に、水溶性であってもなくてもよい接着層を含むことも可能である。特定の一実施形態では、ドライフィルムは、UV 露光により接着結合強度を減少させる UV 感応性接着剤層を含む。このような UV 露光は、その後のプラズマストリートエッチング中に行うことができる。

#### 【0023】

実験的に、エッチング速度選択性が約 1 : 20 (PVA : シリコン) である本明細書の

10

20

30

40

50

他所に説明される典型的なシリコンプラズマエッティングプロセスに対して、ポリ(ビニルアルコール)(PVA)は、 $1 \mu\text{m}/\text{min} \sim 1.5 \mu\text{m}/\text{min}$ のエッティング速度を提供することが見出された。他の代表的な材料は、同様のエッティング特性を提供する可能性がある。このように、ICの最上部のバンプ面の上の最小厚さ(例えば、図5の $T_{\min}$ )は、基板の厚さ $T_{\text{sub}}$ 及びレーザスクライプ深さ $D_L$ の両方の関数であるプラズマエッティング深さ $D_E$ によって決定することができる。 $D_E$ が少なくとも $50 \mu\text{m}$ である例示的な実施形態では、少なくとも $100 \mu\text{m}$ の $D_E$ に対する十分なマージンを提供するために、水溶性層502は、少なくとも $5 \mu\text{m}$ 、有利には少なくとも $10 \mu\text{m}$ の厚さを有する。

【0024】

$30 \mu\text{m}$ 未満の $T_{\max}$ と $10 \mu\text{m}$ 以上の $T_{\min}$ の厚さを有する水溶性層502では、水溶性層502の基板への塗布は、汚染の予防手段のスプレー塗布よりも厳しい。図2Aは、本発明の一実施形態に係る、ダイシングされる基板上に水溶性マスク層をスピンドルするための方法200を示すフロー図である。操作202では、基板がスピンドルシステム上にロードされるか、又は統合プラットフォームのスピンドルモジュール内に搬送される。操作204では、水溶性ポリマーの水溶液が、パッシベーション層511及びバンプ512上で回転される。PVA溶液で行った実験では、 $T_{\min}$ が $5 \mu\text{m}$ を超えると、ストリートにおける $T_{\max}$ は $20 \mu\text{m}$ 未満の平坦化されない $50 \mu\text{m}$ のカバレッジを示した。

【0025】

操作208では、水溶液が、例えば、ホットプレート上で乾燥され、基板は、レーザスクライプのためにアンロードされる、又はレーザスクライプモジュールに真空中で搬送される。水溶性層502が吸湿性である特定の実施形態では、真空中の搬送は、特に有利である。スピンドルパラメータ及びディスペンスパラメータは、材料、基板のトポグラフィー及び所望の層厚に応じた選択事項である。乾燥温度及び時間は、除去を困難にする過度の架橋を回避しながら、十分なエッティング耐性を提供するように選択されるべきである。典型的な乾燥温度は、材料に応じて、 $60 \sim 150$ の範囲である。例えば、PVAは、温度が範囲の限界 $150$ に近付くにつれて、より不溶性になるが、 $60$ では可溶性のまままでいることが見出された。

【0026】

別の一実施形態では、水溶性層502は、パッシベーション層511及びバンプ512を覆うためにドライフィルムラミネートとして塗布される。図2Bは、本発明の一実施形態に係る、ダイシングされる基板に水溶性マスク層を塗布するためのラミネート方法250を示すフロー図である。操作202で始まり、基板がラミネーションシステム上にロードされるか、又は統合プラットフォームのラミネーションモジュール内に搬送される。操作306では、ドライフィルムのラミネーションが、サブ $30 \mu\text{m}$  $T_{\max}$ の膜厚を収容するように調整した前面テーピング装置において従来の技術を用いて真空中で実行される。接着層無しでドライフィルムを用いる特定の実施形態では、バンプパッシベーション層511及び/又はバンプ512にドライフィルムを保持するために、ファンデルワールス力又は静電気力が利用される。ドライフィルムのラミネーション操作306は、水溶性ドライフィルムの加熱のための熱プロセスを更に含むことができ、これによって加熱の改善及び/又はパッシベーション層511及びバンプ512の上の膜を制御可能に伸び縮みさせることを可能にする。操作220でラミネート方法250が完了し、基板はレーザスクライプのためにアンロードされ、又はレーザスクライプモジュールに真空中で搬送される。水溶性層502が吸湿性である特定の実施形態では、真空中の搬送は、特に有利である。

【0027】

実施形態に応じて、いずれかのスピンドル法200又はドライフィルムラミネート法250のいずれかを、裏面研削(BSG)の前に、又は裏面研削(BSG)に続けて実行することができる。スピンドル法は、一般に、従来の $750 \mu\text{m}$ の厚さを有する基板に対しては完成した技術であるので、スピンドル法200を裏面研削の前に有利に実行する

10

20

30

40

50

ことができる。しかしながら、スピンドルコート法 200 は、例えば、薄い基板と回転可能なチャック上のテープ止めされたフレームの両方を支持することによって、代替的に、裏面研削後に行われる。ドライフィルムのラミネートは、一般的に薄くした基板に対して完成した技術であるので、ラミネート法 250 を裏面研削の後に有利に実行することができる。しかしながら、ラミネート法 250 は、例えば、比較的厚い従来の BSG テープが最初に塗布される前面テープスタッカの第 1 層として、代替的に、裏面研削の前に行われる。

#### 【0028】

図 3A は、ウェハを薄化する前のダイシングされる基板にマスク層 402 を塗布するための方法 300 を示すフロー図である。方法 300 は、操作 355 において、バンプ形成及びパッシベートされた基板を受けることから始まる。操作 304 において、水溶性マスク層（例えば、水溶性層 502）を形成する。従って、操作 304 は、本明細書の他の箇所に記載されるように、水溶性マスク層の湿式又は乾式塗布を伴うことができる。操作 360 において、前面テープが水溶性マスク層上に形成される。任意の従来の前面テープ（例えば、UV テープが挙げられるが、これに限定されない。）を水溶性マスク層の上に塗布することができる。操作 370 において、基板は、例えば、図 5 に図示された基板 406 の下面 501 を研削することによって、裏面から薄くされる。操作 375 において、裏面支持体 411 が薄くされた基板に付けられる。例えば、裏面テープ 410 が塗布され、その後、前面テープを取り除いて、水溶性マスク層を露出させることができる。その後、方法 300 は、本発明の一実施形態に係る方法 100 を完了するために、操作 103（図 1）に戻る。

#### 【0029】

図 3B は、ウェハ薄化後にダイシングされる基板にマスク層 402 を塗布するための方法 350 を示すフロー図である。方法 350 は、操作 355 で、バンプ形成され、パッシベートされた基板を受けることから始まる。操作 360 において、任意の従来の前面テープ（例えば、UV テープが挙げられるが、これに限定されない。）を IC 上に塗布する。操作 370 において、基板は、例えば、図 5 に図示された基板 406 の下面 501 を研削することによって、裏面から薄くされる。操作 375 において、裏面支持体 411 が薄くされた基板に付けられる。例えば、裏面テープ 410 が塗布され、その後、水溶性マスク層から前面テープを取り除くことができる。操作 304 で、水溶性マスク層（例えば、水溶性層 502）が次いで形成される。操作 304 は、本明細書の他所に説明されるように、水溶性マスク層の湿式又は乾式塗布のいずれかを再び伴うことができる。その後、方法 350 は、本発明の一実施形態に係る方法 300 を完了するために、操作 103（図 1）に戻る。

#### 【0030】

ここで、方法 100 の操作 103 及び対応する図 4B に戻ると、マスク層 402 は、トレンチ 412 を形成するレーザスクライビングプロセスのアブレーションによってパターニングされ、表面下の薄膜デバイス層まで延ばし、IC 425、426 間の基板の領域を露出させる。このように、もともと IC 425、426 間に形成されていたストリート 427 の薄膜材料を除去するためにレーザスクライビングプロセスが用いられる。本発明の一実施形態によると、レーザベースのスクライビングプロセスによってマスク層 402 をパターニングすることは、図 4B に示されるように、IC 425、426 間の基板 406 の領域内に部分的にトレンチ 414 を形成することを含む。

#### 【0031】

図 5 に示される例示的な実施形態では、レーザスクライビングの深さ  $D_L$  は、パッシベーション層 511 及び表面下の薄膜デバイス層の厚さ  $T_F$  及び水溶性層 502（マスク 402 の一部として含まれる任意の追加的材料層）の厚さを  $T_{max}$  に応じて、およそ 5  $\mu m$  ~ 50  $\mu m$  の深さの範囲内にあり、有利には 10  $\mu m$  ~ 20  $\mu m$  の深さの範囲内にある。

#### 【0032】

一実施形態では、マスク層 402 は、本明細書内でフェムト秒レーザと呼ぶフェムト秒

10

20

30

40

50

範囲（つまり、 $10^{-15}$  秒）のパルス幅（持続時間）を有するレーザによってパターニングされる。パルス幅等のレーザパラメータの選択は、クリーンなレーザスクライプによる切り口を達成するために、チッピング、微小亀裂、及び剥離を最小限にする成功したレーザスクライピング・ダイシングプロセスの開発には重要である可能性がある。フェムト秒域のレーザ周波数は、有利なことに、より長いパルス幅（例えば、ピコ秒又はナノ秒）に対して熱損傷の問題を軽減する。理論に縛られないが、現在理解されているように、フェムト秒エネルギー源は、ピコ秒光源に存在する低エネルギー再結合メカニズムを回避し、ナノ秒光源よりも大きな熱非平衡性を提供する。ナノ秒又はピコ秒レーザ光源を使用すると、ストリート 427 内に存在する様々な薄膜デバイス層材料は、光学吸収及びアブレーションメカニズムの面で、かなり異なって振る舞う。例えば、二酸化ケイ素等の誘電体層は、通常の状態で市販されているすべてのレーザ波長に対して基本的に透明である。対照的に、金属、有機物（例えば、低 材料）及びシリコンは、非常に容易に光子に結合可能である（特に、ナノ秒ベース又はピコ秒ベースのレーザ照射）。最適でないレーザパラメータが選択されている場合は、無機誘電体、有機誘電体、半導体、又は金属のうちの 2 以上を含む積層構造において、ストリート 427 のレーザ照射は、不利なことに剥離を生ずる可能性がある。例えば、測定可能な吸収がなく、高バンドギャップエネルギーの誘電体（例えば、約 9 eV のバンドギャップを有する二酸化ケイ素）を貫通するレーザは、下地の金属又はシリコン層に吸収され、金属層又はシリコン層のかなりの蒸発を引き起こす可能性がある。蒸発は高い圧力を発生させ、潜在的に深刻な層間剥離及び微小亀裂の発生を引き起こす可能性がある。フェムト秒ベースのレーザ照射プロセスは、このような材料積層体のこのような剥離及び微小亀裂の発生を回避又は軽減することが実証されている。10 20

#### 【0033】

フェムト秒レーザベースのプロセス用のパラメータは、無機・有機誘電体、金属、及び半導体に対して実質的に同一のアブレーション特性を有するように選択することができる。例えば、二酸化ケイ素の吸収係数 / 吸収率は非線形であり、有機誘電体、半導体、及び金属のそれにより一致してもたらされる可能性がある。一実施形態では、高強度及び短パルス幅フェムト秒レーザベースのプロセスが、二酸化ケイ素層及び 1 以上の有機誘電体、半導体、又は金属を含む薄膜層の積層体をアブレーションするために使用される。本発明の一実施形態によると、適切なフェムト秒レーザベースのプロセスは、通常、様々な材料の非線形相互作用をもたらす高いピーク強度（照度）によって特徴付けられる。このような一実施形態では、フェムト秒レーザ光源は、概して 10 フェムト秒 ~ 450 フェムト秒の範囲のパルス幅を有するが、好ましくは、50 フェムト秒 ~ 500 フェムト秒の範囲内である。30

#### 【0034】

特定の実施形態では、レーザ放射は、広い又は狭い帯域の発光スペクトル用に、可視スペクトル、紫外線（UV）スペクトル、及び / 又は赤外線（IR）スペクトルの任意の組み合わせに及ぶ。フェムト秒レーザアブレーション用には、特定の波長が他よりも優れたパフォーマンスを提供する場合がある。例えば、一実施形態では、近紫外又は紫外範囲内の波長を有するフェムト秒レーザベースのプロセスは、近赤外又は赤外範囲内の波長を有するフェムト秒レーザベースのプロセスよりもクリーンなアブレーションプロセスを提供する。特定の一実施形態では、半導体基板又は基板のスクライピングに適したフェムト秒レーザは、およそ 540 ナノメートル以下の波長を有するレーザに基づくが、好ましくは、540 ナノメートル ~ 250 ナノメートルの範囲内である。特定の一実施形態では、540 ナノメートル以下の波長を有するレーザに対して、パルス幅は 500 フェムト秒以下である。しかしながら、代替の一実施形態では、デュアルレーザ波長（例えば、赤外線レーザと紫外線レーザの組み合わせ）が使用される。40

#### 【0035】

一実施形態では、レーザ及び関連する光経路は、作業面で約 3  $\mu$ m ~ 15  $\mu$ m の範囲内の焦点を提供するが、有利には、約 5  $\mu$ m ~ 10  $\mu$ m の範囲内である。作業面での空間ビームプロファイルは、シングルモード（ガウス分布）であるか、又はシルクハットプロフ50

アイルの形をしたビームであることができる。一実施形態では、レーザ光源は、約300 kHz ~ 10 MHzの範囲内のパルス繰り返し数を有するが、好ましくは、500 kHz ~ 5 MHzの範囲内である。一実施形態では、レーザ光源は、作業面で約0.5 μJ ~ 100 μJの範囲内のパルスエネルギーを送出するが、好ましくは約1 μJ ~ 5 μJの範囲内である。一実施形態では、レーザスクライビングプロセスは、ワークピース表面に沿って約500 mm / 秒 ~ 5 m / 秒の範囲内の速度で走るが、好ましくは、約600 mm / 秒 ~ 2 m / 秒の範囲内である。

#### 【0036】

スクライビングプロセスは、単一のパスのみ、又は複数のパスで実行可能であるが、有利なことには2パスだけである。レーザは、特定のパルス繰り返し数の単一パルス列又はパルスバーストの列のいずれかで印加することができる。一実施形態では、生成されたレーザ光の切り口の幅は、約2 μm ~ 15 μmの範囲内であるが、シリコン基板のスクライビング / ダイシングでは、デバイス / シリコン界面で測定されたときに、好ましくは約6 μm ~ 10 μmの範囲内である。

#### 【0037】

図1及び図4Cに戻って、基板406は、パターニングされたマスク層402内のトレチ412を貫通してエッチングされ、IC426を個片化する。本発明の一実施形態によると、基板406をエッチングすることは、図4Cに示されるように、フェムト秒ベースのレーザスクライビングプロセスによって形成されたトレチ412をエッチングして、最終的に基板406を完全に貫通してエッチングすることを含む。

#### 【0038】

一実施形態では、基板406をエッチングすることは、プラズマエッチングプロセスを使用することを含む。一実施形態では、スルービアエッチングプロセスが使用される。例えば、特定の一実施形態では、基板406の材料のエッチング速度は、毎分25 μmよりも大きい。高出力で稼働する高密度プラズマ源は、プラズマエッチング操作105に対して使用することができる。典型的な出力は、3 kW ~ 6 kWの間の範囲である。

#### 【0039】

例示的な一実施形態では、基本的に正確なプロファイル制御と事実上スカラップの無い側壁を維持しながら、従来のシリコンのエッチング速度を約40%上回るエッチング速度で単結晶シリコン基板又は基板406をエッチングするのに、ディープシリコンエッチング（即ち、スルーシリコンビア（TSV）エッチング等）が使用される。水溶性マスク上での高出力の効果は、-10 ~ -15に冷却された静電チャック（ESC）を介して冷却電力を印加することを通して制御され、水溶性マスク層を100未満の温度に維持するが、好ましくはプラズマエッチングプロセスの期間を通して、70 ~ 80である。このような温度では、マスクの水溶性は有利に維持される。

#### 【0040】

特定の一実施形態では、プラズマエッチングは、複数のエッチングサイクルと時間の経過と共に交互に配置された複数の保護ポリマー堆積サイクルを伴う。デューティサイクルは、例示的なデューティサイクルを約1:1として、変えることができる。例えば、エッチングプロセスは、250 ms ~ 750 msの持続時間有する堆積サイクルと、250 ms ~ 750 msのエッチングサイクルを有することができる。堆積サイクルとエッチングサイクルの間に、エッチングプロセスの化学物質（例えば、例示的なシリコンエッチングの実施形態用にSF<sub>6</sub>を用いる）を、堆積プロセスの化学物質（重合C<sub>x</sub>F<sub>y</sub>ガスを用いる（例えば、C<sub>4</sub>F<sub>6</sub>又はC<sub>4</sub>F<sub>8</sub>が挙げられるが、これらに限定されない））に入れ替える。当技術分野で知られているように、更にプロセス圧力を、エッチングサイクルと堆積サイクルの間に、特定のサイクルで各々が有利に働くように変更することができる。

#### 【0041】

操作107では、方法300は、マスク層402の除去によって完了する。一実施形態では、水溶性マスクは、水で洗い流され、例えば、周囲温度又は加熱された水浴中で、脱イオン水の加圧されたジェット又は浸漬によって洗い流される。代替実施形態では、マス

10

20

30

40

50

ク層402は、脱イオン水のpHよりも低いpHによって増強された除去速度を有する当該技術分野で公知の水性溶媒の溶液で洗い流してもよい。更に、図4Dに示されるよう、プラズマ個片化プロセス又はマスク除去プロセスのいずれかは、ダイ取り付け膜908を更にパターニングして、パッキングテープ910の頂部を露出させることができる。

#### 【0042】

単一のプロセスツール600は、ハイブリッドレーザアブレーションプラズマエッティング個片化プロセス100内の多くの又はすべての操作を実行するように構成することができる。例えば、図6は、本発明の一実施形態に係る、基板のレーザ・プラズマダイシング用レーザスクライプ装置610と結合されたクラスタツール606のブロック図を示す。図6を参照すると、クラスタツール606は、複数のロードロック604を有するファクトリインターフェース602(FI)に結合される。ファクトリインターフェース602は、レーザスクライプ装置610を有する外部製造施設とクラスタツール606との間をインターフェース接続するのに適した大気ポートであることが可能である。ファクトリインターフェース602は、基板(又はそのキャリア)を格納ユニット(例えば、正面開口式カセット一体型搬送・保管箱(FOUP))からクラスタツール606又はレーザスクライプ装置610のいずれか又はその両方へ搬送するためのアーム又はブレードを備えたロボットを含むことができる。

#### 【0043】

レーザスクライプ装置610はまた、FI602に結合される。一実施形態では、レーザスクライプ装置610は、フェムト秒レーザを含む。フェムト秒レーザは、ハイブリッドレーザ・エッティング個片化プロセス100のレーザアブレーション部を実行する。一実施形態では、可動ステージも、レーザスクライプ装置610に含まれ、可動ステージは、フェムト秒ベースのレーザに対して基板又は基板(又はそのキャリア)を移動させるために構成されている。特定の実施形態では、フェムト秒レーザも移動可能である。

#### 【0044】

クラスタツール606は、基板の真空中での搬送のためのロボットアーム650を収容したロボット搬送チャンバ650によってFIに結合された1以上のプラズマエッティングチャンバ608を含む。プラズマエッティングチャンバ608は、ハイブリッドレーザ・エッティング個片化プロセス100のプラズマエッティング部分を実行するのに適している。例示的な一実施形態では、プラズマエッティングチャンバ608は更に、SF<sub>6</sub>ガス源と、C<sub>4</sub>F<sub>8</sub>とC<sub>4</sub>F<sub>6</sub>源の少なくとも一方に結合される。特定の一実施形態では、1以上のプラズマエッティングチャンバ608は、米国カリフォルニア州サニーベールのアプライドマテリアルズ(Applied Materials)から入手可能なApplied Centura(商標名) Silvi(商標名) Etchシステムであるが、他の適当なエッティングシステムは市販されている。一実施形態では、複数のプラズマエッティングチャンバ608が統合プラットフォーム600のクラスタツール606部に含まれ、これによって個片化又はダイシングプロセスの高い製造スループットを可能にする。

#### 【0045】

クラスタツール606は、ハイブリッドレーザアブレーションプラズマエッティング個片化プロセス100内の機能を実行するのに適した他のチャンバを含むことができる。図6に示される例示的な実施形態では、ウェットプロセスモジュール614がロボット搬送モジュール650に結合され、これによって基板をプラズマエッティングした後に、水溶性マスクの残りを洗い流す。ウェットプロセスモジュール614は、例えば、加圧されたウォータースプレージェット又は他の溶媒のディスペンサを含むことができる。

#### 【0046】

更に他の実施形態では、堆積モジュール612は、本明細書内に記載される水溶性マスク層を塗布するためのスピンドルコーティングモジュール又はラミネーションモジュールであることができる。スピンドルコーティングモジュールとして、堆積モジュール612は、真空中によってクランプするように用いられる回転可能なチャックを含むことができ、そうでなければ、フレーム上に取り付けられたパッキングテープ等のキャリア上に取り付けられた

10

20

30

40

50

薄化基板を含むことができる。ラミネーションモジュールとして、堆積モジュール 612 は、当該技術分野で公知のテープリール・ウェハテーピング機構を含むことができる。

【0047】

図 7 は、少なくとも 1 つのマイクロマシンアーチファクトを識別するタグからの反射光を分析するために、本明細書内で議論された 1 以上のスクリーニング法をマシンに実行させるための命令セットを実行することができるコンピュータシステム 700 を示す。例示的なコンピュータシステム 700 は、プロセッサ 702、メインメモリ 704（例えば、リードオンリーメモリ（ROM）、フラッシュメモリ、ダイナミックランダムアクセスメモリ（DRAM）（例えば、シンクロナスDRAM（SDRAM）又はラムバスDRAM（RDRAM）等）、静态RAM（SRAM）等）、及び二次メモリ 718（例えば、データ記憶装置）を含み、これらはバス 730 を介して互いに通信する。

【0048】

プロセッサ 702 は、1 以上の汎用処理装置（例えば、マイクロプロセッサ、中央処理装置等）を表す。より具体的には、プロセッサ 702 は、複合命令セットコンピューティング（CISC）マイクロプロセッサ、縮小命令セットコンピューティング（RISC）マイクロプロセッサ、超長命令語（VLIW）マイクロプロセッサ等であることができる。プロセッサ 702 は、1 以上の特殊目的処理装置（例えば、特定用途向け集積回路（ASIC）、フィールドプログラマブルゲートアレイ（FPGA）、デジタル信号プロセッサ（DSP）、ネットワークプロセッサ等）であることも可能である。プロセッサ 702 は、本明細書に記載の操作及び手順を実行するための処理ロジック 726 を実行するよう構成される。

【0049】

コンピュータシステム 700 は更に、ネットワークインターフェースデバイス 708 を含むことができる。コンピュータシステム 700 は、ビデオディスプレイユニット 710（例えば、液晶ディスプレイ（LCD）又は陰極線管（CRT））、英数字入力装置 712（例えば、キーボード）、カーソル制御装置 714（例えば、マウス）、及び信号生成装置 716（例えば、スピーカ）も含むことができる。

【0050】

二次メモリ 718 は、本明細書に記載の 1 以上 の方法又は機能の何れかを具現化する 1 以上の命令セット（例えば、ソフトウェア 722）を格納するマシンアクセス可能な記憶媒体（又は、より具体的には、可読記憶媒体）731 を含むことができる。ソフトウェア 722 はまた、コンピュータシステム 700、メインメモリ 704 及びプロセッサ 702（これらもまたマシン可読記憶媒体を構成している）によるその実行中に、メインメモリ 704 及び / 又はプロセッサ 702 内に、完全に又は少なくとも部分的に常駐することもできる。ソフトウェア 722 は更に、ネットワークインターフェースデバイス 708 を介してネットワーク 720 上で送信又は受信されることができる。

【0051】

マシンアクセス可能な記憶媒体 731 は、パターン認識アルゴリズム、アーチファクト形状データ、アーチファクト位置データ、又は粒子の輝きデータを格納するために使用することができる。マシンアクセス可能な記憶媒体 731 は、例示的な一実施形態では単一の媒体であることが示されているが、用語「マシン可読記憶媒体」は、1 以上の命令セットを格納する単一の媒体又は複数の媒体（例えば、集中型又は分散型データベース、及び / 又は関連するキャッシュ及びサーバ）を含むように解釈されるべきである。用語「マシン可読記憶媒体」はまた、マシンによる実行用命令セットを格納又はエンコードすることができ、本発明の 1 以上 の方法の何れかをマシンに実行させる任意の媒体を含むようにも解釈されるべきである。従って、用語「マシン可読記憶媒体」は、固体メモリ、光学メディア及び磁気メディアを含むが、これらに限定されないように解釈されるべきである。

【0052】

このように、半導体基板をダイシングする方法であって、各基板が複数の IC を有する

方法が開示されている。要約書に記載されていることを含む本発明の例示的な実施形態の上記説明は、網羅的であること又は開示された正確な形態に本発明を限定するものではない。本発明の特定の実施及び本発明に対する実施例は、例示の目的で本明細書内に記載されているが、当業者が認識すると思われるよう、様々な等価な修正形態が本発明の範囲内で可能である。従って、本発明の範囲は、請求項解釈の確立された原則に従って解釈されるべきである以下の特許請求の範囲によって完全に決定されるべきである。

【図1】

【図2A】

FIG. 1

FIG. 2A

【図 2 B】

FIG. 2B

【図 3 A】

FIG. 3A

【図 3 B】

FIG. 3B

【図 4 A】

FIG. 4A

【図 4 B】

FIG. 4B

【図 4 C】

FIG. 4C

【図 4 D】

FIG. 4D

【図 5】

FIG. 5

【図 6】

FIG. 6

【図 7】

FIG. 7

---

フロントページの続き

(72)発明者 シン サラブジート

アメリカ合衆国 カリフォルニア州 95051 サンタ クララ カイリー ブルバード 10

00 #74

(72)発明者 ヤラマンチリ マドハバ ラオ

アメリカ合衆国 カリフォルニア州 95037 モルガン ヒル アベニダ デ ロス パドレ

ス 1660

(72)発明者 イートン ブラッド

アメリカ合衆国 カリフォルニア州 94025 メンロ パーク エイス アベニュー 563

(72)発明者 クマー アジャイ

アメリカ合衆国 カリフォルニア州 95014 クバチーノ マンザニタ コート 10457

合議体

審判長 平岩 正一

審判官 西村 泰英

審判官 篠原 将之

(56)参考文献 特開2006-253402 (JP, A)

特開2005-74485 (JP, A)

特開2002-26039 (JP, A)

特開2005-303191 (JP, A)

特開2001-298010 (JP, A)

特表2006-511963 (JP, A)

藤田雅之、橋田昌樹、フェムト秒レーザー加工、J. Plasma Fusion Res.、日本、2005年発行、Vol. 81, Suppl. 195-201

(58)調査した分野(Int.Cl., DB名)

H01L 21/00