(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-156716

(P2006-156716A)

(43) 公開日 平成18年6月15日(2006.6.15)

|                                      |                              |          |                                                 |

|--------------------------------------|------------------------------|----------|-------------------------------------------------|

| (51) Int.CI.                         | F 1                          |          | テーマコード (参考)                                     |

| <b>H01L 21/768</b> (2006.01)         | H01L 21/90                   | A        | 4K029                                           |

| <b>C23C 14/34</b> (2006.01)          | C23C 14/34                   | R        | 4K030                                           |

| <b>C23C 16/06</b> (2006.01)          | C23C 16/06                   |          | 4M104                                           |

| <b>H01L 21/28</b> (2006.01)          | H01L 21/28                   | 301R     | 5F033                                           |

| <b>H01L 21/285</b> (2006.01)         | H01L 21/285                  | S        |                                                 |

| 審査請求 未請求 請求項の数 7 O L (全 14 頁) 最終頁に続く |                              |          |                                                 |

| (21) 出願番号                            | 特願2004-345349 (P2004-345349) | (71) 出願人 | 503121103<br>株式会社ルネサステクノロジ<br>東京都千代田区丸の内二丁目4番1号 |

| (22) 出願日                             | 平成16年11月30日 (2004.11.30)     | (74) 代理人 | 100089233<br>弁理士 吉田 茂明                          |

|                                      |                              | (74) 代理人 | 100088672<br>弁理士 吉竹 英俊                          |

|                                      |                              | (74) 代理人 | 100088845<br>弁理士 有田 貴弘                          |

|                                      |                              | (72) 発明者 | 一之瀬 一仁<br>東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内      |

|                                      |                              | (72) 発明者 | 油谷 明栄<br>東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内       |

|                                      |                              |          | 最終頁に続く                                          |

(54) 【発明の名称】半導体装置およびその製造方法

## (57) 【要約】

【課題】アルミ配線層間をタングステンプラグによって電気的に接続する構成において、スルーホール内面全面にバリアメタル層が形成され、タングステンプラグとアルミ配線層との電気的接続の信頼性が高く、接触抵抗が低い半導体装置を提供することを目的とする。

【解決手段】スルーホール9の内面にチタン膜10および窒化チタン膜11の2層構造で構成されるバリアメタル層を形成する。なお、チタン膜10および窒化チタン膜11は、層間絶縁膜7の主面上にも形成される。このバリアメタル層の形成に際しては、チタンターゲットを用いた高指向性スパッタリングが可能で、かつ、高周波電圧を半導体基板にバイアスする基板バイアス機構を備え、チタンターゲットからのスパッタ粒子を半導体基板に引き付けることで、窒化チタン膜11をアモルファス金属膜とすることが可能となる。

【選択図】図3

10 : チタン膜

11 : 窒化チタン膜

**【特許請求の範囲】****【請求項 1】**

多層配線構造を有する半導体装置であって、

半導体基板上に配設された多層配線層と、

前記多層配線層のうち、アルミ配線層で構成される下層配線層と上層配線層との間に配設された層間絶縁膜と、

前記層間絶縁膜を貫通し、前記下層配線層と前記上層配線層とを電気的に接続するコンタクト部と、を備え、

前記コンタクト部は、

前記層間絶縁膜を貫通して前記下層配線層上に到達するスルーホールと、

前記スルーホールの内面に沿って配設されたバリアメタル層と、

前記バリアメタル層で規定される前記スルーホール内に充填されたタングステンプラグとを有し、

前記バリアメタル層は、アモルファス金属膜を含む、半導体装置。

**【請求項 2】**

前記バリアメタル層は、チタン膜と窒化チタン膜との2層構造を有し、

前記チタン膜の上に前記窒化チタン膜が配設され、

少なくとも前記窒化チタン膜はアモルファスである、請求項1記載の半導体装置。

**【請求項 3】**

前記バリアメタル層は、タングステン膜と窒化タングステン膜との2層構造を有し、少なくとも1方がアモルファスである、請求項1記載の半導体装置。

**【請求項 4】**

前記バリアメタル層は、前記窒化タングステン膜の上に前記タングステン膜が配設され、

少なくとも前記窒化タングステン膜はアモルファスである、請求項3記載の半導体装置。

**【請求項 5】**

前記バリアメタル層は、アモルファスのタングステン膜あるいはアモルファスの窒化タングステン膜で構成される単層構造である、請求項1記載の半導体装置。

**【請求項 6】**

前記スルーホールは、その底面の一部が前記下層配線層上からずれ、前記スルーホールの側面の一部に前記下層配線層の側面の一部が露出し、

前記バリアメタル層は、前記スルーホールの底面および前記スルーホールの側面に露出する前記下層配線層の側面上を均一に覆うように配設される、請求項1記載の半導体装置。

**【請求項 7】**

半導体基板上に配設された多層配線層と、前記多層配線層のうち、アルミ配線層で構成される下層配線層と上層配線層との間に配設された層間絶縁膜と、前記層間絶縁膜を貫通し、前記下層配線層と前記上層配線層とを電気的に接続するコンタクト部とを備えた多層配線構造を有する半導体装置の製造方法であって、

- (a)前記下層配線層を覆うように前記層間絶縁膜を形成する工程と、

- (b)前記層間絶縁膜を貫通して前記下層配線層上に到達するスルーホールを形成する工程と、

- (c)前記スルーホールの内面に沿うようにバリアメタル層を形成する工程と、

- (d)前記バリアメタル層で規定される前記スルーホール内にタングステンプラグを形成する工程と、

(e)前記タングステンプラグに接続されるように、前記層間絶縁膜上に前記上層配線層を形成する工程と、を備え、

前記工程(c)は、

D C マグネットロンスパッタを用いて前記金属バリアメタル層の金属材料をスパッタリン

10

20

30

40

50

グしてスパッタ粒子を生成するとともに、前記半導体基板に高周波電圧をバイアスして、前記スパッタ粒子を前記半導体基板に引きつけることで前記バリアメタル層を形成する工程を含み、

前記D C マグнетロンスパッタのD C パワーは1 ~ 4 0 k W、

成膜温度は室温 ~ 4 0 0 ℃ とし、

前記半導体基板に与える高周波のパワーは1 k W以下とし、

前記工程(d)は、

前記バリアメタル層で規定される前記スルーホール内にC V Dによりタンゲステン膜を充填する工程を含む、半導体装置の製造方法。

【発明の詳細な説明】

10

【技術分野】

【0 0 0 1】

本発明は半導体装置およびその製造方法に関し、特にアルミ配線層の多層配線構造を有し、アルミ配線層間をタンゲステンプラグによって電気的に接続する半導体装置およびその製造方法に関する。

【背景技術】

【0 0 0 2】

多層配線構造を有する半導体装置として、アルミ配線層間をタンゲステンプラグによって電気的に接続する構成が知られている。

【0 0 0 3】

20

多層配線構造とは、半導体基板上に設けた層間絶縁膜を間に挟んで、上下に配線層が配設された構造を上下方向に複数備えた構成である。

【0 0 0 4】

そして、配線層としてはアルミ配線層を使用することが多く、上下のアルミ配線層間を電気的に接続するために、層間絶縁膜を貫通するスルーホール内にタンゲステン層を充填して形成されたタンゲステンプラグを使用することが近年行われている。

【0 0 0 5】

しかし、近年の半導体装置の微細化に伴い、配線パターンが高密度化しており、層間絶縁膜にスルーホールを設ける際のフォトリソグラフィ工程において、マスク位置合わせのずれに起因して、スルーホールの形成位置が下層の配線層上からずれる、いわゆる「目外れ」が発生することが避けられない事態となってきた。

30

【0 0 0 6】

目外れを防止するには配線幅を広げれば良いが、それは半導体装置の小型化逆行することになる。

【0 0 0 7】

また、目外れの防止には、スルーホールを縮小することも有効であるが、配線層との接触面積の減少につながり、接触抵抗が増大するので、これも望ましくない。

【0 0 0 8】

40

このように、配線パターンが高密度化した半導体装置においては、目外れの発生を避けることが困難であり、最近では逆に、目外れを許容する設計も実行されつつある。

【0 0 0 9】

すなわち、半導体装置の設計において、例えば、フォトリソグラフィ工程におけるマスク位置合わせマージンを小さくし、制御された範囲で目外れが起きる可能性を高める設計を行う。ここで、制御された範囲とは、目外れが起きた場合でも、スルーホールが完全に配線層上から外れることはなく、少なくとも一部が配線層上に位置するようマスク位置合わせマージンを設定することを意味する。

【0 0 1 0】

このような制御された範囲での目外れが起きると、スルーホールの底面の一部に配線層の上面が露出し、スルーホールの側面に配線層の側面が露出することになり、そこにタンゲステン層を充填すると、配線層とタンゲステン層との接触面積を目外れが起きない場合

50

と、同等かそれ以上に確保することが可能となる。

【0011】

ここで、配線層としてアルミ配線層を使用し、タンゲステンプラグにより配線層間の電気的接続を行う場合、例えば、特許文献1で示されるように、スルーホール内面（側面および底面を含む）にチタン膜と窒化チタン膜との2層構造のバリアメタル層を形成することが従来的に行われている。

【0012】

特許文献1では、チタン膜および窒化チタン膜の形成にスパッタリング法を使用することが開示されているが、スパッタリング法では、スルーホールのアスペクト比が2以上になると、スルーホールの底面にはバリアメタル層を形成できるものの、側面にはバリアメタル層が形成されにくいとされている。

【0013】

このことは、スルーホールの目外れが発生した場合に、スルーホールの側面に露出する配線層の側面上にバリアメタル層が形成されない可能性が高くなることを意味している。

【0014】

ここで、スルーホール内に充填されるタンゲステン膜はCVD (chemical vapor deposition) で形成されるが、バリアメタル層が形成されない状態でタンゲステン膜の形成を行うと、タンゲステン膜の形成に使用される六フッ化タンゲステン( $WF_6$ )と配線層のアルミニウムとが反応し、フッ化アルミニウム( $AlF_3$ )が生成され、ボイドが発生する原因となる。ボイドが発生すると、タンゲステンプラグとアルミ配線層との電気的接続の信頼性の低下や、接触抵抗の増加を引き起こすことが特許文献1に記載されている。

【0015】

また、非特許文献1には、フッ素(F)はチタンと反応しやすく、フッ化チタン( $TiF_3$ 、 $TiF_4$ )が生成されると、チタン膜と窒化チタン膜との接着力が低下して剥離を起こしやすいことが報告されている。

【0016】

【特許文献1】特開2003-303881号公報（段落0002～0008）

【非特許文献1】Tadashi Ide and Haruko Tamegai著、「ナノメータスケールマテリアルアナライシスユージングフーリエトランスマッピング(Nanometer scale material analysis using Fourier Transform Mapping)」ISSM2000 プロシードィング p 265-268

【発明の開示】

【発明が解決しようとする課題】

【0017】

以上説明したように、従来の半導体装置においては、スルーホール内にバリアメタル層が形成されない部分が存在する可能性を有し、当該部分に起因して、タンゲステンプラグとアルミ配線層との電気的接続の信頼性の低下や、接触抵抗の増加を引き起こすという問題があった。

【0018】

本発明は上記のような問題点を解消するためになされたもので、アルミ配線層間をタンゲステンプラグによって電気的に接続する構成において、スルーホール内面全面にバリアメタル層が形成され、タンゲステンプラグとアルミ配線層との電気的接続の信頼性が高く、接触抵抗が低い半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0019】

本発明に係る請求項1記載の半導体装置は、多層配線構造を有する半導体装置であって、半導体基板上に配設された多層配線層と、前記多層配線層のうち、アルミ配線層で構成される下層配線層と上層配線層との間に配設された層間絶縁膜と、前記層間絶縁膜を貫通し、前記下層配線層と前記上層配線層とを電気的に接続するコンタクト部と、を備え、前記コンタクト部は、前記層間絶縁膜を貫通して前記下層配線層上に到達するスルーホール

10

20

30

40

50

と、前記スルーホールの内面に沿って配設されたバリアメタル層と、前記バリアメタル層で規定される前記スルーホール内に充填されたタンゲステンプラグとを有し、前記バリアメタル層は、アモルファス金属膜を含んでいる。

#### 【0020】

本発明に係る請求項7記載の半導体装置の製造方法は、半導体基板上に配設された多層配線層と、前記多層配線層のうち、アルミ配線層で構成される下層配線層と上層配線層との間に配設された層間絶縁膜と、前記層間絶縁膜を貫通し、前記下層配線層と前記上層配線層とを電気的に接続するコンタクト部とを備えた多層配線構造を有する半導体装置の製造方法であって、前記下層配線層を覆うように前記層間絶縁膜を形成する工程(a)と、前記層間絶縁膜を貫通して前記下層配線層上に到達するスルーホールを形成する工程(b)と、前記スルーホールの内面に沿うようにバリアメタル層を形成する工程(c)と、前記バリアメタル層で規定される前記スルーホール内にタンゲステンプラグを形成する工程(d)と、前記タンゲステンプラグに接続されるように、前記層間絶縁膜上に前記上層配線層を形成する工程(e)とを備え、前記工程(c)は、DCマグネットロンスパッタを用いて前記金属バリアメタル層の金属材料をスパッタリングしてスパッタ粒子を生成するとともに、前記半導体基板に高周波電圧をバイアスして、前記スパッタ粒子を前記半導体基板に引きつけることで前記バリアメタル層を形成する工程を含み、前記DCマグネットロンスパッタのDCパワーは1～40kW、成膜温度は室温～400とし、前記半導体基板に与える高周波のパワーは1kW以下とし、前記工程(d)は、前記バリアメタル層で規定される前記スルーホール内にCVDによりタンゲステン膜を充填する工程を含んでいる。

10

20

30

40

#### 【発明の効果】

#### 【0021】

本発明に係る請求項1記載の半導体装置によれば、スルーホールの内面に沿って配設されたバリアメタル層がアモルファス金属膜を含むので、タンゲステンプラグの形成にCVDを使用する場合、発生するWF<sub>6</sub>やフッ素の拡散がアモルファス金属膜によって防止され、下層配線層のアルミニウムと反応してAlF<sub>3</sub>が生成されることが防止されるので、下層配線層とタンゲステンプラグとの電気的接続の信頼性が高く、接触抵抗を低く保つことができる。

#### 【0022】

本発明に係る請求項7記載の半導体装置の製造方法によれば、バリアメタル層の形成に際して、DCマグネットロンスパッタを用いて金属バリアメタル層の金属材料をスパッタリングしてスパッタ粒子を生成するとともに、半導体基板に高周波電圧をバイアスして、スパッタ粒子を半導体基板に引きつけるので、バリアメタル層をアモルファス金属膜にすることができるとともに、スルーホールのアスペクト比が大きい場合でもスルーホールの側面にも均一に形成することができる。従って、タンゲステンプラグの形成時に発生するWF<sub>6</sub>やフッ素の拡散がアモルファス金属膜によって防止され、下層配線層のアルミニウムと反応してAlF<sub>3</sub>が生成されることが防止されるので、下層配線層とタンゲステンプラグとの電気的接続の信頼性が高く、接触抵抗が低い半導体装置を得ることができる。

#### 【発明を実施するための最良の形態】

#### 【0023】

##### <実施の形態>

本発明の実施の形態について、図1～図7を用いて説明する。なお、図1～図7は製造工程を順に示す断面図であり、最終工程を説明する図7において示される構成が、本発明に係る半導体装置100の発明関連部分を示している。

#### 【0024】

以下、図1～図7を参照して半導体装置100の製造方法を説明しつつ、本発明の特徴について説明する。

図1に示す工程において、図示しない半導体基板上にトランジスタ等の半導体素子を形成した後、当該半導体基板および半導体素子を覆うように層間絶縁膜1を形成する。

#### 【0025】

50

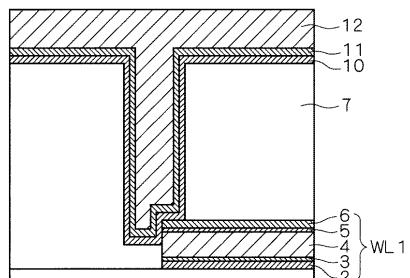

そして、層間絶縁膜 1 上にスパッタリング法で、チタン膜 2、窒化チタン膜 3、アルミニウムを主成分とした銅との合金膜等で構成されるアルミニウム膜 4、チタン膜 5 および窒化チタン膜 6 を順次成膜して多層金属膜を形成した後、その上にフォトリソグラフィ工程で所望の配線パターンを有するレジストマスク（図示せず）を形成する。

【0026】

その後、当該レジスト膜を用いて、ドライエッチングにより多層金属膜をパターニングすることでアルミ配線層 WL 1 を得る。なお、アルミ配線層 WL 1 を下層配線層と呼称する場合もある。

【0027】

アルミ配線層 WL 1 を形成した後、アルミ配線層 WL 1 上および層間絶縁膜 1 上を覆うように層間絶縁膜 7 を形成する。 10

【0028】

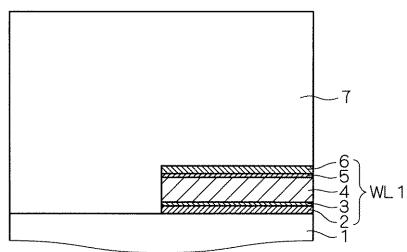

次に、図 2 に示す工程において、層間絶縁膜 7 上にレジスト材を塗布し、フォトリソグラフィ工程を経て、所定のスルーホールパターンを有するレジストマスク RM 1 を形成する。

【0029】

そして、当該レジストマスク RM 1 を用いてドライエッチングにより層間絶縁膜 7 を選択的にエッチングすることでスルーホール 9 を形成する。

【0030】

ここで、レジストマスク RM 1 の形成に際しては、露光マスクの位置合わせマージンが小さく設定され、制御された範囲でスルーホール 9 の形成位置がアルミ配線層 WL 1 上からずれる、いわゆる「目外れ」が起きやすいようになっている。 20

【0031】

従って、図 2 に示されるように、スルーホール 9 の底面位置がアルミ配線層 WL 1 上からずれ、スルーホール 9 の底面の一部に窒化チタン膜 6 の上面が露出し、スルーホール 9 の側面の一部に窒化チタン膜 6、チタン膜 5 およびアルミニウム膜 4 の側面が露出している。なお、アルミ配線層 WL 1 の側面が露出している部分をスリット部と呼称する場合もある。

【0032】

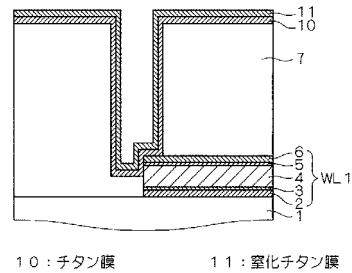

次に、レジストマスク RM 1 をアッシングによって除去した後、図 3 に示す工程において、スルーホール 9 の内面にチタン膜 10 および窒化チタン膜 11 の 2 層構造で構成されるバリアメタル層を形成する。なお、チタン膜 10 および窒化チタン膜 11 は、層間絶縁膜 7 の主面上にも形成される。 30

【0033】

このバリアメタル層の形成に際しては、チタンターゲットを用いた高指向性スパッタリングが可能で、かつ、高周波電圧を半導体基板にバイアスする基板バイアス機構を備え、チタンターゲットからのスパッタ粒子を半導体基板に引き付けることが可能な成膜装置を用いる。

【0034】

ここで、チタンターゲットのスパッタリングには、DC マグнетロンスパッタを用いる。 40

【0035】

DC マグネットロンスパッタは、金属ターゲットに印加される DC ( 直流 ) 電圧と、金属ターゲットに平行に形成される磁場とで電子に  $E \times B$  ドリフトを発生させて、高密度のプラズマを生成し、プラズマ中のイオンによって金属ターゲットをスパッタする構成となっている。

【0036】

このような DC マグネットロンスパッタを用いた高指向性スパッタリングを行うとともに、高周波電圧を半導体基板に印加してバイアスを与え、スパッタ粒子を半導体基板に積極的に引き付けることで窒化チタン膜 11 をアモルファス金属膜とすることが本発明の特徴

の1つである。

#### 【0037】

すなわち、高指向性スパッタリングを用いてバリアメタル層を形成する従来の方法では、スルーホールのアスペクト比が2以上となった場合には、スルーホールの側面にバリアメタル層を形成しにくく、特に、スルーホールの目外れが発生した場合には、スリット部（配線層の側面が露出している部分）に均一にバリアメタル層を形成することが難しかった。

#### 【0038】

また、スリット部にバリアメタル層を形成できたとしても、窒化チタン膜は結晶性の膜であり、タンゲステン膜の形成に使用される六フッ化タンゲステン( $WF_6$ )が結晶粒界に沿って拡散し、フッ素(F)がアルミ配線層と反応するという問題があった。

#### 【0039】

しかし、アモルファスである窒化チタン膜11は、結晶粒界を有さないので、 $WF_6$ やフッ素の拡散防止膜として機能する。また、本願が対象とする半導体装置では、スルーホール9のアスペクト比が4以上となる場合があるが、スパッタ粒子を半導体基板に積極的に引き付けて形成される窒化チタン膜11やチタン膜10は、スルーホール9のアスペクト比が大きい場合でもスルーホール9の側面にも均一に形成され、スルーホール9の目外れが発生した場合でも、スリット部に均一にバリアメタル層を形成することが可能である。

#### 【0040】

従って、後のタンゲステンプラグの形成時に、 $WF_6$ やフッ素がアルミ配線層WL1のアルミニウムと反応して $AlF_3$ が生成されることが防止され、アルミ配線層WL1と後に形成されるタンゲステンプラグとの電気的接続の信頼性の低下や、接触抵抗の増加を防止できる。

#### 【0041】

また、フッ素はチタンと反応しやすいが、アモルファスである窒化チタン膜11がチタン膜10上を覆っているので、フッ素が拡散してチタン膜10に到達することが防止され、チタン膜10と窒化チタン膜11との接着力が低下して剥離することが防止される。

#### 【0042】

ここで、チタン膜10および窒化チタン膜11の形成条件の一例を説明する。

金属ターゲットとしてチタンターゲットを用い、DCマグネットロンスパッタのDCパワーとして1~40kWとする。また、半導体基板に与える高周波のパワーは0~1kWとし、半導体基板を搭載するステージの温度、すなわち成膜温度は室温~400とする。なお、高周波のパワーが0である場合はスパッタ粒子を半導体基板に積極的に引き付けるという効果は期待できないが、限りなく0に近いパワーを印加する場合もあり得るので、上記範囲を開示している。なお、上記パラメータの例示した範囲内での組み合わせによりチタン膜10および/または窒化チタン膜11をアモルファスにすることができる。

#### 【0043】

上記条件下において、チタン膜10の形成に際しては、一旦、真空状態にしたプロセス室内にアルゴンガスを導入し、プロセス室内の圧力を0.4~1.0Pa(パスカル)の範囲で制御して、半導体基板上の膜厚の均一性が最も良好になる条件を選択する。

#### 【0044】

また、窒化チタン膜11の形成に際しては、プロセス室内に窒素とアルゴンの混合ガスを導入し、プロセス室内の圧力を0.4~1.0Paの範囲で制御する。このとき、窒素の流量は、混合ガスの流量の50%以上となるように制御を行い、半導体基板上の膜厚の均一性が最も良好になる条件を選択する。

#### 【0045】

なお、上記条件では、チタン膜10も半導体基板に高周波バイアスを与えて形成するのでアモルファスとなるが、チタン膜10は必ずしもアモルファスでなくても良い。

#### 【0046】

10

20

30

40

50

また、上述したように、本願では金属元素の供給にDCマグネットロンスパッタを用いており、物理的堆積法いわゆるPVD (physical vapor deposition)により金属膜の成膜を行っているが、PVDを用いることは他の方法を使用する場合に比べて以下の点で有利である。

#### 【0047】

すなわち、CVDによりスルーホール内に窒化チタン膜を形成する場合、TiCl<sub>4</sub>-TiNを原料ガスとして用いるが、この場合の成膜温度は600以上となるため、アルミニ配線層に係合するスルーホールの内面に窒化チタン膜を形成するには不適当である。しかし、上述したPVDであれば、ステージの温度、室温～400の範囲であるので、アルミニ配線層WL1に影響を与えることはない。

10

#### 【0048】

また、成膜温度が450以下であるTDMAT (tetrakis dimethyl amino titanium)を用いてMOCVD (metal organic CVD)により窒化チタン膜を形成した場合、次にスルーホール内に充填するタンゲステン膜をCVDにより成膜する際に、MOCVDで形成した窒化チタン膜中に含まれる不純物がガスとして放出され、タンゲステン膜が成長できない。しかし、上述したPVDであれば、窒化チタン膜11中には不純物を含まず、タンゲステン膜の成膜に支障を来すようなガス放出は起こらない。

#### 【0049】

なお、窒化チタン膜11は、WF<sub>6</sub>やフッ素の拡散防止膜として機能するだけでなく、タンゲステン膜の成膜に際しては成長のためのシード膜としても機能する。

20

#### 【0050】

ここで、再び、図を用いた製造方法の説明に戻る。

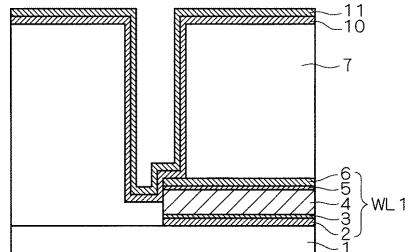

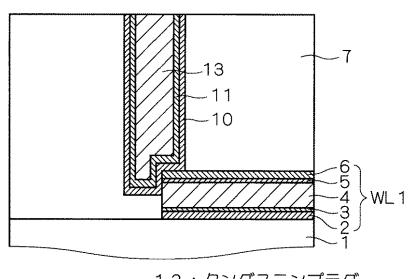

窒化チタン膜11を形成した後、図4に示すようにCVDにより、タンゲステン膜12を成膜し、スルーホール9内にタンゲステン膜12する充填する。なお、タンゲステン膜12は、層間絶縁膜7の主面上にも形成される。

#### 【0051】

その後、CMP (chemical mechanical polishing)により、層間絶縁膜7の主面上のタンゲステン膜12、窒化チタン膜11およびチタン膜10を除去し、層間絶縁膜7の主面を露出させることで、図5に示すように、スルーホール9内にタンゲステンプラグ13が埋め込まれた構成を得る。

30

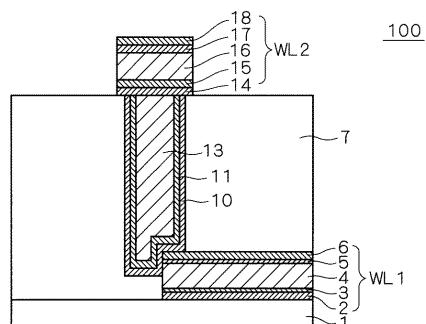

#### 【0052】

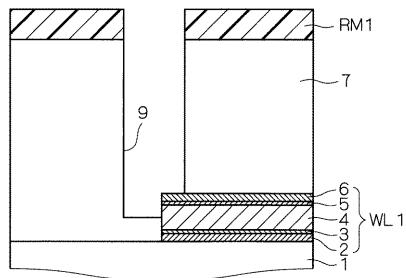

次に、図6に示す工程において、スパッタリング法で、チタン膜14、窒化チタン膜15、アルミニウムと銅の合金膜やアルミニウムの単体膜で構成されるアルミニウム膜16、チタン膜17および窒化チタン膜18を順次成膜して多層金属膜を形成した後、その上にフォトリソグラフィ工程で所望の配線パターンを有するレジストマスクRM2を形成する。

#### 【0053】

その後、当該レジスト膜RM2を用いて、ドライエッティングにより多層金属膜をパターンングすることで、図7に示すようにタンゲステンプラグ13に接続されるアルミニ配線層WL2を得る。なお、アルミニ配線層WL2を上層配線層と呼称する場合もある。なお、スルーホール9、チタン膜10、窒化チタン膜11およびタンゲステンプラグ13とで、下層配線層と上層配線層とが電気的に接続されるので、この部分をコンタクト部を総称する。

40

#### 【0054】

以後は、層間絶縁膜7上にさらに層間絶縁膜を形成し、図1～図7を用いて説明した工程と同様の工程により、アルミニ配線層WL2と、それよりもさらに上層のアルミニ配線層との電気的接続を行うタンゲステンプラグを形成するという動作を繰り返すことで、最終的な半導体装置100を得ることになる。なお、半導体装置100には、上述した多層配線層以外にも層間絶縁膜中に形成される構成も含んでおり、多層配線層の形成と併行してそれらの形成が行われるが、それらについては本発明との関係が薄いので、説明は省略する

50

。

## 【0055】

&lt;変形例1&gt;

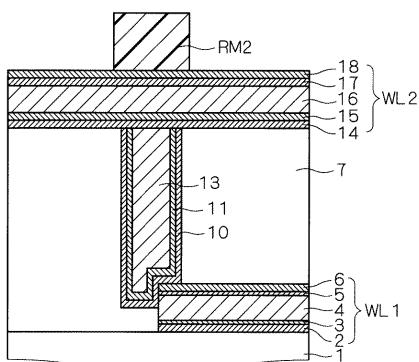

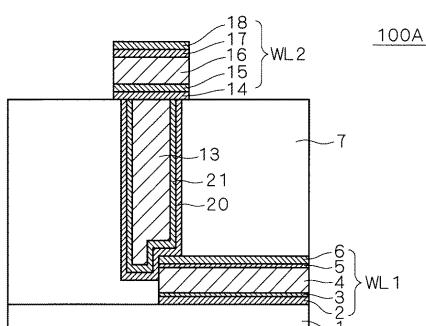

以上説明した本発明に係る実施の形態では、スルーホール9の内面にチタン膜10および窒化チタン膜11の2層構造で構成されるバリアメタル層を形成する例を示したが、これらの代わりに、図8に示す半導体装置100Aのように、窒化タンゲステン膜20およびタンゲステン膜21の2層構造を形成してバリアメタル層としても良い。

## 【0056】

ここで、窒化タンゲステン膜20およびタンゲステン膜21は、チタン膜10および窒化チタン膜11と同様にスパッタ粒子を半導体基板に積極的に引き付けることで形成されるので、共にアモルファスとなっている。

## 【0057】

そして、アモルファス金属膜である窒化タンゲステン膜20は、結晶粒界を有さないので、タンゲステンプラグ形成時に、WF<sub>6</sub>やフッ素の拡散防止膜として機能し、フッ素がバリアメタル層を通過してアルミ配線層WL1と反応してAlF<sub>3</sub>が生成されることが防止され、アルミ配線層WL1と後に形成されるタンゲステンプラグとの電気的接続の信頼性の低下や、接触抵抗の増加を防止できる。

## 【0058】

なお、タンゲステン膜21は、タンゲステンプラグ形成時にCVDによるタンゲステン膜の成長のためのシード膜となりやすいので、タンゲステン膜21を窒化タンゲステン膜20上に形成することで、タンゲステンプラグの成長をよりスムーズに行うことができる。

## 【0059】

ここで、窒化タンゲステン膜20およびタンゲステン膜21の形成条件の一例を説明する。

金属ターゲットとしてタンゲステンターゲットを用い、DCマグネットロンスパッタのDCパワーとして1~40kWとする。また、半導体基板に与える高周波のパワーは0~1kWとし、半導体基板を搭載するステージの温度は、室温~400とする。

## 【0060】

上記条件下において、窒化タンゲステン膜20の形成に際しては、プロセス室内に窒素とアルゴンの混合ガスを導入し、プロセス室内の圧力を0.4~1.0Paの範囲で制御する。このとき、窒素の流量は、混合ガスの流量の50%以上となるように制御を行い、半導体基板上の膜厚の均一性が最も良好になる条件を選択する。

## 【0061】

また、タンゲステン膜21の形成に際しては、一旦、真空状態にしたプロセス室内にアルゴンガスを導入し、プロセス室内の圧力を0.4~1.0Paの範囲で制御して、半導体基板上の膜厚の均一性が最も良好になる条件を選択する。

## 【0062】

なお、以上の説明では、スルーホール9の内面にまず窒化タンゲステン膜20を形成し、その上にタンゲステン膜21を形成するものとしたが、配設順序は逆であっても良い。

## 【0063】

すなわち、スルーホール9の内面にまずタンゲステン膜21を形成し、その上に窒化タンゲステン膜20を形成した構成であっても良い。この場合も、アモルファス金属膜である窒化タンゲステン膜20が、タンゲステンプラグ形成時にWF<sub>6</sub>やフッ素の拡散防止膜として機能し、フッ素がバリアメタル層を通過してアルミ配線層WL1と反応してAlF<sub>3</sub>が生成されることが防止されるという効果は変わらない。

## 【0064】

なお、窒化タンゲステン膜20は、CVDによるタンゲステン膜の成長のためのシード膜としても機能する。

## 【0065】

10

20

30

40

50

## &lt;変形例2&gt;

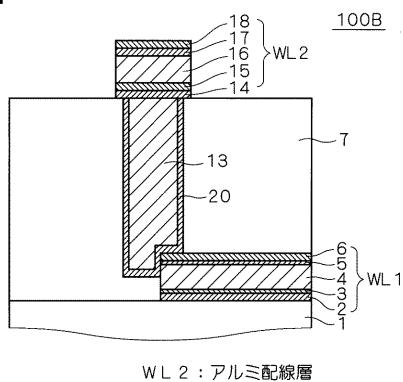

上述した変形例1において説明したスルーホール9内のバリアメタル層は、窒化タングステン膜20およびタングステン膜21の2層構造で構成されていたが、2層構造ではなく単層構造であっても良い。

## 【0066】

図9には、窒化タングステン膜20で構成される単層構造のバリアメタル層を備えた半導体装置100Bを示す。

## 【0067】

ここで、窒化タングステン膜20は、スパッタ粒子を半導体基板に積極的に引き付けることで形成されるのでアモルファスとなっている。

## 【0068】

そして、アモルファスである窒化タングステン膜20は、結晶粒界を有さないので、タングステンプラグ形成時に、WF<sub>6</sub>やフッ素の拡散防止膜として機能し、フッ素がバリアメタル層を通過してアルミ配線層WL1と反応してAlF<sub>3</sub>が生成されることが防止され、アルミ配線層WL1と後に形成されるタングステンプラグとの電気的接続の信頼性の低下や、接触抵抗の増加を防止できる。

## 【0069】

また、上記ではスルーホール内のバリアメタル層を窒化タングステン膜20の単層膜で構成することを説明したが、タングステン膜21の単層膜で構成しても良いことは言うまでもない。

## 【0070】

タングステン膜21は、スパッタ粒子を半導体基板に積極的に引き付けることで形成されるのでアモルファスとなっており、WF<sub>6</sub>やフッ素の拡散防止膜として機能する。

## 【0071】

## &lt;変形例3&gt;

以上説明した実施の形態では、スルーホール9内のバリアメタル層としてチタン膜10および窒化チタン膜11の2層構造を使用する構成を示し、変形例1では窒化タングステン膜20およびタングステン膜21の2層構造を使用する構成を示し、変形例2では、窒化タングステン膜20およびタングステン膜21のどちらかを使用する構成を示したが、使用する金属としてはこれらに限定されるものではない。

## 【0072】

すなわち、高融点金属であるバナジウム(V)、クロム(Cr)、ジルコニウム(Zr)、ニオブ(Nb)、モリブデン(Mo)、ルテニウム(Ru)、ハフニウム(Hf)、タンタル(Ta)およびレニウム(Re)のグループにおいて、このグループから選択される1つの金属と、その金属の窒化膜とで構成される2層構造によってスルーホール9内のバリアメタル層を構成しても良いし、上記グループから選択される1つの金属の単層膜によってスルーホール9内のバリアメタル層を構成しても良い。

## 【0073】

何れの金属を選択した場合でも、高指向性スパッタリングが可能で、かつ、高周波基板バイアス機構を備え、金属ターゲットからのスパッタ粒子を半導体基板に引き付けることが可能な成膜装置を用いることで、上述した実施の形態およびその変形例1および2と同様の効果を得ることができる。

## 【0074】

なお、成膜条件は、DCマグネットロンスパッタのDCパワーとして1~40kWとし、半導体基板に与える高周波のパワーは0~1kWとし、半導体基板を搭載するステージの温度は、室温~400とする。もちろん、ターゲット材には上記グループから選択した金属を用いることは言うまでもない。

## 【0075】

そして、上記条件下において、金属窒化膜を形成する場合は、プロセス室内に窒素とアルゴンの混合ガスを導入し、プロセス室内の圧力を0.4~1.0Paの範囲で制御する

10

20

30

40

50

。このとき、窒素の流量は、混合ガスの流量の50%以上となるように制御を行い、半導体基板上の膜厚の均一性が最も良好になる条件を選択する。

【0076】

また、金属膜の形成に際しては、一旦、真空状態にしたプロセス室内にアルゴンガスを導入し、プロセス室内の圧力を0.4~1.0Paの範囲で制御して、半導体基板上の膜厚の均一性が最も良好になる条件を選択する。

【0077】

上述した方法で形成された金属窒化膜および金属膜は、2層構造の場合はどちらか一方がアモルファスとなっていれば良いし、両方がアモルファスとなっていても良い。また、单層膜の場合は、何れの金属を用いる場合でも、アモルファスとする。

10

【図面の簡単な説明】

【0078】

【図1】本発明に係る実施の形態の半導体装置の製造工程を説明する断面図である。

【図2】本発明に係る実施の形態の半導体装置の製造工程を説明する断面図である。

【図3】本発明に係る実施の形態の半導体装置の製造工程を説明する断面図である。

【図4】本発明に係る実施の形態の半導体装置の製造工程を説明する断面図である。

【図5】本発明に係る実施の形態の半導体装置の製造工程を説明する断面図である。

【図6】本発明に係る実施の形態の半導体装置の製造工程を説明する断面図である。

【図7】本発明に係る実施の形態の半導体装置の構成を説明する断面図である。

20

【図8】本発明に係る実施の形態の半導体装置の変形例の構成を説明する断面図である。

【図9】本発明に係る実施の形態の半導体装置の変形例の構成を説明する断面図である。

【符号の説明】

【0079】

1, 7 層間絶縁膜、9 スルーホール、10 チタン膜、11 窒化チタン膜、20

窒化タングステン膜、12, 21 タングステン膜、13 タングステンプラグ、WL

1, WL2 アルミ配線層。

【図1】

1, 7 : 層間絶縁膜

WL 1 : アルミ配線層

【図3】

10 : チタン膜

11 : 窒化チタン膜

【図2】

9 : スルーホール

【図4】

12 : タングステン膜

【図5】

13 : タングステンプラグ

【図7】

【図6】

WL 2 : アルミ配線層

【図8】

20 : 窒化タングステン膜

21 : タングステン膜

【図9】

WL2 : アルミニ配線層

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

*H 01L 23/52 (2006.01)*

H 01L 21/88

R

*H 01L 21/3205 (2006.01)*

F ターム(参考) 4K029 AA06 AA24 BA17 BA23 BA60 BB02 BB10 BD02 CA05 CA06

CA13 EA08 EA09 GA03

4K030 BA20 CA04 CA12 HA04

4M104 BB14 BB18 DD08 DD38 DD65 DD75 FF13 FF17 FF18 FF22

HH08 HH13 HH16

5F033 HH09 HH18 HH33 JJ18 JJ19 JJ33 JJ34 KK09 KK18 KK33

MM08 MM13 NN06 NN07 NN12 PP17 QQ08 QQ09 QQ10 QQ11

QQ37 QQ48 XX02 XX09 XX13