(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5300317号

(P5300317)

(45) 発行日 平成25年9月25日(2013.9.25)

(24) 登録日 平成25年6月28日(2013.6.28)

(51) Int.Cl.

B 41 J 5/30 (2006.01)

B 41 J 29/38 (2006.01)

F 1

B 41 J 5/30

B 41 J 29/38Z

Z

請求項の数 12 (全 28 頁)

(21) 出願番号 特願2008-123897 (P2008-123897)

(22) 出願日 平成20年5月9日 (2008.5.9)

(65) 公開番号 特開2009-269355 (P2009-269355A)

(43) 公開日 平成21年11月19日 (2009.11.19)

審査請求日 平成23年5月9日 (2011.5.9)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】画像処理装置及びその制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

画像処理装置であって、

ホストから印刷指示情報を受信する受信手段と、

受信した前記印刷指示情報を、レンダリング処理可能な中間情報を変換する第1変換手段と、

前記中間情報をスキャンライン毎のスパン情報に変換する第2変換手段と、

スキャンライン毎のスパン情報に色を付与して、色情報と繰り返し情報をからなるスキャンライン毎のランレングス情報を生成する色塗り手段と、

前記ランレングス情報を展開することによって、タイル順の画素情報を生成する生成手段と、

スキャンライン毎の入力情報を、タイル内のスキャンライン毎の情報を分割してタイル単位の出力情報に並べ替える分割手段と、

タイル単位で前記生成手段が生成したタイル順の画素情報を圧縮処理して圧縮データを生成する圧縮手段と、

タイル単位の前記圧縮データのページ分を保持する記憶手段と、

前記記憶手段に保持されたタイル単位に圧縮された前記圧縮データを用いて印刷処理する印刷手段と

を有し、

前記分割手段は、前記第2変換手段からのスキャンライン毎のスパン情報を前記入力情

10

20

報とし、タイル内のスキャンライン毎のスパン情報に分割してタイル単位のスパン情報に並べ替えて、前記並べ替えたタイル単位のスパン情報を前記色塗り手段に前記出力情報として出力することを特徴とする画像処理装置。

【請求項 2】

前記分割手段は、副走査方向に 2 タイルラインを記憶する記憶手段を有することを特徴とする請求項 1 に記載の画像処理装置。

【請求項 3】

前記記憶手段は、前記画像処理装置のメインメモリであることを特徴とする請求項 2 に記載の画像処理装置。

【請求項 4】

前記分割手段は、前記出力情報としての前記並べ替えたタイル単位のスパン情報を、スキャンライン毎にシーケンスに前記色塗り手段に出力することを特徴とする請求項 1 に記載の画像処理装置。

【請求項 5】

画像処理装置であって、

ホストから印刷指示情報を受信する受信手段と、

受信した前記印刷指示情報を、レンダリング処理可能な中間情報へ変換する第 1 変換手段と、

前記中間情報をスキャンライン毎のスパン情報に変換する第 2 変換手段と、

スキャンライン毎のスパン情報に色を付与して、色情報と繰り返し情報とからなるスキャンライン毎のランレンゲス情報を生成する色塗り手段と、

前記ランレンゲス情報を展開することによって、タイル順の画素情報を生成する生成手段と、

スキャンライン毎の入力情報を、タイル内のスキャンライン毎の情報に分割してタイル単位の出力情報に並べ替える分割手段と、

タイル単位で前記前記生成手段が生成したタイル順の画素情報を圧縮処理して圧縮データを生成する圧縮手段と、

タイル単位の前記圧縮データのページ分を保持する記憶手段と、

前記記憶手段に保持されたタイル単位に圧縮された前記圧縮データを用いて印刷処理する印刷手段と

を有し、

前記分割手段は、前記色塗り手段からのスキャンライン毎の色を付与したランレンゲス情報を前記入力情報とし、タイル内のスキャンライン毎のランレンゲス情報を分割してタイル単位のランレンゲス情報を並べ替えて、前記並べ替えたタイル単位の色を付与したランレンゲス情報を前記生成手段に前記出力情報として出力することを特徴とする画像処理装置。

【請求項 6】

前記分割手段は、副走査方向に 2 タイルラインを記憶する記憶手段を有することを特徴とする請求項 5 に記載の画像処理装置。

【請求項 7】

前記記憶手段は、前記画像処理装置のメインメモリであることを特徴とする請求項 6 に記載の画像処理装置。

【請求項 8】

前記分割手段は、前記出力情報としての前記並べ替えたタイル単位のランレンゲス情報を、スキャンライン毎にシーケンスに前記生成手段に出力することを特徴とする請求項 5 に記載の画像処理装置。

【請求項 9】

画像処理装置の制御方法であって、

受信手段が、ホストから印刷指示情報を受信する受信工程と、

第 1 変換手段が、受信した前記印刷指示情報を、レンダリング処理可能な中間情報へ変

10

20

30

40

50

換する第1変換工程と、

第2変換手段が、前記中間情報をスキャンライン毎のスパン情報に変換する第2変換工程と、

色塗り手段が、スキャンライン毎のスパン情報に色を付与して、色情報と繰り返し情報とからなるスキャンライン毎のランレンゲス情報を生成する色塗り工程と、

生成手段が、前記ランレンゲス情報を展開することによって、タイル順の画素情報を生成する生成工程と、

分割手段が、スキャンライン毎の入力情報を、タイル内のスキャンライン毎の情報に分割してタイル単位の出力情報に並べ替える分割工程と、

圧縮手段が、タイル単位で前記生成工程にて生成したタイル順の画素情報を圧縮処理して圧縮データを生成する圧縮工程と、

記憶手段が、タイル単位の前記圧縮データのページ分を記憶部に保持する記憶工程と、

印刷手段が、前記記憶工程により保持されたタイル単位に圧縮された前記圧縮データを用いて印刷処理する印刷工程と

を有し、

前記分割工程では、前記第2変換工程により変換されたスキャンライン毎のスパン情報を前記入力情報とし、タイル内のスキャンライン毎のスパン情報に分割してタイル単位のスパン情報を並べ替えて、前記並べ替えたタイル単位のスパン情報を前記色塗り工程に対して前記出力情報として出力することを特徴とする画像処理装置の制御方法。

#### 【請求項10】

画像処理装置の制御方法であつて、

受信手段が、ホストから印刷指示情報を受信する受信工程と、

第1変換手段が、受信した前記印刷指示情報を、レンダリング処理可能な中間情報を変換する第1変換工程と、

第2変換手段が、前記中間情報をスキャンライン毎のスパン情報に変換する第2変換工程と、

色塗り手段が、スキャンライン毎のスパン情報に色を付与して、色情報と繰り返し情報とからなるスキャンライン毎のランレンゲス情報を生成する色塗り工程と、

生成手段が、前記ランレンゲス情報を展開することによって、タイル順の画素情報を生成する生成工程と、

分割手段が、スキャンライン毎の入力情報を、タイル内のスキャンライン毎の情報に分割してタイル単位の出力情報に並べ替える分割工程と、

記憶手段が、タイル単位で前記生成工程にて生成されたタイル順の画素情報を圧縮処理して圧縮データを生成する圧縮工程と、

記憶手段が、タイル単位の前記圧縮データのページ分を記憶部に保持する記憶工程と、

印刷手段が、前記記憶工程により保持されたタイル単位に圧縮された前記圧縮データを用いて印刷処理する印刷工程と

を有し、

前記分割工程では、前記色塗り工程によるスキャンライン毎の色を付与したランレンゲス情報を前記入力情報とし、タイル内のスキャンライン毎のランレンゲス情報を分割してタイル単位のランレンゲス情報を並べ替えて、前記並べ替えたタイル単位の色を付与したランレンゲス情報を前記生成工程に対して前記出力情報として出力することを特徴とする画像処理装置の制御方法。

#### 【請求項11】

請求項9または10に記載の画像処理装置の制御方法の各工程をコンピュータに実行させるためのプログラム。

#### 【請求項12】

請求項11に記載のプログラムを記憶したコンピュータで読み取り可能な記憶媒体。

#### 【発明の詳細な説明】

#### 【技術分野】

10

20

30

40

50

**【0001】**

本発明は画像処理装置及びその制御方法に関する。例えば、ページ記述言語等のベクタデータを印刷するプリンタもしくは複合機に関わる画像処理技術である。特に、レンダリング後のラスタ画像をスプールする際に、画像をラスタ順からタイル順に変換するプリンタもしくは複合機に関する画像処理技術に関するものである。

**【背景技術】****【0002】**

ページ記述言語等のベクタデータをレンダリングし、生成したラスタ画像やスキャナから読み込んだラスタ画像をスプールし、プリンタエンジンに印刷を行う画像処理装置として複合機がある。かかる処理を、特許文献1や2に開示されているように、ラスタ画像をスプールする際に画像をラスタ順からタイル順に変換する（以下ラスタタイル変換処理と称す）ことで、画像処理が並列に処理できるようになり高速な印刷が可能となる。10

**【0003】**

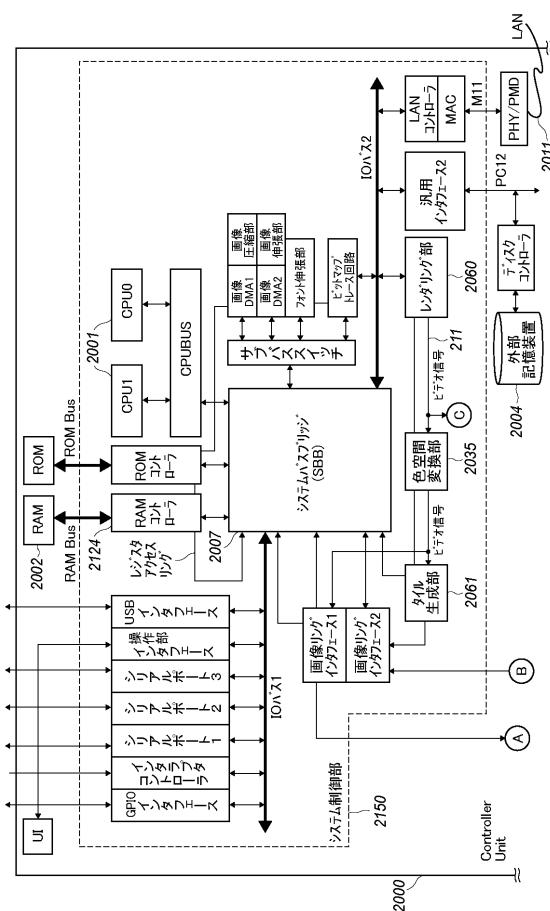

図16A及び図16Bは、かかるラスタタイル変換処理を行なう従来の画像処理装置のコントローラ構成を示した構成図である（なお、図16A及び図16Bにおいては、本願に関連する構成要素のみを説明する）。図16A及び図16Bは、画像処理装置のコントローラ部2000を示す。コントローラ部2000は、破線で囲んだ1チップのASICからなる、外部から受信したページ記述言語データから出力画像データを生成すると共に入力画像データを処理するシステム制御部2150を有する。また、コントローラ部2000は、破線で囲んだ1チップのASICからなる、システム制御部2150からの出力画像データを受信して出力すると共に入力画像データをシステム制御部2150に送信する画像処理部2149を有する。20

**【0004】**

ネットワーク2011経由で受信したページ記述言語データをCPU2001にて処理し、レンダリング可能なディスプレイリストに変換した後、レンダリング部2060にてラスタ画像を生成する。生成されたラスタ画像の各画素は、ラスタ順にビデオ信号211として色変換部2135を経由してタイル生成部2061に送られ、タイル生成部2061でタイル順に変換される。

**【0005】**

以下、図17及び図18の説明において、図16A及び図16Bの構成要素が参照される。30

**【0006】**

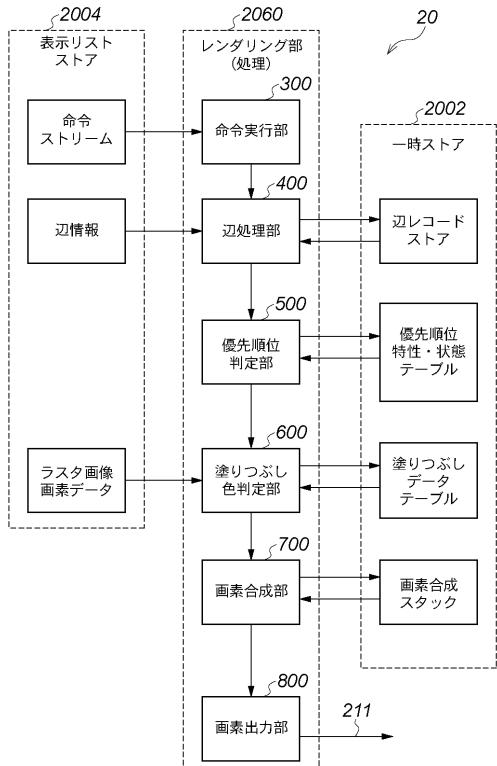

図17は、従来技術のレンダリング部2060の詳細を示したデータフロー図である。なお、図17の左側の表示リストストアは、CPU2001にて処理してページ記述言語データから変換されたレンダリング可能なディスプレイリストに相当し、例えば図16Aの外部記憶装置2004に格納されている。また、図17の右側の一次ストアは、レンダリング部2060による処理中にデータを一次記憶する領域であり、例えば図16AのRAM2002に確保される。図17の中央がレンダリング部2060が実行する処理機能部であり、ハードウェア、ソフトウェアあるいはその組合せで実現される。

**【0007】**

ディスプレイリストの命令ストリームが命令実行部300によりフェッチされて、順に実行される。辺処理部400において、辺レコードストアを使用して辺情報がスキャンラインごとのX座標とグラフィックオブジェクトの情報を変換される。この時のグラフィックオブジェクトごとのX座標対がグラフィックオブジェクトの当該スキャンラインのスパン情報となる。優先順位判定部500は、優先順位特性・状態テーブルを使用して、グラフィックオブジェクトごとの前後関係の優先順位から可視オブジェクトを判定し、当該スキャンラインのスパンを含む塗りつぶし命令を生成する。塗りつぶし色判定部600は、塗りつぶしデータテーブルを使用して、ラスタ画像の画素データを当該スキャンラインのオブジェクトごとにどんな色で塗るかを判定する。そして、単色のオブジェクトであれば単色の色とそのスパンの長さを生成し、イメージやグラデーションなどの単色ではないオ40

プロジェクトでは画素ごとの色を生成する。画素合成部 700 では、画素合成スタックを使用して、生成された色を用いて重なったオブジェクトの色の合成を行う。画素合成部 700 は、合成後の色を、単色オブジェクトの合成であれば色とランレンジス情報を出力し、単色でないオブジェクトの合成結果であれば複数の色情報を出力する。画素出力部 800 は、画素合成部 700 が生成したランレンジス情報を全ての画素情報に伸張し、ビデオ信号 211 として送信する。

#### 【0008】

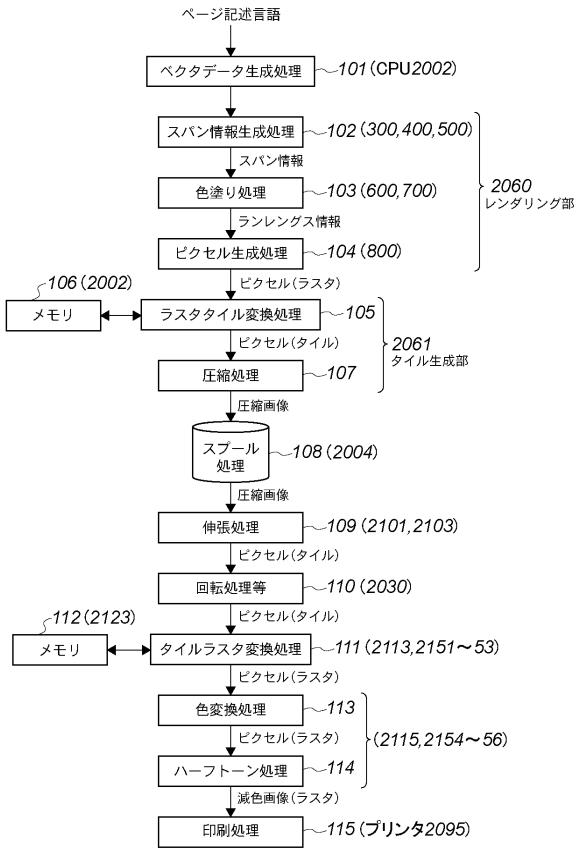

図 18 は、従来技術の図 16 A、図 16 B 及び図 17 の構成におけるページ記述言語の受信から印刷までの処理フローをまとめたデータ処理フロー図である。図 16 A 及び図 16 B で参照番号が付された構成要素、図 17 の各処理部を参照して、以下説明をする。

10

#### 【0009】

CPU 2001 により、ページ記述言語から生成されたディスプレイリスト形式のベクタデータ生成処理 101 が行われる。次に、命令実行部 300、辺処理部 400、優先順位判定部 500 によって、ディスプレイリストデータからスキャンラインごとのスパン情報に変換されるスパン生成処理 102 が行われる。次に、塗りつぶし色判定部 600、画素合成部 700 により、色塗り処理 103 が行われる。次に、画素出力部 800 がピクセル生成処理 104 を行う。かかる、スパン生成処理 102、色塗り処理 103、ピクセル生成処理 104 を、図 16 A のレンダリング部 2060 が実行する。

#### 【0010】

生成された画素（ピクセル）は、図 16 A のタイル生成部 2061 によって、ラスタタイル変換処理 105 が実施される。ラスタタイル変換処理 105 は、タイル高さ分のラスタ画像を保持するために中間バッファメモリ 106 を必要とする。この中間バッファメモリ 106 としては、図 16 A のタイル生成部 2061 がシステムバスプリッジ 2007、RAM コントローラ 2124 経由でアクセスするメインメモリ（RAM）2002 の一部領域を使用する。タイル生成部 2061 はタイル画像の圧縮処理 107 も実施し、圧縮されたタイル順のラスタ画像が図 16 A の外部記憶装置 2004 にスプール処理 108 される。

20

#### 【0011】

図 16 A の外部記憶装置 2004 にスプール処理 108 された画像は、図 16 B のタイル伸張部 2103 にて伸張処理 109 され、タイルバス 2107 を経由して画像回転部 2030 等で回転処理 110 などが行われる。この伸張され回転処理などをしたタイル形式のピクセルデータは、画像出力インターフェース 2113、2151、2152、2153 にてタイルラスタ変換が行われる。そして、プリンタ画像処理部 2115、2154、2155、2156 にて色変換処理 113 やハーフトーン処理 114 が実施され、プリンタ 2095 にて印刷処理 115 がなされる。

30

#### 【0012】

ここで、タイルラスタ変換処理 111 が行われる際にタイル高さ分の中間メモリ 112 が必要になるが、画像出力インターフェース 2113、2151、2152、2153 がメモリバス 2108 を経由して画像メモリ 2123 内の一部領域を使用する。

40

#### 【0013】

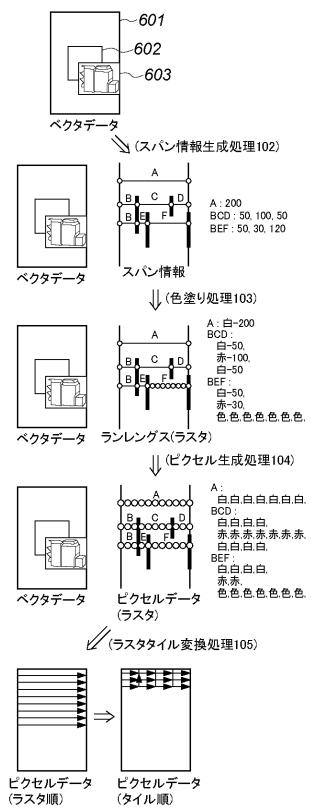

図 19 は、図 18 にて説明した従来技術の処理フローにおいて、ベクタデータ生成処理 101 からラスタタイル変換処理 105 までの処理データ例を示した模式図である。なお、ここでは、背景 601 に単色のオブジェクト 602 とイメージ 603 を展開する処理を例に説明する。赤い矩形オブジェクト 602 とイメージ 603 の無い領域は背景であり、本例では白とする。

#### 【0014】

ベクタデータ生成処理 101 により図 19 の最上段に示すベクタデータが生成される。

#### 【0015】

生成されたベクタデータはスパン情報生成処理 102 により図 19 の 2 段目にしめすスパン情報に変換される。スパン A には背景しかないと、ページの左端から右端までのス

50

パンとなる。スキャンライン B C D は、赤い矩形オブジェクト 602 が存在するスキャンラインである。そのため、スパン B は背景のスパン、赤い矩形オブジェクトのスパンであるスパン C、さらに背景のスパン D が生成される。スキャンライン B E F は、赤い矩形オブジェクト 602 とイメージ 603 が存在するスキャンラインである。そのため、スパン B は背景のスパン、赤い矩形オブジェクト 602 のスパンであるスパン E、さらにイメージ 603 のスパン F が生成される。

#### 【0016】

続いて、図 19 の 3 段目に示すようにいろ塗り処理 103 が実施される。スキャンライン A では、背景色である白とスパンの長さとの組合せのランレンジス情報が生成される。スキャンライン B C D では、背景の白とそのスパン長、赤い矩形オブジェクト 602 の色とそのスパン長、さらに背景の白とそのスパン長によるランレンジス情報が生成される。スキャンライン B E F では、背景の白とそのスパン長、赤い矩形オブジェクト 602 の色とそのスパン長、さらにイメージ 603 による各画素の色情報の並びによるランレンジス情報が生成される。

#### 【0017】

続いて、図 19 の 4 段目に示すように、ピクセル生成処理 104 によって画素情報に変換され、図 19 の最下段に示すように、ラスタタイル変換処理 105 にてページのラスタ順からタイル順の画像に変換される。

【特許文献 1】特開2002-300190公報

【特許文献 2】特開2002-305622公報

10

【発明の開示】

【発明が解決しようとする課題】

#### 【0018】

しかしながら、従来技術のラスタタイル変換処理 105 では、大量のデータを中間バッファメモリ 106 (RAM 2002) に読み書きすることになる。印刷解像度が 600 dpi であった場合には、A4 サイズ(幅 21cm、高さ 29.5cm)の画像をラスタタイル変換するために、次のサイズのデータを中間バッファメモリ 106 に格納する必要がある。

#### 【0019】

$$(21[\text{cm}] / 2.54[\text{cm/inch}] \times 600[\text{dpi}]) \times (29.5[\text{cm}] / 2.54[\text{cm/inch}] \times 600[\text{dpi}])$$

$$= 4960[\text{pixel}] \times 6968[\text{pixel}]$$

20

$$= 34.56[\text{Mpixels}]$$

$$1[\text{pixel}] = 4[\text{byte}] (\text{R}=8\text{bit}, \text{G}=8\text{bit}, \text{B}=8\text{bit}, \text{Attribute}=8\text{bit})$$

$$34.56[\text{Mpixel}] \times 4[\text{byte}] = 138.24[\text{MB}]$$

毎分 85 枚の印刷速度を実現するためには、次のようなメモリのデータ転送帯域が必要となる。

#### 【0020】

$$(138.24[\text{MB}], \text{書き込み}) + (138.24[\text{MB}], \text{読み出し}) / (60[\text{sec}] / 85[\text{ppm}])$$

$$= 391.68[\text{MB/s}]$$

印刷の解像度は年々高くなっているため、印刷の解像度が 1200 dpi に向上した場合に必要になるメモリのデータ転送帯域は、600 dpi の 4 倍となるため、以下のメモリのデータ転送帯域が必要になる。

#### 【0021】

$$391.68[\text{MB/s}] \times 4 = 1566.72[\text{MB/s}] = 1.567[\text{GB/s}]$$

一方、DDR2 SDRAM 400MHz 64bit のメモリの理論的なデータ転送帯域は、3.2[GB/s] であるが、ランダムアクセス時の実効のメモリのデータ転送帯域は、1[GB/s] から 1.5[GB/s] の間である。

#### 【0022】

従って、印刷の解像度 600 dpi ではラスタタイル処理 105 は DRAM を用いて実現可能であり、かつメモリ帯域に余裕があるため他の処理との共用が可能であった。しかし、印刷の解像度が 1200 dpi に高まると、DRAM の 1 チャンネルで実現が出来る限界

40

50

となり、かつメモリ帯域に余裕が無いため、他の処理を実現するためにD R A Mをもう1チャネル増設する必要が生じる。このため、コストが上昇してしまうという課題がある。

#### 【 0 0 2 3 】

ところで、図16Aでは中間バッファメモリ106として使用されるR A M 2 0 0 2をA S I C(破線で囲んだシステム制御部2150や画像処理部2149)の外部に装備している。メモリのデータ転送帯域を上げる別の解決策として、中間バッファメモリ106をA S I C上のオンチップメモリで実現し、D R A Mのチャネル増設を回避するという方法もある。この場合には、以下の容量のメモリが必要となる。

#### 【 0 0 2 4 】

$$\begin{aligned} & (29.5[\text{cm}] / 2.54[\text{cm/inch}] \times 1200 [\text{dpi}]) \times 32[\text{line/title}] \times 2[\text{band}] \times 4[\text{byte}] \\ & = 4960[\text{pixel}] \times 6968[\text{pixel}] \\ & = 3.56[\text{MB}] \end{aligned}$$

10

90nmの半導体プロセスを用いてA S I C上に3.56MBのオンチップメモリを実現することは可能であるが、やはり大幅なコスト上昇を生じてしまうため、前者の方法と同様の課題がある。

#### 【 0 0 2 5 】

本発明は、前記課題を鑑みてなされたものである。本発明者等は、図19の2段目から4段目に示すように、一般にランレンジス情報はほとんどの場合ラスタ画像よりもデータ量が少なく、またスパン情報はランレンジス情報よりもデータ量が少ないと注目した。そこで、タイル順への変換処理を従来のラスタ画像を用いて行うのではなく、その上流の色塗り処理の出力であるランレンジス情報、もしくはスパン生成処理の出力であるスパン情報において、データの並びをタイル順に置き換える。かかる処理により、タイル順に変換する際に一次格納するデータ量を大幅に削減し、従来と同等以下のコストおよびメモリのデータ転送帯域においても高い出力解像度のラスタタイル処理を実現する。

20

#### 【課題を解決するための手段】

#### 【 0 0 2 6 】

この課題を解決するために、本発明の画像処理装置は、画像処理装置であって、ホストから印刷指示情報を受信する受信手段と、受信した前記印刷指示情報を、レンダリング処理可能な中間情報へ変換する第1変換手段と、前記中間情報をスキャンライン毎のスパン情報に変換する第2変換手段と、スキャンライン毎のスパン情報に色を付与して、色情報と繰り返し情報とからなるスキャンライン毎のランレンジス情報を生成する色塗り手段と、前記ランレンジス情報を展開することによって、タイル順の画素情報を生成する生成手段と、スキャンライン毎の入力情報を、タイル内のスキャンライン毎の情報に分割してタイル単位の出力情報に並べ替える分割手段と、タイル単位で前記生成手段が生成したタイル順の画素情報を圧縮処理して圧縮データを生成する圧縮手段と、タイル単位の前記圧縮データのページ分を保持する記憶手段と、前記記憶手段に保持されたタイル単位に圧縮された前記圧縮データを用いて印刷処理する印刷手段とを有し、前記分割手段は、前記第2変換手段からのスキャンライン毎のスパン情報を前記入力情報とし、タイル内のスキャンライン毎のスパン情報を分割してタイル単位のスパン情報を並べ替えて、前記並べ替えたタイル単位のスパン情報を前記色塗り手段に前記出力情報として出力することを特徴とする。

30

#### 【 0 0 2 7 】

ここで、前記分割手段は、副走査方向に2タイルラインを記憶する記憶手段を有する。また、前記記憶手段は、前記画像処理装置のメインメモリである。また、前記分割手段は、前記出力情報としての前記並べ替えたタイル単位のスパン情報を、スキャンライン毎にシーケンスに前記色塗り手段に出力する。

#### 【 0 0 2 8 】

また、本発明の画像処理装置は、画像処理装置であって、ホストから印刷指示情報を受信する受信手段と、受信した前記印刷指示情報を、レンダリング処理可能な中間情報へ変換する第1変換手段と、前記中間情報をスキャンライン毎のスパン情報を変換する第2変

40

50

換手段と、スキャンライン毎のスパン情報に色を付与して、色情報と繰り返し情報とからなるスキャンライン毎のランレングス情報を生成する色塗り手段と、前記ランレングス情報を展開することによって、タイル順の画素情報を生成する生成手段と、スキャンライン毎の入力情報を、タイル内のスキャンライン毎の情報に分割してタイル単位の出力情報に並べ替える分割手段と、タイル単位で前記生成手段が生成したタイル順の画素情報を圧縮処理して圧縮データを生成する圧縮手段と、タイル単位の前記圧縮データのページ分を保持する記憶手段と、前記記憶手段に保持されたタイル単位に圧縮された前記圧縮データを用いて印刷処理する印刷手段とを有し、前記分割手段は、前記色塗り手段からのスキャンライン毎の色を付与したランレングス情報を前記入力情報とし、タイル内のスキャンライン毎のランレングス情報を分割してタイル単位のランレングス情報を前記生成手段に並べ替えて、前記並べ替えたタイル単位の色を付与したランレングス情報を前記生成手段に前記出力情報として出力することを特徴とする。

#### 【0029】

ここで、前記分割手段は、副走査方向に2タイルラインを記憶する記憶手段を有する。また、前記記憶手段は、前記画像処理装置のメインメモリである。また、前記分割手段は、前記出力情報としての前記並べ替えたタイル単位のランレングス情報を、スキャンライン毎にシーケンスに前記生成手段に出力する。

#### 【0031】

また、本発明の画像処理装置の制御方法は、画像処理装置の制御方法であって、受信手段が、ホストから印刷指示情報を受信する受信工程と、第1変換手段が、受信した前記印刷指示情報を、レンダリング処理可能な中間情報を変換する第1変換工程と、第2変換手段が、前記中間情報をスキャンライン毎のスパン情報に変換する第2変換工程と、色塗り手段が、スキャンライン毎のスパン情報に色を付与して、色情報と繰り返し情報を生成する色塗り工程と、生成手段が、前記ランレングス情報を展開することによって、タイル順の画素情報を生成する生成工程と、分割手段が、スキャンライン毎の入力情報を、タイル内のスキャンライン毎の情報に分割してタイル単位の出力情報に並べ替える分割工程と、圧縮手段が、タイル単位で前記生成工程にて生成したタイル順の画素情報を圧縮処理して圧縮データを生成する圧縮工程と、記憶手段が、タイル単位の前記圧縮データのページ分を記憶部に保持する記憶工程と、印刷手段が、前記記憶工程により保持されたタイル単位に圧縮された前記圧縮データを用いて印刷処理する印刷工程とを有し、前記分割工程では、前記第2変換工程により変換されたスキャンライン毎のスパン情報を前記入力情報とし、タイル内のスキャンライン毎のスパン情報を分割してタイル単位のスパン情報を並べ替えて、前記並べ替えたタイル単位のスパン情報を前記色塗り工程に対して前記出力情報として出力することを特徴とする。

#### 【0032】

また、本発明の画像処理装置の制御方法は、画像処理装置の制御方法であって、受信手段が、ホストから印刷指示情報を受信する受信工程と、第1変換手段が、受信した前記印刷指示情報を、レンダリング処理可能な中間情報を変換する第1変換工程と、第2変換手段が、前記中間情報をスキャンライン毎のスパン情報に変換する第2変換工程と、色塗り手段が、スキャンライン毎のスパン情報に色を付与して、色情報と繰り返し情報を生成する色塗り工程と、生成手段が、前記ランレングス情報を展開することによって、タイル順の画素情報を生成する生成工程と、分割手段が、スキャンライン毎の入力情報を、タイル内のスキャンライン毎の情報に分割してタイル単位の出力情報に並べ替える分割工程と、記憶手段が、タイル単位で前記生成工程にて生成されたタイル順の画素情報を圧縮処理して圧縮データを生成する圧縮工程と、記憶手段が、タイル単位の前記圧縮データのページ分を記憶部に保持する記憶工程と、印刷手段が、前記記憶工程により保持されたタイル単位に圧縮された前記圧縮データを用いて印刷処理する印刷工程とを有し、前記分割工程では、前記色塗り工程によるスキャンライン毎の色を付与したランレングス情報を前記入力情報とし、タイル内のスキャンライン毎のランレングス情報を分割してタイル単位のランレングス情報を並べ替えて、前記並べ替

10

20

30

40

50

えたタイル単位の色を付与したランレンゲス情報を前記生成工程に対して前記出力情報として出力することを特徴とする。

**【0033】**

更に、上記画像処理装置の制御方法の各工程をコンピュータに実行させるためのプログラム、及び該プログラムを記憶したコンピュータで読み取り可能な記憶媒体を提供する。

**【発明の効果】**

**【0034】**

以上述べたように、本発明によれば、ラスタタイル変換処理に必要なメモリのデータ転送帯域を大幅に削減することが可能となり、プリンタシステムを実現する際にコスト上昇を抑えながら印刷の解像度を向上することが可能となる。

10

**【0035】**

例えば、印刷の解像度 1200 dpiにおいて、ページの 30 % の面積がイメージで占められていた場合、ランレンゲス情報のデータ量はラスタ画像のデータ量の 30 % にほぼ等しい。従って、必要なメモリのデータ転送帯域は、以下の様に削減される。

**【0036】**

$$1.567[\text{GB/s}] \times 30\% = 470[\text{MB/s}]$$

このメモリのデータ転送帯域であれば、印刷の解像度 600 dpi と同等のコストで実現できる。

**【0037】**

また例えば、スパン情報のデータ量が 32 byte で、かつ全面にひとつのオブジェクトがある場合には、スパン情報によりラスタタイル処理に必要なメモリのデータ転送帯域は以下の帯域となり、非常に少ない帯域で処理が可能となる。

20

**【0038】**

$$\begin{aligned} & (32[\text{byte}] \times (29.5[\text{cm}] / 2.54[\text{cm/inch}] \times 1200[\text{dpi}])) \\ & \times 2(\text{read/write}) / (60[\text{sec}] / 85[\text{ppm}]) \\ & = 1.26[\text{MB/s}] \end{aligned}$$

**【発明を実施するための最良の形態】**

**【0039】**

以下、本発明の実施形態を添付図面を参照して詳細に説明する。

**【0040】**

30

<本実施形態の画像処理装置の構成例>

本実施形態における画像処理装置は、スパン情報あるいはランレンゲス情報においてラスタ順からタイル順への変換を行なう。かかる処理は、従来例で示したレンダリング部 2060において実現される。従って、図 16A 及び図 16Bにおいて、タイル生成部 2061 が無い構成が、本実施形態の画像処理装置のコントロール部の構成例となる（図示せず）。

**【0041】**

なお、本実施形態のレンダリング部 2060 の特徴的部分については、図 9 から図 13 において詳細に説明する。以下、かかる本実施形態の画像処理装置のコントロール部の構成を念頭に置いて、その処理例を説明する。

40

**【0042】**

<第 1 実施形態の画像処理装置の動作例>

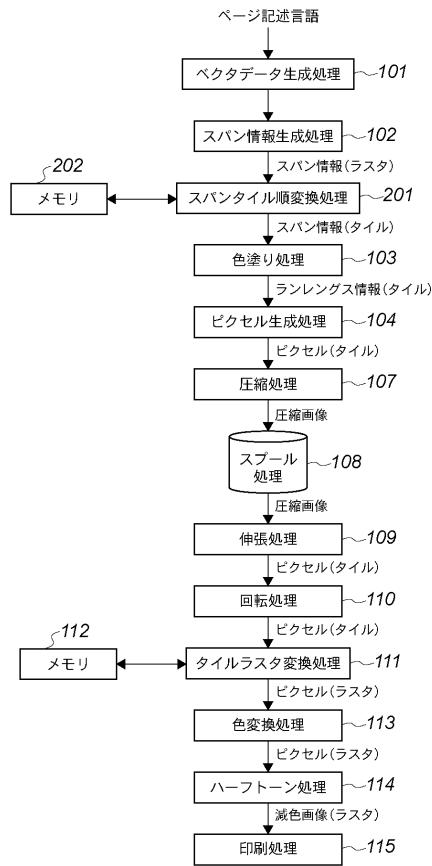

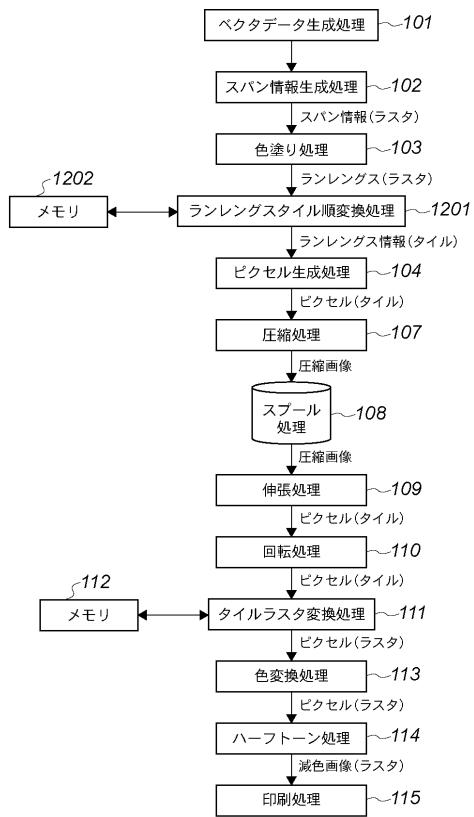

図 1 は、上記のような図 16A 及び図 16Bにおいてタイル生成部 2061 が無い構成における、第 1 実施形態におけるページ記述言語の受信から印刷までの処理フローをまとめたデータ処理フロー図である。なお、従来例の図 17 と同様の処理については、同じ参考番号を付する。

**【0043】**

まず、印刷指示情報であるページ記述言語からレンダリング処理可能な中間情報であるディスプレイリスト形式のベクタデータを生成するベクタデータ生成処理 101 が行われる。かかるベクタデータ生成処理 101 は第 1 変換処理として参照される。

50

**【 0 0 4 4 】**

次に、ディプレイリストデータからスキャンライン毎のスパン情報に変換されるスパン情報生成処理 102 が行われる。かかるスパン情報生成処理 102 は第2変換処理として参照される。第1実施形態では、かかるスキャンライン毎のスパン情報がスパンタイル変換処理 201 への入力情報となる。

**【 0 0 4 5 】**

第1実施形態では、生成されたスキャンラインごとのスパン情報は、スパンタイル変換処理 201 によって各タイル内のスキャンラインのスパン情報に変換される。このときタイル高さ分のスキャンラインごとのスパン情報が、中間バッファメモリ 202 (図 16 A の RAM 2002) に格納され、かつ読み出される。第1実施形態においては、各タイル内 10 のスキャンラインのスパン情報がスパンタイル変換処理 201 からの出力情報となる。

**【 0 0 4 6 】**

次に、各タイル内のスキャンラインのスパン情報は、色塗り処理 103 によってオブジェクトごとの色が付与され、タイルライン (タイルの主走査方向の 1 行分) ごとのランレンジス情報として出力される。タイルラインごとのランレンジス情報は、ピクセル生成処理 104 によって画素情報に変換され、タイル順の画素情報として出力される。

**【 0 0 4 7 】**

ここで、上記のように、中間バッファメモリ 202 はメインメモリである RAM 2002 内の一部領域として確保される。レンダリング部 2060 から、システムバスプリッジ 2007、RAMコントローラ 2124 経由にて RAM 2002 内の中間メモリバッファ 202 の領域がアクセスされる。スパンタイル順変換処理 201 を含むスパン情報生成処理 102 からピクセル生成 104 までの処理は、レンダリング部 2060 に実装される。 20

**【 0 0 4 8 】**

その後は、従来例と同様に、圧縮処理 107 を実施し、圧縮されたタイル順のラスタ画像 (圧縮データとも言う) のページ分が図 16 A の外部記憶装置 2004 にプール処理 108 される。図 16 A の外部記憶装置 2004 にスプール処理 108 されたページ分の画像は、図 16 B のタイル伸張部 2103 にて伸張処理 109 され、タイルバス 2107 を経由して画像回転部 2030 等で回転処理 110 などが行われる。この伸張され回転処理などをしたタイル形式のピクセルデータは、画像出力インターフェース 2113、2115 1、2152, 2153 にてタイルラスタ変換が行われる。そして、プリンタ画像処理部 2115、2154, 2155, 2156 にて色変換処理 113 やハーフトーン処理 114 が実施され、プリンタ 2095 にて印刷処理 115 がなされる。 30

**【 0 0 4 9 】**

ここで、タイルラスタ変換処理 111 が行われる際にタイル高さ分の中間メモリ 112 が必要になるが、画像出力インターフェース 2113、2151、2152, 2153 がメモリバス 2108 を経由して画像メモリ 2123 内の一部領域を使用する。

**【 0 0 5 0 】**

(第1実施形態におけるタイル順への変換の具体例)

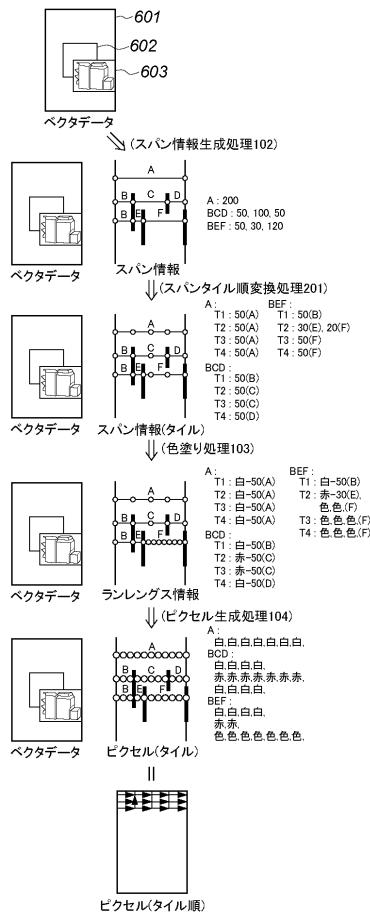

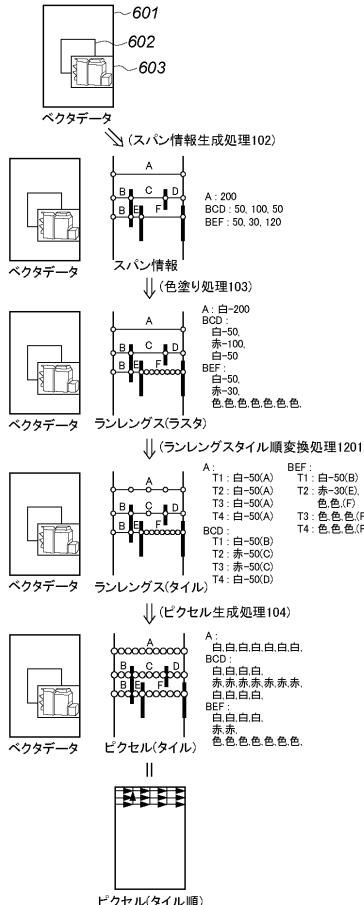

図 2 は、図 1 にて説明した第1実施形態の処理フローにおいてベクタデータ生成処理 101 からピクセル生成処理 104 までの処理データ例を示した模式図である。従来例における、図 18 と対比すると本願発明の作用効果が明瞭となる。なお、従来との対比を明瞭にするため、背景 601 と赤い矩形オブジェクト 602 とイメージ 603 とは、図 18 と同様である。 40

**【 0 0 5 1 】**

ベクタデータ生成処理 101 により、図 2 の最上段に示すベクタデータが生成される。

**【 0 0 5 2 】**

生成されたベクタデータはスパン情報生成処理 102 により、図 2 の 2 段目にしめすスパン情報に変換される。スパン A は背景しかないとページの左端から右端までのスパンとなる。スキャンライン B C D は、赤い矩形オブジェクト 602 が存在するスキャンラインである。そのため、スパン B は背景のスパン、赤い矩形オブジェクトのスパンであるス 50

パンC、さらに背景のスパンDが生成される。スキャンラインB E Fは、赤い矩形オブジェクト602とイメージ603が存在するスキャンラインである。そのため、スパンBは背景のスパン、赤い矩形オブジェクト602のスパンであるスパンE、さらにイメージ603のスパンFが生成される。

#### 【0053】

続いて、図2の3段目に示すように、本実施形態のスパンタイル順変換処理201によって、スキャンライン単位のスパン情報からタイル内のスキャンラインのスパン情報に変換される。

#### 【0054】

スキャンラインAは、4つのタイルT1,T2,T3,T4に分割される。背景であるためページの左端から右端までのスパンであったスパンAは、4つのタイル幅のスパンに分割される。

10

#### 【0055】

スキャンラインB C Dも、4つのタイルT1,T2,T3,T4に分割される。タイル形式への変換前のスキャンラインB C Dは、背景と赤い矩形オブジェクトによって、スパンB、スパンC、スパンDの3つのスパンであった。これが、タイルT1はスパンB、タイルT2はスパンCが分割された前方のスパン、タイルT3もスパンCが分割された後方のスパン、タイルT4はスパンDに分割される。

#### 【0056】

スキャンラインB E Fも、4つのタイルT1,T2,T3,T4に分割される。タイル形式への変換前のスキャンラインB E Fは、背景と赤い矩形オブジェクトとイメージオブジェクトによって、スパンB、スパンE、スパンFの3つのスパンであった。それが、タイルT1はスパンB、タイルT2はスパンEと分割された前方のスパンF、タイルT3は分割された中間のスパンF、タイルT4も後方のスパンFに分割される。

20

#### 【0057】

続いて、図2の4段目6に示すように、タイル内のスキャンラインのスパン情報からタイル単位の色塗り処理103が実施されて、ランレンジス情報が生成される。次に、図2の5段目に示すように、ランレンジス情報からピクセル生成処理104により画素情報が生成される。

#### 【0058】

本実施形態では、このピクセル生成処理104が終了した時点で、図2の最下段に示したように、タイル順の画像情報が完成することになる。

30

#### 【0059】

(本実施形態の画像データ例)

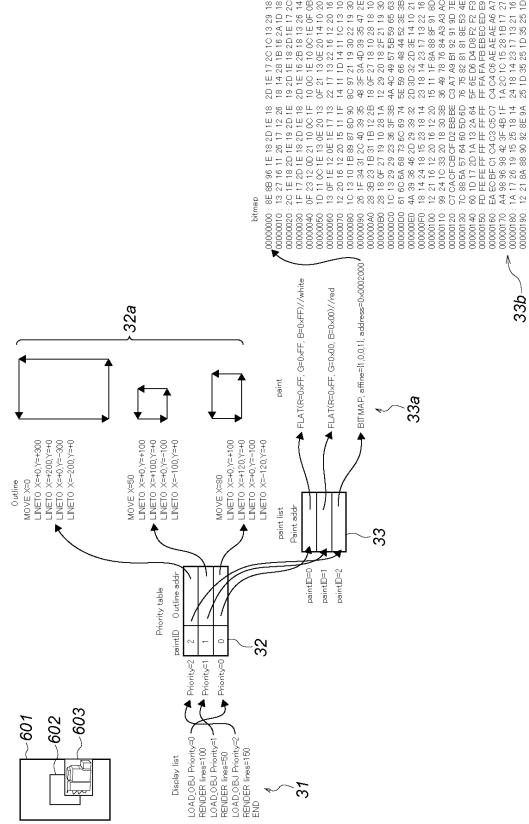

図3は、本実施形態のベクタデータ生成処理101で生成され、スパン情報生成処理102で処理を行うディスプレイリストのデータ形式を示したデータ例である。すなわち、本実施形態において使用される、ディスプレイリスト、優先順位テーブル、塗りつぶしリスト、などの例を示す図である。背景601と赤い矩形オブジェクト602とイメージ603とは、図2及び図18と同様である。

#### 【0060】

31はディスプレイリストであり、上からイメージ、赤い矩形オブジェクト、背景が記述されている。ここで、優先順位(プライオリティー)は“0”が最も高いとする。初めにPriority=0の背景601を指定し、次に100ライン描画する。次にPriority=1の赤い矩形オブジェクト602を指定し、次に50ライン描画する、次にPriority=2のビットマップオブジェクト603を指定し、さらにページ下端まで150ラインを描画する。

40

#### 【0061】

32は、描画記述とは別にオブジェクトの上下関係を示す優先順位テーブル(PriorityTable)が存在し、ディスプレイリストの先頭から順にスタックされている。優先順位テーブル32の各エントリには、色塗りのためのPaintIDと各オブジェクトのアウトラインへのポインタが含まれる。各々のアウトラインは、開始のX座標と、外形のパスがX, Yア

50

ドレスの増減で指定される。そのアウトラインが 3\_2\_a にそれぞれ示されている。

#### 【0062】

PaintID は、塗りつぶしリスト(PaintTable) 3\_3 のエントリに対応しており、PaintTable は各色塗り情報である paint 情報 3\_3\_a へのポインタ配列である。各 paint 情報 3\_3\_a には、単色(FLAT)とビットマップ(BITMAP)が存在し、FLAT は RGB 各色の値が含まれ、BITMAP はアフィン変換のための変換行列と、ビットマップ実体 3\_3\_b へのポインタが含まれる。本例では、背景が白、赤い矩形オブジェクト、イメージのビットマップが定義されている。

#### 【0063】

第 1 実施形態では、優先順位テーブル 3\_2 から各オブジェクトのアウトライン 3\_2\_a が 10 判定された時点で、スパン情報の生成及びスパンタイル順変換処理が実行される。塗りつぶしリスト 3\_3 に基づく塗りつぶし処理は、スパンタイル順変換処理が完了した後に実行される。

#### 【0064】

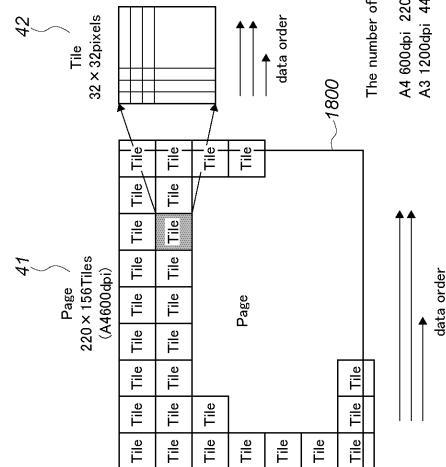

図 4 は、本実施形態において使用される、タイル形式の画像データの例を示す図である。かかるタイル形式の画像データは、既にピクセル単位に展開された結果を示している。

#### 【0065】

図 4 は、A4 サイズのページ 4\_1 で、600 dpi の場合の例を示しており、 $32 \times 32$  画素のタイル 4\_2 に分割されて、1 ページが  $220 \times 156 = 34$ , 320 タイルとなる。なお、1200 dpi の場合には、 $440 \times 624 = 274$ , 560 タイルとなる。 20

#### 【0066】

< 第 1 実施形態のスパンタイル順変換処理の処理手順例 >

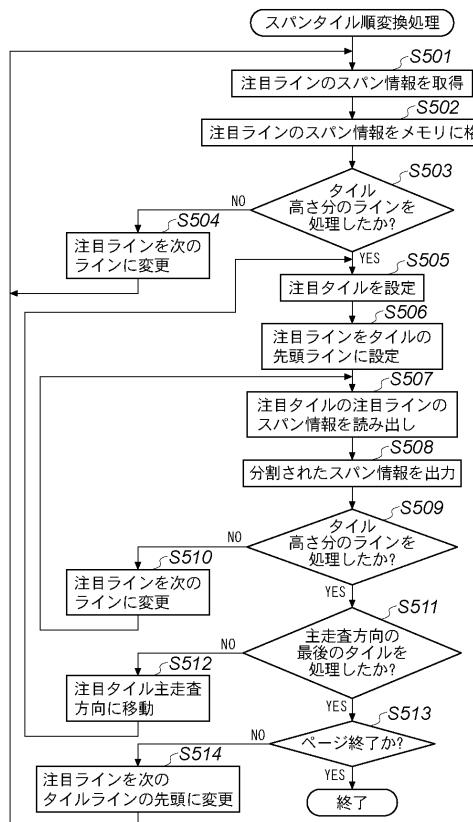

図 5 は、スパンタイル順変換処理 2\_0\_1 の処理フローを示したフローチャートである。なお、かかる処理は、レンダリング部 2\_0\_6\_0 で実行される。レンダリング部 2\_0\_6\_0 を制御する CPU によりソフトウェアで実現されてもよいし、後述のようなステップマシンによるファームウェア、あるいはハイドウェア回路で実現されてもよい。

#### 【0067】

初めに注目スキャンラインのスパン情報を、例えば外部記憶装置 2\_0\_0\_4 から取得する (S5\_0\_1)。次に、注目スキャンラインのスパン情報を中間バッファメモリ 2\_0\_2 (RAM 2\_0\_0\_2) に格納する (S5\_0\_2)。1 つのタイルの高さ分のスキャンラインを取得したかを判断する (S5\_0\_3)。まだ 1 つのタイルの高さ分のスパン情報を取得していない場合には、注目ラインを次ラインに設定し (S5\_0\_4)、注目スキャンラインのスパンを入力 (5\_0\_1) に戻る。 30

#### 【0068】

1 つのタイルの高さ分のスキャンラインを取得したならば、ライン中の注目タイルを設定する (S5\_0\_5)。注目ラインを注目タイルの先頭ラインに設定する (S5\_0\_6)。次に、注目タイルの注目ラインに相当するスパン情報を中間バッファメモリ 2\_0\_2 から読み出し (S5\_0\_7)、注目タイル内のスキャンラインに相当する幅に分割したスパン情報を生成して、タイル順に色塗り処理 1\_0\_3 へ送信する (S5\_0\_8)。次に、注目タイルの高さ分のラインを処理したかを判断する (S5\_0\_9)。注目タイルの高さ分を処理していないければ、注目ラインを次のラインに変更し (S5\_1\_0)、注目タイルの注目ラインのスパン情報を中間バッファメモリ 2\_0\_2 から読み出す処理 (S5\_0\_7) へ戻る。 40

#### 【0069】

注目タイルの高さ分の処理が終わっていたならば、主走査方向 (ライン方向) の最後のタイルまで処理を行ったかを判断する (S5\_1\_1)。主走査方向の最後まで終わっていないければ、主走査方向に注目タイルを移動し (S5\_1\_2)、注目タイルを設定する処理 (S5\_0\_5) へ戻る。

#### 【0070】

主走査方向の最後のタイルを処理し終えたならば、次にページ終了かを判断する (S5\_1\_3)。ページが終了していないならば、注目ラインをこれまで処理したタイルラインの

10

20

30

40

50

次のタイルラインの先頭に変更し( S 5 1 4 )、注目ラインのスパン情報を外部記憶装置 2 0 0 4 から取得する処理( S 5 0 1 )へ戻る。ページが終了していたならば、処理を終了する。

#### 【 0 0 7 1 】

<第1実施形態のスパンタイル順変換処理の具体例>

(スパンタイル順変換処理前のスパン情報例)

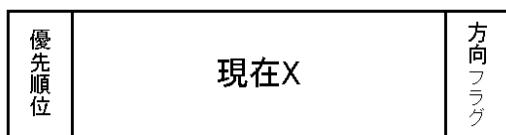

図 6 A は、第1実施形態におけるスパン情報のフォーマット例を示す図である。また、図 6 B は、図 2 の例において図 6 A のフォーマットで外部記憶装置 2 0 0 4 に格納されたスパン情報の格納例を示した模式図である。

#### 【 0 0 7 2 】

図 6 A に示すように、スパン情報は一対のエッジ情報からなり、ひとつのエッジ情報は、少なくとも優先順位情報、現在の X 座標位置、エッジの方向フラグを含む。

#### 【 0 0 7 3 】

図 6 B は、図 2 の例におけるスパン情報である。

#### 【 0 0 7 4 】

ライン 0 には背景しかないため、ページの左端と右端の一対のエッジからなるスパン情報を生成する。これはスキャンライン A に相当する。

#### 【 0 0 7 5 】

赤い矩形オブジェクト 6 0 2 が展開されるスキャンライン B C D に相当するスパン情報が、ライン N に示されている。左からページの左端エッジ、赤い矩形オブジェクト 6 0 2 の左端エッジ、赤い矩形オブジェクト 6 0 2 の右端エッジ、ページの右端エッジからなる。

#### 【 0 0 7 6 】

図 6 B に示すように、スパン情報の情報量はスキャンライン毎に異なるデータ量を持つ。本実施形態では、メモリ上の連続の領域に、異なるデータ量のライン情報を隙間なく詰めて格納する。

#### 【 0 0 7 7 】

(スパンタイル順変換処理の動作例)

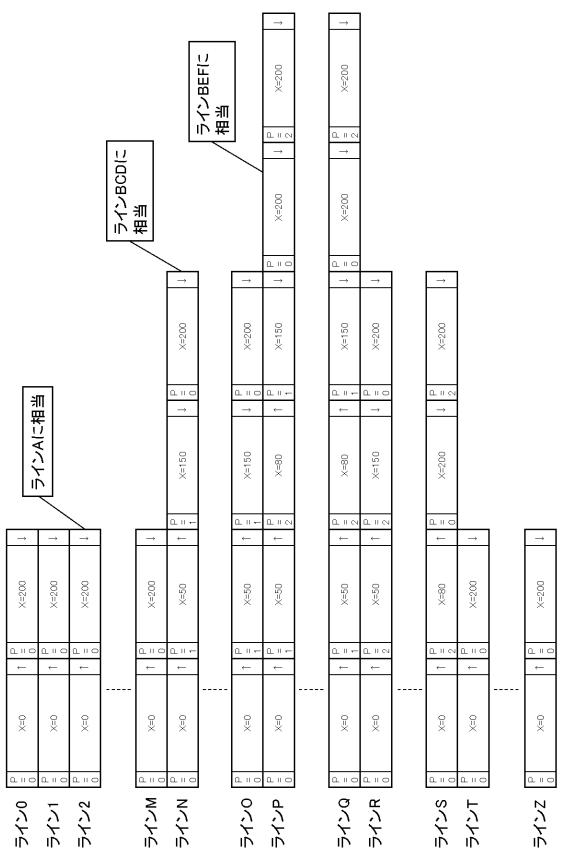

図 7 は、中間バッファメモリ 2 0 2 ( R A M 2 0 0 2 ) におけるスパンタイル順変換処理中のスパン情報について示した図である。なお、図 7 には、図 5 における各ステップとの対応が示されている。

#### 【 0 0 7 8 】

7 0 は、図 2 及び図 3 の処理対象と同じページを示している。ここでは、理解を容易にするためページを  $4 \times 6 = 24$  のタイルに分割する例を示している。

#### 【 0 0 7 9 】

7 1 は、外部記憶装置 2 0 0 4 に格納されているスパン情報の先頭のタイルラインを示している。図 5 のステップ S 5 0 1 の繰り返しにより、図 6 B のスパン情報からかかるスパン情報の先頭のタイルライン分が取得される。7 2 は、図 5 のステップ S 5 0 1 の繰り返しで、中間バッファメモリ 2 0 2 である R A M 2 0 0 2 にスパン情報の先頭のタイルライン分が格納される。7 3 も R A M 2 0 0 2 に格納されたスパン情報の先頭のタイルライン分であり、図 5 のステップ S 5 0 7 の繰り返しで、R A M 2 0 0 2 からスパン情報がタイル順に読み出される。

#### 【 0 0 8 0 】

7 4 は、レンダリング部 2 0 6 0 におけるスパンタイル順変換処理の実行部における処理を示す。図 5 のステップ S 5 0 8 の処理の繰り返しで、R A M 2 0 0 2 から読み出したスパン情報をタイル幅に分割して、7 5 に示すようにタイル順に色塗り処理 1 0 3 へ送信する。

#### 【 0 0 8 1 】

なお、中間バッファメモリ 2 0 2 からタイル順にスパン情報を取得するため、スパンタイル順変換処理 2 0 1 では、注目タイルの高さ内の各スキャンラインの現在の注目スパン

10

20

30

40

50

のアドレス情報を、注目タイル内のスキャンライン数分保持する。そして、注目タイルのスパン情報を生成するごとに当該アドレス情報を更新する。

#### 【0082】

(スパンタイル順変換処理後のスパン情報)

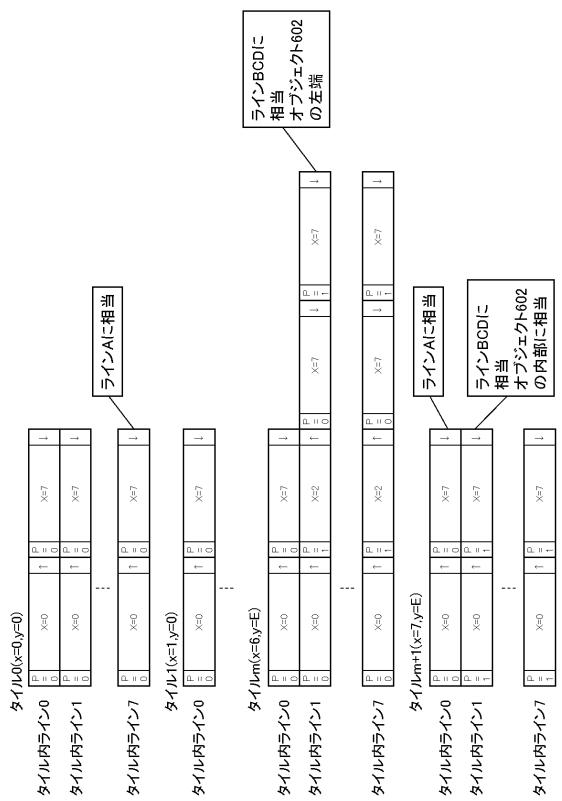

図8は、スパンタイル順変換処理201によってタイル順に変換されて、色塗り処理103へ出力されるタイル分割後のスパン情報を示す模式図である。かかるタイル分割後のスパン情報は、タイル順に色塗り処理103へ送信される。

#### 【0083】

スキャンライン0からスキャンライン7までは、背景しかないと注目タイルの左端エッジと右端エッジからなるスパン情報に分割される。タイル0内のスキャンライン0とタイル1内のスキャンライン0のスパン情報は、図6Bのスキャンライン0のスパン情報が分割されて生成されたものである。10

#### 【0084】

図6BのスキャンラインNは、オブジェクト602が開始されるスキャンラインである。スキャンラインNは、タイルm内のスキャンライン1に対応し、タイルmはオブジェクト602の左上端である。そのために、タイルm内のスキャンライン1の中には、背景のスパン情報と、オブジェクト602のスパン情報とが発生する。タイルm+1を見るとタイルm+1内のスキャンライン1はオブジェクト602のスパンのみが存在する。

#### 【0085】

<本実施形態のスパンタイル順変換処理の回路構成例>

20

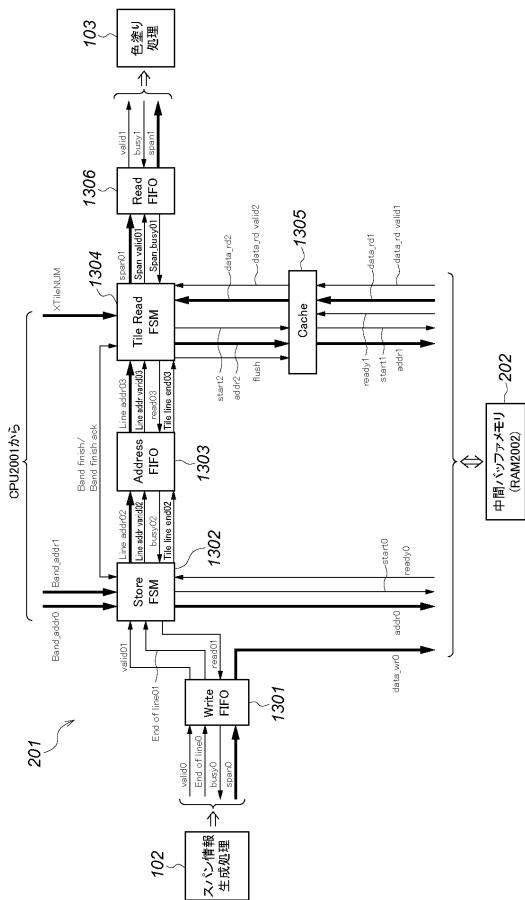

図9は、スパンタイル順変換処理201を実現する回路構成例を示したブロック図である。なお、図9中の"FIFO"はファーストイン・ファーストアウト(先書き込み・先読み出し)のバッファ、"FSM"は特定機能を果たすステート・マシン、"Cache"はキャッシュメモリを表わしている。

#### 【0086】

ライトFIFO(図9中、Write FIFO)1301がスパン情報生成部102から送られてくるスキャン順のスパン情報を受信し、有効なスパン情報を受信したことをvalid01信号でストアFSM(図9中、Store FSM)1302に通知する。ストアFSM1302はライトFIFO1301に有効なスパン情報が入っていると、start0信号を出力することを起点とした中間バッファメモリ202へのライトトランザクションを発生させる。そして、スパン情報を中間バッファメモリ202へ保存する。30

#### 【0087】

ストアFSM1302は、ラインの先頭をEnd of line01信号の出力を検出することで検知する。そして、スキャンラインの先頭のスパン情報を中間バッファメモリ202へ保存するアドレスをアドレスFIFO(図9中、Adress FIFO)1303へ送付する。また、ストアFSM1302は、1つのタイルの高さ分のスパン情報を中間バッファメモリ202に書き出したことを検知すると、Tile line end02信号をアドレスFIFO1303へ送付する。

#### 【0088】

タイルリードFSM(図9中、Tile Read FSM)1304は、アドレスFIFO1303に保持されたスキャンラインのスパン情報の先頭アドレスを獲得する。そして、タイルリードFSM1304が保持する1タイルの高さ分をアドレスするアドレスレジスタに順次記憶する。タイルリードFSM1304は、アドレスFIFO1303からTile line end03信号の出力によってタイルラインの終了を検知すると、記憶したアドレスから中間バッファメモリ202に格納されたスパン情報をリードする。40

#### 【0089】

タイルリードFSM1304が中間バッファメモリ202からスパン情報をリードする際に、キャッシュ(図9中、Cache)1305が中間バッファメモリ202からリードしたスパン情報をアドレスに関連付けてキャッシュする。タイルリードFSM1304のメモリアクセスは、同じスパン情報を次のタイルのリード時にリードする可能性が高いため、キャッシュ1305内にキャッシュされたデータがヒットする場合が多い。50

**【 0 0 9 0 】**

タイルリードFSM1304は、中間バッファメモリ202からキャッシュ1305を経由してリードしたスキャンライン構成のスパン情報を、注目タイルのスパンに分割し、リードFIFO(図9中、Read FIFO)1306へ出力する。リードFIFO1306は、タイル内のスパン情報を色塗り処理103へ送信する。

**【 0 0 9 1 】**

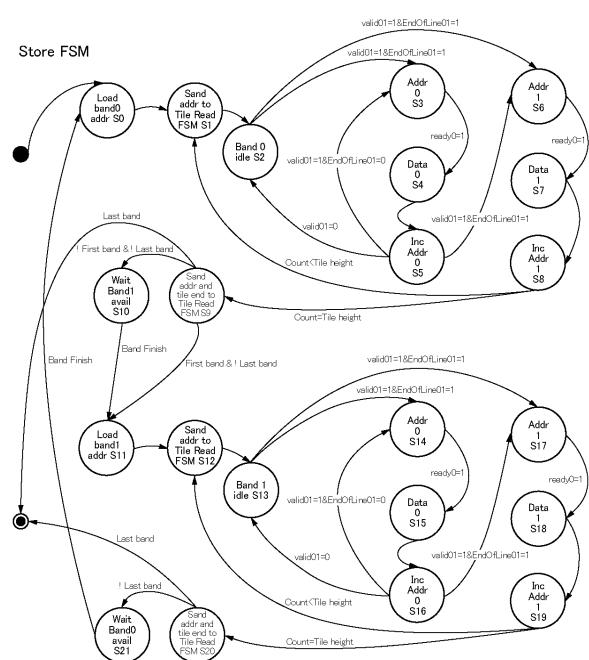

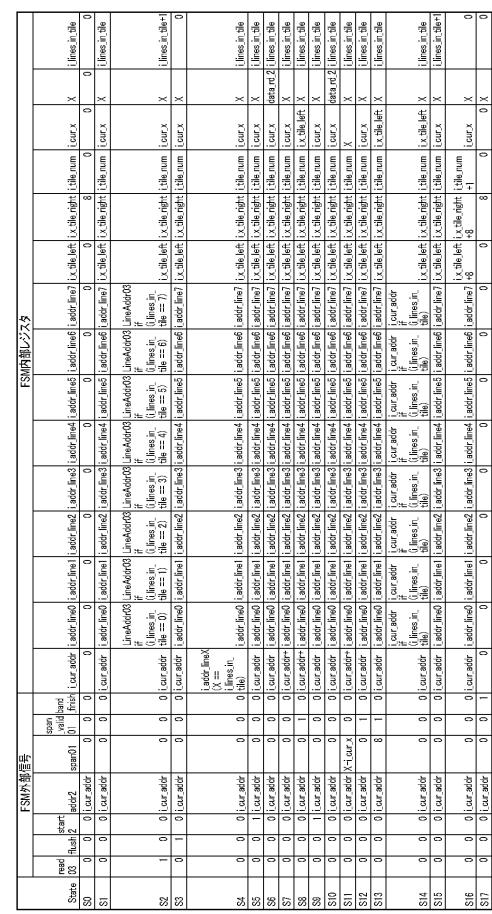

(ストアFSM1302の動作例)

図10Aは、ストアFSM1302の実装を示した状態遷移図である。図10Bは、ストアFSM1302の各状態(State Sx)における出力信号と内部レジスタの状態を示す図である。

10

**【 0 0 9 2 】**

ストアFSMはまず、バンド0のスタートアドレス(Band.addr0)を内部レジスタにロードする(S0)。次に、スタートアドレスを最初のスキャンラインのスタートアドレスとして、アドレスFIFO1303を経由してタイルリードFSM1304へ送信する(S1)。

**【 0 0 9 3 】**

次にライトFIFO1301に有効なスパンデータが格納されているかを、valid01により確認する(S2)。有効なスパンデータが格納されていれば、当該スパンデータを中間バッファメモリ202にライトするために、アドレス信号を出力する(S3)。次に、データをメモリ上に書き出してライトFIFO1301のデータを1つ引き出す(S4)。次に、内部レジスタに保持している書き出し先アドレスをインクリメントする(S5)。ここで、まだライトFIFO1301に有効なデータが保存されていなければ、アイドル(S2)に遷移するが、有効なデータが保持されていれば次のアドレスフェーズ(S3)に遷移する。かかる、S3-S4-S5-(S2)-S3...を繰り返すことで、1ライン分のスパン情報を

20

もし(S2)において、当該有効なデータがラインの最後であれば(End of line01)、ライン最後のアドレスフェーズ(S6)に遷移する。ライン最後のデータをメモリに書き出し(S7)、内部レジスタに保持したアドレス情報とタイル内ライン数カウントをインクリメントする(S8)。タイル内のライン数カウンタが1タイルの高さに達していなければ、既にインクリメントしたアドレスを、次ラインの先頭アドレスとしてアドレスFIFO1303を経由してタイルリードFSM1304へ送信する(S1)。

**【 0 0 9 4 】**

30

タイル内のライン数カウンタが1タイルの高さに達していたならば、タイルの終わりである情報(Tile line end02)を、アドレスFIFO1303を経由してタイルリードFSM1304へ送信する(S9)。次に、最初のバンドでなければ、タイルリードFSM1304からのバンドフィニッシュ信号(Band finish)の出力を待って(S10)、バンド1の先頭アドレスをロードする(S11)。最初のバンドであれば、タイルリードFSM1304からのバンドフィニッシュ信号(Band finish)の出力を待たずに、直接、バンド1の先頭アドレスをロードする(S11)。

**【 0 0 9 5 】**

次に、スタートアドレス(Line addr02)を最初のスキャンラインのスタートアドレスとして、アドレスFIFO1303を経由してタイルリードFSM1304へ送信する(S12)。以降の、S12からS19における処理は、バンドが異なるのみでS1からS8と類似である。

40

**【 0 0 9 6 】**

ライトFIFO1301に有効なスパンデータが格納されているかを確認する(S13)。有効なスパンデータが格納されていれば、当該スパンデータを中間バッファメモリ202にライトするために、まずアドレス信号を出力する(S14)。次に、データをメモリ上に書き出してライトFIFO1301のデータを1つ引き出す(S15)。次に、内部レジスタの保持している書き出し先アドレスをインクリメントする(S16)。まだライトFIFO1301に有効なデータが保存されていなければ、アイドル(S13)に遷移し、有効なデータが保持されていれば次のアドレスフェーズ(S14)に遷移する。もし(S13)において、当該有効なデータがラインの最後であればライン最後のアドレスフェーズ(S17)に遷移する。ライン最

50

後のデータをメモリに書き出し(S18)、内部レジスタに保持したアドレス情報とタイル内のライン数カウントをインクリメントする(S19)。タイル内のライン数カウンタが1タイルの高さに達していなければ、既にインクリメントしたアドレスを、次ラインの先頭アドレスとしてアドレスFIFO1303を経由してタイルリードFSM1304へ送信する(S12)。

#### 【0097】

もし(S19)において、タイル内のライン数カウンタがタイル高さに達していたならば、次にタイルの終わりである情報を、アドレスFIFO1303を経由してタイルリードFSM1304へ送信する(S20)。最後のバンドであったならばシーケンスを終了し、最後のバンドでなければ、次に、タイルリードFSM1304からのバンドフィニッシュ信号の出力を待って(S21)、バンド0の先頭アドレスをロードする(S0)。以上を繰り返す。10

#### 【0098】

このように、ストアFSM1302においては、ダブルバッファ(BAND0, BAND1)処理によって、副走査方向に2タイルライン分を読み出すことで、スパンタイル順変換処理の高速化を図っている。

#### 【0099】

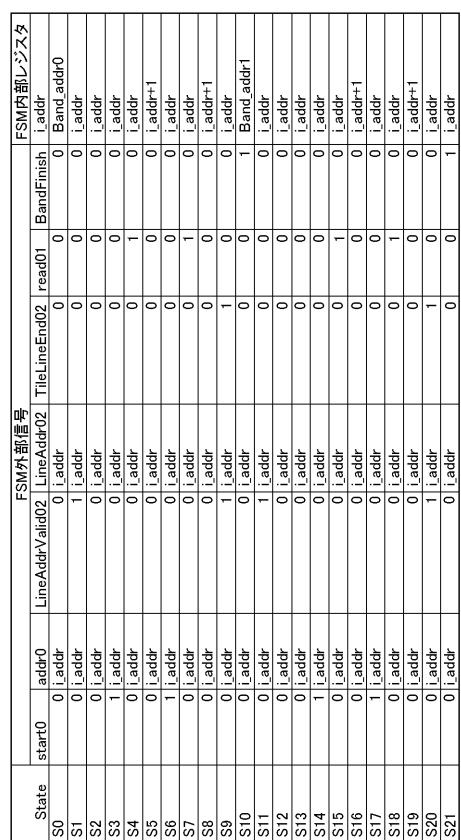

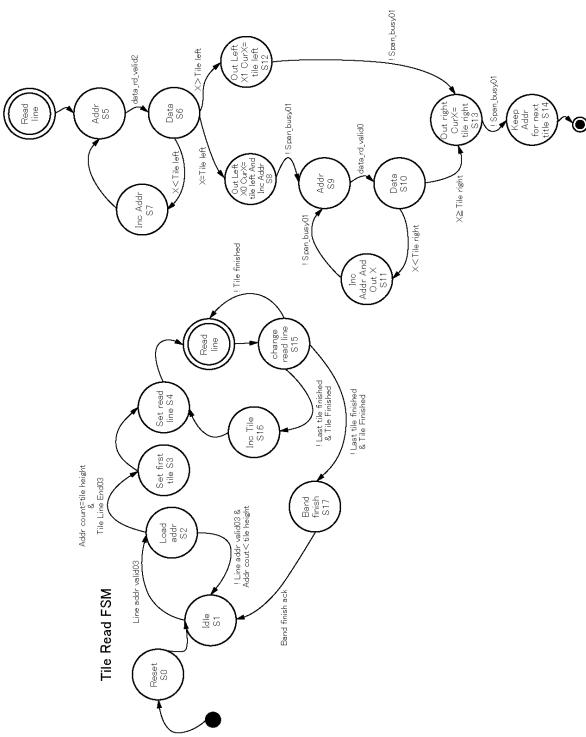

(タイルリードFSM1304の動作例)

図11Aは、タイルリードFSM1304の実装を示した状態遷移図である。図11Bは、タイルリードFSM1304の各状態(State Sx)における出力信号と内部レジスタの状態を示す図である。20

#### 【0100】

初めに内部レジスタの値を初期化し(S0)、次にストアFSM1302からアドレスFIFO1303を経由したLineAddrValid03信号の出力を待つ(S1)。LineAddrValid03信号が出力されたならば、ラインの先頭アドレス(Line addr03)を内部レジスタにロードする(S2)。ラインの先頭アドレスが1タイル内のライン数分送られてきていなければ、アイドル(S1)に戻ってラインの先頭アドレスのロード(S2)を繰り返す。

#### 【0101】

1タイル内のライン数分の先頭アドレスが送られてくれれば、内部レジスタの主走査方向のタイル数カウンタを最初のタイルにセットする(S3)。続いて、中間バッファメモリ202からリードするラインをセットする(S4)。30

#### 【0102】

状態は右図の(S5)に遷移して、当該ラインの最初のスパンデータのアドレスを発行し(S5)、中間バッファメモリ202からキャッシュ1305経由でスパンデータを取得する(S6)。もし(S6)において、取得したスパンデータのX座標が注目タイルの左端よりも小さいX座標であれば、アドレスをインクリメントし(S7)、再度アドレスを発行して(S5)、次のスパンデータを取得する(S6)。

#### 【0103】

もし(S6)において、取得したスパンデータのX座標が注目タイルの左端のX座標と等価であれば、まずタイルの左端のX座標をタイル内のスパンデータの最初の情報として出力して、アドレスをインクリメントする(S8)。次にアドレスを発行し(S9)、中間バッファメモリ202からキャッシュ1305経由でスパンデータを取得する(S10)。取得したスパンデータのX座標が注目タイルの右端よりも小さいX座標であれば、アドレスをインクリメントし(S11)、再度アドレスを発行する(S9)。もし(S10)において、取得したスパンデータのX座標が注目タイルの右端と等価かそれ以上であれば、タイルの右端のX座標をタイル内のスパンデータの右端として出力する(S13)。40

#### 【0104】

もし(S6)において、取得したスパンデータのX座標が注目タイルの左端のX座標より大きいX座標であれば、タイルの左端のX座標をタイル内のスパンデータの左端として出力する(S12)。そして、タイルの右端のX座標をタイル内のスパンデータの右端として出力する(S13)。50

**【0105】**

次に、更新した現状のアドレスをタイル内の当該ラインの注目アドレスとして、注目ラインに関連付けられた内部レジスタに保存し(S14)、状態は左図に戻る。

**【0106】**

現在のアドレスを内部レジスタに保存された次ラインの注目アドレスに切り替えることで、注目ラインを更新する(S15)。更新した注目ラインがタイルの下端でなければ、(S15)から(S5)に遷移し、アドレスを発行して次ラインのスパンデータのリードを開始する(S5)。更新した注目ラインがタイルの下端であれば、注目タイルを主走査方向に更新し(S16)、注目ラインをタイル内の最初のラインに設定する(S4)。そして、アドレスを発行してスパンデータのリードを開始する(S5)。

10

**【0107】**

もし(S15)において、更新した注目ラインがタイルの下端で、かつ主走査方向にリードし、分割すべきタイルの右端のタイルを処理し終えたならば、BandFinish信号を出力する(S17)。ストアFSM1302からの次のバンドバッファが用意されたか(Band finish ack)を確認し、次のバンドバッファが用意されたならばアイドルに戻る(S1)。

**【0108】**

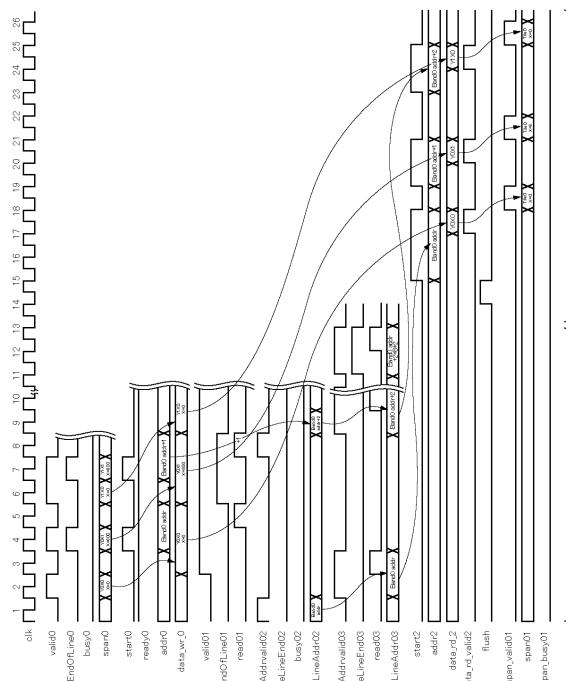

(スパンタイル順変換回路の動作タイミング例)

図12及び図13は、スパンタイル順変換処理201を実行する図9乃至図11に図示のスパンタイル順変換回路の挙動の一部を示した波形図である。なお、"clk"はクロック信号を示し、以下の説明では添付番号をサイクルnとして参照する。従って、図13は図12の後に続く波形図である。

20

**【0109】**

サイクル1において、ストアFSM1302がバンドの先頭アドレスをスキヤンラインの先頭アドレスとして出力し、続くサイクル2で、ライトFIFO1301に最初のスパンデータが受信される。

**【0110】**

サイクル3で、ライトFIFO1301からストアFSM1302にvalid01信号が出力されるため、ストアFSM1302はサイクル4において、start0信号を出力してライトトランザクションをスタートする。ライトトランザクションはサイクル4、5で終了する。ライトFIFO1301に次のスパンデータが既に入力されているため、ストアFSM1302は次のライトトランザクションをサイクル7、8で発生する。

30

**【0111】**

ストアFSM1302は、End of line01信号によってラインの終了であることを検出するため、サイクル9で次ラインの先頭アドレスをLine addr02に載せてアドレスFIFO1303に送信する。スキヤンライン方向のスパンデータの格納がこのように継続し、タイルの最後のラインの際に、ストアFSM1302はTile ine end02信号を出力し、アドレスFIFO1303を介してTile ine end03信号となる。

**【0112】**

Tile line end03信号により、タイルリードFSM1304はまずサイクル14で、キャッシュ1305をflush信号を出力することによって初期化し、続いてタイル内のラインの先頭アドレスからリードトランザクションを発行する。そして、サイクル15～20に示すのように、中間バッファメモリ202からキャッシュ1305を経由してスパンデータを取得する。このスパンデータはサイクル4、5において中間バッファメモリ202に格納されたものをリードしている。

40

**【0113】**

タイルリードFSM1304は、リードしたスキヤンラインのスパンデータをタイル内のスパンデータに分割し、サイクル18、21でリードFIFO1306にタイルに分割されたスパンデータを出力する。

**【0114】**

このようなタイル内に分割されたスパンデータの出力を繰り返し、サイクル31、32

50

においてタイル内の最後のラインの最後のスパンデータを出力すると、注目タイルを主走査方向に1増加し、サイクル36から再度スキャンラインのスパンデータのリードを行う。

#### 【0115】

タイルリードFSM1304は、かかるサイクル14から32の処理を主走査方向のタイルの処理が終了するまで繰り返し、主走査方向のタイルが終了すると、副走査方向の次ぎのタイル(Band1として用意されている)の処理に移る。かかる処理が、ページの全タイルについて行われるまで繰り返される。

#### 【0116】

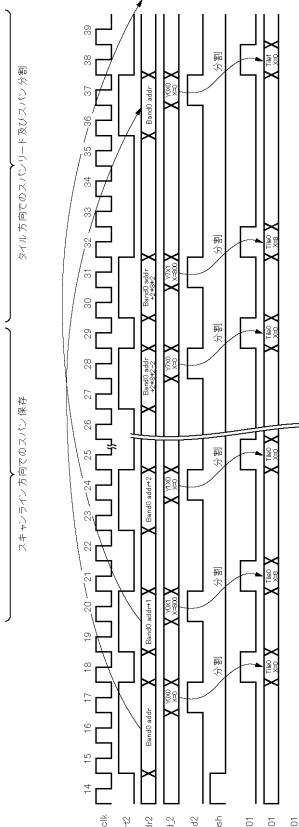

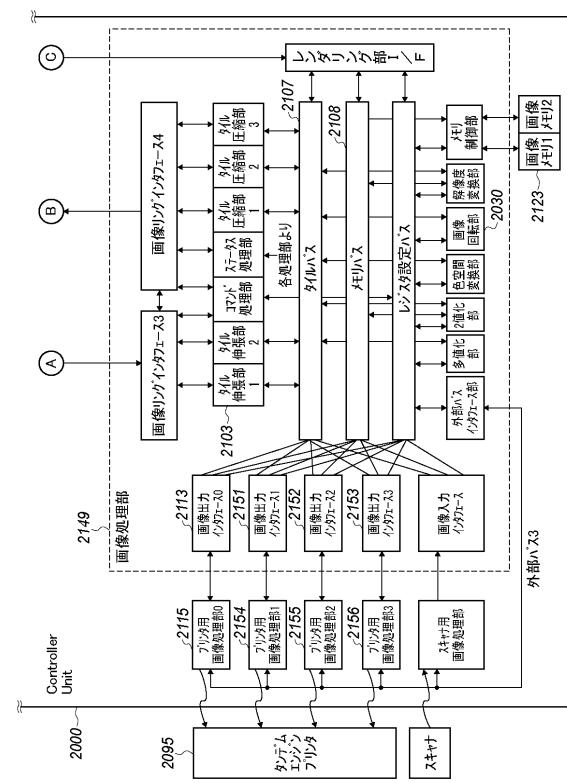

<第2実施形態の画像処理装置の動作例>

10

図14は、第2実施形態におけるページ記述言語印刷の処理フローをまとめたデータ処理フロー図である。第1実施形態ではスパン情報生成処理102で生成されたスパン情報に対してタイル順の変換がされたが、第2実施形態では、色塗り処理後のランレンジス情報に対してタイル順への変換が行われる。

#### 【0117】

ページ記述言語から生成されたディスプレイリスト形式のベクタデータ生成処理101が行われる。次に、ディスプレイリストデータからスキャンラインごとのスパン情報に変換されるスパン情報生成処理102が行われる。生成されたスキャンライン毎のスパン情報は、色塗り処理103によってスパン単位の色が加えられる。単色のスパンでは色情報と繰り返し情報が生成され、イメージ等の画素毎に色の異なるオブジェクトのスパンでは複数の画素のそれぞれの色情報の連続情報からなるスキャンライン毎のランレンジス情報が生成される。第2実施形態では、かかるスキャンライン毎のランレンジス情報がランレンジススタイル変換処理1201への入力情報となる。

20

#### 【0118】

本第2実施形態では、スキャンライン毎のランレンジス情報は、ランレンジスタイル順変換処理1201により、一度中間バッファメモリ1202に格納される。そして、格納されたスキャンライン毎のランレンジス情報をタイル順に読み出し、タイル幅に分割されたランレンジス情報としてピクセル生成処理104に対して出力される。第2実施形態においては、タイル幅に分割されたランレンジス情報ランレンジスタイル変換処理1201からの出力情報となる。

30

#### 【0119】

タイルライン毎のランレンジス情報は、ピクセル生成処理104によって画素情報に変換され、タイル順の画素情報として出力される。

#### 【0120】

ここで、上記のように、中間バッファメモリ202はメインメモリであるRAM2002内的一部領域として確保される。レンダリング部2060から、システムバスブリッジ2007、RAMコントローラ2124経由にてRAM2002内の中間メモリバッファ202の領域がアクセスされる。ランレンジスタイル順変換処理1201を含むスパン情報生成処理102からピクセル生成104までの処理は、レンダリング部2060に実装される。

40

#### 【0121】

その後は、従来例と同様に、圧縮処理107を実施し、圧縮されたタイル順のラスタ画像(圧縮データとも言う)のページ分が図16Aの外部記憶装置2004にスプール処理108される。図16Aの外部記憶装置2004にスプール処理108されたページ分の画像は、図16Bのタイル伸張部2103にて伸張処理109され、タイルバス2107を経由して画像回転部2030等で回転処理110などが行われる。この伸張され回転処理などをしたタイル形式のピクセルデータは、画像出力インターフェース2113、2151、2152、2153にてタイルラスタ変換が行われる。そして、プリンタ画像処理部2115、2154、2155、2156にて色変換処理113やハーフトーン処理114が実施され、プリンタ2095にて印刷処理115がなされる。

50

**【 0 1 2 2 】**

ここで、タイルラスタ変換処理 111 が行われる際にタイル高さ分の中間メモリ 112 が必要になるが、画像出力インターフェース 2113、2151、2152、2153 がメモリバス 2108 を経由して画像メモリ 2123 内の一部領域を使用する。

**【 0 1 2 3 】**

(第 2 実施形態におけるタイル順への変換の具体例)

図 15 は、図 14 にて説明した第 1 実施形態の処理フローにおいてベクタデータ生成処理 101 からピクセル生成処理 104 までの処理データ例を示した模式図である。従来例における、図 18 と対比すると本願発明の作用効果が明瞭となる。なお、従来との対比を明瞭にするため、背景 601 と赤い矩形オブジェクト 602 とイメージ 603 とは、図 18 と同様である。

10

**【 0 1 2 4 】**

ベクタデータ生成処理 101 により、図 15 の最上段に示すベクタデータが生成される。

。

**【 0 1 2 5 】**

生成されたベクタデータはスパン情報生成処理 102 により、図 15 の 2 段目にしめすスパン情報に変換される。スパン A は背景しかないためページの左端から右端までのスパンとなる。スキャンライン B C D は、赤い矩形オブジェクト 602 が存在するスキャンラインである。そのため、スパン B は背景のスパン、赤い矩形オブジェクトのスパンであるスパン C、さらに背景のスパン D が生成される。スキャンライン B E F は、赤い矩形オブジェクト 602 とイメージ 603 が存在するスキャンラインである。そのため、スパン B は背景のスパン、赤い矩形オブジェクト 602 のスパンであるスパン E、さらにイメージ 603 のスパン F が生成される。

20

**【 0 1 2 6 】**

続いて、図 15 の 3 段目に示すように、スキャンラインのスパン情報に対して色塗り処理 103 が実施されて、ランレングス情報が生成される。

**【 0 1 2 7 】**

続いて、図 15 の 4 段目に示すように、本実施形態のランレングスタイル順変換処理 1201 によって、スキャンライン単位のランレングス情報からタイル内のスキャンラインのランレングス情報に変換される。

30

**【 0 1 2 8 】**

スキャンライン A は、4 つのタイル T1, T2, T3, T4 に分割される。背景であるためページの左端から右端までのスパンであったスパン A のランレングス情報は、4 つのタイル幅のランレングス情報に分割される。

**【 0 1 2 9 】**

スキャンライン B C D のランレングス情報も、4 つのタイル T1, T2, T3, T4 に分割される。タイル形式への変換前のスキャンライン B C D のランレングス情報は、背景と赤い矩形オブジェクトによって、スパン B、スパン C、スパン D の 3 つのランレングス情報であった。これが、タイル T1 はスパン B のランレングス情報、タイル T2 はスパン C が分割された前方のランレングス情報、タイル T3 もスパン C が分割された後方のランレングス情報、タイル T4 はスパン D のランレングス情報に分割される。

40

**【 0 1 3 0 】**

スキャンライン B E F のランレングス情報も、4 つのタイル T1, T2, T3, T4 に分割される。タイル形式への変換前のスキャンライン B E F のランレングス情報は、背景と赤い矩形オブジェクトとイメージオブジェクトによって、スパン B、スパン E、スパン F の 3 つのランレングス情報であった。タイル T1 はスパン B のランレングス情報である。しかし、タイル T2 はスパン E のランレングス情報と分割されたスパン F の前方のランレングス情報、タイル T3 は分割されたスパン F の中間のランレングス情報、タイル T4 もスパン F の後方のランレングス情報に分割される。

**【 0 1 3 1 】**

次に、図15の5段目に示すように、ランレンジス情報からピクセル生成処理104により画素情報が生成される。

【0132】

本実施形態では、このピクセル生成処理104が終了した時点で、図15の最下段に示したように、タイル順の画像情報が完成することになる。

【0133】

なお、第2実施形態におけるランレンジスタイル順変換処理1201を実現する回路構成は、第1実施形態の図9乃至図13に示した回路例が開示されれば、当業者により容易に構成できるものである。

【0134】

10

<他の実施形態>

なお、本実施形態では、スパンタイル順変換処理201を実現するステートマシンによる回路例を詳細に示したが、本発明のスパンタイル順変換処理201は図5に示したフローチャートに従う処理が実現できれば、どのような回路構成でも可能である。

【0135】

又、本実施形態では、スパンタイル順変換処理201やランレンジスタイル順変換処理1201が、図16Aのレンダリング部2060に含まれる構成を説明したが、これらの処理が独立の構成要素により処理されてもよい。あるいは、他の構成要素に含まれたり、更に大きな構成要素の一部に組み込まれてもよい。

【0136】

20

更に、本実施形態では、処理結果のタイル形式の画素情報は印刷処理されるものとして説明したが、画素情報による処理、例えば表示処理などに使用されてもよい。本発明は、多量のデータからタイル形式の画素情報を資源を節約しながら高速に実現する構成を提案するものであり、かかる処理を必要とする技術に適用可能である。

【0137】

又、本発明は、複数の機器（例えばホストコンピュータ、インターフェース機器、プリンタなど）から構成されるシステムあるいは統合装置に適用しても、ひとつの機器からなる装置に適用してもよい。

【0138】

30

又、本発明の目的は、前述した実施形態の機能を実現するソフトウェアのプログラムコードを記録した記憶媒体（または記録媒体）を、システムあるいは装置に供給する。そして、そのシステムあるいは装置のコンピュータ（またはCPUやMPU）が記憶媒体に格納されたプログラムコードを読み出し実行することによっても、達成されることはあるまでもない。この場合、記憶媒体から読み出されたプログラムコード自体が前述した実施形態の機能を実現することになり、そのプログラムコードを記憶した記憶媒体は本発明を構成することになる。又、コンピュータが読み出したプログラムコードを実行することにより、前述した実施形態の機能が実現されるだけではない。そのプログラムコードの指示に基づき、コンピュータ上で稼働しているオペレーティングシステム(OS)などが実際の処理の一部または全部を行い、その処理によって前述した実施形態の機能が実現される場合も含まれることは言うまでもない。

40

【0139】

さらに、記憶媒体から読み出されたプログラムコードが、コンピュータに挿入された機能拡張カードやコンピュータに接続された機能拡張ユニットに備わるメモリに書き込まれる。その後、そのプログラムコードの指示に基づき、その機能拡張カードや機能拡張ユニットに備わるCPUなどが実際の処理の一部または全部を行なう。このような処理によって前述した実施形態の機能が実現される場合も含まれることは言うまでもない。

【0140】

本発明を上記記憶媒体に適用する場合、その記憶媒体には、先に説明したフローチャートに対応するプログラムコードが格納されることになる。

【図面の簡単な説明】

50

## 【0141】

【図1】第1実施形態の処理フローの例を示す図である。

【図2】第1実施形態のデータ処理の具体例を示す図である。

【図3】本実施形態で使用されるディスプレイリストのデータ形式の例を示す図である。

【図4】本実施形態で作成されるタイル画像の構成を示した模式図である。

【図5】第1実施形態のスパンタイル順変換処理の手順例を示したフローチャートである。

。

【図6A】本実施形態におけるスパン情報のフォーマット例を示す図である。

【図6B】第1実施形態の図2の具体例におけるスパン情報の例を示す図である。

【図7】第1実施形態におけるスパンタイル順変換処理を示す模式図である。 10

【図8】第1実施形態における図6Bのスパン情報のスパンタイル順変換処理後のタイル順のスパンデータの例を示す図である。

【図9】第1実施形態のスパンタイル順変換処理を実現する回路構成例を示したブロック図である。

【図10A】図9の回路を構成するストアFSM1302の状態遷移を示した状態遷移図である。

【図10B】図10AのストアFSM1302の各状態の出力信号と内部レジスタの状態を示した図である。

【図11A】図9の回路を構成するタイルリードFSM1304の状態遷移を示した状態遷移図である。 20

【図11B】図11AのタイルリードFSM1304の各状態の出力信号と内部レジスタの状態を示した図である。

【図12】図9の回路構成におけるスパンタイル順変換処理の動作例を示した信号波形図である。

【図13】図9の回路構成におけるスパンタイル順変換処理の動作例を示した信号波形図である。

【図14】第2実施形態の処理フローの例を示す図である。

【図15】第2実施形態のデータ処理の具体例を示す図である。

【図16A】画像処理装置のコントラーラ部の構成例を示すブロック図である。

【図16B】画像処理装置のコントラーラ部の構成例を示すブロック図である。 30

【図17】従来技術におけるレンダリング部の構成例を示す図である。

【図18】従来技術におけるタイル順の画素情報作成の処理フローの例を示す図である。

【図19】従来技術におけるデータ処理の具体例を示す図である。

【 図 1 】

【 义 2 】

【 図 3 】

〔四〕

【図5】

【図6 A】

【図6 B】

【図7】

【 四 8 】

【 四 9 】

【図 10 A】

【 図 1 0 B 】

【図 11A】

【図 11B】

【図 12】

【図 13】

【図14】

【図15】

【図16A】

【図16B】

【図17】

【図18】

【図19】

---

フロントページの続き

(72)発明者 松井 信明

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 阿知波 健

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 立澤 正樹

(56)参考文献 特開2006-327155(JP,A)

特開2004-122376(JP,A)

特開2008-294831(JP,A)

(58)調査した分野(Int.Cl., DB名)

B 41 J 5 / 30

B 41 J 29 / 38

H 04 N 1 / 21