(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2013-0048136

(43) 공개일자 2013년05월09일

(51) 국제특허분류(Int. Cl.)

G11B 5/84 (2006.01)

(21) 출원번호 10-2012-0067507

(22) 출원일자 2012년06월22일

심사청구일자 없음

(30) 우선권주장

13/286,718 2011년11월01일 미국(US)

(71) 출원인

엘에스아이 코포레이션

미국 캘리포니아주 95131, 새너제이, 라이더 파크

드라이브 1320

(72) 발명자

피셔 조나단 에이치

미국 콜로라도주 80503 롱몬트 아파트먼트 5108 9

애비뉴 2424

(74) 대리인

제일특허법인

전체 청구항 수 : 총 10 항

(54) 발명의 명칭 디지털 입력 검출기 및 관련 적응형 전원

### (57) 요 약

저장 장치 혹은 다른 타입의 처리 장치의 인터페이스 회로는 디지털 입력 검출기 및 적응형 전원을 포함한다. 디지털 입력 검출기는 입력 트랜지스터를 포함한다. 적응형 전원은 입력 트랜지스터의 임계 전압에 따라 달라지는 가변 공급 전압을 디지털 입력 검출기에 제공한다. 일 실시예에서, 적응형 전원이 디지털 입력 검출기에 제공하는 가변 공급 전압은, 입력 신호의 예상 논리 레벨의 함수로서 결정된 설정 포인트 값에 관한 입력 트랜지스터의 임계 전압에 따라 달라진다. 예컨대, 이 설정 포인트 값은, 최소 예상 논리 하이 입력 신호 레벨의 함수로서 결정될 수 있다. 이러한 배치예에서, 입력 트랜지스터는 최소 예상 논리 레벨을 가진 입력 신호에 대한 임계 전압으로, 혹은 이에 가깝게 입력 트랜지스터가 바이어스되도록, 선택된다.

### 대 표 도 - 도3

## 특허청구의 범위

### 청구항 1

입력 트랜지스터를 포함한 디지털 입력 검출기와,

상기 디지털 입력 검출기에 가변 공급 전압을 제공하는 출력을 구비한 적응형 전원(adaptive power supply)을 포함하고,

상기 적응형 전원이 상기 디지털 입력 검출기에 제공하는 상기 가변 공급 전압은 상기 입력 트랜지스터의 임계 전압에 따라 달라지는

장치.

### 청구항 2

제 1 항에 있어서,

상기 적응형 전원이 상기 디지털 입력 검출기에 제공하는 상기 가변 공급 전압은, 입력 신호의 예상 논리 레벨의 함수로서 결정된 설정 포인트 값(a set point value)에 관한 상기 입력 트랜지스터의 상기 임계 전압에 따라 달라지는

장치.

### 청구항 3

제 2 항에 있어서,

상기 설정 포인트 값은, 최소 예상 논리 하이 입력 신호 레벨과 상기 입력 트랜지스터의 상기 임계 전압의 함수로서 결정되는

장치.

### 청구항 4

제 3 항에 있어서,

상기 설정 포인트 값은, 최소 예상 논리 하이 입력 신호 레벨과 상기 입력 트랜지스터의 상기 임계 전압의 합으로 결정되는

장치.

### 청구항 5

제 2 항에 있어서,

상기 설정 포인트 값은, 상기 예상 논리 레벨을 가진 입력 신호에 대한 상기 임계 전압으로, 혹은 이에 가깝게 상기 입력 트랜지스터가 바이어스되도록, 선택되는

장치.

### 청구항 6

제 1 항에 있어서,

상기 입력 트랜지스터는, 상기 적응형 전원의 출력에 연결된 소스와, 낮은 공급 전위에 연결된 드레인과, 상기 디지털 입력 검출기의 입력 노드에 연결된 게이트를 가진 제 1 PMOS 트랜지스터를 포함하고, 상기 제 1 PMOS 트랜지스터의 드레인은 상기 디지털 입력 검출기의 제 1 출력 노드에도 연결되어 있는

장치.

### 청구항 7

제 6 항에 있어서,

상기 디지털 입력 검출기는, 제 2 PMOS 트랜지스터 및 제 3 PMOS 트랜지스터를 적어도 포함한 입력 레벨 히스테리시스 회로(input level hysteresis circuitry)를 더 포함하고,

상기 제 2 PMOS 트랜지스터 및 상기 제 3 PMOS 트랜지스터 각각의 드레인은 상기 제 1 PMOS 트랜지스터의 소스에 연결되어 있고, 각각의 소스는 상기 적응형 전원의 상기 출력에 연결되어 있으며, 상기 제 2 PMOS 트랜지스터의 게이트는 상기 제 1 PMOS 트랜지스터의 소스에 연결되어 있고, 상기 제 3 PMOS 트랜지스터의 게이트는 상기 디지털 입력 검출기의 제 2 출력 노드에 연결되어 있는

장치.

### 청구항 8

제 6 항에 있어서,

상기 디지털 입력 검출기는 제 1 NMOS 트랜지스터 및 제 2 NMOS 트랜지스터를 더 포함하고,

상기 제 1 NMOS 트랜지스터 및 상기 제 2 NMOS 트랜지스터 각각의 게이트는 상기 제 1 PMOS 트랜지스터의 게이트에 연결되어 있고, 상기 제 1 NMOS 트랜지스터의 드레인은 상기 제 1 PMOS 트랜지스터의 드레인에 연결되어 있으며, 상기 제 2 NMOS 트랜지스터의 드레인은 상기 제 1 NMOS 트랜지스터의 소스에 연결되어 있고, 상기 제 2 NMOS 트랜지스터의 소스는 상기 낮은 공급 전위에 연결되어 있는

장치.

### 청구항 9

제 1 항에 있어서,

상기 적응형 전원은,

제 1 입력, 제 2 입력, 및 출력을 가진 연산 증폭기 - 상기 제 1 입력은 기준 전압원에 연결되어 있고, 상기 출력은 상기 가변 공급 전압을 상기 디지털 입력 검출기에 제공함 - 와,

상기 디지털 입력 검출기의 상기 입력 트랜지스터에 대한 하나 이상의 대응하는 파라미터 변경 특성에 실질적으로 매칭되는 하나 이상의 파라미터 변경 특성을 가진 적응형 전원 트랜지스터 - 상기 적응형 전원 트랜지스터의 소스는 상기 연산 증폭기의 상기 출력에 연결되어 있고, 게이트와 드레인은 서로 연결되어 있음 - 와,

직렬로 연결된 제 1 저항 소자 및 제 2 저항 소자를 포함한 전압 분할기 회로 - 상기 제 1 저항 소자 및 상기 제 2 저항 소자의 직렬 접속의 제 1 단부는 상기 적응형 전원 트랜지스터의 게이트 및 드레인에 연결되어 있고, 상기 제 1 저항 소자 및 상기 제 2 저항 소자의 직렬 접속의 제 2 단부는 낮은 공급 전위에 연결되어 있으며, 상기 제 1 저항 소자와 상기 제 2 저항 소자 사이의 텝은 피드백 라인을 통해서 상기 연산 증폭기의 상기 제 2 입력에 연결되어 있음 - 를 포함하는

장치.

## 청구항 10

입력 트랜지스터를 포함하는 디지털 입력 검출기를 제공하는 단계와,

상기 디지털 입력 검출기에 가변 공급 전압을 제공하는 단계를 포함하고,

상기 디지털 입력 검출기에 제공되는 상기 가변 공급 전압은 상기 입력 트랜지스터의 임계 전압에 따라 달라지는

방법.

## 명세서

### 배경기술

- [0001] 서로 다른 다양한 타입의 데이터 처리 시스템에 비휘발성 데이터 저장 장치를 제공하는데 하드 디스크 드라이브(HDD)와 같은 디스크 기반 저장 장치가 사용되고 있다. 전형적인 HDD는, 플래터라고도 불리는 원판 형상의 저장 디스크를 하나 이상 유지하는 스판들을 포함한다. 각각의 저장 디스크는 알루미늄 혹은 유리와 같은 비자기 물질로 이루어진 기판을 포함하며, 이는 하나 이상의 얇은 자기 물질 층으로 코팅되어 있다. 동작시에, 디스크는 고속으로 회전하고, 판독/기록 헤드가 포지셔닝 아암에 의해 디스크 표면을 가로질러서 정확하게 이동함으로써, 저장 디스크의 트랙으로부터 데이터를 판독하거나 트랙에 데이터를 기록한다.

- [0002] 통상 HDD는, 컴퓨터 혹은 다른 처리 장치로부터의 데이터를 저장 디스크에 기록하기에 적합한 형식으로 처리하고, 저장 디스크로부터 판독된 신호 파형을 컴퓨터에 전달하기 위한 데이터로 변환하는 SOC(a system-on-chip)를 포함한다. HDD는, 저장 디스크로부터 데이터를 판독하거나 저장 디스크에 데이터를 기록하는데 사용되는 판독/기록 헤드에 이 SOC를 인터페이스시키는 프리앰프를 포함한다. SOC는 디지털 인터페이스를 거쳐서 프리앰프와 통신함으로써, 신호 이득 및 대역폭과 같은 프리앰프 파라미터를 프로그래밍하고, 이 프리앰프에 의해 검출된 시스템 오류와 같은 정보를 수신한다.

- [0003] SOC는 확장형(extensive) 디지털 회로를 갖고 있고, 전형적으로 개선된 CMOS 기술을 이용함으로써, 비용 및 성능면에서의 목적을 만족시켰다. 이는, 프리앰프가 이용하는 전압과는 다른 전원 전압을 SOC가 이용하게 하며, SOC와 프리앰프 사이의 디지털 인터페이스가 항상 3.3V, 2.5V 혹은 1.8V 논리 레벨과 같은, 다양한 각각의 논리 하이 입력 신호 레벨을 이용하게 했다. 프리앰프는 저장 디스크를 포맷하는, 공장의 서보 라이터에서도 이용되며, 서보 라이터 중 일부는 5V 논리 레벨을 이용해서 프리앰프와 통신한다.

### 발명의 내용

#### 해결하려는 과제

- [0004] 본 발명의 예시적인 실시예는 하나 이상의 관련 적응형 전원에 의해 전력을 공급받는 개선된 디지털 입력 검출기를 제공하며, 이 디지털 입력 검출기는, HDD와 같은 디스크-기반 저장 장치의 프리앰프의 일부가 될 수도 있고 혹은 다른 타입의 처리 장치의 일부가 될 수도 있는 인터페이스 회로에서 이용하기에 적합하다.

#### 과제의 해결 수단

- [0005] 일 실시예에서, 장치는 디지털 입력 검출기 및 적응형 전원을 포함한다. 적응형 전원은, 디지털 입력 검출기의 입력 트랜지스터의 임계 전압에 따라 달라지는 가변 공급 전압을 디지털 입력 검출기에 제공한다. 이 장치는 저장 장치 혹은 다른 타입의 처리 장치의 인터페이스 회로의 일부가 될 수도 있고, 이 인터페이스 회로를 포함할 수도 있다.

- [0006] 적응형 전원이 디지털 입력 검출기에 제공하는 가변 공급 전압은, 입력 신호의 예상 논리 레벨의 함수로서 결정되는 설정 포인트 값(a set point value)에 관한 입력 트랜지스터의 임계 전압에 따라서 달라질 수 있다. 예컨대, 이 설정 포인트 값은 최소 예상 논리 하이 입력 신호 레벨의 함수로서 결정될 수 있다. 이 경우, 입력 트랜지스터는, 최소 예상 논리 하이 입력 신호 레벨을 가진 입력 신호에 대한 임계 전압으로, 혹은 이에 가깝게 바

이어스된다.

- [0007] 하나 이상의 예시적인 실시예는, 디지털 입력 검출기를 구비하고 있는 디스크-기반 저장 장치 혹은 다른 처리 장치를 크게 개선시킨다. 예컨대, 적응형 전원이 디지털 입력 검출기에 제공하는 가변 공급 전압은, 디지털 입력 검출기의 입력 트랜지스터의 임계 전압의 변화를 추종하도록 구성될 수 있다. 이로써, 입력 신호가 예상 최소값 부근의 논리 하이 레벨을 가질 때, 디지털 입력 검출기로부터의 전류량을 제한할 수 있고, 임계 전압은 프로세스 및 온도에 따라 달라진다.

## 도면의 간단한 설명

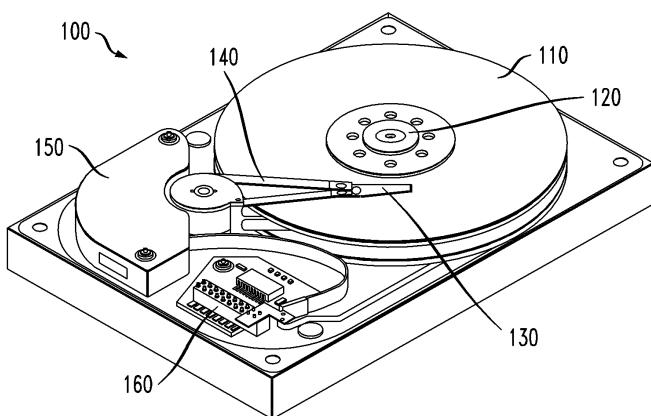

- [0008] 도 1은 본 발명의 예시적인 실시예에 따른 디스크-기반 저장 장치의 사시도,

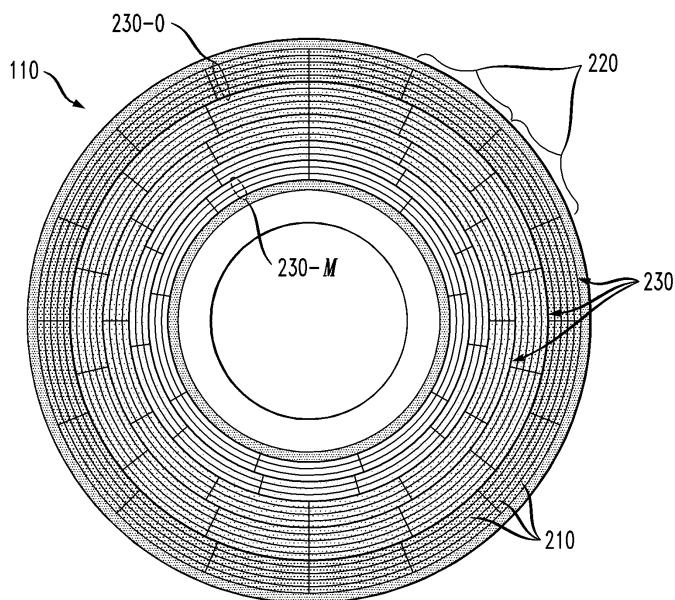

도 2는, 도 1의 저장 장치에 있어서의 저장 디스크의 정면도,

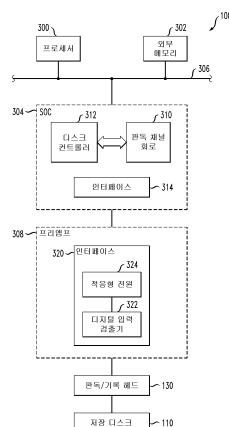

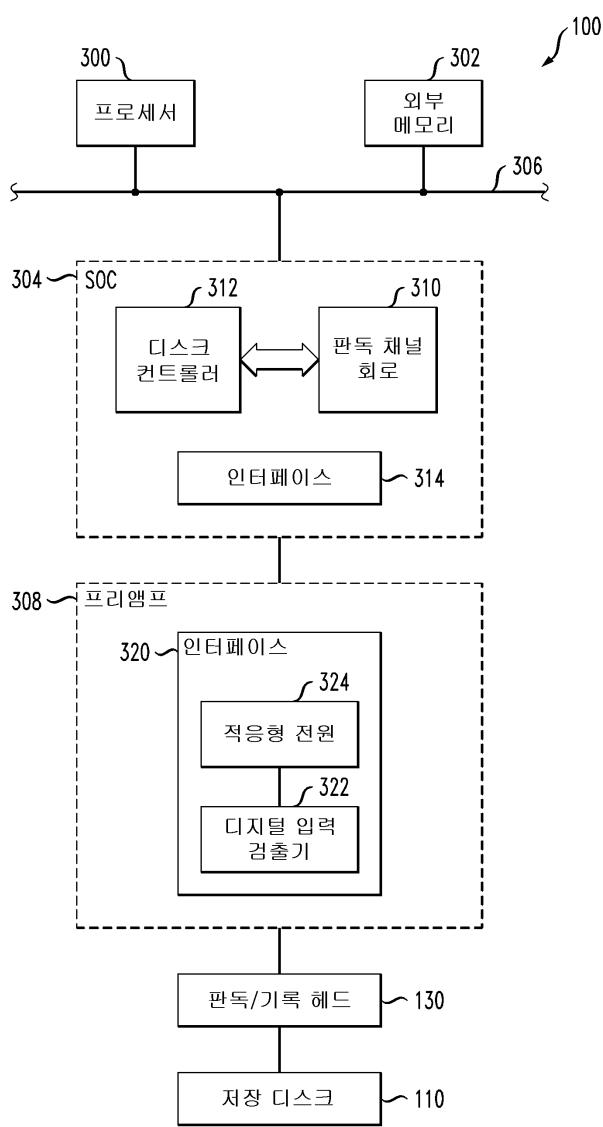

도 3은, 디지털 입력 검출기 및 관련된 적응형 전원을 구비한 예시적인 프리앰프를 포함하는, 도 1의 저장 장치의 일부 블록도,

도 4는, 도 3의 프리앰프의 디지털 입력 검출기 및 다른 인터페이스 회로를 나타내는 개략도,

도 5는, 도 3의 프리앰프의 적응형 전원의 개략도,

도 6은, 도 1의 저장 장치와, 데이터 처리 시스템의 호스트 처리 장치 사이의 상호 접속을 나타내는 도면,

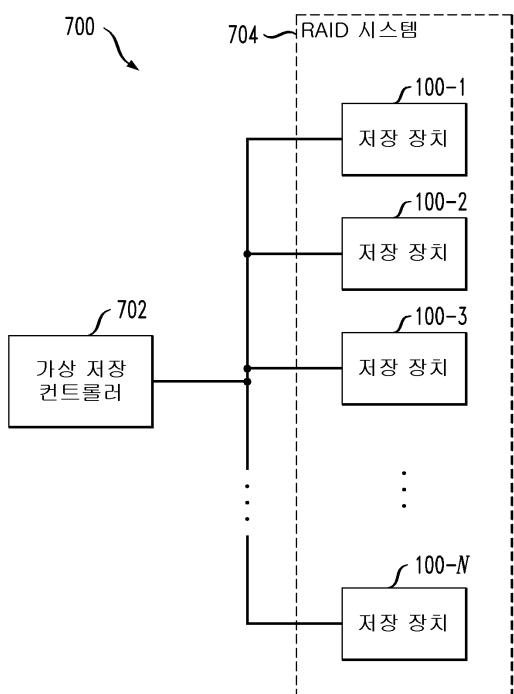

도 7은, 도 1에 도시된 타입의 디스크-기반 저장 장치를 복수 구비한 가상 저장 시스템을 나타내는 도면이다.

## 발명을 실시하기 위한 구체적인 내용

- [0009] 본 발명의 실시예는 예시적인 디스크-기반 저장 장치, 인터페이스 회로 및 관련된 디지털 입력 검출 기술과 관련해서 설명될 것이다. 그러나, 본 발명의 이 실시예 및 다른 실시예가, 개선된 디지털 입력 검출 성능이 요구되는 어떤 처리 장치 애플리케이션에도 널리 적용될 수 있다는 것을 이해할 것이다.

- [0010] 도 1은 본 발명의 예시적인 실시예에 따른 디스크-기반 저장 장치(100)를 도시하고 있다. 본 실시예의 저장 장치(100)는 상세하게는, 저장 디스크(110)를 구비한 HDD를 포함하고 있다. 저장 디스크(110)는 자화 상태의 형태로 데이터를 저장할 수 있는 하나 이상의 자기 물질이 코팅된 저장 표면을 갖고 있다. 저장 디스크(110)는 스픈들(120)에 접속되어 있다. 스픈들(120)은 도시 생략한 스픈들 모터에 의해 구동되어서 저장 디스크(110)를 고속으로 회전시킨다.

- [0011] 데이터는, 포지셔닝 아암(140)에 장착된 판독/기록 헤드(130)를 통해서, 저장 디스크(110)로부터 판독되거나 저장 디스크(110)에 기록된다. 저장 디스크(110)의 저장 표면 상에서의 판독/기록 헤드의 위치는, 전자기 액츄에이터(150)에 의해서 제어된다. 본 실시예에서의 전자기 액츄에이터(150) 및 관련 구동 회로는, 이하 저장 장치(100)의 '제어 회로'라고도 불리는 것의 일부를 포함하는 것으로 볼 수 있다. 본 실시예에서의 이러한 제어 회로는, 이 조립체의 반대쪽에 배치되어 있어서 도 1의 사시도에서는 도시되지 않은 다른 전자 구성 요소를 더 포함하고 있는 것으로 가정한다. 따라서, 여기서 사용되는 용어 '제어 회로'는 예컨대, 구동 전자 장치, 신호 처리 전자 장치, 및 관련 처리 회로와 메모리 회로를 널리 포함하되, 이것으로 한정되는 것은 아니며, 저장 장치의 저장 디스크의 저장 표면에 대한 판독/기록 헤드의 위치를 제어하는데 이용되는 다른 구성 요소도 더 포함할 수도 있다. 커넥터(160)를 이용해서 저장 장치(100)를 호스트 컴퓨터 혹은 다른 관련 처리 장치에 접속시킨다.

- [0012] 도 1에는 본 발명의 실시예가 저장 디스크(110), 판독/기록 헤드(130), 및 포지셔닝 아암(140)을 하나만 갖고 있는 것으로 도시되어 있지만, 이는 단지 예시로, 본 발명의 다른 실시예에서는 이들 구동 소자 및 다른 구성 소자가 복수인 예를 포함할 수 있다는 것을 이해할 것이다. 예컨대, 다른 일 실시예에서는, 복수의 저장 디스크가 같은 스픈들에 부착되어서 모든 디스크가 같은 속도로 회전할 수도 있고, 복수의 판독/기록 헤드 및 관련된 포지셔닝 아암이 하나 이상의 액츄에이터에 연결될 수도 있다.

- [0013] 또한, 도 1에 도시된 저장 장치(100)는, 상세하게 도시된 소자에 대해서 혹은 이 소자 대신에, 이러한 저장 장치의 종래의 구현예에서 일반적으로 볼 수 있는 타입의 소자를 하나 이상 포함할 수 있다. 이러한 종래의 구성 요소는 당업자에게 공지되어 있으므로 여기서는 상세하게 설명하지 않는다. 도 1에 도시된 소자의 특정한 배치 예는 단지 예시적으로 제공된 것이라는 것도 이해할 것이다. 개시된 기법은, 디지털 입력 검출 성능을 제공하는

것이 바람직한 임의의 저장 장치 혹은 처리 장치 애플리케이션에 제한없이 널리 적용될 수 있다. 따라서 당업자라면 다른 다양한 저장 장치 및 처리 장치의 구성이 본 발명의 실시예를 구현하는데 이용될 수 있다는 것을 이해할 것이다.

- [0014] 도 2는 저장 디스크(110)의 저장 표면을 더 상세하게 도시하고 있다. 도시된 바와 같이, 저장 디스크(110)의 저장 표면은 동심의 트랙(210)을 복수 포함하고 있다. 각각의 트랙은, 이후의 검색에 이용하기 위해서, 데이터 블록을 저장할 수 있는 복수의 섹터(220)로 나누어진다. 저장 디스크의 바깥쪽 모서리를 향해서 위치된 트랙은 저장 디스크의 중심을 향해서 위치된 트랙에 비해서 원주가 더 크다. 이 트랙은 복수의 고리형 영역(230)으로 그룹화되고, 여기서 이 영역 중 주어진 영역 내에 위치한 트랙은 동일한 수의 섹터를 갖고 있다. 외측 영역에 위치한 트랙은 내측 영역에 위치한 트랙보다 더 많은 섹터를 갖고 있다. 이 예에서, 저장 디스크(110)는 최외각 영역(230-0) 및 최내각 영역(230-M)을 포함한, M+1개의 영역을 갖고 있는 것으로 가정한다.

- [0015] 저장 디스크(110)의 외측 영역은 내측 영역보다 더 높은 데이터 전송 속도를 제공한다. 이는 부분적으로, 본 실시예의 저장 디스크가 일단 가속되어서 동작 속도로 회전하면, 판독/기록 헤드의 위치에 관계없이 일정한 각속도 또는 반경 속도로 회전하지만, 내측 영역의 트랙은 외측 영역의 트랙보다 원주가 작기 때문이다. 따라서, 판독/기록 헤드가 외측 영역의 트랙 중 하나의 위에 위치하면, 내측 영역의 트랙 중 하나의 위에 위치할 때보다, 저장 디스크의 주어진  $360^\circ$  회전 동안 디스크 표면을 따라서 더 긴 직선 거리를 커버한다. 저장 디스크의  $360^\circ$  회전 각각에 동일한 시간이 걸리기 때문에, 이러한 배치는 등각속도(CAV)를 갖는 것으로 간주되지만, CAV 동작이 본 발명의 필요 조건은 아니라는 점을 이해할 것이다.

- [0016] 저장 장치(110)의 전체 저장 표면에서 데이터 비트 밀도는 일반적으로 일정하기 때문에, 데이터 전송 속도는 외측 영역에서 더 높아진다. 각각의 외측 영역은 내측 영역보다 더 많은 데이터를 저장하기 때문에, 판독/기록 헤드가 외측 영역의 데이터에 액세스할 때 주어진 양의 데이터를 판독하기 위해서 자주 이동될 필요는 없다. 따라서, 내측 영역의 트랙보다 외측 영역의 트랙에서, 더 높은 속도로 데이터를 주고 받을 수 있다.

- [0017] 따라서, 저장 디스크의 최외각 환형 영역(230-0)은 저장 디스크의 최내각 환형 영역(230-M)보다 더 높은 평균 데이터 전송 속도를 갖는다. 주어진 실시예에서, 최내각 환형 영역과 최외각 환형 영역 사이의 평균 데이터 전송율은 2배 이상 차이가 날 수 있다.

- [0018] 단지 예로서 제공되는 일 실시예로서, 최외각 환형 영역은 초당 약 2.3기가비트(Gb/s)의 데이터 전송 속도를 가질 수 있는 반면, 최내각 환형 영역은 약 1.0Gb/s의 데이터 전송 속도를 갖는다. 이러한 구현예에서, 상술한 바와 같은 최외각 환형 영역에서의 약 2.3Gb/s부터 최내각 환형 영역의 1.0Gb/s까지의 데이터 전송 속도의 범위에서, HDD는 상세하게는 500GB의 총 저장 용량 및 7200RPM의 스팬들 속도를 갖는다.

- [0019] 상술한 실시예에서 참조하는 특정 데이터 전송 속도 및 다른 특성은 단지 예시의 목적으로 제공된 것으로, 어떤 식으로든 한정의 의미로 해석되어서는 안된다. 다른 실시예에서는 다른 다양한 데이터 전송 속도 및 저장 디스크 구성이 이용될 수도 있다.

- [0020] 본 발명의 일 실시예가 도 3 내지 도 5를 참조하여 설명될 것이며, 여기서 도 1의 저장 장치(100)가, 개선된 디지털 입력 검출기를 포함하는 인터페이스 회로를 구현하도록 구성된다.

- [0021] 도 3은 도 1의 저장 장치(100)의 일부를 더 상세하게 도시하고 있다. 이 도면에서, 저장 장치(100)는 프로세서(300), 메모리(302) 및 SOC(304)를 포함하고 있으며, 이들은 베스(306)로 통신하고 있다. 저장 장치는 SOC(304)와 판독/기록 헤드(130) 사이에 인터페이스를 제공하는 프리앰프(308)를 더 포함한다. 메모리(302)는 저장 장치(100)의 SOC(304) 및 다른 구성 요소에 대한 외부 메모리이지만, 이 저장 장치의 내부에 있을 수도 있다. 본 실시예에서 SOC(304)는 판독 채널 회로(310) 및 디스크 컨트롤러(312)를 포함하고 있으며, 저장 디스크(110)로부터 데이터를 판독하고 저장 디스크(110)에 데이터를 기록할 때의 판독/기록 헤드(130)의 동작을 지시한다.

- [0022] 프로세서(300), 메모리(302), SOC(304) 및 프리앰프(308)가 전체적으로, 여기서 사용되는 용어 "제어 회로"에 가장 가능한 예를 포함하는 것으로 간주될 수 있다. 다른 실시예에서는 제어 회로의 여러가지 배치예가 이용될 수 있고, 이러한 배치에서는 구성 요소(300, 302, 304, 308)의 서브세트만을 포함할 수도 있고, 혹은 이들 구성 요소 중 하나 이상의 일부를 포함할 수도 있다. 예컨대, SOC(304) 자체가 "제어 회로"의 일례로 간주될 수 있다.

- [0023] 따라서, 도 3에 도시된 저장 장치(100)의 제어 회로는, 일반적으로 판독/기록 헤드(130)로부터 수신된 데이터 및 판독/기록 헤드(130)로 공급될 데이터를 처리하고, 판독/기록 헤드(130)의 저장 디스크(110)에 대한 위치를

제어하도록 구성되어 있다.

- [0024] 본 실시예에서, SOC(304)의 특정 동작은, 외부 메모리(302)에 저장된 코드를 실행하는 프로세서(300)에 의해 지원될 수 있다. 예컨대, 프로세서(300)는 저장 장치(100)에서의 판독 및 기록 동작을 수행하기 위해서, 메모리(302)에 저장된 코드를 실행하도록 구성될 수 있다. 따라서, 저장 장치(100)의 제어 기능 중 적어도 일부는 소프트웨어 코드의 형태로 적어도 부분적으로 구현될 수 있다.

- [0025] 외부 메모리(302)는 RAM(random access memory) 또는 ROM(read-only memory)과 같은 전자 메모리를, 임의의 조합으로 포함할 수 있다. 예컨대, 외부 메모리(302)는 적어도 부분적으로는 DDR(double data rate) SDRAM(synchronous dynamic RAM)으로서 구현될 수 있다. 메모리(302)는, 본 명세서에서 전반적으로 '컴퓨터 판독 가능 저장 매체'라고 간주되는 것의 예이다. 이러한 매체는 기록가능한 것이 될 수도 있다.

- [0026] 본 실시예에서 SOC(304)가 하나의 집적 회로에 구현된 것으로 가정되었지만, 이 집적 회로는 프로세서(300), 메모리(302), 버스(306) 및 프리앰프(308)의 일부를 더 포함할 수 있다. 다른 방안으로, 프로세서(300), 메모리(302), 버스(306) 및 프리앰프(308)의 일부는 적어도 부분적으로, 하나 이상의 추가적인 집적 회로의 형태로 구현될 수도 있고, 예컨대 HDD에서 사용되도록 설계된 종래의 집적 회로를 본 명세서 개시된 인터페이스 회로를 구현하도록 적절하게 변경할 수 있다. 본 발명의 실시예에서 사용하도록 변경될 수 있는 SOC 집적 회로의 예가, 미국 특허 제 7,872,825호 "Data Storage Drive with Reduced Power Consumption"에 개시되어 있으며, 이는 함께 양도된 것으로 여기에 참조로서 포함된다.

- [0027] 주어진 실시예의 프로세서, 메모리 혹은 다른 저장 장치 구성 요소를 구현하는데 이용될 수 있는 다른 타입의 집적 회로로는, 예컨대 마이크로프로세서, DSP(digital signal processor), ASIC(application-specific integrated circuit), FPGA(field-programmable gate array) 혹은 다른 집적 회로 장치를 들 수 있다.

- [0028] 본 발명의 실시예의 집적 회로의 구현예에서, 다수의 집적 회로 다이가 웨이퍼 표면 상의 반복 패턴의 형태로 형성될 수 있다. 각각의 다이는 여기서 설명하는 장치를 포함할 수 있고, 다른 구조 혹은 회로를 포함할 수 있다. 다이는 웨이퍼로부터 절단되거나 다이싱되어서, 집적 회로로서 패키징된다. 당업자라면 웨이퍼를 다이싱하고 다이를 패키징해서 패키징된 집적 회로를 생산하는 방법을 알고 있을 것이다. 이렇게 제조된 집적 회로는 본 발명의 실시예로 간주된다.

- [0029] 프로세서(300) 및 메모리(302)가 본 실시예의 저장 장치(100)의 일부로 도시되어 있지만, 적어도 부분적으로, 저장 장치가 장착되어 있는 호스트 컴퓨터 혹은 서버와 같은 관련 처리 장치 내에 구현될 수도 있다. 따라서, 도 3의 실시예의 구성 요소(300, 302)는 저장 장치(100)로부터는 분리된 것으로 간주될 수도 있고, 혹은 저장 장치 및 관련 처리 장치 모두로부터 분리된 처리 혹은 메모리 회로 구성 요소를 각각 포함하고 있는 복합 소자를 나타내는 것으로 간주될 수도 있다. 상술한 바와 같이, 프로세서(300) 및 메모리(302)의 적어도 일부는 본 명세서에서 널리 사용되는 용어 "제어 회로"를 포함하는 것으로 간주될 수 있다.

- [0030] 본 실시예의 SOC(304)는 프리앰프(308) 내의 인터페이스(320)와 통신하는 인터페이스(314)를 포함한다. 인터페이스(314, 320)는 여기서 넓게 "인터페이스 회로"라고도 불리는 것의 예로서 볼 수 있다. 이를 인터페이스는 예컨대, SOC가 신호 이득 및 대역폭과 같은 프리앰프의 파라미터를 프로그래밍할 수 있고, 프리앰프에 의해 검출된 시스템 오류와 같은 정보를 수신받을 수도 있는 인터페이스를 포함할 수 있다. 그러나, 개시된 기법이 다른 다양한 타입의 인터페이스에서도 사용될 수 있다는 것을 이해할 것이다.

- [0031] 상술한 바와 같이, SOC는 전형적으로, 관련 프리앰프가 사용하는 것과는 다른 전원 전압을 하나 이상 이용하고 있다. 예컨대, 인터페이스(314) 중 하나는 3.3V, 2.5V 혹은 1.8V의 SOC 전원 전압에 기초한 디지털 입력 신호를 프리앰프에 제공할 수 있다. 따라서, SOC(304)로부터 프리앰프(308)에 인가되는 디지털 입력 신호는, 이를 신호를 생성한 SOC 인터페이스에서 이용되는 전원 전압에 따라서, 서로 다른 논리 하이 신호 레벨을 나타낼 수 있다. 이러한 서로 다른 논리 하이 신호 레벨을 취급하는 것에 대해서, 저장 디스크(110) 상의 서보 마크를 포맷하는데 이용되는 공장의 서보 라이터와의 인터페이스에서도 대응 프리앰프 인터페이스가 필요할 수 있으며, 이러한 서보 라이터는 5V 전원 전압에 기초한 논리 하이 신호 레벨을 가진 디지털 입력 신호를 프리앰프에 제공할 수 있다.

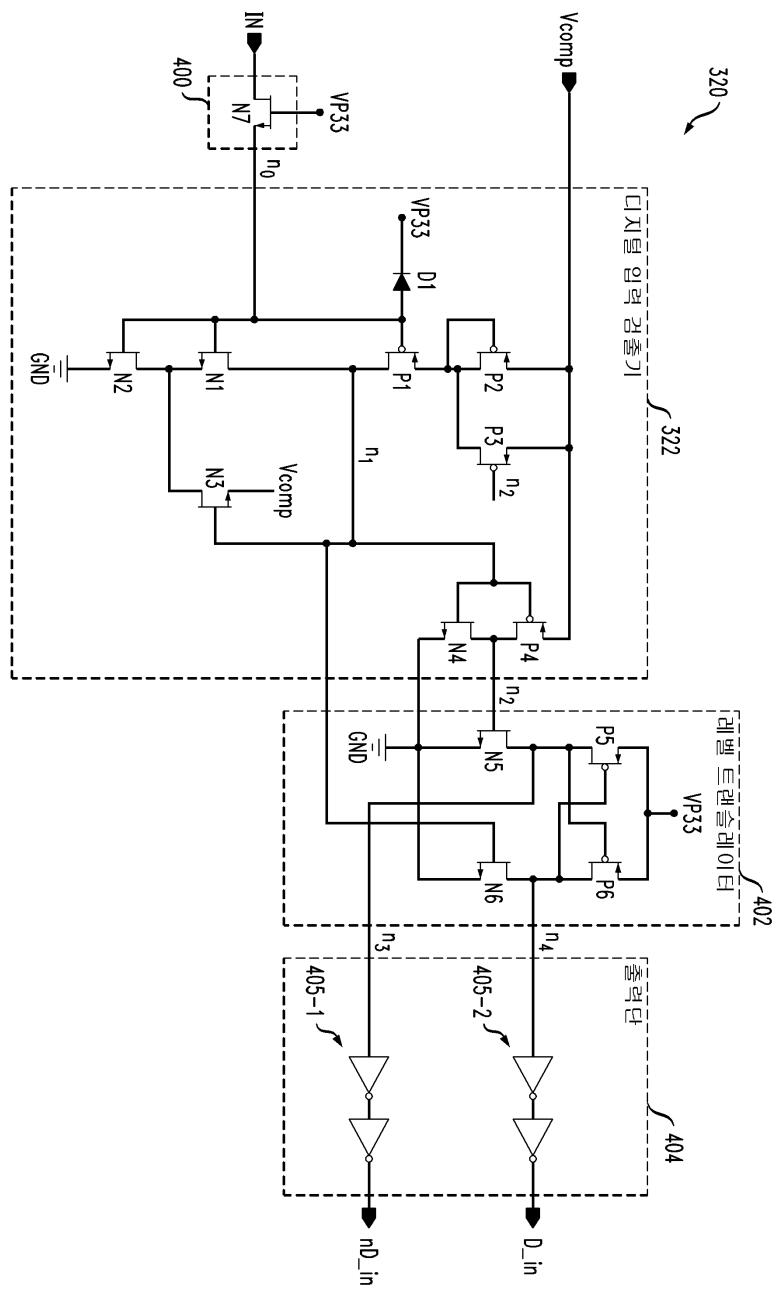

- [0032] 본 실시예의 프리앰프(308)의 인터페이스(320)는, 관련 적응형 전원(324)을 가진 디지털 입력 검출기(322)를 적어도 하나 포함하고 있다. 프리앰프 인터페이스(320) 중 주어진 하나의 적어도 일부에 대한 개략도가 도 4에 도시되어 있다. 디지털 입력 검출기(322)는 입력 트랜지스터를 포함하며, 도 4에서는 예시적으로 P형 MOS(PMOS) 트랜지스터(P1)로서 도시되어 있다. 적응형 전원(324)은 가변 공급 전압 Vcomp을 디지털 입력 검출기(322)에 제공할 수 있다.

공한다. 본 실시예의 디지털 입력 검출기(322)는 1.8V, 2.5V, 3.3V 및 5V 입력 논리 레벨 중 하나 이상을 프리앰프(308) 내에서 사용되는 3.3V 논리 레벨로 변환한다.

[0033] 본 실시예의 적응형 전원(324)이 디지털 입력 검출기(322)에 제공하는 가변 공급 전압 Vcomp은, 프리앰프(308)에서 수신되는 SOC(304)로부터의 예상 논리 하이 입력 신호 레벨의 함수로서 결정되는 설정 포인트 값에 관한, 입력 트랜지스터(P1)의 임계 전압에 따라서 달라진다. 예컨대, 이 설정 포인트 값은 SOC(304)로부터의 최소 예상 논리 하이 입력 신호 레벨과 입력 트랜지스터(P1)의 임계 전압의 함수로서 결정될 수 있다. 더 상세한 예로서, 이 설정 포인트 값은 최소 예상 논리 하이 입력 신호 레벨과 입력 트랜지스터(P1)의 임계 전압의 합으로서 결정될 수 있다. 이하, 적응형 전원(324)의 예시적인 실시예가 도 5를 참조로 설명된다.

[0034] 다른 실시예에서, 적응형 전원이 사용하는 설정 포인트 값을 예상 논리 하이 입력 신호 레벨의 함수로서 결정하는데 다른 기법이 이용될 수 있다. 예컨대, 다른 기법을 이용해서, 입력 트랜지스터(P1)가 최소 예상 논리 하이 입력 신호 레벨을 가진 입력 신호에 대한 임계 전압으로, 혹은 이에 가깝게 바이어스되도록, 설정 포인트 값을 선택할 수 있다. 또한, 다른 실시예의 설정 포인트 값은, 예컨대 도 4의 실시예에서 이용되는 최소 예상 논리 하이 입력 신호 레벨이 아닌, 최소 예상 논리 로우 입력 신호 레벨과 같이, 또 다른 입력 신호의 예상 논리 레벨의 함수로서 결정될 수 있다.

[0035] 도 4를 계속 참조하면, 프리앰프(308)의 인터페이스 회로(320)는 디지털 입력 검출기(322)에 대해서, 디지털 입력 검출기의 입력 노드( $n_0$ )에 연결된 입력 과부하 보호 회로(400), 디지털 입력 검출기(322)의 제 1 및 제 2 출력 노드( $n_1, n_2$ ) 각각에 연결된 제 1 및 제 2 입력을 가진 레벨 트랜슬레이터 회로(402), 및 레벨 트랜슬레이터 회로(402)의 제 1 출력( $n_3$ )에 연결된 제 1 직렬-접속된 인버터의 쌍(405-1) 및 레벨 트랜슬레이터 회로(402)의 제 2 출력( $n_4$ )에 연결된 제 2 직렬-접속된 인버터의 쌍(405-2)을 구비한 출력단(404)을 더 포함하고 있다.

[0036] 입력 트랜지스터(P1)의 소스는 다른 PMOS 트랜지스터(P2)를 통해서 적응형 전원의 Vcomp 출력에 연결되어 있고, 드레인은 낮은 공급 전위에, 예시적으로 N형 MOS(NMOS) 트랜지스터(N1, N2)를 통해서 접지 전위에 연결되어 있다. 입력 트랜지스터(P1)의 게이트는 디지털 입력 검출기(322)의 입력 노드( $n_0$ )에 연결되어 있다. 입력 트랜지스터(P1)의 드레인은 디지털 입력 검출기(322)의 제 1 출력 노드( $n_1$ )에도 연결되어 있다. 다른 실시예에서 낮은 공급 전위는 음의 공급 전압 혹은 다른 타입의 VSS 공급 전압으로 구현될 수 있다.

[0037] P1의 게이트는 D1을 통해서 높은 공급 전위에도 연결되어 있으며, 이는 본 실시예에서는 예시적으로 3.3V 공급 전압이고, 도면에서는 VP33으로 표시되어 있다. 다이오드(D1)의 애노드는 P1의 게이트에 연결되어 있고, 캐소드는 높은 공급 전위 VP33에 접속되어 있다. 다른 실시예에서, 높은 공급 전위로서 다른 공급 전압이 이용될 수 있다. 따라서, 도 4에 도시된 인터페이스 회로(320)는 2개의 다른 전원, 즉 적응형 전원 Vcomp 및 3.3V 전원(VP33)을 이용하고 있다.

[0038] NMOS 트랜지스터(N1, N2)의 각각의 게이트는 PMOS 트랜지스터(P1)의 게이트에 연결되어 있고, 따라서, 디지털 입력 검출기(322)의 입력 노드( $n_0$ )에 연결되어 있다. 또한, N1의 드레인은 P1의 드레인에 연결되어 있고, N2의 드레인은 N1의 소스에 연결되어 있으며, N2의 소스는 낮은 공급 전위에 연결되어 있다.

[0039] 디지털 입력 검출기(322)는 입력 레벨 히스테리시스 회로를 더 포함하고 있으며, 이는 본 실시예에서, 각각의 드레인이 P1의 소스에 연결되어 있고, 각각의 소스가 적응형 전원의 Vcomp 출력에 연결되어 있는 PMOS 트랜지스터(P2, P3)를 적어도 포함한다. P2의 게이트는 자신의 드레인 및 P1의 소스에도 연결되어 있고, P3의 게이트는 디지털 입력 검출기(322)의 제 2 출력 노드( $n_2$ )에 연결되어 있다. 본 실시예에서의 입력 레벨 히스테리시스 회로는 NMOS 트랜지스터(N3)를 더 포함하고, 이 NMOS 트랜지스터(N3)의 게이트는 출력 노드( $n_1$ ) 및 P1의 드레인에 연결되어 있다. N3의 드레인은 N2의 드레인에 연결되어 있고, N3의 소스는 적응형 전원(324)의 Vcomp 출력에 연결되어 있다.

[0040] 본 실시예의 트랜지스터(P2, P3, N3)를 포함하는 입력 레벨 히스테리시스 회로는 신호 전파 시간에 관계없이 비교적 큰 입력 히스테리시스 레벨이 가능하도록 구성되어 있다. 본 실시예의 히스테리시스는 다음과 같이 동작한다. 노드( $n_0$ )의 입력 신호가 논리 0 레벨에 있다면, P3는 온 상태로 P1의 소스를 Vcomp에 접속시킨다. 입력 전압은, 노드( $n_1$ )가 논리 1에서 논리 0로 전환하는 것이 가능해지기 전에, Vcomp에 P1의 임계 전압 Vt를 합한 전압에 가깝게 상승할 것이다. 입력이, 노드( $n_1$ )이 논리 1에서 논리 0으로 상태를 전환할 수 있을 정도로 양의 값

으로 된 이후에, P3는 턴오프되고, 노드( $n_1$ )의 상태가 0에서 1로의 변경을 개시할 수 있기 전에, 입력 전압은 Vcomp와 P1 및 P2의 임계 전압의 합 이하까지 감소되어야 한다. 따라서, P2의 임계 전압을 증가시킴으로써, 제공되는 히스테리시스의 양이 증가될 수 있다.

[0041] 디지털 입력 검출기(322)는 출력 인버터도 포함하고 있으며, 이 인버터의 입력은 P1의 드레인 및 제 1 출력 노드( $n_1$ )에 연결되어 있고, 출력은 제 2 출력 노드( $n_2$ )에 연결되어 있다. 인버터는 PMOS 트랜지스터(P4) 및 NMOS 트랜지스터(N4)를 포함한다. P4 및 N4의 게이트는 모두 제 1 출력 노드( $n_1$ )에 연결되어 있으며, 따라서 입력 트랜지스터(P1)의 드레인에 연결되어 있다. P4의 소스는 적응형 전원(324)의 Vcomp 출력에 연결되어 있다. P4의 드레인과 N4의 드레인은 모두 제 2 출력 노드( $n_2$ )에 연결되어 있다. N4의 소스는 낮은 공급 전위에, 예시적으로 접지 전위에 연결되어 있다. 트랜지스터(P4, N4)를 포함하는 인버터는 소망의 히스테리시스를 구현하도록 P3를 구동하는데 이용되는 논리 반전을 제공한다. 인버터는 레벨 트랜슬레이터 회로(402)의 하나의 입력도 구동한다.

[0042] 레벨 트랜슬레이터 회로(402)는 PMOS 트랜지스터(P5, P6) 및 NMOS 트랜지스터(N5, N6)를 포함한다. 상술한 바와 같이, 레벨 트랜슬레이터 회로의 제 1 및 제 2 입력은 디지털 입력 검출기(322)의 출력 노드( $n_1, n_2$ ) 각각에 연결되어 있다. 더 상세하게, 노드( $n_1$ )는 N6의 게이트에 연결되어 있고, 노드( $n_2$ )는 N5의 게이트에 연결되어 있다. P5 및 P6의 게이트는 P6 및 P5의 드레인에 각각 교차 연결되어 있고, N6 및 N5의 드레인에도 각각 연결되어 있다. P5 및 P6의 소스는 모두 높은 공급 전위에, 예시적으로 3.3V 전원에 연결되어 있고, N5 및 N6의 소스는 모두 접지 전위에 연결되어 있다. 레벨 트랜슬레이터 회로(402)의 출력은 노드( $n_3, n_4$ )에서 제공된다. 트랜지스터(P5, P6, N5, N6)를 포함하는 레벨 트랜슬레이터 회로는, 출력단(404)의 직렬-접속된 인버터의 쌍(405) 및 프리앰프(308)의 다른 내부 로직에 의해 사용하도록, 노드( $n_1, n_2$ ) 상의 Vcomp-접지 신호 스윙을 노드( $n_3, n_4$ )의 VP33-접지 신호 스윙으로 트랜슬레이트하도록 구성된다.

[0043] 출력단(404)의 인버터(405)는, 프리앰프(308)의 내부 신호 라인을 구동시키도록 인터페이스 회로(320)의 출력 드라이브를 만드는데 이용된다. 출력단(404)은, 각각 D\_in 및 nD\_in으로 표시된, 비상보형(uncomplemented) 출력 및 상보형 출력을 제공하며, 이들은 인터페이스 회로(320)의 입력(IN)에 인가되는 입력 신호를 검출함으로써 생성된다.

[0044] 인터페이스 회로 입력(IN)과 디지털 입력 검출기(322)의 입력 노드( $n_0$ ) 사이에 연결된 입력 과부하 보호 회로(400)는, 하나의 NMOS 트랜지스터(N7)를 포함한다. 입력 과부하 보호 트랜지스터(N7)는 다이오드(D1)과 함께 작용하여, 입력 노드( $n_0$ )의 최대 양의 전압을 트랜지스터(P1, N1, N2)의 안전 게이트-소스 전압 Vgs까지 클램프시켜서, 서로 라이터가 공급하는 것과 같은 5V 논리 레벨에 의해 인터페이스 회로가 구동될 때의 과부하를 방지한다. 입력 레벨이 0 내지 3.3V 레벨로 제한된 경우에는, 본 실시예에서의 입력 과부하 보호 트랜지스터(N7)는 생략될 수 있다.

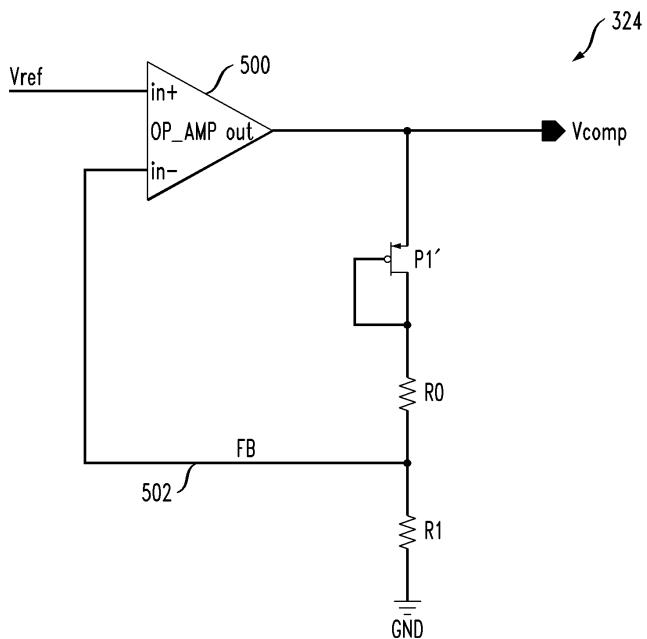

[0045] 도 5를 참조하면, 적응형 전원(324)의 일 실시예는, 비반전 입력(+), 반전 입력(-), 및 Vcomp 공급 전압을 디지털 입력 검출기(322)에 제공하는 출력을 가진 연산 증폭기(500)를 포함한다. 비반전 입력은 기준 전압 Vref에 연결되어 있으며, 반전 입력은 피드백(FB) 경로(502)에 연결된다. 적응형 전원(324)은, 프로세스 및 온도와 같은 하나 이상의 환경 요인에 대한 하나 이상의 파라미터 변경 특성을 갖고 있는 적응형 전원 트랜지스터(P1')를 더 포함하고, 이 파라미터 변경 특성은 디지털 입력 검출기(322)의 입력 트랜지스터(P1)의 파라미터 변경 특성에 실질적으로 매칭된다. 트랜지스터(P1')의 소스는 연산 증폭기(500)의 출력에 연결되어 있고, 그 게이트와 드레인은 서로 연결되어 있다. 일 실시예에서, 프로세스 또는 온도의 변화에 의한 P1의 임계 전압의 변화를 대응하는 P1'의 임계 전압의 변화가 추종하고, 따라서 적응형 공급 전압 Vcomp에서 반영된다.

[0046] 적응형 전원(324)는, 직렬로 연결되어서 P1'의 드레인과 낮은 공급 전위 사이에 전압 분할기 회로를 형성하는 저항의 쌍(R0, R1)을 더 포함하며, 상술한 바와 같이 본 실시예에서 낮은 공급 전위는 접지 전위이다. 본 실시예에서의 R0 및 R1의 예시적인 값은 각각 48k $\Omega$  및 192k $\Omega$ 이지만, 이 값은 물론 적응형 전원(324)에 대한 소망의 설정 포인트 값에 따라 달라질 것이며, 이 설정 포인트 값은 상술한 바와 같이 SOC(304)로부터 수신될 예상 논리 하이 입력 신호 레벨의 함수로서 결정될 수 있다. 연산 증폭기(500)의 반전 입력으로 돌아오는 피드백 경로(502)는 제 1 및 제 2 저항(R0, R1) 사이의 전압 분할기 회로의 텁에 연결되어 있다.

[0047] 본 실시예에서, 적응형 전원(324)에 의해 제공되는 적응형 공급 전압 Vcomp은, 입력 트랜지스터(P1)가 최소 예상 논리 하이 입력 신호 레벨에 의해 구동될 때, 임계 전압 부근에서 바이어스되도록 설정된다. 이는, Vcomp에

대한 설정 포인트 값이, 최소 예상 논리 하이 입력 신호 레벨과 P1의 임계 전압의 합에 의해 주어지게 함으로써, 구현될 수 있다. 이러한 실시예에서, 다른 방안으로 설정 포인트 값은 최소 예상 논리 하이 입력 신호 레벨과, P1의 게이트-소스 전압 강하 Vgs의 함수로 표현될 수도 있다.

[0048] 따라서, 공급 전압 Vcomp가 프로세스 및 온도에 따른 PMOS 임계 전압의 대응하는 변화를 보상하도록 변경되어서, 디지털 입력 검출기(322)의 입력 트랜지스터(P1)는, 입력 신호 레벨이 최소 예상 논리 하이 값에 있을 때 자신의 임계 전압에 가깝게 바이어스되어 유지되게 된다. 예컨대, 접합 온도가 약  $2\text{mV}/^\circ\text{C}$ 의 속도로 증가하면, PMOS 임계 전압은 그만큼 감소될 수 있다. 이렇게 변화가 공급 전압 Vcomp에 의해 보상되지 않으면, 입력이 SOC로부터의 최소 예상 논리 하이 레벨에 의해 구동될 때, PMOS 소자(P1)를 흐르는 전류가 온도에 따라 증가할 것이며, 이는 디지털 입력 검출기(322)에 흐르는 공급 전류를 수용할 수 없을 정도로 크게 할 수 있다. 프로세스 및 온도에 있어서의 총 변화는 본 실시예에서는 0.2 내지 0.5V 정도로 커질 수 있다.

[0049] 예컨대, 일 실시예에서, 1.8V의 기지의 SOC 공급 전압과, SOC와 프리앰프 사이의 예상 접지 전위차에 기초해서, 최소 예상 논리 하이 입력 신호 레벨은 1.52V라고 가정한다. 논리 하이 입력 신호 레벨이 1.52V 이상이면, P1은 오프 영역으로 더 푸시되고, 이에 따라 P1을 흐르는 공급 전류는 감소된다. 본 실시예에서의 전압 분할기의 저항(R0, R1)의 비율은, 밴드캡 기준 소스로부터의 1.2V의 Vref 값을 이용해서, Vcomp가 SOC로부터의 1.52V의 최소 예상 논리 하이 레벨에 하나의 PMOS Vgs를 더한 값에 의해 주어지도록, 설정된다.

[0050] 이 특정 실시예에서, 논리 하이 입력 신호 레벨이 1.52V의 예상 최소값에 있을 때, 디지털 입력 검출기(322)에 의해 Vcomp 공급 전압으로부터 유도된 최대 전류는 단지 약 6마이크로앰프이다.

[0051] 이렇게 낮은 최대 유도 전류가 달성되면, 종래의 인터페이스 회로 배치에 비해서, 다이 면역도 감소시키고, 입력 검출기 및 관련 전원의 총 소비 전력도 감소시킨다.

[0052] 도 4 및 도 5의 인터페이스 회로(320)의 MOS 트랜지스터 소자(P1-P6, P1', N1-N7)의 예시적인 소자 크기가 다음 표에 개시되어 있지만, 다른 실시예에서는 다른 소자 크기가 이용될 수도 있다. 소자 크기는 폭과 길이를 마이크로미터( $\mu\text{m}$ ) 단위로 표시한다.

| 인터페이스 회로 소자 크기 |                     |                     |

|----------------|---------------------|---------------------|

| 소자             | W ( $\mu\text{m}$ ) | L ( $\mu\text{m}$ ) |

| P1             | 20.00               | 0.30                |

| P2             | 10.00               | 0.13                |

| P3             | 15.45               | 0.30                |

| P4             | 8.00                | 0.30                |

| P5             | 6.00                | 0.30                |

| P6             | 6.00                | 0.30                |

| P1'            | 7.5                 | 0.30                |

| N1             | 30.00               | 0.35                |

| N2             | 30.00               | 0.35                |

| N3             | 5.00                | 0.35                |

| N4             | 4.00                | 0.35                |

| N5             | 15.00               | 0.35                |

| N6             | 15.00               | 0.35                |

| N7             | 9.28                | 0.48                |

[0053] [0054] 도 4 및 도 5에 도시된 특정 인터페이스 회로 배치는 단지 예로서 제공된 것으로, 본 발명의 다른 실시예에서는 하나 이상의 디지털 입력 검출기 및 관련 적응형 전원을 구현하는데 다른 타입의 회로를 이용할 수 있다는 것을 이해할 것이다. 복수의 디지털 입력 검출기가 동일한 적응형 전원에 의해서 전력을 공급받을 수도 있다는 점에 주의한다.

[0055] 예컨대, 본 발명의 다른 실시예에서, 도 4 및 도 5의 모든 PMOS 소자는 NMOS 소자로 변경될 수 있고, 그 반대로 변경될 수도 있다. 이러한 실시예에서는, 도 4 및 도 5에 도시된 바와 같은 접지 전위와 양의 공급 전위 사이에서 변하는 논리 상태가 아닌, 음의 공급 전위와 접지 전위 사이에서 변하는 논리 상태를 갖는다. 트랜지스터를 P형에서 N형으로 변경하거나, 그 반대로 변경하는 것에 더해서, 양의 전원 VP33을 음의 전원 VN33으로 변경함으로써, 접지 전원 이하의 공급 전압 3.3V를 제공하고, 다이오드(D1)의 양극과 음극 접속을 반전시키고, Vref를 양에서 음으로 변경하는 것도 가능하다. 이러한 배치예에서, 적응형 공급 전압 Vcomp의 설정 포인트 값은 최소 예상 논리 로우 입력 신호 레벨과 입력 트랜지스터의 임계 전압의 합수로서 정의될 수 있으며, 이 경우 최소 예상 논리 로우란, 최소의 음의 논리 로우를 나타낸다. 다른 실시예에서는 디지털 입력 검출기 및 관련 적응형 전원을 구현하는데 다양한 다른 회로의 구성이 이용될 수 있다.

- [0056] 상술한 바와 같이, 다른 실시예에서는 저장 장치 구성이 달라질 수 있다. 예컨대, 저장 장치는 하나 이상의 저장 디스크에 더해서 플래시 메모리를 구비한 하이브리드형 HDD를 포함할 수 있다. 또한, 상술한 인터페이스 회로는 저장 장치에 사용되는 것으로 한정되는 것은 아니며, 다른 타입의 처리 장치에서도 널리 구현될 수 있다.

- [0057] 특정 저장 디스크 구성 및 기록 메커니즘이 본 발명의 다른 실시예에서는 달라질 수 있다는 것도 이해할 것이다. 예컨대, 본 발명의 하나 이상의 실시예에서는, SMR(shingled magnetic recording) 및 BPM(bit-patterned media)와 같은 기록 기술이 이용될 수 있다.

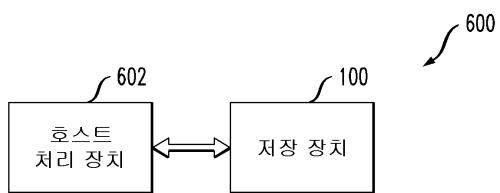

- [0058] 도 6은 호스트 처리 장치(602)에 연결된 디스크-기반 저장 장치(100)를 포함하는 처리 시스템(600)을 도시하고 있으며, 이는 컴퓨터, 서버, 통신 장치 등이 될 수 있다. 도면에서는 별개의 구성 요소로서 도시되어 있지만, 저장 장치(100)는 호스트 처리 장치에 포함될 수 있다. 저장 장치(100)에 지시되는 판독 커맨드 및 기록 커맨드와 같은 인스트럭션은 처리 장치(602)로부터 생성될 수 있으며, 이는 도 3과 관련하여 상기 설명된 것과 유사한 프로세서 및 메모리 소자를 포함할 수 있다.

- [0059] 도 7에 도시된 바와 같이 다수의 디스크-기반 저장 장치(100)가 가상 저장 시스템(700)에 포함될 수 있다. 저장 가상화 시스템이라고도 불리는 가상 저장 시스템(700)은 예시적으로 RAID 시스템(704)에 연결된 가상 저장 컨트롤러(702)를 포함하고, 여기서 RAID은 복수 배열 독립 디스크(Redundant Array of Independent Disks)이다. 상세하게, RAID 시스템은 N개의 개별적인 저장 장치(100-1, 100-2, …, 100-N)를 포함하고, 그 중 하나 이상이, 상술한 적어도 하나의 디지털 입력 검출기 및 관련 적응형 전원을 구비한 인터페이스 회로를 포함하도록 구성되어 있다고 가정한다.

- [0060] 상술한 타입의 HDD 또는 다른 디스크-기반 저장 장치를 구비한 가상 저장 시스템은 본 발명의 실시예로서 간주된다. 도 6의 호스트 처리 장치는 가상 저장 시스템의 구성 요소가 될 수도 있고, 가상 저장 컨트롤러(702)를 포함할 수도 있다.

- [0061] 또한, 본 발명의 상술한 실시예는 단지 예시라는 점을 강조한다. 예컨대, 다른 실시예에서는 다른 타입 및 배치의 저장 디스크, 판독/기록 헤드, 제어 회로, 인터페이스 회로 및 다른 저장 장치 소자를 이용해서 소망의 기능을 구현할 수 있다. 또한, 상술한 입력 검출기 및 관련 적응형 전원은 다른 다양한 타입의 처리 장치에서 구현될 수 있다. 또한, 설정 포인트 값이 입력 신호의 예상 논리 레벨의 함수로서 결정되는 것과 같은, 디지털 입력 검출기 및 관련 적응형 전원이 구성되는 특정한 방식은, 다른 실시예에서는 달라질 수 있다. 이 대안의 실시예 및 다른 다수의 실시예가 하기 청구의 범위 내에 있다는 것은 당업자에게는 자명할 것이다.

## 도면

### 도면1

## 도면2

## 도면3

도면4

## 도면5

## 도면6

## 도면7