**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) Int. Cl.<sup>6</sup>

G06F 13/38

(45) 공고일자 1999년01월15일

(11) 등록번호 특0167938

(24) 등록일자 1998년09월30일

(21) 출원번호 특1995-026842

(22) 출원일자 1995년08월28일

(65) 공개번호 특1997-012177

(43) 공개일자 1997년03월29일

(73) 특허권자 대우전자주식회사 배순훈

서울특별시 종구 남대문로 5가 541번지

(72) 발명자 김영민

서울특별시 마포구 도화 우성아파트 15동 1203호

(74) 대리인 박상기, 이윤민

**심사관 : 오를수**

**(54) 데이터 전송망의 통신상태 감지회로**

**요약**

본 발명은 컴퓨터와 보조장치간의 데이터의 전송이 가능한 전송망에 관한 것으로서, 특히 전송망의 버스상에서 전송되는 데이터로 부터 버스가 비지(Busy)인지 또는 아이들(Idle) 상태인지를 감지하는 통신상태 감지회로를 연결하여 버스의 정확한 통신상태를 알 수 있어 오동작을 방지할 수 있는 데이터 전송망의 통신상태 감지회로에 관한 것이다.

이와 같은 본 발명은 다수의 버스라인으로 연결되어 있는 데이터 전송망에 있어서, 버스를 통해 전송되는 시리얼 데이터 및 시리얼 클럭으로부터 시작신호를 검출하는 시작신호 검출부와, 버스를 통해 전송되는 시리얼 데이터 및 시리얼 클럭으로부터 종료신호를 검출하는 종료신호 검출부와, 상기 시작신호 검출부와 종료신호 검출부의 출력신호가 검출되는 동안 비지 신호를 출력하는 비지신호 검출부로 구성된 통신상태 감지회로를 버스의 소정위치에 부가하여서 된 것이다.

**대표도**

**명세서**

[발명의 명칭]

데이터 전송망의 통신상태 감지회로

[도면의 간단한 설명]

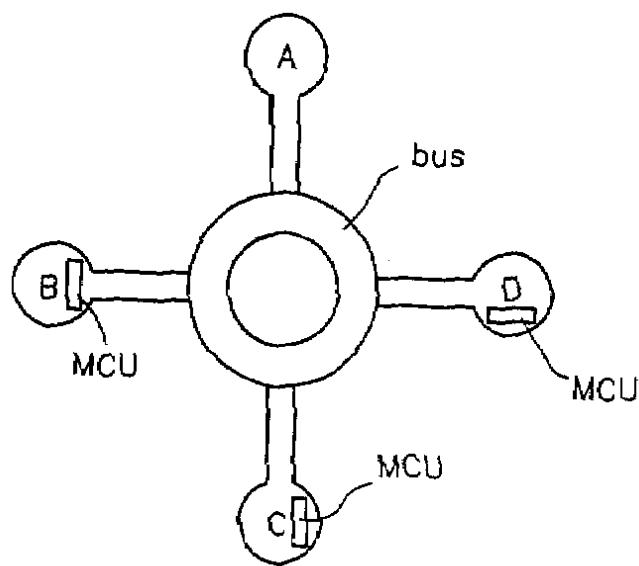

제1도는 일반적인 데이터 전송망의 구조를 보인 도면.

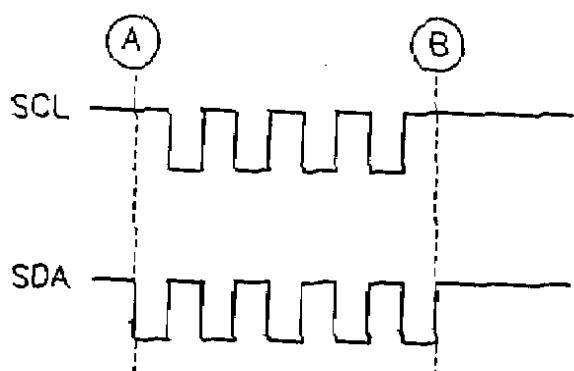

제2도는 일반적인 데이터 전송망의 데이터 구조를 보인 도면.

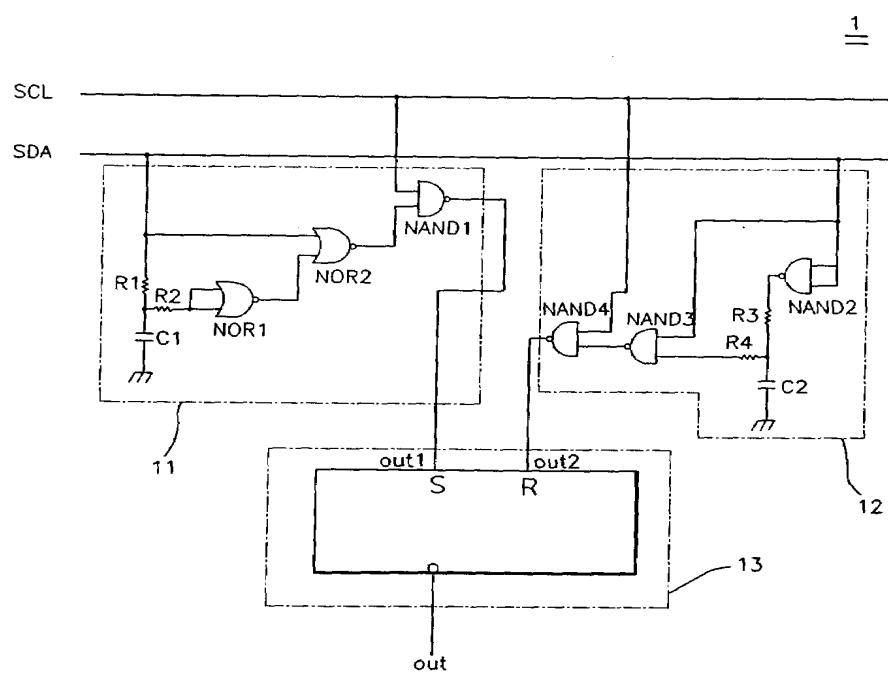

제3도는 본 발명에 따른 데이터 전송망의 통신상태 감지회로의 구성을 보인 도면.

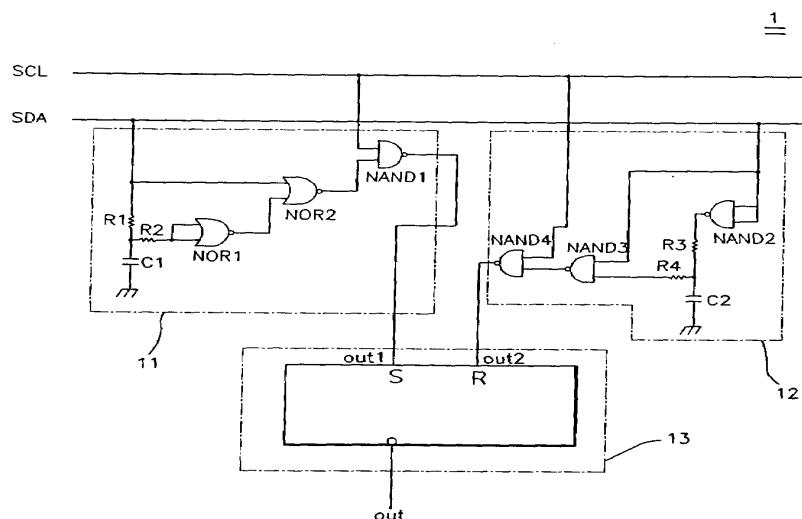

제4도는 제3도의 통신상태 감지회로의 구성을 보인 상세회로도.

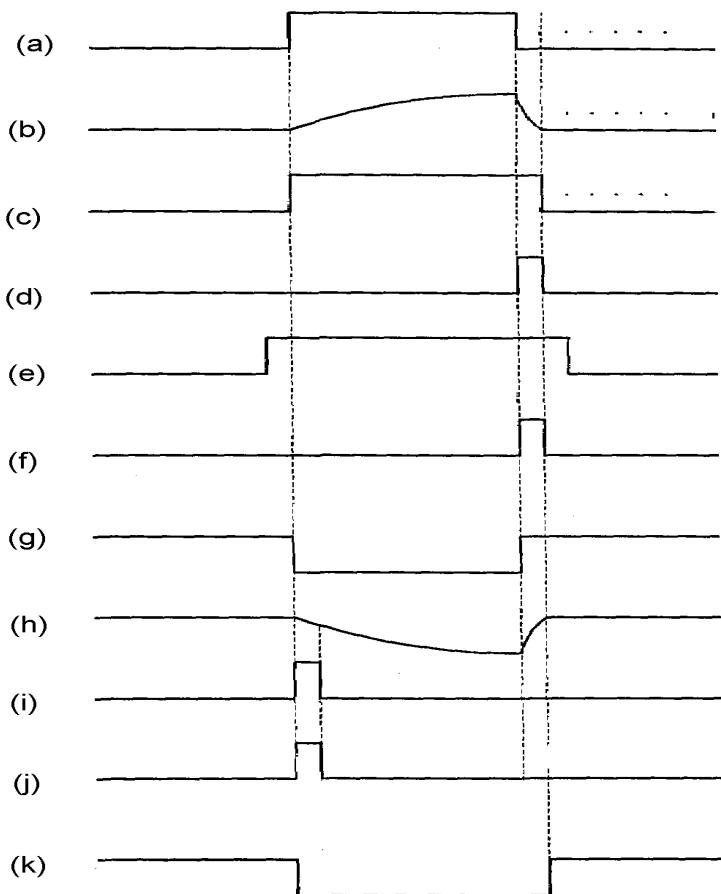

제5도는 제4도의 각부의 출력신호를 보인 파형도.

\* 도면의 주요부분에 대한 부호의 설명

|                   |                     |

|-------------------|---------------------|

| 1 : 통신상태 감지회로     | 11 : 시작신호 검출부       |

| 12 : 종료신호 검출부     | 13 : 비지신호 발생부       |

| R1-R4 : 저항        | C1,C2 : 콘덴서         |

| NOR1,NOR2 : 노아게이트 | NAND1-NAND4 : 낸드게이트 |

[발명의 상세한 설명]

본 발명은 컴퓨터와 보조장치간의 데이터의 전송이 가능한 전송망에 관한 것으로서, 특히 전송망의 버스상에서 전송되는 데이터로 부터 버스가 비지(Busy)인지 또는 아이들(Idle) 상태인지를 감지하는 통신상태감지회로를 연결하여 버스의 정확한 통신상태를 알 수 있어 오동작을 방지할 수 있는 데이터 전송망의 통신상태 감지회로에 관한 것이다.

일반적인 시리얼 전송망은 컴퓨터에 연결되어 있는 마이스 등의 보조장치들을 연결하는 망으로서, 최근에는 많이 사용되고 있다.

상기와 같은 컴퓨터(A)와 보조장치(B)(C)(D)는 제1도에 도시된 바와 같이, 컴퓨터(A) 및 보조장치(B)(C)(D)들 간에 버스(bus)를 통해 상호 데이터가 전송되어, 컴퓨터(A) 및 보조장치(B)(C)(D)의 마이크로프로세서(MCU)에서 상기 데이터가 상호 송수신되도록 한 링의 구조를 이루고 있다.

그때 버스를 통해 전송되는 데이터는 전송되는 필요한 장비를 최소로 줄이기 위하여 직렬(Serial)로 전송되며, 그때 전송되는 데이터의 형태는 제2도에 도시된 바와 같이, 시리얼 클럭(SCL)과 시리얼 데이터(SDA)로 전송된다.

상기 컴퓨터(A)에서 보조장치(B)로 전송될 때 보조장치(B)의 마이크로프로세서(MCU)에 의해 시리얼 클럭(SCL)이 고전위 상태로 수신되고, 동시에 시리얼 데이터(SDA)가 고전위 상태에서 저전위 상태로의 트리거가 수신되면, 마이크로프로세서(MCU)는 시리얼 데이터(SDA)를 수신할 준비단계에 있게 된다.

한편, 시리얼 클럭(SCL) 및 시리얼 데이터(SDA)가 모두 저전위 상태로 상기 마이크로프로세서(MCU)에 수신되면, 마이크로프로세서(MCU)는 현재 버스(bus)가 통신중임을 나타내는 비지(Busy)상태로 인식하게 된다.

그러나, 상기와 같은 일반적인 데이터 전송망의 통신상태 감지회로는 시리얼 데이터(SDA) 및 시리얼 클럭(SCL)이 제2도(a)(b)에 도시된 바와 같이, 마이크로프로세서(MCU)에 수신되어도 현재 통신상태가 비지로 인식하게 되는 경우 데이터 전송망이 오동작하게 되는 문제점이 발생하게 된다.

본 발명은 상기와 같은 문제점을 해소하기 위해, 버스의 소정위치에 병렬접속되어 현재 버스의 통신상태를 감지한 후, 컴퓨터의 마이크로프로세서로 그 감지신호를 인가하는 통신상태 감지회로를 연결함으로써, 현재의 통신상태를 정확하게 감지하여 데이터 전송망의 오동작을 방지하는 데이터 전송망의 통신상태 감지회로를 제공하는데 본 발명의 목적이 있는 것이다.

이와 같은 목적을 달성하기 위한 본 발명은, 다수의 버스라인으로 연결되어 있는 데이터 전송망에 있어서, 버스를 통해 전송되는 시리얼 데이터 및 시리얼 클럭으로부터 시작신호를 검출하는 검출부와, 버스를 통해 전송되는 시리얼 데이터 및 시리얼 클럭으로부터 종료신호를 검출하는 종료신호 검출부와, 상기 시작신호 검출부와 종료신호 검출부의 출력신호가 검출되는 동안 비지신호를 출력하는 비지신호 검출부로 구성된 통신상태 감지회로를 버스의 소정위치에 부가하여서 된 것이다.

이하 본 발명에 따른 데이터 전송망의 통신상태 감지회로를 첨부된 도면에 의거하여 보다 상세하게 설명하면 다음과 같다.

제3도 및 제4도는 본 발명에 따른 데이터 전송망의 통신상태 감지회로의 구성을 보인 도면으로서, 통신상태 감지회로(1)는 버스를 통해 전송되는 시리얼 데이터(SDA) 및 시리얼 클럭(SCL) 신호로부터 시작신호(OUT1)를 출력하는 시작신호 검출부(11)와, 버스를 통해 전송되는 시리얼 데이터(SDA) 및 시리얼 클럭(SCL) 신호로부터 종료신호(OUT2)를 출력하는 종료신호 검출부(12)와, 상기 시작신호 검출부(11)와 종료신호 검출부(12)의 출력신호(OUT1)(OUT2)가 검출되는 동안 비지신호(OUT)를 출력하여 컴퓨터(A)의 마이크로프로세서(MCU)로 전송시키는 비지신호 검출부(13)로 구비된다.

여기서, 상기 시작신호 검출부(11)는 제4도에 도시된 바와 같이, 버스를 통해 수신된 시리얼 데이터(SDA)를 바이어스시키는 저항(R1)과, 저항(R1)의 출력신호를 충방전시키는 콘덴서(C1)와, 콘덴서(C1)의 충방전된 신호를 바이어스시키는 저항(R2)과, 저항(R2)의 출력신호가 저전위 상태인 경우 고전위 상태로 출력하는 노아게이트(NOR1)와, 상기 노아게이트(NOR1)의 출력신호 및 입력되는 시리얼 데이터(SDA)가 모두 저전위 상태인 경우 고전위 상태의 신호를 출력하는 노아게이트(NOR2)로 이루어져 있고, 또한 그 노아게이트(NOR2)의 출력신호와 버스를 통해 수신된 시리얼 클럭(SCL)이 모두 고전위 상태인 경우 시작클럭(OUT)을 고전위 상태로 출력하는 낸드게이트(NAND1)로 구비된다.

그리고, 상기 종료신호 검출부(12)는 버스로 부터 입력되는 시리얼 데이터(SDA)를 반전시키는 낸드게이트(NAND2)와, 낸드게이트(NAND2)의 출력신호를 적분시킨 후 바이어스시키는 저항(R3)(R4) 및 콘덴서(C2)와, 시리얼 데이터(SDA) 및 저항(R4)의 출력신호가 모두 고전위 상태인 경우 고전위 상태의 신호를 출력시키는 낸드게이트(NAND3)와, 낸드게이트(NAND3)의 출력신호와 입력되는 시리얼 클럭(SCL)이 모두 고전위 상태인 경우 고전위 상태로 출력하는 낸드게이트(NAND4)로 구비된다.

한편, 상기 비지신호 검출부(13)는 상기 시작신호 검출부(11)에서 시작신호가 검출될 때부터 종료신호 검출부(12)에서 종료신호가 검출될 때까지 고전위 상태의 비지신호를 출력하는 플립플롭으로 구비된다.

이와 같이 이루어진 본 발명에 따른 데이터 전송망의 통신상태 감지회로를 제5도를 참조하여 설명하면 다음과 같다.

우선, 제5도(a)에 도시된 바와 같은 시리얼 데이터(SDA)가 입력되면, 그 시리얼 데이터(SDA)는 시작신호 검출부(11)의 저항(R1) 및 콘덴서(C1)에 의해 제5도(b)에 도시된 바와 같은 신호로 출력되고, 그 출력된 신호는 저항(R2)을 통해 노아게이트(NOR1)에 인가된다.

상기 노아게이트(NOR1)는 저항(R2)의 출력신호를 받아 제5도(c)에 도시된 바와 같은 신호를 출력하게 되며, 그 노아게이트(NOR1)의 출력신호 및 입력되는 시리얼 데이터(SDA)는 노아게이트(NOR2)에 의해 제5도(d)에 도시된 바와 같은 신호가 출력된다. 그때 상기 버스를 통해 입력되는 시리얼 클럭(SCL)은 제5도(e)에 도시된 바와 같다.

그리고, 상기 시리얼 클럭(SCL) 및 노아게이트(NOR2)의 출력신호는 낸드게이트(NAND1)에 인가되어 제5도(f)에 도시된 바와 같은 신호가 출력된다.

즉, 버스를 통해 시리얼 데이터(SDA)가 고전위 상태에서 저전위 상태로 트리거되고, 시리얼 클럭(SCL)이 제2도에 도시된 바와 같이 고전위 이면, 제5도(f)에 도시된 바와 같은 시작신호(OUT1)가 출력된다.

한편, 상기 제5도(a)에 도시된 바와 같이 입력되는 시리얼 데이터(SDA)는 종료신호 검출부(12)의 낸드게이트(NAND2)에 인가되어 제5도(g)에 도시된 바와 같은 신호가 출력되고, 그 낸드게이트(NAND2)의 출력신호는 저항(R3) 및 콘덴서(C2)에 의해 적분된 후 저항(R4)을 통해 바이어스되어 제5도(h)에 도시된 바와 같은 신호가 출력된다.

제5도(a)에 도시된 바와 같은 시리얼 데이터(SDA)와 저항(R4)의 출력신호는 낸드게이트(NAND3)에 인가되어 제5도(i)에 도시된 바와 같은 신호가 출력되고, 그 낸드게이트(NAND3)의 출력신호와 제5도(e)에 도시된 바와 같이 입력되는 시리얼 클럭(SCL)은 낸드게이트(NAND4)에 인가되어 제5도(j)에 도시된 바와 같은 신호가 출력된다.

즉, 상기 제2도에 도시된 바와 같이 시리얼 데이터(SDA)가 저전위 상태에서 고전위 상태로 트리거되고 시리얼 클럭(SCL)이 고전위 상태이면, 제5도(j)에 도시된 바와 같은 종료신호(OUT2)가 출력된다.

그리고, 상기 시작신호 검출부(11)의 출력신호(OUT1)가 신호발생부(13)의 셋트단자(S)에 인가되어 제5도(k)에 도시된 바와 같이 비지신호(OUT)가 고전위 상태로 트리거되고, 또한 상기 종료신호 검출부(12)의 출력신호(OUT1)는 신호발생부(13)의 플립플롭의 리셋단자(R)에 인가되어 제5도(k)에 도시된 바와 같이 비지신호(OUT)로 저전위 상태로 트리거된다.

이상에서 설명한 바와 같이, 본 발명에 따른 데이터 전송망의 통신상태 감지회로는 버스의 소정위치에 데이터 전송망의 상태를 감지하는 통신상태 감지회로를 설치하여 마이크로프로세서의 효용을 높일 수 있는 효과가 있다.

### (57) 청구의 범위

#### 청구항 1

컴퓨터(A)의 마이크로프로세서(MCU)와 링 구조의 접속관계를 갖는 다수 보조장치(B,C,D)간의 데이터전송망에 있어서, 버스를 통해 전송되는 시리얼 데이터(SDA) 및 시리얼 클럭(SCL)으로부터 시작신호(OUT1)를 출력하는 시작신호 검출부(11)와, 버스를 통해 전송되는 시리얼 데이터(SDA) 및 시리얼 클럭(SCL)으로부터 종료신호(OUT2)를 검출하는 종료신호 검출부(12)와, 상기 시작신호 검출부(11)와 종료신호 검출부(12)의 출력신호(OUT1)(OUT2)가 검출되는 동안 비지신호(OUT)를 출력하는 비지신호 검출부(13)로 구성되어 상기 마이크로프로세서(MCU)로 데이터의 전송상태를 출력하는 데이터 전송망의 통신상태 감지회로.

#### 청구항 2

제1항에 있어서, 시작신호 검출부(11)는 버스를 통해 수신된 시리얼 데이터(SDA)를 바이어스시키는 저항(R1)과, 상기 저항(R1)의 출력신호를 충방전시키는 콘덴서(C1)와, 상기 콘덴서(C1)의 충방전된 신호를 바이어스시키는 저항(R2)과, 상기 저항(R2)의 출력신호가 저전위 상태인 경우 고전위 상태로 출력하는 노아게이트(NOR1)와, 상기 노아게이트(NOR1)의 출력신호 및 입력되는 시리얼 데이터(SDA)가 모두 저전위 상태인 경우 고전위 상태의 신호를 출력하는 노아게이트(NOR2)와, 상기 노아게이트(NOR2)의 출력신호와 버스를 통해 수신된 시리얼 클럭(SCL)이 모두 고전위 상태인 경우, 시작클럭(OUT)을 고전위 상태로 출력하는 낸드게이트(NAND1)로 구비됨을 특징으로 하는 데이터 전송망의 통신상태 감지회로.

#### 청구항 3

제1항에 있어서, 상기 종료신호 검출부(12)는 버스로 부터 입력되는 시리얼 데이터(SDA)를 반전시키는 낸드게이트(NAND2)와, 상기 낸드게이트(NAND2)의 출력신호를 적분시킨 후 바이어스시키는 저항(R3)(R4) 및 콘덴서(C2)와, 시리얼 데이터(SDA) 및 저항(R4)의 출력신호가 모두 고전위 상태인 경우 고전위 상태의 신호를 출력시키는 낸드게이트(NAND3)와, 상기 낸드게이트(NAND3)의 출력신호와 입력되는 시리얼 클럭(SCL)이 모두 고전위 상태인 경우 고전위 상태로 출력하는 낸드게이트(NAND4)로 구비됨을 특징으로 하는 데이터 전송망의 통신상태 감지회로.

#### 청구항 4

제1항에 있어서, 상기 비지신호 검출부(13)는 상기 시작신호 검출부(11)에서 시작신호가 검출될 때부터 종료신호 검출부(12)에서 종료신호가 검출될 때까지 고전위 상태의 비지신호를 출력하는 플립플롭으로 구비됨을 특징으로 하는 데이터 전송망의 통신상태 감지회로.

도면

도면1

도면2

도면3

도면4

**도면5**