(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7699436号**

**(P7699436)**

(45)発行日 令和7年6月27日(2025.6.27)

(24)登録日 令和7年6月19日(2025.6.19)

(51)国際特許分類

|         |                  |     |         |        |

|---------|------------------|-----|---------|--------|

| H 0 4 N | 25/67 (2023.01)  | F I | H 0 4 N | 25/67  |

| H 0 4 N | 25/704 (2023.01) |     | H 0 4 N | 25/704 |

請求項の数 13 (全22頁)

|          |                             |

|----------|-----------------------------|

| (21)出願番号 | 特願2021-7365(P2021-7365)     |

| (22)出願日  | 令和3年1月20日(2021.1.20)        |

| (65)公開番号 | 特開2022-111738(P2022-111738) |

|          | A)                          |

| (43)公開日  | 令和4年8月1日(2022.8.1)          |

| 審査請求日    | 令和6年1月11日(2024.1.11)        |

|          |                                            |

|----------|--------------------------------------------|

| (73)特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74)代理人  | 110003281<br>弁理士法人大塚国際特許事務所                |

| (72)発明者  | 岩原 知永<br>東京都大田区下丸子3丁目30番2号<br>キヤノン株式会社内    |

| 審査官      | 堀井 康司                                      |

最終頁に続く

(54)【発明の名称】 撮像装置および画像処理方法

**(57)【特許請求の範囲】****【請求項1】**

複数の画素が行列状に配置された画素アレイと、前記画素の列ごとに設けられた複数の列信号線とを有し、前記画素アレイから画像信号および焦点検出用信号を読み出し可能な撮像素子と、

前記撮像素子に設けられ、前記画像信号に対して所定の補正処理を適用する第1の補正回路と、

前記撮像素子の外部に設けられ、複数行分の前記焦点検出用信号を合成し、合成後の前記焦点検出用信号に対して前記所定の補正処理を適用する第2の補正回路と、

を有することを特徴とする、撮像装置。

**【請求項2】**

前記第1の補正回路が前記所定の補正処理に用いる補正值は前記撮像素子が有するメモリに保持され、前記第2の補正回路が前記所定の補正処理に用いる補正值は前記撮像素子の外部に設けられたメモリに保持されることを特徴とする請求項1に記載の撮像装置。

**【請求項3】**

前記撮像素子が有するメモリに保持される補正值は、前記撮像素子の外部に設けられたメモリから取得されることを特徴とする請求項2に記載の撮像装置。

**【請求項4】**

前記所定の補正処理は、前記画素の列ごとの回路特性に起因する信号レベルのばらつきを補正するオフセット補正処理を含むことを特徴とする請求項1から3のいずれか1項に

記載の撮像装置。

**【請求項 5】**

前記第2の補正回路は、前記焦点検出用信号が全ての行の画素から読み出される場合と、前記焦点検出用信号が一部の行の画素から読み出される場合とで、前記焦点検出用信号の合成後の行数が等しくなるように前記複数行分の前記焦点検出用信号を合成することを特徴とする請求項1に記載の撮像装置。

**【請求項 6】**

前記第2の補正回路は、前記焦点検出用信号が全ての行の画素から読み出される場合と、前記焦点検出用信号が一部の行の画素から読み出される場合とで、同じ補正值を用いて前記合成後の焦点検出用信号に前記所定の補正処理を適用することを特徴とする請求項5に記載の撮像装置。 10

**【請求項 7】**

前記焦点検出用信号が全ての行の画素から読み出される場合と、前記焦点検出用信号が一部の行の画素から読み出される場合とが、前記撮像装置の設定に応じて変更されることを特徴とする請求項5または請求項6に記載の撮像装置。

**【請求項 8】**

前記設定が撮影モードであることを特徴とする請求項7に記載の撮像装置。

**【請求項 9】**

前記画像信号と前記焦点検出用信号とが記録される場合には、前記画像信号と前記焦点検出用信号とが全ての行の画素から読み出され、 20

前記画像信号が記録され、前記焦点検出用信号が記録されない場合には、前記画像信号が全ての行の画素から読み出され、前記焦点検出用信号が一部の行の画素から読み出される、

ことを特徴とする請求項1から7のいずれか1項に記載の撮像装置。

**【請求項 10】**

前記複数の列信号線の第1のグループから第1の周期で前記画像信号が読み出され、前記複数の列信号線の第2のグループから前記第1の周期よりも短い第2の周期で前記焦点検出用信号が読み出される場合、

読み出される周期が異なる前記画像信号の一方に前記第1の補正回路が前記所定の補正処理を適用し、他方に前記第2の補正回路が前記所定の補正処理を適用する、 30

ことを特徴とする請求項1から9のいずれか1項に記載の撮像装置。

**【請求項 11】**

さらに、前記焦点検出用信号が前記第1の周期で読み出される場合は前記第1の周期で読み出される前記画像信号に前記所定の補正処理を適用する補正回路で前記焦点検出用信号に前記所定の補正処理を適用し、

前記焦点検出用信号が前記第2の周期で読み出される場合は前記第2の周期で読み出される前記画像信号に前記所定の補正処理を適用する補正回路で前記焦点検出用信号に前記所定の補正処理を適用する、

ことを特徴とする請求項10に記載の撮像装置。

**【請求項 12】**

前記第1のグループに属する列信号線の数が、前記第2のグループに属する列信号線の数より多いことを特徴とする請求項10または11に記載の撮像装置。 40

**【請求項 13】**

前記画素は複数の光電変換部を有し、前記画像信号が前記複数の光電変換部から読み出される画素信号であり、前記焦点検出用信号が前記複数の光電変換部の一部から読み出される画素信号であることを特徴とする請求項1から12のいずれか1項に記載の撮像装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は撮像装置および画像処理方法に関し、特に画像補正技術に関する。

10

20

30

40

50

**【背景技術】****【0002】**

デジタル（ビデオ）カメラなどの撮像装置には撮像素子が用いられている。撮像素子には数百万から数千万の微細な画素が形成されており、各画素における光電変換によって蓄積された電荷量に相当する電圧値を画像信号として取得する。

**【0003】**

各画素が有するフォトダイオードやトランジスタの特性に生じるばらつきに起因した信号値のばらつきは画像信号に含まれるノイズ成分となるため、読み出した画像信号に対してノイズ成分を除去もしくは抑制するための補正を適用する必要がある。

**【0004】**

また、画素から信号を読み出すために画素列ごとに設けられている読み出し回路（垂直信号線および列回路）についても特性にばらつきが存在する。そのため読み出し回路の特性のばらつきが画素信号に与える影響についても補正する必要がある。

**【0005】**

特許文献1には、画素列ごとに複数の読み出し回路が設けられている構成の撮像装置において、読み出し回路ごとの補正值を用いて特性のばらつきを補正することが開示されている。

**【先行技術文献】****【特許文献】****【0006】****【文献】特許第6579782号公報**

20

**【発明の概要】****【発明が解決しようとする課題】****【0007】**

読み出し回路の特性のばらつきを高精度に補正するためには、読み出し回路ごと、かつ読み出す信号の種類ごとに異なる補正值を用いる必要がある。例えば、各画素が2つの副画素A, Bを有し、副画素A, Bの両方からまとめて画素信号を読み出す場合と、副画素AまたはBの一方から画素信号を読み出し可能な場合がある。この場合、それぞれの場合について別個の補正值を用いる必要がある。したがって、各画素から2種類の信号が読み出し可能で、画素列ごとに6本の垂直信号線が設けられている場合、12種類の補正值が必要となる。

30

**【0008】**

記憶すべき補正值が増加すると、必要なメモリ容量ならびに部品コストが増大する。また、撮像装置の起動時にメモリから補正值を読み出すための時間が増大するため、撮像装置の応答性低下の要因となる。

**【0009】**

また、画像信号を補正するための補正回路に対して1フレーム内に通信できるデータ量やデータレートには制限がある。したがって、使用する補正值の増加は、補正回路に送信可能な画像データの量を制限し、撮影フレームレートや1フレーム当たりの画素数の向上を妨げる要因となる。

40

**【0010】**

本発明はその一態様において、補正值の増加を抑制しつつ、適切な補正を実現することが可能な撮像装置およびその制御方法を提供する。

**【課題を解決するための手段】****【0011】**

上述の目的は、複数の画素が行列状に配置された画素アレイと、画素の列ごとに設けられた複数の列信号線とを有し、画素アレイから画像信号および焦点検出用信号を読み出し可能な撮像素子と、撮像素子に設けられ、画像信号に対して所定の補正処理を適用する第1の補正回路と、撮像素子の外部に設けられ、複数行分の焦点検出用信号を合成し、合成後の焦点検出用信号に対して所定の補正処理を適用する第2の補正回路と、を有すること

50

を特徴とする、撮像装置によって達成される。

【発明の効果】

【0012】

本発明の一態様によれば、補正值の増加を抑制しつつ、適切な補正を実現することができる撮像装置およびその制御方法を提供することができる。

【図面の簡単な説明】

【0013】

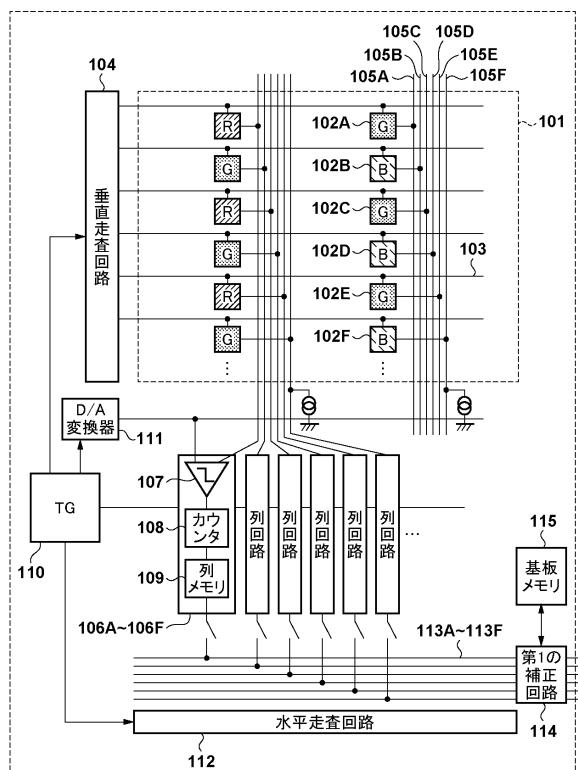

【図1】実施形態に係る撮像素子の画素と周辺回路の構成例を示す図

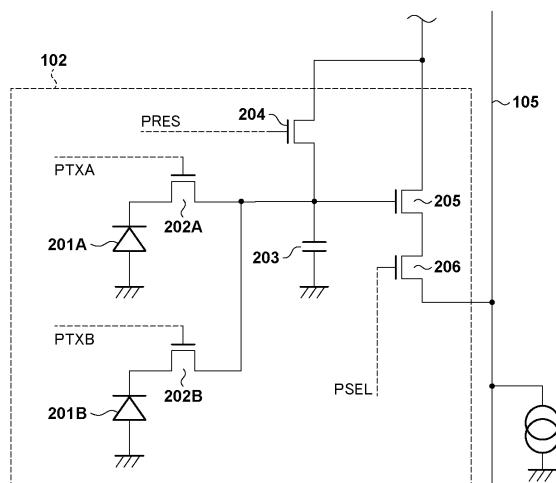

【図2】実施形態に係る撮像素子における単位画素の構成例を示す図

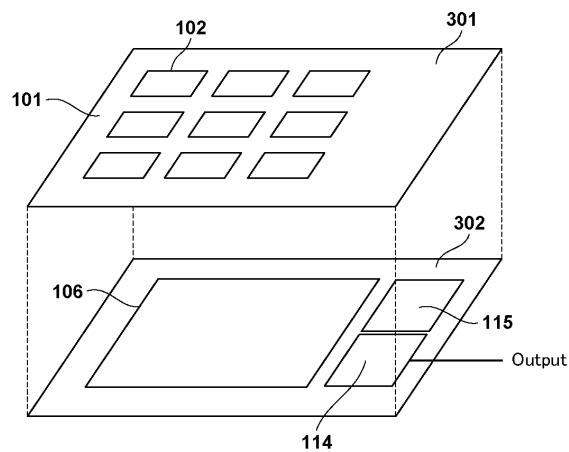

【図3】実施形態に係る撮像素子の積層構造を示す模式図

10

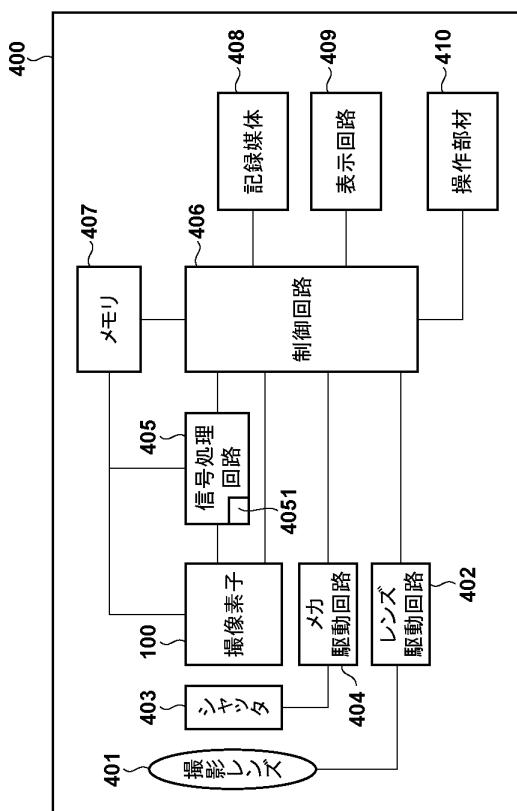

【図4】実施形態に係る撮像装置の構成例を示すブロック図

【図5】実施形態に係る第1の読み出し動作を示すタイミングチャート

【図6】実施形態に係る第2の読み出し動作を示すタイミングチャート

【図7】垂直信号線に起因するオフセットを説明するための図

【図8】オフセット補正を説明するための図

【図9】実施形態に係る撮像素子の読み出し方法を示す図

【図10】第1実施形態に係る読み出しおよび補正動作の模式図

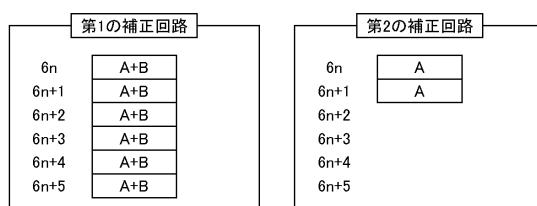

【図11】第2実施形態に係る読み出しおよび補正動作の模式図

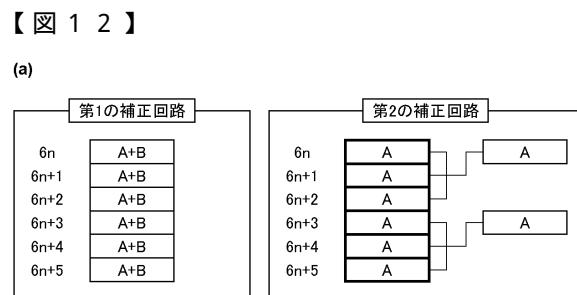

【図12】第3実施形態に係る読み出しおよび補正動作の模式図

20

【図13】第4実施形態に係る読み出しおよび補正動作の模式図

【図14】第5実施形態に係る読み出しおよび補正動作の模式図

【発明を実施するための形態】

【0014】

以下、添付図面を参照して本発明をその例示的な実施形態に基づいて詳細に説明する。なお、以下の実施形態は特許請求の範囲に係る発明を限定しない。また、実施形態には複数の特徴が記載されているが、その全てが発明に必須のものとは限らず、また、複数の特徴は任意に組み合わせられてもよい。さらに、添付図面においては、同一若しくは同様の構成に同一の参照番号を付し、重複した説明は省略する。

【0015】

なお、以下の実施形態では、本発明をデジタルカメラもしくはデジタルビデオカメラである撮像装置で実施する場合に関して説明する。しかし、本発明は撮像機能を有する任意の電子機器で実施可能である。このような電子機器には、コンピュータ機器（パソコンコンピュータ、タブレットコンピュータ、メディアプレーヤ、PDAなど）、携帯電話機、スマートフォン、ゲーム機、ロボット、ドローン、ドライブレコーダが含まれる。なお、これらは例示であり、本発明は他の電子機器でも実施可能である。

30

【0016】

（第1実施形態）

図1は本発明の実施形態に係る撮像素子の構成例を示すブロック図である。撮像素子100は、複数の画素102が行列状に配置された画素部101を有する。画素部101は画素アレイとも呼ばれる。画素部101には原色ベイヤ配列のカラーフィルタが設けられている。図1において、画素102に付されているR、G、Bは、その画素に設けられているカラーフィルタの色を示している。また、画素列ごとに6本の垂直信号線（列信号線）が設けられている。なお、画素列ごとの垂直信号線の数は一例であり、4本、12本、20本など、任意の複数でありうる。図1では画素部101に設けられた数百万から数千万の画素のうち、6行2列の12画素のみを示している。

40

【0017】

画素102Aは、不図示の選択スイッチにより垂直信号線105Aに接続され、画素信号を行ごとに列回路106Aへ出力する。垂直信号線105Aには第1行目から6行ごとに、第6n+1行目（nは0以上の整数）の画素が接続されている。同様に、垂直信号線105Bには第6n+2行目、垂直信号線105Cには第6n+3行目、垂直信号線10

50

5 D には第 6 n + 4 行目、垂直信号線 1 0 5 E には第 6 n + 5 行目、垂直信号線 1 0 5 F には第 6 ( n + 1 ) 行目、の画素が接続される。また、垂直信号線 1 0 5 A ~ 1 0 5 F のそれには対応する列回路 1 0 6 A ~ 1 0 6 F が接続されている。

#### 【 0 0 1 8 】

選択スイッチのオンおよびオフは、垂直走査回路 1 0 4 に接続された信号線 1 0 3 によって画素行ごとに制御される。本実施形態では垂直走査回路 1 0 4 が複数の画素行について同じタイミングで選択スイッチを制御することにより、最大 6 画素行分の画素 1 0 2 から信号を一度に読み出すことができる。

#### 【 0 0 1 9 】

タイミングジェネレータ ( T G ) 1 1 0 は、垂直走査回路 1 0 4 および水平走査回路 1 1 2 の動作を制御するパルス信号を出力する。垂直走査回路 1 0 4 は、T G 1 1 0 から出力されるパルス信号に基づいて、画素部 1 0 1 の各画素 1 0 2 が有するトランジスタの動作を制御する。T G 1 1 0 はまた、D / A 変換器 1 1 1 が用いる基準信号を出力する。D / A 変換器 ( D A C ) 1 1 1 は、時間とともに電圧が変化する参照信号 ( スロープ信号またはランプ信号 ) を生成し、列回路 1 0 6 が有する比較器 1 0 7 に供給する。

10

#### 【 0 0 2 0 】

次に列回路 1 0 6 の構成を述べる。列回路 1 0 6 は垂直信号線 1 0 5 ごとに設けられており、図 1 では垂直信号線 1 0 5 A から 1 0 5 F に対応した列回路 1 0 6 A から 1 0 6 F が形成される。

#### 【 0 0 2 1 】

列回路 1 0 6 は比較器 1 0 7 、カウンタ 1 0 8 、列メモリ 1 0 9 から構成される。比較器 1 0 7 の一方の入力には D A C 1 1 1 で生成された参照信号が入力され、他方の入力には垂直信号線 1 0 5 からの画素信号が入力される。

20

#### 【 0 0 2 2 】

比較器 1 0 7 は垂直信号線 1 0 5 から入力される画素信号の電圧値 ( 電位 V ) と、参照信号の電圧値とを比較し、信号の大小関係が変化すると出力信号のレベルを変化させる。比較器 1 0 7 の出力信号はカウンタ 1 0 8 の動作を制御する。カウンタ 1 0 8 は不図示の信号源から入力されるクロックパルスのパルス数を計測する。カウンタ 1 0 8 は、比較器 1 0 7 の出力信号により、パルス数の計測を終了し、そのときの計測値を出力する。カウンタ 1 0 8 の計測値は、画素信号の電圧値に対応するデジタル値である。なお、パルス数の代わりに時間を計測してもよい。カウンタ 1 0 8 の計測値は列メモリ 1 0 9 に保持される。そして、カウンタ 1 0 8 の計測値はリセットされる。

30

#### 【 0 0 2 3 】

このように、個々の列回路 1 0 6 は対応する垂直信号線 1 0 5 から入力される画素信号を、所定範囲 ( 例えば 0 ~ 2 5 5 ) 内の値を有するデジタル信号に変換する A / D 変換器として機能する。列回路 1 0 6 A は水平走査回路 1 1 2 がオンオフを制御するスイッチを介して水平信号線 1 1 3 A に接続される。列回路 1 0 6 B ~ 1 0 6 F も同様に、水平信号線 1 1 3 B ~ 1 1 3 F に接続される。

#### 【 0 0 2 4 】

水平走査回路 1 1 2 はスイッチをオンオフ制御し、列回路 1 0 6 の列メモリ 1 0 9 に保持されたデジタル信号を水平信号線 1 1 3 A から 1 1 3 F に出力する。水平走査回路 1 1 2 の動作は T G 1 1 0 から供給される制御信号によって制御される。水平信号線 1 1 3 A から 1 1 3 F に出力されたデジタル信号は第 1 の補正回路 1 1 4 に供給される。第 1 の補正回路 1 1 4 は、後述する制御回路 4 0 6 による設定に従って、デジタル信号に対してオフセット補正を適用して、あるいはオフセット補正を適用せずに、撮像素子 1 0 0 の外部へ出力する。基板メモリ 1 1 5 は第 1 の補正回路 1 1 4 がオフセット補正を適用する際に用いるメモリであり、例えば D R A M である。第 1 の補正回路 1 1 4 の詳細については後述する。

40

#### 【 0 0 2 5 】

図 2 は画素 1 0 2 の構成例を示す回路図である。画素 1 0 2 は 1 つのマイクロレンズ(不

50

図示)を共有する複数のフォトダイオード(PD)201Aと201Bとを有する。PD201AおよびPD201Bはそれぞれ、入射光量に応じた電荷を生成する光電変換部として機能する。PD201AおよびPD201Bはそれぞれ副画素とも呼ばれる。

#### 【0026】

以下では、PD201Aが生成する電荷に基づく信号をA信号、PD201Bが生成する電荷に基づく信号をB信号と呼ぶ。また、同じ画素で得られるA信号とB信号とを合わせた信号をA+B信号と呼ぶ。A信号からなる画像とB信号からなる画像とは視差画像対を形成する。一方、複数の画素102から得られるA信号列とB信号列とを用いることで、位相差検出方式の自動焦点検出(AF)を実施することができる。したがって、A信号、B信号は焦点検出用信号もしくはAF用信号とも呼ばれる。

10

#### 【0027】

また、A+B信号は、画素102が1つのPDを有する一般的な撮像素子で得られる画像信号と見なすことができる。したがって、A+B信号は、A信号やB信号を焦点検出用信号と呼ぶ場合に、画像信号もしくは撮影画像信号と呼ばれることがある。なお、A信号はA+B信号からB信号を減じることによって得てもよく、またB信号はA+B信号からA信号を減じることによって得てもよい。画素信号は画素から読み出される信号を意味し、A+B信号、A信号、B信号、もしくは後述するリセット信号Nのいずれでもありうる。

#### 【0028】

PD201Aは転送スイッチ202Aを介して、PD201Bは転送スイッチ202Bを介して、それぞれ共通のフローティングディフュージョン(以下FD)203に接続される。転送スイッチ202Aのオンオフは転送パルスPTXAによって、転送スイッチ202Bのオンオフは転送パルスPTXBによって、それぞれ制御される。転送パルスPTXAおよびPTXBは垂直走査回路104から与えられる。

20

#### 【0029】

FD203はPD201Aおよび201Bの少なくとも一方から転送された電荷を一時的に蓄積することにより、転送された電荷量に応じた電圧を示す。したがって、FD203は電荷を電圧に変換する機能を有する。

#### 【0030】

リセットスイッチ204はFD203に基準電位VDDを供給する。リセットスイッチ204のオンオフは垂直走査回路104が供給するリセットパルスPRESによって制御される。

30

#### 【0031】

画素アンプ205はMOSトランジスタと定電流源からなるソースフォロア回路である。選択スイッチ206は画素アンプ205の電位変動を垂直信号線105に出力する。選択スイッチ206のオンオフは垂直走査回路104が供給する選択パルスPSELによって制御される。

#### 【0032】

転送スイッチ202Aおよび202B、リセットスイッチ204、および選択スイッチ206はそれぞれMOSトランジスタである。

#### 【0033】

図3は撮像素子100の実装例を模式的に示した斜視図である。撮像素子100は主に画素部101が形成された第1の半導体基板301と、列回路106などの読み出し回路と、第1の補正回路114と、基板メモリ115が形成された第2の半導体基板302とが積層された構造をとることができる。第1の半導体基板301と第2の半導体基板302とは例えばバンプによって電気的に接続され、第2の半導体基板302に実装される列回路106は、第1の半導体基板301に設けられた画素102から読み出された画素信号を受け取ることができる。

40

#### 【0034】

図4は撮像素子100を用いた電子機器の一例としての撮像装置400の構成例を示すブロック図である。

50

撮影レンズ 401 は被写体光学像を撮像素子 100 の撮像面に形成する。撮影レンズ 401 は電子機器に対して着脱することで交換可能であってもよい。撮影レンズ 401 はフォーカスレンズなどの可動レンズと絞りとを有している。可動レンズおよび絞りの動作はレンズ駆動回路 402 を通じて制御回路 406 が制御する。

#### 【0035】

シャッタ 403 はメカニカルシャッタであり、撮像素子 100 の露光量を制御する。シャッタ 403 の動作はメカ駆動回路 404 を通じて制御回路 406 が制御する。なお、絞りがメカニカルシャッタを兼ねる場合、メカ駆動回路 404 は絞りを駆動し、レンズ駆動回路 402 は可動レンズを駆動するように構成してもよい。

#### 【0036】

信号処理回路 405 は、撮像素子 100 から得られる信号に対して予め定められた画像処理を適用し、信号を補正したり、別の信号を生成したり、画像データを生成したり、各種の情報を取得および / または生成したりする。後述するオフセット補正処理についても、信号処理回路 405 が行う。信号処理回路 405 は例えば特定の機能を実現するように設計された ASIC のような専用のハードウェア回路であってもよいし、DSP のようなプログラマブルプロセッサがソフトウェアを実行することで特定の機能を実現する構成であってもよい。あるいは、制御回路 406 が信号処理回路 405 の少なくとも一部を兼ねてもよい。

#### 【0037】

信号処理回路 405 が適用する画像処理には、前処理、色補間処理、補正処理、検出処理、データ加工処理、評価値算出処理、特殊効果処理などが含まれる。

前処理には、オフセット補正、信号增幅、基準レベル調整、欠陥画素補正などが含まれる。

色補間処理は、撮影時に得られない色成分の値を補間する処理であり、デモザイク処理や同時化処理とも呼ばれる。

補正処理には、ホワイトバランス調整、階調補正（ガンマ処理）、撮影レンズ 401 の光学収差や周辺減光の影響を補正する処理、色を補正する処理などが含まれる。

検出処理には、特徴領域（たとえば顔領域や人体領域）やその動きの検出、人物の認識処理などが含まれる。

データ加工処理には、合成処理、スケーリング処理、符号化および復号処理、ヘッダ情報生成処理などが含まれる。

評価値算出処理には、自動焦点検出（AF）に用いる信号や評価値の生成、自動露出制御（AE）に用いる評価値の算出処理などが含まれる。

特殊効果処理には、ぼかしの付加、色調の変更、リライティング処理などが含まれる。なお、これらは信号処理回路 405 が適用しうる画像処理の例示であり、信号処理回路 405 が適用する画像処理を限定するものではない。また、例示した画像処理の全てを信号処理回路 405 が実施可能であることを要しない。

#### 【0038】

制御回路 406 は例えば CPU (MPU、マイクロプロセッサとも呼ばれる)、ROM、RAM を有する。制御回路 406 は ROM に記憶されたプログラムを RAM に読み込んで実行することにより、撮像装置 400 の各部の動作を制御し、撮像装置 400 の機能を実現する。なお、撮影レンズ 401 が交換式の場合、制御回路 406 は撮影レンズ 401 が有する制御回路と通信しながら、撮影レンズ 401 の動作を制御する。

#### 【0039】

メモリ 407 は例えば画像データやオフセット補正值を保持するために用いられる。メモリ 407 は撮像素子 100 が有する第 1 の補正回路 114 と、撮像素子 100 の外部に設けられている信号処理回路 405 が有する第 2 の補正回路 4051 との両方からアクセス可能である。なお、第 2 の補正回路 4051 は信号処理回路 405 の一部ではなく、信号処理回路 405 が第 2 の補正回路 4051 として機能してもよい。

#### 【0040】

10

20

30

40

50

記録媒体 408 は例えば着脱可能なメモリカードであり、撮像素子 100 を用いて取得された信号に基づくデータ（例えば撮像画像データ）などを記録するために用いられる。

表示回路 409 は例えば LCD などの表示デバイスを有し、撮像装置 400 の情報、撮影画像およびその情報、GUI 画像などを表示する。

#### 【0041】

操作部材 410 はユーザが撮像装置 400 に指示を与えるために設けられている入力デバイスの総称である。典型的な入力デバイスはボタンおよびスイッチである。また、表示回路 409 がタッチディスプレイの場合、タッチディスプレイが有するタッチパネルは操作部材 410 に含まれる。操作部材 410 に含まれる入力デバイスには、シャッターボタン、電源ボタン、決定ボタン、方向キー、メニューボタンなど、割り当てられた機能に応じた名称が与えられている。なお、同一の操作部材に割り当てられる機能が撮像装置 400 の動作モードなどに応じて変化してもよい。

10

#### 【0042】

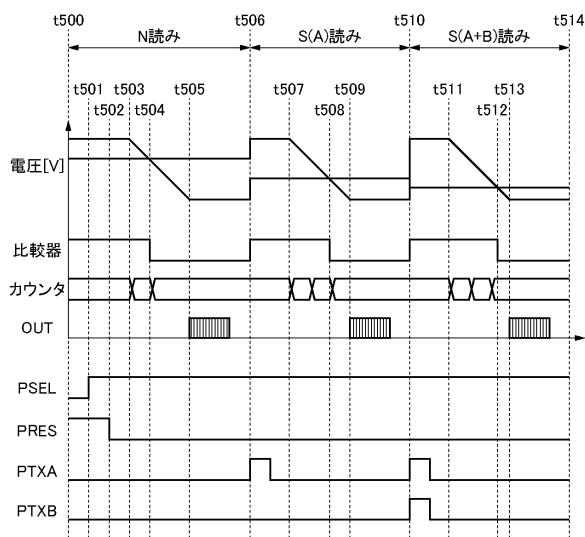

図 5 は撮像素子 100 から信号を読み出す際のタイミングチャートの一例を示している。本実施形態において撮像素子 100 は第 1 ~ 第 3 の読み出しモードを有する。図 5 は第 1 の読み出しモードにおける動作のタイミングチャートである。なお、第 1 の読み出しモードでは撮像素子 100 からリセット信号 N、画像信号（A + B 信号）、および焦点検出用信号（A 信号）を読み出すものとする。

#### 【0043】

時刻 t500 の前にリセットパルス PRES を Hi、転送パルス PTX を Hi とすることにより画素 102 がリセットされる。時刻 t500 において、転送パルス PTX を Lo とすることにより画素 102 のリセットが解除され、電荷の蓄積が開始される。上述の通り、これらの制御パルスは TG110 から供給される制御信号に基づいて垂直走査回路 104 から画素 102 に供給される。

20

#### 【0044】

時刻 t501 において信号の読み出しを行う画素行の選択パルス PSEL が Hi になり、その画素行に含まれる画素 102 が垂直信号線 105 と接続される。

#### 【0045】

時刻 t502 においてリセットパルス PRES が Hi から Lo に変化する。これにより、リセット時点における FD203 の電位 V（リセット信号 N）が垂直信号線 105 を介して比較器 107 に入力される。リセット信号 N は、画素 102 をリセットする際に発生するリセットノイズを除去するために用いられる。

30

#### 【0046】

時刻 t503 において DAC111 は時間とともに電圧レベルが線形に増加もしくは減少する参照信号 VL（ランプ信号）の出力を開始する。図 5 の例では線形減少する参照信号 VL を用いている。DAC111 が参照信号 VL を出力すると、カウンタ 108 がパルスの計数を開始する。

#### 【0047】

時刻 t504 においてリセット信号 N と参照信号 VLとの大小関係が逆転すると、比較器 107 の出力レベルが Hi から Lo に変化する。比較器 107 の出力レベルが Hi から Lo に変化すると、カウンタ 108 の計数値が列メモリ 109 に保持される。

40

#### 【0048】

その後、参照信号 VL が時刻 t505 で所定の下限値に達するまで遷移したのち、水平走査回路 112 によって列回路 106 からリセット信号 N に対応する計数値が出力されると、画素 102 のリセット信号 N の読み出し（N 読み）が終了する。

#### 【0049】

時刻 t506 で転送パルス PTXA が Hi になると、PD201A に蓄積された電荷が FD203 に転送される。これにより、垂直信号線 105 の電位 V が、PD201A に蓄積された電荷に応じた電位となる。この電位が A 信号の値に相当する。また、時刻 t506 で比較器 107 がリセットされる。

50

**【0050】**

時刻  $t_{507}$ においてD A C 1 1 1は再び参照信号V Lの出力を開始する。D A C 1 1 1が参照信号V Lを出力すると、カウンタ1 0 8がパルスの計数を開始する。

時刻  $t_{508}$ においてA信号と参照信号V Lの大小関係が逆転すると、比較器1 0 7の出力レベルがH iからL oに変化する。比較器1 0 7の出力レベルがH iからL oに変化すると、カウンタ1 0 8の計数値が列メモリ1 0 9に保持される。

**【0051】**

その後、参照信号V Lが時刻  $t_{509}$ で所定の下限値に達するまで遷移したのち、水平走査回路1 1 2によって列回路1 0 6からA信号に対応する計数値が出力されると、画素1 0 2のA信号の読み出し(A読み)が終了する。

10

**【0052】**

時刻  $t_{510}$ で転送パルスP T X AとP T X Bの両方がH iになると、P D 2 0 1 AとP D 2 0 1 Bに蓄積された電荷がF D 2 0 3に転送される。これにより、垂直信号線1 0 5の電位Vが、P D 2 0 1 AおよびP D 2 0 1 Bに蓄積された電荷に応じた電位となる。この電位がA + B信号の値に相当する。また、時刻  $t_{510}$ で比較器1 0 7がリセットされる。

**【0053】**

時刻  $t_{511}$ においてD A C 1 1 1は再び参照信号V Lの出力を開始する。D A C 1 1 1が参照信号V Lを出力すると、カウンタ1 0 8がパルスの計数を開始する。

時刻  $t_{512}$ においてA + B信号と参照信号の大小関係が逆転すると、比較器1 0 7の出力レベルがH iからL oに変化する。比較器1 0 7の出力レベルがH iからL oに変化すると、カウンタ1 0 8の計数値が列メモリ1 0 9に保持される。

20

**【0054】**

その後、参照信号V Lが時刻  $t_{513}$ で所定の下限値に達するまで遷移したのち、水平走査回路1 1 2によって列回路1 0 6からA + B信号に対応する計数値が出力されると、画素1 0 2のA + B信号の読み出し(A + B読み)が終了する。

**【0055】**

その後、A信号、A + B信号のそれぞれからリセット信号Nを減算するなど、所定の信号処理が実施される。また、A + B信号からA信号を減算することでB信号が得られる。このようにして、画素1 0 2から画像信号(A + B信号)と、焦点検出用信号(A信号およびB信号)が得られる。

30

**【0056】**

図5には1つの画素1 0 2からの読み出し動作について示している。しかし、同じ動作を垂直信号線1 0 5 Aから1 0 5 Fに接続された複数の画素1 0 2と、対応する列回路1 0 6 Aから1 0 6 Fとについて並行して実施することで、最大で6つの画素行から信号を並列に読み出すことができる。

**【0057】**

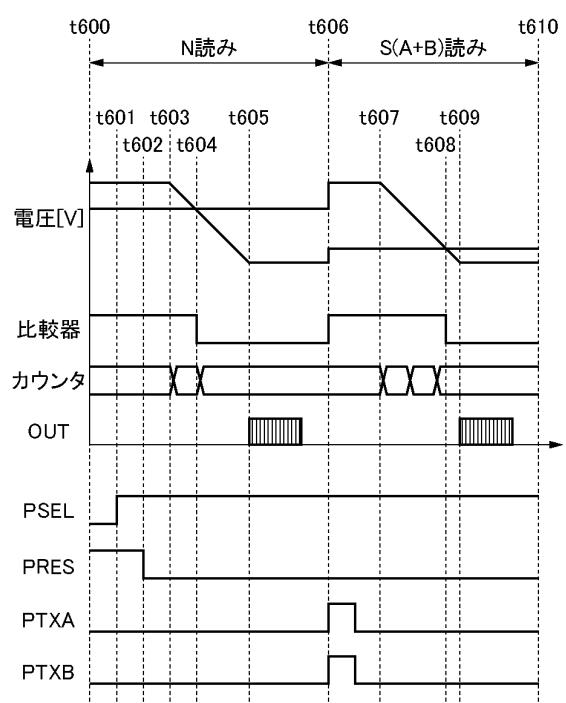

図6は撮像素子1 0 0の第2の読み出しモードにおける動作のタイミングチャートである。第2の読み出しモードでは、リセット信号Nと画像信号(A + B信号)とを読み出すものとする。

40

**【0058】**

時刻  $t_{600}$ から  $t_{605}$ までのリセット信号Nの読み出し(N読み)終了までは図5を用いて説明した第1の読み出しモードにおける時刻  $t_{500}$ から  $t_{505}$ までの動作と同一であるため説明を省略する。

**【0059】**

時刻  $t_{606}$ で転送パルスP T X AとP T X BがH iになると、P D 2 0 1 Aに蓄積された電荷とP D 2 0 1 Bに蓄積された電荷がF D 2 0 3に転送される。これにより、垂直信号線1 0 5の電位Vが、P D 2 0 1 AおよびP D 2 0 1 Bに蓄積された電荷に応じた電位となる。この電位が画像信号(A + B信号)の値に相当する。また、時刻  $t_{606}$ で比較器1 0 7がリセットされる。

50

**【 0 0 6 0 】**

時刻  $t_{607}$ においてD A C 1 1 1は再び参照信号V Lの出力を開始する。D A C 1 1 1が参照信号V Lを出力すると、カウンタ1 0 8がパルスの計数を開始する。

時刻  $t_{608}$ においてA + B信号と参照信号V Lの大小関係が逆転すると、比較器1 0 7の出力レベルがH iからL oに変化する。比較器1 0 7の出力レベルがH iからL oに変化すると、カウンタ1 0 8の計数値が列メモリ1 0 9に保持される。

**【 0 0 6 1 】**

その後、参照信号V Lが時刻  $t_{609}$ で所定の下限値に達するまで遷移したのち、水平走査回路1 1 2によって列回路1 0 6からA + B信号に対応する計数値が出力されると、画素1 0 2のA + B信号の読み出し(A + B読み)が終了する。

10

**【 0 0 6 2 】**

その後、A + B信号からN信号を減算するなど、所定の信号処理が実施される。このようにして、画素1 0 2から画像信号(A + B信号)が得られる。

**【 0 0 6 3 】**

このように、第2の読み出しモードではリセット信号Nと画像信号(A + B信号)の読み出しを行い、第1の読み出しモードで行う焦点検出用信号(A信号またはB信号)の読み出しを行わない。

**【 0 0 6 4 】**

なお、第1の読み出しモードにおいて、時刻  $t_{509}$ での水平走査回路1 1 2がA信号を転送しないことにより、実質的に第2の読み出しモードと同様の読み出しを実現してもよい。第1の読み出しモードにおいて焦点検出用信号を転送しない場合を、第3の読み出しモードと呼ぶ。

20

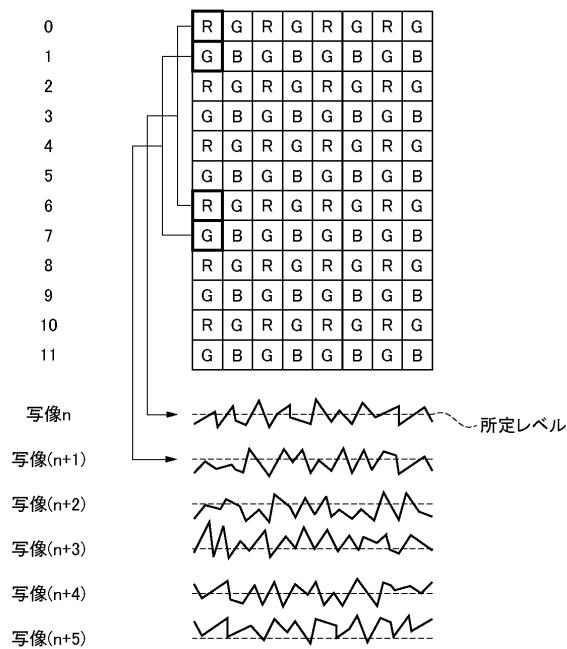

**【 0 0 6 5 】**

図7は画素部1 0 1に含まれる画素1 0 2の列オフセットを説明するための模式図である。列オフセットは、画素列に対応づけて設けられる読み出し回路間の特性のばらつきによって生じる信号レベルのばらつきである。列オフセットは、筋状のノイズとして画像信号に重畠する。

**【 0 0 6 6 】**

図7では一例として、同じ画素列に設けられた6つの列回路1 0 6 Aから1 0 6 Fのそれぞれから出力された信号に基づく、画素部1 0 1が露光されていない状態における列オフセットの分布を示している。

30

**【 0 0 6 7 】**

写像nから写像n + 5は、画素列ごとに、同じ垂直信号線1 0 5に接続された複数の画素についてのオフセットの平均値を求め、平均値を画素行ごとにプロットしたものである。例えば、写像nは、垂直信号線1 0 5 Aに接続されている、画素部1 0 1の6 n(nは0以上の整数)行目に含まれる複数の画素1 0 2について求めたオフセットの平均値の水平方向における分布である。写像(n + 1)から写像(n + 5)は、それぞれ(6 n + 1)行目から(6 n + 5)行目に含まれる画素について同様に求めたオフセットの平均値の分布である。

**【 0 0 6 8 】**

図7に示すように、オフセットの平均値は一定でない。そのため、破線で示した所定のオフセットレベルと実際のオフセットレベルとのずれが、画像の部分的な色むらや、縦筋、横筋といったパターンノイズとして画像信号に現れる。また、一般に、列オフセットは、電源インピーダンスや容量カップリング等に起因する電圧レベルの変動により、垂直信号線ごとにレベルが異なる。このため、撮像素子1 0 0のように画素列ごとに複数の垂直信号線1 0 5 A ~ 1 0 5 Fが設けられている場合、周期的な横筋ノイズが発生しやすい。また、列オフセットは画素から読み出す信号の種類(画像信号か焦点検出用信号か)によつても異なりうる。読み出す信号の種類によるオフセットの差は、主に画素がリセットされてから信号が読み出されるまでの時間の差に起因する。

40

**【 0 0 6 9 】**

50

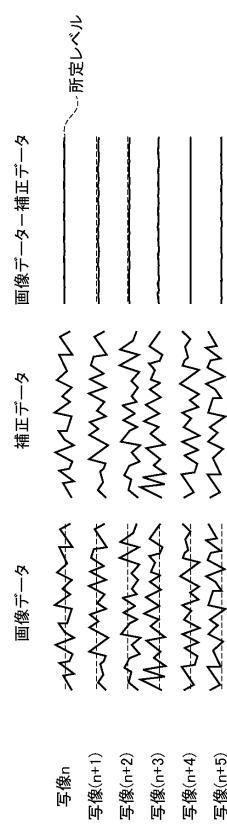

オフセット補正は、上述したオフセットのばらつきを抑制するために実施される。図8はオフセット補正を模式的に示す図である。撮像素子100は、第1の補正回路114により、列回路106Aから106Fのそれぞれから出力される信号に対して個別にオフセット補正を適用することができる。

#### 【0070】

第1の補正回路114は、同じ列に配置され、かつ同じ垂直信号線105に接続される画素102から読み出された信号に対して、あらかじめ記憶された同一の値を減算するオフセット補正を適用する。

#### 【0071】

画素から読み出される信号の値は被写体の明るさやランダムノイズなどの影響によって一定でない。しかし、図7に写像として示したオフセットの平均値を減じることは、列に対応した一定値（オフセット補正值）を減算することに相当する。

10

#### 【0072】

撮像素子の製造時などに、例えば画素部101を遮光した状態で読み出した画像信号や焦点検出用信号に基づいて、図7で説明したように算出したオフセットの平均値を補正值として算出することができる。そして、この補正值を、例えば第1の補正回路114とともに設けられた不揮発性の基板メモリ115に記憶しておく。そして、第1の補正回路114は水平走査回路112によって水平信号線113に出力される信号から補正值を減じることによってオフセット補正を適用することができる。

20

#### 【0073】

オフセット補正により、図8に示すように列方向におけるオフセットのばらつきが抑制され、列方向のオフセットは所定レベル近辺の値となる。そのため、横筋ノイズや色むらを抑制することができる。

#### 【0074】

なお、信号処理回路405が有する第2の補正回路4051は第1の補正回路114と同じ補正機能を有している。第2の補正回路4051は、オフセット補正において用いる補正值を、撮像素子100の第1の補正回路114や基板メモリ115から取得してもよいし、遮光状態において撮像素子100から読み出した画像信号または焦点検出用信号に基づいて生成してもよい。

30

#### 【0075】

なお、第1の補正回路114および第2の補正回路4051が用いる補正值は必ずしも予め記憶された補正值でなくてもよい。例えば、撮影の直前に撮像素子100から得られる信号に基づいて補正值を生成して用いるように構成されてもよい。

#### 【0076】

また、補正の対象は遮光時における画素値のオフセットに限定されない。例えば、垂直信号線105ごとのゲインのばらつきを予め補正值として記憶しておき、各列のゲイン補正として適用することも可能である。

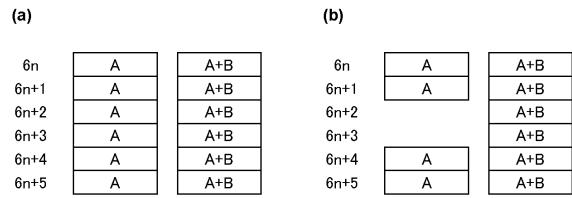

#### 【0077】

次に、図9を用いて、撮像素子100から行ごとに読み出す信号の種別に関して説明する。図9(a)は撮像素子100のすべての行で画像信号(A+B信号)と焦点検出用信号(A信号またはB信号)とを読み出す場合を模式的に示している。図9以降では画像信号をA+B、焦点検出用信号をAと表記する。本実施形態では列ごとに6つの垂直信号線105A～105Fが設けられているため、撮像素子100の画素部101の画素行を6n行目～(n+5)行目として示している(nは0以上の整数)。

40

#### 【0078】

図9(a)に示すように、全ての画素行について画像信号と焦点検出用信号とを読み出す場合、全ての画素行から第1の読み出しモードで信号を読み出す。

#### 【0079】

一方、図9(b)は、画像信号(A+B信号)は全ての画素行から読み出すが、焦点検出用信号(A信号またはB信号)は一部の画素行からのみ読み出す場合を示している。具

50

体的には、図9(b)は、 $6n$ 行目、 $6(n+1)$ 行目、 $6(n+4)$ 行目、 $6(n+5)$ 行目から焦点検出用信号(A信号)を読み出し、 $6(n+2)$ 行目と $6(n+3)$ 行目からは焦点検出用信号(A信号)を読み出さない場合を示している。

#### 【0080】

図9(b)に示すような場合、画像信号と焦点検出用信号の両方を読み出す画素行については第1の読み出しモードで信号を読み出し、画像信号のみを読み出す画素行については第2または第3の読み出しモードで信号を読み出す。図9(b)のように、焦点検出用信号を読み出さない画素行を設けることで、1フレーム分の信号読み出し時間を削減することができる。

#### 【0081】

以下、全ての画素行から焦点検出用信号を読み出す場合を全行AF読み出し、一部の画素行から焦点検出用信号を読み出す場合を部分AF読み出しと呼ぶ。第1から第3の読み出しモードに応じた読み出し動作は、制御回路406がTG110の動作を制御することにより実現することができる。また、部分AF読み出しにおいてどの行から焦点検出用信号を読み出すかについても、制御回路406がTG110の動作を制御することにより制御することができる。

#### 【0082】

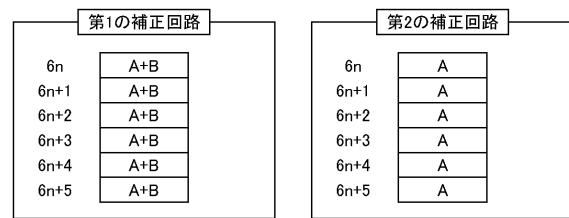

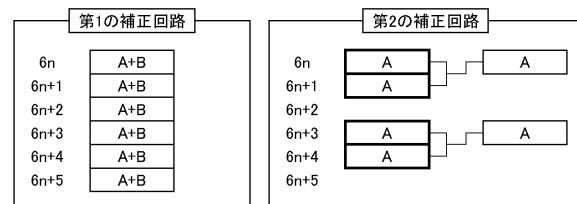

次に、第1の補正回路114と第2の補正回路4051とがどのようにオフセット補正を分担するかについて図10を用いて説明する。図10は、全行AF読み出しの場合の例を示している。

#### 【0083】

図10に示すように、全行AF読み出しの場合、第1の補正回路114では画像信号(A+B信号)に対してオフセット補正を適用し、焦点検出用信号(A信号)に対してはオフセット補正を適用しない。一方、第2の補正回路4051は焦点検出用信号(A信号)に対してオフセット補正を適用し、画像信号(A+B信号)に対してはオフセット補正を適用しない。

#### 【0084】

具体的には、制御回路406が、第1の補正回路114に対し、画像信号(A+B信号)についてはオフセット補正を適用してから信号を出力し、焦点検出用信号(A信号)についてはオフセット補正を行わずに信号を出力するように設定する。また、制御回路406が、第2の補正回路4051に対し、画像信号(A+B信号)についてはオフセット補正を適用せず、焦点検出用信号(A信号)についてはオフセット補正を行うように設定する。

#### 【0085】

したがって、図5に示した第1の読み出しモードの動作において、第1の補正回路114は、時刻t509から出力される焦点検出用信号(A信号)についてはオフセット補正を適用せずにメモリ407に書き込む。そして、第2の補正回路4051(信号処理回路405)が、メモリ407から焦点検出用信号(A信号)を読み出してオフセット補正を適用し始める。第2の補正回路4051(信号処理回路405)は、オフセット補正を適用した焦点検出用信号(A信号)をメモリ407に再び書き込む。

#### 【0086】

その後、第1の補正回路114は、時刻t513から出力される画像信号(A+B信号)についてオフセット補正を適用してからメモリ407に書き込む。一方、第2の補正回路4051(信号処理回路405)は、メモリ407に書き込まれた画像信号(A+B信号)についてはオフセット補正を適用しない。

#### 【0087】

信号処理回路405は、メモリ407に書き込まれたオフセット補正済みの画像信号(A+B信号)および焦点検出用信号(A信号)から焦点検出用信号(B信号)を生成する。

#### 【0088】

このように、本実施形態では、撮像素子から画像信号と焦点検出用信号とを読み出す場

10

20

30

40

50

合、それぞれの信号に対して適用する補正処理を、一方の信号については撮像素子内の補正回路で、他方の信号については撮像素子外の補正回路で適用するようにした。これにより、読み出す信号の種類ごとに異なる補正值を用いる場合、撮像素子内に保持する補正值の量を削減することができる。特に、画素列ごとに複数の垂直信号線が設けられており、垂直信号線ごとの補正值を用いる場合には効果が大きい。

#### 【0089】

また、画像信号と焦点検出用信号のように、1回の露光処理に対応して複数種の画素信号を読み出す場合、連写速度の上限は読み出しに要する時間によって制限を受ける。本実施形態では、信号の種類に応じて補正処理を2つの補正回路で分担するため、読み出しに要する時間を短縮することができ、連写速度の向上に寄与する。

10

#### 【0090】

なお、上述の説明ではオフセット補正を画像信号と焦点検出用信号に適用するものとしたが、リセット信号Nについてもオフセット補正を適用してもよい。この場合、リセット信号Nのオフセット補正是第1の補正回路114と第2の補正回路4051のどちらで適用してもよい。制御回路406はリセット信号N用の補正值を記憶した補正回路にリセット信号Nに対するオフセット補正を適用するように設定する。

#### 【0091】

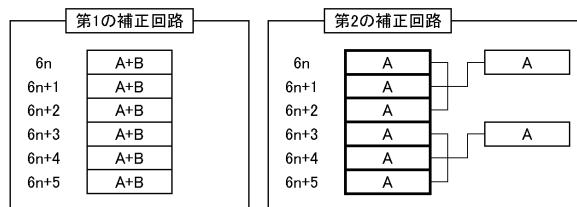

##### (第2実施形態)

次に、本発明の第2実施形態について説明する。なお、本実施形態は第2の補正回路4051の動作以外は第1実施形態と同じであってよいため、以下では本実施形態における第2の補正回路4051の動作について重点的に説明する。

20

#### 【0092】

図11は第2実施形態における読み出しおよび補正動作を図10と同様に示した図である。ここでは、画像信号(A+B信号)と焦点検出用信号(A信号)は第1実施形態と同様に、全行にわたって読み出されている。

#### 【0093】

第1の補正回路114が画像信号(A+B信号)に対して適用するオフセット補正処理は第1実施形態と同じである。一方、焦点検出用信号を補正する第2の補正回路4051は、垂直信号線105A～105Fにそれぞれ接続された6n行～(6n+5)行の画素から読み出された焦点検出用信号から、補正を適用する焦点検出用信号を生成する。

30

#### 【0094】

第2の補正回路4051は複数行分の画素信号を1行分に合成する。例えば、第2の補正回路4051は、6n行、(6n+1)行、(6n+2)行の画素から読み出された焦点検出用信号を1行分の焦点検出用信号に合成する。また、第2の補正回路4051は、(6n+3)行、(6n+4)行、(6n+5)行の画素から読み出された焦点検出用信号を1行分の焦点検出用信号に合成する。合成は例えば各行の同じ列から読み出された焦点検出用信号を加算平均することであってよい。

#### 【0095】

なお、第2の補正回路4051が合成を行なうか否か、またどの行の画素信号を合成するかについては、制御回路406が第2の補正回路4051に設定する。また、第2の補正回路4051が複数の合成方法をサポートしている場合、使用する合成方法についても制御回路406が第2の補正回路4051に設定する。

40

#### 【0096】

そして第2の補正回路4051は、生成した2行分の焦点検出用信号に対してオフセット補正を適用する。したがって、第2の補正回路4051が用いる補正值は、合成後の焦点検出用信号に対応した補正值である。補正值は、例えば、合成を行わない場合に用いる補正值(第1実施形態の第2の補正回路4051が用いる補正值)を、焦点検出用信号と同様に合成することによって生成することができる。また、合成後の焦点検出用信号に対応した補正值をあらかじめ取得し、保持しておいてよい。

#### 【0097】

50

このように、補正を適用する焦点検出用信号を削減することにより、第2の補正回路4051が用いる補正值の量を削減することができる。合成によって補正の精度は低下するが、焦点検出用信号は画像信号よりも要求される補正精度が低いため、補正值のデータ量を削減できる効果の方が大きい。画素列ごとに複数の垂直信号線が設けられる場合、合成を行わないと垂直信号線ごとに補正值が必要になるため、特に効果が大きい。

#### 【0098】

なお、図11では画素列ごとに6つの垂直信号線が設けられる構成において、隣接する3つの垂直信号線から読み出される信号に対して共通の補正值を用いるようにした。しかし、共通の補正值を用いる垂直信号線の数や位置関係は単なる例示に過ぎない。

#### 【0099】

例えば $6n$ 行から $(6n+5)$ 行を1行に合成し、全ての焦点検出用信号について共通の補正值を用いてもよい。また、図1のように画素部101に原色ベイヤ配列のカラーフィルタが設けられている場合、同色のカラーフィルタが設けられた複数の画素から読み出された焦点検出用信号を合成するようにしてもよい。具体的には、 $6n$ 行、 $(6n+2)$ 行、 $(6n+4)$ 行の画素から読み出された信号を1行に合成し、 $(6n+1)$ 行、 $(6n+3)$ 行、 $(6n+5)$ 行の画素から読み出された信号を1行に合成することができる。

#### 【0100】

また、全行AF読み出しを行う代わりに部分AF読み出し(図9(b))を行ってもよい。この場合、A信号の読み出しに要する時間や第2の補正回路4051での合成に要する時間を削減することができる。第2の補正回路4051は、焦点検出用信号の読み出し方法と合成方法に合わせた補正值を用いてオフセット補正を適用する。

#### 【0101】

本実施形態では、第1実施形態の効果に加え、画像信号の補正精度は維持しながら、焦点検出用信号のオフセット補正に要する記憶容量や処理時間を削減することができる。

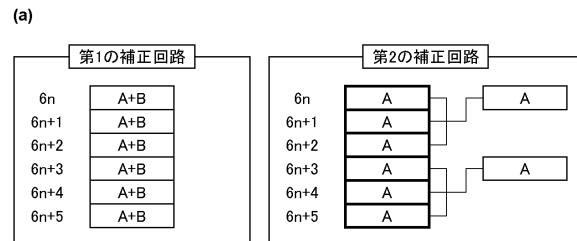

#### 【0102】

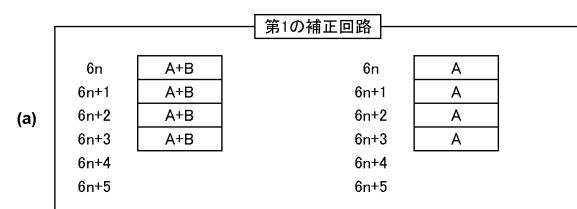

##### (第3実施形態)

次に、本発明の第3実施形態について説明する。なお、本実施形態は第2の補正回路4051の動作以外は第1実施形態と同じであってよいため、以下では本実施形態における第2の補正回路4051の動作について重点的に説明する。

#### 【0103】

図12は第3実施形態における読み出しおよび補正動作を図10と同様に示した図である。画像信号(A+B信号)の読み出しと、画像信号(A+B信号)に対するオフセット補正とについては、第1実施形態と同様である。

#### 【0104】

一方、焦点検出用信号(A信号)については、全行AF読み出しの場合(図12(a))と、部分AF読み出し(図12(b))の場合がある。焦点検出用信号の読み出し方法は、例えば撮像装置400の撮影モードと予め対応付けられている。したがって、制御回路406は、設定されている撮影モードに応じて、像素子100からの焦点検出用信号の読み出し方法を全行AF読み出しか部分AF読み出しか決定し、TG110に読み出し方法を設定する。また、第2の補正回路4051において画素信号の合成を行う場合、制御回路406は合成する行および合成方法を第2の補正回路4051に設定する。

#### 【0105】

例えば低照度のシーンなど、AF精度が低下しやすいシーンを撮影する撮影モードについては、全行AF読み出しを行い、それ以外のシーンを撮影する撮影モードについては部分AF読み出しを行う。あるいは、高い撮影フレームレートが必要な撮影モードについては部分AF読み出しを行い、他の撮影モードでは全行AF読み出しを行ってもよい。なお、これらは読み出し方法と撮影モードとの対応付けの単なる例示であり、他の対応付け也可能である。

#### 【0106】

また、撮影モードに限らず、他の条件に応じて読み出し方法を決定してもよい。例えば

10

20

30

40

50

、消費電力を低減する必要がある場合や、低消費電力での動作が設定されている場合には部分 A F 読み出しを行うようにすることができる。

#### 【 0 1 0 7 】

図 1 2 ( b ) に示す例では部分 A F 読み出し時に ( 6 n + 2 ) 行および ( 6 n + 5 ) 行以外の画素から焦点検出用信号 ( A 信号 ) を読み出すが、信号を読み出さない行の数や配置はこれに限定されない。

#### 【 0 1 0 8 】

全行 A F 読み出しの場合、第 2 の補正回路 4 0 5 1 は、第 2 実施形態と同様に、6 行分の焦点検出用信号 ( A 信号 ) の連続する 3 行分をそれぞれ 1 行に合成して 2 行分の焦点検出用信号を生成する。

10

#### 【 0 1 0 9 】

一方、部分 A F 読み出しの場合、第 2 の補正回路 4 0 5 1 は、6 n 行の画素から読み出された信号と ( 6 n + 1 ) 行の画素から読み出された信号とを 1 行に合成する。第 2 の補正回路 4 0 5 1 は、さらに、( 6 n + 3 ) 行の画素から読み出された信号と ( 6 n + 4 ) 行の画素から読み出された信号とを 1 行に合成することにより、2 行分の焦点検出用信号を生成する。合成は例えば列ごとに画素値を加算平均することであってよい。部分 A F 読み出しにより焦点検出用信号の読み出し量を削減でき、撮影フレームレートの向上や消費電力の低減が実現できる。

#### 【 0 1 1 0 】

本実施形態により、第 2 実施形態と同様に、焦点検出用信号に適用するオフセット補正で用いる補正值のデータ量を削減することができる。具体的には、全行 A F 読み出しの場合と、部分 A F 読み出しの場合とのそれについて、2 行分の補正值を記憶しておけばよい。

20

#### 【 0 1 1 1 】

なお、本実施形態では、全行 A F 読み出しの場合と部分 A F 読み出しの場合とで合成後の焦点検出用信号の行数が等しい。さらに、全行 A F 読み出しの場合に合成する行に含まれる行を部分 A F 読み出しの場合に合成するようにしている。そのため、用意する補正值のデータ量をさらに削減する必要があれば、全行 A F 読み出しの場合に用いる補正值を、部分 A F 読み出しの場合にも用いるようにしてもよい。これにより、補正值のデータ量をさらに削減することができる。

30

#### 【 0 1 1 2 】

補正值は、例えば、合成を行わない場合の補正值 ( 第 1 実施形態の第 2 の補正回路 4 0 5 1 が用いる補正值 ) を、第 2 の補正回路 4 0 5 1 における行データの合成方法と同様にして合成することによって生成することができる。

#### 【 0 1 1 3 】

第 2 の補正回路 4 0 5 1 は、合成後の 2 行分の焦点検出用信号のそれから、対応する補正值を減算することにより、オフセット補正を適用する。

#### 【 0 1 1 4 】

本実施形態では、第 2 実施形態の効果に加え、部分 A F 読み出しを併用することにより、焦点検出用信号の読み出しおよび補正に要する時間を短縮することができる。また、全行 A F 読み出しの場合の補正值を部分 A F 読み出しの場合にも用いるようにすれば、補正值用の記憶容量を第 2 実施形態と同等に抑制することができる。

40

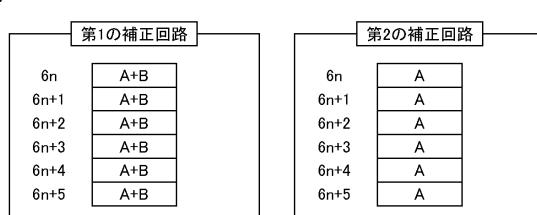

#### 【 0 1 1 5 】

##### ( 第 4 実施形態 )

次に、本発明の第 4 実施形態について説明する。第 4 実施形態は、撮像装置 4 0 0 が記録する信号の種類に応じた補正動作に関する。撮像装置 4 0 0 は、ユーザ設定により、記録する信号の種類を変更可能である。例えば、撮像装置 4 0 0 は、画像信号に加え、焦点検出用信号を記録するか否かを設定可能であるものとする。

#### 【 0 1 1 6 】

図 1 3 ( a ) は、焦点検出用信号を記録する場合の読み出し動作と補正動作を模式的に

50

示している。この場合、画像信号（A + B 信号）と焦点検出用信号（A 信号）とが全行について読み出される。このように、全画素について焦点検出用信号を記録することにより、撮影後に合焦距離の調整やゴースト除去を実施することが可能になる。これらの処理において A 信号は画像信号としても用いられるため、A + B 信号と同様の精度でオフセット補正を行う必要がある。

#### 【0117】

したがって、焦点検出用信号（A 信号）を記録する場合には、第 1 実施形態と同様に、A + B 信号については第 1 の補正回路 114 でオフセット補正を適用し、A 信号については第 2 の補正回路 4051 でオフセット補正を適用する。

#### 【0118】

焦点検出用信号（A 信号）を記録しない場合は、第 1 ~ 第 3 実施形態における焦点検出用信号（A 信号）と同様に、焦点検出用信号を撮像装置 400 の AF 動作にのみ用いる場合である。この場合、図 13 (b) に示すように、部分 AF 読み出しを行い、焦点検出用信号（A 信号）に対して第 2 の補正回路 4051 でオフセット補正を適用する。なお、焦点検出用信号（A 信号）を記録しない場合には、第 2 実施形態（図 11 (a)）または第 3 実施形態（図 12 (b)）と同様に焦点検出用信号（A 信号）に対するオフセット補正を適用してもよい。

#### 【0119】

制御回路 406 は、記録する信号の設定に応じて、図 13 (a) および図 13 (b) に示した読み出しおよびオフセット補正を実施するように、TG110、第 1 の補正回路 114、および第 2 の補正回路 4051 に設定する。

#### 【0120】

本実施形態によれば、画像信号に加えて焦点検出用信号を記録する場合と、焦点検出用信号は記録しない場合とで、それぞれ適切なオフセット補正を焦点検出用信号に適用することができる。また、2つの補正回路でオフセット補正処理を分担することにより、撮像素子内に保持する補正值のデータ量を削減することができるとともに、オフセット補正に要する時間を短縮することができる。

#### 【0121】

なお、焦点検出用信号（A 信号）を記録する場合に、画像信号（A + B 信号）だけでなく焦点検出用信号（A 信号）についても第 1 の補正回路 114 でオフセット補正を適用するようにしてかまわない。撮像素子内に保持する補正值のデータ量を減らす必要がある場合には、撮像素子の外部から補正值を入力するようにしてもよい。

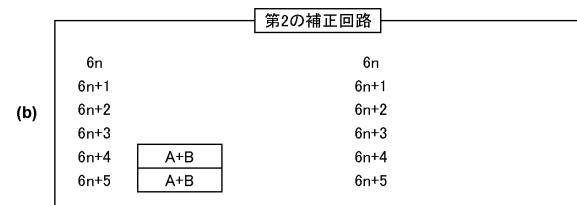

#### 【0122】

##### (第 5 実施形態)

次に、本発明の第 5 実施形態について説明する。本実施形態は、列ごとに設けられた複数の垂直信号線を 2 つのグループに分割し、第 1 グループの垂直信号線と第 2 グループの垂直信号線とで読み出し周期（読み出しレート）が異なる場合のオフセット補正に関する。

#### 【0123】

図 14 は第 5 実施形態における読み出しおよび補正動作を図 10 と同様に示した図である。本実施形態では列ごとに設けられている 6 つの垂直信号線 105A ~ 105F を垂直信号線 105A ~ 105D と 105E ~ 105F との 2 グループに分割し、各グループで読み出し周期を異ならせている。

#### 【0124】

具体的には、垂直信号線 105A ~ 105D (6n 行 ~ (6n + 3) 行) の画素からは第 1 の周期で画像信号（A + B 信号）と焦点検出用信号（A 信号）とを読み出す（図 14 (a)）。読み出された画素信号は、画像データの生成と焦点検出に用いられる。

#### 【0125】

また、垂直信号線 105E ~ 105F ((6n + 4) 行 ~ (6n + 5) 行) の画素からは第 1 の周期より短い第 2 の周期で画像信号（A + B 信号）を読み出し、焦点検出用信号は読み出さない（図 14 (b)）。読み出された画素信号は一般にマルチストリーム信号

10

20

30

40

50

と呼ばれ、環境光のフリッカー検知や露出制御に用いられる。

#### 【0126】

なお、垂直信号線 105 をグループに分割する方法や読み出す信号の種類については単なる例示である。例えば、第1の周期では画像信号のみを読み出し、焦点検出用信号については第2の周期で読み出して第2の補正回路 4051 でオフセット補正を適用してもよい。ただし、第2の周期で読み出す垂直信号線の数は、第1の周期よりも短い周期で読み出すために、第1の周期で読み出す垂直信号線の数よりも少なくするのが一般的である。

#### 【0127】

このような、垂直信号線 105 に応じた読み出し周期の制御は、制御回路 406 が TG 110 の動作を制御することで実現することができる

10

#### 【0128】

本実施形態では、第1の周期で読み出される画素信号については第1の補正回路 114 で、第2の周期で読み出される画素信号については第2の補正回路 4051 でオフセット補正を適用するものとする。なお、補正回路と補正する画素信号の関係は逆でもよい。基本的に、画素信号を合成してオフセット補正を適用する場合には第2の補正回路 4051 を用いるが、画素信号の合成を伴わない場合には、第1の補正回路 114 および第2の補正回路 4051 のどちらでオフセット補正を適用してもよい。

#### 【0129】

図14に示す例では、基板メモリ 115 に垂直信号線 105A ~ 105D ごと、かつ読み出す画素信号の種類ごとの、計 8 種類の補正值を保持する。また、メモリ 407 には垂直信号線 105E ~ 105F ごとに計 2 種類の画像信号用の補正值を保持する。先の実施形態と同様、基板メモリ 115 が保持する補正值は、予め保持されていてもよいし、メモリ 407 から取得してもよい。

20

#### 【0130】

なお、第2の補正回路 4051 では、(6n+4) 行と (6n+5) 行の画素から読み出された画素信号 (A+B 信号) を 1 行に合成してからオフセット補正を適用してもよい。この場合、第2の補正回路 4051 で用いる補正值の量を半減することができる。

#### 【0131】

制御回路 406 は、垂直信号線 105A ~ 105D に対応する水平信号線 113A ~ 113D に読み出される画素信号にのみオフセット補正を適用するように第1の補正回路 114 を設定する。また、制御回路 406 は、垂直信号線 105E ~ 105F に対応する水平信号線 113E ~ 113F に読み出される画素信号にのみオフセット補正を適用するように第2の補正回路 4051 を設定する。制御回路 406 は、第2の補正回路 4051 に、補正前に合成を行うか否かについても設定することができる。

30

#### 【0132】

本実施形態によれば、画素行に応じて周期が異なる読み出しを行う場合に、第1の周期で読み出される画素信号については第1の補正回路で、第2の周期で読み出される画素信号については第2の補正回路で、それぞれオフセット補正を適用する。そのため、撮像素子に保持する補正值を削減しつつ、オフセット補正の負荷を分散することができる。

#### 【0133】

##### (その他の実施形態)

本発明は、上述の実施形態の 1 以上の機能を実現するプログラムを、ネットワーク又は記憶媒体を介してシステム又は装置に供給し、そのシステム又は装置のコンピュータにおける 1 つ以上のプロセッサーがプログラムを読み出し実行する処理でも実現可能である。また、1 以上の機能を実現する回路（例えば、ASIC）によっても実現可能である。

40

#### 【0134】

本発明は上述した実施形態の内容に制限されず、発明の精神および範囲から離脱することなく様々な変更及び変形が可能である。したがって、発明の範囲を公にするために請求項を添付する。

#### 【符号の説明】

50

## 【0135】

100...撮像素子、114...第1の補正回路、304...基板メモリ、400...撮像装置、

401...撮影レンズ、402...レンズ駆動回路、403...シャッタ、404...メカ駆動回路、

405...信号処理回路、406...制御回路、407...メモリ

## 【図面】

## 【図1】

## 【図2】

100

10

20

30

40

50

【図3】

【図4】

【図5】

【図6】

10

20

30

40

50

【図 7】

【図 8】

10

20

30

【図 9】

【図 10】

40

50

【図 1 1】

【図 1 2】

10

(a)

【図 1 3】

【図 1 4】

20

(a)

(a)

(b)

30

(b)

40

50

---

フロントページの続き

(56)参考文献      特開2015-002531(JP,A)

特開2021-002807(JP,A)

特開2016-201660(JP,A)

特開2013-037296(JP,A)

(58)調査した分野 (Int.Cl., DB名)

H04N 5/30 - 5/33

H04N 23/11

H04N 23/20 - 23/30

H04N 25/00

H04N 25/20 - 25/61

H04N 25/615 - 25/79