(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4200682号

(P4200682)

(45) 発行日 平成20年12月24日(2008.12.24)

(24) 登録日 平成20年10月17日(2008.10.17)

(51) Int.Cl.

B 41 J 2/44 (2006.01)

F 1

B 41 J 3/00

M

請求項の数 3 (全 12 頁)

(21) 出願番号 特願2002-72081 (P2002-72081)

(22) 出願日 平成14年3月15日 (2002.3.15)

(65) 公開番号 特開2003-266760 (P2003-266760A)

(43) 公開日 平成15年9月24日 (2003.9.24)

審査請求日 平成17年1月26日 (2005.1.26)

(73) 特許権者 000001270

コニカミノルタホールディングス株式会社

東京都千代田区丸の内一丁目6番1号

(74) 代理人 100090033

弁理士 荒船 博司

(72) 発明者 芳野 剛

東京都八王子市石川町2970番地 コニカ株式会社内

(72) 発明者 高木 幸一

東京都八王子市石川町2970番地 コニカ株式会社内

(72) 発明者 泉宮 賢二

東京都八王子市石川町2970番地 コニカ株式会社内

最終頁に続く

(54) 【発明の名称】 画像形成装置

## (57) 【特許請求の範囲】

## 【請求項 1】

多段接続された複数の遅延素子により、基準クロック信号を遅延させ、各段毎に遅延基準クロック信号として出力する遅延手段と、所定信号と同期する遅延基準クロック信号に基づいて、前記基準クロック信号の1周期分に係る前記遅延素子の段数を検出する検出手段と、

前記所定信号を計数する計数手段と、

前記検出手段により検出された段数、前記計数手段により計数された計数量、位相制御信号及び前記遅延手段を選択するための選択信号の刻み幅を示す分解能を積算した積算情報を作成し、当該積算された積算情報を基づいて、前記選択信号を生成し、当該生成された選択信号に基づいて、前記遅延基準クロック信号の中から逐一的に信号を選択することにより画素クロック信号を出力する信号選択手段と、

前記画素クロック信号に同期した画像先端信号を生成し、出力する画像先端信号生成手段と、

を有することを特徴とする画像形成装置。

## 【請求項 2】

前記画像先端信号に応じて画像の各行の先頭の書き出し位置を制御することを特徴とする請求項1に記載の画像形成装置。

## 【請求項 3】

前記信号選択手段は、前記積算情報を前記基準クロック信号の周期を超えた際に、前記

画像先端信号の位相を変化させるための指示信号を出力し、

前記画像先端信号生成手段は、前記指示信号に基づいて前記画像先端信号を生成することを特徴とする請求項1または請求項2に記載の画像形成装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、画像形成装置に関する。

【0002】

【従来の技術】

複写機等の画像形成装置は、温度変化による書き込みユニットおよび読み取りユニットのレンズ特性の変化、装置組み立て時の製造誤差、各製品の製造バラツキ等によって、画像読み取り時もしくは書き込み時において読み取り画像もしくは形成する画像が傾く（歪む）ことがあった。そこで、画像を形成する際に画像データを画素単位で加工して、画像がまっすぐに形成されるように補正する処理を行っていた。

10

【0003】

【発明が解決しようとする課題】

しかしながら、このような画像データの加工は誤差拡散等の画像処理に影響を及ぼし、モアレ等の発生を引き起こす場合があり、画像の画質劣悪等の原因となっていた。一方、複写機等の画像形成装置では、1つの画像を主走査方向に1行ずつ出力し、それを副走査方向に対して繰り返すことによって画像を形成する。

20

【0004】

そこで、本発明の課題は、基準クロックの周期以下の分解能で画像の各行の先頭の書き出し位置を制御することによって、高精度な画像の補正を行う回路を提供することである。

【0005】

【課題を解決するための手段】

以上の課題を解決するため、請求項1記載の発明は、

多段接続された複数の遅延素子により、基準クロック信号を遅延させ、各段毎に遅延基準クロック信号として出力する遅延手段と、所定信号と同期する遅延基準クロック信号に基づいて、前記基準クロック信号の1周期分に係る前記遅延素子の段数を検出する検出手段と、

30

前記所定信号を計数する計数手段と、

前記検出手段により検出された段数、前記計数手段により計数された計数量、位相制御信号及び前記遅延手段を選択するための選択信号の刻み幅を示す分解能を積算した積算情報を演算し、当該演算された積算情報を基づいて、前記選択信号を生成し、当該生成された選択信号に基づいて、前記遅延基準クロック信号の中から択一的に信号を選択することにより画素クロック信号を出力する信号選択手段と、

前記画素クロック信号に同期した画像先端信号を生成し、出力する画像先端信号生成手段と、を有することを特徴としている。

【0006】

この請求項1記載の発明によれば、例えば、パルス信号やステップ信号等の所定信号と同期する遅延基準クロック信号に基づいて基準クロック信号の1周期分に係る遅延素子の段数を検出し、この段数、計数量、位相制御信号及び遅延手段を選択するための選択信号の刻み幅を示す分解能を積算した積算情報を演算する。そして、この積算情報を基づいて、選択信号を生成し、当該生成された選択信号に基づいて、遅延基準クロック信号の中から択一的に選択した信号を外部出力する。これにより、遅延基準クロック信号のタイミングを基準クロック信号の1周期以下の時間で制御でき、高精度な制御を実現できる。

40

【0008】

また、請求項2記載の発明は、請求項1記載の画像形成装置であって、

前記画像先端信号に応じて画像の各行の先頭の書き出し位置を制御することを特徴としている。

50

## 【0009】

この請求項 2 記載の発明によれば、画像先端信号に基づいたタイミングで、信号選択手段から出力された信号に同期した信号を生成する。これにより、画像の各行の先端の書き出し位置を高精度で制御できる。

## 【0011】

そして、請求項 3 記載の発明は、請求項 1 または 2 記載の画像形成装置であって、前記信号選択手段は、前記積算情報が前記基準クロック信号の周期を超えた際に、前記画像先端信号の位相を変化させるための指示信号を出力し、

前記画像先端信号生成手段は、前記指示信号に基づいて前記画像先端信号を生成することを特徴としている。

10

## 【0012】

この請求項 3 記載の発明によれば、画像先端信号生成手段は、指示信号に基づいて画像先端信号を生成する。これにより、画像の傾き等を補正して出力することができる。

## 【0013】

## 【発明の実施の形態】

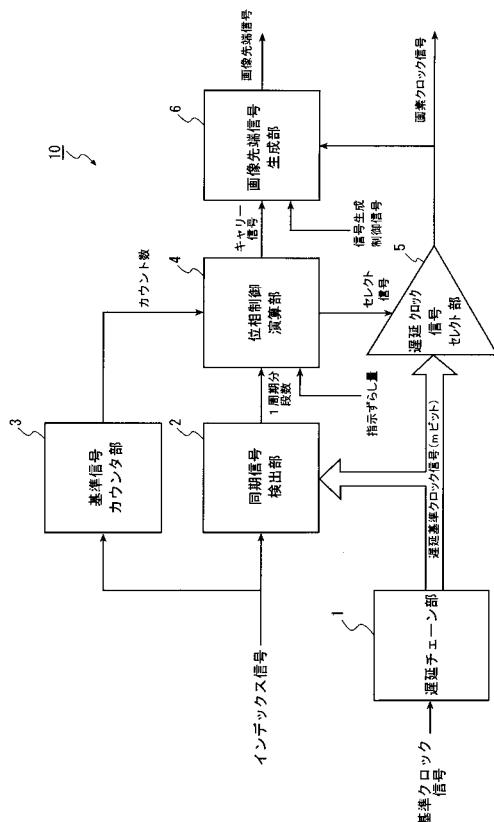

以下、図 1 ~ 図 7 を参照して本発明を適用した信号制御回路 10 の、実施の形態を詳細に説明する。本実施の形態では、信号制御回路 10 を用いて 1 つの画像データに対して画像の傾き（歪み）の補正を行うこととして説明する。

## 【0014】

図 1 は、信号制御回路 10 の構成を示すブロック図である。信号制御回路 10 は、遅延チェーン部 1、同期信号検出部 2、基準信号カウンタ部 3、位相制御演算部 4、遅延クロック信号セレクト部 5 および画像先端信号生成部 6 によって構成される。信号制御回路 10 は、例えば複写機等に用いられる。

20

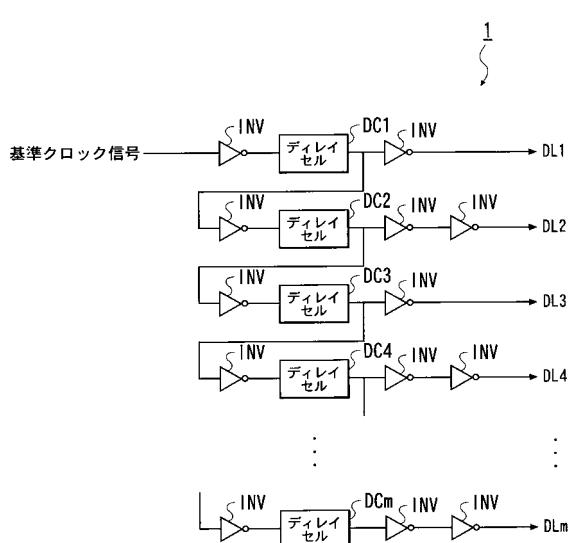

## 【0015】

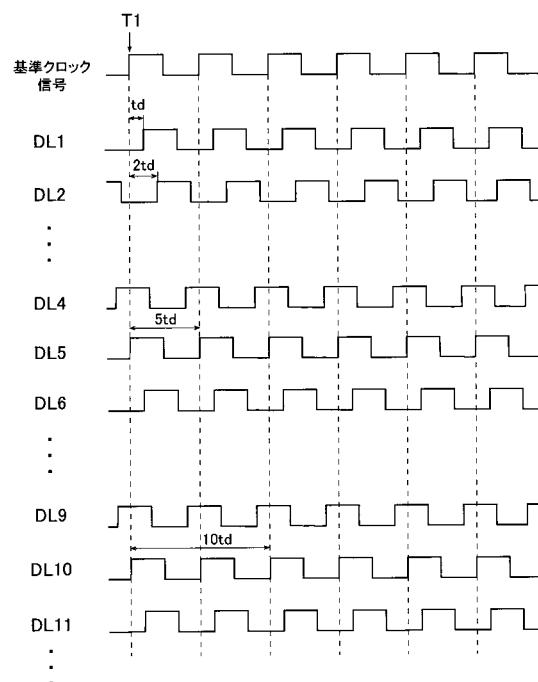

遅延チェーン部 1 は、図 2 に示すように、m 個のディレイセル D C 1 ~ m と、複数のインバータ IN V と、により構成され、基準クロック信号を遅延させて同期信号検出部 2 および遅延クロック信号セレクト部 5 に出力する。ここで、インバータ IN V は、基準クロック信号のデューティの崩れを抑制するために挿入される。

## 【0016】

ディレイセル D C 1 ~ m は、それぞれ入力された入力信号を所定遅延量（例えば、 $t_d [p_s \text{ オーダ}]$ ）だけ遅延させてそれぞれ出力する。つまり、図 2 に示すように、ディレイセル D C 1 ~ m を多段（直列）に接続し、各ディレイセルに対応する出力段を設けることで、所定遅延量の整数倍（1 ~ m 倍）で遅延させた入力信号を各出力段から出力する。これが m ビット幅の信号として、同期信号検出部 2 および遅延クロック信号セレクト部 5 に出力される。

30

## 【0017】

詳述すると、図 2 において、1 段目のディレイセル D C 1 は、基準クロック信号を所定遅延量（例えば、 $t_d [p_s \text{ オーダ}]$ ）だけ遅延させて出力する。そして、この出力された信号は、ディレイセル D C 1 に対応する出力段から遅延信号 D L 1 として同期信号検出部 2 および遅延クロック信号セレクト部 5 に出力されると共に、ディレイセル D C 2 へ出力される。また、2 段目のディレイセル D C 2 は、入力された遅延信号 D L 1 を所定遅延量（例えば、 $t_d [p_s \text{ オーダ}]$ ）だけ遅延させて出力する。そしてこの出力された信号は、ディレイセル D C 2 に対応する出力段から遅延信号 D L 2 として同期信号検出部 2 および遅延クロック信号セレクト部 5 に出力されると共に、ディレイセル D C 3 へ出力される。

40

## 【0018】

同様に、m 段目のディレイセル D C m は、入力された遅延信号 D L m - 1 を所定遅延量（例えば、 $t_d [p_s \text{ オーダ}]$ ）だけ遅延させて出力する。そして、この出力された信号は、ディレイセル D C m に対応する出力段から遅延信号 D L m として同期信号検出部 2 および遅延クロック信号セレクト部 5 に出力される。ここで遅延チェーン部 1 は、遅延手段と

50

しての機能を有している。また、遅延信号  $D_L 1 \sim m$  は、遅延基準クロック信号を意味する。

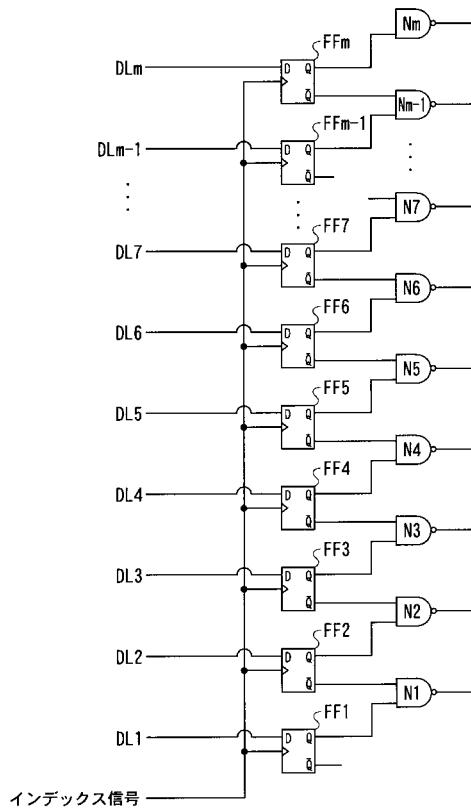

【0019】

同期信号検出部 2 は、図 3 に示すように、 $m$  個の D フリップフロップ  $FF 1 \sim m$ 、 $m$  個の NAND 回路  $N 1 \sim m$  および演算回路（図示省略）によって構成される。D フリップフロップ  $FF 1 \sim m$  は、インデックス信号が入力されたタイミングで遅延チェーン部 1 から入力された遅延信号  $D_L 1 \sim m$  の状態（“H”または“L”）を検出し、対応する NAND 回路  $N 1 \sim m$  に出力する。

【0020】

D フリップフロップ  $FF 1 \sim m$  には、各入力端子 D に遅延チェーン部 1 から出力された遅延信号  $D_L 1 \sim m$  が入力され、各クロック端子にインデックス信号が入力される。そして、インデックス信号に同期して各入力端子 D に入力された遅延信号  $D_L 1 \sim m$  の状態（“H”または“L”）を保持し、保持した値を出力端子 Q から出力すると共に、この保持した値を反転させた値を反転出力端子から出力する。

10

【0021】

そして NAND 回路  $N 1 \sim m$  は、前段（ここでは 1 ~  $m$  段）の D フリップフロップの出力端子 Q から出力される値と、次段（ここでは 2 ~  $m + 1$  段）の D フリップフロップの反転出力端子から出力される値と、をそれぞれ入力し、入力された 2 つの値の否定論理積を演算し、演算結果を演算回路（図示省略）に出力する。

20

【0022】

演算回路（図示省略）は、NAND 回路  $N 1 \sim m$  から出力された演算結果を入力し、基準クロック信号の 1 周期分の遅延を行うディレイセルの段数を算出する。また、算出したディレイセルの数を位相制御演算部 4 に出力する。

【0023】

ここで、同期信号検出部 2 は、第 1 入力手段および検出手段としての機能を有している。

【0024】

基準信号カウンタ部 3 は、インデックス信号を入力し、インデックス信号の入力回数を計数する。そして、計数した結果を位相制御演算部 4 へ出力する。ここで基準信号カウンタ部 3 は、計数手段としての機能を有している。

30

【0025】

位相制御演算部 4 には、同期信号検出部 2 から出力された基準クロック信号 1 周期分のディレイセルの段数と、基準信号カウンタ部 3 から出力されたインデックス信号の計数結果と、外部（例えば、複写機を構成する CPU 等）から指示される指示ずらし量と、が入力される。

【0026】

位相制御演算部 4 は、遅延チェーン部 1 の出力段番号を選択するセレクト信号を生成し、セレクト信号を遅延クロック信号セレクト部 5 に出力する。具体的には、例えば、基準クロック信号 1 周期分のディレイセルが X 段、指示ずらし量が Z、予め決められている分解能が  $1 / n$ 、カウント数が K である場合、ずらし段  $M = X \text{ 段} \times 1 / n \times K \times Z$  として計算する。そして、基準クロック信号と同期した遅延信号を出力するディレイセルの段番号にずらし段  $M$  を加算した値をセレクト信号として出力する。

40

【0027】

分解能  $1 / n$  とは、カウント数 K が加算される度に出力されるセレクト信号の値の刻み幅を示している。具体的には、分解能が  $1 / n$  の時、セレクト信号の値は基準クロック信号 1 周期分のディレイセルの段数に分解能  $1 / n$  を乗算した値を刻み幅として変化する。つまり、基準クロック信号 1 周期分のディレイセルの段数が 100 段であり、分解能が  $1 / 50$  の時、セレクト信号はカウント数 K が加算される度に、100 / 50 段ずつ、すなわち 2 段ずつ変化する。また、分解能  $1 / n$  は予め任意に設定されている固定値であってもいいし、可変値であってもよい。

【0028】

50

キャリー C とは、ずらし段 M の値が基準クロック信号 1 周期分のディレイセルの段数以上になる度に 1 加算されるデータである。キャリー C の値は、位相制御演算部 4 からキャリー信号として画像先端信号生成部 6 へ出力される。また、分解能  $1/n$  およびキャリー C は、位相制御演算部 4 が備える RAM 等で構成される記憶回路に記憶される。

【 0 0 2 9 】

ここで位相制御演算部 4 は、第 2 入力手段および位相演算手段としての機能を有している。また、指示ずらし量は位相制御信号を意味する。

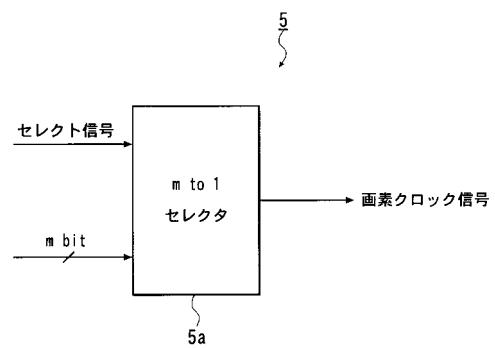

【 0 0 3 0 】

遅延クロック信号セレクト部 5 は、図 4 に示すようにセレクト 5 a を備えて構成される。このセレクト 5 a には、位相制御演算部 4 から出力されるセレクト信号と、遅延チェーン部 1 から出力される遅延信号  $D_L 1 \sim m$  と、が入力される。そしてセレクト 5 a は、セレクト信号に応じて、遅延信号  $D_L 1 \sim m$  の内、一の信号を選択し、選択した信号を画素クロック信号として画像先端信号生成部 6 と、外部とに出力する。

10

【 0 0 3 1 】

ここで遅延クロック信号セレクト部 5 は、信号選択手段としての機能を有している。

【 0 0 3 2 】

画像先端信号生成部 6 は、画素クロック信号に同期した画像先端信号を生成する。画像先端信号生成部 6 には、位相制御演算部 4 から出力されるキャリー信号と、遅延クロック信号セレクト部 5 から出力される画素クロック信号と、外部（例えば、複写機を構成する CPU 等）から指示される信号生成制御信号と、が入力される。信号生成制御信号とは、画素クロック信号に同期して画像先端信号を生成する際の生成のタイミングを示した信号である。

20

【 0 0 3 3 】

画像先端信号生成部 6 は、信号生成制御信号に従って画像先端信号を生成するタイミングを決定する。また、更にキャリー信号が 1 以上の場合には、信号生成制御信号の示した位置に対して、画素クロック信号の周期にキャリー信号の値を乗算した値の位相を変化させたタイミングで画像先端信号を出力する。

【 0 0 3 4 】

ここで、画像先端信号生成部 6 は、信号生成手段としての機能を有している。また、キャリー信号は指示信号を意味する。

30

【 0 0 3 5 】

次に図 5 および 6 を参照して、本実施の形態における動作を説明する。図 5 は、遅延チェーン部 1 に入力される基準クロック信号と、遅延チェーン部 1 から出力される遅延信号  $D_L 1 \sim 11$  と、のタイミングチャートの一例を示した図である。図 5 に示すように、遅延信号  $D_L 1$  は、基準クロック信号をディレイセル  $D_C 1$  によって所定遅延量（例えば、 $t_d [ps\ \text{オーダ}]$ ）だけ遅延し、遅延信号  $D_L 2$  は、基準クロック信号をディレイセル  $D_C 1$  および  $2$  によって所定遅延量の 2 倍（つまり、 $2 t_d [ps\ \text{オーダ}]$ ）だけ遅延し、遅延信号  $D_L 10$  は、基準クロック信号をディレイセル  $D_C 1 \sim 10$  によって所定遅延量の 10 倍（つまり、 $10 t_d [ps\ \text{オーダ}]$ ）だけ遅延する。

40

【 0 0 3 6 】

また、ここで、遅延信号  $D_L 5$  および  $10$  は、基準クロック信号と同期している。つまり、遅延信号  $D_L 5$  および  $10$  の遅延量である時間  $5 t_d$  および  $10 t_d$  は、基準クロック信号の周期の整数倍であることを意味する。

【 0 0 3 7 】

そして遅延チェーン部 1 は、遅延信号  $D_L 1 \sim m$  を同期信号検出部 2 および遅延クロック信号セレクト部 5 に出力する。同期信号検出部 2 は、インデックス信号が入力されたタイミングで遅延信号  $D_L 1 \sim m$  の状態を検出し、基準クロック信号の 1 周期分にあたるディレイセルの段数を算出する。

【 0 0 3 8 】

例えば、図 5 に示すように、インデックス信号が基準クロック信号の立ち上がりエッジに

50

同期したタイミング(図5に示す時間T1)で同期信号検出部2に入力されたとする。この時間T1において、遅延信号DL1～3、6、11は“L”になっており、遅延信号DL4、5、9、10は“H”になっている。このように、インデックス信号が入力された時間T1の遅延信号DL1～mの状態をDフリップフロップFF1～mが保持して、NAND回路N1～mに出力する。

【0039】

そして、NAND回路N1～mは、DフリップフロップFF1～mから出力された状態に基づいて否定論理積を演算し、演算結果を演算回路(図示省略)に出力する。そして演算回路により、インデックス信号と同期する信号と同期しない信号とが識別される。したがって、図5に示す遅延信号DL5および10(つまり、インデックス信号と同期する信号)に対応するNAND回路N5および10からは“L”が出力され、NAND回路N5および10以外のNAND回路からは“H”が出力される。

10

【0040】

そして演算回路は、NAND回路N1～mから出力された値に基づいて、基準クロック信号の1周期分の遅延を行うディレイセルの段数(即ち、NAND回路N10の“10”-NAND回路N5の“5”=5段)を演算して、位相制御演算部4に出力する。

【0041】

基準信号カウンタ部3は、1つの画像データに対して入力されたインデックス信号の入力回数を計数し、計数した結果を位相制御演算部4へ出力する。

20

【0042】

位相制御演算部4は、同期信号検出部2から出力された基準クロック信号1周期分のディレイセルの段数と、基準信号カウンタ部3から出力されたインデックス信号のカウント数と、外部(例えば、複写機を構成するCPU等)から指示ずらし量と、を入力する。入力した値と、分解能1/nおよびキャリーキーと、を用いて演算することにより遅延チェーン部1の出力段番号を選択するセレクト信号を生成し、遅延クロック信号セレクト部5へ出力する。

【0043】

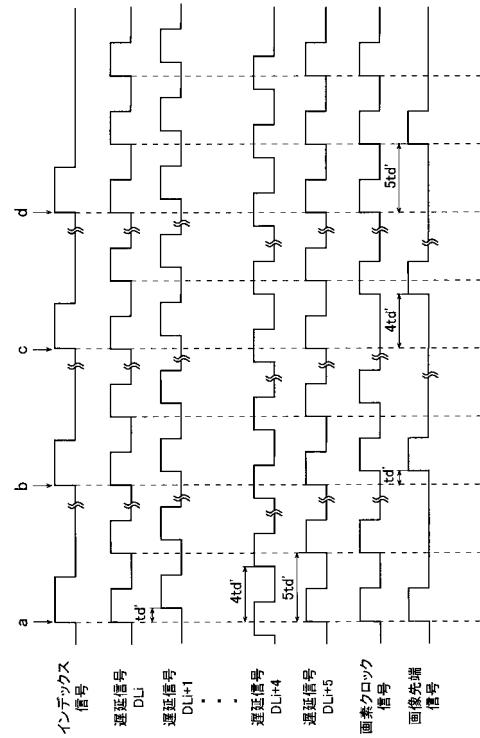

図6は、信号制御回路10に外部から入力されるインデックス信号と、遅延クロック信号セレクト部5に入力される遅延信号と、信号制御回路10から出力される画素クロック信号および画像先端信号と、のタイミングチャートの一例を示した図である。

30

【0044】

図6において、遅延信号DLi, i+1, …, i+4, i+5は遅延クロック信号セレクト部5に入力される遅延信号DL1～mの一部であり、画素クロック信号は遅延クロック信号セレクト部5から出力された信号である。画像先端信号は、画像先端信号生成部6から出力された信号である。

【0045】

ここで、説明のため、遅延チェーン部1のディレイセル1段による遅延量はtdとし、基準クロック信号の1周期分のディレイセルが5段である場合を一例として図示している。更に分解能1/5、指示ずらし量Z=iとし、カウント数Kおよびキャリーキーは初期値をゼロとして説明する。

40

【0046】

図6において、タイミングaで1回目のインデックス信号が入力されることにより、遅延クロック信号セレクト部5はセレクト信号によって遅延信号DLiを選択し、該信号を画素クロック信号として出力する。そして、画像先端信号生成部6は画素クロック信号に同期して画像先端信号を出力する。

【0047】

続いて、タイミングbで2回目のインデックス信号が入力されると、遅延クロック信号セレクト部5はセレクト信号によって遅延信号DLi+1を選択し、該信号を画素クロック信号として出力する。そして、画像先端信号生成部6は画素クロック信号に同期して画像先端信号を出力する。この時、画像先端信号はインデックス信号の立ち上がりエッジに対

50

して、時間  $t d'$  ほど遅れて出力されることになる。

【0048】

次に、タイミング  $c$  で 5 回目のインデックス信号が入力されると、遅延クロック信号セレクト部 5 はセレクト信号によって遅延信号  $D L_i + 4$  を選択し、該信号を画素クロック信号として出力する。そして、画像先端信号生成部 6 は画素クロック信号に同期して画像先端信号を生成する。この時、画像先端信号はインデックス信号の立ち上がりエッジに対して、時間  $4 t d'$  ほど遅れて出力されることになる。

【0049】

続いて、タイミング  $d$  で 6 回目のインデックス信号が入力されると、位相制御演算部 4 において演算されるずらし段  $M$  が、基準クロック信号 1 周期分のディレイセルの段数（図 6 においては“5”）を超えるため、キャリー  $C$  を“1”としてずらし段  $M$  を演算し、セレクト信号を出力する。したがって、遅延クロック信号セレクト部 5 はセレクト信号によって遅延信号  $D L_i$  を選択し、該信号を画素クロック信号として出力する。そして、画像先端信号生成部 6 は画素クロック信号に対して 1 周期遅れたタイミングで画像先端信号を生成する。この時、画像先端信号はインデックス信号の立ち上がりエッジに対して、時間  $5 t d'$  ほど遅れて出力されることになる。

10

【0050】

尚、画像先端信号生成部 6 が画像先端信号を出力する画素クロック信号に同期したタイミングは、外部（例えば、複写機を構成する CPU 等）から入力される信号生成制御信号によって任意に設定可能である。また、インデックス信号が外部から入力される度に遅延クロック信号セレクト部 5 によって切り替えられた画素クロック信号が出力されるが、安定した画素クロック信号を用いるために、画像先端信号は遅延クロック信号セレクト部 5 を出力して所定周期経過後の画素クロック信号に同期して生成される。

20

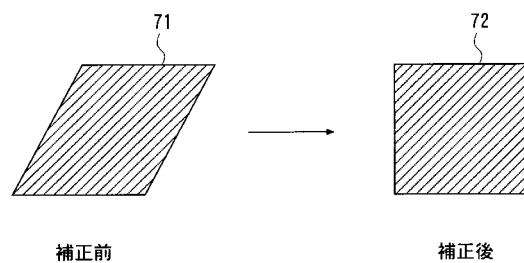

【0051】

このように、信号制御回路 10 は、基準クロック信号に対して位相をずらした信号を画素クロック信号として出力し、更に該画素クロック信号に同期して画像先端信号を出力することにより、画像の各行の先頭の書き出し位置を制御することができる。即ち、図 7 に示すように、複写機等の画像形成装置によって補正前は傾いて出力されていた画像 7 1 を、信号制御回路 10 を用いて画像の各行の先頭の書き出し位置を示す画像先端信号を制御することにより、画像 7 2 のように傾きを補正してまっすぐに出力することができる。

30

【0052】

更に、画像先端信号生成部 6 に入力される信号生成制御信号によって、画像先端信号を出力するタイミングは任意に設定可能であるから、画像の各行の先頭の書き出し位置も任意に制御することができる。つまり、画像の各行の先端の書き出し位置のずらす量を任意に設定することができる。

【0053】

以上のように、本実施の形態の信号制御回路 10 によれば、遅延チェーン部 1 で基準クロック信号から所定遅延量を遅延させた遅延信号を  $m$  ビット出力し、同期信号検出部 2 で基準クロック信号の 1 周期分の遅延を行うために必要となるディレイセルの段数を検出する。そして位相制御演算部 4 は、同期信号検出部 2 によって算出されたディレイセルの段数と、基準信号カウンタ部 3 から入力されるインデックス信号のカウンタ数と、外部（例えば、複写機を構成する CPU 等）から入力される指示ずらし量  $Z$  と、分解能  $1 / n$  と、に基づいて、ずらし段  $M$  を演算する。更にずらし段  $M$  に基づいてセレクト信号を生成し、セレクト信号を遅延クロック信号セレクト部 5 に出力する。

40

【0054】

遅延クロック信号セレクト部 5 は、入力されたセレクト信号に応じて、遅延チェーン部 1 が出力する遅延信号の内、一の信号を選択し、選択した信号を画素クロック信号として外部に出力すると共に、画像先端信号生成部 6 に出力する。

【0055】

画像先端信号生成部 6 は、外部（例えば、複写機を構成する CPU 等）から入力される信

50

号生成制御信号に応じて、入力された画素クロック信号に同期した信号を生成し、画像先端信号として外部に出力する。

【0056】

したがって、信号生成回路10は、基準クロック信号の1周期/nの時間を遅延させた遅延信号を生成し、外部から入力されたインデックス信号に対して任意のずらし量を遅延させた遅延信号を画素クロック信号として出力する。これにより、画素クロック信号のタイミングを高精度で制御できるため、画像の傾き(歪み)も高精度で補正することができる。

【0057】

更に、画像先端信号は画素クロック信号に同期したタイミングで生成するが、外部(例えば、複写機を構成するCPU等)から入力される信号生成制御信号によって画像先端信号を生成するタイミングを制御することができる。このため、信号生成制御信号を任意に設定することにより、画像の各行の先頭の書き出し位置を任意に制御できる。

【0058】

分解能1/nおよび信号生成制御信号の値は、複写機等の画像形成装置の温度変化による書き込みユニットおよび読み取りユニットのレンズ特性の変化、装置組み立て時の製造誤差、各製品の製造バラツキ等にしたがって予め設定され、画像形成装置に含まれる記憶回路等に記憶されて出荷される。そして複写機等で画像を形成する際に、信号制御回路10によって画像の各行の先端の書き出し位置が制御されることにより、画像の傾き(歪み)が補正されて出力される。

【0059】

また、集積回路(デジタル回路)内に信号制御回路10を構成すれば、信号制御回路10は高精度の遅延を実現でき、信号制御回路10を安価に提供できる。

【0060】

なお、本発明は、上記実施の形態の内容に限定されるものではなく、本発明の趣旨を逸脱しない範囲で適宜変更可能であり、例えば、画像のより複雑な補正を実現するために、位相制御演算部4におけるずらし段Mの演算式として、“ずらし段M = X段 × 1/n × K × Z”を一例として挙げて説明したが、これに限定されるものではなく、二次関数等を含む演算式としてもよい。これにより、画像に対してより複雑な補正が可能となる。また、分解能1/nは、外部(例えば、複写機を構成するCPU等)から入力される値であってもよい。これにより、分解能1/nを小さな値に設定した場合、画像を更に細かく補正することが可能となる。更に、本実施の形態において、ずらし段Mは1インデックス信号毎に加算されるものとして説明したが、複数のインデックス信号毎にずらし段Mを加算してもよい。また、インデックス信号によってずらし段Mの値が異なってもよく、ずらし段Mは位相制御演算部6においてインデックス信号の入力毎に任意に設定することが可能である。

【0061】

【発明の効果】

請求項1記載の発明によれば、例えば、パルス信号やステップ信号等の所定信号と同期する遅延基準クロック信号に基づいて基準クロック信号の1周期分に係る遅延素子の段数を検出し、この段数、計数量、位相制御信号及び遅延手段を選択するための選択信号の刻み幅を示す分解能を積載した積算情報を演算する。そして、この積算情報に基づいて、選択信号を生成し、当該生成された選択信号に基づいて、遅延基準クロック信号の中から逐一的に選択した信号を外部出力する。これにより、遅延基準クロック信号のタイミングを基準クロック信号の1周期以下の時間で制御でき、高精度な制御を実現できる。

【0063】

請求項2記載の発明によれば、画像先端信号に基づいたタイミングで、信号選択手段から出力された信号に同期した信号を生成する。これにより、画像の各行の先端の書き出し位置を高精度で制御できる。

【0065】

10

20

30

40

50

請求項 3 記載の発明によれば、画像先端信号生成手段は、指示信号に基づいて画像先端信号を生成する。これにより、画像の傾き等を補正して出力することができる。

### 【図面の簡単な説明】

【図1】信号制御回路の構成を示すブロック図。

【図2】遅延チェーン部の回路構成を示す図。

【図3】同期信号検出部が備える検出回路の回路構成を示す図。

【図4】遅延クロック信号ヤレクト部が備えるヤレクトを示す図。

【図5】基準クロック信号と、遅延チェーン部から出力される遅延信号と、を示すタイミングチャート。

【図6】インデックス信号と、遅延信号と、画素クロック信号と、画像先端信号と、を示すタイミングチャート

【図7】信号制御回路10による補正前後の画像を示す図。

## 【符号の説明】

- 1 遅延 チェーン 部

- 2 同期 信号 検出 部

- 3 基準 信号 カウンタ 部

- 4 位相 制御 演算 部

- 5 遅延 クロック 信号 セレクト 部

- 6 画像 先端 信号 生成 部

( 1 )

〔 図 2 〕

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

審査官 藏田 敦之

(56)参考文献 特開2001-292133(JP,A)

特開2000-190558(JP,A)

特開平04-242712(JP,A)

(58)調査した分野(Int.Cl., DB名)

B41J 2/44

G02B 26/10

H04N 1/04 - 1/203