## WORLD INTELLECTUAL PROPERTY ORGANIZATION International Bureau

## INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(51) International Patent Classification <sup>6</sup>:

G05B 19/045

(11) International Publication Number:

WO 96/26470

(43) International Publication Date:

29 August 1996 (29.08.96)

(21) International Application Number:

PCT/US96/02781

A1

(22) International Filing Date:

23 February 1996 (23.02.96)

(30) Priority Data:

08/393,935

23 February 1995 (23.02.95)

US

(71) Applicant: DATALOGIC, INC. [US/US]; 104 Whispering Pines Drive, Scotts Valley, CA 95066 (US).

(72) Inventors: MUDRYK, John, S.; 206 Kilbreck Drive, Cary, NC 27511 (US). YAUCH, Steven, S.; P.O. Box 99010, Raleigh, NC 27624 (US). LYMAN, Richard, R.; 15995 Rose Avenue, Los Gatos, CA 95030 (US).

(74) Agent: KING, Patrick, T.; Law Offices of Patrick T. King, 36 Seascape Village, Aptos, CA 95003 (US).

(81) Designated States: European patent (AT, BE, CH, DE, DK, ES, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE).

#### Published

With international search report.

Before the expiration of the time limit for amending the claims and to be republished in the event of the receipt of amendments.

#### (54) Title: CONFIGURABLE I/O

#### (57) Abstract

A configurable I/O arrangement (100) for a controller has a number of internal and external input/output terminals, each of which are field selected as either an input or an output terminal. Logic functions (106) of the controller are configured for a number of output terminals using up to 32 internal logical states and the states of 32 external physical I/O points. The update timing for each logic circuit is selectable to be synchronized in several different ways: synchronous with an internal event within the controller, synchronous with an event external to the controller, and asynchronous. The I/O arrangement includes a combination of a synchronous latchable input state array (102) user configurable means (112) for logically combining the output signals of the reading circuits, and means for actuating external devices as a function of the logical combinations of the output signals of the reading circuits.

#### FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

| AM | Armenia                  | GB | United Kingdom               | MW | Malawi                   |

|----|--------------------------|----|------------------------------|----|--------------------------|

| ΑT | Austria                  | GE | Georgia                      | MX | Mexico                   |

| AU | Australia                | GN | Guinea                       | NE | Niger                    |

| BB | Barbados                 | GR | Greece                       | NL | Netherlands              |

| BE | Belgium                  | HU | Hungary                      | NO | Norway                   |

| BF | Burkina Faso             | IE | Ireland                      | NZ | New Zealand              |

| BG | Bulgaria                 | IT | Italy                        | PL | Poland                   |

| BJ | Benin                    | JP | Japan                        | PT | Portugal                 |

| BR | Brazil                   | KE | Kenya                        | RO | Romania                  |

| BY | Belarus                  | KG | Kyrgystan                    | RU | Russian Federation       |

| CA | Canada                   | KP | Democratic People's Republic | SD | Sudan                    |

| CF | Central African Republic |    | of Korea                     | SE | Sweden                   |

| CG | Congo                    | KR | Republic of Korea            | SG | Singapore                |

| CH | Switzerland              | KZ | Kazakhstan                   | SI | Slovenia                 |

| CI | Côte d'Ivoire            | LI | Liechtenstein                | SK | Slovakia                 |

| CM | Cameroon                 | LK | Sri Lanka                    | SN | Senegal                  |

| CN | China                    | LR | Liberia                      | SZ | Swaziland                |

| CS | Czechoslovakia           | LT | Lithuania                    | TD | Chad                     |

| CZ | Czech Republic           | LU | Luxembourg                   | TG | Togo                     |

| DE | Germany                  | LV | Latvia                       | TJ | Tajikistan               |

| DK | Denmark                  | MC | Мопасо                       | TT | Trinidad and Tobago      |

| EE | Estonia                  | MD | Republic of Moldova          | UA | Ukraine                  |

| ES | Spain                    | MG | Madagascar                   | UG | Uganda                   |

| FI | Finland                  | ML | Mali                         | US | United States of America |

| FR | France                   | MN | Mongolia                     | UZ | Uzbekistan               |

| GA | Gabon                    | MR | Mauritania                   | VN | Viet Nam                 |

1

### CONFIGURABLE I/O

#### 5 TECHNICAL FIELD

The present invention relates generally to user-configurable logic configurations, and more particularly, controllers used with bar code decoders and verifiers.

10

15

30

## BACKGROUND OF THE INVENTION

A controller is an electronic device which provides control functions for an external device in response to input signals. A controller provides one or more output control or command signals to the external device in response to one or more input signals. Controllers are used, for example, in industrial packaging applications in the pharmaceutical, cosmetic, beverage, and other industries.

20 Programmed Logic Controllers (PLCs) use programmed logic devices to implement a controller function. The logic functions of a PLC are executed at a fixed scan rate, which is asynchronous to any input signal. Logic functions implemented in the PLC internal program incur a latency equal to the scan period. This slows down the response time and results in the output signals of the PLC not being synchronized with external events. PLCs operate asynchronously so that their output signals are not synchronized with either internal or external events.

Alternatively, control functions are implemented with "hardware" logic. Hardware logic is programmed, for example, by physically wiring devices together, blowing fuses, or programming non-volatile memory devices. Hardware logic is not easily or quickly reconfigured or reprogrammed.

Consequently, a need exists for a controller which is easily reprogrammed and which also provides synchronized output signals.

2

#### SUMMARY OF THE INVENTION

It is, therefore, an object of the present invention to provide a controller which has a configurable I/O arrangement and which provides flexibility in the utilization of a number of external physical input/output points, or terminals. Each individual I/O point, or output terminal of the controller, can be field selected as either an input or an output terminal. In one embodiment of the invention, the logic functions of the controller are configured for each output terminal using up to 32 internal logical states and the states of 32 external physical I/O points.

The update timing for each logic circuit in a controller with a configurable I/O arrangement according to the invention is selectable to be synchronized in several different ways. One way is to synchronize with an internal event which is provided to an input state array within the controller. Another way is to synchronize with an event which is external to the controller. Alternatively, asynchronous update timing can be provided, if desired.

20

25

30

35

5

10

15

The invention includes a combination of reading circuits, user configurable means for logically combining the output signals of the reading circuits, signal conditioning means for combining the outputs of reading signals and intermediate signals resulting from other signal conditioning means, an update trigger means for supplying update trigger signals to the configurable means and signal conditioning means, and means for actuating external devices as a function of the logical combinations of the output signals of the reading circuits. A presence detector, which detects, for example, the presence of a bar code, can be used to trigger the system.

A controller having a configurable I/O system according to the invention includes means for initializing the system; means for detecting an input event; means for placing the input event in a circular event queue; functional dispatch means for removing the input event from the circular event queue; and means for executing a

predetermined function in response to the input event. The functional dispatch means includes means for mapping the event through a table to a combinatorial logic calculation routine and includes means for initiating execution of a combinatorial logic routine.

5

20

25

30

Inputs to the state array are looked for at the end of a gate period provided by a trigger event.

The means for executing a predetermined function in response to the event includes: means for providing state variables representing input values; and means for operating on the state variables to produce output states. The predetermined function is a software simulation of a programmable array. The programmable array is an array of AND/OR gates by means of which outputs can be specified as logical functions of the inputs. The state variable inputs consist of external signals, internally generated states, counter states, shift register states, and latch states.

In specific embodiments of the invention, the external signals include a signal which is generated from an "item" presence sensor, which detects, for example, the presence of a bar code. The presence sensor provides an "event gate" time during which one of the main functions of the controller can be initiated. The signal which is generated from the presence sensor includes, for example, a signal generated when an item is in front of an infrared light beam.

According to another aspect of the invention, a configurable I/O system includes an input state array; a trigger function; logic functions; and an output signal conditioner. The trigger function is the means for synchronizing the logic functions with other external events or internal events within a control system. In contrast, a PLC does not provide for synchronization with external or internal events.

According to another aspect of the invention a configurable I/O system includes an input state array for receiving a plurality of input signals and having a plurality of elements respectively corresponding to

one of said input signals A latch array has elements for receiving and storing the states of the elements of the input state array. Means are provided for selecting a clock signal provided to the latch array.

An AND logic sequence includes an AND inverter array having elements for receiving and selectively inverting the elements of the latch means; a multi-input AND array; an AND input selection array for directing a corresponding bit from the latch array into one of the inputs of the multi-input AND array; and an AND Output Inverter. An OR logic sequence includes an OR inverter array having elements for receiving and selectively inverting the elements of the latch means; a multi-input OR array; an OR input selection array for directing a corresponding bit from the latch array into one of the inputs of the multi-input OR array; and an OR Output Inverter. An OR gate combines the outputs of the AND Output Inverter and the OR Output Inverter.

According to another aspect of the invention, a configurable AND logic sequence for a configurable I/O system includes a first Exclusive OR array for logically combining each respective element of a state array with the respective element of an AND Invert array. A first AND array is provided for logically combining each respective elements of the first Exclusive OR array with each respective elements of an And enable array A first OR array logically combines the respective elements of the AND array into a single element. A first inverting Exclusive-OR invert Array combines the single element of the OR array with an invert command signal to provide an inverted or non-inverted AND output signal.

A configurable OR logic sequence for a configurable I/O system includes a second Exclusive OR array logically combining respective elements of the state array and an OR Invert array. A Second AND array logically combines respective elements of the second Exclusive OR array with respective elements of an OR enable array A second OR array logically combines the respective elements of the second AND array into a single element. A second inverting Exclusive-OR invert Array combines the single element of the OR array with an invert

5

command signal to provide an inverted or non-inverted OR output signal.

An output OR Array logically combines the inverted or non-inverted AND output signal with the inverted or non-inverted OR output signal. The configurable I/O system further includes an output signal conditioner which alternatively provides direct channels to output terminals, shift registers, a pulse circuit, a latch circuit, and an internal counter.

10

15

20

25

5

In one specific embodiment of a configurable I/O system, the AND logic sequence and the OR logic sequences are the same. The difference between the AND sequence and the OR sequence is only in the sense of the INV/INV control to the inverting XOR gate and the sense of the control bits in the AND and OR Invert Arrays.

A method of providing a configurable I/O system, comprising the steps of: initializing the system; detecting an input event; placing the input event in a circular event queue; removing the input event from the circular event queue using a functional dispatch means; and executing a predetermined function in response to the input event. The method includes the step of mapping the event through a table to a combinatorial logic calculation routine and including the step of initiating execution of the combinatorial logic routine. The step of executing a predetermined function in response to the event includes the steps of providing state variables representing input values and operating on the state variables to produce output states. The step of executing a predetermined function in response to the input event includes the step of using a software simulation of a programmable array. The step of using a software simulation of a programmable array includes using a programmable array which is an array of AND/OR gates by means of which outputs can be specified as logical functions of the inputs. The input state variables consist of external signals, internally generated signals, counter states, shift register states, and latch states.

30

#### BRIEF DESCRIPTION OF THE DRAWINGS

15

25

The accompanying drawings which are incorporated in and form a part of this specification, illustrate embodiments of the invention and, together with the description, serve to explain the principles of the invention:

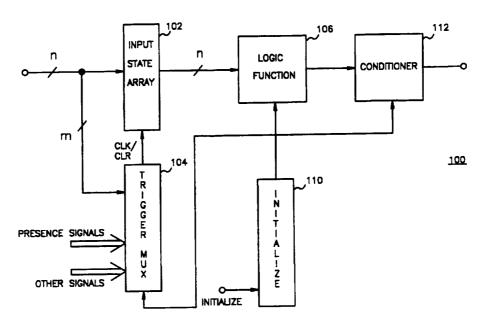

- FIG. 1 is a block diagram of a generalized configurable I/O system which includes an input state array, a logic function, a trigger function, and an output signal conditioner.

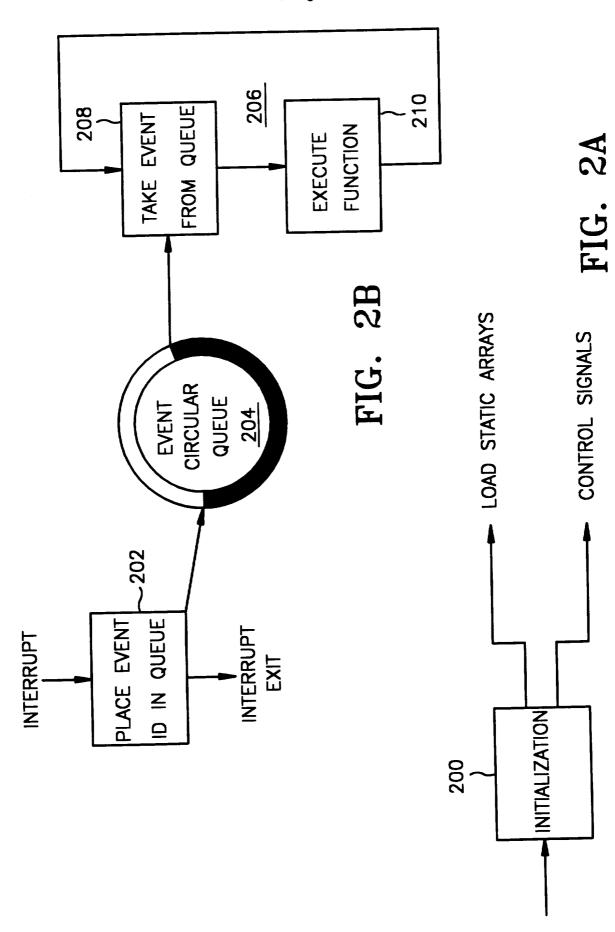

- FIG. 2A is a functional block diagram illustrating initialization of a configurable I/O system according to the invention.

- FIG. 2B is a functional block diagram illustrating a technique for providing a trigger function for a configurable I/O system according to the invention.

- 20 FIG. 3A is a flow chart illustrating detection of a trigger event and add the trigger event to a circular event queue.

- FIG. 3B is a flow chart illustrating the taking of a trigger event from the circular event queue and executing logical functions.

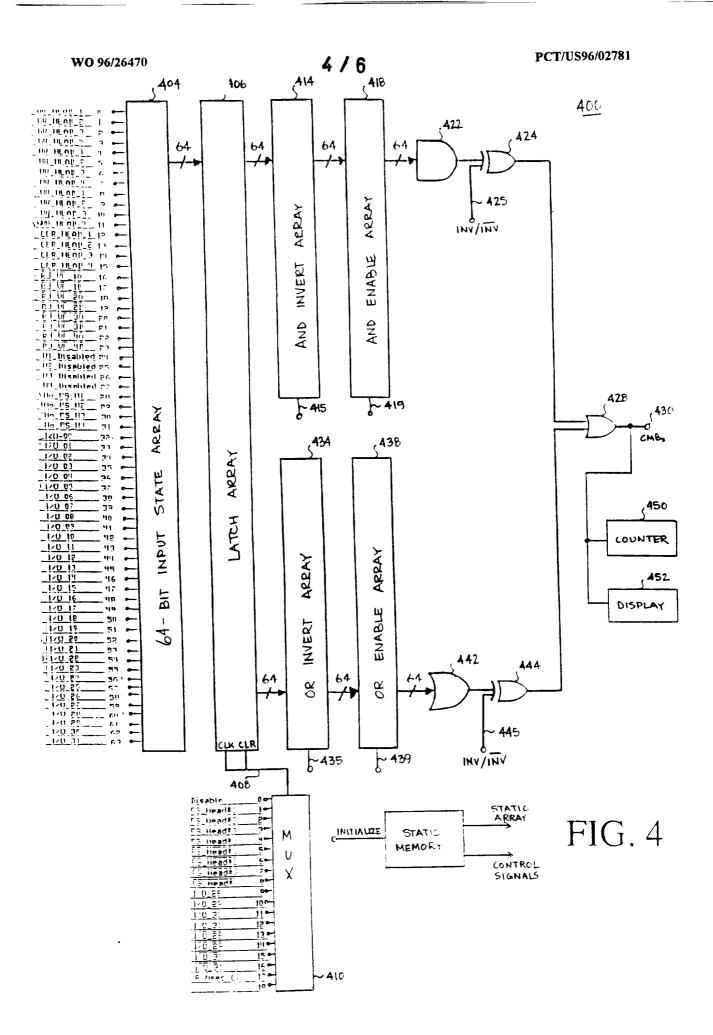

- FIG. 4 is a block diagram of an input state array and a logic function.

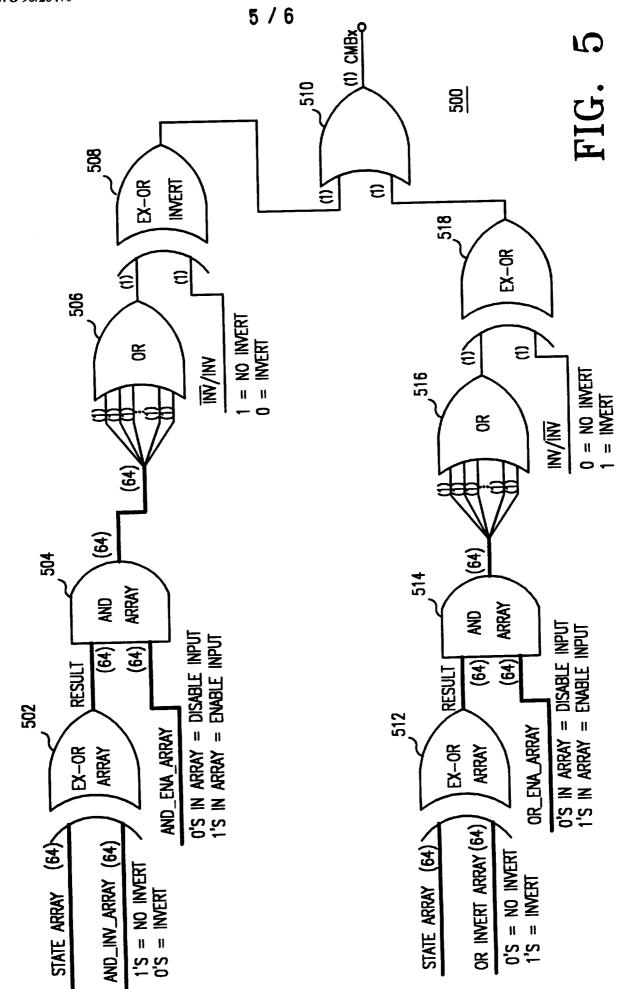

- FIG. 5 is a diagram illustrating AND and OR combinatorial functions of a configurable I/O system according to the invention.

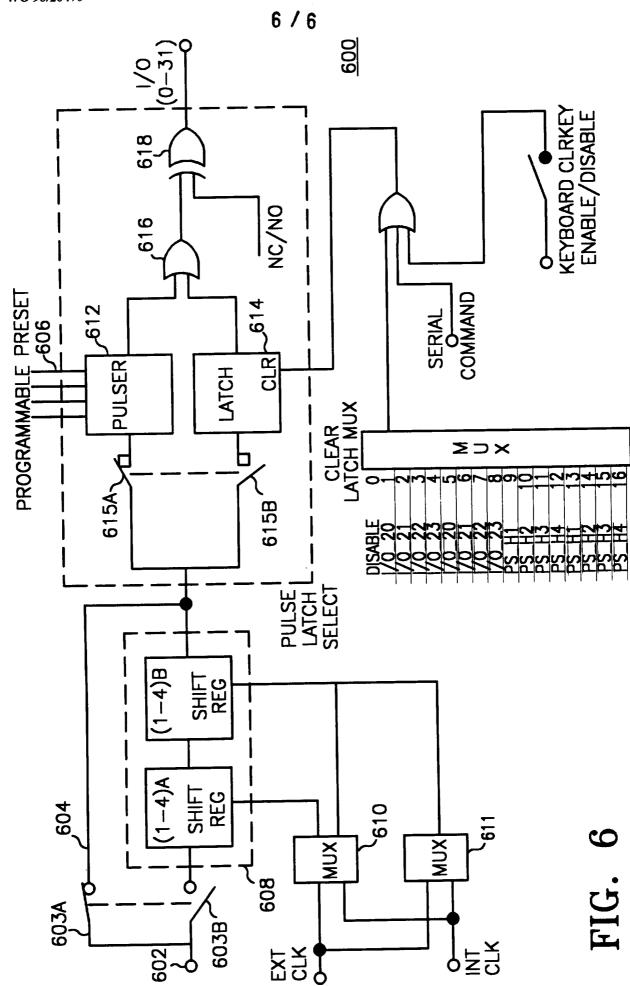

- FIG. 6 is a block diagram of an output conditioner circuit for a configurable I/O according to the invention.

10

15

20

25

30

35

## DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

Reference will now be made in detail to the preferred embodiments of the invention, examples of which are illustrated in the accompanying drawings. While the invention will be described in conjunction with the preferred embodiments, it will be understood that they are not intended to limit the invention to these embodiments. On the contrary, the invention is intended to cover alternatives, modifications and equivalents, which may be included within the spirit and scope of the invention as defined by the appended claims.

FIG. 1 shows a block diagram showing the principle elements of a configurable I/O system 100, according to the invention. The configurable I/O system 100 includes an input state array 102 for receiving n input state variables.

A trigger function multiplexer 104 provides clock and clear signals to an output latch array, which is part of the input state array 102. The trigger function multiplexer 104 provides one of a number of preselected signals to trigger the latch array of the input state array 102. The trigger function multiplexer 104 receives inputs from a number of sources, including: m input state variables, presence signals indicating the presence of an item, and other signals such as periodic clock pulses and a disable signal. In this manner the input state variables are latched and provided at a precise time to a configurable logic function 106 for execution of the logic function 106 in synchronization with the selected input of the trigger function multiplexer 104.

The output of the logic function is then provided to an output signal conditioner 112.

Initialization of the logic function, the signal conditioner 112, and the trigger multiplexer 104 is provided by an initialization function block 110. The initialization function 110 allows a user to select, for example, which of the n input state variables are to be operated upon by the logic

8

function 106.

20

25

30

35

The initialization function 110 also allows a user to select the configuration of the logic function 106, for example, as a simulated combinatorial AND/OR logic function. The initialization function permits inversion and enablement of preselected input state variables as well as of various intermediate and final state variables for the logic function.

The initialization function 110 further allows a user to select further signal conditioning functions for the output of the logic function 106. Further signal conditioning may alternatively include, for example, connecting output signals to a counter, an output terminal, shift registers, a pulse circuit, a latch circuit, or another internal counter.

FIG. 2A shows an initialization module 200 which initializes the system. The initialization module 200 includes a static memory. The initialization module 200 provides outputs for static logic arrays and provides control signals or states to logic elements. The initialization module 200 is activated by an initialization command to load the appropriate arrays and to initiate operation of the system. The initiation module is a program block which sets up the connections between the various system modules. The connections are kept in a list of functional block addresses to call upon event triggers.

FIG. 2B is a functional block diagram illustrating the program steps which provide a trigger to initiate execution of a function for a configurable I/O system according to the invention. An event detector module 202 detects an interrupt event caused by a change in an input signal. The event detector module 202 detects these events which are be used as triggers and also detects timer interrupts. Upon detecting an event, that event is placed into a circular event queue 204. The event queue 204 isolates the event detection interrupts from slower event processing operations. This provides a system with a high event burst rate rating.

10

15

20

25

30

35

A functional dispatcher module 206 initiates execution of a functional logic block by having a module 208 take an event from the event queue 204 at an appropriate time, as determined by the length of delay provided by the event queue 204. An execute function module 210 simulates a configurable logic function for the configurable I/O system.

The system is optimized to operate in real-time and to satisfy two important real-time constraints: namely, to maximize the rate of acquisition of the changes in the inputs and to maximize the average processing rate of the elements of the configurable system, which includes combinatorial logic and signal conditioners, such as shift registers, latches and counters.

The function dispatcher modules 206 removes events from the event queue 204 and executes an appropriate functional block in module 210. For example, it may be desired that a certain input variable change to trigger a particular configurable I/O combinatorial logic calculation required to produce a certain output control bit. When the input variable changes, an event identifier is placed in the event queue 204. The function dispatcher module 206 removes the event identifier, maps the event through a table to the combinatorial logic calculation routine, and then initiates execution of the combinatorial logic routine in the execute module 210. The function dispatcher 206 continues to take events out of the queue 204 and to execute functional blocks until the event queue 204 is empty.

After being called by the functional dispatcher, the function triggered by an I/O event is executed. The execution functions provided by the execute module 210 take all of the input state variables, operate upon them, and produce output states. An example of a particular execute function is an AND/OR logic function shown herein below in connection with FIG. 5.

FIG. 3A is a flow chart illustrating the steps to detect a trigger event and to add the trigger event to the circular event queue 204. An element 302 detects an appropriate trigger source and an element 304

adds an event to the event queue 204.

FIG. 3B is a flow chart illustrating the steps to take a trigger event from the circular event queue and execute functions. An element 310 triggers the event logged into the queue 204. The element 312 determines whether additional functions are attached to the trigger event in the queue 204 and if so they are executed as indicated by the element 314. Elements 312 and 314 continue to function until all functions attached to the received trigger event are completed.

FIG. 4 is a functional block diagram which illustrates an input state array, a trigger function, and a logic function for a configurable I/O system module 400, according to the invention. A complete configurable I/O system contains, for example, 32 such modules. The I/O system module 400 combines the input state module 102, the trigger module 104, and the logic function module 106 of FIG. 1. While the invention is described in terms of various arrays and logic elements, one preferred embodiment of the invention is implemented using various software arrays, logic functions, and interconnecting paths as provided in a conventional programmed personal computer, work station, or similar system.

Each I/O system module includes a 64-bit input state array 404 having 64 input signals (0-63). The 64-bit input state array 404 receives signals from various sources such as bar code decoders. The 64 outputs of the 64-bit input state array are connected to the input terminals of a 64-bit input latch array 406. The input latch array 406 receives clock signals on a signal line 408 from the output terminal of a multiplexer 410. The 64 bit input array does not receive interrupts or note transitions per se. The 64 bit input array always contains the latest/most up-to-date state of all of the inputs. The MUX 410 detects transitions and routes them to the appropriate Latch Arrays. Transition of the state array are subsequently processed by combinatorial logic. The outputs of the input latch 406 are provided to two subsequent parallel combinatorial logic paths: one path provides an AND function and the other path provides an OR function.

10

15

20

25

30

35

For the AND path, the output of the latch array 406 are provided as inputs to a 64-bit AND invert array 414. Configuration control states AND\_INV are received by the 64-bit AND invert array on a 64-bit bus 415. The outputs of the AND invert array 414 are connected to respective inputs of an AND enable array 418. Configuration control signals AND\_EN signals are received by the 64-bit AND invert array 418 on a 64bit bus 419. The outputs of the AND enable array 418 are connected to the respective inputs of a 64-input AND gate array 422. The output of the 64input AND gate array 422 is connected to one input terminal of an Exclusive-OR gate 424 which functions as a master inverting gate for the AND function. An INV/\*INV signal is provided on a line 425 to the other input terminal of the Exclusive-OR gate 424. The output terminal of the exclusive-OR gate 424 is connected to one input terminal of an OR gate 428. The output terminal of the OR gate provides a CMBx signal, 430 where x corresponds to one of the 32 output terminals for a 32-bit system.

For the OR path, the output terminals of the input latch array 406 are also connected to respective inputs of a 64-bit OR invert array 434. Configuration control signals OR\_INV signals are received by the 64-bit OR invert array on a 64-bit bus 435. The output terminals of the OR invert array are connected to respective inputs of an OR enable array 438. Configuration control signals OR\_EN signals are received by the 64-bit OR invert array on a 64-bit bus 439. The outputs of the OR enable array 438 are connected to respective inputs of a 64-input OR gate 442. The output of the 64-input OR gate array 442 is connected to one input terminal of an exclusive-OR gate 444 which functions as a master inverting gate. An INV/\*INV signal is provided on a signal line 445 to the other input terminal of the exclusive-OR gate 444. The output terminal of the exclusive-OR gate 444 is connected by a signal line to the other input terminal of the OR gate 428 where the OR gate 428 combines the outputs of the And and the OR channels to provide CMBx signals 430, where x corresponds to one of the 32 output terminals of a 32-bit system.

The 64-bit input state array 404 of the I/O system module 400 has terminals 0-31 which are always only input terminals. The input state array 404 includes a number of I/O terminals (numbered 32 through 63). All of these I/O terminals are input terminals unless otherwise programmed. Until configuration codes are loaded into the I/O system module 400, no output signals are provided at an output terminal for control of any external actions. Without configuration codes, the internal controller operations such as decoding of a bar code and matching of the bar code to a match code are performed but no output signal is provided at the output terminal. The results of the matching operation are only placed into the internal 64-bit input state array 404.

The 64-bit input state array 404 contains all of the input states that are subsequently made available to both the AND and OR combinatorial logic circuits for all of the I/O system module. The 32 I/O system modules therefore provide 32 outputs. Of the 64 input bits provided to the input terminals (0-63) to the 64-bit input state array, the 32 bits provided at terminals 0-31 are bits indicating the internal logical states of, for example, a bar code reader system, such as provided in connection with a PMC80 Series of printed-matter controllers provided by DataLogic, Inc. of Scotts Valley, California. The other 32 input bits provided at terminals 32-63 are associated with the external I/O points, or terminals.

The 32 internal logical states provided at terminals 0-31 include all of the internal states of, for example, the bar code reader system. The internal states provided by the bar code reader system are the results of operations performed by bar code readers. These basic results include: a status of the bar code reading and matching functions for each bar code scanner, a consecutive-error status for each scanner, a reject-verify-failure status for up to 8 I/O points, and a scanner-head-disabled status. The 32 external I/O terminals 32-63 of the state array provide the inputs to subsequent combinatorial logic circuits as well as feed-back/feed-forward connections to other outputs. The feed-forward feature provides the capability of performing more complex logic functions by cascading the logic functions.

10

15

20

25

30

35

Each logic internal status terminal 0-31 and each external input/output terminal 32-63 is assigned a bit position in the 64-bit input state array 104 which contains a total of 64 bits, or possible inputs. These 64 possible inputs are made available to subsequent AND or OR combinatorial logic.

In order to properly control the timing of the outputs generated by the combinatorial logic, an input latch is provided with a clock/clear signal provided on the signal line 408 from the multiplexer 410. This arrangement allows a programmer to synchronize the output of the configurable I/O system module with inspection events. Whenever the selected clock signal on signal line goes from false to true, the latest value in the input state array is presented to the input terminals of the AND and OR combinatorial logic circuits.

The clock signal to the input latch array 406 is enabled through the multiplexer 410, which provides for the selection of any of the four bar code presence signals in either the "true-to-false" or the "false-to-true" transition modes. External I/O points 28 thru 31 are also available as clocks to the Input Latch in the "true to false" and "false to true" transition.

The four bar code presence signals and 4 external I/O points are available as clock sources. A periodic internal clocking signal is also available which provides updates of the outputs similar to a PLC's scan cycle. This latch clock is used whenever it is desired to have constant/continuous update of the selected output according to the latest state of the bits in the input state array. This is the type of update that typically occurs with relay logic solving functions of programmable logic controllers.

The input latch passes the latest state of the input state array 404 to the combinatorial logic on the transition of the selected clock. The outputs of the latch are cleared, or set to "false," on the opposite edge of the selected clock. This guarantees that there will be transitions of the

14

subsequent combinatorial logic from one inspection to the next.

Note that the clearing function does not occur when the periodic clock source is used.

Each enabled output must have an update control enabled for it. This update control selects which of a number of events will cause an update to the output. These events will be the periodic clock source or external inputs (clock inputs or presence inputs). The timers should be 2 milliseconds and 10 milliseconds. These will be selected by a numeric value in an array which defines the update event for each output. These will be:

|    | 0       | - | Disabled                      |

|----|---------|---|-------------------------------|

|    | 1       | - | Presence #1 false to true     |

| 15 | 2       | - | Presence #2 false to true     |

|    | 3       | - | Presence #3 false to true     |

|    | 4       | - | Presence #4 false to true     |

|    | 5       | - | Presence #1 true to false     |

|    | 6       | - | Presence #2 true to false     |

| 20 | 7       | - | Presence #3 true to false     |

|    | 8       | - | Presence #4 true to false     |

|    | 9       | • | Input 29 false to true        |

|    | Α       | - | Input 29 false to true        |

|    | В       | • | Input 30 false to true        |

| 25 | C       | - | Input 31 false to true        |

|    | D       | - | Input 28 true to false        |

|    | ${f E}$ | - | Input 29 true to false        |

|    | ${f F}$ | - | Input 30 true to false        |

|    | 10      | - | Input 31 true to false        |

| 30 | 11      | - | 2 msec periodic clock source  |

|    | 12      | • | 10 msec periodic clock source |

35

40

Each of the output terminals of the input latch array 406 are connected to the corresponding inputs of the AND invert array 414 and the OR invert array 434. These arrays each contain 64 bits, each of which correspond to a position in the input state array. Any particular bit position that is set to a "1" in the corresponding invert array causes the logic value from the state array to be inverted before going into an associated combinatorial logic gate.

The output terminals of the AND invert array 414 are connected to corresponding inputs of the AND enable array 418. The output

terminals of the OR invert array 434 are connected to corresponding input terminals of the OR enable array 438. Each enable array contains 64 bits, each of which corresponds to a bit in the input state array. Setting a particular bit in one of the enable arrays directs the corresponding bit position from the corresponding input state array into the corresponding combinatorial logic gate. Enabling of an input is analogous to closing a switch in a circuit connecting an input state array bit to an input terminal of the corresponding combinatorial logic gate.

10

15

20

35

5

Each of the outputs of the AND enable array 418 are fed to a corresponding one of the 64 input terminals of the 64-input AND gate array 422. Each of the outputs of the OR enable array 438 is fed to a corresponding one of the 64 inputs of the 64-input OR gate array 444. All inputs to the AND gate that are not enabled are forced to TRUE (pulled-up). All inputs to the OR gate array that are not enabled are forced to FALSE (pulled-down).

The output of the AND gate array 422 has a selectable output inversion function provided by the Exclusive Or gate 424. The output of the OR gate array 444 has a selectable output inversion function provided by the Exclusive Or gate 444. The Exclusive Or gates 424, 444 are used to implement NAND and NOR functions.

The AND and OR logic states are combined using the final OR gate 428. At this point the combinatorial logic stage is complete. A CMBx signal 430 (where x = 0 to 31) appears at the output terminal of the I/O system module.

Each CMBx signal 430 may also be routed to a shift register, a pulse circuit, a direct channel to the physical output, or a latch circuit, as described in connection with FIG 6 herein below. A CMBx output may also be directed to drive an internal counter.

The output signal at terminal 430 may be fed to a counter 450 which then drives a display.

16

If no inputs are enabled for the AND array then the AND master invert (424) is set to invert. If no inputs are enabled for the OR array, then the OR master invert (444) is disabled.

5

10

15

20

25

30

35

Default definitions for external I/O points require that all I/O points including the SHF CLKs and the RJ VERs may also be used as general purpose inputs if they are not used for their default purpose. Their status is available in the input state array whether or not they are programmed to be an input or an output.

For a software implementation of the invention, each of the above events has an event handling routine that is called when the event occurs. This event handler will go to its own list which is made up at initialization time and which contains the vectors to each of the outputs to be updated. This list is made up at initialization time or whenever the configuration is performed in order to save time during execution.

In addition, with the exception of the 2msec and 10msec clocks, the external clocking signals to the input latch clear the latch on the off phase trailing edge (or) the unspecified edge.

- FIG. 5 illustrates the AND and OR combinatorial functions simulated for a configurable I/O system according to the invention. The And/Or Logic 500 is provided, for example, as a software simulation of a programmable multilevel array of AND/OR gates so that outputs are specified as a logical function of the inputs. The input state variables which are acted upon by the functional logic block include externally generated signals, program generated outputs, counter states, shift register states, and latch states. For each of an array of outputs, there can be a separate logic equation based on the input state variables.

- FIG. 5 shows the 64 elements of the input state array are combined with respective 64 elements of the inverter AND-INV-ARRAY in an Exclusive -Or Array 502. The 64 elements of the Exclusive -Or Array 502 are combined with respective 64 elements of the enable AND-

10

ENA\_ARRAY in an AND array 504. The 64 individual elements of the AND array 504 are combined together in an OR function 506 to provide a single output element, which is combined in another Exclusive-Or function 508 with the INV/\*INV control signal. A "0" value for the INV/\*INV control signal inverts the AND function to a NAND function. The output of the Exclusive-Or function 508 is one input to an output OR gate 510 which provides a CMBx output signal.

Similarly, FIG. 5 also shows the 64 elements of the input state array are combined with respective 64 elements of the inverter OR-INV-ARRAY in an Exclusive-Or Array 522. The 64 elements of the Exclusive-Or Array 512 are combined with respective 64 elements of the enable OR-ENA\_ARRAY in an AND array 514. The 64 individual elements of the AND array 514 are combined together in an OR function 516 to provide a single output element, which is combined in another Exclusive-Or function 518 with the INV/\*INV control signal. A "1" value for the INV/\*INV control signal inverts the OR function to a NOR function. The output of the Exclusive-Or function 518 is the other input to the output OR gate 510 which provides the CMBx output signal.

20

25

15

Note that the AND\_INV\_ARRAY inverts if a 0 is present, while the OR INV\_ARRAY inverts if a 1 is present.

An example of an externally generated input signal is a presence sensor which outputs a logic 1 whenever a package is in front of an infrared beam of light.

An example of an internally generated state variable comes from a consecutive error counter which increments once for each time a package passes the presence sensor without the label on the package being decoded. When the counter reaches a programmed limit value, it latches a state variable to a 1. This state variable can then be used by the combinatorial logic to set or clear output signals on the machine, such as a machine-stop signal.

35

30

With reference to FIG. 4, the combinatorial logic contains two

18

arrays of gates, the AND array and OR array. The state variables are input to each logic array. For each input there are also two programmable variables, the ENABLE and the INVERT.

5 The complete equation for a CMBx output (x=i) at terminal 430 of FIG. 4 is:

output(i)430 = Invert (AND\_result[i]422  $\oplus$  AND\_total\_invert[i] 424)+ (OR\_result[i]442  $\oplus$  OR\_total\_invert[i]444),

10

where:

$$AND\_result[i]422 = \sum_{j=1}^{j=M} (input(j)406 \oplus \overline{AND\_invert(i,j)414})$$

$$AND\_enable(i,j)418 \text{ and}$$

15

OR\_result(i)442=

$$\sum_{j=1}^{j=M}$$

(input(j)406  $\oplus$  OR\_invert(i,j)434)

•OR\_enable(i,j)438

The following symbols are provided as follows:  $\oplus$  means the 20 EXCLUSIVE OR operation;  $\oplus$  means Exclusive NOR operation;  $\bullet$  means the AND function; + means the OR function, and  $\sum_{j=1}^{j=M}$  is a summation for a number of terms.

There are M input state variables, designated input(j)406. There are multiple output signals designated output(i)430. For each input in each output equation there is an inversion for the input, in both the AND array designated And\_invert(i,j)424. For each input in each output equation there is an inversion variable, designated OR\_invert(i,j), for the input in both of the OR arrays. For each input in each output equation there is an enable variable, designated And\_enable(i,j), for the inputs in both of the AND arrays. For each input in each output equation there is an enable, designated OR\_enable(i,j), for the inputs in

both of the OR array. For each output, there is an inversion variable, designated And\_total\_invert(i), to change the AND equation to a NAND equation. For each output, there is an inversion variable, designated OR\_total\_invert(i), to change the OR equation to a NOR equation.

5

An event will trigger the calculation of the output states for one or more outputs. For example, if an event triggers the calculation of output(5), then the above equations are executed with i=5.

10

15

FIG. 6 shows a functional block diagram of an output conditioner module 600 which receives at input terminal 602 the output signal CMBx, where CMBx is provided from terminal 430 of the combinatorial logic phase of the I/O system module of FIG. 4. The signal at input terminal 602 is routed using mutually exclusive switches 603a, 603b either directly through a signal line 604 to an output conditioning module 606 or, alternatively, to an input terminal of a shift register module 608. Four register modules are available so that up to 8 shift registers are available either singly or paired as 1A to 1B, 2A to 2B, etc. Each module can be assigned to any of the CMBx outputs.

20

Either one or two shifters can be put into any of the output streams. If the shift register value is non-zero it will caused a shift operation, otherwise the signal goes directly thru to the next module.

25

The clock input to the shift registers comes through multiplexers 610, 611 that allows for separate selection of a clock input, in the same manner as the clock inputs to the combinatorial latch. This provides internal clock pulses or external inputs including the presence inputs.

30

35

Reject /Verify test blocks are related to any of the I/O points. Thus, when an output signal CMBx propagates through to the I/O points, the reject/verify test block is initiated, if its timer is non-zero. The reject timer starts when the output is initiated. If the reject timer expires before a transition is detected on the verify input, the RJ\_VF\_(X) state bit in the input state register will be asserted. The bit is cleared during the next slow periodic update cycle guaranteeing that an I/O

20

point will capture the state change.

In addition, the outputs of the combinatorial phase CMB00 - CMB31 are available through a multiplexer to clock any of six configurable event counters.

5

10

15

The remainder of the output conditioner module includes an output conditioner submodule which contains a pulse output timer 612 and a latch 614. The inputs to the timer 612 or the latch 614 are obtained using mutually exclusive switches 615a,a 615b. Operations of the pulse output timer and the latch are mutually exclusive so that when the pulse output is selected, the latch is de-selected and vice-versa.

The pulse output timer module 612, or pulser, provides a pulse output with a programmable duration. A pulse output is retriggerable. If a new trigger arrives before the pulse is complete, the pulser timeout is restarted and the pulse continues. If the pulser is set to zero, then the pulser module acts like a short and passes the state of the signal to the output circuit. Otherwise, a pulse always starts on a transition from a 0 to a 1. The pulse timer is programmable from 2msec to 2 seconds.

20

25

The latch 614 is always triggered from an input which goes from a 0 to a 1 state. When the latch output occurs, the output level remains until the latch is cleared. The signal that clears the latch is selected with a multiplexer similar to the clock selector for the input latch. Signals that clear the latch are: keyboard input, serial command, and selected external inputs. The latch also has an enable bit which can cause the name of the output to be written to a display and also to a serial port. The display is locked until cleared by the keypad. This allows alarm messages to be displayed.

30

35

After a signal exits the latch or pulser, it is fed to a two-input OR gate 616. The output of the OR gate is fed to on input of an EXCLUSIVE-OR gate 618. The other input terminal of the gate 618 receives a NC/NO signal which determines whether the final I/O output I/O (00-31) at terminal is NORMALLY OPEN OR NORMALLY CLOSED. (which refers to the final relay output). The output terminal is then directly

connected to a physical output device.

The output at terminal 430 is also available to the input latch. This allows logic circuits to be chained as well as to create circuits such as oscillators.

5

10

15

The PMC80 Series of printed-matter controllers includes four sets of counters 452 for each of the four bar code scanner. An additional 2 sets of 4 counters are available, of which 6 can be mapped to combinatorial outputs of modules. The first 3 counters in each group of four perform specific counting tasks while the fourth counter is used for totals and is incremented each time one of the other three counters is incremented. Whenever these additional sets of counters are enabled, a display program shows these counters and a printout routines prints these counters. A 10 char modifiable name is available for the counters which are identified as G, N, W, A, B, C, D, E, F, and T.

TABLE I shows the values of various control signals which are set during initialization of the system to obtain a specific I/O configuration.

#### TABLE I

| 20         | ; Application :<br>; Output Bit F<br>; Output Bit # | $unction = L_i$ | atch, WC_H     | 1, S                                  | hft Reg 3.                             | A (6)                                                                                                              |

|------------|-----------------------------------------------------|-----------------|----------------|---------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| 25         | ;<br>01<br>0<br>6<br>00                             |                 |                | · · · · · · · · · · · · · · · · · · · | counte<br>shifter<br>shifter<br>Rej Ve | source 00-17 (00=dis)<br>er 0-6 (0=dis)<br>r 0-8 (0=dis) L=link<br>r clock 00-14 (00=dis)<br>er Timer 0-8 (0=none) |

| <b>3</b> 0 | Ö                                                   |                 |                | ;                                     |                                        | er AND invert<br>er OR invert                                                                                      |

|            | 0                                                   |                 |                | ;                                     | maste                                  | er Ok invert                                                                                                       |

|            | ;<br>; AND_INV                                      | OR_INV          | AND_EN         |                                       | OR_EN                                  |                                                                                                                    |

|            | 0                                                   | 0               | $\overline{0}$ | 0                                     | ;                                      | good read head 1                                                                                                   |

|            | Õ                                                   | 0               | 0              | 0                                     | ;                                      | good read head 2                                                                                                   |

|            | 0                                                   | 0               | 0              | 0                                     | ;                                      | good read head 3                                                                                                   |

|            | 0                                                   | 0               | 0              | 0                                     | ;                                      | good read head 4                                                                                                   |

|            | 0                                                   | 0               | 0              | 0                                     | ;                                      | no read head 1                                                                                                     |

|            | 0                                                   | 0               | 0              | 0                                     | ;                                      | no read head 2                                                                                                     |

|            | 0                                                   | 0               | 0              | 0                                     | ;                                      | no read head 3                                                                                                     |

|            | 0                                                   | 0               | 0              | U                                     | ;                                      | no read head 4                                                                                                     |

|   |        |   | <b>2</b> 3 |     |         |                                |    |

|---|--------|---|------------|-----|---------|--------------------------------|----|

|   | 0      | 0 | 0          | 0   | ;       | i/o 26                         |    |

|   | Ô      | 0 | 0          | 0   | ;       | i/o 27                         |    |

|   | Ŏ      | Ö | 0          | 0   | ;       | i/o 28                         |    |

|   | Ŏ      | 0 | 0          | 0   | ;       | i/o 29                         |    |

|   | ñ      | Õ | 0          | 0   | :       | i/o 30                         |    |

|   | ő      | ŏ | 0          | 0   | ;       | i/o 31                         |    |

|   | WCH1   |   | ;          |     |         | ame (max length 10)            |    |

|   | NO     |   | ;          | NO  | or NC   | ,                              |    |

|   | Latch  |   | ;          | Lat | ch      |                                |    |

| 5 | Enable |   |            | Lat | ch dis  | play flag Enable/Disable       |    |

| U | Enable |   | <b>:</b>   | Lat | ch clea | ar by keyboard Enable/Disab    | le |

|   | 00     |   | ;          | Lat | ch clea | ar selection 00-16 (00-no clea | r) |

The foregoing descriptions of specific embodiments of the present invention have been presented for the purposes of illustration and description. They are not intended to be exhaustive or to limit the invention to the precise forms disclosed, and obviously many modifications and variations are possible in light of the above teaching. The embodiments were chosen and described in order to best explain the principles of the invention and its practical application, to thereby enable others skilled in the art to best utilize the invention and various embodiments with various modifications as are suited to the particular use contemplated. It is intended that the scope of the invention be defined by the Claims appended hereto and their equivalents.

24

#### IN THE CLAIMS

1. A configurable I/O system, comprising:

an input state array having a plurality of state variables representing input values;

a logic function means for operating on the plurality of state variables and for providing a logic output signal;

10

trigger means for synchronizing operation of the logic function means with a trigger event.

- 2. The configurable I/O system of Claim 1 including multiplexing means for selecting the trigger event from a plurality of trigger functions.

- 3. The configurable I/O system of Claim 1 including an output signal conditioner for conditioning the logic output signal.

20

30

35

- 4. The configurable I/O system of Claim 1 including means for initially configuring the logic function means.

- 5. The configurable I/O system of Claim 1 wherein the trigger means includes means for detecting a preselected input event.

- 6. The configurable I/O system of Claim 5 wherein the trigger means includes functional dispatch means for placing a detected preselected input event in a circular event queue and for removing the detected preselected input event from the circular event queue; and

wherein the logic function means for operating on the plurality of state variables and for providing a logic output signal includes means for executing a predetermined function in response to the preselected input event.

25

30

35

- 7. The configurable I/O system of Claim 6 wherein the functional dispatch means includes means for mapping the event through a table to the logic function means which include combinatorial logic calculation routine and wherein the functional dispatch means includes means for initiating execution of the combinatorial logic routine.

- 8. The configurable I/O system of Claim 1 wherein the logic function means includes a software simulation of a programmable array.

- 9. The configurable I/O system of Claim 8 wherein the programmable array is an array of AND/OR gates by means of which outputs can be specified as logical functions of the inputs.

- 10. The configurable I/O system of Claim 1 wherein the input values are state variables which consist of external signals, internally generated signals, counter states, shift register states, and latch states.

- 11. The configurable I/O system of Claim 10 wherein the external signals include a signal which is generated from a presence sensor.

- 12. The configurable I/O system of Claim 11 wherein the signal which is generated from the presence sensor includes a signal generated when an item is in front of an infrared light beam.

- 13. The configurable I/O system of Claim 6 wherein the internally generated signals are internally generated state variables which are provided by a consecutive error counter.

## 14. A configurable I/O system, comprising

an input state array for receiving a plurality of input signals and having a plurality of elements respectively corresponding to one of said input signals;

a latch array having elements for receiving and storing the states

PCT/US96/02781

5

20

25

of the elements of the input state array;

means for controlling a clock signal provided to the latch array to synchronize operation of the system with the occurrence of the clock signal.

an AND inverter array having elements for receiving and selectively inverting the elements of the latch means;

10 a multi-input AND array;

an AND input selection array for directing a corresponding bit from the latch array into one of the inputs of the multi-input AND array;

an AND Output inverter for selectably inverting the output of the multi-input AND array;

an OR inverter array having elements for receiving and selectively inverting the elements of the latch means;

a multi-input OR array;

an OR input selection array for directing a corresponding bit from the latch array into one of the inputs of the multi-input OR array;

an OR Output inverter for selectably inverting the output of the multi-input OR array;

an OR gate for combining the outputs of the AND Output inverter and the OR Output inverter.

### 15. A configurable I/O system, comprising

a first Exclusive OR array for logically combining each respective element of an input state array with the respective elements of an AND invert array;

- a first AND array for logically combining each respective elements of the exclusive OR array with each respective elements of an And enable array;

- a first OR array for logically combining the respective elements of the AND array into a single element;

- a first Exclusive-OR invert Array for combining the single element of the OR array with an invert command signal to selectably provide an inverted or non-inverted AND output signal;

- a second Exclusive OR array for logically combining each respective element of the input state array with the respective elements of an OR Invert array;

- a second AND array for logically combining respective elements of the second Exclusive OR array with respective elements of an OR enable array;

- 20 a second OR array for logically combining the respective elements of the second AND array into a single element;

30

35

- a second Exclusive-OR invert Array for combining the single element of the OR array with an invert command signal to selectably provide an inverted or non-inverted OR output signal;;

- an output OR function for logically combining the inverted or non-inverted AND output signal with the inverted or non-inverted OR output signal to provide an output signal.

- 16. The configurable I/O system of Claim 15 including an output signal conditioner for the output signal which alternatively provides a direct channels to an output terminal, shift registers, a pulse circuit, a latch circuit.

- 17. The configurable I/O system of Claim 15 wherein the output signal is provided to a counter.

3/6

INTERRUPT DRIVER EVENT QUEUE 302 DETECT NO **TRIGGER** SOURCE? ADD TRIGGER 304 SOURCE TO Rx EVENT QUEUE FIG. 3A 310 TRIGGER NO EVENT IN Rx QUEUE? ANY MORE FUNC NO TIONS ATTACHED TO Rx TRIGGER **EVENT?** 312 EXECUTE Rx **FUNCTION WITH** 314 Rx PARAMETERS AND SOURCE I.D. FIG. 3B

## INTERNATIONAL SEARCH REPORT

Interns al Application No PCT/US 96/02781

| A. CLASSIFICATION OF SUBJECT MATTER IPC 6 G05B19/045 |  |

|------------------------------------------------------|--|

|                                                      |  |

According to International Patent Classification (IPC) or to both national classification and IPC

### B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols) IPC 6 - 605B

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

| ategory * | MENTS CONSIDERED TO BE RELEVANT  Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No. |

|-----------|---------------------------------------------------------------------------------------------------------------------|-----------------------|

|           | EP,A,O 238 230 (ADVANCED MICRO DEVICES                                                                              | 1,8-10                |

|           | INC) 23 September 1987 see the whole document                                                                       | 6,7                   |

|           | EP,A,O 071 661 (IBM DEUTSCHLAND ;IBM (US))                                                                          | 6,7                   |

|           | 16 February 1983 see page 9, line 22 - page 13, line 8; figures 1,2                                                 |                       |

|           | EP,A,O 254 479 (ADVANCED MICRO DEVICES INC) 27 January 1988 see the whole document                                  | 1-5,8                 |

| (         | EP,A,O 349 391 (CROUZET SA) 3 January 1990 see the whole document                                                   | 1,11,12               |

|           | -/                                                                                                                  |                       |

|           |                                                                                                                     |                       |

| X Further documents are listed in the continuation of box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Patent family members are listed in annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| * Special categories of cited documents:  'A' document defining the general state of the art which is not considered to be of particular relevance  'E' earlier document but published on or after the international filing date  'L' document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)  'O' document referring to an oral disclosure, use, exhibition or other means  'P' document published prior to the international filing date but later than the priority date claimed | "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention.  "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone.  "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.  "&" document member of the same patent family  Date of mailing of the international search report |

| Date of the actual completion of the international search  17 July 1996                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2 6. 07. 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Name and mailing address of the ISA  European Patent Office, P.B. 5818 Patentiaan 2 NL - 2280 HV Rijswijk Tel. (+31-70) 340-2040, Tx. 31 651 epo nl, Fax: (+31-70) 340-3016                                                                                                                                                                                                                                                                                                                                                                                                                     | Authorized officer  Hauser, L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

## INTERNATIONAL SEARCH REPORT

Interns' al Application No PCT/US 96/02781

|           |                                                                                                           | PCT/US 96/02781       |

|-----------|-----------------------------------------------------------------------------------------------------------|-----------------------|

| •         | ation) DOCUMENTS CONSIDERED TO BE RELEVANT                                                                |                       |

| ategory * | Citation of document, with indication, where appropriate, of the relevant passages                        | Relevant to claim No. |

| X         | US,A,5 227 965 (KLAES CARL D ET AL) 13 July 1993 see column 2, line 48 - column 5, line 40; examples 1,2  | 14-16                 |

| X         | US,A,5 220 215 (DOUGLAS KURT P ET AL) 15 June 1993 see column 3, line 44 - column 4, line 39; figures 1-4 | 14,15                 |

| A         | EP,A,O 290 121 (TEKTRONIX INC) 9 November<br>1988<br>see the whole document                               | 1,8-10,<br>14,15      |

| A         | EP,A,0 380 456 (SGS THOMSON<br>MICROELECTRONICS) 1 August 1990<br>see the whole document                  | 1,14,15               |

| A         | DE,A,41 11 069 (GAZELLE MICROCIRCUITS INC) 31 October 1991 see the whole document                         | 1,14,15               |

|           |                                                                                                           |                       |

|           |                                                                                                           |                       |

|           |                                                                                                           |                       |

|           |                                                                                                           |                       |

|           |                                                                                                           |                       |

# INTERNATIONAL SEARCH REPORT

L...ormation on patent family members

Interna d Application No

PCT/US 96/02781

| Patent document<br>cited in search report | Publication date | Patent f<br>membe                         |                                                       | Publication date                                         |

|-------------------------------------------|------------------|-------------------------------------------|-------------------------------------------------------|----------------------------------------------------------|

| EP-A-0238230                              | 23-09-87         | DE-A-<br>JP-B-<br>JP-A-<br>US-A-          | 3783151<br>7092740<br>62277813<br>5042004             | 04-02-93<br>09-10-95<br>02-12-87<br>20-08-91             |

| EP-A-0071661                              | 16-02-83         | CA-A-<br>JP-C-<br>JP-B-<br>JP-A-<br>US-A- | 1187192<br>1675992<br>3042189<br>58031783<br>4495597  | 14-05-85<br>26-06-92<br>26-06-91<br>24-02-83<br>22-01-85 |

| EP-A-0254479                              | 27-01-88         | JP-A-<br>US-A-                            | 63030934<br>5349670                                   | 09-02-88<br>20-09-94                                     |

| EP-A-0349391                              | 03-01-90         | FR-A-<br>DE-D-<br>DE-T-<br>ES-T-<br>US-A- | 2633407<br>68911042<br>68911042<br>2047140<br>5191325 | 29-12-89<br>13-01-94<br>01-06-94<br>16-02-94<br>02-03-93 |

| US-A-5227965                              | 13-07-93         | NONE                                      |                                                       |                                                          |

| US-A-5220215                              | 15-06-93         | NONE                                      |                                                       |                                                          |

| EP-A-0290121                              | 09-11-88         | US-A-<br>CA-A-<br>JP-A-                   | 4801813<br>1274002<br>63282804                        | 31-01-89<br>11-09-90<br>18-11-88                         |

| EP-A-0380456                              | 01-08-90         | DE-D-<br>JP-A-                            | 69027227<br>2289098                                   | 11-07-96<br>29-11-90                                     |

| DE-A-4111069                              | 31-10-91         | GB-A-<br>JP-A-<br>US-A-                   | 2243008<br>7099440<br>5204555                         | 16-10-91<br>11-04-95<br>20-04-93                         |