**(19) 대한민국특허청(KR)**

**(12) 공개특허공보(A)**

**(51) Int. Cl.<sup>6</sup>**

**H01L 21/82**

**(11) 공개번호** 특 1995-0034685

**(43) 공개일자** 1995년 12월 28일

|                                     |                               |

|-------------------------------------|-------------------------------|

| (21) 출원번호                           | 특 1995-0009647                |

| (22) 출원일자                           | 1995년 04월 24일                 |

|                                     |                               |

| (30) 우선권주장                          | 94-98548 1995년 05월 12일 일본(JP) |

| (71) 출원인                            | 가부시키가이샤 히타치세이사쿠쇼 가나이 쓰토무      |

| 일본국 도오쿄오토 치요다쿠 간다스루가다이 4쵸오메 6반치     |                               |

| (72) 발명자                            | 스즈키 치카시                       |

| 일본국 도오쿄오토 고쿠분지시 미나미마치 3-3-15        |                               |

| 오큐야마 고오스케                           |                               |

| 일본국 사이타마켄 가와고에시 미나미오오츠카 688-4       |                               |

| 다케다 도시후미                            |                               |

| 일본국 도오쿄오토 고다이라시 죠우스이촌쵸오 5-18-1-13   |                               |

| 구보타 가즈히코                            |                               |

| 일본국 도오쿄오토 히가시무라야마시 미스미쵸오 2-3-11-408 |                               |

| (74) 대리인                            | 임석재, 강용복                      |

**심사청구 : 없음**

**(54) 반도체 집적회로장치의 제조방법**

**요약**

반도체 기판상에 형성된 TiW로 되는 하부전극상에 아모르피스 실리콘으로 되는 유전체막을 끼워 TiW로 되는 상부전극을 설치해도 되는 안티퓨즈를 가지는 FPGA(Field Programmable Gate Array)의 프로그램에 즈음해서 그 안티퓨즈의 도통부분의 기계적 강도를 향상시키기 위해 교류전압을 인가하여 교류전류를 흐르게 하였다.

**대표도**

**도1**

**명세서**

[발명의 명칭]

반도체 집적회로장치의 제조방법

[도면의 간단한 설명]

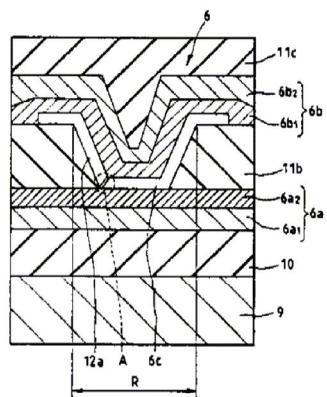

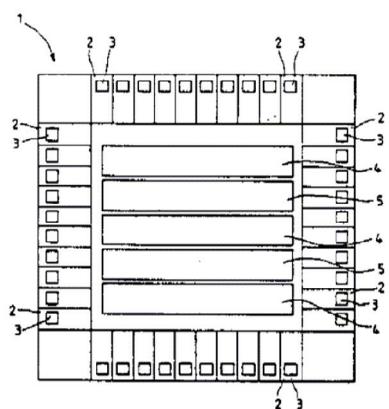

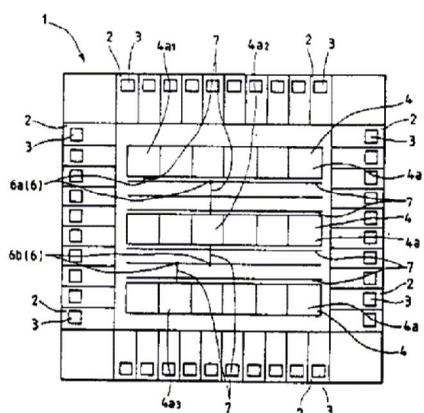

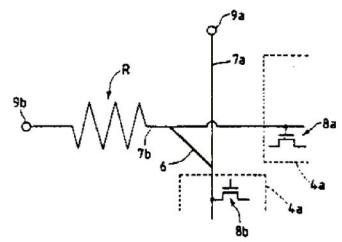

제1도는 본 발명의 실시예인 반도체 집적회로장치를 구성하는 반도체칩의 전체 평면도, 제2도는 프로그램후의 반도체칩을 설명하기 위한 전체 평면도, 제3도는 안티퓨즈(antifuse)의 접촉상태를 설명하기 위한 회로도.

본 건은 요부공개 건이므로 전문 내용을 수록하지 않았음

**(57) 청구의 범위**

**청구항 1**

주면고, 상기 주면상에서 금속으로 형성된 하부전극과, 상기 하부전극상에서 금속으로 형성된 상부전극 및 상기 하부전극과 상부전극 사이에 형성된 유전체막을 가지며, 상기 하부전극, 상기 상부전극 및 유전체막이 안티퓨즈를 구성하는 반도체 기판을 준비하는 스텝과, 상기 하부전극 및 상부전극 사이에 교류전압을 인가하는 것에 의해 상기 안티퓨즈를 프로그래하는 스텝을 구비하고, 상기 안티퓨즈를 프로그램하는 상기 스텝에서, 상기 유전체막에 교류를 흐르게 함으로써 상기 유전체막에 도통부분이 형성되고, 상기 도통부분에 기계적인 강도가 향상되도록 한 반도체 집적회로장치의 제조방법.

**청구항 2**

주면과, 상기 주면상에서 금속으로 형성된 하부전극과, 상기 하부전극상에서 금속으로 형성된 상부전극 및 상기 하부전극과 상부전극 사이에 형성된 유전체막을 가지며, 상기 하부전극, 상기 상부전극 및 유전체막이 안티퓨즈를 구성하는 반도체 기판을 준비하는 스텝과, 상기 하부전극 및 상부전극 사이에 직류전압을 인가함으로써 상기 유전체막에 도통부분을 형성하는 스텝과, 상기 도통부분에 기계적인 강도가 향상시키기 위해 상기 안티퓨즈를 통해 교류전류가 흐르도록 상기 상부전극 및 하부전극 사이에 교류전압을 인가하는 스텝을 구비하는 반도체 집적회로장치의 안티퓨즈를 프로그램하는 방법.

**청구항 3**

주면과 상기 주면상에서 금속으로 형성된 하부전극과, 상기 하부전극상에서 금속으로 형성된 상부전극 및 상기 하부전극과 상부전극 사이에 형성된 유전체막을 가지며, 상기 하부전극, 상기 상부전극 및 유전체막으로 안티퓨즈를 구성하는 반도체 기판을 준비하는 스텝과, 상기 하부전극 및 상부전극 사이에 교류전압을 인가하는 것에 의해 상기 안티퓨즈를 구성하는 프로그램하는 스텝을 구비하고, 상기 안티퓨즈를 프로그램하는 스텝에서, 상기 유전체막에 도통부분이 형성되고, 또한, 교류전류가 상기 도통부분에 기계적인 강도가 향상시키기 위해 상기 안티퓨즈를 통해 교류전류가 흐르도록 상기 상부전극 및 하부전극 사이에 교류전압을 인가하는 스텝을 구비하는 반도체 집적회로장치의 안티퓨즈를 프로그램하는 방법.

**청구항 4**

주연가, 상기 주면상에 형성된 MISRET와 상기 MISFET 및 주면상에 형성된 제1절연막과, 상기 제1절연막상에 하부전극과, 상기 MISFET의 게이트전극과 소스/드레인영역을 전기적으로 접속하는 제1배선을 포함하여 형성된 제1금속배선층과, 상기 제1절연막 및 제1금속배선층상에 형성되어 제1개구를 가지는 제2절연막 및 상기 제2절연막상에 상부전극과, 상기 제1배선을 전기적으로 접속하는 제2배선을 포함하여 형성된 제2금속 배선층을 가지고, 상기 제1개구에서 상기 하부전극과 상부전극 사이에 형성된 유전체막을 더 가지며, 상기 상부전극, 상기 절연막 및 하부전극이 안티퓨즈를 구성하는 반도체 기판을 준비하는 스텝과, 상기 하부전극과 상부전극 사이에 교류전압을 인가하는 것에 의해 상기 안티퓨즈를 프로그램하는 스텝을 구비하고, 상기 안티퓨즈를 프로그램하는 스텝하는, 교류전류가 상기 유전체막에 형성된 도통부분에 기계적인 강도를 향상시키기 위해 상기 도통부분을 통해 흐르는 반도체 집적회로장치의 제조방법.

**청구항 5**

제1항에 있어서, 상기 각각의 하부전극과 상부전극은 실리콘과 화학적으로 각각 결합하여 규화물을 형성하는 금속, 티탄(Ti), 텉스텐(W) 및 몰리브덴(Mo) 중 하나를 포함하고, 상기 유전체막은 아모르퍼스 실리콘, 이산화실리콘, 질화실리콘, 탄화실리콘 및 실리콘을 포함하는 화합물 중 하나로 형성되고, 상기 도통부분은 상기 금속중 하나와 실리콘으로 된 규화물을 포함하는 반도체 집적회로장치의 제조방법.

**청구항 6**

제2항에 있어서, 상기 각각의 하부전극과 상부전극은 실리콘과 화학적으로 각각 결합하여 규화물을 형성하는 금속, 티탄(Ti), 텉스텐(W) 및 몰리브덴(Mo) 중 하나를 포함하고, 상기 유전체막은 아모르퍼스 실리콘, 이산화실리콘, 질화실리콘, 탄화실리콘 및 실리콘을 포함하는 화합물 중 하나로 형성되고, 상기 도통부분은 상기 금속중 하나와 실리콘으로 된 규화물을 포함하는 반도체 집적회로장치의 안티퓨즈를 프로그램하는 방법.

**청구항 7**

제3항에 있어서, 상기 각각의 하부전극과 상부전극은 실리콘과 화학적으로 각각 결합하여 규화물을 형성하는 금속, 티탄(Ti), 텉스텐(W) 및 몰리브덴(Mo) 중 하나를 포함하고, 상기 유전체막은 아모르퍼스 실리콘, 이산화실리콘, 질화실리콘, 탄화실리콘 및 실리콘을 포함하는 화합물 중 하나로 형성되고, 상기 도통부분은 상기 금속중 하나와 실리콘으로 된 규화물을 포함하는 반도체 집적회로장치의 제조방법.

**청구항 8**

제4항에 있어서, 상기 각각의 하부전극과 상부전극은 실리콘과 화학적으로 각각 결합하여 규화물을 형성하는 금속, 티탄(Ti), 텉스텐(W) 및 몰리브덴(Mo) 중 하나를 포함하고, 상기 유전체막은 아모르퍼스 실리콘, 이산화실리콘, 질화실리콘, 탄화실리콘 및 실리콘을 포함하는 화합물 중 하나로 형성되고, 상기 도통부분은 상기 금속중 하나와 실리콘으로 된 규화물을 포함하는 반도체 집적회로장치의 제조방법.

**청구항 9**

제4항에 있어서, 상기 MISFET에 의해 논리블록이 형성되고, 상기 안티퓨즈가 상기 논리블록 사이에 위치되며, 상기 안티퓨즈, 상기 제1배선 및 상기 제2배선은 상기 논리블록 사이에서 전기적으로 접속되는 반도체 집적회로장치의 제조방법.

**청구항 10**

제4항에 있어서, 상기 제1금속배선층은 제1알루미늄(Al)막과, 상기 제1알루미늄막상에 형성된 제1금속막으로 형성되고, 상기 제2금속배선층은 제2금속막과, 상기 제2금속막상에 형성된 제2금속막으로 형성되며, 상기 제1금속막과 제2금속막은 실리콘과 화학적으로 결합하여 규화물을 형성하는 금속을 포함하고, 상기 유전체막은 실리콘을 포함하며, 상기 유전체막은 상기 제1금속막과 제2금속막 사이에 끼워지는 반도체 집적회로장치의 제조방법.

**청구항 11**

제10항에 있어서, 상기 제1금속막은 상기 유전체막으로 함해서 제1알루미늄막을 형성하는 알루미늄의 이동을 억제하기에 충분한 두께로 형성되는 반도체 집적회로장치의 제조방법.

#### 청구항 12

제11항에 있어서, 상기 제1금속막의 두께는 약 150nm인 반도체 집적회로장치의 제조방법.

#### 청구항 13

제5항에 있어서, 상기 반도체 집적회로장치는 게이트 어레이이고, 상기 게이트 어레이에는 소정의 논리회로를 형성하며, 상기 논리회로는 상기 복수의 논리블록과, 상기 논리블록을 상호 접속시키는 접속경로를 포함하고, 상기 접속경로는 도통 안티퓨즈와 비도통 안티퓨즈의 조합인 반도체 집적회로장치의 제조장치.

#### 청구항 14

제6항에 있어서, 상기 반도체 집적회로장치는 게이트 어레이이고, 상기 게이트 어레이에는 소정의 논리회로를 형성하며, 상기 논리회로는 상기 복수의 논리블록과, 상기 논리블록을 상호 접속시키는 접속경로를 포함하고, 상기 접속경로는 도통 안티퓨즈와 비도통 안티퓨즈의 조합인 반도체 집적회로장치의 안티퓨즈를 프로그램하는 방법.

※ 참고사항 : 최초출원 내용에 의하여 공개하는 것임.

#### 도면

##### 도면1

##### 도면2

## 도면3

## 도면4