(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6945388号

(P6945388)

(45) 発行日 令和3年10月6日(2021.10.6)

(24) 登録日 令和3年9月16日(2021.9.16)

(51) Int.Cl.

F 1

|              |           |             |      |

|--------------|-----------|-------------|------|

| HO1L 21/3065 | (2006.01) | HO1L 21/302 | 105A |

| HO1L 21/28   | (2006.01) | HO1L 21/28  | L    |

| HO1L 21/768  | (2006.01) | HO1L 21/90  | A    |

| HO1L 21/336  | (2006.01) | HO1L 29/78  | 371  |

| HO1L 29/788  | (2006.01) | HO5H 1/46   | M    |

請求項の数 6 (全 14 頁) 最終頁に続く

(21) 出願番号

特願2017-160546 (P2017-160546)

(22) 出願日

平成29年8月23日(2017.8.23)

(65) 公開番号

特開2019-40959 (P2019-40959A)

(43) 公開日

平成31年3月14日(2019.3.14)

審査請求日

令和2年6月3日(2020.6.3)

(73) 特許権者 000219967

東京エレクトロン株式会社

東京都港区赤坂五丁目3番1号

(74) 代理人 100107766

弁理士 伊東 忠重

(74) 代理人 100070150

弁理士 伊東 忠彦

(72) 発明者 斎藤 祐介

東京都港区赤坂五丁目3番1号 赤坂Bizタワー 東京エレクトロン株式会社内

審査官 鈴木 智一郎

最終頁に続く

(54) 【発明の名称】エッティング方法及びエッティング処理装置

## (57) 【特許請求の範囲】

## 【請求項 1】

処理容器内にガスと、第1の周波数の第1電力と、該第1の周波数よりも低い第2の周波数の第2電力を供給し、浮遊電位の電極層の上層に形成されたシリコン含有膜をエッティングするエッティング方法であって、

前記処理容器は、

前記シリコン含有膜のエッティング中に基板が載置される下部電極と、前記下部電極と対向する上部電極と、を有し、

前記下部電極または前記上部電極に前記第1電力を、そして前記下部電極に前記第2電力を供給するよう構成されており、

前記シリコン含有膜は、浮遊電位の電極層の上層に形成されており、

前記エッティング方法は、

前記シリコン含有膜のエッティング中に、前記シリコン含有膜に形成されたエッティングパターンの底部が、前記電極層から所定の距離よりも離れている間、前記第1電力を連続波として供給し、前記第2電力を連続波又はデューティー比が50%以上のパルス波として供給し、

前記シリコン含有膜のエッティング中に、前記シリコン含有膜に形成されたエッティングパターンの底部が、前記電極層から所定の距離以下になると、前記第1電力を連続波として供給し、前記第2電力をデューティー比が20%以下のパルス波として供給する、エッティング方法。

**【請求項 2】**

前記エッチングパターンの底部が前記電極層から前記所定の距離よりも離れている間に供給される前記第2電力の大きさは、前記エッチングパターンの底部が前記電極層から前記所定の距離以下になった後に供給される前記第2電力の大きさと同じである、

請求項1に記載のエッチング方法。

**【請求項 3】**

前記シリコン含有膜をエッチングしたパターンの底部が、前記電極層から所定の距離以下になると、前記第1電力を連続波として供給し、前記第2電力をデューティー比が5%以上20%以下のパルス波として供給する、

請求項1又は2に記載のエッチング方法。

10

**【請求項 4】**

前記第2電力のパルス周波数は、0.1kHz以上50kHz以下である、

請求項1～3のいずれか一項に記載のエッチング方法。

**【請求項 5】**

前記エッチング方法では、前記シリコン含有膜としてシリコン酸化膜、シリコン窒化膜、シリコン酸化膜とシリコン窒化膜との積層膜、炭素含有シリコン酸化膜、炭素含有シリコン窒化膜、炭素含有シリコン酸化膜と炭素含有シリコン窒化膜との積層膜のいずれかをエッチングする、

請求項1～4のいずれか一項に記載のエッチング方法。

**【請求項 6】**

20

処理容器内にガスを供給するガス供給部と、第1の周波数の第1電力と該第1の周波数よりも低い第2の周波数の第2電力とを供給する電力供給部と、制御部と、を有し、接地電位となる導電層と対向する浮遊電位の電極層の上層に形成されたシリコン含有膜をエッチングするエッチング処理装置であって、

前記制御部は、

前記シリコン含有膜のエッチング中に、前記シリコン含有膜に形成されたエッチングパターンの底部が、前記電極層から所定の距離よりも離れている間、前記第1電力を連続波として供給し、前記第2電力を連続波又はデューティー比が50%以上のパルス波として供給し、

前記シリコン含有膜のエッチング中に、前記シリコン含有膜に形成されたエッチングパターンの底部が、前記電極層から所定の距離以下になると、前記第1電力を連続波として供給し、前記第2電力をデューティー比が20%以下のパルス波として供給する、ことを含む処理を実行する、エッチング処理装置。

30

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、エッチング方法及びエッチング処理装置に関する。

**【背景技術】****【0002】**

3次元構造を有するNAND(3D-NAND)型フラッシュメモリを製造する場合において、エッチングにより絶縁膜に複数のホールを形成する技術が知られている(例えば、特許文献1～3を参照)。

40

**【0003】**

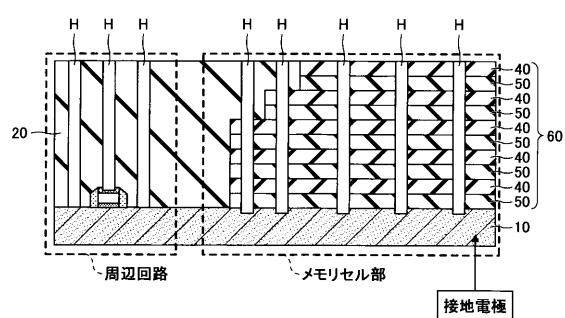

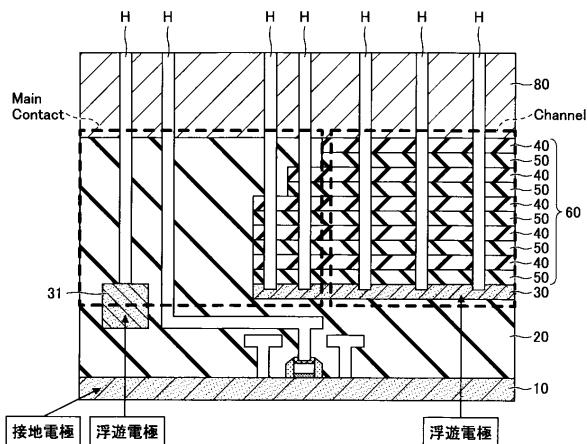

図1(a)に示す従来の3D-NAND型フラッシュメモリ構造では、メモリセル部と周辺回路は並列に配置されている。この場合、メモリセル部及び周辺回路の最下層は、シリコン基板である接地電位の導電層10となる。

**【先行技術文献】****【特許文献】****【0004】**

【特許文献1】米国特許出願公開第2013/0059450号明細書

50

【特許文献 2】特開 2016 - 219771 号公報

【特許文献 3】特開 2014 - 90022 号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、図 1 (b) に示す 3D-NAND 型フラッシュメモリ構造では、デバイスの集積度を上げるために、周辺回路の上方にメモリセル部が配置される。この構造では、メモリセル部の電極層は、シリコン基板から離れた位置にあり、浮遊電極 30 となる。

【0006】

この状態で、メモリセル部のシリコン酸化膜 40 とシリコン窒化膜 50 との積層膜 60 をエッティングすると、浮遊電極 30 と接地電位の導電層 10 との間に電位差が生じ、電子シェーディング効果に起因するアーキングが生じる。

【0007】

アーキングが生じると、周辺回路にダメージを与える場合があるため、アーキングを抑制する必要がある。一方、アーキングを生じ難くするために、供給するパワーを抑えてエッティングを行うと、エッティングレート等の所定のエッティング特性が得られない場合がある。

【0008】

上記課題に対して、一側面では、本発明は、所定のエッティング特性を維持しつつ、アーキングを抑制することを目的とする。

【課題を解決するための手段】

【0009】

上記課題を解決するために、一の態様によれば、処理容器内にガスと、第 1 の周波数の第 1 電力と、該第 1 の周波数よりも低い第 2 の周波数の第 2 電力とを供給し、浮遊電位の電極層の上層に形成されたシリコン含有膜をエッティングするエッティング方法であって、前記処理容器は、前記シリコン含有膜のエッティング中に基板が載置される下部電極と、前記下部電極と対向する上部電極と、を有し、前記下部電極または前記上部電極に前記第 1 電力を、そして前記下部電極に前記第 2 電力を供給するよう構成されており、前記シリコン含有膜は、浮遊電位の電極層の上層に形成されており、前記エッティング方法は、前記シリコン含有膜のエッティング中に、前記シリコン含有膜に形成されたエッティングパターンの底部が、前記電極層から所定の距離よりも離れている間、前記第 1 電力を連続波として供給し、前記第 2 電力を連続波又はデューティー比が 50 % 以上のパルス波として供給し、前記シリコン含有膜のエッティング中に、前記シリコン含有膜に形成されたエッティングパターンの底部が、前記電極層から所定の距離以下になると、前記第 1 電力を連続波として供給し、前記第 2 電力をデューティー比が 20 % 以下のパルス波として供給する、エッティング方法が提供される。

【発明の効果】

【0010】

一の側面によれば、所定のエッティング特性を維持しつつ、アーキングを抑制することができる。

【図面の簡単な説明】

【0011】

【図 1】3D-NAND 構造の一例を説明するための図。

【図 2】一実施形態に係る 3D-NAND 構造によるアーキングの発生を説明するための図。

【図 3】一実施形態に係るエッティング処理装置の構成の一例を示す図。

【図 4】一実施形態に係る 3D-NAND 構造のエッティングについて説明するための図。

【図 5】一実施形態に係るエッティングにおけるバイアスパルスとアーキングとの関係の一例を示す図。

【図 6】一実施形態に係るエッティング処理を説明するための図。

10

20

30

40

50

【図7】一実施形態に係るエッティング処理の一例を示すフローチャート。

【図8】一実施形態に係るエッティング処理の結果のパターンの一例を示す図。

【図9】一実施形態に係るバイアスパルスの効果を説明するための図。

【図10】一実施形態に係るエッティング特性の一例を示す図。

【発明を実施するための形態】

【0012】

以下、本発明を実施するための形態について図面を参照して説明する。なお、本明細書及び図面において、実質的に同一の構成については、同一の符号を付することにより重複した説明を省く。

【0013】

10

[はじめに]

図1に示す3D-NANDフラッシュメモリ等のデバイスの製造には、プラズマを用いてシリコン酸化膜(SiO<sub>2</sub>)40とシリコン窒化膜(SiN)50との積層膜60に複数のホールH(コンタクトホール)を形成するエッティング工程がある。このとき、積層膜60及びシリコン酸化膜20に対して、同時にエッティングが行われる。

【0014】

図1(a)に示す従来の3D-NAND型フラッシュメモリ構造では、メモリセル部と周辺回路は並列に配置されている。この場合、周辺回路の電極は接地され、シリコン基板である接地電位の導電層10との間に電位差は生じない。

【0015】

20

一方、図1(b)に示す3D-NAND型フラッシュメモリ構造では、デバイスの集積度を上げるために、周辺回路の上方にメモリセル部が配置される。この構造では、メモリセル部の電極層(以下、「浮遊電極30」ともいう。)は、接地電位の導電層10から離れた位置にあり、浮遊電位となる。

【0016】

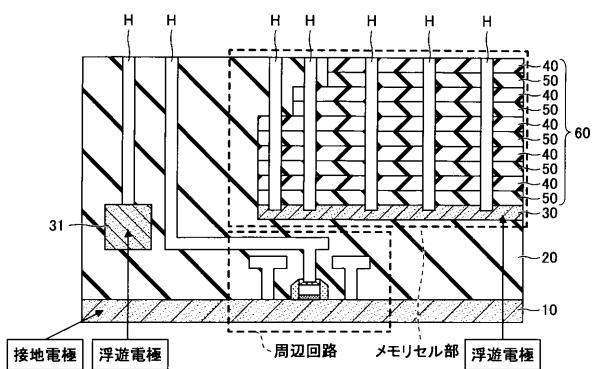

この状態で、積層膜60及びシリコン酸化膜20を同時にエッティングすると、図2に示すように、浮遊電極30及び浮遊電極31と導電層10との間に電位差Vが生じる。そうすると、浮遊電極30や浮遊電極31に電子シェーディング効果に起因するアーキングが生じる。

【0017】

30

図2の下側にホールHの底部周辺の拡大図を示すように、プラズマ中のイオンは、ホールHのエッティングパターンに垂直に入射するのに対して、プラズマ中の電子はランダムな方向から入射する。以上から、電子シェーディング効果とは、積層膜60上のマスク(カーボン膜80)に遮断される狭いスペースからエッティングパターンの底部まで到達する電子(入射電子量)が減少する現象をいう。この結果、エッティングパターンの底部が正にチャージアップし、浮遊電極30、31と導電層(シリコン基板)10との間に電位差が生じることでシェーディングダメージが起こる。シェーディングダメージとは、電子シェーディング効果に起因するウェハのアーキングをいう。アーキングが生じると、ウェハW上の周辺回路にダメージを与える場合がある。

【0018】

40

そこで、本実施形態では、接地電位となる導電層のシリコン基板と対向する浮遊電位の電極層の上層に形成されたシリコン含有膜をエッティングする際に、アーキングの発生を抑制することが可能なエッティング方法を提案する。

【0019】

以下の説明では、最初に、本実施形態に係るエッティング処理装置の全体構成を説明し、その後、本実施形態に係るエッティング方法について説明する。

【0020】

[エッティング処理装置の全体構成]

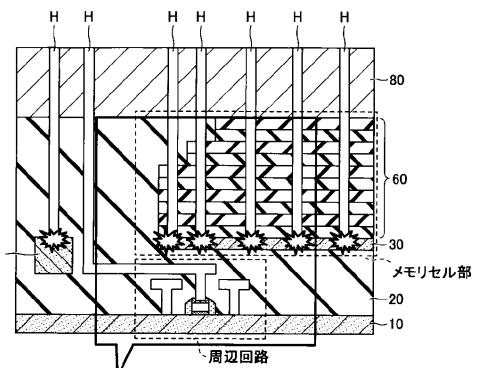

まず、本発明の一実施形態に係るエッティング処理装置1の全体構成について、図3を参照しながら説明する。ここでは、エッティング処理装置1の一例として容量結合型プラズマ

50

エッティング装置を挙げる。

**【0021】**

本実施形態にかかるエッティング処理装置1は、特に半導体ウェハW(以下、「ウェハW」とも呼ぶ。)をエッティングする。

**【0022】**

エッティング処理装置1は、例えばアルミニウム等の導電性材料からなる処理容器2と、処理容器2の内部にガスを供給するガス供給部11とを有する。処理容器2は電気的に接地されている。処理容器2の内部には下部電極21と、これに対向して平行に配置された上部電極22とを有する。下部電極21は、ウェハWを載置する載置台としても機能する。

10

**【0023】**

下部電極21には、第1整合器33を介して第1高周波電源32が接続され、第2整合器35を介して第2高周波電源34が接続される。第1高周波電源32は、27MHzよりも高く、例えば100MHzの周波数の高周波電力HF(プラズマ生成用の高周波電力)を下部電極21に印加する。第2高周波電源34は、13MHzよりも低い、例えば3MHzの高周波電力LF(イオン引き込み用の高周波電力)を下部電極21に印加する。高周波電力HFは、上部電極22に印加してもよい。

**【0024】**

第1整合器33は、第1高周波電源32の内部(または出力)インピーダンスに負荷インピーダンスを整合させる。第2整合器35は、第2高周波電源34の内部(または出力)インピーダンスに負荷インピーダンスを整合させる。

20

**【0025】**

上部電極22は、その周縁部を被覆するシールドリング41を介して処理容器2の天井部に取り付けられている。上部電極22には、ガスを拡散する拡散室51と、ガス導入口45とが形成されている。ガス供給部11から出力されたガスは、ガス導入口45を介して拡散室51に供給され、拡散室51にて拡散され、ガス流路55を経てガス孔28から下部電極21と上部電極22との間のプラズマ空間に供給される。このようにして上部電極22は、ガスを供給するガスシャワーへッドとしても機能する。

**【0026】**

処理容器2の底面には排気口61が形成されており、排気口61に接続された排気装置65によって処理容器2の内部が排気される。これによって、処理容器2の内部を所定の真空度に維持することができる。処理容器2の側壁には、ゲートバルブGが設けられている。ゲートバルブGは、処理容器2からウェハWの搬入及び搬出を行う際に搬出入口を開閉する。

30

**【0027】**

[制御部のハードウェア構成]

エッティング処理装置1には、装置全体の動作を制御する制御部100が設けられている。制御部100は、CPU(Central Processing Unit)101、ROM(Read Only Memory)102及びRAM(Random Access Memory)103を有している。

**【0028】**

40

ROM102には、制御部100により実行される基本プログラム等が記憶されている。RAM103には、レシピが格納されている。レシピにはプロセス条件(エッティング条件)に対するエッティング処理装置1の制御情報が設定されている。制御情報には、プロセス時間、圧力(ガスの排気)、高周波電力や電圧、各種ガス流量、チャンバ内温度(例えば、上部電極温度、処理容器2の側壁温度、ウェハの設定温度)等が含まれる。なお、レシピは、ハードディスクや半導体メモリに記憶されていてもよい。また、レシピは、CD-ROM、DVD等の可搬性のコンピュータにより読み取り可能な記憶媒体に収容された状態で、記憶領域の所定位置にセットするようにしてもよい。

**【0029】**

CPU101は、ROM102に格納された基本プログラムに基づき、エッティング処理

50

装置1の全体の制御を行う。CPU101は、RAM103に格納されたレシピの手順に従い、ウェハWへのエッティング処理を制御する。

#### 【0030】

##### [エッティング時のアーキング数]

本実施形態では、浮遊電極が存在するデバイス構造において、浮遊電極上の絶縁膜のエッティング時に発生する電子シェーディングによるダメージを抑制する。浮遊電極が存在するデバイス構造の一例として、本実施形態では、3D-NAND構造を例に挙げて説明する。しかしながら、本実施形態に係るエッティング方法を適用可能なデバイス構造は、3D-NAND構造に限らず、接地電位となる導電層と対向する浮遊電位の電極層の上層に形成されたシリコン含有膜をエッティングする場合に適用可能である。

10

#### 【0031】

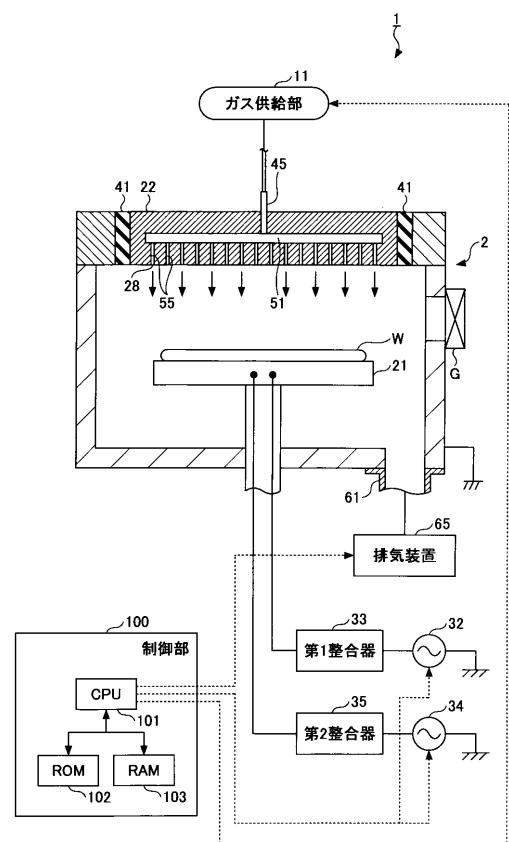

図4に示す3D-NAND構造におけるエッティングでは、浮遊電極31へのメインコンタクト(Main Contact)と、浮遊電極30へのコンタクト(Channel)のホールHのエッティングが一括して実行される。

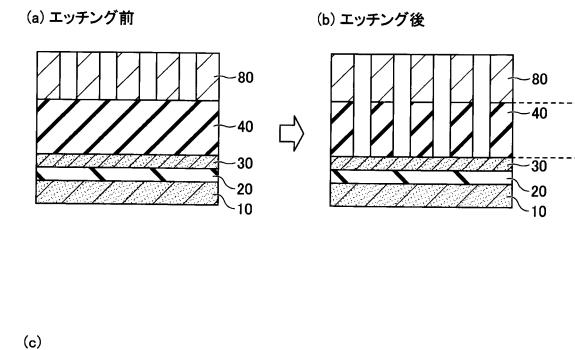

#### 【0032】

このときに発生するアーキング数について、図5の実験結果の一例を参照しながら説明する。この実験では、図5(a)に示す膜構造において、エッティング対象膜であるシリコン酸化膜40を、図5(b)に示すように、下地膜のポリシリコンの浮遊電極30までカーボン膜80に形成されたマスクパターンにエッティングする。このとき、エッティングの途中でエッティング条件を切り替えず、下記プロセス条件に基づき浮遊電極30が露出するまでエッティングを続ける。

20

<プロセス条件>

|                        |                                                          |

|------------------------|----------------------------------------------------------|

| 圧力                     | 20 mT (2.666 Pa)                                         |

| ガス種                    | C <sub>4</sub> F <sub>6</sub> ガス、COガス及びO <sub>2</sub> ガス |

| 高周波電力HF                | 600W(連続波) 100MHz                                         |

| 高周波電力LF                | 11000W(連続波、パルス波) 3MHz                                    |

| 高周波電力LFがパルス波の場合:パルス周波数 | 10kHz~50kHz、Duty 5%~90%                                  |

なお、パルス周波数は、高周波電力を印加する際のオン/オフの繰り返しにおける、周期を示す。

30

#### 【0033】

このとき、シリコン基板である接地電位の導電層10に対してシリコン酸化膜20を挟んで上方に位置するポリシリコンの浮遊電極30は浮遊電極であるため、エッティング処理中にアーキングが発生することがある。図5(c)のグラフは、エッティング処理中に生じたアーキング数の一例である。横軸は、高周波電力LFのDuty(デューティー)比である。縦軸は、高周波電力LFのDuty比を変化させたときのアーキング数の変化を示す。アーキング数は、実験によりウェハWに放電が生じた痕跡がある箇所の数である。

#### 【0034】

高周波電力HF及び高周波電力LFが連続波(CW)のときのアーキング数「2000」を参照値(CW ref.)とし、高周波電力LFがパルス波の場合(以下、「バイアスパルス」ともいう。)のアーキング数と比較する。バイアスパルスのDuty比が5%~90%の範囲のいずれにおいても、高周波電力HF及び高周波電力LFが連続波のときのアーキング数よりも少なくなっている。

40

#### 【0035】

許容されるアーキング数を約600個(ターゲット)とすると、バイアスパルスのDuty比が20%以下であれば、発生するアーキング数は許容範囲内となることがわかる。よって、図5(c)のグラフから、高周波電力LFをパルス波にして印加する場合、Duty比は5%~20%の範囲内が好ましいことがわかった。

#### 【0036】

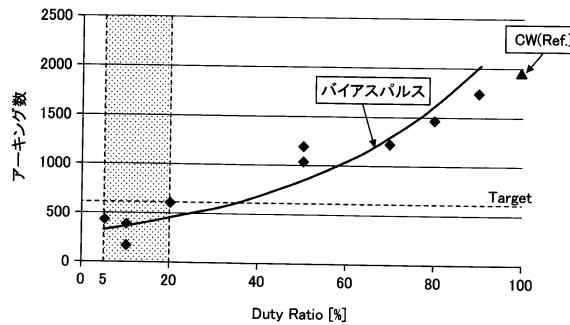

図6(a)に示すように、エッティングが進むにつれ電子シェーディング効果によりエッ

50

チングパターンの底部に正電荷のイオンが溜まる。例えば、図6(b)に示すように、エッチングパターンの底部が、ポリシリコンの浮遊電極30から距離dよりも近付くと、浮遊電極30と導電層10との間に電位差Vが生じ、アーキングが発生するとする。

#### 【0037】

本実施形態では、図5(c)のグラフが示す結果を利用して、図6(c)に示すように、エッチングパターンの底部が、浮遊電極30から距離dの位置に到達すると、高周波電力LFを連続波からパルス波に切り替え、バイアスパルスを用いたエッチングを行う。このようにして、高周波電力HF及び高周波電力LFのいずれも連続波の高周波を印加する第1ステップ(Step1)から、高周波電力HFは連続波であって高周波電力LFはパルス波の高周波を印加する第2ステップ(Step2)に切り替える。これによりアーキングを抑制可能なエッチング方法を実現できる。なお、バイアスパルスに切り替えるタイミングの指標である浮遊電極30からの距離dは、実験により予め定められている。10

#### 【0038】

##### [エッチング処理]

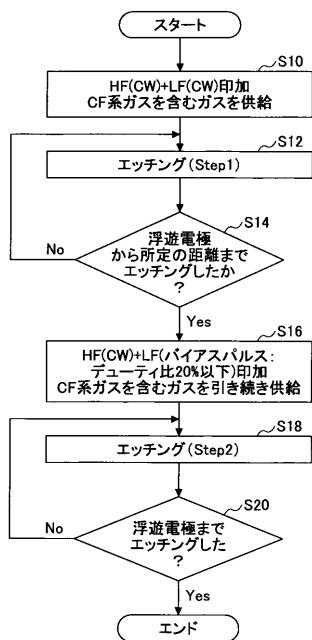

次に、本実施形態に係るエッチング処理について、図7を参照しながら説明する。図7は、一実施形態に係るエッチング処理の一例を示すフローチャートである。本エッチング処理は、図4に示す3D-NAND構造が形成されたウェハWに対するエッチング加工において適用される。本エッチング処理の制御は、制御部100により行われる。

#### 【0039】

本処理が開始されると、制御部100は、連続波(CW)の高周波電力HF及び連続波(CW)の高周波電力LFを下部電極21に印加する(ステップS10)。また、制御部100は、CF系ガスを含むガスを処理容器2内に供給する(ステップS10)。本実施形態では、CF系ガスを含むガスの一例として、C<sub>4</sub>F<sub>6</sub>ガス、COガス及びO<sub>2</sub>ガスの混合ガスが処理容器2内に供給される。これにより、前記混合ガスからプラズマが生成される。20

#### 【0040】

次に、制御部100は、生成されたプラズマにより、図4に示す積層膜60及びシリコン酸化膜20を並行してエッチングする(ステップS12:Step1)。ステップS12のエッチングのプロセス条件は、前記の<プロセス条件:LF連続波の場合>に記載した通りである。これによれば、Step1のエッチングでは、高周波電力HFと高周波電力LFのいずれも連続波にすることで、イオンの引き込み力により高いエッチングレートでエッチングを促進することができる。30

#### 【0041】

次に、制御部100は、浮遊電極30から所定の距離dになるまでエッチングしたかを判定する(ステップS14)。制御部100は、浮遊電極30から所定の距離dになるまでステップS12、S14を繰り返す。

#### 【0042】

制御部100は、浮遊電極30から所定の距離dになるまでエッチングが進んだと判定すると、次に、制御部100は、連続波(CW)の高周波電力HF及びDuty比が20%以下のパルス波(バイアスパルス)の高周波電力LFを下部電極21に印加する(ステップS16)。また、制御部100は、CF系ガスを含むガスとして、引き続きC<sub>4</sub>F<sub>6</sub>ガス、COガス及びO<sub>2</sub>ガスの混合ガスを処理容器2内に供給する。なお、制御部100は、ステップS16において、Duty比が5%以上のバイアスパルスの高周波電力LFを下部電極21に印加することが好ましい。40

#### 【0043】

次に、制御部100は、生成されたプラズマにより、図4に示す積層膜60及びシリコン酸化膜20を引き続きエッチングする(ステップS18:Step2)。ステップS18のエッチングのプロセス条件は、前記の<プロセス条件:LFパルス波の場合>に記載した通りである。これによれば、切替後のStep2のエッチングでは、高周波電力HFを連続波にし、高周波電力LFをパルス波にすることで、エッチングパターンのチ50

ヤージをキャンセルすることができる。

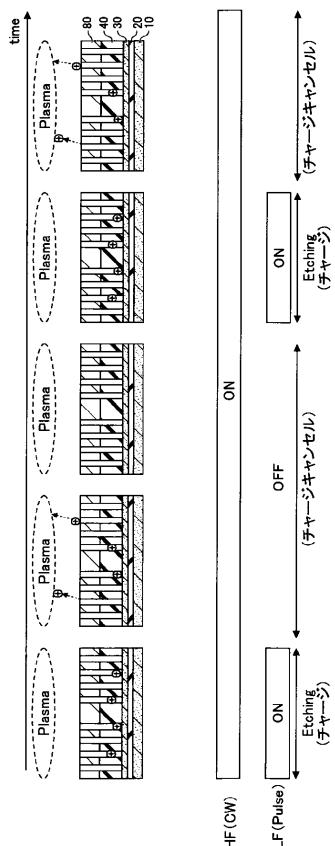

**【0044】**

図9に示すように、高周波電力HF及び高周波電力LFがオンの間にエッティングパターンの底部にチャージされた正の電荷（イオン）は、高周波電力LFがオフの間にエッティングパターンの底部からプラズマに放出され、チャージキャンセルされる。この繰り返しにより、アーキングの発生を抑制できる。

**【0045】**

次に、制御部100は、浮遊電極30までエッティングしたかを判定する（ステップS20）。制御部100は、浮遊電極30までエッティングしていないと判定した場合、ステップS18に戻り、Step2のエッティングを続ける。ステップS20において、制御部100は、浮遊電極30までエッティングしたと判定した場合、本処理を終了する。

10

**【0046】**

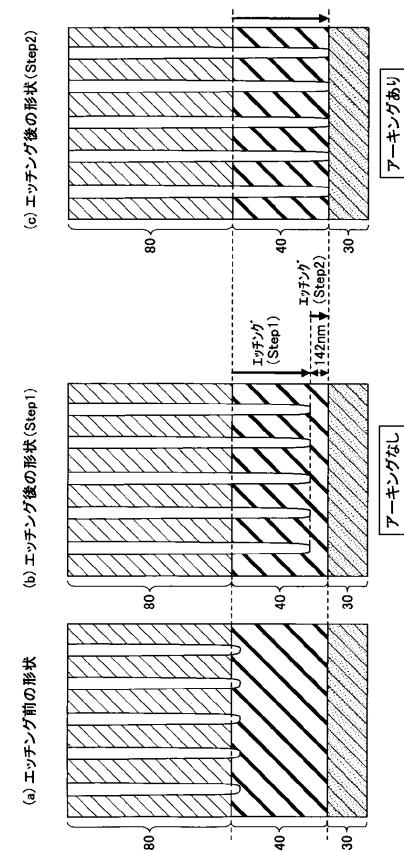

本実施形態に係るエッティング方法では、ステップS12のエッティングにおいていずれも連続波の高周波電力HF及び高周波電力LFを印加することで、エッティングを促進する。これにより、図8（b）及び図8（c）にエッティング処理結果のパターンの一例を示すように、図8（a）に示す初期状態のカーボン膜80のパターンにシリコン酸化膜40がエッティングされる。図8では、シリコン酸化膜40とシリコン窒化膜50の積層膜60の替わりに、シリコン酸化膜40がエッティング対象膜となっている。

**【0047】**

図8（b）に示すとおり、連続波の高周波電力HF及び高周波電力LFを印加することによってシリコン酸化膜40の途中までエッティングした場合、アーキングは発生しなかった。このとき、浮遊電極30からエッティングされたシリコン酸化膜40の深さまでの距離が142nmであった。続いて、図8（c）に示すように、図8（b）から引き続き、エッティングされたシリコン酸化膜40の深さが浮遊電極30まで到達し、浮遊電極30が露出するまでエッティングした場合であり、この時、アーキングの発生が確認された。これは、連続波の高周波電力HF及び高周波電力LFを印加した場合、エッティング中にエッティングパターンの底部のチャージをキャンセルすることができず、アーキングが発生し、シェーディングダメージが生じたものと考えられる。

20

**【0048】**

のことから、ステップS12のエッティングによって浮遊電極30から所定の距離d（図8（b）では、142nm）までエッティングを行い、続いて、ステップS12のエッティングからステップS18に切り替え、Duty比が20%以下のバイアスパルスの高周波電力LFが下部電極21に印加したエッティングを行うことによって、エッティング対象膜のパターンの底部のチャージをキャンセルし、アーキングを発生させずに（または、アーキング数をターゲットとなる個数以下にして）、エッティングを完了することができる。

30

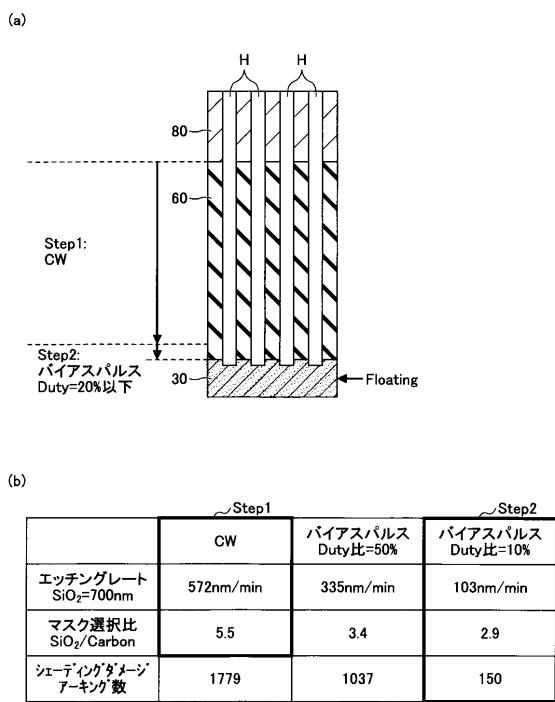

**【0049】**

エッティングレートとシェーディングダメージとはトレードオフの関係にある。例えば、図10（b）には、図10（a）に示す構造の浮遊電極30の上層に形成された積層膜60をエッティングしたときの結果の一例を示す。

**【0050】**

第1ステップ（Step1）のエッティングにおいて、連続波の高周波電力HF及び連続波の高周波電力LFを印加したときの積層膜60のエッティングレートは「572nm/m in」、カーボン膜80に対する積層膜60のマスク選択比は「5.5」であった。

40

**【0051】**

これに対して、第2ステップ（Step2）のエッティングにおいて、連続波の高周波電力HF及びパルス波の高周波電力LFを印加したときの積層膜60のエッティングレートは「103nm/m in」、カーボン膜80に対する積層膜60のマスク選択比は「2.9」といずれも低くなった。特にエッティングレートは第1ステップのエッティングレートの約1/5であった。しかしながら、このときのシェーディングダメージ（アーキング数）は、150であり、第1ステップのシェーディングダメージ（アーキング数：1779）の約1

50

/ 12 であった。

#### 【0052】

以上から、第1ステップのエッティング時間に対する第2ステップのエッティング時間を長くする程、トータルのエッティングレートが下がり、エッティング特性が低下するため、アーキングが生じない最大限の深さまで第1ステップのエッティングを行うことが好ましい。つまり、浮遊電極からの距離を示す所定の距離dは、帯電しても十分な耐圧が保てる膜厚であって、アーキングが生じない最小限の距離に設定されることが好ましい。

#### 【0053】

本実施形態によれば、エッティング工程を第1ステップ及び第2ステップの2ステップに切り替えて実行し、第2ステップでは Duty 比が 5 % 以上 20 % 以下のバイアスパルスの高周波電力 LF を印加する。これにより、エッティングパターンの底部のチャージをキャンセルしながらエッティングを行うことができる。この結果、エッティングレート等、所定のエッティング特性を維持しつつ、アーキングを抑制することができる。また、浮遊電極からの所定の距離をアーキングが生じない最小限の深さに設定し、浮遊電極からの所定の距離にならば、第1ステップから第2ステップに切り替える。これにより、エッティングレート及び選択比等のエッティング特性を所定の程度に維持しつつ、アーキングを抑えることができる。

10

#### 【0054】

##### [変形例]

以上、3D-NAND構造の浮遊電極30の上層に形成された積層膜60をエッティングするエッティング方法について説明した。しかしながら、本実施形態に係るエッティング方法は、3D-NAND構造に限定されず、接地電位となる導電層と対向する浮遊電位の電極層の上層に形成されたシリコン含有膜をエッティングする方法に適用することができる。つまり、本実施形態に係るエッティング方法は、絶縁膜の中に電気的にフローティングした電極がある構造において絶縁膜のエッティングに適用されることが好ましい。

20

#### 【0055】

シリコン含有膜は、SiO<sub>2</sub>、SiN、SiO<sub>2</sub>とSiNの積層膜の他、SiC、SiCN、SiCO、SiOCH等の炭素含有シリコン酸化膜や炭素含有シリコン窒化膜、炭素含有シリコン酸化膜と炭素含有シリコン窒化膜との積層膜であってもよい。

#### 【0056】

30

また、例えば、接地電位となる導電層としては、Poly-Si(ポリシリコン)に限らず、シリコン(Si)の単結晶やボロン等がドープされたシリコンであってもよい。

#### 【0057】

なお、マスクとして、本実施形態ではカーボン膜80を例に挙げたが、これに限らず、Poly-Si、W(タンゲステン)、TiN、有機系のマスクであってもよい。

#### 【0058】

上記実施形態の第1ステップでは、連続波の高周波電力HFと連続波の高周波電力LFとを供給し、シリコン含有膜をエッティングした。しかしながら、これに限らず、第1ステップでは、連続波の高周波電力HFと、Duty比が50 % 以上のパルス波の高周波電力LFとを供給し、シリコン含有膜をエッティングしてもよい。

40

#### 【0059】

また、上記実施形態では、高周波電力LFがパルス波の場合、10 kHz ~ 50 kHzの範囲のいずれかのパルス周波数の高周波電力LFを印加したが、これに限らず、高周波電力LFがパルス波の場合、そのパルス周波数は、0.1 kHz ~ 50 kHzの範囲であればよい。

#### 【0060】

以上、エッティング方法及びエッティング処理装置を上記実施形態により説明したが、本発明にかかるエッティング方法及びエッティング処理装置は上記実施形態に限定されるものではなく、本発明の範囲内で種々の変形及び改良が可能である。上記複数の実施形態に記載された事項は、矛盾しない範囲で組み合わせることができる。

50

**【 0 0 6 1 】**

本発明に係る基板処理装置は、Capacitively Coupled Plasma(CCP), Inductively Coupled Plasma(ICP), Radial Line Slot Antenna, Electron Cyclotron Resonance Plasma(ECR), Helicon Wave Plasma(HWP)のどのタイプでも適用可能である。

**【 0 0 6 2 】**

本明細書では、基板の一例として半導体ウェハWを挙げて説明した。しかし、基板は、これに限らず、LCD(Liquid Crystal Display)、FPD(Flat Panel Display)に用いられる各種基板や、フォトマスク、CD基板、プリント基板等であっても良い。

**【 符号の説明 】****【 0 0 6 3 】**

1 : エッチング処理装置

10

2 : 処理容器

1 0 : 導電層(シリコン基板)

1 1 : ガス供給部

2 0 : シリコン酸化膜

2 1 : 下部電極(載置台)

2 2 : 上部電極

3 0 : 浮遊電極

3 2 : 第1高周波電源

20

3 4 : 第2高周波電源

4 0 : シリコン酸化膜

4 5 : ガス導入口

5 0 : シリコン窒化膜

5 1 : 拡散室

6 0 : 積層膜

6 5 : 排気装置

8 0 : カーボン膜

1 0 0 : 制御部

【図1】

(a) 3D NAND構造

(b) 3D NAND構造

【図2】

【図3】

【図4】

【図5】

(c)

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(51)Int.Cl. F I

H 01L 29/792 (2006.01)

H 05H 1/46 (2006.01)

(56)参考文献 特開2002-184869(JP,A)

特開平08-139077(JP,A)

特開平08-241885(JP,A)

特開2010-272649(JP,A)

特表2002-532899(JP,A)

国際公開第2014/069559(WO,A1)

特開2013-033856(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 01L 21/302

H 01L 21/3065

H 01L 21/3205 - 21/3213

H 01L 21/336

H 01L 21/461

H 01L 21/768

H 01L 23/522

H 01L 23/532

H 01L 29/76

H 01L 29/772

H 01L 29/78

H 01L 29/788 - 29/792

H 05H 1/00 - 1/54