(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5379418号

(P5379418)

(45) 発行日 平成25年12月25日(2013.12.25)

(24) 登録日 平成25年10月4日(2013.10.4)

(51) Int.Cl.

F 1

|              |           |

|--------------|-----------|

| HO1L 21/66   | (2006.01) |

| HO1L 21/3205 | (2006.01) |

| HO1L 21/768  | (2006.01) |

| HO1L 23/522  | (2006.01) |

| HO1L 21/822  | (2006.01) |

|            |

|------------|

| HO1L 21/66 |

| HO1L 21/88 |

| HO1L 27/04 |

|   |

|---|

| Y |

| Z |

| T |

請求項の数 5 (全 19 頁) 最終頁に続く

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2008-187486 (P2008-187486) |

| (22) 出願日     | 平成20年7月18日 (2008.7.18)       |

| (65) 公開番号    | 特開2009-27169 (P2009-27169A)  |

| (43) 公開日     | 平成21年2月5日 (2009.2.5)         |

| 審査請求日        | 平成23年7月15日 (2011.7.15)       |

| (31) 優先権主張番号 | 10-2007-0071708              |

| (32) 優先日     | 平成19年7月18日 (2007.7.18)       |

| (33) 優先権主張国  | 韓国 (KR)                      |

|           |                                                                                                                                                                 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 390019839<br>三星電子株式会社<br>Samsung Electronics<br>Co., Ltd.<br>大韓民国京畿道水原市靈通区三星路 129<br>129, Samsung-ro, Yeongtong-gu, Suwon-si, Gyeonggi-do, Republic<br>of Korea |

| (74) 代理人  | 100093779<br>弁理士 服部 雅紀                                                                                                                                          |

| (72) 発明者  | 鄭 世泳<br>大韓民国京畿道龍仁市器興区上葛洞 459<br>-2番地 304 号                                                                                                                      |

最終頁に続く

(54) 【発明の名称】半導体装置のテスト構造物

## (57) 【特許請求の範囲】

## 【請求項 1】

基板の第1アクティブ領域上に形成され、第1方向に延長される第1ゲートラインを含むトランジスタと、

前記基板の第2アクティブ領域上に形成され、前記トランジスタに接続されたダミートランジスタと、

前記トランジスタに接続されたパッドユニットと、

前記第1方向に延長される第2ゲートラインと、

を備え、

前記ダミートランジスタは、複数個形成され、前記第2アクティブ領域上に形成され前記第1ゲートラインと接続されるダミーゲートラインを含み、

前記第2ゲートラインは、前記第1方向に対して実質的に垂直である第2方向に延長された第1導電性ラインによって前記第1ゲートラインと接続される半導体装置のテスト構造物。

## 【請求項 2】

複数個の前記第2ゲートラインは、前記第2方向に前記第1ゲートラインと一定の間隔で離隔して形成されることを特徴とする請求項1記載の半導体装置のテスト構造物。

## 【請求項 3】

前記トランジスタは、複数個形成されることを特徴とする請求項1記載の半導体装置のテスト構造物。

10

20

**【請求項 4】**

前記トランジスタは、前記第1ゲートラインに隣接した前記第1アクティブ領域の上部に形成されたソース領域及びドレイン領域を備え、

前記基板は、ウェル領域が形成された第3アクティブ領域をさらに含み、

前記パッドユニットは、前記第1ゲートライン、前記ソース領域、前記ドレイン領域、及び前記ウェル領域に各々接続されたゲートパッド、ソースパッド、ドレインパッド、及びバルクパッドを含むことを特徴とする請求項1記載の半導体装置のテスト構造物。

**【請求項 5】**

前記ダミートランジスタは、前記トランジスタが受けるプラズマダメージを減少させる機能を有することを特徴とする請求項1記載の半導体装置のテスト構造物。 10

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体装置のテスト構造物、その形成方法に関する。より詳しくは、本発明はダミー (dummy) トランジスタを有する半導体装置のテスト構造物、その形成方法に関する。

**【背景技術】****【0002】**

半導体装置を製造するにあたって、フォトリソグラフィー (photolithography) 技術は必須的である。前記フォトリソグラフィー技術は、プラズマエッチング工程、反応性イオンエッチング工程などのエッチング工程を含む。半導体装置が高集積化されることにより、狭い線幅を有する各種構造物を形成するために、高密度プラズマエッチング工程のようなプラズマエッチング工程が幅広く使われている。しかし、高密度プラズマの使用により、基板とゲートの間に強い電界が形成され、これはゲート絶縁膜に深刻なダメージを発生させる。これによって、前記ゲート絶縁膜を含む半導体装置の信頼性が低下される。 20

**【0003】**

他方、半導体装置のスレッショルド電圧、トランスクンダクタンス、漏洩電流などの各種の特性を評価するために、前記半導体装置が形成される基板のスクリーブレーン (scribe lane) 領域にテスト素子グループ (Test Element Group : TEG) パターンのようなテスト構造物を形成している。前記TEGパターンも、やはりプラズマエッチング工程を通じて形成され、これにより前記TEGパターンに含まれたゲート絶縁膜もプラズマダメージ (plasma induced damage) を受けることになる。 30

**【0004】**

特に、半導体装置のスレッショルド電圧を測定するためのTEGパターンの場合、複数のゲートラインの内、1つのゲートラインにトランジスタが形成され、これによって前記ゲートライン形成の後、遂行されるプラズマを使用する各種エッチング工程によりプラズマダメージが前記トランジスタに集中される。これは前記半導体装置のスレッショルド電圧測定の正確度を落とすことになる。 40

**【発明の開示】****【発明が解決しようとする課題】****【0005】**

本発明の目的は、トランジスタが減少されたプラズマダメージを受けるように設計された半導体装置のテスト構造物を提供することである。

**【0006】**

本発明の他の目的は、トランジスタが減少されたプラズマダメージを受けるように設計された半導体装置のテスト構造物の形成方法を提供することである。

**【課題を解決するための手段】****【0009】**

10

20

30

40

50

前述の本発明の目的を達成するために、本発明の態様による半導体装置のテスト構造物は、トランジスタ、ダミートランジスタ、及びパッドユニットを備える。前記トランジスタは、基板の第1アクティブ領域上に形成される。前記ダミートランジスタは、前記基板の第2アクティブ領域上に形成され、前記トランジスタに接続される。前記パッドユニットは、前記トランジスタに接続される。

【0010】

本発明の一態様によると、前記ダミートランジスタは複数個形成される。

【0011】

本発明の一態様によると、前記ダミートランジスタは、前記第2アクティブ領域上に形成されたダミーゲートラインを含むことができる。このとき、前記トランジスタは第1ゲートラインを備え、前記ダミーゲートラインは前記第1ゲートラインと接続されることができる。10

【0012】

本発明の一態様によると、前記第1ゲートラインは第1方向に延長され、前記半導体装置のテスト構造物は前記第1方向に延長され、前記第1方向と実質的に垂直である第2方向に前記第1ゲートラインと一定の間隔で離隔し、形成された1つ以上の第2ゲートラインをさらに含むことができる。このとき、前記第2ゲートラインは、前記第1方向に対し

て実質的に垂直である第2方向に延長された第1導電性ラインによって前記第1ゲート

ラインと接続されることができる。20

【0013】

本発明の一態様によると、前記トランジスタは複数個形成することができる。

【0014】

本発明の一態様によると、前記トランジスタは、前記第1アクティブ領域上に形成されたゲートライン、前記ゲートラインに隣接した前記第1アクティブ領域の上部に形成されたソース領域及びドレイン領域を備え、前記基板はウェル領域が形成された第3アクティブ領域をさらに含み、前記パッドユニットは前記ゲートライン、前記ソース領域、前記ドレイン領域、及び前記ウェル領域に各々接続されたゲートパッド、ソースパッド、ドレインパッド、及びバルクパッドを含むことができる。このとき、前記半導体装置のテスト構造物は、前記ゲートパッド、前記ソースパッド、前記ドレインパッド、及び前記バルクパッドに電気的信号を印加して前記トランジスタのスレッショルド電圧を測定することができる。30

【0015】

本発明の一態様によると、前記ダミートランジスタは、前記トランジスタが受けるプラズマダメージ (plasma induced damage) を減少させることができる。

【0016】

前述の本発明の他の目的を達成するために、本発明の態様による半導体装置テスト構造物の形成方法においては、基板に第1アクティブ領域及び第2アクティブ領域が形成される。前記第1アクティブ領域上にトランジスタが形成され、前記第2アクティブ領域上に前記トランジスタと接続されるダミートランジスタが形成される。前記トランジスタに接続されるパッドユニットが形成される。40

【0017】

本発明の一態様によると、前記ダミートランジスタは複数個形成することができる。

【0018】

本発明の一態様によると、前記ダミートランジスタを形成する時、前記第2アクティブ領域上にダミーゲートラインが形成されることがある。前記トランジスタを形成するとき、前記第1アクティブ領域上に第1ゲートラインが形成されることが可能、前記ダミーゲートラインは前記第1ゲートラインに接続されるように形成されることがある。

【0019】

本発明の一態様によると、前記第1ゲートラインは第1方向に延長して形成され、前記

50

第1方向に延長されて前記第1方向と実質的に垂直する第2方向に前記第1ゲートラインと一定の間隔で離隔されるように1つ以上の第2ゲートラインがさらに形成されることができる。この時、前記第2ゲートラインは前記第1ゲートラインと接続されるように形成されることができる。

【0020】

本発明の一態様によると、前記トランジスタは複数個形成されることがある。

【0021】

本発明の一態様によると、前記第1アクティブ領域及び第2アクティブ領域を形成するとき、前記基板に第3アクティブ領域が形成されることができ、前記第3アクティブ領域を形成した後、前記第3アクティブ領域にウェル領域が形成されることができ、前記トランジスタを形成するとき、前記第1アクティブ領域上にゲートラインが形成され、前記ゲートラインに隣接する前記アクティブ領域上部にソース領域及びドレイン領域が形成されることがある。

10

【0022】

本発明の一態様によると、前記パッドユニットを形成するとき、前記ゲートライン、前記ソース領域、前記ドレイン領域、及び前記ウェル領域に各々接続されたゲートパッド、ソースパッド、ドレインパッド、及びバルクパッドが形成されることがある。

【0023】

前述の本発明のさらに他の目的を達成するために、本発明の態様による半導体装置は、トランジスタ及びダミートランジスタを具備する。前記トランジスタは、基板の第1アクティブ領域上に形成される。前記ダミートランジスタは前記基板の第2アクティブ領域上に形成され、前記トランジスタに接続される。

20

【0024】

本発明の一態様によると、前記ダミートランジスタは複数個形成されることがある。

【0025】

本発明の一態様によると、前記ダミートランジスタは、前記第2アクティブ領域上に形成されたダミーゲートラインを含むことができる。このとき、前記トランジスタはゲートラインを備え、前記ダミーゲートラインは前記ゲートラインと接続されることがある。

【0026】

本発明の一態様によると、前記ダミートランジスタは前記トランジスタが受けるプラズマダメージを減少させることができる。

30

【0027】

前述の本発明のさらに他の目的を達成するために、本発明の態様による半導体装置の製造方法においては、基板に第1アクティブ領域及び第2アクティブ領域が形成される。前記第1アクティブ領域上にトランジスタを形成し、前記第2アクティブ領域上に前記トランジスタと接続されるダミートランジスタが形成される。

【0028】

本発明の一態様によると、前記ダミートランジスタは複数個形成されることがある。

【0029】

本発明の一態様によると、前記ダミートランジスタを形成する時、前記第2アクティブ領域上にダミーゲートラインが形成されることがある。

40

【0030】

本発明の一態様によると、前記トランジスタを形成するとき、前記第1アクティブ領域上にゲートラインが形成され、前記ダミーゲートラインは前記ゲートラインに接続されるように形成されることがある。

【発明の効果】

【0031】

本発明によると、半導体装置のテスト構造物は、スレッショルド電圧のような素子特性を測定するトランジスタのみでなく、ダミートランジスタを共に具備している。これにより、プラズマを使用するエッチング工程により前記トランジスタのゲートラインが受けける

50

プラズマダメージが前記ダミートランジスタのダミーゲートラインに分散される。従って、前記半導体装置のテスト構造物は前記トランジスタのスレッショルド電圧などの素子特性がより正確に測定できる。

**【発明を実施するための最良の形態】**

**【0033】**

以下、本発明の実施の形態を図面に基づいて説明する。本発明の実施の形態による半導体装置のテスト構造物、その形成方法、半導体装置、及びこれの製造方法について詳細に説明するが、本発明が後述の実施例に制限されることはなく、本発明が属する技術分野において通常の知識を有するものであれば本発明の技術的思想の範囲内で、本発明が多様な形態で具現できる。添付図面において、基板、層（膜）、領域、パターン、又は構造物のサイズは本発明の明確性を期するために実際より拡大して図示したものである。本発明において、各層（膜）、領域、電極、パターン、又は構造物が基板、各層（膜）、領域、電極、構造物、又はパターンの「上に」、「上部に」、又は「下部に」形成されることと言及される場合には各層（膜）、領域、電極、パターン、又は構造物が直接的に基板、各層（膜）、領域、構造物、又はパターンの上に形成されるか或いは下に位置することを意味するか、他の層（膜）、他の領域、他の電極、他のパターン、又は他の構造物が基板上に追加的に形成されることができる。また、物質、層（膜）、領域、電極、パターン、又は構造物が「予備」、「第1」、「第2」、「第3」、及び／又は「第4」と言及される場合、このような部材を限定するためではなく、ただ各物質、層（膜）、領域、電極、パターン、又は構造物を区分するためである。よって、「予備」、「第1」、「第2」、「第3」、及び／又は「第4」は、各層（膜）、領域、電極、パターン、又は構造物について各々選択的に、又は交換可能に使用されることができる。

10

**【0034】**

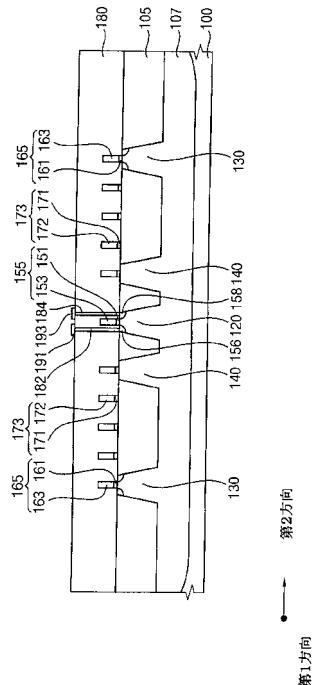

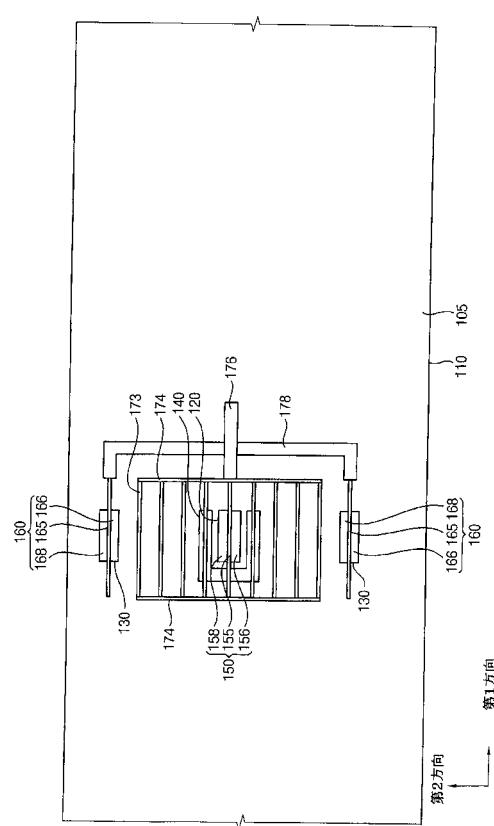

図1は本発明の一実施形態による半導体装置のテスト構造物を説明するための平面図で、図2は図1でI-I'線に沿って切断した断面図である。

**【0035】**

図1及び図2を参照すると、半導体装置のテスト構造物は、基板100のスクライブレーン（scribe lane）領域110上に形成されたトランジスタ150、ダミートランジスタ160及びパッドユニットを具備する。また、前記半導体装置のテスト構造物は複数個の第2ゲートライン172をさらに含むことができる。

20

**【0036】**

基板100は、半導体装置を製造するための半導体基板、或いは、平板表示装置用集積回路を製造するためのガラス基板を含む。前記半導体基板は、シリコン基板、ゲルマニウム基板、シリコン・ゲルマニウム基板、SOI（silicon-on-insulator）基板、GOI（germanium-on-insulator）基板などを含むことができる。基板100は、各種回路パターンを有する図示しないネットダイ（net die）領域及び前記テスト構造物を具備し、前記ネットダイ領域の間に形成されたスクライブレーン領域110に区分される。スクライブレーン領域110には、アライン（align）パターン及びオーバーレイ（overlaid）パターンがさらに形成されることがある。

40

**【0037】**

基板100は、また素子分離膜105が形成されたフィールド領域とアクティブ領域に区分されることができる。素子分離膜105は、シリコン酸化物を含む。前記アクティブ領域は、第1アクティブ領域120、第2アクティブ領域130及び第3アクティブ領域140を含む。

**【0038】**

トランジスタ150は、第1アクティブ領域120上に形成された第1ゲートライン155と、第1ゲートライン155に隣接する第1アクティブ領域120の上部に形成された第1ソース領域156及び第1ドレイン領域158とを含む。

**【0039】**

10

20

30

40

50

第1ゲートライン155は、第1ゲート絶縁膜151及び第1ゲート電極153を具備する。第1ゲート絶縁膜151は、シリコン酸化物或いは金属酸化物を含むことができ、第1ゲート電極153は不純物がドーピングされたポリシリコン、金属及び/又は金属シリサイドを含むことができる。他方、第1ゲートライン155の側壁には、シリコン窒化物或いはシリコン酸化物を含む図示しないゲートスペーサーがさらに形成されることがある。本発明の一実施形態によると、第1ゲートライン155は、第1方向に延長され、第1アクティブ領域120の外側にも一部形成されることがある。

#### 【0040】

第1ソース領域156及び第1ドレイン領域158は、ホウ素、ガリウム、インジウムなどのP型不純物、或いは、リン、ヒ素、アンチモンなどのN型不純物を含むことができる。10

#### 【0041】

トランジスタ150は、前記ネットダイ領域に形成されたセルトランジスタと実質的に同一又は類似の構成を有することができ、トランジスタ150のスレッショルド電圧などの特性を測定することで、前記セルトランジスタの特性が推定できる。

#### 【0042】

他方、図1及び図2にはトランジスタ150が1つのみの形成されているが、場合によって複数個形成されることがある。また、トランジスタ150は各第2ゲートライン173の間のどこにも形成されることが可能、場合によって第2ゲートライン173の外側にも形成されることがある。20

#### 【0043】

第2ゲートライン173は、第2ゲート絶縁膜171及び第2ゲート電極172を具備する。第2ゲート絶縁膜171及び第2ゲート電極172は、各々第1ゲート絶縁膜151及び第1ゲート電極153と実質的に同一物質を含むことができる。また、第2ゲートライン173の各側壁には図示しないゲートスペーサーがさらに形成されることがある。第2ゲートライン173は、前記ネットダイ領域に形成されたゲートラインアレーと実施的に同一又は類似の構成を有するように形成されることがある。本発明の一実施形態によると、第2ゲートライン173、各々は前記第1方向に延長され、前記第1方向と実質的に垂直である第2方向に一定の間隔で離隔して形成される。

#### 【0044】

他方、第2ゲートライン173は、前記第2方向に延長された第1導電性ライン174によって互いに接続されることがある。このとき、第1ゲートライン165も第1導電性ライン174により第2ゲートライン173に接続されることがある。第1導電性ライン174は、第1ゲートライン155及び第2ゲートライン173と実質的に同一の物質を含むことができる。図1においては、前記第1方向に延長された第2ゲートライン173の各両端に第1導電性ライン174が形成されているが、第1導電性ライン174はいずれの片側の端部のみに形成されることがあるか或いは全く形成されないこともできる。

#### 【0045】

ダミートランジスタ160は、第2アクティブ領域130上に形成されたダミーゲートライン165と、ダミーゲートライン165とに隣接する第2アクティブ領域130の上部に形成された第2ソース領域166及び第2ドレイン領域168を含む。40

#### 【0046】

ダミーゲートライン165は、ダミーゲート絶縁膜161及びダミーゲート電極163を具備する。ダミーゲート絶縁膜161及びダミーゲート電極163は、各々第1ゲート絶縁膜151及び第1ゲート電極153と実質的に同一物質を含むことができる。また、ダミーゲートライン165の各側壁には図示しないゲートスペーサーがさらに形成されることがある。本発明の一実施形態によると、ダミーゲートライン165は、前記第1方向に延長され、第2アクティブ領域130の外側にも一部形成されることがある。

#### 【0047】

10

20

30

40

50

第2ソース領域166及び第2ドレイン領域168は、第1ソース領域156及びドレイン領域158と実質的に同一の不純物を含むことができる。

【0048】

ダミートランジスタ160は、トランジスタ150と実質的に同一又は類似の構成を有することができるが、後述のソースパッド192、ドレインパッド194、及びバルクパッド198には接続されない。即ち、ソースパッド192、ドレインパッド194、ゲートパッド196、及びバルクパッド198に接続されることで、一定の電気的信号が印加されるトランジスタ150とは違ってスレッショルド電圧などのトランジスタの特性が測定されない。

【0049】

他方、図1及び図2にはダミートランジスタ160が2つに形成されているが、場合によっては1つのみ形成されるか或いは3つ以上の複数個に形成されることができる。また、1つの第2アクティブ領域130に2つ以上のダミーゲートライン165を形成して、ダミーゲートライン165をさらに含むダミートランジスタ160が複数個形成できる。また、ダミートランジスタ160は第2ゲートライン173の外側に形成されるのみでなく、各第2ゲートライン173の間にも形成されることができる。

【0050】

ダミートランジスタ160は、トランジスタ150と接続され、本発明の一実施形態によると、ダミーゲートライン165が第1ゲートライン155と接続される。図1において、ダミーゲートライン165と第1ゲートライン155とは第1導電性ライン174、第2導電性ライン176、及び第3導電性ライン178により互いに接続されている。このとき、第2導電性ライン176及び第3導電性ライン178は、第1導電性ライン174と実質的に同一物質を含むことができる。

【0051】

これにより、後続工程で発生するプラズマダメージがトランジスタ150のみでなく、ダミートランジスタ160にも影響を及ぼし、これは結局トランジスタ150が受けるプラズマダメージを分散させる効果を有する。

【0052】

前記パッドユニットは、ソースパッド192、ドレインパッド194、ゲートパッド196、及びバルクパッド198を含む。ソースパッド192、ドレインパッド194、ゲートパッド196、及びバルクパッド198は、金属及び/又は金属窒化物のような導電性物質を含むことができる。ソースパッド192、ドレインパッド194、ゲートパッド196、及びバルクパッド198は、層間絶縁膜180上に形成される。

【0053】

層間絶縁膜180は、トランジスタ150、ダミートランジスタ160、第2ゲートライン173、第1導電性ライン174、第2導電性ライン176、及び第3導電性ライン178を覆いつつ基板100上に形成される。層間絶縁膜180は、酸化物、窒化物及び/又は酸窒化物を含むことができる。

【0054】

ソースパッド192は、層間絶縁膜180上に形成されたソースパッド接続ライン191及び層間絶縁膜180を貫通する第1プラグ182を通じて第1ソース領域156と接続される。ドレインパッド194は、層間絶縁膜180上に形成されたドレインパッド接続ライン193及び層間絶縁膜180を貫通する第2プラグ184を通じて第1ドレイン領域158と接続される。ゲートパッド196は、層間絶縁膜180を貫通する第3プラグ186を通じて第2導電性ライン176と接続され、第1ゲートライン155と接続される。バルクパッド198は、層間絶縁膜180上に形成されたバルクパッド接続ライン197及び層間絶縁膜180を貫通する第4プラグ188を通じて第3アクティブ領域140と接続される。このとき、ソースパッド接続ライン191、ドレインパッド接続ライン193、バルクパッド接続ライン197、第1プラグ182、第2プラグ184、第3プラグ186、及び第4プラグ188は、金属及び/又は金属窒化物のような導電性物質

10

20

30

40

50

を含むことができる。

**【0055】**

第3アクティブ領域140は、スクライブレーン領域110の一部に形成される。本発明の一実施形態によると、第3アクティブ領域140は、第1アクティブ領域120の周辺に形成される。第3アクティブ領域140は、基板100の一部に形成されたウェル(well)領域107に電気的信号を印加する一種の通路の役割ができる。即ち、バルクパッド198に印加された電気的信号は、バルクパッド接続ライン197、第4プラグ188、及び第3アクティブ領域140を経てウェル領域107に印加できる。ウェル領域107は、P型或いはN型不純物を含むことができる。

**【0056】**

他方、ソースパッド192、ドレインパッド194、ゲートパッド196、及びバルクパッド198の順番又は位置は変更が可能である。

**【0057】**

図示はしていないが、前述の各種パターン以外に、ピットライイン或いはコンデンサー、各種配線がさらに形成できる。

**【0058】**

前述の構成を有する半導体装置のテスト構造物は、スレッショルド電圧のような素子特性を測定して前記ネットダイ領域に形成された素子特性を推定するためのトランジスタ150のみでなく、ダミートランジスタ160と共に具備している。これによって、プラズマを使用するエッチング工程によりトランジスタ150の第1ゲートライイン155が受けけるプラズマダメージがダミートランジスタ160のダミーゲートライイン165に分散されて、前記半導体装置のテスト構造物はトランジスタ150のスレッショルド電圧などの素子特性がより正確に測定できる。

**【0059】**

図1及び図2において、前記半導体装置のテスト構造物はスクライブレーン領域110に形成されると図示されているが、前記ネットダイ領域に形成されることができ、この場合、前述の本発明の特徴を含む半導体装置のテスト構造物であるならば、本発明の範囲に属することは当業者にとって自明な事実である。

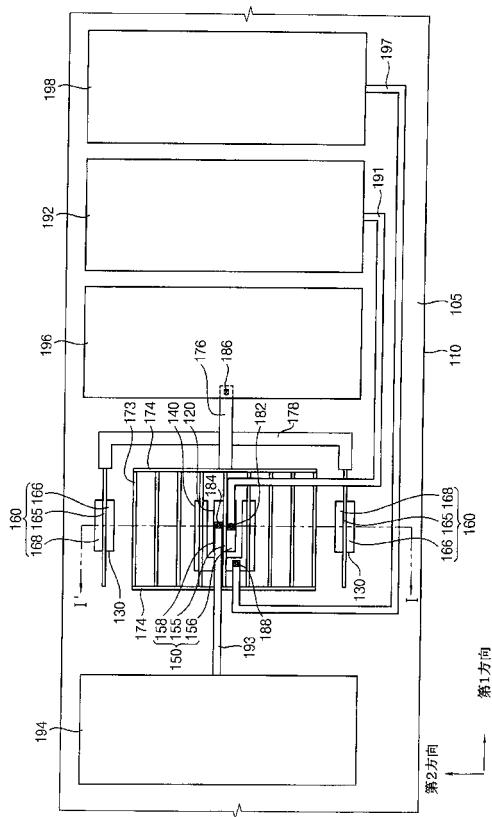

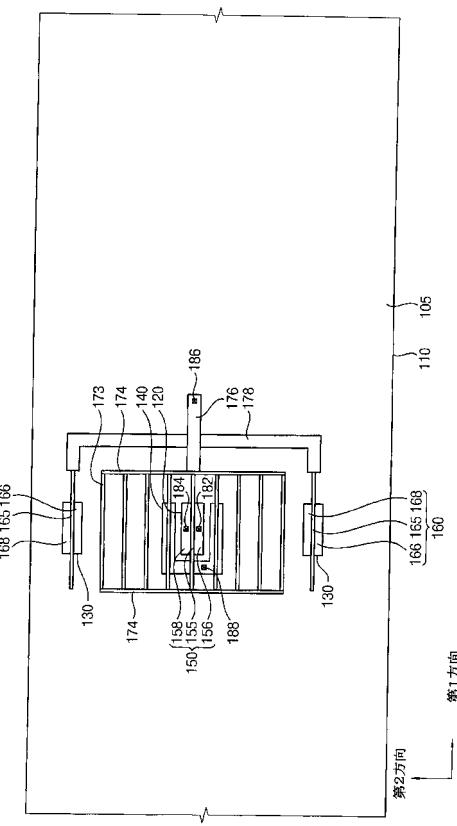

**【0060】**

図3は、本発明の他の実施形態による半導体装置のテスト構造物を説明するための平面図である。図3に図示された半導体装置のテスト構造物は、図1に図示された半導体装置のテスト構造物と比較した場合、第3導電性ラインがないということを除いては実質的に同一であるか類似である。これによって同一の構成要素には同一の参照符号を付け、重複説明を避けるために異なる点についてのみ説明する。

**【0061】**

図3を参照すると、ダミートランジスタ160のダミーゲートライイン165は、第1導電性ライン174によってトランジスタ150の第1ゲートライイン155に接続される。このとき、ダミーゲートライイン165は、第2ゲートライイン173にも接続される。この場合には、図1に図示された半導体装置のテスト構造物とは異なり、第1導電性ライン174は1つ以上形成され、形成されない場合はない。但し、ダミートランジスタ160はトランジスタ150のみに接続されればよいため、第1導電性ライン174はダミーゲートライイン165と第1ゲートライイン155とを接続するように形成されれば十分である。即ち、第2方向に順次に第1ゲートライイン155、ダミーゲートライイン165、及び第2ゲートライイン173が形成される場合、第1導電性ライン174は第1ゲートライイン155とダミーゲートライイン165の両端或いは一端のみに形成されればよく、第2ゲートライイン173の各両端或いは一端に必ず形成される必要はない。

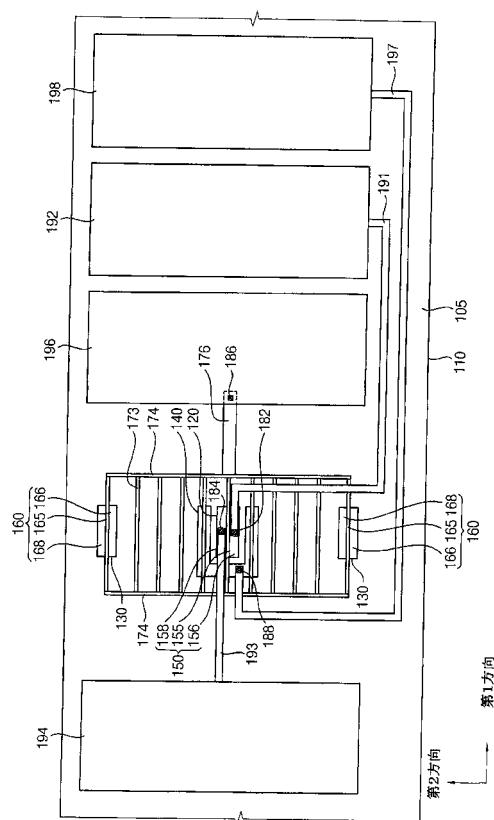

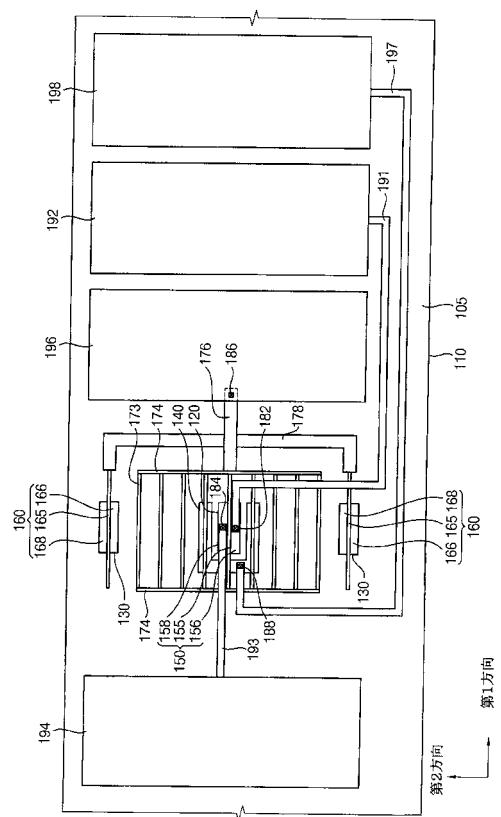

**【0062】**

図4～図7は、本発明の一実施形態による半導体装置のテスト構造物形成方法を説明するための平面図である。図4～図7において、図1に図示したように実質的に同一の構造を有する半導体装置のテスト構造物の形成方法を例示的に説明するが、図4～図7を参照

10

20

30

40

50

しつつ、説明する半導体装置のテスト構造物形成方法がこれに限定されるとは限らない。

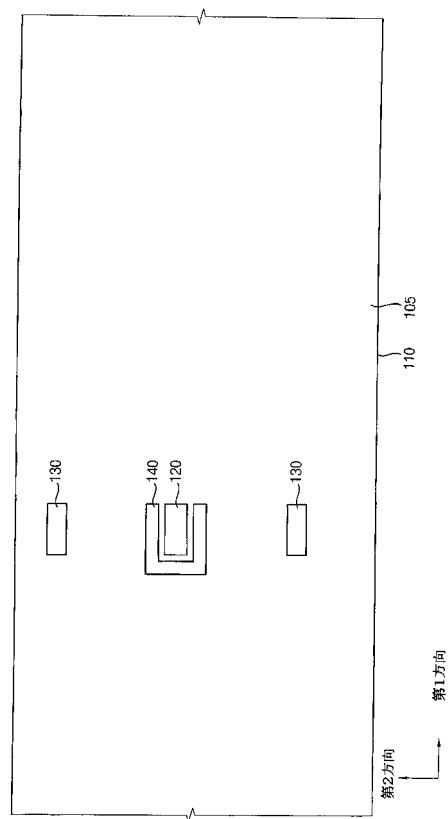

#### 【0063】

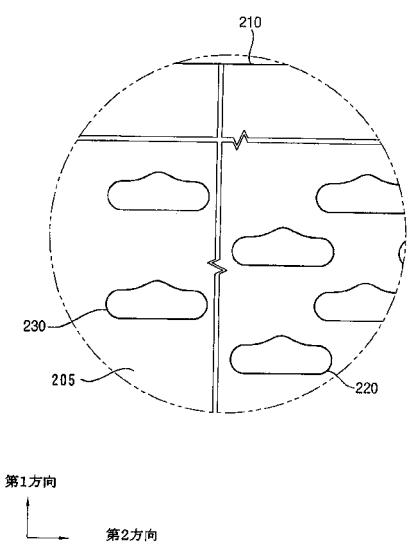

図4を参照すると、図示しない基板のスクライブレーン領域110に第1アクティブ領域120、第2アクティブ領域130、及び第3アクティブ領域140を定義する素子分離膜105を形成する。素子分離膜105は、シャロートレンチ工程(Shallow Trench Isolation: STI)或いはシリコン部分酸化(Local Oxidation of Silicon: LOCOS)工程などの素子分離工程を通じて形成されることがある。その後、前記基板にイオン注入工程を遂行してスクライブレーン領域110にウェル領域107を形成する(図2参照)。

#### 【0064】

他方、図4には第1アクティブ領域120が1つに形成されているが、場合によって複数個形成されることがある。また、第2アクティブ領域130は2つに形成されているが、場合によって1つ或いは3つ以上に形成されることがある。第3アクティブ領域140は第1アクティブ領域120の周辺に逆コ字状に形成されているが、他にも多様な形状を有することもできる。

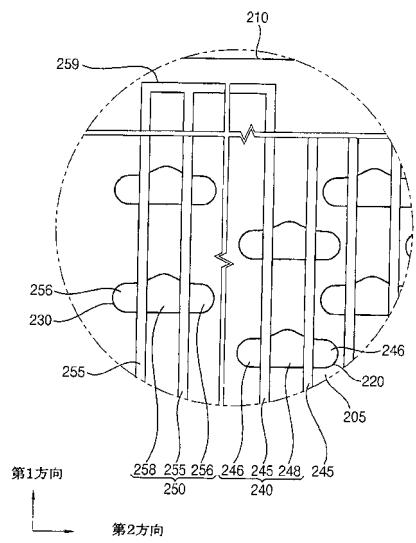

#### 【0065】

図5を参照すると、第1アクティブ領域120及び第2アクティブ領域130上に各々トランジスタ150及びダミートランジスタ160が形成される。また、複数個の第2ゲートライン173、第1導電性ライン174、第2導電性ライン174、及び第3導電性ライン178が形成される。

#### 【0066】

具体的には、スクライブレーン領域110上に図示しない絶縁膜を形成する。前記絶縁膜は、酸化物、窒化物及び/又は酸窒化物を使用して形成されることがある。また、前記絶縁膜は、化学気象蒸着工程、低圧化学気象蒸着工程、プラズマ増大化学気象蒸着工程、高密度プラズマ化学気象蒸着工程などを通じて形成されることがある。

#### 【0067】

前記絶縁膜上に不純物がドーピングされたポリシリコン、金属及び/又は金属シリサイドを使用して第1導電膜を形成する。前記第1導電膜は、化学気象蒸着工程、原子層積層工程、高密度プラズマ化学気象蒸着工程などをを利用して形成されることがある。

#### 【0068】

前記第1導電膜上に図示しないフォトレジストパターンを形成して、前記フォトレジストパターンをエッチングマスクを使用するエッチング工程を通じて前記第1導電膜及び前記絶縁膜の一部を除去することで、第1ゲートライン155、ダミーゲートライン165、第2ゲートライン173、第1導電性ライン174、第2導電性ライン174、及び第3導電性ライン178を形成する。第1ゲートライン155は第1ゲート絶縁膜151及び第1ゲート電極153を具備し、ダミーゲートライン165はダミーゲート絶縁膜161及びダミーゲート電極163を具備し、第2ゲートライン173は第2ゲート絶縁膜171及び第2ゲート電極172を具備する(図2参照)。

#### 【0069】

その後、イオン注入工程を通じて第1アクティブ領域120及び第2アクティブ領域130に不純物を注入する。これにより、第1ゲートライン155に隣接する第1アクティブ領域120上部に第1ソース領域156及び第1ドレイン領域158が形成され、ダミーゲートライン165に隣接する第2アクティブ領域130上部に第2ソース領域166及び第2ドレイン領域168が形成される。第1ゲートライン155、第1ソース領域156、及び第1ドレイン領域158はトランジスタ150を形成し、ダミーゲートライン165、第2ソース領域166、及び第2ドレイン領域168はダミートランジスタ160を形成する。

#### 【0070】

本発明の一実施形態によると、第1ゲートライン155、ダミーゲートライン165、及び第2ゲートライン173は、各々第1方向に延長されるように形成される。また、本

10

20

30

40

50

発明の一実施形態によると、第1ゲートライン165及び第2ゲートライン173は、前記第1方向に実質的に垂直する第2方向に延長された第1導電性ライン174により互いに接続される。他方、第1ゲートライン155とダミーゲートライン165は、第2導電性ライン176及び第3導電性ライン178により互いに接続される。

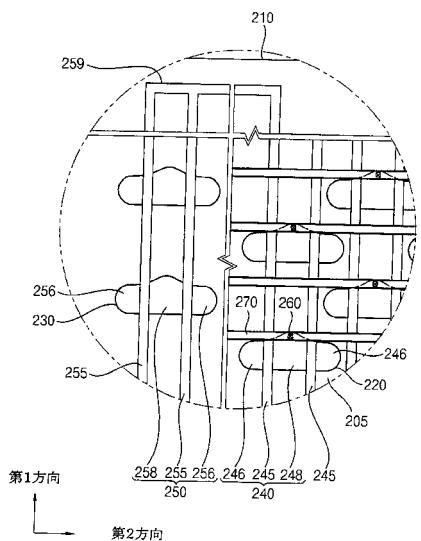

#### 【0071】

図6を参照すると、トランジスタ150、ダミートランジスタ160、第2ゲートライン173、第1導電性ライン174、第2導電性ライン174、及び第3導電性ライン178を覆いつつ、スクリップレーン領域110上に層間絶縁膜180を形成する(図2参照)。層間絶縁膜180は、酸化物、窒化物、及び/又は酸窒化物を使用して形成できる。層間絶縁膜180は、化学気象蒸着工程、低圧化学気象蒸着工程、プラズマ増大化学気象蒸着工程、高密度プラズマ化学気象蒸着工程などを通じて形成されることがある。

10

#### 【0072】

その後、層間絶縁膜180を貫通する第1プラグ182、第2プラグ184、第3プラグ186、及び第4プラグ188を第1ソース領域156、第1ドレイン領域158、第2導電性ライン176、及び第3アクティブ領域140上に各々形成される。

#### 【0073】

具体的に、第1ソース領域156、第1ドレイン領域158、第2導電性ライン176、及び第3アクティブ領域140を部分的に露出させる図示しない開口部を層間絶縁膜180に形成する。その後、金属及び/又は金属窒化物を使用する化学気象蒸着工程、原子層積層工程、高密度プラズマ化学気象蒸着工程などを遂行して前記開口部を埋めるように層間絶縁膜180上に第2導電膜を形成する。化学的、機械的研磨工程及び/又はエッチバック工程を使用して層間絶縁膜180上の前記第2導電膜部分を除去することで、第1ソース領域156、第1ドレイン領域158、第2導電性ライン176、及び第3アクティブ領域140と接続された第1プラグ182、第2プラグ184、第3プラグ186、及び第4プラグ188を形成する。

20

#### 【0074】

図7を参照すると、ソースパッド192、ドレインパッド194、ゲートパッド196、及びバルクパッド198を形成して、各々第1ソース領域156、第1ドレイン領域158、第1ゲートライン165、及び第3アクティブ領域140と接続する。

30

#### 【0075】

具体的には、層間絶縁膜180及び第1プラグ182、第2プラグ184、第3プラグ186、及び第4プラグ188上に第3導電膜を形成する。前記第3導電膜は、金属及び/又は金属窒化物を使用する化学気象蒸着工程、原子層積層工程、高密度プラズマ化学気象蒸着工程などを遂行して形成できる。その後、図示しないフォトレジストパターンを使用する写真エッチング工程を通じて前記第3導電膜をパターニングして、第3プラグ186と接続するゲートパッド196を形成し、ゲートパッドと前記第1方向に一定間隔で離隔されるようにソースパッド192、ドレインパッド194、及びバルクパッド198を形成する。このとき、ソースパッド192、ドレインパッド194、ゲートパッド196、及びバルクパッド198は互いに位置が換わってもいい。また、ソースパッド192と第1プラグ182とを接続するソースパッド接続ライン191、ドレインパッド194と第2プラグ184とを接続するドレインパッド接続ライン193、及びバルクパッド198と第4プラグ188とを接続するバルクパッド接続ライン197も共に形成する。これにより、ソースパッド192、ドレインパッド194、ゲートパッド196、及びバルクパッド198は各々第1ソース領域156、第1ドレイン領域158、第1ゲートライン165、及び第3アクティブ領域140と接続できることができる、バルクパッド198は第3アクティブ領域140を通じてウェル領域107と接続できる。

40

#### 【0076】

前述の工程を通じて、本発明の実施形態による半導体装置のテスト構造物が形成される。図示はしていないが、前述の各種パターン以外に、ビット或いはコンデンサー、各種配線がさらに形成できる。この時、発生するプラズマダメージは、トランジスタ150のみ

50

でなく、ダミートランジスタ 160 にも加わるため、結果的にトランジスタ 150 に加わるプラズマダメージの量が減少することになる。

【0077】

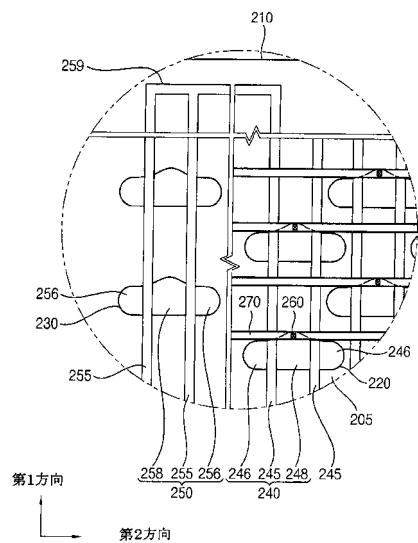

図 8 は、本発明の実施例による半導体装置を説明するための平面図である。

【0078】

図 8 を参照すると、半導体装置は、図示しない基板のネットダイ領域 210 上に形成されたトランジスタ 240 及びダミートランジスタ 250 を具備する。

【0079】

前記基板は、シリコン基板、ゲルマニウム基板、シリコン・ゲルマニウム基板、SOI 基板、GOI 基板などを含むことができる。前記基板は各種回路パターンを具備するネットダイ領域 210 及び前記ネットダイ領域の間に形成されて、各種テスト構造物、アラインパターン及びオーバーレイパターンを具備する図示しないスクライブレーン領域に区分される。10

【0080】

また、前記基板は、素子分離膜 205 が形成されたフィールド領域とアクティブ領域に区分できる。素子分離膜 205 は、シリコン酸化物を含む。前記アクティブ領域は、第 1 アクティブ領域 220 及び第 2 アクティブ領域 230 を含む。本発明の一実施形態によると、第 1 アクティブ領域 220 は、複数個形成され、アレーを成す。他方、第 2 アクティブ領域 230 は、1 つ或いは 2 つ以上に形成されることがある。20

【0081】

トランジスタ 240 は、第 1 アクティブ領域 220 上に形成されたゲートライン 245 と、ゲートライン 245 に隣接する第 1 アクティブ領域 220 の上部に形成された第 1 ソース領域 246 及び第 1 ドレイン領域 248 を含む。

【0082】

ゲートライン 245 は、図示しないゲート絶縁膜及び図示しないゲート電極を具備する。前記ゲート絶縁膜はシリコン酸化物或いは金属酸化物を含むことができ、前記ゲート電極は不純物がドーピングされたポリシリコン、金属及び / 又は金属シリサイドを含むことができる。他方、ゲートライン 245 の側壁にはシリコン窒化物或いはシリコン酸窒化物を含む図示しないゲートスペーサーがさらに形成されることもできる。30

【0083】

本発明の一実施形態によると、ゲートライン 245 は第 1 方向に延長され、1 つのゲートライン 245 は複数個の第 1 アクティブ領域 220 上に形成されることがある。また、ゲートライン 245 は複数個形成されることが可能、各ゲートライン 245 は前記第 1 方向と実質的に垂直する第 2 方向に一定の間隔で離隔して形成されることがある。本発明の一実施形態によると、1 つの第 1 アクティブ領域 220 上に 2 つのゲートライン 245 が形成される。

【0084】

第 1 ソース領域 246 及び第 1 ドレイン領域 248 は、ホウ素、ガリウム、インジウムなどの P 型不純物、或いは、リン、ヒ素、アンチモンなどの N 型不純物を含むことができる。図 8 に図示されたのと違って、第 1 ソース領域 246 及び第 1 ドレイン領域 248 は、互いに位置が換わってもいい。40

【0085】

ダミートランジスタ 250 は、第 2 アクティブ領域 230 上に形成されたダミーゲートライン 255 と、ダミーゲートライン 255 に隣接する第 2 アクティブ領域 230 の上部に形成された第 2 ソース領域 256 及び第 2 ドレイン領域 258 とを含む。

【0086】

ダミーゲートライン 255 は、図示しないダミーゲート絶縁膜及び図示しないダミーゲート電極を具備する。前記ダミーゲート絶縁膜及び前記ダミーゲート電極は、各々前記ゲート絶縁膜及び前記ゲート電極と実質的に同一物質を含むことができる。また、ダミーゲートライン 255 の各側壁には図示しないゲートスペーサーがさらに形成されることがで50

きる。

**【0087】**

本発明の一実施形態による、ダミーゲートライン255は前記第1方向に延長されて、1つのダミーゲートライン255は1つ或いは複数個の第2アクティブ領域230上に形成されることができる。また、ダミーゲートライン255は複数個形成されることができ、各ダミーゲートライン255は前記第1方向と実質的に垂直する第2方向に一定の間隔で離隔して形成されることができる。このとき、各ダミーゲートライン255は、後述する導電性ライン259により互いに接続されることがある。本発明の一実施形態によると、1つの第2アクティブ領域230上に2つのダミーゲートライン255が形成される。

10

**【0088】**

他方、ダミーゲートライン255は、ゲートライン245と接続される。本発明の一実施形態によると、前記第2方向に延長された導電性ライン259によりダミーゲートライン255とゲートライン245が接続される。導電性ライン259は、ゲートライン245及びダミーゲートライン255と実質的に同一物質を含むことができる。

**【0089】**

第2ソース領域256及び第2ドレイン領域258は、第1ソース領域246及び第1ドレイン領域248と実質的に同一の不純物を含むことができる。

**【0090】**

ダミートランジスタ250は、トランジスタ240と実質的に同一であるか類似の構成を有することができるが、後述するビットライン270には接続されない。即ち、トランジスタ240とは違って、ビットライン270に接続されないため、ダミートランジスタ250には一定の電気的信号が印加されない。

20

**【0091】**

しかし、ダミーゲートライン255がゲートライン245と接続されることで、後続工程において発生するプラズマダメージがトランジスタ240のみでなくダミートランジスタ250にも影響を及ぼし、これにより、トランジスタ240が受けるプラズマダメージを分散させる効果をもたらす。

**【0092】**

図示はしていないが、層間絶縁膜は、トランジスタ240、ダミートランジスタ250及び導電性ライン259を覆いつつ前記基板上に形成される。前記層間絶縁膜は、酸化物、窒化物及び/又は酸窒化物を含むことができる。

30

**【0093】**

ビットライン270は、前記層間絶縁膜を貫通するプラグ260を通じて第1ドレイン領域248と接続される。ビットライン270及びプラグ260は、金属及び/又は金属窒化物のような導電性物質を含むことができる。

**【0094】**

他方、ビットライン270及び前記層間絶縁膜上に第1ソース領域246と接続される図示しないコンデンサー構造物及び各種配線がさらに形成できる。

**【0095】**

前述の構成を有する半導体装置は、スイッチング素子として使用されるトランジスタ240のみでなく、ダミートランジスタ250と共に具備している。これにより、プラズマを使用するエッチング工程によりトランジスタ240のゲートライン245が受けるプラズマダメージがダミートランジスタ250のダミーゲートライン255に分散される。結果的にトランジスタ240を含む前記半導体装置は高い信頼性及び優秀な電気的特性を有することができる。

40

**【0096】**

図9～図11は、本発明の実施形態による半導体装置の製造方法を説明するための平面図である。図9～図11において、図8に図示したように実質的に同一の構造を有する半導体装置の製造方法を例示的に説明するが、図9～図11を参照して説明する半導体装置

50

の製造方法がこれに限定されるとは限らない。

【0097】

図9を参照すると、図示しない基板のネットダイ領域210に第1アクティブ領域220及び第2アクティブ領域230を定義する素子分離膜205を形成する。素子分離膜205は、シャロートレンチ工程或いはシリコン部分酸化工程などの素子分離工程を通じて形成されることができる。

【0098】

本発明の一実施形態によると、第1アクティブ領域220は、複数個に形成されてアレーを成す。他方、第2アクティブ領域230は、1つ或いは2つ以上に形成されることがある。

10

【0099】

図10を参照すると、第1アクティブ領域220及び第2アクティブ領域230上に各々トランジスタ240及びダミートランジスタ250が形成される。

【0100】

具体的に、ネットダイ領域210上に図示しない絶縁膜を形成する。前記絶縁膜は、酸化物、窒化物、及び／又は酸窒化物を使用して形成されることがある。また、前記絶縁膜は、化学気象蒸着工程、低圧化学気象蒸着工程、プラズマ増大化学気象蒸着工程、高密度プラズマ化学気象蒸着工程などを通じて形成されることがある。

【0101】

前記絶縁膜上に不純物がドーピングされたポリシリコン、金属及び／又は金属シリサイドを使用して、第1導電膜を形成する。前記第1導電膜は、化学気象蒸着工程、原子層積層工程、高密度プラズマ化学気象蒸着工程などを利用して形成されることがある。

20

【0102】

前記第1導電膜上に図示しないフォトレジストパターンを形成し、前記フォトレジストパターンをエッチングマスクを使用するエッチング工程を通じて前記第1導電膜及び前記絶縁膜の一部を除去することで、ゲートライン245、ダミーゲートライン255、及び導電性ライン259を形成する。ゲートライン245は図示しないゲート絶縁膜及びゲート電極を具備し、ダミーゲートライン255は図示しないダミーゲート絶縁膜及び図示しないダミーゲート電極を具備する。

【0103】

30

本発明の一実施形態によると、ゲートライン245は、複数個形成される。このとき、各ゲートライン245は、第1方向に延長され、前記第1方向と実質的に垂直する第2方向に一定の間隔で離隔されるように形成される。他方、ダミーゲートライン255は、1つ或いは複数個形成されることがある。ダミーゲートライン255は、導電性ライン259によりゲートライン245に接続される。本発明の一実施形態によると、ダミーゲートライン255は、前記第1方向に延長され、1つの第2アクティブ領域230上に2つのダミーゲートライン255が形成される。このとき、各ダミーゲートライン255も導電性ライン259により互いに接続される。

【0104】

40

この後、イオン注入工程を通じて第1アクティブ領域220及び第2アクティブ領域230に不純物を注入する。これにより、第1ゲートライン245に隣接する第1アクティブ領域220上部に第1ソース領域246及び第1ドレイン領域248が形成され、ダミーゲートライン255に隣接する第2アクティブ領域230上部に第2ソース領域256及び第2ドレイン領域258が形成される。ゲートライン245、第1ソース領域246、及び第1ドレイン領域248はトランジスタ240を形成し、ダミーゲートライン255、第2ソース領域256及び第2ドレイン領域258はダミートランジスタ250を形成する。

【0105】

図11を参照すると、トランジスタ240、ダミートランジスタ250、及び導電性ライン259を覆いつつ、ネットダイ領域210上に図示しない層間絶縁膜を形成する。前

50

記層間絶縁膜は、酸化物、窒化物、及び／又は酸窒化物を使用して形成されることができる。また、前記層間絶縁膜は、化学気象蒸着工程、低圧化学気象蒸着工程、プラズマ増大化学気象蒸着工程、高密度プラズマ化学気象蒸着工程などを通じて形成されることができる。

【0106】

その後、前記層間膜を貫通するプラグ260を第1ドレイン領域248上に形成する。

【0107】

具体的に、第1ドレイン領域248を部分的に露出させる図示しない開口部を前記層間絶縁膜に形成する。その後、金属及び／又は金属窒化物を使用する化学気象蒸着工程、原子層積層工程、高密度プラズマ化学気象蒸着工程などを遂行して前記開口部を埋めるように前記層間絶縁膜上に第2導電膜を形成する。化学的、機械的研磨工程及び／又はエッチバック工程を使用して前記層間絶縁膜上の前記第2導電膜部分を除去することで、第1ドレイン領域248と接続されたプラグ260を形成する。プラグ260は第1ドレイン領域248の個数に対応して、複数個形成される。

10

【0108】

その後、ビットライン270を形成して、第1ドレイン領域248と接続される。

【0109】

具体的には、前記層間絶縁膜及びプラグ260上に第3導電膜を形成する。前記第3導電膜は金属及び／又は、金属窒化物を使用する化学気象蒸着工程、原子層積層工程、高密度プラズマ化学気象蒸着工程などを遂行して形成することができる。その後、図示しないフォトレジストパターンを使用する写真エッチング工程を通じて前記第3導電膜をパターニングして、プラグ260と接続されるビットライン270とを形成する。本発明の一実施形態によると、ビットライン270は、前記第2方向に延長するように形成される。

20

【0110】

他方、ビットライン270及び前記層間絶縁膜上に第1ソース領域246と接続される図示しないコンデンサー構造物及び各種配線をさらに形成することができる。

【産業上の利用可能性】

【0111】

本発明によると、半導体装置のテスト構造物でプラズマを使用するエッチング工程によってトランジスタが受けるプラズマダメージがダミートランジスタに分散される。これによって、前記半導体装置のテスト構造物は、前記トランジスタのスレッショルド電圧などの素子特性をより正確に測定できる。

30

【0112】

また、半導体装置は、スイッチング素子として使用されるトランジスタのみでなく、プラズマを使用するエッチング工程により発生するプラズマダメージを分散させるダミートランジスタを共に具備している。これによって、前記トランジスタを含む前記半導体装置は高い信頼性及び優秀な電気的特性を有することができる。

【0113】

以上、本発明の実施例によって詳細に説明したが、本発明はこれに限定されず、本発明が属する技術分野において通常の知識を有するものであれば本発明の思想と精神を離れることなく、本発明を修正又は変更できる。

40

【図面の簡単な説明】

【0114】

【図1】本発明の一実施形態による半導体装置のテスト構造物を説明するための平面図である。

【図2】図1でI-I'線に沿って切断した断面図である。

【図3】本発明の他の実施形態による半導体装置のテスト構造物を説明するための平面図である。

【図4】本発明の一実施形態による半導体装置のテスト構造物の形成方法を説明するための平面図である。

50

【図5】本発明の一実施形態による半導体装置のテスト構造物の形成方法を説明するための平面図である。

【図6】本発明の一実施形態による半導体装置のテスト構造物の形成方法を説明するための平面図である。

【図7】本発明の一実施形態による半導体装置のテスト構造物の形成方法を説明するための平面図である。

【図8】本発明の一実施形態による半導体装置を説明するための平面図である。

【図9】本発明の一実施形態による半導体装置の製造方法を説明するための平面図である。

【図10】本発明の一実施形態による半導体装置の製造方法を説明するための平面図である。

【図11】本発明の一実施形態による半導体装置の製造方法を説明するための平面図である。

## 【符号の説明】

[ 0 1 1 5 ]

100 : 基板、105 : 素子分離膜、110 : スクライブレーン領域、120

、220 : 第1アクティブ領域、130、230 : 第2アクティブ領域、140 : 第3アクティブ領域、150、240 : ドラインジスタ、155 : 第1ゲートライン、160、250 : ダミートランジスタ、165、225 : ダミーゲートライン、173 : 第2ゲートライン、174 : 第1導電性ライン、176 : 第2導電性ライン、178 : 第3導電性ライン、182 : 第1プラグ、184 : 第2プラグ、186 : 第3プラグ、188 : 第4プラグ、192 : ソースパッド、194 : ドレインパッド、196 : ゲートパッド、198 : バルクパッド、210 : ネットダイ領域、245 : ゲートライン、260 : プラグ、270 : ビットライン、259 : 導電性ライン

【 図 1 】

【図2】

【 図 3 】

【 図 4 】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【 図 1 1 】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 27/04 (2006.01)

(72)発明者 金 智 恵

大韓民国京畿道城南市盆唐区書 見 洞書 見 ポスパーク203棟304号

審査官 行武 哲太郎

(56)参考文献 特開2007-116197 (JP, A)

特開平11-345885 (JP, A)

特開平5-21557 (JP, A)

韓国公開特許第10-2005-0023719 (KR, A)

特開2002-217258 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/66