(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6091674号

(P6091674)

(45) 発行日 平成29年3月8日(2017.3.8)

(24) 登録日 平成29年2月17日(2017.2.17)

|                       |                |

|-----------------------|----------------|

| (51) Int.Cl.          | F 1            |

| HO4N 5/374 (2011.01)  | HO4N 5/335 740 |

| HO4N 5/345 (2011.01)  | HO4N 5/335 450 |

| HO4N 5/232 (2006.01)  | HO4N 5/232 H   |

| HO1L 27/14 (2006.01)  | HO1L 27/14 D   |

| HO1L 27/146 (2006.01) | HO1L 27/14 A   |

請求項の数 9 (全 48 頁)

|              |                                                             |           |                                            |

|--------------|-------------------------------------------------------------|-----------|--------------------------------------------|

| (21) 出願番号    | 特願2016-33276 (P2016-33276)                                  | (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (22) 出願日     | 平成28年2月24日(2016.2.24)                                       | (74) 代理人  | 100126240<br>弁理士 阿部 琢磨                     |

| (62) 分割の表示   | 特願2013-1084 (P2013-1084)<br>の分割<br>原出願日 平成25年1月8日(2013.1.8) | (74) 代理人  | 100124442<br>弁理士 黒岩 創吾                     |

| (65) 公開番号    | 特開2016-105649 (P2016-105649A)                               | (72) 発明者  | 橋本 誠二<br>東京都大田区下丸子3丁目30番2号キヤ<br>ノン株式会社内    |

| (43) 公開日     | 平成28年6月9日(2016.6.9)                                         | (72) 発明者  | 古林 篤<br>東京都大田区下丸子3丁目30番2号キヤ<br>ノン株式会社内     |

| 審査請求日        | 平成28年3月23日(2016.3.23)                                       |           |                                            |

| (31) 優先権主張番号 | 特願2012-45653 (P2012-45653)                                  |           |                                            |

| (32) 優先日     | 平成24年3月1日(2012.3.1)                                         |           |                                            |

| (33) 優先権主張国  | 日本国(JP)                                                     |           |                                            |

最終頁に続く

(54) 【発明の名称】撮像装置、撮像システム、撮像装置の駆動方法、撮像システムの駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数行および複数列に渡って配された複数の画素と、

複数のマイクロレンズを有するとともに、前記複数のマイクロレンズの各々が前記複数の画素の各々に対応して配されたマイクロレンズアレイと、

前記複数列の各列に対応して各々が配された複数の增幅回路とを有し、

前記複数の画素の各々が、入射光に対応する信号を生成するm個(mは2以上の整数)の光電変換部を含む撮像装置であつて、

1フレーム期間内に、前記複数の画素の各々は第2の信号を出力し、前記複数の画素の一部のみの画素の各々は、第1の信号をさらに出力し、

前記第1の信号は、前記m個の光電変換部のうちの一部のみの光電変換部の前記信号に基づく信号であり、

前記第2の信号は、前記m個の光電変換部の少なくとも他の一部の光電変換部の前記信号に基づく信号であり、

前記複数の増幅回路の各々は、対応する列の画素の前記第1の信号を増幅した第1の増幅信号と、前記対応する列の画素の前記第2の信号を増幅した第2の増幅信号とをそれぞれ生成することを特徴とする撮像装置。

## 【請求項 2】

前記第2の信号は、前記m個の光電変換部の信号に基づく信号であることを特徴とする請求項1に記載の撮像装置。

**【請求項 3】**

前記複数の画素の前記一部のみの画素の各々が前記第1の信号を出力した後、前記複数の画素の各々が前記第2の信号を出力することを特徴とする請求項1または2に記載の撮像装置。

**【請求項 4】**

前記第1の増幅信号と、前記第2の増幅信号をそれぞれデジタル信号に変換するA/D変換部を有することを特徴とする請求項1～3のいずれか1項に記載の撮像装置。

**【請求項 5】**

前記複数行のうちの一部のみの行の画素が、前記複数の画素の一部のみの画素として、前記第1の信号を出力することを特徴とする請求項1～4のいずれか1項に記載の撮像装置。

10

**【請求項 6】**

複数行および複数列に渡って配された複数の画素と、複数のマイクロレンズを有するとともに、前記複数のマイクロレンズの各々が前記複数の画素の各々に対応して配されたマイクロレンズアレイと、

前記複数列の各列に対応して各々が配された複数のA/D変換部とを有し、前記複数の画素の各々が、入射光に対応する信号を生成するm個（mは2以上の整数）の光電変換部を含む撮像装置であって、

1フレーム期間内に、前記複数の画素の各々は第2の信号を出力し、前記複数の画素の一部のみの画素の各々は、第1の信号をさらに出力し、

20

前記第1の信号は、前記m個の光電変換部のうちの一部のみの光電変換部の前記信号に基づく信号であり、

前記第2の信号は、前記m個の光電変換部の少なくとも他の一部の光電変換部の前記信号に基づく信号であり、

前記複数のA/D変換部の各々は、対応する列の画素の前記第1の信号をA/D変換した第1のデジタル信号と、前記対応する列の画素の前記第2の信号をA/D変換した第2のデジタル信号とをそれぞれ生成することを特徴とする撮像装置。

**【請求項 7】**

前記複数行のうちの一部のみの行の画素が、前記複数の画素の一部のみの画素として、前記第1の信号を出力することを特徴とする請求項6に記載の撮像装置。

30

**【請求項 8】**

請求項1～5のいずれか1項に記載の撮像装置と、出力信号処理部とを有する撮像システムであって、

前記出力信号処理部に、前記第1の増幅信号に基づく信号と、前記第2の増幅信号に基づく信号とが出力され、

前記出力信号処理部が、

前記第1の増幅信号に基づく信号と、前記第2の増幅信号に基づく信号との差分である差分信号を得て、前記差分信号と前記第1の増幅信号に基づく信号とによって焦点検出を行い、さらに前記出力信号処理部が、前記第2の増幅信号に基づく信号によって画像を形成することを特徴とする撮像システム。

40

**【請求項 9】**

請求項6または7に記載の撮像装置と、出力信号処理部とを有する撮像システムであって、

前記出力信号処理部に、前記第1のデジタル信号に基づく信号と、前記第2のデジタル信号に基づく信号とが出力され、

前記出力信号処理部が、

前記第1のデジタル信号に基づく信号と、前記第2のデジタル信号に基づく信号との差分である差分信号を得て、前記差分信号と前記第1のデジタル信号に基づく信号とによって焦点検出を行い、さらに前記出力信号処理部が、前記第2のデジタル信号に基づく信号によって画像を形成することを特徴とする撮像システム。

50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、複数の光電変換部を含む画素を複数有する撮像装置、撮像システムに関するものである。

**【背景技術】****【0002】**

複数の光電変換部を含む画素を複数有し、一方の光電変換部に基づく信号と、他方の光電変換部の一部の光電変換部に基づく信号とを出力する撮像装置が知られている。この少なくとも2つの信号を用いた形態として、例えば位相差検出方式の焦点検出を行う焦点検出方法が提案されている。このような焦点検出方法に利用可能な信号を出力する撮像装置の一例として、1対の光電変換部を、2次元に配列したマイクロレンズアレイのマイクロレンズ毎に設けたものがある。特許文献1には、1つのマイクロレンズを介して光が入射される1対の光電変換部が出力する信号の加算、非加算を1対の光電変換部を有する画素単位で任意に行うことのできる撮像装置が提案されている。

**【0003】**

また、特許文献2には、測距用の画素と撮像用の画素とを有する撮像装置が、静止画撮影モード、間引きモード、測距モードの3種類の読み出し方法で動作することが記載されている。静止画撮影モードでは、測距用の画素と撮像用の画素信号が撮像装置から出力されるが、測距用の画素からの画素信号はその後の信号処理で使用せず、撮像用の画素信号のみを使用する。測距モードは、静止画撮影モードとは逆に、撮像用の画素からの画素信号をその後の信号処理で使用せず、測距用の画素からの画素信号を使用する形態である。間引きモードは、撮像装置から画素信号を出力させる際に、撮像用の画素からのみ画素信号を出力させ、測距用の画素からは画素信号を出力させない形態である。

**【先行技術文献】****【特許文献】****【0004】**

【特許文献1】特開2001-83407号公報

【特許文献2】特開2000-156823号公報

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

特許文献1に記載の撮像装置では複数の光電変換部に基づく信号である画像取得用信号を得ると共に、位相差検出方式の焦点検出を行うための信号であり、一部の光電変換部に基づく信号である焦点検出用信号を高速に得る検討が充分になされていなかった。

**【0006】**

特許文献2に記載の撮像装置では、画像取得用信号を得るために静止画撮影モードと間引きモードの一方で動作を行い、焦点検出用信号を得るために測距モードで動作を行うことが必要だった。よって、画像取得用信号と焦点検出用信号とを得るために、複数回、固体撮像素子の画素を走査して画素信号を出力させる必要があった。

**【0007】**

従って、特許文献1, 2ともに、撮像装置から複数の光電変換部のうちの一部の光電変換部に基づく信号を高速に得ると共に、複数の光電変換部に基づく信号を得る検討が充分では無かった。

**【課題を解決するための手段】****【0008】**

本発明は上記の課題を解決するために為されたものであり、一の態様は、複数行および複数列に渡って配された複数の画素と、複数のマイクロレンズを有するとともに、前記複数のマイクロレンズの各々が前記複数の画素の各々に対応して配されたマイクロレンズアレイと、前記複数列の各列に対応して各々が配された複数の增幅回路とを有し、前記複数

10

20

30

40

50

の画素の各々が、入射光に対応する信号を生成するm個（mは2以上の整数）の光電変換部を含む撮像装置であって、1フレーム期間内に、前記複数の画素の各々は第2の信号を出力し、前記複数の画素の一部のみの画素の各々は、第1の信号をさらに出力し、前記第1の信号は、前記m個の光電変換部のうちの一部のみの光電変換部の前記信号に基づく信号であり、前記第2の信号は、前記m個の光電変換部の少なくとも他の一部の光電変換部の前記信号に基づく信号であり、前記複数の增幅回路の各々は、対応する列の画素の前記第1の信号を増幅した第1の増幅信号と、前記対応する列の画素の前記第2の信号を増幅した第2の増幅信号とをそれぞれ生成することを特徴とする撮像装置である。

## 【0009】

また、一の態様は、複数行および複数列に渡って配された複数の画素と、複数のマイクロレンズを有するとともに、前記複数のマイクロレンズの各々が前記複数の画素の各々に対応して配されたマイクロレンズアレイと、前記複数列の各列に対応して各々が配された複数のA/D変換部とを有し、前記複数の画素の各々が、入射光に対応する信号を生成するm個（mは2以上の整数）の光電変換部を含む撮像装置であって、1フレーム期間内に、前記複数の画素の各々は第2の信号を出力し、前記複数の画素の一部のみの画素の各々は、第1の信号をさらに出力し、前記第1の信号は、前記m個の光電変換部のうちの一部のみの光電変換部の前記信号に基づく信号であり、前記第2の信号は、前記m個の光電変換部の少なくとも他の一部の光電変換部の前記信号に基づく信号であり、前記複数のA/D変換部の各々は、対応する列の画素の前記第1の信号をA/D変換した第1のデジタル信号と、前記対応する列の画素の前記第2の信号をA/D変換した第2のデジタル信号とをそれぞれ生成することを特徴とする撮像装置である。

10

## 【発明の効果】

## 【0013】

本発明は、複数の光電変換部の一部の光電変換部に基づく信号を高速に得ると共に、複数の光電変換部に基づく信号を得ることができる撮像装置、撮像システムを提供することができる。

## 【図面の簡単な説明】

## 【0014】

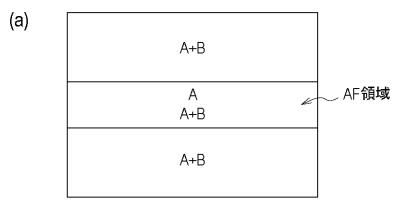

【図1】焦点検出画素として動作させる画素の配置例を示した模式図。

30

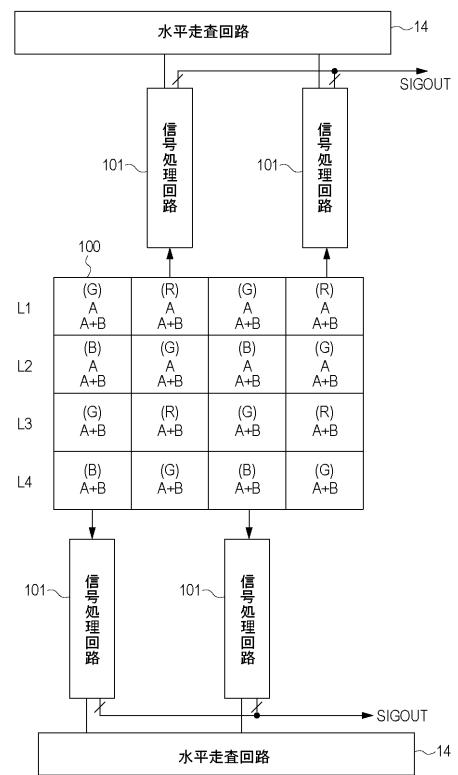

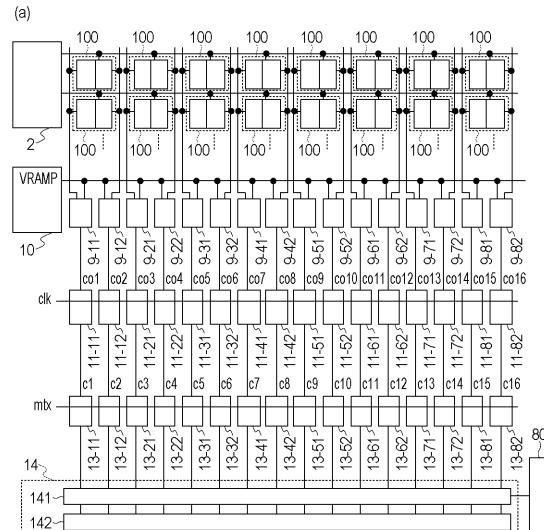

【図2】撮像装置に関する画素部と信号処理回路とを例示した模式図。

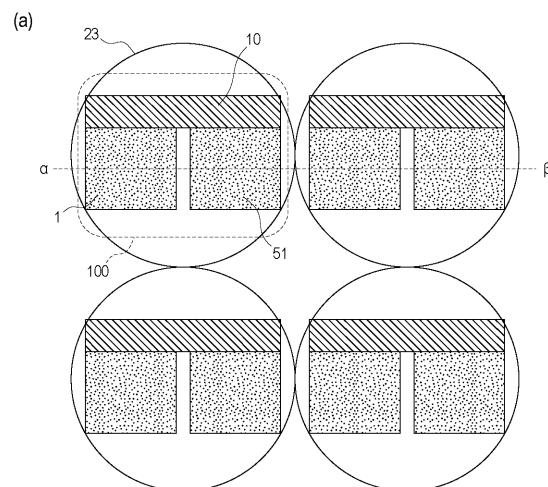

【図3】撮像装置の画素部に関する配置例を示した図。

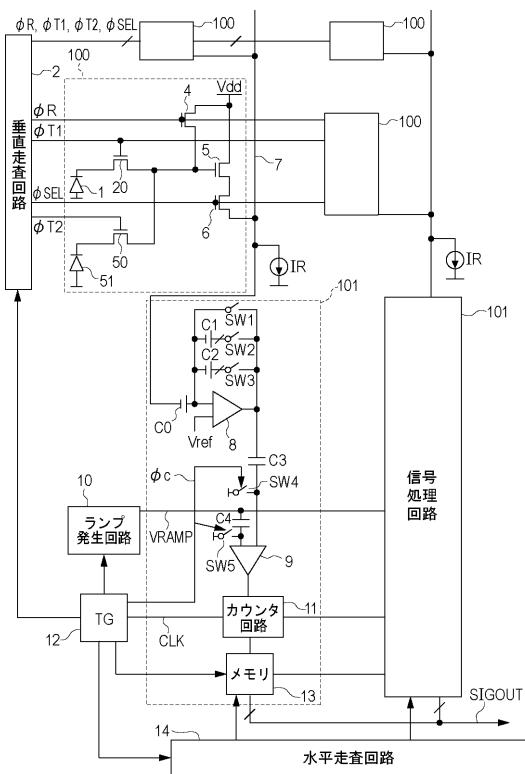

【図4】撮像装置に関する模式図。

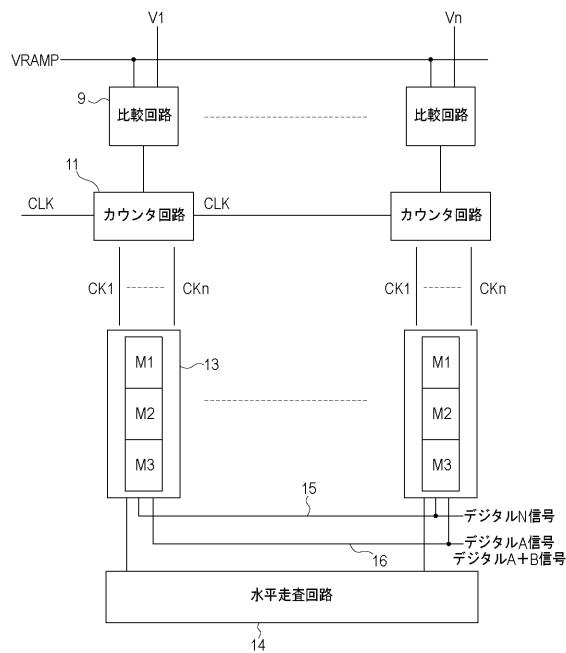

【図5】撮像装置のアナログデジタル変換回路の一例を示した模式図。

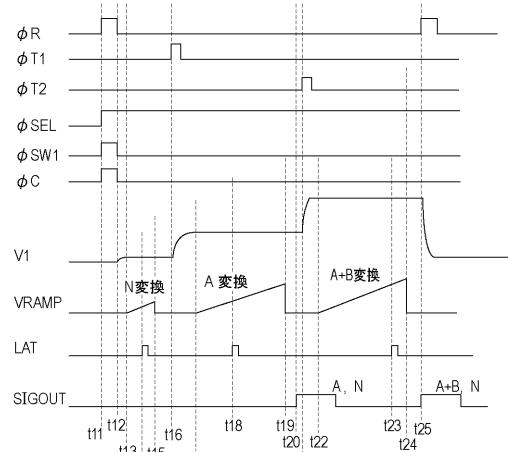

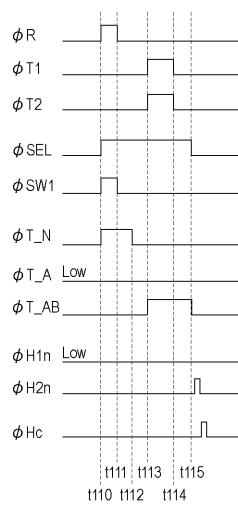

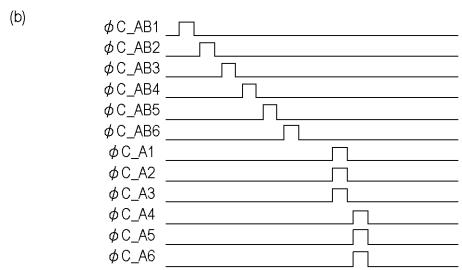

【図6】撮像装置に関する動作タイミングを表した図。

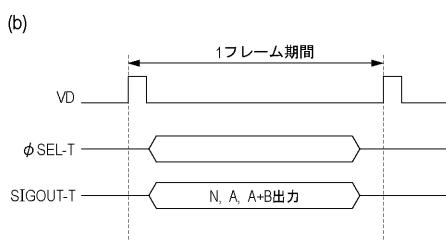

【図7】撮像装置に関する他の一例の動作タイミングを表した図。

【図8】撮像装置のアナログデジタル変換回路の別の一例を示した模式図。

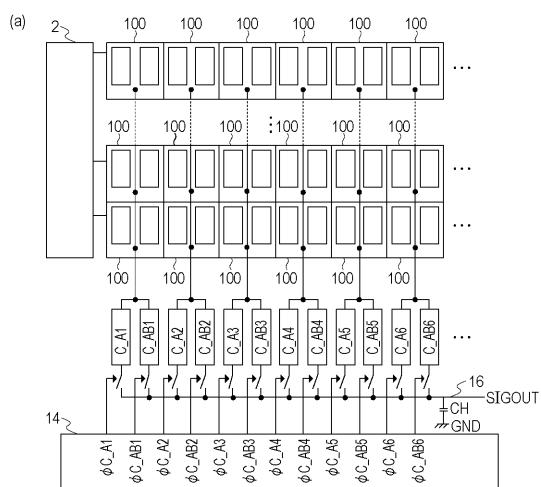

【図9】他の一例の撮像装置に関する画素部と信号処理回路とを例示した模式図。

【図10】他の一例の撮像装置に関する画素部を例示した模式図。

【図11】他の一例の撮像装置に関する模式図。

【図12】他の一例の撮像装置に関する動作タイミングを表した図。

40

【図13】他の一例の撮像装置に関する模式図。

【図14】他の一例の撮像装置に関する動作タイミングを表した図。

【図15】他の一例の撮像装置に関する動作タイミングを表した図。

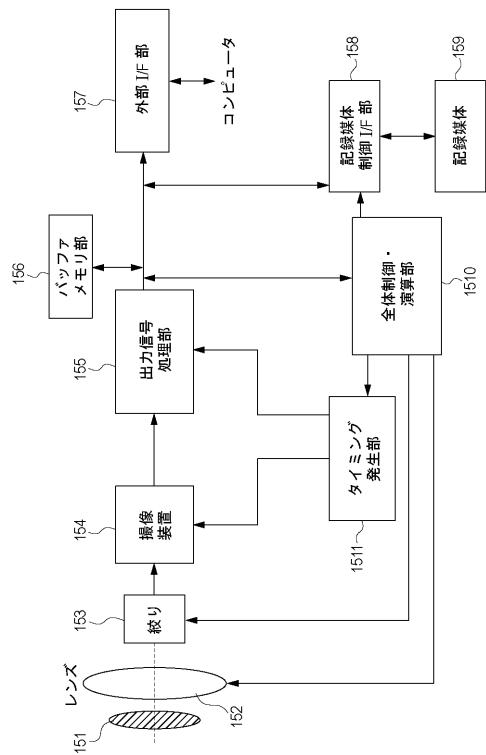

【図16】撮像システムに関する模式図。

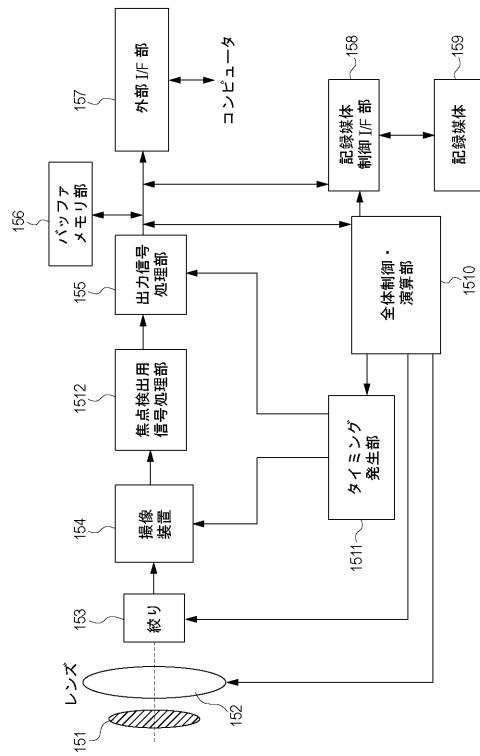

【図17】他の一例の撮像システムに関する模式図。

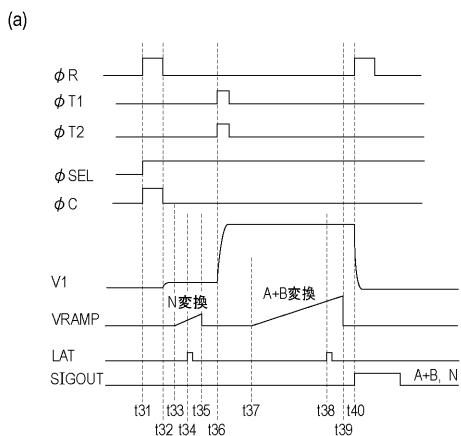

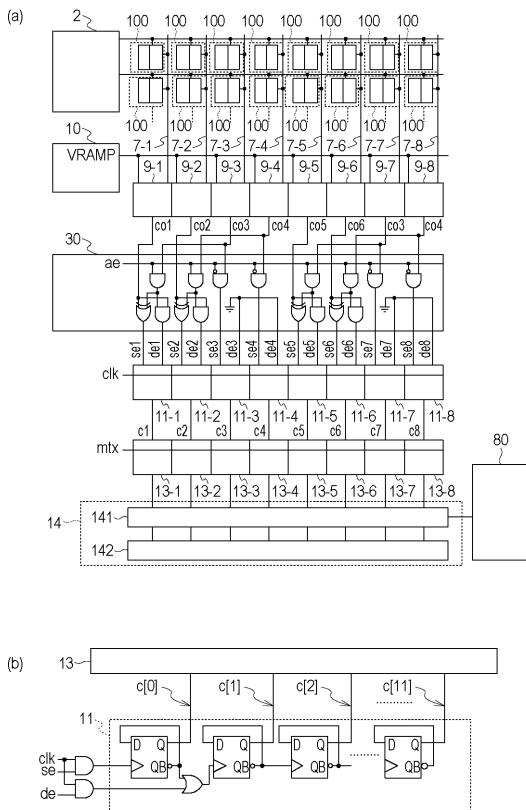

【図18】他の一例の撮像装置と、カウンタ回路に関する模式図。

【図19】他の一例の撮像装置に関する動作タイミングを表した図。

【図20】他の一例の画素部と、他の一例の撮像装置の模式図。

【図21】他の一例の撮像装置に関する動作タイミングを表した図。

【図22】他の一例の撮像装置の模式図と、他の一例の撮像装置に関する動作タイミング

50

を表した図。

【図23】他の一例の撮像装置に関する動作タイミングを表した図。

【図24】他の一例の撮像装置の模式図と、他の一例の撮像装置に関する動作タイミングを表した図。

【図25】他の一例の撮像装置の模式図と、他の一例の撮像装置に関する動作タイミングを表した図。

【図26】他の一例の撮像装置に関する動作タイミングを表した図。

【図27】他の一例の撮像装置の模式図と、他の一例の撮像装置に関する動作タイミングを表した図。

【図28】他の一例の撮像装置の模式図と、他の一例の撮像装置に関する動作タイミングを表した図。 10

【図29】他の一例の撮像装置の模式図と、他の一例の撮像装置に関する動作タイミングを表した図。

【図30】他の一例の撮像装置の模式図と、他の一例の増幅回路の模式図。

【図31】他の一例の撮像装置に関する動作タイミングを表した図。

#### 【発明を実施するための形態】

##### 【0015】

###### 〔実施例1〕

以下、図面を参照しながら本実施例の撮像装置について説明する。

##### 【0016】

本実施例の撮像装置に設けられた画素は、位相差検出方式による焦点検出のための焦点検出用信号の基となる信号と、撮像のための信号である画像取得用信号の基となる信号を出力する。例えば、ライン状またはクロス状に配置された、複数の画素から焦点検出用信号の基となる信号が出力される。撮像装置は、画素から出力される焦点検出用信号の基となる信号と画像取得用信号の基となる信号を処理して焦点検出用信号、画像取得用信号を出力する。撮像装置から出力された焦点検出用信号に基づいて、入射光の相互の位相差を検出することができる。この検出された位相差に基づいて焦点検出を行うことができる。 20

##### 【0017】

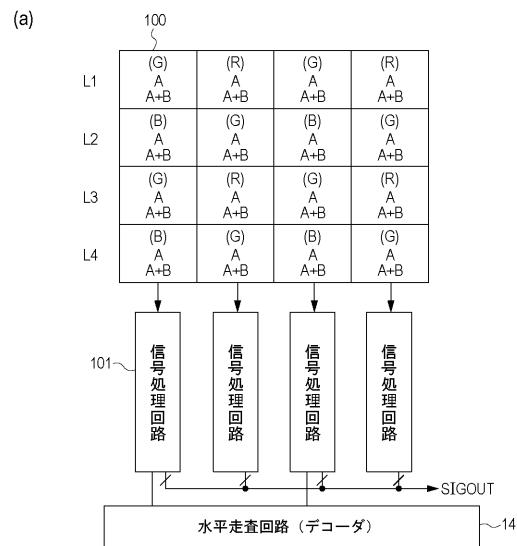

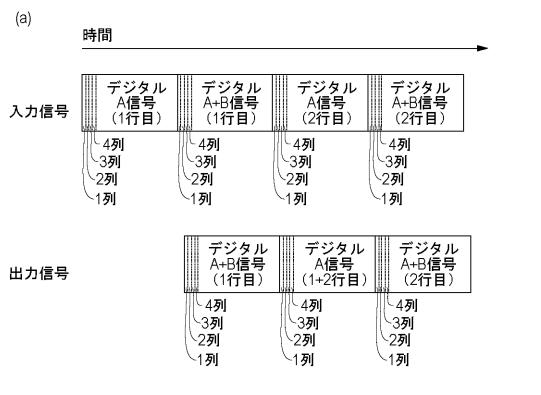

図1(a)に、本実施例の撮像装置における、画素が output する信号(以下、画素信号と表記する)の読み出し方の一例を示す。本実施例の画素の各々は、後述するように、複数の光電変換部を有している。複数の光電変換部の一方の信号電荷に基づいて出力される画素信号をA信号と表記する。また、複数の光電変換部の信号電荷に基づいて出力される画素信号をA+B信号と表記する。A信号は焦点を検出するための信号である焦点検出用信号の基となる信号である。A+B信号は画像取得用信号の基となる信号である。A+B信号は画素が output する第2の信号であり、A信号は画素が output する第1の信号である。 30

##### 【0018】

図1(a)～(c)は、画素が複数行、複数列配された形態を模式的に表している。図1(a)は、一部の行において全ての画素がA信号を output する形態である。また、AとA+Bとが併記された領域の画素はA信号を output した後、A+B信号を output する。A+Bと記された領域の画素は、A+B信号の出力を行うが、A信号の出力は行わない。 40

##### 【0019】

図2に、図1(a)に示した撮像装置の一部である4行4列の画素を抜き出すとともに、画素からの信号を処理する信号処理回路と水平走査回路とを合わせて示した模式図を示す。図2の画素は、4行×4列を基本単位としたペイヤー配列で配置されている。以下、複数行、複数列の画素が配列された領域を画素部と表記する。図2では、画素に設けられているカラーフィルター22の色であるR(赤)、G(緑)、B(青)を括弧書きで示し、その下段に出力する信号を記している。つまり、図2の上から数えて1行目、左から数えて1列目の画素は緑のカラーフィルターを有しており、A信号とA+B信号とを時分割で出力することを示している。図2において、図の上から数えて1行目L1、2行目L2の全ての画素はA信号と、A+B信号を時分割で出力する。図の上から数えて3行目L3 50

、4行目L4の全ての画素は、A信号は出力せず、A+B信号のみを出力する。尚、以下特に断りのない限りは、本明細書を通じてX行目(Xは自然数)と表記する際は全て図の上から数えたものとして表す。同様に、Y列目(Yは自然数)と表記する際にについても、特に断りのない限り本明細書を通じて図の左から数えたものとして表す。複数列配された画素の各列に信号処理回路101が設けられており、水平走査回路14からの信号に基づいて各画素から画素信号を読み出し、読み出した信号を撮像装置の外部に出力する。図2に示した撮像装置の例では、水平走査回路14が行列状に画素100が配された画素領域を挟んで2つ設けられている。信号処理回路101は1列おきに同一の水平走査回路14に電気的に接続されている。この構成により、例えば1列目と2列目に設けられた信号処理回路を2つの水平走査回路14のそれぞれが選択することにより、1列目と2列目の画素100のそれぞれから画素信号を同時に出力させることができる。

10

#### 【0020】

図3(a)は本実施例に関する撮像装置の上面模式図である。画素100は、第1の光電変換部である第1のフォトダイオード1、第2の光電変換部である第2のフォトダイオード51、フォトダイオード1、51に電気的に接続された画素内読み出し回路部10を含んでいる。以下では、1つの画素100が有するフォトダイオード1とフォトダイオード51とをまとめて表す際は、受光部と表記する。1つのマイクロレンズ23は、1つの受光部を覆うように配され、光束を受光部に集光する。つまり、1つのマイクロレンズは1つの受光部に対応して設けられている。また、1つのマイクロレンズによって集光された光は、1つのマイクロレンズに対応して設けられた画素100が有する複数の光電変換部に入射する。本実施例の撮像装置は、複数のマイクロレンズを有するマイクロレンズアレイを有する。

20

#### 【0021】

次に、図3(b)に、図3(a)で - の直線で示した部分のうち、2つの画素100の断面を示す。カラーフィルター22はマイクロレンズ23とフォトダイオード1、51との間に設けられている。

#### 【0022】

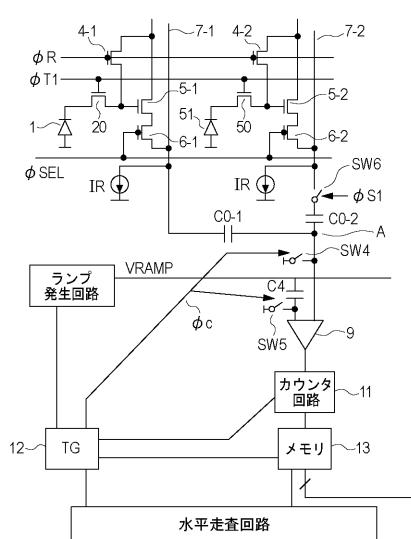

図4は本実施例の撮像装置のうち、2行2列の画素100と、2列の信号処理回路101を抜き出して模式的に表した模式図である。2は垂直走査回路であり、タイミングジェネレータ12(以下、TG12と表記する)からのタイミング信号に基づいて画素を行ごとに選択して、画素から画素信号を出力させる垂直走査回路である。

30

#### 【0023】

次に画素100について説明する。

#### 【0024】

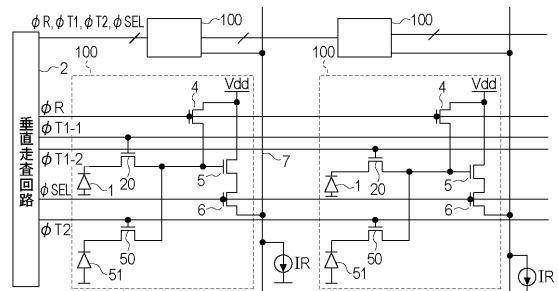

画素100は、転送MOSトランジスタ20、50、リセットMOSトランジスタ4、増幅MOSトランジスタ5、選択MOSトランジスタ6を有する。フォトダイオード1、51では光が入射すると、光電変換により信号電荷が生じる。転送MOSトランジスタ20のゲートに、図6を用いて後述する垂直走査回路2が供給する転送パルスT1をHighレベル(以降、Hレベルと表記する。同様に、LowレベルをLレベルと表記する。)として、フォトダイオード1が保持する信号電荷を増幅MOSトランジスタ5の入力ノードに転送する。同様に、転送MOSトランジスタ50のゲートに、垂直走査回路2が供給する転送パルスT2をHレベルとして、フォトダイオード51が有する信号電荷を増幅MOSトランジスタ5の入力ノードに転送する。リセットMOSトランジスタ4のゲートに垂直走査回路2が供給するリセットパルスRをHレベルとすると、増幅MOSトランジスタ5の入力ノードの電位がリセットされる。増幅MOSトランジスタ5は、入力ノードに転送された信号電荷に基づいて、電気信号を選択MOSトランジスタ6に出力する。選択MOSトランジスタ6は、増幅MOSトランジスタ5が出了した信号を、垂直走査回路2からゲートに供給される選択パルスSELがHレベルの時に垂直信号線7に出力する。

40

#### 【0025】

フォトダイオード 1 からの信号電荷が転送された増幅MOSトランジスタ5の入力ノードの電位に基づいて、垂直信号線7に出力される信号が前述したA信号に相当する。また、フォトダイオード5 1 からの信号電荷が転送された増幅MOSトランジスタ5の入力ノードの電位に基づいて、垂直信号線7に出力される信号がB信号である。また、転送パルス T 1、T 2 を共にHレベルとして、フォトダイオード1、5 1 のそれぞれに蓄積された信号電荷を増幅MOSトランジスタ5の入力ノードに転送する。この時の増幅MOSトランジスタ5の入力ノードの電位に基づいて垂直信号線7に出力される信号が前述したA+B信号に相当する。本実施例では、B信号、すなわち、フォトダイオード5 1において光電変換を行って保持した信号電荷のみが増幅MOSトランジスタ5の入力ノードに転送されて垂直信号線7に出力される信号については、画素100からの出力動作を行わない。B信号に相当する信号は、画像取得用信号と焦点検出用信号との差分処理を、後述するデジタル信号処理回路が行うことによって取得する。このB信号もA信号と同様に焦点検出に用いられる焦点検出用信号の基となる信号である。以上が画素100についての説明である。

#### 【0026】

次に、信号処理回路101について説明する。C0はクランプ容量である。8はオペアンプであり、クランプ容量C0を介して画素100から出力される画素信号を増幅して出力する。オペアンプ8の帰還経路にはフィードバック容量C1、C2がそれぞれスイッチSW2、SW3とともに設けられている。オペアンプ8の出力端子には、フィードバック容量C1、C2のうち、オペアンプ8の出力端子と入力端子とに対して導通状態にあるスイッチSW2、SW3と直列に接続されたフィードバック容量の容量値の総和Cf\_to\_talとクランプ容量C0の容量比による反転ゲインが発生する。

#### 【0027】

オペアンプ8から出力された信号は、クランプ容量C3を介して、比較回路9に入力される。比較回路9はランプ信号発生回路10から、時間に依存して電圧値が変化するランプ信号VRAMPがクランプ容量C4を介して供給される。比較回路9は、ランプ信号VRAMPとクランプ容量C3を介してオペアンプ8から出力される信号との比較を行い、比較結果に基づく信号であるラッチ信号LATをカウンタ回路11に出力する。つまり、ランプ信号VRAMPとオペアンプ8から出力される信号との大小関係が逆転した時に、比較回路9が出力するラッチ信号LATの信号レベルが変化する。カウンタ回路11にはTG12からクロックパルス信号CLKが出力されている。カウンタ回路11は、ランプ信号発生回路10が時間に依存したランプ信号VRAMPの電圧値の変化を開始してから比較回路9からラッチ信号LATが変化するまでの間、クロックパルス信号CLKを計数したカウント信号を生成する。比較回路9から出力されるラッチ信号LATが変化した時、クロックパルス信号CLKの計数を終了するとともに、ラッチ信号LATが変化した時のカウント信号を保持する。信号保持部であるメモリ13はランプ信号VRAMPを変化させる期間が終了すると、カウンタ回路11に保持されたカウント信号の取り込みを行い、カウント信号を保持する。水平走査回路14はTG12からのタイミング信号に基づいて各列のメモリ13を順次選択し、各列のメモリ13が保持したカウント信号を転送する。この水平走査回路14によって出力された信号が、撮像装置の出力する出力信号SIGOUTである。本実施例の出力信号SIGOUTは、後述するデジタルN信号、デジタルA信号、デジタルA+B信号である。すなわち、出力信号SIGOUTは、画素信号に基づく信号である。また、デジタルA+B信号は第2の信号に基づく信号であり、デジタルA信号は第1の信号に基づく信号である。本実施例では、第2の信号に基づく信号は画像取得用信号であり、第1の信号に基づく信号は焦点検出用信号である。尚、ランプ信号VRAMPは、比較回路9においてアナログ信号と比較される参照信号の一例である。

#### 【0028】

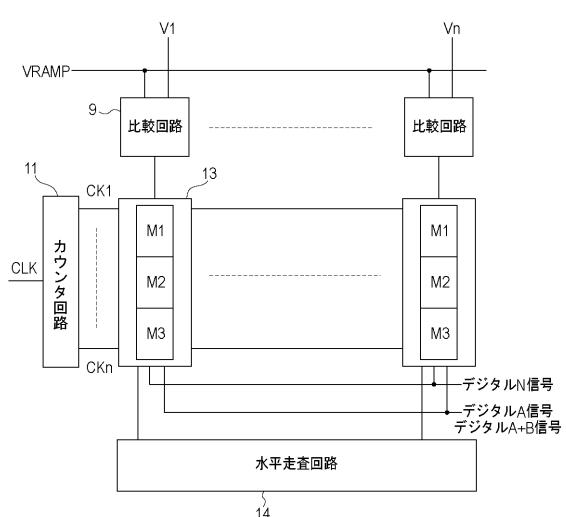

次に、図5に、カウンタ回路11とメモリ13の構成の一例を示す。カウンタ回路11は、TG12から供給されるクロックパルス信号CLKに基づいて、nビットのカウント信号CKnを生成し、メモリ13に出力する。カウンタ回路11とメモリ13との間には

10

20

30

40

50

$n$ ビットのカウント信号を伝送するカウント信号伝送線が $n$ 本設けられている。本実施例の撮像装置は、後述するが、相関二重サンプリング（以下、CDS（Correlated Double Sampling）と表記する。）を行う。よって、画素100のノイズレベルの信号であるN信号と、受光部が光電変換して生じた信号電荷が転送された増幅MOSトランジスタ5の入力ノードの電位に基づいて出力されるS信号とが画素100から出力される。S信号は、本実施例ではA信号とA+B信号である。従って、画素100からは1フレーム期間内に、N信号、A信号、A+B信号の3つの信号が出力される。なお、1フレーム期間とは、後述する図7（b）で示した垂直同期信号VDが1度Hレベルとなった後、次にHレベルとなるまでの期間である。本実施例では、アナログ信号であるN信号、A信号、A+B信号のそれぞれが画素100から出力される都度、デジタル信号に変換する動作を行う。このため、メモリ13はデジタル信号値を保持するメモリ部をそれぞれの信号に対応して3つ設けている。即ち、メモリ部M1はN信号に基づくデジタルN信号、メモリ部M2はA信号に基づくデジタルA信号、メモリ部M3はA+B信号に基づくデジタルA+B信号を保持する。すなわち、メモリ部M1はノイズレベルの信号値であるデジタル信号が入力されるNメモリである。また、メモリ部M2は、画素の一部の光電変換部に基づく前記画素信号に基づく信号を保持するS1メモリである。また、メモリ部M3は、画素の複数の光電変換部に基づく画素信号に基づく信号を保持するS2メモリである。メモリ13にはN信号線15とS信号線16とが電気的に接続されており、N信号線15にはメモリ部M1からデジタルN信号、S信号線16にはメモリ部M2、M3のそれからデジタルA信号と、A+B信号に基づくデジタルA+B信号とが時分割で出力される。

#### 【0029】

次に図6に、図2に例示した撮像装置のうち、1行目の画素100が行う動作のタイミングを示す。スイッチパルスSW1は、スイッチSW1のオン、オフを切り替えるパルスであり、Hレベルの時にスイッチSW1がオンとなる。V1はオペアンプ8の出力を表している。SIGOUTは水平走査回路14が各列のメモリ13を選択し、各メモリ部からカウント信号を出力させるタイミングを示している。以下では、SW2およびSW3の少なくとも一方がハイレベルである、つまり、クランプ容量C0の容量値との比で信号を増幅するものとする。

#### 【0030】

時刻t11において、リセットパルスRはHレベルとし、増幅MOSトランジスタ5の入力ノードをリセットレベルの電位とする。また、選択パルスSELをHレベルとする。これにより、増幅MOSトランジスタ5の入力ノードがリセットレベルの電位である時の画素信号が垂直信号線7に出力される。スイッチパルスSW1、CをHレベルとする。スイッチパルスCがHレベルとなる事により、スイッチSW4とスイッチSW5がオンとなる。スイッチパルスSW1をHレベルとして、オペアンプ8の出力端子と入力端子とをショートさせることにより、オペアンプ8のリセットを行う。スイッチパルスCをHレベルとすることによりクランプ容量C4のリセットを行う。また、時刻t11において、選択パルスSELをHレベルとし、増幅MOSトランジスタ5の入力ノードのリセットレベルの電位に基づいて垂直信号線7に画素信号が出力される。

#### 【0031】

時刻t12において、リセットパルスR、スイッチパルスSW1、CをLレベルとする。クランプ容量C0、C3、C4には、スイッチパルスSW1、CがLレベルとなるときの電位がそれぞれ保持される。リセットパルスRがHレベルからLレベルに遷移する時、リセットMOSトランジスタ4で生じるチャージインジェクションによって増幅MOSトランジスタ5の入力ノードの電位が変化する。これにより、垂直信号線7に出力される画素信号の信号レベルも変化する。この時刻t12において出力される画素信号を、以下N信号と表記する。同様に受光部が入射光を光電変換した信号電荷を保持した増幅MOSトランジスタ5の入力ノードの電位に基づいて垂直信号線7に出力される画素信号をS信号と以下表記する。オペアンプ8はクランプ容量C0を介して与えられた信号

10

20

30

40

50

を増幅してクランプ容量 C 3 に出力する。クランプ容量 C 3 に与えられる信号は、クランプ容量 C 0 を介して画素 1 0 0 から出力された信号を増幅した信号に、オペアンプ 8 のオフセット信号 V o f f が重畠されている。比較回路 9 には、クランプ容量 C 3 を介してオペアンプ 8 が出力した信号が与えられる。

#### 【 0 0 3 2 】

時刻 t 1 3 において、ランプ信号発生回路 1 0 はランプ信号 V R A M P の変化を開始する。比較回路 9 はクランプ容量 C 3 を介してオペアンプ 8 から出力された信号と、ランプ信号発生回路 1 0 から供給されるランプ信号 V R A M P との比較動作を開始する。また、カウンタ回路 1 1 は、ランプ信号発生回路 1 0 がランプ信号 V R A M P の変化を開始すると同時にクロックパルス信号 C L K の計数を開始し、計数結果であるカウント信号をメモリ 1 3 に出力する。10

#### 【 0 0 3 3 】

例えば、クランプ容量 C 3 を介してオペアンプ 8 から出力されている信号と、ランプ信号 V R A M P との大小関係が、時刻 t 1 4 で逆転したとする。すると、比較回路 9 はラッチ信号 L A T を出力する。このラッチ信号 L A T が出力されたカウンタ回路 1 1 は、カウント信号のメモリ 1 3 への出力を停止する。メモリ 1 3 はこの時刻 t 1 4 でのカウント信号を保持する。ランプ信号発生回路 1 0 は時刻 t 1 5 でランプ信号 V R A M P を変化させるのを終了する。後述する S 信号をデジタル信号に変換する場合に比して、この N 信号をデジタル信号に変換する場合はランプ信号 V R A M P を変化させる時間を短縮している。これは一般的に、N 信号はノイズ成分やオフセット成分が主であるために、N 信号の信号範囲が、S 信号の信号範囲に比して狭いことによるものである。したがって、ランプ信号 V R A M P を変化させる時間を短いものとすることができる。このようにすることによって、1 行の画素が出力する画素信号の変換動作に掛かる時間を短縮することができる。20

#### 【 0 0 3 4 】

この時刻 t 1 3 から時刻 t 1 5 までにおいて行われる比較回路 9 、カウンタ回路 1 1 、メモリ 1 3 の動作によって、オペアンプ 8 からクランプ容量 C 3 を介して出力されたアナログ信号が、デジタル信号に変換される。時刻 t 1 3 から時刻 t 1 5 までにおいて行う、比較回路 9 、カウンタ回路 1 1 、メモリ 1 3 が行う動作を総称して、以下 N 変換と表記する。この N 変換によってメモリ 1 3 に保持されたデジタル信号がデジタル N 信号である。

#### 【 0 0 3 5 】

時刻 t 1 6 において、転送パルス T 1 を H レベルとする。これにより、フォトダイオード 1 において光電変換により生じた信号電荷が増幅 M O S トランジスタ 5 の入力ノードに転送される。よって、垂直信号線 7 には、S 信号の一つである A 信号が出力される（本実施例では、S 信号として A 信号と A + B 信号が時分割で出力される）。A 信号をクランプ容量 C 0 に画素 1 0 0 から出力させた後、転送パルス T 1 を L レベルとする。オペアンプ 8 は、画素 1 0 0 からクランプ容量 C 0 を介して出力される A 信号を増幅し、クランプ容量 C 3 を介して比較回路 9 に出力する。30

#### 【 0 0 3 6 】

時刻 t 1 7 において、ランプ信号発生回路 1 0 はランプ信号 V R A M P の変化を開始する。さらに、比較回路 9 はオペアンプ 8 からクランプ容量 C 3 を介して出力された信号とランプ信号 V R A M P との比較動作を開始する。さらに、カウンタ回路 1 1 も先の N 信号の場合と同様に、ランプ信号 V R A M P が信号レベルの変化を開始すると同時にクロックパルス信号 C L K の計数を開始する。40

#### 【 0 0 3 7 】

例えば、時刻 t 1 8 において、オペアンプ 8 からクランプ容量 C 3 を介して出力された A 信号とランプ信号 V R A M P との大小関係が逆転したとする。すると、比較回路 9 はカウンタ回路 1 1 にラッチ信号 L A T を出力する。このラッチ信号 L A T が出力されたカウンタ回路 1 1 は、カウント信号のメモリ 1 3 への出力を停止する。メモリ 1 3 はこの時刻 t 1 4 でのカウント信号を保持する。ランプ信号発生回路 1 0 は時刻 t 1 9 でランプ信号 V R A M P を変化させるのを終了する。50

## 【0038】

この時刻  $t_{17}$  から時刻  $t_{19}$  までにおいて行われる比較回路 9、カウンタ回路 11、メモリ 13 の動作によって、オペアンプ 8 からクランプ容量 C 3 を介して出力されたアナログ信号が、デジタル信号に変換される。時刻  $t_{17}$  から時刻  $t_{19}$  までにおいて行う、比較回路 9、カウンタ回路 11、メモリ 13 が行う動作を総称して、以下 A 変換と表記する。この A 変換によってメモリ 13 に保持されたデジタル信号がデジタル A 信号である。

## 【0039】

次に、時刻  $t_{20}$  において、N 信号線 15 にデジタル N 信号と、S 信号線 16 にデジタル A 信号とをメモリ 13 から撮像装置の外部に転送する。撮像装置の外部とは、例えば後述するデジタル信号処理回路がある。本実施例ではデジタル N 信号、デジタル A 信号の撮像装置の外部への転送をこの時刻  $t_{20}$  としているが、時刻  $t_{21}$  の転送パルス T 2 と順番が前後しても差し支えない。後述する A + B 変換が終了する時刻  $t_{24}$  までにデジタル A 信号、デジタル N 信号の転送が終了することが好ましい。これにより、後述するデジタル A + B 信号、デジタル N 信号の転送が A + B 変換終了後すぐに行うことができる。

10

## 【0040】

次に、時刻  $t_{21}$  において、転送パルス T 2 を H レベルとする。これにより、フォトダイオード 51 において光電変換により生じた信号電荷が増幅 MOS トランジスタ 5 の入力ノードに転送される。すでに増幅 MOS トランジスタ 5 の入力ノードには、フォトダイオード 1 からの信号電荷が保持されている。従って、転送パルス T 2 を H レベルとすることにより、FD 領域にはフォトダイオード 1、51 の両方からの信号電荷が保持される。垂直信号線 7 には、このフォトダイオード 1、51 の両方の信号電荷が転送された増幅 MOS トランジスタ 5 の入力ノードの電位に基づく信号、すなわち A + B 信号が出力される。従って、オペアンプ 8 には、クランプ容量 C 0 を介して画素 100 から出力された A + B 信号を増幅して出力した信号を、クランプ容量 C 3 を介して比較回路 9 に出力する。

20

## 【0041】

時刻  $t_{22}$  において、ランプ信号発生回路 10 はランプ信号 V R A M P の変化を開始する。さらに、比較回路 9 はオペアンプ 8 からクランプ容量 C 3 を介して出力された信号とランプ信号 V R A M P との比較動作を開始する。さらに、カウンタ回路 11 も先の N 信号の場合と同様に、ランプ信号 V R A M P が信号レベルの変化を開始すると同時にクロックパルス信号 C L K の計数を開始する。

30

## 【0042】

例えば、時刻  $t_{23}$  において、オペアンプ 8 からクランプ容量 C 3 を介して出力された信号とランプ信号 V R A M P との大小関係が逆転したとする。すると、比較回路 9 からカウンタ回路 11 にラッチ信号 L A T が出力される。このラッチ信号 L A T が出力されたカウンタ回路 11 は、カウント信号のメモリ 13 への出力を停止する。メモリ 13 はこの時刻  $t_{23}$  でのカウント信号を保持する。ランプ信号発生回路 10 は時刻  $t_{24}$  でランプ信号 V R A M P を変化させるのを終了する。

## 【0043】

この時刻  $t_{22}$  から時刻  $t_{24}$  までにおいて行われる比較回路 9、カウンタ回路 11、メモリ 13 の動作によって、アナログ信号である、オペアンプ 8 からクランプ容量 C 3 を介して出力された信号がデジタル信号に変換される。時刻  $t_{22}$  から時刻  $t_{24}$  までにおいて行う、比較回路 9、カウンタ回路 11、メモリ 13 が行う動作を総称して、以下 A + B 変換と表記する。この A + B 変換によってメモリ 13 に保持されたデジタル信号がデジタル A + B 信号である。

40

## 【0044】

次に、時刻  $t_{25}$  において、N 信号線 15 に N 変換によって得たデジタル N 信号と、S 信号線 16 に A + B 変換によって得たデジタル A + B 信号とをメモリ 13 から撮像装置の外部に転送する。この撮像装置の外部とは、例えば図 16 に例示した撮像システムの出力信号処理部 155 の一例であるデジタル信号処理回路である。このデジタル信号処理回路は、デジタル A 信号とデジタル N 信号との差分、デジタル A + B 信号とデジタル N 信号と

50

の差分を得る処理や、デジタル A + B 信号とデジタル A 信号との差分を演算して、デジタル B 信号を得る処理などを行う。デジタル B 信号とは、増幅 MOS トランジスタ 5 の入力ノードでフォトダイオード 1 とフォトダイオード 5 1 との信号電荷を合わせず、フォトダイオード 5 1 のみが保持する信号電荷を増幅 MOS トランジスタ 5 の入力ノードが保持した時に出力される B 信号を、A 変換と同様にデジタル信号に変換した場合に得られると想定されるデジタル信号である。デジタル信号処理回路は、デジタル A 信号とデジタル B 信号とを用いて、位相差検出方式の焦点検出を行うことができる。また、各画素から出力される A + B 信号を A + B 変換したデジタル A + B 信号を用いて、画像を形成することができる。また、デジタル A 信号、デジタル A + B 信号に重畠されている画素 100、オペアンプ 8 などから生じるノイズレベルの信号については、デジタル信号処理回路がデジタル N 信号をデジタル A 信号とデジタル A + B 信号のそれぞれから差し引くことによって低減することができる。

10

#### 【0045】

これまで、図 2 で示した撮像装置の 1 行目の画素 100 の画素信号を読み出す動作について説明したが、2 行目の画素についても同様の動作とすることができる。

#### 【0046】

次に、図 2 で示した撮像装置の 3 行目の画素 100 の画素信号を読み出す動作について図 7 (a) を参照しながら説明する。

#### 【0047】

3 行目の画素 100 の画素信号を読み出す場合についても N 変換にかかる動作は 1 行目の画素 100 の画素信号の読み出し動作で説明したものと同様とすることができる。即ち、3 行目の画素 100 の画素信号を読み出す場合の時刻 t31、t32、t33、t34、t35 のそれぞれでの動作は、1 行目の画素信号を読み出す場合の時刻 t11、t12、t13、t14、t15 のそれぞれでの動作と同様とすることができる。

20

#### 【0048】

3 行目の画素 100 は、先の 1 行目の画素 100 の画素信号の読み出し動作において述べた、時刻 t16 における A 信号の転送動作、および、時刻 t17 から時刻 t19 の A 変換の動作は行わない。また、A 変換を行わないと、時刻 t20 におけるデジタル A 信号とデジタル N 信号を転送する動作についても行わない。

#### 【0049】

3 行目の画素 100 については、A + B 信号を画素 100 が出力し、信号処理回路 101 によってデジタル A + B 信号を得る動作を行う。

30

#### 【0050】

3 行目の画素 100 が A + B 信号を出力する動作であるが、まず時刻 t36 において転送パルス T1、T2 をともに H レベルとする。これにより、フォトダイオード 1 と、フォトダイオード 5 1 とにおいて光電変換によって生じた信号電荷が増幅 MOS トランジスタ 5 の入力ノードに転送される。これによりフォトダイオード 1 とフォトダイオード 5 1 とから転送された信号電荷を保持した増幅 MOS トランジスタ 5 の入力ノードの電位に基づいた信号、すなわち A + B 信号が画素 100 から垂直信号線 7 に出力される。以降、A + B 信号をデジタル信号に変換する A + B 変換に関わる動作は、1 行目の画素 100 の画素信号を読み出す場合の A + B 変換を行う動作と同様とすることができる。すなわち、3 行目の画素 100 の画素信号を A + B 変換する場合の時刻 t37、t38、t39 における動作は、1 行目の画素 100 の画素信号を A + B 変換する場合の時刻 t22、t23、t24 における動作と同様とすることができる。

40

#### 【0051】

時刻 t40 で行う、A + B 変換によって得られたデジタル A + B 信号をメモリ 13 から転送する動作についても、1 行目の画素 100 からの画素信号を読み出す場合の時刻 t25 における動作と同様とすることができる。

#### 【0052】

このように、3 行目の画素 100 の画素信号を読み出す場合は、A 信号の読み出し動作

50

を行わず、A + B 信号のみの読み出し動作を行う。従って、A 信号の読み出し動作、A 変換を行う動作を行わないため、これらの動作に掛かる時間を短縮することができる。即ち、3 行目の画素 100 の画素信号を読み出す場合は、1 行目の画素 100 の画素信号を読み出す場合における、時刻 t16 から時刻 t19 までの期間を短縮することができる。従つて、撮像装置の全行の画素 100 において A 信号および A + B 信号を読み出す動作を行う場合に比べて、A 信号の出力を行わない画素 100 を有することにより、アナログデジタル変換動作に関わる期間を短縮することができる。また、A 信号の出力を行わない画素 100 を有することで、1 フレーム期間で複数列のメモリ 13 がデジタル A 信号を出力する回数が減る。よって、撮像装置からデジタル信号を読み出す時間を短縮することができる。

10

#### 【0053】

図 7 (b) は、垂直同期信号 VD、画素部の各行に与えられる選択パルス SEL の合計期間である SEL-T、複数列のメモリ 13 から出力される期間である SIGOUT-T を表したタイミング図である。垂直同期信号 VD を H レベルとした後、垂直走査回路 2 は各行の画素 100 に対応する選択パルス SEL を順次 H レベルとする。水平走査回路 14 は各列の信号処理回路 101 からデジタル信号を順次出力させる。先述したように、垂直同期信号 VD が H レベルとなってから、次に H レベルとなるまでの期間が 1 フレームである。この 1 フレーム期間内に、撮像装置から画素信号に基づく信号であるデジタル N 信号、デジタル A 信号、デジタル A + B 信号が出力される。

#### 【0054】

A 信号と B 信号とを読み出す場合には、画素 100 が A 信号の出力を行った後、リセットパルス R をもう一度 H レベルとして L レベルとし、増幅 MOS トランジスタ 5 の入力ノードの電位をリセットしてから転送パルス T2 を H レベルとする必要がある。即ち、リセットパルス R を図 6 で説明した動作タイミング図において、時刻 t19 から時刻 t21 までの間に H レベルとし、さらに L レベルに戻す動作が必要となる。本実施例では、リセットパルス R を H レベルとするのは時刻 t11 から時刻 t12 までの期間とすることができるので、より高速に画素信号の出力動作を行うことができる。

20

#### 【0055】

本実施例では、1 行目の画素 100 から N 信号、A 信号、A + B 信号を出力させてから、2 行目の画素 100 から N 信号、A 信号、A + B 信号を出力させている。この形態と、1 行目、2 行目の画素 100 から N 信号、A 信号を出力させ、次に 1 行目～4 行目の画素 100 から順次 A + B 信号を出力させる形態（以下、この形態を参考形態と表記する）と比較する。参考形態では、1 行目の画素 100 から N 信号を出力させてから 1 行面の画素 100 の A + B 信号を得るまでに、1、2 行目の A 信号を読み出す期間が存在する。従つて、本実施例の形態に比して参考形態では、1 行目の N 信号を読み出してから 1 行目の A + B 信号を出力させるまでの期間が長くなる。これにより、1 行目の画素 100 が N 信号を出力した時のノイズレベルから、1 行目の画素 100 が A + B 信号を出力する時のノイズレベルとの差が生じやすくなる。すなわち、A + B 信号へのランダムノイズの影響が大きくなる。従つて、参考形態は本実施例の形態に比して画質および測距精度が低下しやすくなる。本実施例の形態では、例えば 1 行目の画素 100 の N 信号を出力した後、他の行の画素 100 からの読み出し動作に移る前に 1 行目の画素 100 からの A + B 信号を得る。このため、参考形態に比して A + B 信号へのランダムノイズの影響を抑制することができ、画質および測距精度を向上させることができる。また、参考形態では A + B 信号に加えて A 信号を出力する画素 100 を含む行は、A 信号の出力と、A + B 信号の出力とで 2 度垂直走査を行う。本実施例の形態では、1 度の垂直走査で 1 行の画素 100 から A 信号と A + B 信号との出力をを行う。これにより、本実施例の形態は参考形態に比して垂直走査に関わる時間を短縮することができる。

30

#### 【0056】

本実施例では、1 行目の画素信号を読み出す場合において、デジタル A 信号、デジタル N 信号の転送に関わる時間が、A + B 変換におけるランプ信号 VRAMP が変化する時間

40

50

よりも短い例を記載した。しかし、デジタルA信号、デジタルN信号の転送に関わる時間が、A+B変換におけるランプ信号VRAMPが変化する時間よりも、時間Tだけ長い形態であってもよい。この形態では、3行目の画素信号を読み出す際、A信号の読み出し動作、A変換を行う動作に関わる期間に加えて、この時間Tの期間も短縮することができる。

#### 【0057】

本実施例は、それぞれの信号処理回路101にカウンタ回路11が含まれている形態を示した。別の形態として、カウンタ回路11が信号処理回路101とは別に設けられていて、各列の信号処理回路101に共通してカウント信号CKnを出力する、いわゆる共通カウンタ型のアナログデジタル変換回路であっても良い。図8に共通カウンタ型のアナログデジタル変換回路の一例を示す。カウンタ回路11にはTG12からクロックパルス信号CLKが供給されている。カウンタ回路11は、クロックパルス信号CLKに基づいてnビットのカウント信号CKnを生成する。カウンタ回路11は、各列のメモリ13に共通してカウント信号CKnを出力する。メモリ13は、比較回路9からラッチ信号LATが出力された時に、カウンタ回路11から出力されているカウント信号CKnの取り込みを行う。このような共通カウンタ型のアナログデジタル変換回路においても、本実施例を好適に実施することができる。

#### 【0058】

また、本実施例では、画素100が2個の光電変換部に基づく信号であるA+B信号と、1個の光電変換部に基づく信号であるA信号とを出力する形態を基に説明した。本実施例はこの形態に限定されるものではない。つまり、複数の画素の各々が有するm個（mは整数）の光電変換部に基づいた第1の画素信号を出力する。そして、この第1の画素信号を出力した複数の画素のうちの一部の画素が、m個よりも少ないn個（nは整数）の光電変換部に基づいた第2の画素信号をさらに出力する形態であれば好適に実施することができる。この形態であれば、全行の画素において第1の画素信号および第2の画素信号を読み出す動作を行う場合に比べて、第1の画素信号の出力を行わない画素を有することにより、アナログデジタル変換動作に関わる時間を短縮することができる。また、1フレーム期間で複数列のメモリ13が第1の画素信号に基づくデジタル信号を出力する回数が減る。よって、撮像装置からのデジタル信号を読み出す時間を短縮することができる。また、m個の光電変換部は、1つの画素100が有する光電変換部の数よりも少ない数であっても良い。つまり、本実施例の撮像装置は、1つの画素100が有する光電変換部の数がj個（jは整数）であるとすると、 $j > m$ の関係にある形態であれば良い。

#### 【0059】

また、本実施例では、図7（b）のように1フレーム期間は、垂直同期信号VDが1度Hレベルとなった後、次にHレベルとなるまでの期間である形態を説明した。他の形態として、例えばインターレース方式の信号出力形態のように、偶数行の画素100から画素信号を出力させるフィールドと、奇数行の画素100から画素信号を出力させるフィールドとを1フレーム期間が有する形態であってもよい。つまり、1フレーム期間に、垂直走査回路2が複数の画素100の選択を複数のフィールドに分割して行う形態であっても良い。さらに言えば、必ずしも偶数行、奇数行とでフィールドを分ける必要はなく、ある行については第1のフィールド、他の行については第2のフィールドで画素信号を出力させる形態であっても良い。

#### 【0060】

##### [実施例2]

本実施例の一つは、実施例1で例示した撮像装置において、図1（b）のように、A信号とA+B信号とを出力する画素100とA+B信号のみを出力する画素100のそれぞれが、画素部のすべての行に含まれている形態である。

#### 【0061】

本実施例における水平走査回路14は、各列のメモリ13を順に走査する動作以外に、

10

20

30

40

50

複数列のメモリ 1 3 からデジタル信号を転送させるメモリ 1 3 を選択して転送させることができるデコーダである。

#### 【 0 0 6 2 】

図 9 ( a ) は、図 1 ( b ) に例示した撮像装置の一部の画素 1 0 0 を抜き出して模式的に示したものである。図 9 ( a ) に示した全画素から A 信号と A + B 信号が出力される。ただし、1 行目、2 行目ともに、2 列目、3 列目の画素が出力した A 信号と A + B 信号を利用し、1 列目、4 列目が出力した A 信号は使用せず、A + B 信号のみを利用する。

#### 【 0 0 6 3 】

1 行目の画素 1 0 0 から画素信号を読み出す動作について、実施例 1 と異なる点を中心に説明する。

10

#### 【 0 0 6 4 】

本実施例における、画素 1 0 0 、信号処理回路 1 0 1 の動作は、実施例 1 で説明した、図 2 で例示した撮像装置の 1 行目の動作、即ち図 6 に例示した動作と同様のものとすることができる。このように動作させることにより、本実施例の撮像装置では、画素 1 0 0 から画素信号が転送されるすべてのメモリ 1 3 に N 信号、A 信号、A + B 信号が保持される。

#### 【 0 0 6 5 】

図 9 ( b ) は、本実施例の水平走査回路であるデコーダ 1 4 が転送する信号を模式的に示したものである。メモリ 1 3 - 1 ~ 1 3 - 4 のそれぞれには図 9 ( a ) で例示した撮像装置の 1 列目 ~ 4 列目のそれぞれの画素 1 0 0 の画素信号に基づいたデジタル信号が保持されている。以下、1 列目のメモリ 1 3 - 1 が保持しているデジタル信号については、デジタル N 信号は、N 1 、デジタル A 信号は A 1 、デジタル A + B 信号については A 1 + B 1 と、各デジタル信号を図の左から数えた列番号を付して表記する。2 列目から 4 列目についても同様である。

20

#### 【 0 0 6 6 】

デコーダ 1 4 はまず、2 列目のメモリ 1 3 - 2 を選択し、メモリ 1 3 - 2 から N 2 と A 2 をデジタル信号処理回路に出力させる。デジタル信号処理回路は出力された N 2 と A 2 の差分信号である、( A 2 - N 2 ) を取得する。続いて、3 列目のメモリ 1 3 - 3 を選択し、メモリ 1 3 - 3 から N 3 と A 3 をデジタル信号処理回路に出力させる。デジタル信号処理回路は、2 列目のメモリ 1 3 - 2 の場合と同様に、N 3 と A 3 との差分信号である、( A 3 - N 3 ) を取得する。

30

#### 【 0 0 6 7 】

続いて、デコーダ 1 4 は、各列のメモリ 1 3 - 1 ~ 1 3 - 4 を順に選択してデジタル A + B 信号をデジタル信号処理回路に出力させる。つまり、1 列目のメモリ 1 3 - 1 を選択し、メモリ 1 3 - 1 から N 1 と A 1 + B 1 をデジタル信号処理回路に出力させる。デジタル信号処理回路は N 1 と A 1 + B 1 との差分信号である、( A 1 + B 1 - N 1 ) を取得する。2 列目 ~ 4 列目のメモリ 1 3 - 2 ~ 1 3 - 4 についても同様の動作を行う。また、デジタル信号処理回路についても 1 列目のメモリ 1 3 - 1 から N 1 と A 1 が出力された場合と同様の動作を行う。これにより、差分信号 ( A 2 + B 2 - N 2 ) 、( A 3 + B 3 - N 3 ) 、( A 4 + B 4 - N 4 ) をそれぞれ取得する。

40

#### 【 0 0 6 8 】

引き続いてデジタル信号処理回路は、2 列目のメモリ 1 3 - 2 から N 2 と A 2 を出力させて得た差分信号 ( A 2 - N 2 ) と、N 2 、A 2 + B 2 を出力させて得た差分信号 ( A 2 + B 2 - N 2 ) との差分を取得する。即ち、( A 2 + B 2 - N 2 ) - ( A 2 - N 2 ) の処理を行い、B 2 を取得する。3 列目のメモリ 1 3 - 3 についても同様の処理を行い、B 3 を取得する。よって、1 行目の 2 列目、3 列目の画素 1 0 0 が出力した画素信号に基づいて、A 2 と B 2 、および、A 3 と B 3 を得ることができる。この A 2 と B 2 、および、A 3 と B 3 を用いて位相差検出方式の焦点検出を行うことができる。これまで 1 行目の画素 1 0 0 についての動作を説明したが、同様の動作を 2 行目の画素 1 0 0 についても同様の動作とすることができます。

50

**【 0 0 6 9 】**

本実施例では、1列目と4列目のメモリ13-1、13-4からN1とA1、および、N4とA4とを出力させる動作を行っていない。従って、このN1とA1、および、N4とA4とを出力させるのに要する時間を本実施例では短縮することができる。従って、A+B信号を得つつ、A信号を得る動作を高速に行うことができる。

**【 0 0 7 0 】**

次に本実施例の別の一つである、図1(c)に例示した撮像装置について説明する。これは、撮像装置の複数行、複数列の画素のうち、一部の領域に含まれる画素がA信号とA+B信号とを出力するように動作する形態である。即ち、図1(b)に例示した撮像装置に対し、A信号を出力しない行を含む形態である。

10

**【 0 0 7 1 】**

図1(c)に例示した撮像装置について、A信号を出力しない行の画素100からの画素信号を読み出す動作は、実施例1において図7を参照しながら説明した動作と同様として、N変換とA+B変換を行うことができる。

**【 0 0 7 2 】**

また、A信号も出力する行の画素100からの画素信号の読み出し動作は、本実施例でこれまで説明した通りの動作とすることができます。即ち、実施例1で図6を参照しながら説明した動作によりN変換、A変換、A+B変換を行う。さらに、図9(b)を参照しながら説明した通り、A信号も出力する画素100からの画素信号に基づくデジタルA信号、デジタルN信号を保持するメモリ13からそれぞれのデジタル信号をデジタル信号処理回路に出力させる。その後、デジタルA+B信号を保持しているメモリ13から、デジタルN信号とデジタルA+B信号とをデジタル信号処理回路に出力させる。これにより、デジタル信号処理回路は、デジタルA信号を出力した列についてはデジタルB信号を求めて位相差検出方式の焦点検出を行うとともに、デジタルA+B信号を用いて画像の形成を行う。

20

**【 0 0 7 3 】**

図1(c)に例示した撮像装置の場合では、A信号を出力しない行の画素100の画素信号の読み出し動作においては、A変換を行わないため、A変換に関わる時間を短縮することができる。また、A信号も出力する行についても、図1(b)で例示した撮像装置の場合と同様に、デジタルA信号のデジタル信号処理回路への出力を行わない列を含む。よって、デジタルA信号のメモリ13からデジタル信号処理回路への出力に関わる時間を短縮することができる。従って、A+B信号を得つつ、A信号を得る動作を高速に行うことができる。

30

**【 0 0 7 4 】**

本実施例では、図1(b)、図1(c)のようにA信号およびA+B信号を出力するように動作する形態について説明した。しかし、本実施例はこれに限定されず、例えば、カラーフィルター22の色に応じてA信号を出力する画素100を選択しても良い。例えば、図2で例示した撮像装置において、G(緑)のカラーフィルター22を有する画素100がA信号を出力する画素とする場合には、1行目および3行目は1列目と3列目、2行目及び4行目は2列目と4列目の画素100がA信号を出力する。このA信号の出力動作についても、本実施例および実施例1で図6を参照しながら説明した動作に基づいて行うことができる。また、メモリが保持したデジタル信号の読み出しについては、本実施例で図9(b)を参照しながら説明したように動作させればよい。このように動作させることで、カラーフィルター22の色に応じてA信号も出力する画素100を選択する場合にも、A+B信号を得つつ、A信号を得る動作を高速に行うことができる。

40

**【 0 0 7 5 】**

また、実施例1、実施例2で説明した図1(a)～(c)のA信号を出力する画素100の配置は、TG12によって可変的に設定することができる。他の形態として、撮像装置の外部からのシリアル通信などによって撮像装置に供給される設定情報に基づいて設定しても良い。この撮像装置の外部とは、例えば後述する図16に例示した撮像システムの

50

全体制御・演算部 1510 が挙げられる。また、A 信号を出力する画素 100 の配置は、例えば光学的基線長や、使用する測距点に基づいて設定すれば良い。

#### 【0076】

また、本実施例では、画素 100 が 2 個の光電変換部に基づく信号である A + B 信号と、1 個の光電変換部に基づく信号である A 信号とを出力する形態を基に説明した。本実施例はこの形態に限定されるものではない。つまり、1 フレーム期間内に、複数の画素の各々は、各々が有する m 個 (m は整数) の光電変換部の信号電荷に基づいた第 2 の信号を出力する。そして、複数の画素の少なくとも一部の画素の各々は、各々が有する m 個よりも少ない n 個 (n は整数) の光電変換部の信号電荷に基づいた第 1 の信号をさらに出力する。

撮像装置は、この 1 フレーム期間内に、複数の画素の第 2 の信号に基づく信号を出力し、複数の画素の一部の画素の第 1 の信号に基づく信号をさらに出力する。この形態であれば好適に実施することができる。この形態であれば、全画素からの第 2 の信号と第 1 の信号とのそれぞれに基づく信号をそれぞれ撮像装置が出力する場合に比べて、第 1 の信号に基づく信号の出力に関わる期間を短縮することができる。よって、撮像装置からのデジタル信号を読み出す時間を短縮することができる。10

#### 【0077】

また、本実施例では、水平走査回路 14 がデコーダであり、一部のメモリ 13 から A 信号を出力する形態を説明した。他の形態として、図 10 で例示したように、1 行の画素 100 に対してフォトダイオード 1 に複数の転送パルス T1 - 1、T1 - 2 が垂直走査回路 2 から与えられる構成としても良い。すなわち、1 行の画素 100 のうち、A 信号、A + B 信号を出力する画素 100 については転送パルス T1 - 1 を H レベルとし、その後、転送パルス T2 を H レベルとする。一方、A + B 信号のみを出力させる画素 100 については、T1 - 1 を H レベルとせず、転送パルス T2 が H レベルとなっている間に転送パルス T1 - 2 を H レベルとすれば良い。また、別の形態として、転送パルス T1 を複数設ける代わりに、1 行の画素を選択する選択パルス SEL を、1 行の画素 100 について複数の選択パルス SEL - 1、SEL - 2 のいずれかを与える形態であっても良い。つまり、A 信号、A + B 信号を出力する画素については、転送パルス T1、T2 が H レベルの間に H レベルとなる選択パルス SEL - 1 を与える。そして、A + B 信号のみを出力する画素 100 については、転送パルス T1 の期間には L レベルであり、転送パルス T2 が H レベルの時に H レベルとなる選択パルス SEL - 2 を与える形態であっても良い。これらの形態は、或る行の画素 100 から、m 個の光電変換部の信号電荷に基づく信号と、m 個よりも少ない n 個の光電変換部の信号電荷に基づく信号とを出力させる期間に、同じ行の別の画素から、n 個の光電変換部の信号電荷に基づく信号を出力させず、m 個の光電変換部の前記信号電荷に基づく前記信号を出力させる垂直走査回路を有する形態である。20

30

#### 【0078】

##### [実施例 3]

本実施例に係る撮像装置の等価回路を図 11 に例示する。本実施例の撮像装置は、画素 100 に含まれるフォトダイオード 1 とフォトダイオード 51 とがそれぞれ別の増幅 MOS トランジスタ 5 - 1、5 - 2 の入力ノードに信号電荷を転送する形態である。実施例 1 の画素は、2 つのフォトダイオードが 1 つの増幅 MOS トランジスタ 5 によって垂直信号線 7 に画素信号が出力されていた。これに対し、本実施例では、垂直信号線に A 信号を出力する画素と B 信号を出力する画素とが設けられている。即ち、同一のマイクロレンズを透過した光を受ける 2 つのフォトダイオードは、互いに異なる増幅 MOS トランジスタを介して互いに異なる垂直信号線に画素信号を出力する。この A 画素と B 画素とのそれぞれに電気的に接続された垂直信号線 7 - 1、7 - 2 はノード A で電気的に接続されている。このノード A で電気的に接続された垂直信号線に画素信号を出力する A 画素と B 画素とによって、A + B 信号を出力する 1 つの画素が構成される。40

#### 【0079】

さらに、本実施例では、実施例1で例示した撮像装置が有していたオペアンプ8を有していない形態である。オペアンプ8については本実施例においても、画素100から出力される画素信号を増幅させる場合には、実施例1で説明した撮像装置と同様に比較回路9の前段に設けることができる。

#### 【0080】

以下、図11を参照しながら説明する。尚、図4に例示した撮像装置で示した構成と同じ機能を奏するものについては、図4で付した符号と同じ符号を図11でも付している。また、A画素とB画素とがそれぞれ同じ機能を奏するものを有している場合には枝番を付して示している。例えば、増幅MOSトランジスタはA画素については5-1、B画素については5-2として付している。以下、リセットMOSトランジスタ4、選択MOSトランジスタ6、垂直信号線7、クランプ容量C0についても同様である。リセットMOSトランジスタ4-1、4-2は共通のリセットパルスRが供給される。また、転送MOSトランジスタ20、50についても共通の転送パルスT1が供給される。また、選択MOSトランジスタ6-1、6-2についても、共通の選択パルスSELが供給される。

10

#### 【0081】

A画素とB画素のそれぞれが有する選択MOSトランジスタ6-1、6-2はそれぞれが垂直信号線7-1、7-2に電気的に接続されている。垂直信号線7-1、7-2はノードAで電気的に接続されている。また、垂直信号線7-2は、スイッチSW6が設けられている。このスイッチSW6は、B画素からのB信号の、クランプ容量C0-2を介して比較回路9への出力を切り替えるスイッチである。すなわち、スイッチSW6がオンである時には、B信号がクランプ容量C0-2を介して比較回路9に出力され、スイッチSW6がオフである時には比較回路にB信号は出力されない。尚、本実施例ではノードAから比較回路9に至る信号線を垂直信号線7と呼び、A画素、B画素のそれぞれに電気的に接続された垂直信号線7-1、7-2と区別する。

20

#### 【0082】

以下では、図1(a)を用いて説明した実施例1と同様に、一部の行において全ての画素がA信号とA+B信号とを出力する形態を説明する。また、図1(a)においてAとA+Bとを併記した領域の画素は、A信号を出力した後、A+B信号を出力する。図1(a)においてA+Bのみを記した領域の画素は、A信号を出力せずに、A+B信号の出力をを行う。

30

#### 【0083】

次に、図12(a)に図11に例示した撮像装置のうち、A信号とA+B信号とを出力する行の動作タイミングの一例を示す。図12(a)中に示したスイッチパルスS1は、図11で例示したスイッチSW6のオン、オフを切り替えるパルス信号である。S1がHレベルの時にスイッチSW6はオンであり、S1がLレベルの時にスイッチSW6はオフである。

#### 【0084】

時刻t60において、リセットパルスRをHレベルとする。また、時刻t60において、選択パルスSEL、スイッチパルスC、S1をHレベルとする。この動作により、増幅MOSトランジスタ5-1、5-2の入力ノード、クランプ容量C0-1、C0-2、C4の電荷がリセットされる。

40

#### 【0085】

時刻t61において、リセットパルスR、スイッチパルスCをLレベルとする。スイッチパルスS1は引き続きHレベルのままである。

#### 【0086】

時刻t62からN変換を行う。ランプ信号発生回路10はランプ信号VRAMPの変化を開始する。比較回路9は垂直信号線7にクランプ容量C0-1、C0-2を介して与えられたN信号と、ランプ信号発生回路10から供給されるランプ信号VRAMPとの比較動作を開始する。また、カウンタ回路11は、ランプ信号発生回路10がランプ信号VR

50

A M P の変化を開始すると同時にクロックパルス信号 C L K の計数を開始し、計数結果であるカウント信号をメモリ 1 3 に出力する。

#### 【 0 0 8 7 】

例えば、ノード A に出力された N 信号と、ランプ信号 V R A M P との大小関係が、時刻 t 6 3 に逆転したとする。すると、比較回路 9 が出力するラッチ信号 L A T が変化する。このラッチ信号 L A T が変化すると、カウンタ回路 1 1 はカウント信号のメモリ 1 3 への出力を停止する。メモリ 1 3 はこの時刻 t 6 3 でのカウント信号を保持する。ランプ信号発生回路 1 0 は時刻 t 6 4 でランプ信号 V R A M P を変化させるのを終了する。また、スイッチパルス S 1 は時刻 t 6 4 に L レベルとする。

#### 【 0 0 8 8 】

時刻 t 6 5 において、転送パルス T 1 を H レベルとする。フォトダイオード 1 から増幅 M O S トランジスタ 5 - 1 、フォトダイオード 5 1 から増幅 M O S トランジスタ 5 - 2 のそれぞれの入力ノードに信号電荷が転送される。これにより垂直信号線 7 - 1 には A 信号、垂直信号線 7 - 2 には B 信号が出力される。スイッチパルス S 1 は L レベルであるので、ノード A には A 信号が出力される。

10

#### 【 0 0 8 9 】

時刻 t 6 6 から A 変換を行う。ランプ信号発生回路 1 0 はランプ信号 V R A M P の変化を開始する。比較回路 9 は垂直信号線 7 に出力された A 信号とランプ信号 V R A M P との比較動作を開始する。さらに、カウンタ回路 1 1 も先の N 信号の場合と同様に、ランプ信号 V R A M P が信号レベルの変化を開始すると同時にクロックパルス信号 C L K の計数を開始する。

20

#### 【 0 0 9 0 】

例えば、ノード A に出力された A 信号とランプ信号 V R A M P との大小関係が、時刻 t 6 7 に逆転したとする。すると、比較回路 9 が出力するラッチ信号 L A T が変化する。このラッチ信号 L A T が変化すると、カウンタ回路 1 1 はカウント信号のメモリ 1 3 への出力を停止する。メモリ 1 3 はこの時刻 t 1 4 でのカウント信号を保持する。ランプ信号発生回路 1 0 は時刻 t 6 8 でランプ信号 V R A M P を変化させるのを終了する。

#### 【 0 0 9 1 】

時刻 t 6 8 にランプ信号 V R A M P の変化が終了した後、先の N 変換と A 変換によって得たデジタル N 信号とデジタル A 信号とをデジタル信号処理部に転送する。本実施例ではこのデジタル N 信号、デジタル A 信号のデジタル信号処理部への転送を時刻 t 7 0 としているが、時刻 t 6 9 のスイッチパルス S 1 と順番が前後しても差し支えない。後述する A + B 変換が終了する時刻 t 7 3 までにデジタル A 信号、デジタル N 信号の転送が終了することが好ましい。これにより、後述するデジタル A + B 信号、デジタル N 信号の転送が A + B 変換終了後すぐに行うことができる。

30

#### 【 0 0 9 2 】

時刻 t 6 9 において、スイッチパルス S 1 を H レベルにする。これにより、ノード A には A + B 信号が出力される。

#### 【 0 0 9 3 】

時刻 t 7 1 において、A + B 変換を開始する。ランプ信号発生回路 1 0 はランプ信号 V R A M P の変化を開始する。さらに、比較回路 9 は垂直信号線 7 に出力された A + B 信号とランプ信号 V R A M P との比較動作を開始する。さらに、カウンタ回路 1 1 も先の N 信号の場合と同様に、ランプ信号 V R A M P が信号レベルの変化を開始すると同時にクロックパルス信号 C L K の計数を開始する。

40

#### 【 0 0 9 4 】

例えば、垂直信号線 7 に出力された A + B 信号とランプ信号 V R A M P との大小関係が、時刻 t 7 2 に逆転したとする。すると、比較回路 9 からカウンタ回路 1 1 にラッチ信号 L A T が出力される。このラッチ信号 L A T が出力されたカウンタ回路 1 1 は、カウント信号のメモリ 1 3 への出力を停止する。メモリ 1 3 はこの時刻 t 7 2 でのカウント信号を保持する。ランプ信号発生回路 1 0 は時刻 t 7 3 でランプ信号 V R A M P を変化させるの

50

を終了する。

**【0095】**

時刻 t 7 4 に、デジタル A + B 信号とデジタル N 信号とをデジタル信号処理回路に転送する。

**【0096】**

次に、図 1 2 ( b ) に、図 1 1 に例示した撮像装置のうち、A 信号を出力しない行の動作タイミングの一例を例示する。

**【0097】**

時刻 t 8 0 、 t 8 1 、 t 8 2 、 t 8 3 のそれぞれは、A 信号および A + B 信号を出力する行の動作タイミングで説明した時刻 t 6 0 、 t 6 1 、 t 6 2 、 t 6 3 のそれと同様の動作とすることができます。10

**【0098】**

時刻 t 8 4 において、N 変換におけるランプ信号 V R A M P の変化を終了する。先の A 信号および A + B 信号を出力する行の動作においては、スイッチパルス S 1 をここで L レベルとしたが、A 信号を出力しない行については引き続き H レベルとする。

**【0099】**

時刻 t 8 5 における動作は、先の A 信号および A + B 信号を出力する行の動作タイミングにおける時刻 t 6 5 と同様である。転送パルス T 1 を H レベルとすることにより、増幅 M O S トランジスタ 5 - 1 、 5 - 2 のそれぞれの入力ノードに、フォトダイオード 1 、 5 1 のそれからの信号電荷が転送される。スイッチパルス S 1 は H レベルであるので、垂直信号線 7 には A + B 信号が出力される。20

**【0100】**

時刻 t 8 6 、 t 8 7 、 t 8 8 、 t 8 9 のそれにおける動作は、先の A 信号および A + B 信号を出力する行の動作タイミングで説明した時刻 t 7 1 、 t 7 2 、 t 7 3 、 t 7 4 のそれと同様の動作とすることができます。

**【0101】**

A 信号を出力しない行の動作は、実施例 1 で述べたのと同様に、A 変換に関わる動作を行う時間、即ち A 信号を出力する画素を含む行の動作タイミングの時刻 t 6 6 ~ t 6 8 の時間を短縮することができます。

**【0102】**

本実施例の撮像装置は、A 信号の出力を行わない画素 1 0 0 を有する。これにより、撮像装置の全行の画素 1 0 0 が A 信号および A + B 信号を出力する動作を行なう場合に比べて、1 フレーム期間内の撮像装置からのデジタル信号を出力する時間を短縮することができます。30

**【0103】**

本実施例は図 1 ( a ) のように、一部の行において全ての画素が A 信号および A + B 信号を出力する形態について説明した。本実施例は図 1 ( a ) の読み出し方に限定されず、図 1 ( b ) 、図 1 ( c ) に例示した形態であっても、水平走査回路 1 4 としてデコーダを用いて実施することができます。その際には、本実施例で説明した A 信号および A + B 信号を出力する行の動作タイミングを図 1 ( b ) 、 ( c ) で例示した撮像装置の全行において行なう。メモリ 1 3 に保持されたデジタル N 信号、デジタル A 信号、デジタル A + B 信号については、実施例 2 と同様の動作で読み出せばよい。40

**【0104】**

本実施例の撮像装置においても、A + B 信号を得つつ、A 信号を得る動作を高速に行なうことができる。

**【0105】**

[ 実施例 4 ]

本実施例は、垂直信号線 7 のそれぞれに比較回路 9 、カウンタ回路 1 1 を有しておらず、メモリ 1 3 は画素 1 0 0 から出力される画素信号に基づいて、デジタル信号ではなく、アナログ信号である電圧値を保持する形態である。50

**【0106】**

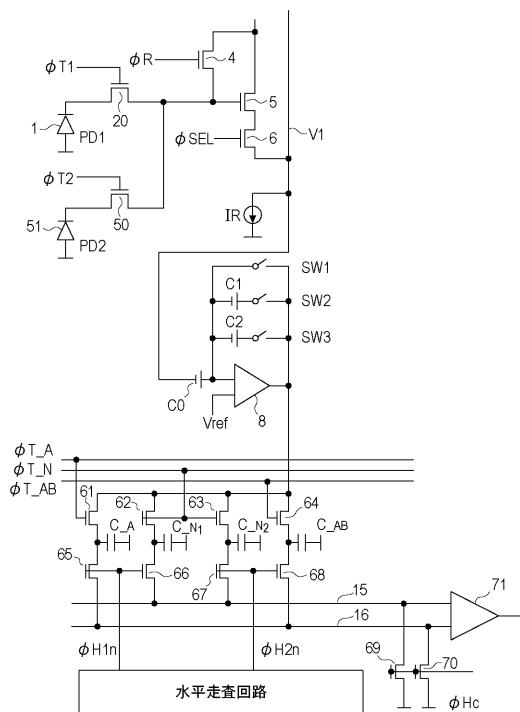

図13は本実施例に関する撮像装置の構成の一例を示したものである。尚、図4に例示した撮像装置と同じ機能を奏する者については、図4に付した符号と同じ符号を図13でも付している。

**【0107】**

本実施例の画素100、オペアンプ8については、実施例1と同様の画素100、オペアンプ8を用いることができる。

**【0108】**

容量C\_N1、C\_N2はともにオペアンプ8がN信号を増幅して出力した信号VNを保持する信号保持容量である。また、容量C\_A、C\_ABは、それぞれオペアンプ8がA信号、A+B信号をそれぞれ増幅した信号VA、VABを保持する信号保持容量である。10

本実施例の信号保持部は信号保持容量信号C\_A、C\_N1、C\_N2、C\_ABである。信号VA、VN、VABのそれぞれにはオペアンプ8が有するオフセット信号Vofが重畠されている。

**【0109】**

信号保持容量C\_A、C\_N1、C\_N2、C\_ABのそれぞれは、オペアンプ8からスイッチ61, 62, 63、64のそれぞれを介して各信号が出力される。スイッチ61, 64のゲートにはそれぞれTG12から信号書き込み信号T\_A、T\_ABが供給される。また、スイッチ62、63のゲートにはTG12から信号書き込み信号T\_Nが供給される。スイッチ61、62、63、64は、それぞれのスイッチに供給される信号書き込み信号がHレベルであるとオンとなる。すなわちスイッチ61, 62, 63、64がオンの時に、それぞれ各信号保持容量C\_A、C\_N1、C\_N2、C\_ABに各信号が書き込まれる。信号保持容量C\_N1、C\_N2はそれぞれ画素が有するノイズレベルの信号が保持されるNメモリである。Nメモリは画素の有するノイズレベルの信号を保持する第1のメモリである。また、信号保持容量C\_Aは、画素の一部の光電変換部に基づく画素信号に基づいた信号を保持するS1メモリである。S1メモリは、焦点検出用信号を保持する第2のメモリである。また、信号保持容量C\_ABは、画素の複数の光電変換部に基づく画素信号に基づいた信号を保持するS2メモリである。S2メモリは画像取得用信号を保持する第3のメモリである。20

**【0110】**

さらに信号保持容量C\_N1、C\_N2は、それぞれスイッチ66、67を介してN信号線15に電気的に接続されている。また、信号保持容量C\_A、C\_ABのそれぞれは、スイッチ65、68のそれぞれを介して、S信号線16に電気的に接続されている。スイッチ65、66のゲートには、水平走査回路14から水平選択信号H1nが供給される。スイッチ67, 68のゲートには水平走査回路14から水平選択信号H2nが供給される。水平選択信号H1nがHレベルとなると、スイッチ65、66がオンとなり、信号保持容量C\_Aから信号VAがS信号線16に出力され、信号保持容量C\_N1から信号VNがN信号線15に出力される。水平選択信号H1nがオンとなることによって、スイッチ65、66が共にオンとなるため、信号VA、VNは同期してそれぞれS信号線16、N信号線15に出力される。同様に、水平選択信号H2nがHレベルとなると、スイッチ67、68がオンとなり、信号保持容量C\_N2から信号VNがN信号線15に出力され、信号保持容量C\_ABから信号VABがS信号線16に出力される。水平選択信号H2nがオンとなることによって、スイッチ67、68が共にオンとなるため、信号VN、VABは同期してそれぞれN信号線15、S信号線16に出力される。40

**【0111】**

N信号線15、S信号線16は差動アンプ71に電気的に接続されている。差動アンプ71はN信号線15とS信号線16とが伝送するそれぞれの信号の差分を出力する。つまり、水平選択信号H1nがHレベルとなり、S信号線16に信号VA、N信号線に信号VNが出力される場合では、差動アンプ71は信号VAから信号VNを差し引いた信号、すなわちVA - VNを出力する。同様に、水平選択信号H2nがHレベルとなり、S信50

号線 1 6 に信号 V A B 、 N 信号線 1 5 に信号 V N が出力される場合では、差動アンプ 7 1 は信号 V A B から信号 V N を差し引いた信号、すなわち V A B - V N を出力する。本実施例における焦点検出用信号は V A であり、画像取得用信号は V A B である。即ち、本実施例の撮像装置からは 1 フレーム期間内に焦点検出用信号、画像取得用信号の各々から信号 V N が差し引かれた信号がそれぞれ出力される。

#### 【 0 1 1 2 】

N 信号線 1 5 、 S 信号線 1 6 のそれぞれには、リセットスイッチ 6 9 、 7 0 が電気的に接続されている。リセットスイッチ 6 9 、 7 0 には T G 1 2 から水平リセットパルス H c が供給される。リセットスイッチ 6 9 、 7 0 のドレインにはドレン電圧 V d d が供給されている。N 信号線 1 5 、 S 信号線 1 6 のそれぞれが信号を差動アンプ 7 1 に出力した後、水平リセットパルス H c を H レベルとしてリセットスイッチ 6 9 、 7 0 をオンとし、N 信号線 1 5 、 S 信号線 1 6 の電位をリセットする。尚、図 1 3 では図示を省略しているが、N 信号線 1 5 、 S 信号線 1 6 にはそれぞれ容量が電気的に接続されている。N 信号線 1 5 に電気的に接続された容量の容量値を C H 1 とする。例えば信号保持容量 C \_ N 1 の保持した信号は、信号保持容量 C \_ N 1 の保持した信号値に、 C \_ N 1 / ( C \_ N 1 + C H 1 ) を乗算した信号が差動アンプ 7 1 に出力される。S 信号線 1 6 に電気的に接続された容量の容量値を C H 2 とする。例えば信号保持容量 C \_ A の保持した信号は、信号保持容量 C \_ A の保持した信号値に、 C \_ A / ( C \_ A + C H 1 ) を乗算した信号が差動アンプ 7 1 に出力される。水平リセットパルス H c を H レベルとしてリセットスイッチ 6 9 、 7 0 をオンとすると、容量 C H 1 、 C H 2 の電荷がリセットされる。

10

20

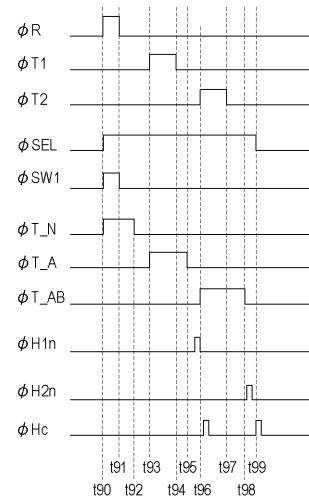

#### 【 0 1 1 3 】

次に、図 1 4 に、図 1 3 に例示した撮像装置において、A 信号を出力する画素を含む行の動作タイミングの一例を示す。本実施例における A 信号を出力する画素は図 1 ( a ) のように配置されている。

#### 【 0 1 1 4 】

時刻 t 9 0 において、リセットパルス R を H レベルとする。また、選択パルス S E L を H レベルとする。これにより、垂直信号線 7 には N 信号が出力される。また、スイッチパルス S W 1 を H レベルとする。これにより、N 信号はクランプ容量 C 0 に保持される。また、N 信号に基づく信号が増幅され、さらにオペアンプ 8 のオフセット信号 V o f f が重畠された信号 V N が出力される。信号書き込み信号 T \_ N もまた、H レベルとする。これにより、信号保持容量 C \_ N 1 、 C \_ N 2 に信号 V N の書き込みが行われる。時刻 t 9 1 にリセットパルス R 、スイッチパルス S W 1 を L レベルとする。

30

#### 【 0 1 1 5 】

時刻 t 9 2 に信号読み出しスイッチ T \_ N を L レベルとする。信号読み出しスイッチ T \_ N を L レベルにするのは、リセットパルス R を L レベルとした後とすることが好みしい。これは、リセットパルス R を L レベルとすることによってリセット M O S トランジスタで生じるチャージインジェクションにより、増幅 M O S トランジスタ 5 の入力ノードの電位が変化するためである。この変化後の増幅 M O S トランジスタ 5 の入力ノードの電位に基づく信号を信号保持容量 C \_ N 1 、 C \_ N 2 に保持させることが好みしい。信号保持容量 C \_ N 1 、 C \_ N 2 には、この時刻 t 9 2 においてオペアンプ 8 から出力された信号 V N が保持される。

40

#### 【 0 1 1 6 】

時刻 t 9 3 において、転送パルス T 1 を H レベルとする。これにより、フォトダイオード 1 に保持された信号電荷が増幅 M O S トランジスタ 5 の入力ノードに転送され、画素 1 0 0 から A 信号が出力される。また、信号書き込み信号 T \_ A を H レベルとする。これにより、信号保持容量 C \_ A にはクランプ容量 C 0 を介して出力された A 信号に基づいて、オペアンプ 8 が増幅して出力した信号 V A が書き込まれる。

#### 【 0 1 1 7 】

時刻 t 9 4 において、転送パルス T 1 を L レベルとする。

#### 【 0 1 1 8 】

50

時刻  $t_{95}$ において、信号書き込み信号  $T_A$ をLレベルとし、信号  $V_A$ が信号保持容量  $C_A$ に保持される。信号書き込み信号  $T_A$ をLレベルとした後、水平選択信号  $H_{1n}$ をHレベルとして、信号保持容量  $C_A$ 、  $C_{N1}$ からそれぞれ信号  $V_A$ 、  $V_N$ をS信号線16、 N信号線15に出力させる。信号保持容量  $C_A$ 、  $C_{N1}$ からのそれぞれの信号  $V_A$ 、  $V_N$ の出力を終えた後、水平選択信号  $H_{1n}$ をLレベルとする。また、水平選択信号  $H_{1n}$ をLレベルとした後、 N信号線15、 S信号線16の電位をリセットするため、水平リセットパルス  $H_c$ をHレベルとする。N信号線15、 S信号線16の電位をリセットした後、水平リセットパルス  $H_c$ をLレベルとする。尚、図14の動作タイミング図では示していないが、複数列の信号保持容量  $C_A$ 、  $C_{N1}$ から信号  $V_A$ 、  $V_N$ を出力させるため、水平リセットパルス  $H_c$ をLレベルとする。次に信号  $V_A$ 、  $V_N$ を出力させる列の水平選択信号  $H_{1n}$ をHレベルとして、順次信号をS信号線16、 N信号線15に出力させる。同様に、水平リセットパルス  $H_c$ についても、1列の信号  $V_N$ 、  $V_S$ のN信号、 S信号の出力が終わる都度、 N信号線15、 S信号線16の電位をリセットするためにHレベルとする。N信号線15、 S信号線16の電位がリセットされると水平リセットパルス  $H_c$ をLレベルとする。以降、焦点検出画素から信号が出力された信号保持容量  $C_A$ 、  $C_{N1}$ について、同様に水平選択信号  $H_{1n}$ 、 水平リセットパルス  $H_c$ の供給動作を順次繰り返して信号  $V_A$ 、  $V_N$ を出力させる。

10

## 【0119】

時刻  $t_{96}$ において、転送パルス  $T_2$ をHレベルとする。これにより、画素100からはA+B信号が出力される。また、信号書き込み信号  $T_{AB}$ をHレベルとする。これにより、クランプ容量  $C_0$ を介して出力されたA+B信号に基づいて、オペアンプ8が増幅して出力した信号  $V_{AB}$ が信号保持容量  $C_{AB}$ に書き込まれる。

20

## 【0120】

時刻  $t_{97}$ において、転送パルス  $T_2$ をLレベルとする。

## 【0121】

時刻  $t_{98}$ において、信号書き込み信号  $T_{AB}$ をLレベルとし、信号  $V_{AB}$ が信号保持容量  $C_{AB}$ に保持される。信号書き込み信号  $T_{AB}$ をLレベルとした後、水平選択信号  $H_{2n}$ をHレベルとして、信号保持容量  $C_{AB}$ 、  $C_{N2}$ からそれぞれ信号  $V_{AB}$ 、  $V_N$ をS信号線16、 N信号線15に出力させる。信号保持容量  $C_{AB}$ 、  $C_{N2}$ からのそれぞれの信号  $V_{AB}$ 、  $V_N$ の出力を終えた後、水平選択信号  $H_{2n}$ をLレベルとする。また、水平選択信号  $H_{2n}$ をLレベルとした後、 N信号線15、 S信号線16の電位をリセットするため、水平リセットパルス  $H_c$ をHレベルとする。N信号線15、 S信号線16の電位をリセットした後、水平リセットパルス  $H_c$ をLレベルとする。尚、図14の動作タイミング図では示していないが、複数列の信号保持容量  $C_{AB}$ 、  $C_{N2}$ から信号  $V_{AB}$ 、  $V_N$ を出力させるため、水平リセットパルス  $H_c$ をLレベルとする。次に信号  $V_{AB}$ 、  $V_N$ を出力させる列の水平選択信号  $H_{2n}$ をHレベルとして、順次信号をN信号線15、 S信号線16に出力させる。同様に、水平リセットパルス  $H_c$ についても、1列の信号  $V_N$ 、  $V_{AB}$ のN信号、 S信号の出力が終わる都度、 N信号線15、 S信号線16の電位をリセットするためにHレベルとする。N信号線15、 S信号線16の電位がリセットされると水平リセットパルス  $H_c$ をLレベルとする。以降、

30

画素の各列から信号が出力された信号保持容量  $C_{AB}$ 、  $C_{N2}$ について、同様に水平選択信号  $H_{2n}$ 、 水平リセットパルス  $H_c$ の供給動作を順次繰り返して信号  $V_{AB}$ 、  $V_N$ を出力させる。

40

## 【0122】

時刻  $t_{99}$ において、選択パルス  $S_{EL}$ をLレベルとする。

## 【0123】

以上、これまでA信号を出力する画素を含む行の動作タイミングについて説明した。次に、A信号を出力する画素を含まない行の動作タイミングについて説明する。

## 【0124】

図15は、A信号を出力する画素を含まない行の動作タイミングの一例を示したもので

50

ある。時刻  $t_{110}$ 、 $t_{111}$ 、 $t_{112}$  のそれぞれにおける動作については、A 信号を出力する画素を含む行の動作タイミングにおける時刻  $t_{90}$ 、 $t_{91}$ 、 $t_{92}$  と同様とすることができる。

#### 【0125】

時刻  $t_{113}$ において、転送パルス  $T_1$ 、 $T_2$ をHレベルとする。これにより、垂直信号線7には画素100からA+B信号が出力される。また、信号書き込み信号  $T_{AB}$ をHレベルとする。これにより、クランプ容量  $C_0$ を介して出力されたA+B信号に基づいて、オペアンプ8が増幅して出力した信号  $V_{AB}$ が信号保持容量  $C_{AB}$ に書き込まれる。

#### 【0126】

時刻  $t_{114}$ において、転送パルス  $T_1$ 、 $T_2$ をLレベルとする。

#### 【0127】

時刻  $t_{115}$ において、信号書き込み信号  $T_{AB}$ をLレベルとする。これにより、信号保持容量  $C_{AB}$ には信号  $V_{AB}$ が保持される。信号書き込み信号  $T_{AB}$ をLレベルとした後、水平選択信号  $H_{2n}$ をHレベルとする。信号保持容量  $C_{N2}$ には、時刻  $t_{112}$ において、図14で説明したA信号を出力する画素を含む行の動作タイミングでの時刻  $t_{92}$ と同様に、信号  $V_N$ が保持されている。従って、N信号線15には信号  $V_N$ 、S信号線16には信号  $V_{AB}$ がそれぞれ出力される。N信号線15、S信号線16に信号  $V_N$ 、 $V_{AB}$ のそれぞれの出力した後、水平選択信号  $H_{2n}$ をLレベルとし、その後、水平リセットパルス  $H_c$ をHレベルとしてN信号線15、S信号線16の電位をリセットする。尚、図15の動作タイミング図では示していないが、複数列の信号保持容量  $C_{AB}$ 、 $C_{N2}$ から信号  $V_{AB}$ 、 $V_N$ を出力させるため、水平リセットパルス  $H_c$ をLレベルとする。次に信号  $V_{AB}$ 、 $V_N$ を出力させる列の水平選択信号  $H_{2n}$ をHレベルとして、順次信号をN信号線15、S信号線16に出力させる。同様に、水平リセットパルス  $H_c$ についても、1列の信号  $V_N$ 、 $V_{AB}$ のN信号、S信号の出力が終わる都度、N信号線15、S信号線16の電位をリセットするためにHレベルとする。N信号線15、S信号線16の電位がリセットされると水平リセットパルス  $H_c$ をLレベルとする。以降、画素の各列から信号が出力された信号保持容量  $C_{AB}$ 、 $C_{N2}$ について、同様に水平選択信号  $H_{2n}$ 、水平リセットパルス  $H_c$ の供給動作を順次繰り返して信号  $V_{AB}$ 、 $V_N$ を出力させる。

#### 【0128】

以上、説明したように、A信号を出力する画素を含まない行の動作においては、A信号を出力する画素を含む行の動作での、画素100からA信号を出力させる動作、信号保持容量  $C_A$ に信号  $V_A$ を保持させる動作を省くことができる。即ち、A信号を出力する画素を含む行における動作の時刻  $t_{93} \sim t_{95}$ の期間を短縮することができる。撮像装置の全行の画素100においてA信号およびA+B信号を読み出す動作を行なう場合に比べて、A信号の出力を行わない画素100を有することにより、1フレーム期間内の撮像装置から信号を読み出す時間を短縮することができる。従って、A+B信号を得つつ、A信号を得る動作を高速に行なうことができる。

#### 【0129】

これまで、A信号を出力する画素が図1(a)のように配置された形態を基に説明した。本実施例では、図1(b)のようにA信号を出力する画素が配置された形態についても、水平走査回路14をデコーダとしていることで、実施例2と同様に、1フレーム期間内の撮像装置から信号を読み出す時間を短縮することができる。図1(b)のようにA信号を出力する画素が配された形態では、水平選択信号  $H_{1n}$ の動作を除いて、本実施例で図14を参照しながら説明した動作と同様とすることができる。水平選択信号  $H_{1n}$ は、A信号を出力する画素として動作させる画素を有する列のみHレベルとし、そのほかの列はLレベルとする。本実施例の固体撮像では、信号保持容量  $C_A$ 、 $C_{N1}$ から信号  $V_A$ 、 $V_N$ を出力しない列を有する。これにより、全列の信号保持容量  $C_A$ 、 $C_{N1}$ から信号  $V_A$ 、 $V_N$ を出力させる場合に比べて、1フレーム期間内のS信号線16、N信号

10

20

30

40

50

線 1 5 に信号を出力する時間を短縮することができる。従って、A + B 信号を得つつ、A 信号を得る動作を高速に行うことができる。

#### 【 0 1 3 0 】

また、図 1 ( c ) のように A 信号を出力する画素が配置された形態についても、実施例 2 で述べたのと同様に、水平走査回路 1 4 をデコーダとしてすることで、1 フレーム期間内の撮像装置から信号を読み出す時間を短縮することができる。A 信号を出力する画素を含む行については、水平選択信号 H 1 n の動作を除いて、本実施例で図 1 4 を参照しながら説明した動作と同様とすることができる。また、A 信号を出力する画素を含まない行については、本実施例で図 1 5 を参照しながら説明した動作と同様とすることができる。A 信号を出力する画素を含む行では、本実施例で先の図 1 ( b ) を参照しながら説明したのと同様に、水平選択信号 H 1 n は、A 信号を出力する画素として動作させる画素を有する列のみ H レベルとし、そのほかの列は L レベルとする。よって、信号保持容量 C\_A , C\_N 1 から信号 V\_A , V\_N を出力しない列が存在する。これにより、全列の信号保持容量 C\_A 、C\_N 1 から信号 V\_A 、V\_N を出力させる場合に比べて、画素 1 行当たりの S 信号線 1 6 、N 信号線 1 5 に信号を出力する時間を短縮することができる。また、図 1 ( c ) の撮像装置は、A 信号を出力する画素を含まない行を有する。よって、本実施例で先の図 1 ( a ) を参照しながら説明した通り、A 信号を出力する画素を含む行の動作での、画素 1 0 0 から A 信号を出力させる動作と、信号保持容量 C\_A に信号 V\_A を保持させる動作を省くことができる。従って、図 1 ( c ) のように A 信号を出力する画素を配置した形態であっても、実施例 2 と同様に、1 フレーム期間内の撮像装置から信号を読み出す時間を短縮することができる。従って、A + B 信号を得つつ、A 信号を得る動作を高速に行うことができる。

10

20

#### 【 0 1 3 1 】

本実施例では、画素 1 0 0 の一例としてフォトダイオード 1 とフォトダイオード 5 1 の面積が異なる形態を説明した。本実施例はこの形態に限定されるものではなく、フォトダイオード 1 、 5 1 の面積を同じとしても良い。

#### 【 0 1 3 2 】

##### [ 実施例 5 ]

これまで焦点検出用信号を出力する撮像装置について述べた。本実施例は別の形態の撮像装置である。

30

#### 【 0 1 3 3 】

画素 1 0 0 、垂直走査回路 2 、信号処理回路 1 0 1 の等価回路は実施例 1 で説明した図 4 と同様とすることができる。水平走査回路 1 4 については、A 信号を出力させる画素 1 0 0 が図 1 ( b ) , ( c ) のように配される場合には実施例 2 と同様にデコーダとすれば良い。A 信号を出力する画素 1 0 0 が図 1 ( a ) のように配される場合には水平走査回路 1 4 は実施例 1 と同様とすることができる。

#### 【 0 1 3 4 】

実施例 1 の撮像装置では、1 つのマイクロレンズ 2 3 が 1 つの画素 1 0 0 の受光部に光を集光するように配されていた。本実施例はマイクロレンズ 2 3 の配置には特に限定されない。例えば、1 つのマイクロレンズ 2 3 が複数の画素 1 0 0 の受光部に光を集めるように配されていても良い。また、マイクロレンズ 2 3 を有さない撮像装置の形態であっても良い。

40

#### 【 0 1 3 5 】

本実施例においても、1 フレーム期間内に複数の画素 1 0 0 から A + B 信号が出力され、さらに A + B 信号を出力した複数の画素 1 0 0 の一部の画素 1 0 0 の A 信号が使用される。A 信号を出力する画素 1 0 0 の配置は、これまでの実施例 1 ~ 4 で述べたのと同様に図 1 ( a ) ~ ( c ) で例示したようなレイアウトとすることができる。図 1 ( a ) のレイアウトで A 信号を使用する画素 1 0 0 を配した場合には、実施例 1 で図 6 、図 7 を参照しながら述べた動作タイミング図と同様の動作とすることができる。図 1 ( b ) 、( c ) のレイアウトで A 信号を使用する画素 1 0 0 を配した場合には、実施例 2 で図 6 、図 9 ( a )

50

)、(b)を参照しながら説明した動作タイミングと同様とすることができる。

#### 【0136】

実施例1、2で述べたのと同様に、本実施例の撮像装置からは複数の画素100からのA+B信号に基づくデジタルA+B信号と、A+B信号を出力した複数の画素100の一部の画素100のA信号に基づくデジタルA信号とが outputされる。撮像装置から出力されたデジタルA信号、デジタルA+B信号は、例えば図16に例示した撮像システムの出力信号処理部155の一例であるデジタル信号処理回路に出力される。デジタル信号処理回路は、デジタルA+B信号とデジタルA信号との差分を演算して、デジタルB信号を得る処理などを行う。

#### 【0137】

10

本実施例の撮像装置の1フレームの信号出力で得られる画像は、A信号を使用する画素100の配された領域が、他の領域に比して高解像度で表現できる。A信号を使用する画素100の領域については、撮像装置からデジタルA信号が出力され、デジタル信号処理回路でデジタルA+B信号とデジタルA信号との差分処理が行われてデジタルB信号が得られる。よって、A信号を使用する画素100が配された領域については、デジタルA信号と、デジタルB信号とを得る。従って、A信号を使用しない領域(デジタルA+B信号を使用する領域)よりも、A信号を使用する領域(デジタルA信号、デジタルB信号のそれぞれを使用する領域)では、デジタルA信号とデジタルB信号を得る分、高解像度となる。

#### 【0138】

20

1フレームの撮像動作によって得られる画像において高解像度で表現したい領域に配された画素100についてはA信号とA+B信号とを出力し、他の領域の画素100はA+B信号を出力する。撮像装置の信号出力に関わる動作は実施例1または実施例2と同様であるから、全画素のA信号、A+B信号を使用する形態に比して、本実施例の撮像装置は1フレーム期間内の撮像装置からの信号読み出しに要する時間を短縮することができる。

#### 【0139】

本実施例では、光電変換信号としてA信号とA+B信号とを出力する画素100を説明した。本実施例はこの形態に限定されず、さらに別のフォトダイオードを有し、このフォトダイオードで生成する信号電荷に基づいたC信号を出力する画素100を有していても良い。この形態では、得たい解像度によって画素100から出力させる信号を変えればよい。例えば、全画素からA+B信号を出力させ、高解像度で表示したい領域に含まれる一部の画素100からさらにC信号を出力させる形態がある。また、全画素からA+B+C信号を出力させて、高解像度で表示したい領域に含まれる一部の画素100からA信号、B信号、A+B信号、B+C信号、A+C信号のいずれかの信号を出力させる形態でもよい。このような形態であっても、全画素から2つの光電変換信号を出力させる形態に比べて、全画素から1つの光電変換信号を出力させ、一部の画素から別の光電変換信号を出力させる形態であれば、1フレーム期間内の撮像装置からの信号読み出しに要する時間を短縮することができる。

#### 【0140】

30

##### [実施例6]

40

これまでに述べた撮像装置を撮像システムに適用した場合の実施例について述べる。撮像システムとして、デジタルスチルカメラやデジタルカムコーダーや監視カメラなどがあげられる。図16に、撮像システムの例としてデジタルスチルカメラに撮像装置を適用した場合の模式図を示す。

#### 【0141】

図16において、151はレンズの保護のためのバリア、152は被写体の光学像を撮像装置154に結像させるレンズ、153はレンズ152を通った光量を可変にするための絞りである。レンズ152、絞り153は撮像装置154に光を導く光学系である。155は撮像装置154より出力される出力信号の処理を行う出力信号処理部である。

#### 【0142】

50

撮像装置 154 からの出力信号が実施例 4 のようにアナログ信号である場合には、出力信号処理部 155 は、アナログ信号処理部、アナログデジタル変換部とデジタル信号処理部とを有する形態とする。撮像装置 154 からの出力信号をアナログ信号処理部が各種の補正を行って、アナログデジタル変換部に信号を出力する。アナログ信号処理部から出力された信号をアナログデジタル変換部がデジタル信号に変換し、デジタル信号処理部に出力する。デジタル信号処理部は必要に応じて各種の補正、圧縮を行ったうえで信号を出力する。尚、実施例 4 における撮像装置 154 では、一部の画素が A + B 信号の出力を行うものの、A 信号を出力しない場合を例示した。従って、1 フレーム期間内に撮像装置 154 から出力される焦点検出用信号のデータ量は、全画素が A 信号を出力する場合に比べて少なくなる。従って、出力信号処理部 155 についてもアナログデジタル変換の処理時間が短くなるため、信号処理を高速化することができる効果を有している。10

#### 【 0143 】

一方、撮像装置 154 が先に示した実施例 1 ~ 3 のように、デジタル信号を出力する場合には、出力信号処理部 155 はデジタル信号処理部を有する。デジタル信号処理部は、撮像装置 154 から出力されるデジタル A 信号、デジタル A + B 信号のそれぞれからデジタル N 信号を差し引く差分処理やデジタル A + B 信号からデジタル A 信号を差し引いてデジタル B 信号を得る差分処理を行う。また、出力信号処理部 155 はその他、必要に応じて各種の補正、圧縮を行って信号を出力する動作を行う。尚、実施例 1 ~ 3 の撮像装置 154 では、A + B 信号の出力を行うものの、A 信号を出力しない画素を有していた。従って、1 フレーム期間内に撮像装置 154 から出力される焦点検出用信号のデータ量は、全画素が A 信号を出力する場合に比べて少なくなる。よって、撮像装置 154 がデジタル信号を出力する場合においても、信号処理を行うデータ量が少なくなるため、信号処理を高速化することができる効果を有している。20

#### 【 0144 】

そして、図 16 において、156 は画像データを一時的に記憶する為のバッファメモリ部、158 は記録媒体に記録または読み出しを行うためのインターフェース部、159 は撮像データの記録または読み出しを行う為の半導体メモリ等の着脱可能な記録媒体である。157 は外部コンピュータ等と通信する為のインターフェース部である。1510 は各種演算とデジタルスチルカメラ全体を制御する全体制御・演算部、1511 は撮像装置 154、出力信号処理部 155 に、各種タイミング信号を出力するタイミング発生部である。ここで、タイミング信号などは外部から入力されてもよく、撮像システムは少なくとも撮像装置 154 と、撮像装置 154 から出力された出力信号を処理する出力信号処理部 155 とを有すればよい。30

#### 【 0145 】

出力信号処理部 155 が行う、デジタル信号 A + B 信号からデジタル A 信号を差し引く処理、あるいは、信号 VAB - VN から信号 VA - VN を差し引く処理は、共に同じ画素から出力された信号同士で行われる。すなわち、画素が出力した A 信号に基づく焦点検出用信号と、A 信号を出力した画素と同じ画素が出力した A + B 信号に基づく画像取得用信号とで差分処理が行われる。これにより、画素の B 信号に基づく信号が得られ、この信号と A 信号に基づく信号との信号値を比較することにより、位相差検出方式の焦点検出が行われる。40

#### 【 0146 】

以上のように、本実施例の撮像システムは、撮像装置 154 を適用して撮像動作を行うことが可能である。本実施例の撮像システムに、実施例 1 ~ 4 に例示した撮像装置を適用することにより、撮像装置 154 から出力される焦点検出用信号に基づいた位相差検出式の焦点検出動作と、画像取得用信号に基づいた画像の形成とを行うことができる。

#### 【 0147 】

##### [ 実施例 7 ]

本実施例の撮像システムについて、図 17 を参照しながら説明する。実施例 6 で説明した撮像システムとは異なる点を中心に説明する。図 17 に例示した撮像システムは、実施50

例 6 で説明した撮像システムに対し、撮像装置 154 から出力される焦点検出用信号を処理する焦点検出用信号処理部 1512 が設けられている。そして、焦点検出用信号処理部 1512 から信号が出力信号処理部 155 に出力される形態である。

#### 【0148】

本実施例の撮像装置 154 は全画素が A 信号を出力する画素として動作する。すなわち、撮像装置 154 の全画素から A 信号と A + B 信号とがそれぞれ出力される。従って、全画素からの画素信号に基づく、焦点検出用信号と画像取得用信号とが撮像装置 154 から出力される。撮像装置 154 がアナログデジタル変換回路を有し、デジタル信号を出力する場合には、焦点検出用信号はデジタル A 信号であり、画像取得用信号はデジタル A + B 信号である。撮像装置 154 からデジタル信号の焦点検出用信号、画像取得用信号が出力される場合の回路構成は、実施例 1 で例示した図 4 のような構成でも良いが、この構成には限定されない。つまり、画素 100 が A 信号と A + B 信号とを時分割で出力し、メモリ 13 にはこれらの信号に基づくデジタル A 信号、デジタル A + B 信号が保持されると共に水平走査回路 14 によって各メモリ 13 から順次デジタル信号が出力される形態であれば良い。撮像装置 154 からアナログ信号が出力される場合には、焦点検出用信号は信号 V A であり、画像取得用信号は V A B である。撮像装置 154 からアナログ信号の焦点検出用信号、画像取得用信号が出力される場合の回路構成について、実施例 6 で例示した図 13 のような回路構成でも良いが、この構成に限定されない。つまり、画素 100 が A 信号と A + B 信号とを時分割で出力し、信号保持容量にこれらの信号に基づく信号 V A , V A B が保持され、水平走査回路 14 によって各信号保持容量から信号 V A , V A B が出力される形態であれば良い。撮像装置 154 からアナログ信号が出力される形態では、出力信号処理部 155 は、アナログ信号処理部、アナログデジタル変換部とデジタル信号処理部とを有する形態とする。撮像装置 154 からの出力信号をアナログ信号処理部が各種の補正を行って、アナログデジタル変換部に信号を出力する。アナログ信号処理部から出力された信号をアナログデジタル変換部がデジタル信号に変換し、デジタル信号処理部に出力する。デジタル信号処理部は必要に応じて各種の補正、圧縮を行ったうえで信号を出力する。

#### 【0149】

焦点検出用信号処理部 1512 は、撮像装置 154 から出力される全画素の A 信号に基づく焦点検出用信号のうち、一部の画素からの A 信号に基づく焦点検出用信号を出力信号処理部 155 に出力する。また、他の一部の画素からの A 信号に基づく焦点検出用信号は破棄する処理を行う。

#### 【0150】

一方、撮像装置 154 から出力された画像取得用信号については、焦点検出用信号処理部 1512 は処理を行わず、そのまま出力信号処理部 155 に出力される。

#### 【0151】

出力信号処理部 155 には、撮像装置 154 の一部の画素からの A 信号に基づく焦点検出用信号と、全画素からの A + B 信号に基づく画像取得用信号が入力される。出力信号処理部 155 は全画素からの A 信号に基づく焦点検出用信号が入力される場合に比べて、焦点検出用信号処理部 1512 が一部の画素のみからの A 信号に基づく焦点検出用信号を出力信号処理部 155 に出力するため、出力信号処理部 155 に入力される焦点検出用信号のデータ量が少なくなる。従って、出力信号処理部 155 は全画素の A 信号に基づく焦点検出用信号が入力される場合に比べて高速に信号処理を行うことができる。

#### 【0152】

よって、本実施例の撮像システムは、撮像装置 154 から出力される焦点検出用信号のうち、一部の画素からの A 信号に基づく焦点検出用信号を出力信号処理部 155 に出力する焦点検出用信号処理部を有することにより、高速に信号処理を行うことができる。

#### 【0153】

##### [実施例 8]

図面を参照しながら、本実施例の撮像装置について説明する。

10

20

30

40

50

**【0154】**

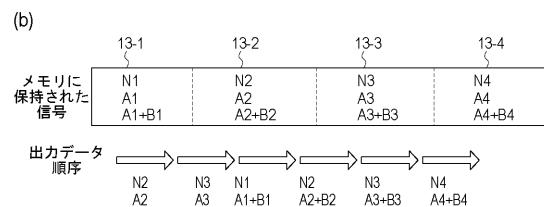

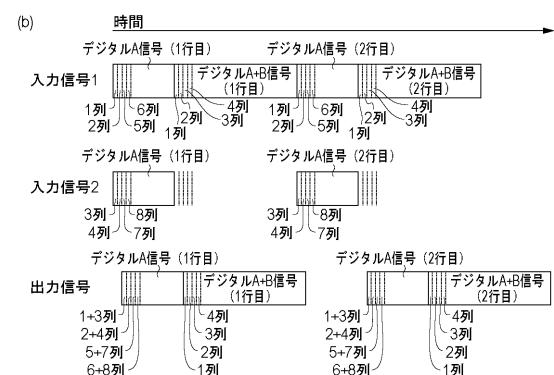

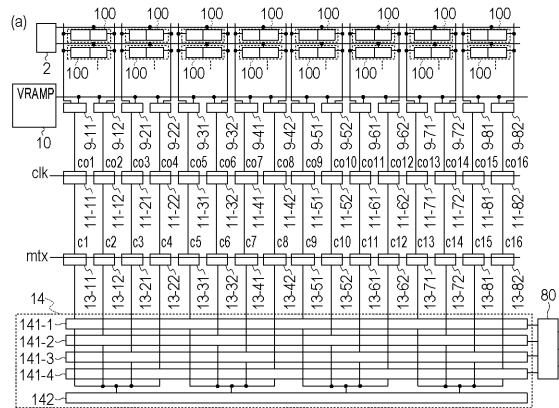

図18(a)は本実施例の撮像装置の構成の一例を示した模式図である。

**【0155】**

図18(a)では、画素100が持つ2つのフォトダイオード1、51を、2つの長方形を用いて模式的に表している。また、図18(a)では、図4と同じ機能を有する部材については、図4で付した符号と同じ符号を図18(a)でも付している。また、図18では、垂直信号線7、比較回路9、カウンタ回路11、メモリ13については、図の左から数えて何列目に位置しているかを表す枝番を付している。水平走査回路14は、水平転送部141と水平走査部142を有している。また、図18(a)に記載の撮像装置は、カウンタ制御部30を有している。メモリ13には、TGから信号m<sub>t</sub>xが与えられる。10

**【0156】**

図18(b)は、本実施例の1列のカウンタ回路11、メモリ13の構成を示した図である。カウンタ回路11はビット信号c[0]～c[11]の12ビットのデジタル信号を出力する形態として示している。カウンタ制御部30が outputする信号d<sub>e</sub>がHレベルであって、信号s<sub>e</sub>がLレベルの期間では、ビット信号c[1]～c[11]の信号値がクロック信号c<sub>lk</sub>に応じて変化する。一方、信号d<sub>e</sub>がLレベルであって、信号s<sub>e</sub>がHレベルの期間では、ビット信号c[0]～c[11]の信号値がクロック信号c<sub>lk</sub>に応じて変化する。ビット信号c[1]はビット信号c[0]の信号値が変化する場合は、ビット信号c[0]を2分周した信号となる。よって、信号d<sub>e</sub>がHレベルであって、信号s<sub>e</sub>がLレベルの場合のカウンタ回路11の単位時間当たりのカウント数は、信号d<sub>e</sub>がLレベルであって、信号s<sub>e</sub>がHレベルの場合の2倍となる。以下、信号d<sub>e</sub>がHレベルであって、信号s<sub>e</sub>がLレベルの場合のカウンタ回路11のカウント動作をダブルカウント動作、信号d<sub>e</sub>がLレベルであって、信号s<sub>e</sub>がHレベルの場合のカウンタ回路11のカウント動作をシングルカウント動作と表記する。20

**【0157】**

次に図19を参照しながら、図18(a)に示した撮像装置の動作について説明する。本実施例の比較回路9は、比較結果信号として、信号c<sub>o</sub>をカウンタ制御部30に出力する。本実施例の比較回路9は、ランプ信号VRAMPの電位よりも垂直信号線7の電位の方が大きい場合には、Hレベルの信号を出力する。ランプ信号VRAMPの電位よりも垂直信号線7の電位の方が小さい場合には、Lレベルの信号を出力する。30

**【0158】**

図19に示した符号は、それぞれ図18(a)に示した符号と対応している。本実施例では、信号d<sub>e</sub>3、d<sub>e</sub>4は共に全期間Lレベルとしている。

**【0159】**

A変換期間について説明する。A変換期間に先立って、1行目の画素100からはA信号が比較回路9に出力されている。

**【0160】**

まず、カウンタ制御部は信号a<sub>e</sub>をHレベルとする。その後、比較回路9-1、9-2、9-3、9-4はランプ信号VRAMPと垂直信号線7-1、7-2、7-3、7-4の電位との比較動作をそれぞれ開始する。比較回路9-1、9-3の比較結果信号c<sub>o</sub>1、c<sub>o</sub>3が共にHレベルの時には、カウンタ制御部30が outputする信号s<sub>e</sub>1はLレベル、信号d<sub>e</sub>1はHレベルである。この時、カウンタ回路11-1はダブルカウント動作にてクロック信号c<sub>lk</sub>をカウントする。また、比較回路9-2、9-4の比較結果信号c<sub>o</sub>2、c<sub>o</sub>4が共にHレベルの時には、カウンタ制御部30が outputする信号s<sub>e</sub>2はLレベル、信号d<sub>e</sub>2はHレベルである。この時、カウンタ回路11-2はダブルカウント動作にてクロック信号c<sub>lk</sub>をカウントする。また、比較回路9-3、9-4の比較結果信号c<sub>o</sub>3、c<sub>o</sub>4の信号レベルに関わらず、信号a<sub>e</sub>がHレベルの期間は、信号s<sub>e</sub>3はLレベルである。信号d<sub>e</sub>3もLレベルであるため、カウンタ回路11-3はクロック信号c<sub>lk</sub>のカウント動作を行わない。また、比較回路9-4の比較結果信号c<sub>o</sub>4の信号レベルに関わらず、信号a<sub>e</sub>がHレベルの期間は、信号s<sub>e</sub>4はLレベルである。信号d40

50

e 4 も L レベルであるため、カウンタ回路 11 - 4 はクロック信号 c 1 k のカウント動作を行わない。

#### 【 0 1 6 1 】

次に、比較回路 9 - 2 の比較結果信号 c o 2 が H レベルから L レベルに変化したとする。これにより、信号 s e 2 は L レベルから H レベルに変化し、信号 d e 2 は H レベルから L レベルに変化する。よって、カウンタ回路 11 - 2 はダブルカウント動作からシングルカウント動作に移行して、クロック信号 c 1 k をカウントする。

#### 【 0 1 6 2 】

続いて、比較回路 9 - 3 の比較結果信号 c o 3 が H レベルから L レベルに変化したとする。これにより、信号 d e 1 は H レベルから L レベルに変化し、信号 s e 1 は L レベルから H レベルに変化する。よって、カウンタ回路 11 - 1 はダブルカウント動作からシングルカウント動作に移行して、クロック信号 c 1 k をカウントする。10

#### 【 0 1 6 3 】

続いて、比較回路 9 - 4 の比較結果信号 c o 4 が H レベルから L レベルに変化したとする。これにより、信号 s e 2 が H レベルから L レベルに変化するため、カウンタ回路 11 - 2 はクロック信号 c 1 k のカウント動作を停止し、この時点でのカウント信号値を保持する。

#### 【 0 1 6 4 】

続いて、比較回路 9 - 1 の比較結果信号 c o 1 が H レベルから L レベルに変化する。これにより、信号 s e 1 が H レベルから L レベルに変化する。よって、カウンタ回路 11 - 1 はクロック信号 c 1 k のカウントを停止し、この時点でのカウント信号値を保持する。20

#### 【 0 1 6 5 】

カウンタ回路 11 - 1 が保持したカウント信号値は、1 列目の画素 1 0 0 の A 信号と 3 列目の画素 1 0 0 の A 信号とを加算した信号に基づくデジタル信号である。このデジタル信号を、デジタル A 1 + A 3 信号と表記する。カウンタ回路 11 - 2 が保持したカウント信号は、2 列目の画素 1 0 0 の A 信号と、4 列目の画素 1 0 0 の A 信号とを加算した信号に基づくデジタル信号である。このデジタル信号をデジタル A 2 + A 4 信号と表記する。

#### 【 0 1 6 6 】

次に、T G は信号 m t x を H レベルとする。これにより、カウンタ回路 11 が保持したカウント信号をメモリ 13 が保持する。メモリ 13 - 1 はデジタル A 1 + A 3 信号を保持する。メモリ 13 - 2 はデジタル A 2 + A 4 信号を保持する。メモリ 13 - 3 、 13 - 4 は、0 の信号値を保持する。水平転送部 14 1 は水平走査部 14 2 からの信号に基づいて、順次、各列のメモリ 13 が保持したデジタル信号を D S P 8 0 に出力させる。他の形態として、このメモリ 13 から D S P 8 0 へのデジタル信号の出力動作は、水平転送部 14 1 が、0 の信号値を保持したメモリ 13 をスキップする。そして、複数の A 信号を加算した信号に基づくデジタル信号を保持したメモリ 13 のみからデジタル信号を出力させるようにも良い。30

#### 【 0 1 6 7 】

続いて、A + B 変換期間について説明する。A + B 変換期間に先立って、1 行目の画素 1 0 0 からは A + B 信号が比較回路 9 に出力されている。40

#### 【 0 1 6 8 】

まず、信号 a e は L レベルのまます。また、カウンタ回路 11 - 1 、 11 - 2 、 11 - 3 、 11 - 4 のカウント信号を初期値にリセットする。

#### 【 0 1 6 9 】

その後、比較回路 9 - 1 、 9 - 2 、 9 - 3 、 9 - 4 はランプ信号 V R A M P と垂直信号線 7 - 1 、 7 - 2 、 7 - 3 、 7 - 4 の電位との比較動作をそれぞれ開始する。A + B 変換期間では、信号 a e が L レベルのため、信号 d e 1 、 d e 2 は A + B 変換期間の間、L レベルである。これにより、カウンタ回路 11 - 1 は、比較結果信号 c o 1 が H レベルから L レベルになるまでの期間、クロック信号 c 1 k をシングルカウント動作でカウントする。カウンタ回路 11 - 2 、 11 - 3 、 11 - 4 についても同様に、それぞれ、比較結果信50

号 c o 2、c o 3、c o 4 が H レベルから L レベルになるまでの期間、クロック信号 c l k をシングルカウント動作でカウントする。これにより、カウンタ回路 1 1 - 1 は、1 列目の画素 1 0 0 が出力した A + B 信号に基づくデジタル (A + B) 1 信号を保持する。同様に、カウンタ回路 1 1 - 2、1 1 - 3、1 1 - 4 は、デジタル (A + B) 2 信号、デジタル (A + B) 3 信号、デジタル (A + B) 4 信号を保持する。その後、T G は信号 m t x を H レベルとして、メモリ 1 3 - 1、1 3 - 2、1 3 - 3 - 、1 3 - 4 がそれぞれデジタル (A + B) 1 信号、デジタル (A + B) 2 信号、デジタル (A + B) 3 信号、デジタル (A + B) 4 信号を保持する。水平転送部 1 4 1 は水平走査部 1 4 2 からの信号に基づいて、順次、各列のメモリ 1 3 が保持したデジタル信号を D S P 8 0 に出力させる。

## 【0170】

10

本実施例のメモリ 1 3 が保持するデジタル A 信号は、複数列の A 信号を加算した信号に基づくデジタル信号である。よって、デジタル A + B 信号に比して、デジタル A 信号を保持するメモリ 1 3 の数が少なくなるため、D S P 8 0 に出力されるデジタル A 信号の信号量はデジタル A + B 信号の比して少なくなる。よって、本実施例の撮像装置においても、1 フレーム期間に出力されるデジタル A 信号の信号量は、デジタル A + B 信号の信号量よりも少ない。これにより、全列のメモリ 1 3 がデジタル A 信号を保持する形態に比して、デジタル A 信号を保持した全メモリ 1 3 からデジタル A 信号を D S P 8 0 に出力させる時間を短縮することができる。また、デジタル A 信号の信号量が減ることにより、D S P 8 0 の信号処理の負荷を減らすことができる。

## 【0171】

20

本実施例の形態を、図 3 (a)、図 3 (b) に示したように、A 信号を焦点検出用信号として用いる場合について説明する。焦点検出用信号である A 信号は画像取得用信号である A + B 信号に比して、求められる信号の精度が低い場合がある。このような場合に、本実施例のように、複数列の A 信号をした信号に基づくデジタル A 信号を得る形態を好適に実施することができる。

## 【0172】

## [実施例 9]

本実施例の撮像装置について、図面を参照しながら実施例 8 と異なる点を中心に説明する。本実施例では、画素 1 0 0 から A 信号と B 信号が異なる垂直信号線 7 に出力される形態である。

30

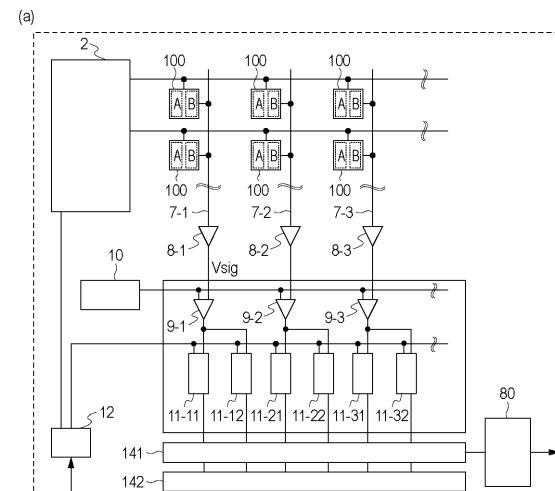

## 【0173】

図 2 0 (a) は本実施例の画素の構成の一例である。図 2 0 (a) では、図 4 に示した部材と同じ機能を有する部材については、図 4 で付した符号と同じ符号を付して表している。図 4 に示した画素では、転送 M O S トランジスタ 2 0 が転送パルス T 1、転送 M O S トランジスタ 5 0 が転送パルス T 2 によって制御される形態として示した。図 2 0 (a) では、転送 M O S トランジスタ 2 0、5 0 が共に同じ転送パルス T によって制御される形態としている。また、図 4 では、フォトダイオード 1、5 1 のそれぞれが生成した信号電荷が増幅 M O S トランジスタ 5 に転送される形態として示した。図 2 0 (a) では、フォトダイオード 1 で生成した信号電荷が転送 M O S トランジスタ 2 0 を介して増幅 M O S トランジスタ 5 - 1 に転送される。また、フォトダイオード 5 1 で生成した信号電荷が転送 M O S トランジスタ 5 0 を介して増幅 M O S トランジスタ 5 - 2 に転送される。増幅 M O S トランジスタ 5 - 1、5 - 2 はそれぞれの入力ノードに転送された信号電荷に基づく信号を、選択 M O S トランジスタ 6 - 1、6 - 2 を介して垂直信号線 7 - 1 1、7 - 1 2 に出力する。フォトダイオード 1 が生成した信号電荷に基づいて垂直信号線 7 - 1 1 に出力される信号が A 信号である。また、フォトダイオード 5 1 が生成した信号電荷に基づいて垂直信号線 7 - 1 2 に出力される信号が B 信号である。

40

## 【0174】

図 2 0 (b) は、本実施例の撮像装置の構成の一例を示した図である。図 2 0 (b) では、図 1 8 (a) に示した部材と同じ機能を有する部材については、図 1 8 (a) で付した符号と同じ符号を付して表している。1 列目の画素 1 0 0 から垂直信号線 7 - 1 1 に出

50

力されたA信号（以下、A1信号）は比較回路9-11に出力される。同様に、垂直信号線7-12に出力されたB信号（以下、B1信号）は、比較回路9-12に出力される。2列目の画素100から垂直信号線7-21に出力されたA信号（以下、A2信号）は、比較回路9-21に出力される。また、2列目の画素100から垂直信号線7-22に出力されたB信号（以下、B2信号）は、比較回路9-22に出力される。3列目の画素100から垂直信号線7-31に出力されたA信号（以下、A3信号）は、比較回路9-31に出力される。また、3列目の画素100から垂直信号線7-32に出力されたB信号（以下、B3信号）は、比較回路9-32に出力される。比較回路9のそれぞれは、垂直信号線7に出力された信号とランプ信号VRAMPとを比較した比較結果信号COをそれぞれカウンタ制御部30に出力する。

10

#### 【0175】

次に、図21を参照しながら、図20(b)に示した撮像装置のカウンタ回路11-1～11-3の動作について説明する。図21に示した動作は、カウンタ回路11-1がA1+B1信号、カウンタ回路11-2がA1+A3信号、カウンタ回路11-3がA2+B2信号、カウンタ回路11-5がA3+B3信号を生成する形態である。

#### 【0176】

まず、比較結果信号CO1～CO5は全てHレベルとなっている。この時、信号se1、se2、se3はLレベルであり、信号de1、de2、de3はHレベルである。カウンタ回路11-1、11-2、11-3はそれぞれ、ダブルカウント動作でクロック信号clkを計数する。

20

#### 【0177】

次に、比較結果信号CO3がHレベルからLレベルに変化する。これにより、信号se3がLレベルからHレベルに変化する。また、信号de3がHレベルからLレベルに変化する。これにより、カウンタ回路11-3は、シングルカウント動作でクロック信号clkを計数する。

#### 【0178】

次に、比較結果信号CO2がHレベルからLレベルに変化する。これにより、信号se1がLレベルからHレベルに変化する。また、信号de1がHレベルからLレベルに変化する。これにより、カウンタ回路11-1はシングルカウント動作でクロック信号clkを計数する。

30

#### 【0179】

次に、比較結果信号CO4がHレベルからLレベルに変化する。これにより、信号se3がHレベルからLレベルに変化する。よって、カウンタ回路11-3はこの時点でのカウント信号を保持する。この保持したカウント信号が、A2+B2信号に基づくデジタルA2+B2信号である。

#### 【0180】

次に、比較結果信号CO1がHレベルからLレベルに変化する。これにより、信号se1がHレベルからLレベルに変化する。よって、カウンタ回路11-1はこの時点でのカウント信号を保持する。この保持したカウント信号が、A1+B1信号に基づくデジタルA1+B1信号である。

40

#### 【0181】

次に、比較結果信号CO5がHレベルからLレベルに変化する。これにより、信号se2がHレベルからLレベルに変化する。

#### 【0182】

次に、TGは信号mtxをHレベルとする。これにより、カウンタ回路11-1、11-2、11-3が保持したデジタル信号がそれぞれメモリ13-1、13-2、13-3に出力される。

#### 【0183】

本実施例のメモリ13が保持するデジタルA信号は、複数列のA信号を加算した信号に基づくデジタル信号である。よって、デジタルA+B信号に比して、デジタルA信号を保

50

持するメモリ 13 の数が少なくなるため、DSP80 に出力されるデジタル A 信号の信号量はデジタル A + B 信号の信号量に比して少なくなる。よって、本実施例の撮像装置においても、実施例 8 で述べた効果と同様の効果を得ることができる。

#### 【0184】

##### [実施例 10]

本実施例の撮像装置について、図面を参照しながら説明する。本実施例の撮像装置は DSP80 が複数列のデジタル A 信号を加算して出力する形態である。

#### 【0185】

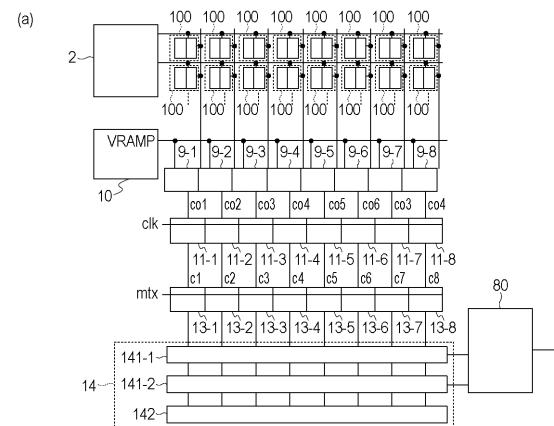

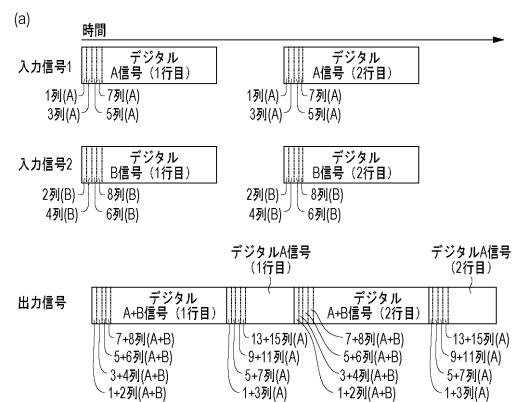

図 22 (a) は本実施例の撮像装置の構成の一例を示した図である。1列目の画素 100 の出力した A 信号、A + B 信号は、それぞれ比較回路 9 - 1 に出力される。比較回路 9 - 1、カウンタ回路 11 - 1、メモリ 13 - 1 は A 変換期間、A + B 変換期間でデジタル A 信号、デジタル A + B 信号をそれぞれ生成する。他の列の信号処理回路も同様に、デジタル A 信号、デジタル A + B 信号をそれぞれ生成する。水平転送部 141 は、水平走査部 142 の信号に基づいて、各列のメモリ 13 からデジタル A 信号、デジタル A + B 信号をそれぞれ DSP80 に出力させる。10

#### 【0186】

図 22 (b) は、本実施例の DSP80 が出力する信号を表した図である。入力信号とは、水平転送部 141 によって各列のメモリ 13 から DSP80 に出力される信号を表している。出力信号は、DSP80 が出力する信号である。まず、1列目から順に各メモリ 13 からデジタル A 信号が DSP80 に出力される。DSP80 は、複数列のデジタル A 信号を加算した信号を出力する。図 22 (b) では、1列目と 3列目のメモリ 13 が保持したデジタル A 信号を加算したデジタル信号を出力する。以降、同様に、2列目と 4列目、5列目と 7列目、のデジタル A 信号を加算したデジタル信号を出力する。20

#### 【0187】

水平転送部 141 が各メモリ 13 から DSP80 にデジタル A 信号を出力させた後、水平転送部 141 は各メモリ 13 から DSP80 にデジタル A + B 信号を出力させる。

#### 【0188】

DSP80 は、各列から出力されたデジタル A + B 信号を順次出力する。

#### 【0189】

2行目の画素 100 の A 信号、A + B 信号に基づくデジタル A 信号、デジタル A + B 信号についても、DSP80 は 1行目の画素の A 信号、A + B 信号に基づくデジタル A 信号、デジタル A + B 信号と同様の処理とすることができます。30

#### 【0190】

これにより、撮像装置から出力されるデジタル A 信号の信号量を、デジタル A + B 信号の信号量よりも少なくすることができます。これにより、実施例 2 の撮像装置と同様の効果を得ることができます。

#### 【0191】

また、本実施例では、複数列のデジタル A 信号を DSP80 が加算する形態を示した。他の形態として、図 23 (a) に示すように、複数行の A 信号に基づくデジタル A 信号を加算する形態としても良い。図 23 (a) では、水平転送部 141 が各列のメモリ 13 から 1行目の画素 100 の A 信号に基づくデジタル A 信号を DSP80 に出力させる。DSP80 は、各デジタル A 信号を保持する。そして、水平転送部 141 が各列のメモリ 13 から 1行目の画素 100 の A + B 信号に基づくデジタル A + B 信号を DSP80 に出力させる。DSP80 は、各列のデジタル A + B 信号を出力する。次に、水平転送部 141 が各列のメモリ 13 から 2行目の画素 100 の A 信号に基づくデジタル A 信号を DSP80 に出力させる。DSP80 は、2行目の画素 100 の A 信号に基づくデジタル A 信号と、保持していた1行目の画素 100 の A 信号に基づくデジタル A 信号と、を加算した信号を出力する。次に、水平転送部 141 が各列のメモリ 13 から 2行目の画素 100 の A + B 信号に基づくデジタル A + B 信号を DSP80 に出力させる。DSP80 は、各列のデジタル A + B 信号を出力する。4050

**【0192】**

よって、図23(a)の形態においても、図22(b)に述べた形態と同様の効果を得ることができる。

**【0193】**

また、他の形態として、図23(b)のように、1行目の画素100のA+B信号に基づくデジタルA+B信号がDSP80に出力されてから、DSP80が複数のデジタルA信号を加算した信号を出力する形態であっても良い。

**【0194】**

本実施例では撮像装置がDSP80を有する形態としたが、DSP80は、撮像装置の外部に設けられた出力信号処理部の形態であっても良い。

10

**【0195】****[実施例11]**

本実施例の撮像装置について、実施例10と異なる点を中心に説明する。

**【0196】**

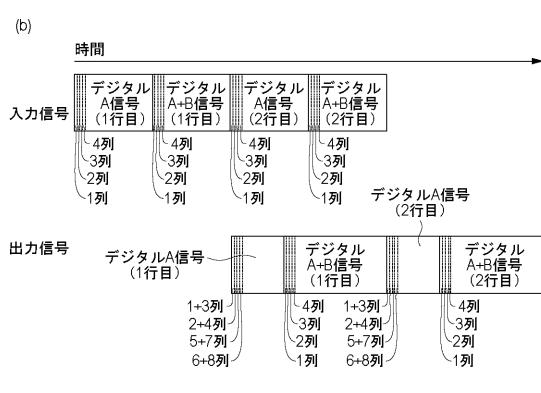

図24(a)は本実施例の撮像装置の構成の一例を示した図である。本実施例では、水平転送部141を水平転送部141-1、141-2の複数とし、複数チャンネルで各列のメモリ13からデジタル信号をDSP80に出力させる形態である。

**【0197】**

図24(b)は、図24(a)に示した撮像装置において、DSP80に出力されるデジタル信号と、DSP80が出力するデジタル信号と、を表した図である。

20

**【0198】**

図24(b)に示した入力信号1は、水平転送部141-1によって各列のメモリ13からDSP80に出力されるデジタル信号を表している。また、入力信号2は、水平転送部141-2によって各列のメモリ13からDSP80に出力されるデジタル信号を表している。出力信号は、DSP80が出力するデジタル信号を表している。

**【0199】**

入力信号1と入力信号2として、まず各列のメモリ13から1行目の画素100のA信号に基づくデジタルA信号がDSP80に出力される。DSP80は、入力信号1と入力信号2のデジタルA信号を加算した信号を出力する。次に、入力信号1として、各列のメモリ13から1行目の画素100のA+B信号に基づくデジタルA+B信号がDSP80に出力される。DSP80はデジタルA+B信号を出力する。2行目の画素100のA信号に基づくデジタルA信号についても、DSP80は入力信号1と入力信号2のデジタルA信号を加算した信号を出力する。図24(b)では、2行目の画素100のA信号に基づくデジタルA信号については、各列のメモリ13からデジタルA信号がDSP80に出力された後に、DSP80が複数のデジタルA信号を加算した信号を出力する形態を示した。他の形態として、1行目の画素100のA信号に基づくデジタルA信号と同様に、各列のメモリ13からDSP80にデジタルA信号が出力されるのと並行して、DSP80が複数のデジタルA信号を加算した信号を出力する形態であっても良い。

30

**【0200】**

本実施例の撮像装置においても、実施例10と同様の効果を得ることができる。また、本実施例によれば、DSP80にデジタルA信号が出力されるのとほぼ同時に、DSP80が複数のデジタルA信号を加算した信号を出力できる。よって、メモリ13からデジタル信号がDSP80に出力されてから、DSP80がデジタル信号の出力を終えるまでの期間を実施例10の図23(a)、図23(b)のいずれの形態に比しても短縮することができる。

40

**【0201】**

本実施例では撮像装置がDSP80を有する形態としたが、DSP80は、撮像装置の外部に出力信号処理部が設けられた形態であっても良い。

**【0202】****[実施例12]**

50

本実施例の撮像装置を図 25 (a) に示す。本実施例の撮像装置は、図 20 (b) に示したように、A 信号と B 信号とが異なる垂直信号線 7 に出力される形態である。図 25 (a) に示した撮像装置では、1 列目の画素 100 から A 信号が比較回路 9 - 11 に出力され、B 信号が比較回路 9 - 12 に出力される。比較回路 9 - 11 は A 信号とランプ信号 V RAM P とを比較し、比較結果信号に基づいてカウンタ回路 11 - 11 がカウント信号を保持する。このカウント信号がデジタル A 信号である。同様に、比較回路 9 - 12 は A + B 信号とランプ信号 V RAM P とを比較し、比較結果信号に基づいてカウンタ回路 11 - 12 がカウント信号を保持する。このカウント信号がデジタル B 信号である。メモリ 13 - 11、13 - 12 はそれぞれカウンタ回路 11 - 11、11 - 12 が保持したデジタル A 信号、デジタル B 信号を保持する。他の列についても、奇数列のメモリ 13 がデジタル A 信号、偶数列のメモリ 13 がデジタル B 信号を保持する。

10

#### 【0203】

図 25 (b) は、図 25 (a) に示した撮像装置において、DSP 80 に出力されるデジタル信号と、DSP 80 が出力するデジタル信号と、を表した図である。

#### 【0204】

まず、水平転送部 141 は各列のメモリ 13 からデジタル A 信号およびデジタル B 信号を DSP 80 に出力する。DSP 80 は、同じ画素 100 に基づくデジタル A 信号、デジタル B 信号を加算したデジタル A + B 信号を出力する。

#### 【0205】

DSP 80 は各列の画素 100 のデジタル A 信号、デジタル B 信号を出力した後、DSP 80 は、複数列のメモリ 13 のデジタル A 信号を加算した信号を出力する。

20

#### 【0206】

これにより、撮像装置から出力されるデジタル A 信号の信号量を、デジタル A + B 信号の信号量よりも少なくすることができる。これにより、実施例 2 の撮像装置と同様の効果を得ることができる。

#### 【0207】

他の形態として、図 25 (a) に示した撮像装置において、水平転送部 141 が図 24 (a) のように、複数設けられている形態であっても良い。この形態の場合においても、図 26 (a) に示すように、DSP 80 がデジタル A + B 信号を出力した後、DSP 80 が複数のデジタル A 信号を加算した信号を出力する形態とすることができる。また、図 26 (b) に示す形態としても良い。つまり、DSP 80 が 1 行目と 2 行目の画素 100 の A 信号、B 信号に基づくデジタル A + B 信号を出力する。その後、DSP 80 が 1 行目の画素 100 の A 信号に基づくデジタル A 信号と、2 行目の画素 100 の A 信号に基づくデジタル A 信号と、を加算した信号を出力する。この形態であっても、実施例 2 の撮像装置と同様の効果を得ることができます。

30

#### 【0208】

本実施例では撮像装置が DSP 80 を有する形態としたが、DSP 80 は、撮像装置の外部に設けられた出力信号処理部の形態であっても良い。

#### 【0209】

##### [実施例 13]

40

本実施例の撮像装置について、実施例 12 と異なる点を中心に説明する。

#### 【0210】

図 27 (a) は本実施例の撮像装置の構成の一例を示した図である。本実施例の撮像装置は、水平転送部 141 を水平転送部 141 - 1、141 - 2、141 - 3、141 - 4 の 4 つとした構成である。その他の構成については、図 25 (a) に示した撮像装置と同様とすることができます。本実施例の撮像装置は水平転送部 141 - 1、141 - 2、141 - 3、141 - 4 を有することにより、メモリ 13 - 11、13 - 12、13 - 21、13 - 22 から DSP 80 に同時にデジタル信号を出力させることができる。つまり、メモリ 13 から DSP 80 に 4 チャンネルでデジタル信号を出力させることができる。一方で、本実施例の DSP 80 は 3 チャンネルでの出力としている。

50

**【0211】**

次に、図27(b)を参照しながら、図27(a)に示した撮像装置の動作の一例を説明する。

**【0212】**

図27(b)に示した入力信号1～4はそれぞれ、水平転送部141-1～141-4がメモリ13からDSP80に出力するデジタル信号を示している。また、図27(b)に示した出力信号1～3はDSP80が出力するデジタル信号を示している。

**【0213】**

まず、入力信号1、入力信号3として、1行目の画素100のA信号に基づくデジタルA信号がDSP80に出力される。また、入力信号2、入力信号4として、1行目の画素100のB信号に基づくデジタルA+B信号がDSP80に出力される。DSP80は出力信号1、出力信号2として、1行目の同じ画素100のA信号とB信号に基づくデジタルA信号とデジタルB信号とを加算したデジタルA+B信号を出力する。また、DSP80は出力信号3として、画素100のA信号に基づくデジタルA信号同士を加算した信号を出力する。以降、2行目、3行目の画素100のA信号、B信号についても、1行目の画素100のA信号、B信号と同様の処理とすることができます。10

**【0214】**

本実施例の撮像装置では、DSP80から出力されるデジタルA信号の信号量は、全列のメモリ13のデジタルA信号を出力する形態よりも少ない。よって、実施例12の撮像装置と同様の効果を得ることができる。また、メモリ13からDSP80に4チャンネルでデジタルA信号が出力される。これにより、メモリ13からDSP80にデジタルA信号が出力されるのとほぼ同時に、DSP80が複数列のデジタルA信号を加算した信号を出力することができる。よって、メモリ13からDSP80に1チャンネルでデジタルA信号が出力される形態に比して、本実施例の撮像装置は、メモリ13からDSP80にデジタルA信号が出力されてから、DSP80が複数のデジタルA信号を加算した信号の出力を終えるまでの期間を短縮することができる。また、DSP80は同時に入力されるデジタル信号を加算して出力するため、DSP80内の、一時的にデジタル信号を保持するメモリを実施例12の形態に比して少なくすることができます。20

**【0215】**

本実施例では撮像装置がDSP80を有する形態としたが、DSP80は、撮像装置の外部に設けられた出力信号処理部の形態であっても良い。30

**【0216】**

尚、実施例8～13では、画素100の出力するA信号、B信号、A+B信号が比較回路9に出力される形態を示した。この形態に限定されるものではなく、画素100と比較回路9との間の電気的経路に、実施例1のようにオペアンプ8を設けた形態としても良い。

**【0217】****[実施例14]**

本実施例の撮像装置について、実施例10と異なる点を中心に説明する。図28(a)は本実施例の撮像装置の構成の一例である。画素100の出力するA信号、A+B信号はオペアンプ8に出力される。オペアンプ8は、A信号、A+B信号を增幅して比較回路9に出力する。40

**【0218】**

本実施例では、画素100の各列に、カウンタ回路11が2つ設けられている。1列目の画素100の設けられた列に対応して、カウンタ回路11-11、11-12が設けられている。カウンタ回路11-11は、複数行の画素100のデジタルA信号を加算したデジタル信号を生成するカウンタ回路である。カウンタ回路11-12は、デジタルA+B信号を生成するカウンタ回路である。本実施例では、水平転送部141がカウンタ回路11からデジタル信号をDSP80に出力させる形態としている。

**【0219】**

図28(b)を参照しながら、図28(a)に示した撮像装置のカウンタ回路11-11、11-12の動作を中心に説明する。カウンタ回路11-11、11-12のカウント動作において、カウント値を増加させるか減少させるかは、TG12によって制御される。

#### 【0220】

1行目の画素100のN変換においては、カウンタ回路11-11、11-12は初期値からカウント値が減少する方向でカウント動作を行う。そして、A変換では、カウンタ回路11-11がN変換で保持したカウント値から増加する方向でカウント動作を行う。このA変換でカウンタ回路11-11が保持したデジタルA信号は、A信号からN信号を差し引いた信号に基づくデジタル信号である。10

#### 【0221】

A+B変換では、カウンタ回路11-12が、N変換で保持したカウント値から増加する方向でカウント動作を行う。このA+B変換でカウンタ回路11-12が保持したデジタルA+B信号は、A+B信号からN信号を差し引いた信号に基づくデジタル信号である。水平転送部141は、カウンタ回路11-12からデジタルA+B信号をDSP80に出力させる。そして、TG12はカウンタ回路11-12のカウント値をリセットする。20

#### 【0222】

次に、2行目の画素100のN変換を行う。カウンタ回路11-11は、先の1行目の画素100のA信号に基づくデジタルA信号のカウント値から減少する方向でカウント動作を行う。カウンタ回路11-12はリセットされたカウント値から減少する方向でカウント動作を行う。20

#### 【0223】

そして、2行目の画素100のA変換では、カウンタ回路11-11は、2行目の画素100のN変換で保持したカウント値から増加する方向でカウント動作を行う。このA変換でカウンタ回路11-11が保持したデジタルA信号は、1行目の画素100と2行目の画素100のそれぞれの、A信号からN信号を差し引いた信号同士を加算した信号に基づくデジタル信号である。

#### 【0224】

次に、2行目の画素100のA+B変換では、カウンタ回路11-12は2行目の画素100のN変換で保持したカウント値から増加する方向でカウント動作を行う。このA+B変換でカウンタ回路11-12が保持したデジタルA+B信号は、2行目の画素100のA+B信号からN信号を差し引いた信号に基づくデジタル信号である。30

#### 【0225】

続いて、水平転送部141は、カウンタ11-11、11-12からそれぞれデジタル信号をDSP80に出力させる。

#### 【0226】

本実施例の撮像装置では、カウンタ回路11が複数行の画素100のA信号を加算した信号に基づくデジタル信号を生成する形態である。これにより、カウンタ回路11が各行の画素100のデジタルA信号を生成する形態に比して、カウンタ回路11からデジタルA信号をDSP80に出力させる期間を短縮することができる。また、カウンタ回路11が各行の画素100のデジタルA信号を生成する形態に比して、DSP80に出力されるデジタルA信号の信号量が減少する。これにより、DSP80の信号処理の負荷を低減することができる。40

#### 【0227】

##### [実施例15]

本実施例の撮像装置について、図面を参照しながら説明する。

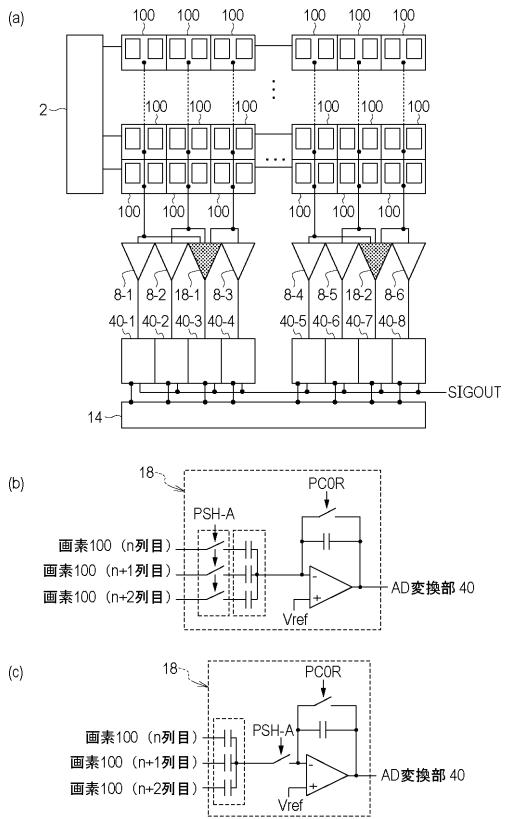

#### 【0228】

図29(a)は、本実施例の撮像装置の構成の一例を示した図である。本実施例の撮像装置は、実施例4の撮像装置のように、各列の信号処理回路がアナログ信号であるA信号、A+B信号を保持する形態である。図29(a)に示すように、各列に、A信号を保持50

するメモリ C\_A、A+B 信号を保持するメモリ C\_AB が設けられている。水平走査回路 14 が信号 C\_A、C\_AB を H レベルとすると、メモリ C\_A、C\_AB から A 信号、A+B 信号が S 信号線 16 に信号 SIGOUT として出力される。各メモリは、たとえば容量素子とスイッチから成るサンプルホールド回路で構成される。S 信号線 16 には、容量 CH の一方のノードが電気的に接続され、容量 CH の他方のノードはグラウンド電位 GND が与えられている。

#### 【0229】

図 29 (b) は図 29 (a) に示した撮像装置の動作の一例を示した図である。

#### 【0230】

まず、水平走査回路 14 は、信号 C\_AB 1~6 を順次 H レベルとして、各列のメモリ C\_AB から、A+B 信号を順次出力させる。

10

#### 【0231】

そして、水平走査回路 14 は、信号 C\_A1、C\_A2、C\_A3 を同時に H レベルとする。これにより、メモリ C\_A1、C\_A2、C\_A3 のそれぞれが保持していた A 信号が S 信号線 16 に同時に出力される。メモリ C\_A1、C\_A2、C\_A3 のそれぞれの容量素子の容量値を C1、C2、C3 とする。信号 SIGOUT は、メモリ C\_A1、C\_A2、C\_A3 の信号の和に、 $(C1 + C2 + C3) / (C1 + C2 + C3 + CH)$  を乗じた値の信号となる。つまり、メモリ C\_A1、C\_A2、C\_A3 のそれぞれが保持した A 信号同士を加算した信号に基づく信号が出力される。

20

#### 【0232】

次に、水平走査回路 14 は、信号 C\_A4、C\_A5、C\_A6 を同時に H レベルとする。これにより、メモリ C\_A4、C\_A5、C\_A6 のそれぞれが保持していた A 信号が同時に出力される。これにより、出力される信号 SIGOUT は、メモリ C\_A4、C\_A5、C\_A6 のそれぞれが保持した A 信号同士が加算された信号が出力される。

。

#### 【0233】

本実施例では、複数のメモリ C\_A が保持した A 信号を加算して出力する。これにより、各列のメモリ C\_A からそれぞれ A 信号を信号 SIGOUT として出力させる形態に比して、A 信号をメモリ C\_A から出力させる期間を短縮することができる。また、各列のメモリ C\_A からそれぞれ A 信号を信号 SIGOUT として出力させる形態に比して A 信号の信号量が減少するため、撮像装置の外部に設けられた AD 变換部の負荷を減らすことができる。

30

#### 【0234】

本実施例では、3 列のメモリ C\_A の A 信号を加算する形態について説明したが、複数列のメモリ C\_A の A 信号を加算する形態であれば良い。

#### 【0235】

##### [実施例 16]

本実施例の撮像装置について、図面を参照しながら説明する。

#### 【0236】

図 30 (a) は、本実施例の撮像装置の構成の一例を示した図である。図 30 (a) では、図 29 (a) と同じ機能を有する部材については、図 29 (a) で付した符号と同一の符号を付して表している。図 30 (a) の撮像装置は、オペアンプ 18-1, 18-2 が複数列の画素 100 の A 信号を加算した信号を増幅して AD 变換部 40-3, 40-7 にそれぞれ出力する形態である。AD 变換部 40 の構成は、図 5、図 8 に示したいずれの形態であっても良い。

40

#### 【0237】

オペアンプ 8-1、8-2、8-3、8-4、8-5、8-6 はそれぞれ、各列の画素 100 の A+B 信号を増幅した信号を AD 变換部 40 に出力する。

#### 【0238】

図 30 (b) は、図 30 (a) に示したオペアンプ 18 の構成の一例について、詳細を

50

示した図である。n列目、n+1列目、n+2列目の画素100のA信号がそれぞれ、信号P S H - AをHレベルとすることで導通するスイッチと、容量素子とを介して、差動増幅器の反転入力ノードに出力される構成としている。差動増幅器からA D変換部40に3列の画素100のA信号を加算した信号に基づく信号が出力される。

#### 【0239】

図30(c)は、オペアンプ18の構成の他の一例について、詳細を示した図である。n列目、n+1列目、n+2列目の画素100のA信号がそれぞれ、容量素子と、信号P S H - AをHレベルとすることで導通するスイッチとを介して、差動増幅器の反転入力ノードに出力される構成としている。図30(c)に示したオペアンプ18の構成であっても、差動増幅器からA D変換部40に3列の画素100のA信号を加算した信号に基づく信号が出力される。図30(b)、図30(c)のいずれのオペアンプ18も、信号P C 0 RをHレベルとすると帰還容量の電荷がリセットされる。これをオペアンプ18のリセットと表記する。

10

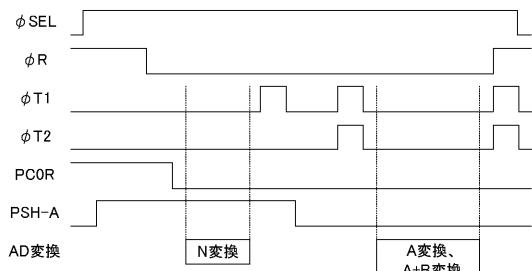

#### 【0240】

図31は、図30(b)あるいは図30(c)に示したオペアンプ18の動作を中心にして示した図である。まず、垂直走査回路2は、1行目の画素100を選択する信号S E LをHレベルとする。その後、図30(a)では不図示のT G 1 2が、信号P S H - AをHレベルとする。そして、垂直走査回路2は、1行目の画素100の信号RをLレベルとする。そして、T G 1 2は、信号P C 0 RをLレベルとし、オペアンプ18のリセットを解除する。この時にオペアンプ18がA D変換部40に出力する信号をN変換として、A D変換部40がデジタルN信号に変換する。

20

#### 【0241】

その後、垂直走査回路2は、信号T 1をHレベルとする。これにより、画素100からA信号が出力される。信号P S H - AがHレベルのため、オペアンプ18は複数列の画素100のA信号を加算した信号を増幅してA D変換部40に出力する。その後、T G 1 2は信号P S H - AをLレベルとする。

#### 【0242】

そして、垂直走査回路2は、信号T 1、T 2をHレベルとする。これにより、1行目の各画素100からA+B信号がオペアンプ8に出力される。

#### 【0243】

続いて、オペアンプ18から信号が出力されるA D変換部40は、A変換として、オペアンプ18から出力される信号をデジタルA信号に変換する。

30

#### 【0244】

そして、オペアンプ8から信号が出力されるA D変換部40は、A+B変換として、オペアンプ8から出力される信号をデジタルA+B信号に変換する。

#### 【0245】

その後、水平走査回路14は各列のA D変換部40から、生成したデジタル信号を順次S I G O U Tとして出力させる。

#### 【0246】

本実施例の撮像装置では、複数列のA信号を加算した信号に基づく信号がA D変換部40に出力される。これにより、各列のA信号に基づく信号をA D変換部40がA D変換する形態に比して、A D変換期間を短縮することができる。また、各列のA信号に基づく信号をA D変換部40がA D変換する形態に比して、デジタルA信号の信号量が減少するため、図30(a)では不図示のD S P 8 0の信号処理の負荷を低減することができる。

40

#### 【0247】

本実施例では、オペアンプ18が3列の画素100のA信号を加算した信号に基づく信号をA D変換部40に出力する形態について説明した。本実施例はこの形態に限定されるものではなく、オペアンプ18が、複数列の画素100のA信号を加算した信号に基づく信号を出力する形態であれば良い。

#### 【0248】

また、本実施例では、オペアンプ8、18の出力する信号が各列のA/D変換部40でデジタル信号に変換される形態を示したが、この形態に限定されるものではない。例えば、図13に示したように、各列からオペアンプ8、18の出力する信号がアナログ信号として出力される形態であっても良い。この形態の場合には、各列からA信号を増幅した信号が出力される形態に比して、A信号を増幅した信号を出力する列数が減少する。これにより、1フレーム期間において、各列からA信号を増幅した信号が出力される形態に比して、A信号を増幅した信号を出力する出力期間を短縮することができる。

## 【0249】

これまでに述べた各実施例の撮像装置は他の実施例と適宜組み合わせて実施しても良い。

。

10

## 【符号の説明】

## 【0250】

1、51 光電変換部

2 垂直走査回路

4 リセットMOSトランジスタ

5 増幅MOSトランジスタ

6 選択MOSトランジスタ

7 垂直信号線

8 オペアンプ

9 比較回路

20

10 ランプ発生回路

11 カウンタ回路

12 TG

13 メモリ

14 水平走査回路

20,50 転送MOSトランジスタ

21 FD領域

10 画素内読み出し回路部

22 カラーフィルター

23 マイクロレンズ

30

100 画素

101 信号読み出し回路

【 図 1 】

(b)

|     |          |      |

|-----|----------|------|

|     |          | AF領域 |

| A+B | A+B      |      |

| A+B | A<br>A+B | A+B  |

(c)

A+B

A

A+B

AF領域

【図2】

【図3】

【 义 4 】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【 図 25 】

(b) 時間

|       |                          |       |       |                          |                          |  |  |  |

|-------|--------------------------|-------|-------|--------------------------|--------------------------|--|--|--|

|       | デジタルA信号<br>デジタルB信号 (1行目) |       |       |                          | デジタルA信号<br>デジタルB信号 (2行目) |  |  |  |

| 1列(A) | 4列(B)                    | 1列(A) | 4列(B) | デジタルA信号<br>デジタルB信号 (1行目) | デジタルA信号<br>(2行目)         |  |  |  |

| 2列(B) | 3列(A)                    | 2列(B) | 3列(A) |                          |                          |  |  |  |

|  |                                                                                       |  |  |  |                                                                                       |  |  |  |

|--|---------------------------------------------------------------------------------------|--|--|--|---------------------------------------------------------------------------------------|--|--|--|

|  | デジタルA+B<br>信号 (1行目)                                                                   |  |  |  | デジタルA+B<br>信号 (2行目)                                                                   |  |  |  |

|  | $-7+8\text{列}(A+B)$<br>$5+6\text{列}(A+B)$<br>$3+4\text{列}(A+B)$<br>$1+2\text{列}(A+B)$ |  |  |  | $13+15\text{列}(A)$<br>$9+11\text{列}(A)$<br>$5+7\text{列}(A)$<br>$1+3\text{列}(A)$       |  |  |  |

|  |                                                                                       |  |  |  | $-7+8\text{列}(A+B)$<br>$5+6\text{列}(A+B)$<br>$3+4\text{列}(A+B)$<br>$1+2\text{列}(A+B)$ |  |  |  |

|  |                                                                                       |  |  |  | $13+15\text{列}(A)$<br>$9+11\text{列}(A)$<br>$5+7\text{列}(A)$<br>$1+3\text{列}(A)$       |  |  |  |

【図26】

The diagram illustrates the digital signal processing flow over time, showing the relationship between input signals, intermediate digital signals, and final output signals.

**時間** (Time) is indicated by a horizontal arrow pointing to the right at the top.

**入力信号 1** (Input Signal 1):

- デジタル A 信号 (1行目) (Digital A Signal (1st row))

- 1列(A) [1列(A)]

- 3列(A) [3列(A)]

- 7列(A) [7列(A)]

- 5列(A) [5列(A)]

**入力信号 2** (Input Signal 2):

- デジタル B 信号 (1行目) (Digital B Signal (1st row))

- 2列(B) [2列(B)]

- 4列(B) [4列(B)]

- 8列(B) [8列(B)]

- 6列(B) [6列(B)]

**出力信号** (Output Signal):

| デジタル A+B 信号 (1行目) | デジタル A+B 信号 (2行目) | デジタル A 信号 (1行目+2行目) |

|-------------------|-------------------|---------------------|

| 7+8列(A+B)         | 7+8列(A+B)         | 7列(A)               |

| 5+6列(A+B)         | 5+6列(A+B)         | 5列(A)               |

| 3+4列(A+B)         | 3+4列(A+B)         | 3列(A)               |

| 1+2列(A+B)         | 1+2列(A+B)         | 1列(A)               |

【図27】

| (b)   | 時間                                                     |

|-------|--------------------------------------------------------|

| 入力信号1 | デジタルA信号 (1行)<br>1列(A)<br>5列(A)<br>9列(A)                |

|       | デジタルA信号 (2行)<br>1列(A)<br>5列(A)<br>9列(A)                |

|       | デジタルA信号 (3行)<br>1列(A)<br>5列(A)<br>9列(A)                |

| 入力信号2 | デジタルB信号 (1行)<br>2列(B)<br>6列(B)<br>10列(B)               |

|       | デジタルB信号 (2行)<br>2列(B)<br>6列(B)<br>10列(B)               |

|       | デジタルB信号 (3行)<br>2列(B)<br>6列(B)<br>10列(B)               |

| 入力信号3 | デジタルA信号 (1行)<br>3列(A)<br>7列(A)<br>11列(A)               |

|       | デジタルA信号 (2行)<br>3列(A)<br>7列(A)<br>11列(A)               |

|       | デジタルA信号 (3行)<br>3列(A)<br>7列(A)<br>11列(A)               |

| 入力信号4 | デジタルB信号 (1行)<br>4列(B)<br>8列(B)                         |