(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2014-143498

(P2014-143498A)

(43) 公開日 平成26年8月7日(2014.8.7)

(51) Int.Cl.

HO4N 5/374 (2011.01)

F 1

HO 4 N 5/335 7 4 O

テーマコード(参考)

HO4N 5/355 (2011.01)

HO 4 N 5/335 5 5 O

5 C 0 2 4

HO4N 5/359 (2011.01)

HO 4 N 5/335 5 9 O

審査請求 未請求 請求項の数 5 O L (全 12 頁)

(21) 出願番号

特願2013-9644 (P2013-9644)

(22) 出願日

平成25年1月22日 (2013.1.22)

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100089118

弁理士 酒井 宏明

(72) 発明者 三原 隆彦

東京都港区芝浦一丁目1番1号 株式会社

東芝内

(72) 発明者 立澤 之康

東京都港区芝浦一丁目1番1号 株式会社

東芝内

(72) 発明者 芦谷 達治

東京都港区芝浦一丁目1番1号 株式会社

東芝内

最終頁に続く

(54) 【発明の名称】 固体撮像装置

## (57) 【要約】

【課題】 固体撮像装置の低照度時の感度を維持しつつダイナミックレンジを拡大するとともに、ブルーミングを抑制する。

【解決手段】 読み出しタイミング制御部 7 E は、画素 PC に蓄積された電荷の読み出しタイミングを制御し、第 1 露光用リセットタイミング制御部 7 C は、画素アレイ部 1 の第 1 ライン上の画素 PC に蓄積された電荷のリセットタイミングを制御し、第 2 露光用リセットタイミング制御部 7 D は、画素アレイ部 1 の第 1 ライン上の画素 PC よりも露光期間が短くなるように第 2 ライン上の画素 PC に蓄積された電荷のリセットタイミングを制御し、補助リセットタイミング制御部 7 F は、画素アレイ部 1 の第 2 ライン上の画素 PC の非露光期間に第 2 ライン上の画素 PC に蓄積された電荷のリセットタイミングを制御する。

【選択図】 図 1

**【特許請求の範囲】****【請求項 1】**

光電変換した電荷を蓄積する画素がマトリックス状に配置された画素アレイ部と、

前記画素を垂直方向に走査する垂直走査回路と、

前記画素を水平方向に走査する水平走査回路と、

前記画素から読み出された画素信号を垂直方向に伝送する垂直信号線と、

前記画素との間でソースフォロア動作を行うことにより、前記画素から前記垂直信号線

にカラムごとに信号を読み出す負荷回路と、

前記画素の露光期間をラインごとに制御する露光期間制御部と、

前記画素の非露光期間に前記画素に蓄積された電荷の排出制御を行なう電荷

排出制御部と、

前記画素から読み出された前記露光期間の異なる信号を合成する画像処理装置とを備え

、

前記露光期間制御部は、

前記画素に蓄積された電荷の読み出しタイミングを制御する読み出しタイミング制御部

と、

第1ライン上の前記画素に蓄積された電荷のリセットタイミングを制御する第1露光用

リセットタイミング制御部と、

前記第1ライン上の前記画素よりも前記露光期間が短くなるように第2ライン上の前記

画素に蓄積された電荷のリセットタイミングを制御する第2露光用リセットタイミング制

御部とを備え、

前記電荷排出制御部は、

前記第2ライン上の前記画素の非露光期間に前記第2ライン上の前記画素に蓄積された

電荷のリセットタイミングを制御する補助リセットタイミング制御部を備えることを特徴

とする固体撮像装置。

**【請求項 2】**

光電変換した電荷を蓄積する画素がマトリックス状に配置された画素アレイ部と、

前記画素の露光期間をラインごとに制御する露光期間制御部と、

前記画素の非露光期間に前記画素に蓄積された電荷の排出制御を行なう電荷

排出制御部とを備えることを特徴とする固体撮像装置。

**【請求項 3】**

前記露光期間制御部は、

前記画素に蓄積された電荷の読み出しタイミングを制御する読み出しタイミング制御部

と、

第1ライン上の前記画素に蓄積された電荷のリセットタイミングを制御する第1露光用

リセットタイミング制御部と、

前記第1ライン上の前記画素よりも前記露光期間が短くなるように第2ライン上の前記

画素に蓄積された電荷のリセットタイミングを制御する第2露光用リセットタイミング制

御部とを備え、

前記電荷排出制御部は、

前記第2ライン上の前記画素の非露光期間に前記第2ライン上の前記画素に蓄積された

電荷のリセットタイミングを制御する補助リセットタイミング制御部を備えることを特徴

とする請求項2に記載の固体撮像装置。

**【請求項 4】**

前記露光期間において、前記第1ライン上の前記画素の前記読み出しタイミングと前記

リセットタイミングの時間間隔は、前記第2ライン上の前記画素の前記読み出しタイミン

グと前記リセットタイミングの時間間隔よりも長いことを特徴とする請求項3に記載の固

体撮像装置。

**【請求項 5】**

前記露光期間の前記第2ライン上の前記画素の前記読み出しタイミングと前記非露光期

10 20 30 40 50

間の前記第2ライン上の前記画素の前記リセットタイミングの時間間隔は、前記露光期間の前記第1ライン上の画素の前記読み出しタイミングと前記露光期間の前記第1ライン上の前記画素の前記リセットタイミングの時間間隔と等しいことを特徴とする請求項4に記載の固体撮像装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、固体撮像装置に関する。

【背景技術】

【0002】

固体撮像装置では、低照度時の感度を維持しつつダイナミックレンジを拡大するためには、短時間露光されるラインと長時間露光されるラインとを交互に設定し、短時間露光されるラインの画素から得られた画像信号と長時間露光されるラインの画素から得られた画像信号とを合成するものがある。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2011-244309号公報

【特許文献2】特開2008-124842号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の一つの実施形態は、低照度時の感度を維持しつつダイナミックレンジを拡大するとともに、ブルーミングを抑制することが可能な固体撮像装置を提供することを目的とする。

【課題を解決するための手段】

【0005】

本発明の一つの実施形態によれば、画素アレイ部と、露光期間制御部と、電荷排出制御部とが設けられている。画素アレイ部は、光電変換した電荷を蓄積する画素がマトリックス状に配置されている。露光期間制御部は、前記画素の露光期間をラインごとに制御する。電荷排出制御部は、前記画素の非露光期間に前記画素に蓄積された電荷の排出制御を行なう。

【図面の簡単な説明】

【0006】

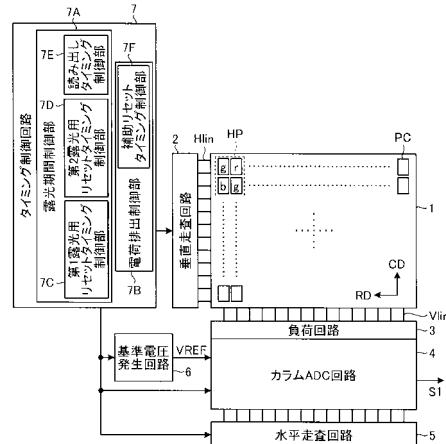

【図1】図1は、第1実施形態に係る固体撮像装置の概略構成を示すブロック図である。

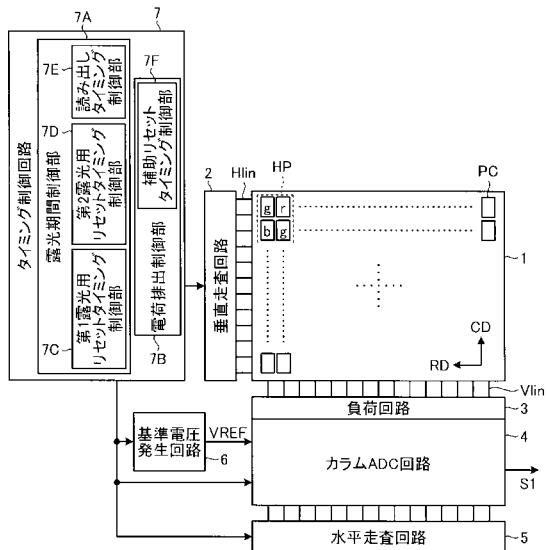

【図2】図2は、図1の固体撮像装置の画素の構成例を示す回路図である。

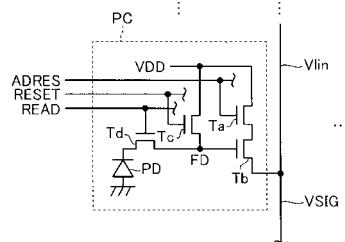

【図3】図3(a)は、第1露光期間における図2の画素の各部の電圧波形を示すタイミングチャート、図3(b)は、第2露光期間における図2の画素の各部の電圧波形を示すタイミングチャートである。

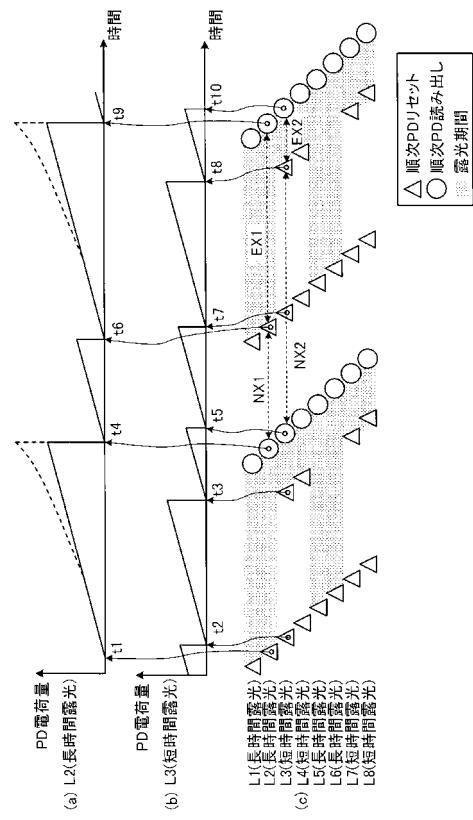

【図4】図4(a)は、第1露光期間におけるPD電荷量を示すタイミングチャート、図4(b)は、第2露光期間におけるPD電荷量を示すタイミングチャート、図4(c)は、画素のリセットタイミングと読み出しタイミングをラインごとに示すタイミングチャートである。

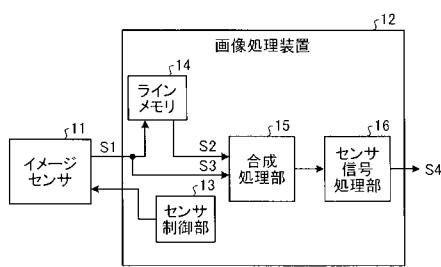

【図5】図5は、第1露光期間および第2露光期間に読み出された信号を合成する画像処理装置の概略構成を示すブロック図である。

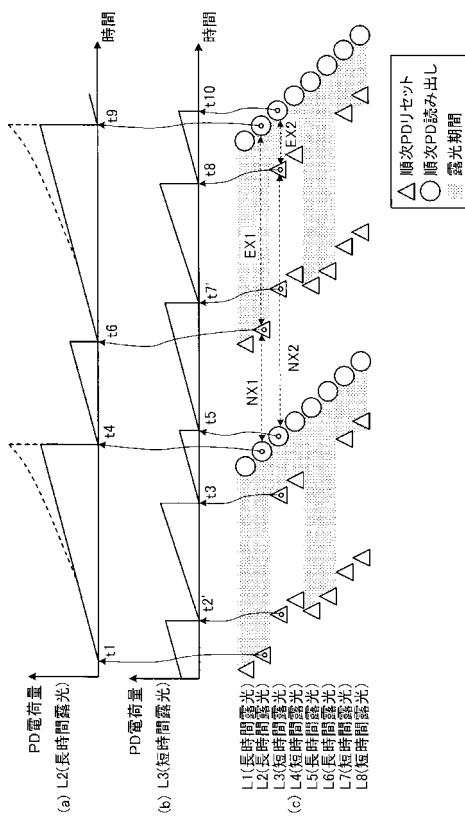

【図6】図6(a)は、第2実施形態に係る固体撮像装置の第1露光期間におけるPD電荷量を示すタイミングチャート、図6(b)は、第2実施形態に係る固体撮像装置の第2露光期間におけるPD電荷量を示すタイミングチャート、図6(c)は、第2実施形態に係る固体撮像装置の画素のリセットタイミングと読み出しタイミングをラインごとに示すタイミングチャートである。

10

20

30

40

50

## 【発明を実施するための形態】

## 【0007】

以下に添付図面を参照して、実施形態に係る固体撮像装置を詳細に説明する。なお、これらの実施形態により本発明が限定されるものではない。

## 【0008】

## (第1実施形態)

図1は、第1実施形態に係る固体撮像装置の概略構成を示すブロック図である。

図1において、固体撮像装置には、画素アレイ部1が設けられている。画素アレイ部1には、光電変換した電荷を蓄積する画素PCがロウ方向RDおよびカラム方向CDにマトリックス状に配置されている。また、この画素アレイ部1において、ロウ方向RDには画素PCの読み出し制御を行う水平制御線Hlinが設けられ、カラム方向CDには画素PCから読み出された信号を伝送する垂直信号線Vlinが設けられている。

10

## 【0009】

また、固体撮像装置には、読み出し対象となる画素PCを垂直方向に走査する垂直走査回路2、画素PCとの間でソースフォロア動作を行うことにより、画素PCから垂直信号線Vlinにカラムごとに信号を読み出す負荷回路3、各画素PCの信号成分をCDSにてカラムごとに検出するカラムADC回路4、読み出し対象となる画素PCを水平方向に走査する水平走査回路5、カラムADC回路4に基準電圧VREFを出力する基準電圧発生回路6および各画素PCの読み出しや蓄積のタイミングを制御するタイミング制御回路7が設けられている。なお、基準電圧VREFはランプ波を用いることができる。

20

## 【0010】

なお、画素アレイ部1では、撮像画像をカラー化するために、4個の画素PCを1組としたベイヤ配列HPをなすことができる。このベイヤ配列HPでは、一方の対角方向に2個の緑色用画素gが配置され、他方の対角方向に1個の赤色用画素rと1個の青色用画素bが配置される。

## 【0011】

タイミング制御回路7には、露光期間制御部7Aおよび電荷排出制御部7Bが設けられている。露光期間制御部7Aには、第1露光用リセットタイミング制御部7C、第2露光用リセットタイミング制御部7Dおよび読み出しタイミング制御部7Eが設けられている。電荷排出制御部7Bには、補助リセットタイミング制御部7Fが設けられている。露光期間制御部7Aは、画素PCの露光期間をラインごとに制御する。電荷排出制御部7Bは、画素PCの非露光期間に画素PCに蓄積された電荷の排出制御を行なう。読み出しタイミング制御部7Eは、画素PCに蓄積された電荷の読み出しタイミングを制御する。第1露光用リセットタイミング制御部7Cは、画素アレイ部1の第1ライン上の画素PCに蓄積された電荷のリセットタイミングを制御する。第2露光用リセットタイミング制御部7Dは、画素アレイ部1の第1ライン上の画素PCよりも露光期間が短くなるように第2ライン上の画素PCに蓄積された電荷のリセットタイミングを制御する。補助リセットタイミング制御部7Fは、画素アレイ部1の第2ライン上の画素PCの非露光期間に第2ライン上の画素PCに蓄積された電荷のリセットタイミングを制御する。なお、第1ラインと第2ラインは、画素アレイ部1上で交互に設定することができる。例えば、ベイヤ配列HPでは、第1ラインは、画素アレイ部1の4n+1(nは0以上の整数)行目と4n+2行目、第2ラインは、画素アレイ部1の4n+3行目と4n+4行目に設定することができる。

30

## 【0012】

そして、垂直走査回路2にて画素PCが垂直方向に走査されることで、ロウ方向RDに画素PCが選択される。そして、負荷回路3において、その画素PCとの間でソースフォロア動作が行われることにより、画素PCから読み出された信号が垂直信号線Vlinを介して伝送され、カラムADC回路4に送られる。また、基準電圧発生回路6において、基準電圧VREFとしてランプ波が設定され、カラムADC回路4に送られる。そして、カラムADC回路4において、画素PCから読み出された信号レベルとリセットレベルが

40

50

ランプ波のレベルに一致するまでクロックのカウント動作が行われ、その時の信号レベルとリセットレベルとの差分がとられることで各画素 P C の信号成分が C D S にて検出され、出力信号 S 1 として出力される。

#### 【 0 0 1 3 】

ここで、画素アレイ部 1 の第 1 ライン上の画素 P C よりも露光時間が短くなるように第 2 ライン上の画素 P C に蓄積された電荷のリセットタイミングを制御することにより、第 1 ライン上の画素 P C では第 2 ライン上の画素 P C に比べて感度を高くすることができる。このため、第 1 ライン上の画素 P C から生成された出力信号 S 1 と第 2 ライン上の画素 P C から生成された出力信号 S 1 とを合成することにより、ダイナミックレンジを向上させることができる。

10

#### 【 0 0 1 4 】

また、画素アレイ部 1 の第 2 ライン上の画素 P C の非露光期間に第 2 ライン上の画素 P C に蓄積された電荷のリセットタイミングを制御することにより、非露光期間に第 2 ライン上の画素 P C に蓄積される電荷を減少させることができる。このため、非露光期間に第 2 ライン上の画素 P C に蓄積される電荷が第 1 ライン上の画素 P C に溢れるのを抑制することができ、ブルーミングを低減することができる。

20

#### 【 0 0 1 5 】

図 2 は、図 1 の固体撮像装置の画素の構成例を示す回路図である。

図 2 において、画素 P C には、フォトダイオード P D 、行選択トランジスタ T a 、増幅トランジスタ T b 、リセットトランジスタ T c および読み出しトランジスタ T d がそれぞれ設けられている。また、増幅トランジスタ T b とリセットトランジスタ T c と読み出しトランジスタ T d との接続点には検出ノードとしてフローティングディフュージョン F D が形成されている。

20

#### 【 0 0 1 6 】

そして、読み出しトランジスタ T d のソースは、フォトダイオード P D に接続され、読み出しトランジスタ T d のゲートには、読み出し信号 R E A D が入力される。また、リセットトランジスタ T c のソースは、読み出しトランジスタ T d のドレインに接続され、リセットトランジスタ T c のゲートには、リセット信号 R E S E T が入力され、リセットトランジスタ T c のドレインは、電源電位 V D D に接続されている。また、行選択トランジスタ T a のゲートには、行選択信号 A D R E S が入力され、行選択トランジスタ T a のドレインは、電源電位 V D D に接続されている。また、増幅トランジスタ T b のソースは、垂直信号線 V l i n に接続され、増幅トランジスタ T b のゲートは、読み出しトランジスタ T d のドレインに接続され、増幅トランジスタ T b のドレインは、行選択トランジスタ T a のソースに接続されている。

30

#### 【 0 0 1 7 】

なお、図 1 の水平制御線 H l i n は、読み出し信号 R E A D 、リセット信号 R E S E T および行選択信号 A D R E S をロウごとに画素 P C に伝送することができる。

30

#### 【 0 0 1 8 】

図 3 ( a ) は、第 1 露光期間における図 2 の画素の各部の電圧波形を示すタイミングチャート、図 3 ( b ) は、第 2 露光期間における図 2 の画素の各部の電圧波形を示すタイミングチャートである。

40

図 3 ( a ) において、図 1 の画素アレイ部 1 の第 1 ライン上の画素 P C には第 1 露光期間 E X 1 が設定され、図 3 ( b ) において、図 1 の画素アレイ部 1 の第 2 ライン上の画素 P C には第 2 露光期間 E X 2 が設定される。第 1 露光期間 E X 1 は第 2 露光期間 E X 2 よりも長い。

#### 【 0 0 1 9 】

そして、図 3 ( a ) に示すように、第 1 ライン上の画素 P C では、行選択信号 A D R E S がロウレベルの場合、行選択トランジスタ T a がオフ状態となり、垂直信号線 V l i n に画素信号 V S I G は出力されない。この時、読み出し信号 R E A D とリセット信号 R E S E T がハイレベルになると ( t a 1 ) 、読み出しトランジスタ T d がオンし、第 1 非露

50

光期間  $N_{X1}$  にフォトダイオード PD に蓄積されていた電荷がフローティングディフュージョン FD に排出される。そして、リセットトランジスタ Tc を介して電源 VDD に排出される。

#### 【0020】

第1非露光期間  $N_{X1}$  にフォトダイオード PD に蓄積されていた電荷が電源 VDD に排出された後、読み出し信号 READ がロウレベルになると、フォトダイオード PD では、有効な信号電荷の蓄積が開始され、第1非露光期間  $N_{X1}$  から第1露光期間 EX1 に移行する。

#### 【0021】

次に、行選択信号 ADRES がハイレベルになると (ta2)、画素 PC の行選択トランジスタ Ta がオンし、増幅トランジスタ Tb のドレインに電源電位 VDD が印加される。

10

#### 【0022】

そして、行選択トランジスタ Ta がオンの状態でリセット信号 RESET がハイレベルになると (ta3)、リセットトランジスタ Tc がオンし、フローティングディフュージョン FD にリーク電流などで発生した余分な電荷がリセットされる。そして、フローティングディフュージョン FD のリセットレベルに応じた電圧が増幅トランジスタ Tb のゲートにかかり、増幅トランジスタ Tb のゲートに印加された電圧に垂直信号線 Vin の電圧が追従することで、リセットレベルの画素信号 VSIG が垂直信号線 Vin に出力される。

20

#### 【0023】

そして、リセットレベルの画素信号 VSIG はカラム ADC 回路 4 に入力され、基準電圧 VREF と比較される。そして、その比較結果に基づいてリセットレベルの画素信号 VSIG がデジタル値に変換され保持される。

#### 【0024】

次に、画素 PC の行選択トランジスタ Ta がオンの状態で読み出し信号 READ がハイレベルになると (ta4)、読み出しトランジスタ Td がオンし、第1露光期間 EX1 にフォトダイオード PD に蓄積されていた電荷がフローティングディフュージョン FD に転送される。そして、フローティングディフュージョン FD の信号読み出しレベルに応じた電圧が増幅トランジスタ Tb のゲートにかかり、増幅トランジスタ Tb のゲートに印加された電圧に垂直信号線 Vin の電圧が追従することで、信号読み出しレベルの画素信号 VSIG が垂直信号線 Vin に出力される。

30

#### 【0025】

そして、信号読み出しレベルの画素信号 VSIG はカラム ADC 回路 4 に入力され、基準電圧 VREF と比較される。そして、その比較結果に基づいてリセットレベルの画素信号 VSIG と信号読み出しレベルの画素信号 VSIG との差分がデジタル値に変換され、第1露光期間 EX1 に応じた出力信号 S1 として出力される。

#### 【0026】

一方、図 3 (b) に示すように、第2ライン上の画素 PC では、行選択信号 ADRES がロウレベルの場合、行選択トランジスタ Ta がオフ状態となり、垂直信号線 Vin に画素信号 VSIG は出力されない。この時、読み出し信号 READ とリセット信号 RESET がハイレベルになると (tb1)、読み出しトランジスタ Td がオンし、第2非露光期間  $N_{X2}$  にフォトダイオード PD に蓄積されていた電荷がフローティングディフュージョン FD に排出される。そして、リセットトランジスタ Tc を介して電源 VDD に排出される。

40

#### 【0027】

第2非露光期間  $N_{X2}$  にフォトダイオード PD に蓄積されていた電荷が電源 VDD に排出された後、読み出し信号 READ がロウレベルになると、フォトダイオード PD では、第2非露光期間  $N_{X2}$  における有効な信号電荷の蓄積が開始される。

#### 【0028】

その後、読み出し信号 R E A D とリセット信号 R E S E T が再びハイレベルになると ( t b 2 ) 、読み出しへンジスタ T d がオンし、第 2 非露光期間 N X 2 にフォトダイオード P D に蓄積されていた電荷がフローティングディフュージョン F D に再度排出される。そして、リセットトランジスタ T c を介して電源 V D D に排出される。

#### 【 0 0 2 9 】

第 2 非露光期間 N X 2 にフォトダイオード P D に蓄積されていた電荷が電源 V D D に再度排出された後、読み出し信号 R E A D がロウレベルになると、フォトダイオード P D では、有効な信号電荷の蓄積が開始され、第 2 非露光期間 N X 2 から第 2 露光期間 E X 2 に移行する。

#### 【 0 0 3 0 】

次に、行選択信号 A D R E S がハイレベルになると ( t b 3 ) 、画素 P C の行選択トランジスタ T a がオンし、増幅トランジスタ T b のドレインに電源電位 V D D が印加される。

#### 【 0 0 3 1 】

そして、行選択トランジスタ T a がオンの状態でリセット信号 R E S E T がハイレベルになると ( t b 4 ) 、リセットトランジスタ T c がオンし、フローティングディフュージョン F D にリーク電流などで発生した余分な電荷がリセットされる。そして、フローティングディフュージョン F D のリセットレベルに応じた電圧が増幅トランジスタ T b のゲートにかかり、増幅トランジスタ T b のゲートに印加された電圧に垂直信号線 V l i n の電圧が追従することで、リセットレベルの画素信号 V S I G が垂直信号線 V l i n に出力される。

#### 【 0 0 3 2 】

そして、リセットレベルの画素信号 V S I G はカラム A D C 回路 4 に入力され、基準電圧 V R E F と比較される。そして、その比較結果に基づいてリセットレベルの画素信号 V S I G がデジタル値に変換され保持される。

#### 【 0 0 3 3 】

次に、画素 P C の行選択トランジスタ T a がオンの状態で読み出し信号 R E A D がハイレベルになると ( t b 5 ) 、読み出しへンジスタ T d がオンし、第 2 露光期間 E X 2 にフォトダイオード P D に蓄積されていた電荷がフローティングディフュージョン F D に転送される。そして、フローティングディフュージョン F D の信号読み出しレベルに応じた電圧が増幅トランジスタ T b のゲートにかかり、増幅トランジスタ T b のゲートに印加された電圧に垂直信号線 V l i n の電圧が追従することで、信号読み出しレベルの画素信号 V S I G が垂直信号線 V l i n に出力される。

#### 【 0 0 3 4 】

そして、信号読み出しレベルの画素信号 V S I G はカラム A D C 回路 4 に入力され、基準電圧 V R E F と比較される。そして、その比較結果に基づいてリセットレベルの画素信号 V S I G と信号読み出しレベルの画素信号 V S I G との差分がデジタル値に変換され、第 2 露光期間 E X 2 に応じた出力信号 S 1 として出力される。

#### 【 0 0 3 5 】

図 4 ( a ) は、第 1 露光期間における P D 電荷量を示すタイミングチャート、図 4 ( b ) は、第 2 露光期間における P D 電荷量を示すタイミングチャート、図 4 ( c ) は、画素のリセットタイミングと読み出しタイミングをラインごとに示すタイミングチャートである。なお、図 4 ( a ) ~ 図 4 ( c ) の例では、画素 P C がベイヤ配列 H P をなし、第 1 ライン ( ライン L 1 、 L 2 、 L 5 、 L 6 ) と第 2 ライン ( ライン L 3 、 L 4 、 L 7 、 L 8 ) が 2 ラインづつ交互に設定される場合を示した。

#### 【 0 0 3 6 】

図 4 ( a ) ~ 図 4 ( c ) において、ライン L 1 、 L 2 、 L 5 、 L 6 では、第 1 露光期間 E X 1 および第 1 非露光期間 N X 1 が設定され、ライン L 3 、 L 4 、 L 7 、 L 8 では、第 2 露光期間 E X 2 および第 2 非露光期間 N X 2 が設定される。

そして、例えば、ライン L 2 の画素 P C では、第 1 非露光期間 N X 1 にフォトダイオード

10

20

30

40

50

ド P D に蓄積された電荷が排出されることにより ( t 1 ) 、第 1 非露光期間 N X 1 から第 1 露光期間 E X 1 に移行する。一方、例えば、ライン L 3 の画素 P C では、第 2 非露光期間 N X 2 にフォトダイオード P D に蓄積された電荷が排出され ( t 2 ) 、第 2 非露光期間 N X 2 が維持される。その後、ライン L 3 の画素 P C では、第 2 非露光期間 N X 2 にフォトダイオード P D に蓄積された電荷が再度排出され ( t 3 ) 、第 2 非露光期間 N X 2 から第 2 露光期間 E X 2 に移行する。

#### 【 0 0 3 7 】

次に、ライン L 2 の画素 P C では、第 1 露光期間 E X 1 にフォトダイオード P D に蓄積された電荷が読み出されることにより ( t 4 ) 、第 1 露光期間 E X 1 から第 1 非露光期間 N X 1 に移行する。一方、ライン L 3 の画素 P C では、第 2 露光期間 E X 2 にフォトダイオード P D に蓄積された電荷が読み出されることにより ( t 5 ) 、第 2 露光期間 E X 2 から第 2 非露光期間 N X 2 に移行する。10

#### 【 0 0 3 8 】

同様に、ライン L 2 の画素 P C では、第 1 非露光期間 N X 1 にフォトダイオード P D に蓄積された電荷が排出されることにより ( t 6 ) 、第 1 非露光期間 N X 1 から第 1 露光期間 E X 1 に移行する。一方、ライン L 3 の画素 P C では、第 2 非露光期間 N X 2 にフォトダイオード P D に蓄積された電荷が排出され ( t 7 ) 、第 2 非露光期間 N X 2 が維持される。その後、ライン L 3 の画素 P C では、第 2 非露光期間 N X 2 にフォトダイオード P D に蓄積された電荷が再度排出され ( t 8 ) 、第 2 非露光期間 N X 2 から第 2 露光期間 E X 2 に移行する。20

#### 【 0 0 3 9 】

次に、ライン L 2 の画素 P C では、第 1 露光期間 E X 1 にフォトダイオード P D に蓄積された電荷が読み出されることにより ( t 9 ) 、第 1 露光期間 E X 1 から第 1 非露光期間 N X 1 に移行する。一方、ライン L 3 の画素 P C では、第 2 露光期間 E X 2 にフォトダイオード P D に蓄積された電荷が読み出されることにより ( t 1 0 ) 、第 2 露光期間 E X 2 から第 2 非露光期間 N X 2 に移行する。

#### 【 0 0 4 0 】

ここで、第 1 露光期間 E X 1 が第 2 露光期間 E X 2 よりも長いと、第 2 非露光期間 N X 2 は第 1 非露光期間 N X 1 よりも長くなる。そして、第 2 非露光期間 N X 2 が長くなると、第 2 非露光期間 N X 2 にフォトダイオード P D に蓄積される電荷量が増える。この結果、フォトダイオード P D の入射光量が大きいと、第 2 非露光期間 N X 2 にフォトダイオード P D に蓄積された電荷が溢れ、ライン L 3 上の画素 P C からライン L 2 上の画素 P C に流れ込む。ライン L 3 上の画素 P C からライン L 2 上の画素 P C に電荷が流れ込むと、ライン L 2 上の画素 P C の電荷量は点線で示すように増大し、ブルーミングが発生する。このため、第 2 非露光期間 N X 2 にフォトダイオード P D に蓄積された電荷を第 2 非露光期間 N X 2 に複数回繰り返してフォトダイオード P D から排出させることにより、第 2 非露光期間 N X 2 にフォトダイオード P D に蓄積される電荷量を減少させることができ、第 2 非露光期間 N X 2 にフォトダイオード P D に蓄積された電荷が溢れるのを抑制することができる。30

#### 【 0 0 4 1 】

また、第 2 露光期間 E X 2 の第 2 ライン上の画素 P C の読み出しタイミング ( ライン L 3 では時刻 t 7 ) と第 2 非露光期間 N X 2 の第 2 ライン上の画素 P C のリセットタイミング ( ライン L 3 では時刻 t 5 ) の時間間隔は、第 1 露光期間 E X 1 の第 1 ライン上の画素 P C の読み出しタイミング ( ライン L 2 では時刻 t 6 ) と第 1 露光期間 E X 1 の第 1 ライン上の画素 P C のリセットタイミング ( ライン L 2 では時刻 t 4 ) の時間間隔と等しくすることができる。これにより、第 2 ライン上の画素 P C のフォトダイオード P D から補助的に電荷を排出させるタイミングを、第 1 ライン上の画素 P C のフォトダイオード P D から電荷を排出させるタイミングと整合させることができ、これらのタイミング制御を容易化することが可能となることから、回路構成の煩雑化を防止することができる。40

#### 【 0 0 4 2 】

10

20

30

40

50

図5は、第1露光期間および第2露光期間に読み出された信号を合成する画像処理装置の概略構成を示すプロック図である。

図5において、画像処理装置12には、センサ制御部13、ラインメモリ14、合成処理部15およびセンサ信号処理部16が設けられている。そして、画像処理装置12は、イメージセンサ11に接続されている。なお、イメージセンサ11は、図1の構成を用いることができる。

#### 【0043】

ここで、センサ制御部13は、ユーザ操作等に応じて制御信号を生成し、イメージセンサ11の各部に制御信号を供給することで、イメージセンサ11がユーザ操作に応じた動作となるように制御する。また、センサ制御部13は、イメージセンサ11を制御し、例えば、第1ライン上の長時間露光および第2ライン上の短時間露光の出力信号S1を生成させることができる。

#### 【0044】

ラインメモリ14は、イメージセンサ11から出力された出力信号S1を露光期間ごとに分離して、露光期間ごとの出力信号S1のタイミングを一致させて出力することができる。合成処理部15は、長時間露光および短時間露光の出力信号S1を合成することで、ダイナミックレンジの拡張された画像信号を生成することができる。センサ信号処理部16は、ホワイトバランス調整やデモザイク処理、画質調整などの信号処理を行うことができる。

#### 【0045】

そして、ラインメモリ14には、第1ライン上の長時間露光および第2ライン上の短時間露光の出力信号S1のうち、例えば、第1ライン上の長時間露光の出力信号S2が保存される。そして、次のライン読み出しのタイミングにおいて、イメージセンサ11から第2ライン上の短時間露光の出力信号S3が出力されると、それと同時にラインメモリ14から第1ライン上の長時間露光の出力信号S2が読み出され、合成処理部15に送られる。そして、合成処理部15において出力信号S2、S3が合成された後、センサ信号処理部16にて信号処理が行われることで、ダイナミックレンジの拡大された画像信号S4が出力される。

#### 【0046】

なお、上述した実施形態において、第1ライン上の画素PCではフォトダイオードPDに蓄積された電荷の排出を第1非露光期間NX1に1回だけ行い、第2ライン上の画素PCではフォトダイオードPDに蓄積された電荷の排出を第2非露光期間NX2に2回だけ行う方法について説明したが、第2ライン上の画素PCにおいてフォトダイオードPDに蓄積された電荷の排出を第2非露光期間NX2に3回以上行ってもよいし、第1ライン上の画素PCにおいてフォトダイオードPDに蓄積された電荷の排出を第1非露光期間NX1に複数回行ってもよい。

#### 【0047】

また、上述した実施形態では、ダイナミックレンジを拡大するために、長時間露光と短時間露光の2つの異なる露光時間をラインごとに設定する方法について説明したが、長時間露光と中時間露光と短時間露光の3つの異なる露光時間をラインごとに設定するようにしてもよいし、4以上の異なる露光時間をラインごとに設定するようにしてもよい。

#### 【0048】

##### (第2実施形態)

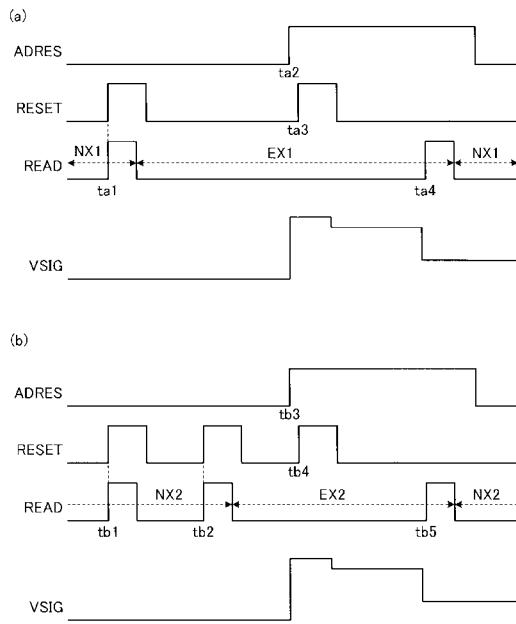

図6(a)は、第2実施形態に係る固体撮像装置の第1露光期間におけるPD電荷量を示すタイミングチャート、図6(b)は、第2実施形態に係る固体撮像装置の第2露光期間におけるPD電荷量を示すタイミングチャート、図6(c)は、第2実施形態に係る固体撮像装置の画素のリセットタイミングと読み出しタイミングをラインごとに示すタイミングチャートである。

図6(a)～図6(c)において、この第2実施形態では、第2非露光期間NX2の第2ライン上の画素PCのリセットタイミング(ラインL3では時刻t2'、t7')は第

10

20

30

40

50

2 非露光期間  $N \times 2$  の中央に設定される。すなわち、例えば、ライン L 3において、読み出しタイミング  $t_5$  と 1 回目の P D リセットタイミング  $t_7'$ との間隔は、1回目の P D リセットタイミング  $t_7'$  と 2回目の P D リセットタイミング  $t_8$ との間隔と等しい。これにより、第 2 非露光期間  $N \times 2$  において、各 P D リセットまでにフォトダイオード P D に蓄積される電荷量を均一化することができ、フォトダイオード P D に蓄積される電荷量の最大値を低下させることができるとなることから、フォトダイオード P D に蓄積された電荷を溢れ難くすることができる。

#### 【0049】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

10

#### 【符号の説明】

#### 【0050】

1 画素アレイ部、2 垂直走査回路、3 負荷回路、4 カラムADC回路、5 水平走査回路、6 基準電圧発生回路、7 タイミング制御回路、7A 露光期間制御部、7B 電荷排出制御部、7C 第1露光用リセットタイミング制御部、7D 第2露光用リセットタイミング制御部、7E 読み出しタイミング制御部、7F 補助リセットタイミング制御部、PC 画素、HP ベイヤ配列、Ta 行選択トランジスタ、Tb 増幅トランジスタ、Tc リセットトランジスタ、Td 読み出しへトランジスタ、PD フォトダイオード、FD フローティングディフュージョン、Vlin 垂直信号線、Hlin 水平制御線

20

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(72)発明者 吉武 由実

東京都港区芝浦一丁目1番1号 株式会社東芝内

F ターム(参考) 5C024 CX03 CX12 CX43 CX47 GY31 GY38 GZ01 JX41