(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2012년05월25일

(11) 등록번호 10-1150638

(24) 등록일자 2012년05월21일

- (51) 국제특허분류(Int. C1.)

*H01F 17/00* (2006.01) *H01F 27/00* (2006.01)

*H03H 7/06* (2006.01)

- (21) 출원번호 10-2008-0094707

(22) 출원일자 2008년09월26일

심사청구일자 2008년09월26일

- (65) 공개번호 10-2009-0033115

(43) 공개일자 2009년04월01일

- (30) 우선권주장

JP-P-2007-00254661 2007년09월28일 일본(JP)

- (56) 선행기술조사문헌

JP11154730 A\*

JP2001044105 A\*

JP2001326517 A\*

US20030184495 A1

- \*는 심사관에 의하여 인용된 문헌

(73) 특허권자

**후지쯔 가부시끼가이샤**

일본국 가나가와肯 가와사키시 나카하라구 가미고다나카 4초메 1-1

**다이요 유덴 가부시끼가이샤**

일본국 도쿄도 다이토구 우에노 6초메 16반 20고

(72) 발명자

**우에다 사또시**

일본 가나가와Ken 가와사끼시 나카하라구 가미고다나카 4초메 1-1 후지쯔 가부시끼가이샤 내

**다까하시 다케오**

일본 가나가와Ken 요코하마시 고호꾸꾸 신요꼬하마 2초메 3-12 후지쯔 메디아 테바이스 가부시끼가이샤 내

(뒷면에 계속)

(74) 대리인

**이중희, 박충범, 장수길**

전체 청구항 수 : 총 6 항

심사관 : 조성찬

## (54) 발명의 명칭 전자 부품

**(57) 요 약**

도전성 패턴을 갖는 전자 부품에서, 도전성 패턴의 화상 인식이 가능하며, 도전성 패턴의 인덕터 특성에의 영향을 억제하는 것을 가능하게 하는 것이다. 본 발명은, 기판(25)과, 기판(25) 위에 설치된 스파이럴 형상의 코일(10, 20)과, 코일(10, 20)의 내측에 형성되고, 코일(10, 20)의 표면의 광의 반사율보다 높은 광의 반사율을 가지며, 복수로 분할된 도전성 패턴(50)을 구비하는 전자 부품이다.

**대 표 도 - 도2**

(72) 발명자

**마쓰모토 쯔요시**

일본 가나가와쿄 가와사끼시 나카하라구 가미꼬다

나카 4조메 1-1 후지쓰 가부시끼가이샤 내

**요꼬야마 쯔요시**

일본 가나가와쿄 가와사끼시 나카하라구 가미꼬다

나카 4조메 1-1 후지쓰 가부시끼가이샤 내

---

미 시아오유

일본 가나가와쿄 가와사끼시 나카하라구 가미꼬다

나카 4조메 1-1 후지쓰 가부시끼가이샤 내

## 특허청구의 범위

### 청구항 1

기판과,

상기 기판 위에 설치된 원형 스파이럴 형상의 코일과,

상기 코일의 내측에 형성되고, 상기 코일의 표면의 광의 반사율보다 높은 광의 반사율을 갖고, 복수로 분할된 도전성 패턴과,

상기 기판 위의 하부 전극과 상기 하부 전극 위에 형성된 유전체 층과 상기 유전체 층 위에 형성된 상부 전극을 포함하고, 상기 코일과 전기적으로 접속된 캐페시터를 구비하고,

상기 도전성 패턴은 상기 하부 전극과 동일한 재료로 형성되며, 상기 코일은 도금층으로 형성되는 것을 특징으로 하는 전자 부품.

### 청구항 2

제1항에 있어서,

상기 코일은, 세로 방향으로 이격하여 설치되고 서로 전기적으로 접속된 복수의 코일인 것을 특징으로 하는 전자 부품.

### 청구항 3

제1항 또는 제2항에 있어서,

상기 복수로 분할된 도전성 패턴은, 위치 확인용 마커인 것을 특징으로 하는 전자 부품.

### 청구항 4

제1항 또는 제2항에 있어서,

상기 복수로 분할된 도전성 패턴은, 화상 인식용 패턴인 것을 특징으로 하는 전자 부품.

### 청구항 5

제1항 또는 제2항에 있어서,

상기 복수의 분할된 도전성 패턴 각각의 형상은, 원형, 사각형, 삼각형, 마름모형 및 타원형 중 어느 하나인 것을 특징으로 하는 전자 부품.

### 청구항 6

삭제

### 청구항 7

삭제

### 청구항 8

기판과,

상기 기판 위에 설치된 원형 스파이럴 형상의 코일과,

상기 코일의 외주로부터 상기 코일의 반경의 거리 이내에 형성되고, 상기 코일의 표면의 광의 반사율보다 높은 광의 반사율을 갖고, 복수로 분할된 위치 확인용 마커인 도전성 패턴과,

상기 기판 위의 하부 전극과 상기 하부 전극 위에 형성된 유전체 층과 상기 유전체 층 위에 형성된 상부 전극을 포함하고, 상기 코일과 전기적으로 접속된 캐페시터를 구비하고,

상기 도전성 패턴은 화상 인식용 패턴이고,

상기 도전성 패턴은 상기 하부 전극과 동일한 재료로 형성되며, 상기 코일은 도금층으로 형성되는 것을 특징으로 하는 전자 부품.

## 청구항 9

삭제

### 명세서

#### 발명의 상세한 설명

##### 기술분야

[0001]

본 발명은 전자 부품에 관한 것으로, 도전성 패턴을 갖는 전자 부품에 관한 것이다.

##### 배경기술

[0002]

위상 정합 등을 행하는 경우, 인덕터나 캐패시터가 이용된다. 예를 들면, 휴대 전화나 와이어리스 LAN(Local Area Network) 등의 RF(Radio frequency) 시스템에서는, 소형화, 저코스트화, 고성능화의 요구가 있다. 이 요구를 만족하기 위해, 기판 위에 인덕터나 캐패시터 등의 수동 소자를 집적화한 집적형 수동 소자 등의 전자 부품이 이용된다.

[0003]

집적형 수동 소자를 패키지 또는 모듈 기판에 실장하는 경우, 고성능화를 위해 페이스 다운 실장을 행하는 것이 유효하다. 집적화 수동 소자를 페이스 다운 실장하기 위해서는, 우선, 집적화 수동 소자의 외부에 접속하기 위한 패드 위에, 금 등의 스터드 범프, 도금 범프, 또는, 땀납 볼을 형성한다. 스터드 범프는 와이어 본더를 이용하여 형성되고, 땀납 볼은 볼 마운터를 이용하여 형성된다. 다음으로, 플립 칩 본더를 이용하여, 집적화 수동 소자를 패키지 또는 모듈 기판에 실장한다.

[0004]

특히 문헌 1에는, 기판 위에 스파이럴 형상의 코일을 인덕터로서 이용한 집적 전자 부품이 개시되어 있다. 특히 문헌 2 및 특허 문헌 3에는, 스파이럴 형상의 복수의 코일이 세로 방향으로 이격하여 설치된 인덕터가 개시되어 있다.

[0005]

[특허 문헌 1] 일본 특허 공개 2006-157738호 공보

[0006]

[특허 문헌 2] 일본 특허 공개 2007-67236호 공보

[0007]

[특허 문헌 3] 미국 특허 제6518165호 명세서

#### 발명의 내용

##### 해결 하고자하는 과제

[0008]

와이어 본더, 볼 마운터 또는 플립 칩 본더 등의 본더를 사용할 때에는, 위치 확인용 마커를, 미리 집적화 수동 소자 내에 형성한다. 본당시에는, 위치 확인용 마커를 기준으로, 스터드 범프나 땀납 볼의 형성 또는 플립 칩 실장을 행한다. 본더에서, 위치 확인용 마커의 인식은 화상 인식에 의해 행해진다. 이 때문에, 위치 확인용 마커의 크기나 콘트라스트는 본더를 화상 인식할 수 있을 정도인 것이 요구된다. 따라서, 위치 확인용 마커는 일정 이상의 크기이고, 또한 광의 반사율이 큰 도전성 패턴으로 하는 것이 요구된다. 한편, 도전성인 위치 확인용 마커가 커지면, 코일로부터의 유도 전류가 위치 확인용 마커에 생겨 와전류손이 발생하여 인덕터 특성에 영향을 미치게 된다.

[0009]

본 발명은, 상기 과제를 감안하여 이루어진 것으로, 도전성 패턴을 갖는 전자 부품에서, 도전성 패턴의 화상 인식이 가능하고, 도전성 패턴의 인덕터 특성에의 영향을 억제하는 것을 가능하게 하는 것을 목적으로 한다.

##### 과제 해결수단

[0010]

본 발명은, 기판과, 상기 기판 위에 설치된 스파이럴 형상의 코일과, 상기 코일의 내측에 형성되고, 상기 코일의 표면의 광의 반사율보다 높은 광의 반사율을 갖고, 복수로 분할된 도전성 패턴을 구비하는 것을 특징으로 하는 전자 부품이다. 본 발명에 따르면, 도전성 패턴의 광의 반사율이 높기 때문에 도전성 패턴의 화상 인식이 가능하고, 또한 도전성 패턴이 복수로 분할되어 있기 때문에 도전성 패턴의 인덕터 특성에의 영향을

역제할 수 있다.

[0011] 상기 구성에서, 상기 코일은, 세로 방향으로 이격하여 설치되고 서로 전기적으로 접속된 복수의 코일인 구성으로 할 수 있다.

[0012] 상기 구성에서, 상기 복수로 분할된 도전성 패턴은, 위치 확인용 마커인 구성으로 할 수 있다. 또한, 상기 구성에서, 상기 복수로 분할된 도전성 패턴은, 화상 인식용 패턴인 구성으로 할 수 있다. 또한, 상기 구성에서, 상기 복수의 분할된 도전성 패턴 각각의 형상은, 원형, 사각형, 삼각형, 마름모형 및 타원형 중 어느 하나인 구성으로 할 수 있다.

[0013] 상기 구성에서, 상기 기판 위에 설치된 캐패시터를 구비하고, 상기 도전성 패턴은, 상기 캐패시터의 하부 전극과 동일한 재료로 이루어지는 구성으로 할 수 있다. 이 구성에 따르면, 제조 공정을 간략화할 수 있다.

[0014] 상기 구성에서, 상기 코일은 도금층으로 이루어지는 구성으로 할 수 있다.

[0015] 본 발명은, 기판과, 상기 기판 위에 설치된 스파이럴 형상의 코일과, 상기 코일의 외주로부터 상기 코일의 절반의 거리 이내에 형성되고, 상기 코일의 표면의 광의 반사율보다 높은 광의 반사율을 갖고, 복수로 분할된 위치 확인용 마커인 도전성 패턴을 구비하고, 상기 도전성 패턴은 화상 인식용 패턴인 것을 특징으로 하는 전자 부품이다.

## 효과

[0016] 본 발명에 따르면, 도전성 패턴의 광의 반사율이 높기 때문에 도전성 패턴의 화상 인식이 가능하고, 또한 도전성 패턴이 복수로 분할되어 있기 때문에 도전성 패턴의 인덕터 특성에의 영향을 억제할 수 있다.

### 발명의 실시를 위한 구체적인 내용

[0017] 이하, 도면을 참조하여, 본 발명의 실시예에 대하여 설명한다.

[0018] <실시예 1>

[0019] 큰 위치 확인용 마커는, 집적화 수동 소자의 칩 면적 삭감의 장해로 된다. 따라서, 인덕터의 코일 내에 위치 확인용 마커를 배치하는 것이 생각된다. 그러나, 인덕터 코일 내에 위치 확인용 마커를 배치하면 인덕터의 인덕턴스 및 Q값(첨예도)이 저하하는 것을 알 수 있었다. 이하에, 이 과제를 해결하기 위해 행한 실험 및 실시예 1에 대하여 설명한다.

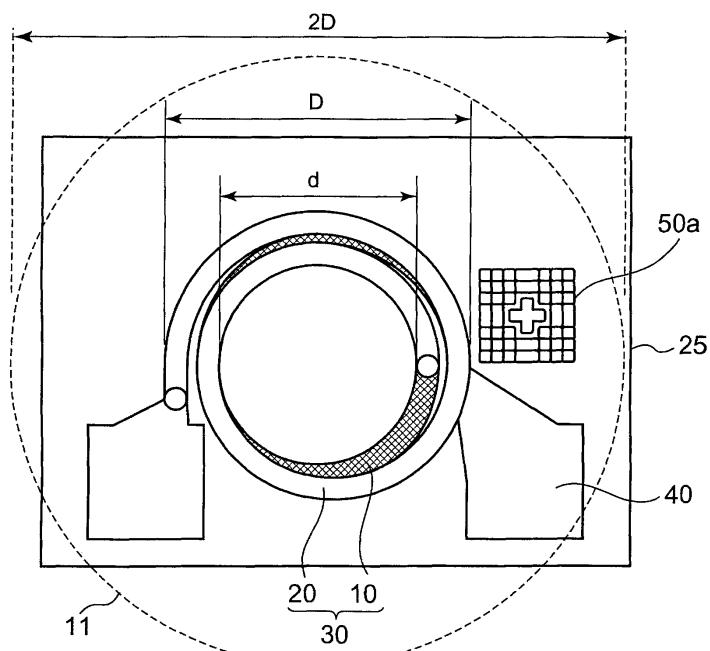

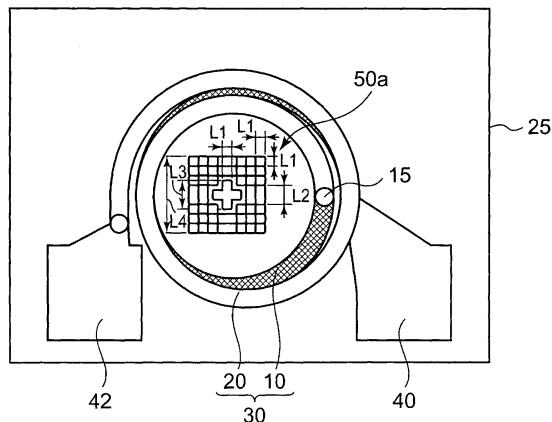

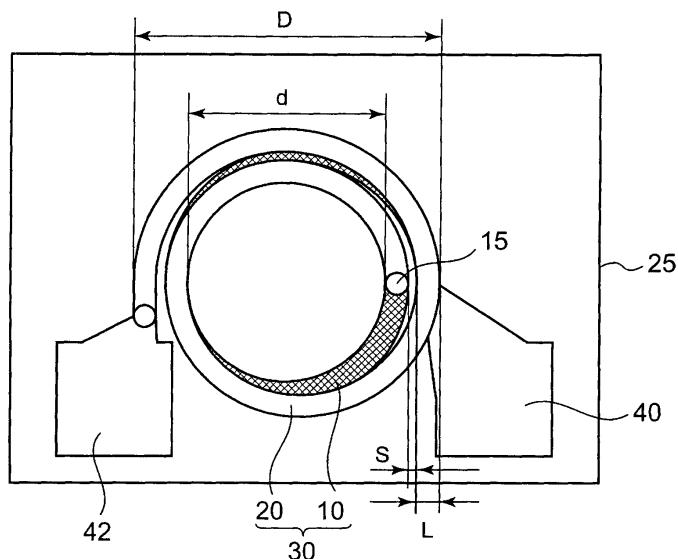

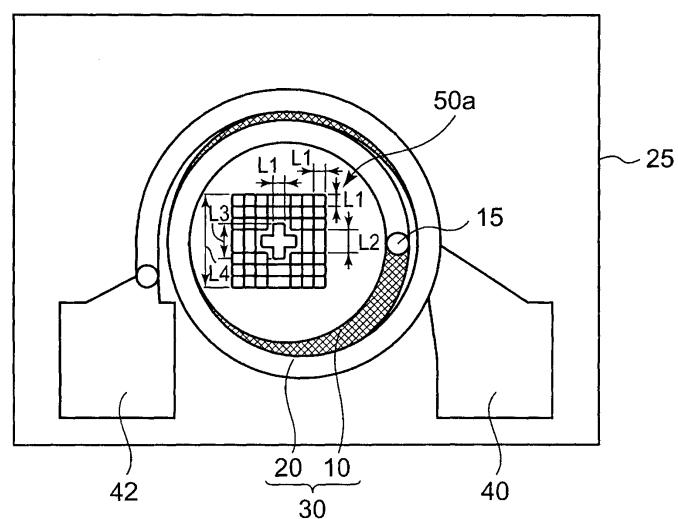

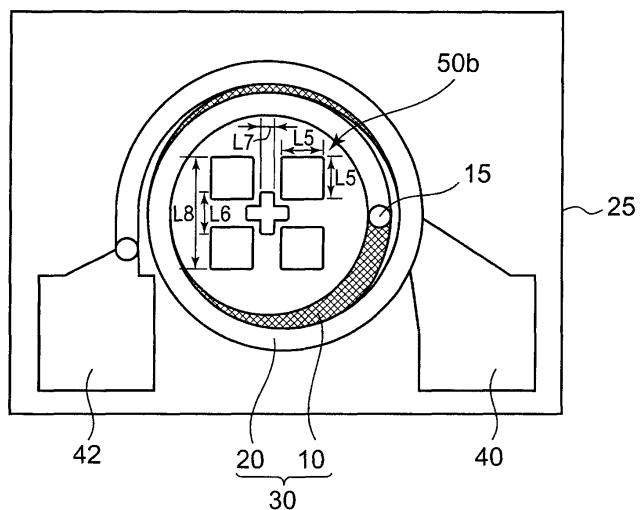

[0020] 도 1 내지 도 4는 시작(試作)한 인덕터 소자의 평면도이다. 도 1은 비교예 1에 따른 인덕터 소자, 도 2는 실시예 1에 따른 인덕터 소자, 도 3은 실시예 1의 변형예에 따른 인덕터 소자, 도 4는 비교예 2에 따른 인덕터 소자를 나타내고 있다. 도 1 내지 도 4에서, 인덕터 소자는 모두 동일한 구성이다. 도 1을 참조하여, 제작한 인덕터 소자의 구성을 설명한다. 인덕터 소자는 클래스 기판(25) 위에 설치된 인덕터(30)와 패드(40 및 42)를 갖고 있다. 인덕터(30)는 원형 스파이럴 형상의 제1 코일(10)과 제2 코일을 갖고 있다. 기판(25) 위에 스파이럴 형상의 제1 코일(10), 제1 코일(10) 위에 스파이럴 형상의 제2 코일(20)이 이격하여 설치되고, 제1 코일(10)과 제2 코일(20) 사이는 공극으로 되어 있다. 즉 대기가 충만되어 있다. 제1 코일(10) 및 제2 코일(20)은 거의 겹치도록 설치되어 있다. 제1 코일(10)은, 최외주에서 패드(40)에 접속되며 1주의 스파이럴이다. 제2 코일(20)은, 최외주에서 패드(42)에 접속되며 1.5주의 스파이럴이다. 제1 코일(10)과 제2 코일(20)은, 최내주에서 접속부(15)에 의해 접속되어 있다. 인덕터(30)의 외경 D는  $480\mu\text{m}$ , 내경 d는  $300\mu\text{m}$ , 선폭 L은  $40\mu\text{m}$ , 선 간격 S는  $10\mu\text{m}$ 이다.

[0021] 도 2를 참조하여, 실시예 1에 따른 인덕터 소자에서는, 인덕터(30)의 내경 내에 위치 확인용 마커로서 도전성 패턴(50a)이 형성되어 있다. 도전성 패턴(50a)은, 1변 L1이  $15\mu\text{m}$ 인 정방형 패턴 36개와, 변 L1 및 변 L2가 각각  $15\mu\text{m}$  및  $30\mu\text{m}$ 인 직사각형 패턴 8개와, 최소폭 L1 및 최대폭 L3이 각각  $15\mu\text{m}$  및  $70\mu\text{m}$ 이고 중앙에 형성된 십자 패턴을 갖고 있다. 정방형 패턴과 장방형 패턴의 간격은  $5\mu\text{m}$ 이며, 도전성 패턴(50a)의 외변 L4는  $150\mu\text{m}$ 이다.

[0022] 도 3을 참조하여, 실시예 1의 변형예에 따른 인덕터 소자에서는, 인덕터(30)의 내경 내에 위치 확인용 마커로서 도전성 패턴(50b)이 형성되어 있다. 도전성 패턴(50b)은, 1변 L5가  $65\mu\text{m}$ 인 정방형 패턴 4개와, 최소폭 L7 및 최대폭 L6이 각각  $25\mu\text{m}$  및  $75\mu\text{m}$ 이고 중앙에 형성된 십자 패턴을 갖고 있다. 정방형 패턴끼리의 간격은  $50\mu\text{m}$ 이며, 도전성 패턴(50b)의 외변 L8은  $180\mu\text{m}$ 이다.

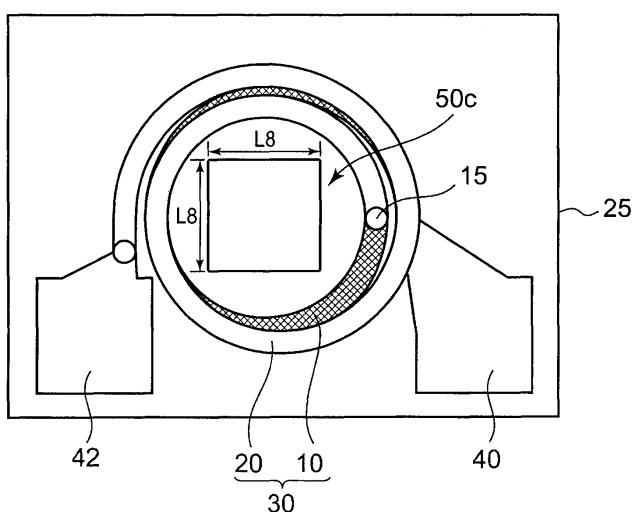

[0023] 도 4를 참조하여, 실시예 1에 따른 인덕터 소자에서는, 인덕터(30)의 내경 내에 위치 확인용 마커로서 도전성 패턴(50c)이 형성되어 있다. 도전성 패턴(50c)은, 1번 L8이  $180\mu\text{m}$ 인 정방형 패턴이다. 제1 코일(10) 및 제2 코일(20)은, 도금법을 이용하여 형성된 막 두께가 약  $10\mu\text{m}$ 인 구리로 이루어진다. 한편, 도전성 패턴(50a 내지 50c)은, 스파터링법을 이용하여 형성된 아래에서부터 순서대로 티탄( $20\text{nm}$ )/금( $1000\text{nm}$ )으로 이루어진다. 제1 코일(10) 및 제2 코일(20)은 도금법을 이용하여 형성되어 있기 때문에, 표면에 형성되는 요철이 크고, 광의 반사율은 작다. 한편, 도전성 패턴(50a 내지 50c)은 스파터링법을 이용하여 형성되고, 또한 표면이 금이기 때문에, 표면의 광의 반사율이 크다.

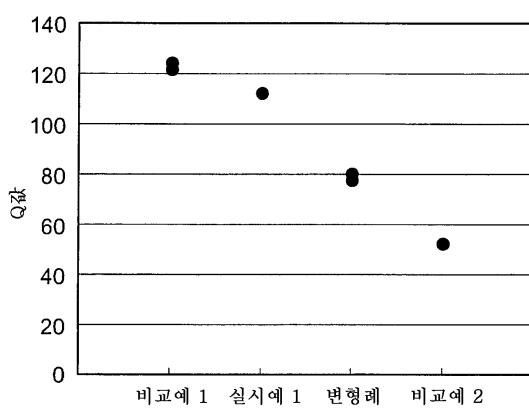

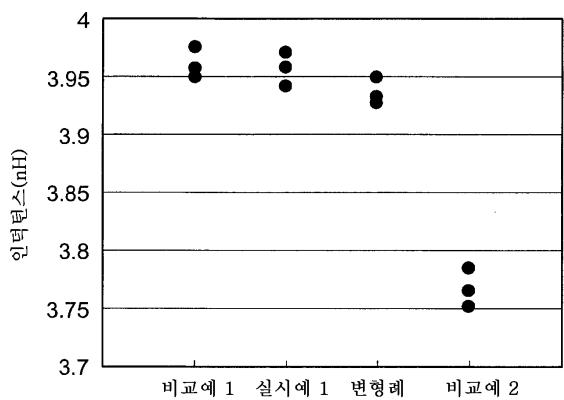

[0024] 도 5는 제작한 각 종류(비교예 1, 실시예 1의 변형에 및 비교예 2)의 인덕터 소자의 Q값을 측정한 결과를 나타내는 도면이며, 도 6은 제작한 각 종류의 인덕터 소자의 인덕턴스값을 측정한 결과를 나타내는 도면이다. 도 5 및 도 6에서, 각 종류의 인덕터 소자에 대하여 도시된 복수의 도트는, 1개의 종류에 대하여 측정한 복수의 인덕터 소자의 결과이다.

[0025] 도 5를 참조하여, Q값은, 비교예 1이 가장 크고, 비교예 2가 가장 작다. 실시예 1 및 그 변형예는, 비교예 1 및 비교예 2 사이의 값으로 된다. 도 6을 참조하여, 인덕턴스값은, 비교예 1이 가장 크고, 비교예 2가 가장 작다. 실시예 1 및 그 변형예는 비교예 1과 거의 동일한 인덕턴스값이다.

[0026] 비교예 1에 따른 인덕터 소자는, 인덕터(30) 내에 도전성 패턴이 형성되어 있지 않고, 본래의 Q값 및 인덕턴스값을 갖고 있다. 이에 대하여 비교예 2에 따른 인덕턴스 소자는, 인덕터(30) 내에 도전성 패턴을 형성함으로써, Q값 및 인덕턴스값이 작게 되어 있다. 이것은, 인덕터(30) 내에 도전성 패턴(50c)을 배치한 것에 기인하여, 와전류순이 생겼기 때문이다. 실시예 1 및 그 변형예에서는, 도전성 패턴(50a 및 50b)이 분할되어 있다. 이 때문에, 도전성 패턴(50a 및 50b)에 생기는 와전류가 억제되어, 인덕터(30)의 Q값 및 인덕턴스값이 비교예 2에 대하여 향상된다.

[0027] 실시예 1에 따르면, 도전성 패턴(50a 또는 50b)이 제1 코일(10) 및 제2 코일(20)의 내측에 형성되어 있음으로써, 도전성 패턴(50a 또는 50b)을 배치하는 칩 면적을 삐감할 수 있다. 또한, 도전성 패턴(50a 또는 50b)이 복수로 분할되어 있음으로써, 도 5 및 도 6에 도시한 바와 같이 도전성 패턴(50a 또는 50b)의 인덕터 특성에의 영향을 억제할 수 있다. 또한, 도전성 패턴(50a 또는 50b)의 광의 반사율이, 제1 코일(10) 및 제2 코일(20)의 광의 반사율보다 높음으로써, 도전성 패턴(50a 또는 50b)을 일체로 하여 위치 확인용 마커로서 사용할 수 있다. 와이어 본더, 볼 마운터 또는 플립 칩 본더 등의 본더를 사용할 때의 위치의 인식은, 광학 현미경을 이용하여 행해진다. 이 때문에, 패턴의 광의 반사율이 높으면 분할된 패턴은 일체로서 인식된다. 따라서, 도전성 패턴(50a 및 50b)을 일체로 하여 화상 인식용 패턴으로서 이용할 수 있다.

[0028] <실시예 2>

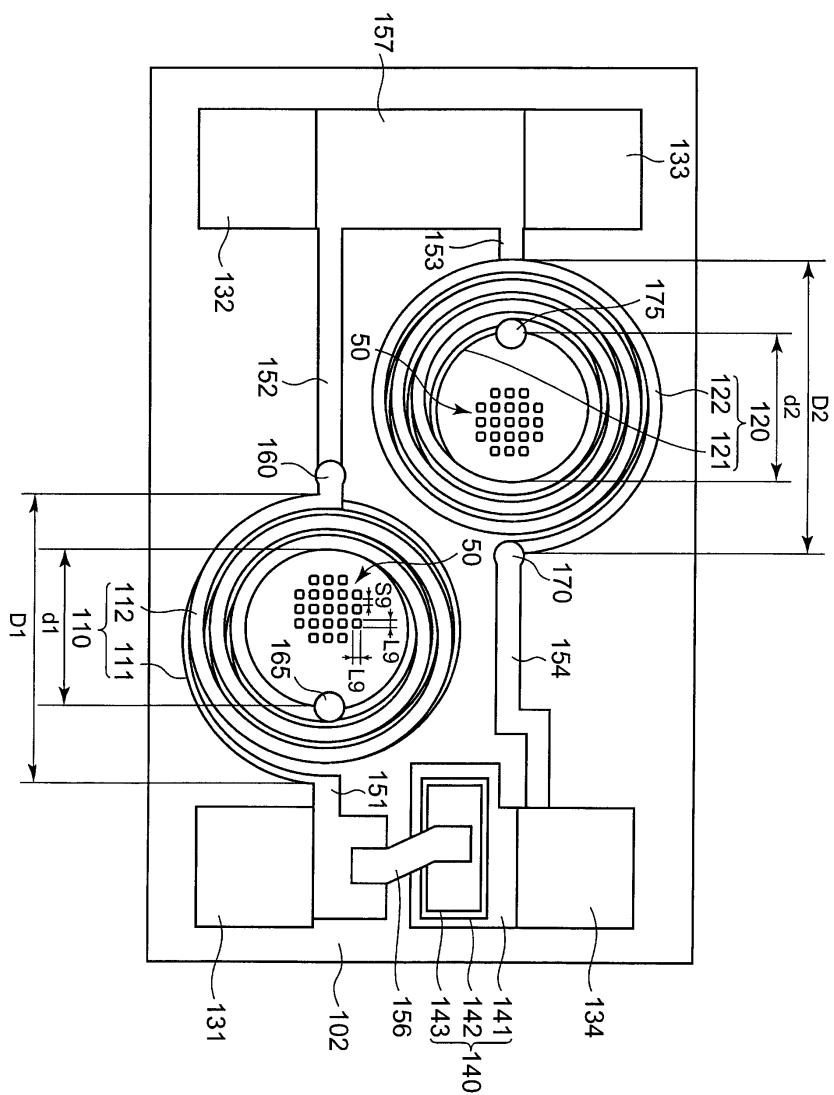

[0029] 실시예 2는, 인덕터와 캐패시터를 이용한 집적화 수동 소자의 예이다. 도 7은 실시예 2에 따른 집적화 수동 소자의 상면도이다. 도 7을 참조하여, 기판(102) 위에, 제1 코일(111) 및 제2 코일(112)로 이루어지는 인덕터(110), 및 제1 코일(121) 및 제2 코일(122)로 이루어지는 인덕터(120)가 형성되어 있다. 인덕터(110)의 제1 코일(111) 및 제2 코일(112)의 내단은 접속부(165)에 의해 서로 접속되며, 제1 코일(111)은 외단에서 배선(151)에 접속되고, 제2 코일(112)은 외단에서 접속부(160)를 통하여 배선(152)에 접속되어 있다. 인덕터(120)의 제1 코일(121) 및 제2 코일(122)의 내단은 접속부(175)에 의해 서로 접속되며, 제1 코일(121)은 외단에서 배선(153)에 접속되고, 제2 코일(122)은 외단에서 접속부(170)를 통하여 배선(154)에 접속되어 있다. 배선(151 내지 154)은 기판(102) 위에 형성되고, 각각 패드(131 내지 134)에 접속되어 있다. 패드(132)와 패드(133)는 배선(157)에 의해 접속되어 있다. 패드(131)와 패드(134) 사이에는, 하부 전극(141), 유전체층(142) 및 상부 전극(143)으로 이루어지는 캐패시터(140)가 접속되어 있다. 상부 전극(143)과 배선(151)은 상부의 배선(156)에 의해 접속되어 있다. 패드(131)를 입력, 패드(134)를 출력, 패드(132 및 133)를 접지함으로써, 집적화 수동 소자는, 패드(131)와 패드(134) 사이에  $\pi$ 형 L-C-L 회로를 구성한다. 인덕터(110)의 외경 D1은  $350\mu\text{m}$ , 내경 d1은  $200\mu\text{m}$ , 인덕터(120)의 외경 D2는  $400\mu\text{m}$ , 내경 d2는  $190\mu\text{m}$ 이다. 제1 코일(111 및 121) 및 제2 코일(112 및 122)의 선폭은  $15\mu\text{m}$ , 선 간격은  $15\mu\text{m}$ 이다.

[0030] 도 7을 참조하여, 제2 코일(112 및 122)의 내측에 각각 도전성 패턴(50)이 배치되어 있다. 도전성 패턴(50)은, 1번 L9가  $10\mu\text{m}$ 인 정방형 패턴이 21개로 이루어지고, 외경은  $115\mu\text{m}$ 이다. 정방형 패턴의 간격 S9는  $10\mu\text{m}$ 이다.

[0031] 실시예 2에 따른 집적화 수동 소자를 복수 제작한 바, 인덕터(110 및 120)의 인덕턴스값은 각각 설계값과  $\pm 5\%$  이내의 정밀도에서 일치하고, 또한 높은 Q값을 얻을 수 있었다. 또한, 도전성 패턴(50)을 이용하여 스터

드 범프의 형성 및 페이스 다운 실장을 문제없이 행할 수 있었다. 이에 의해, 도전성 패턴(50)은 화상 인식용 패턴으로서 이용할 수 있는 것을 확인하였다.

[0032] <실시예 3>

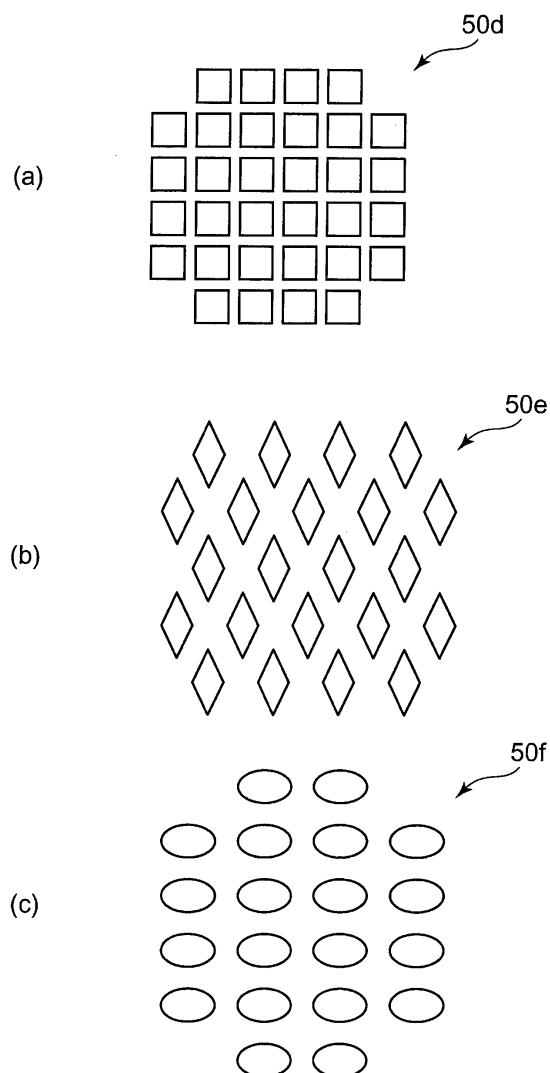

[0033] 실시예 3은 도전성 패턴의 예이다. 도 8의 (a)와 같이, 도전성 패턴(50d)은, 복수의 정방형 패턴이 배열된 패턴이어도 된다. 또한, 도 8의 (b)와 같이, 도전성 패턴(50e)은, 복수의 마름모형 패턴이 배열된 패턴이어도 된다. 도 8의 (c)와 같이, 도전성 패턴(50f)은 타원형 패턴이 배열된 패턴이어도 된다. 도 9의 (a)와 같이, 도전성 패턴(50g)은 복수의 삼각형 패턴이 배열된 패턴이어도 된다. 도 9의 (b)와 같이, 도전성 패턴(50h)은 분할된 패턴이 2중으로 배열된 형상이어도 된다. 도 9의 (c)와 같이, 도전성 패턴(50i)은, 분할된 패턴이 2열로 배열된 패턴이어도 된다. 도 9의 (d)와 같이, 도전성 패턴(50j)은, 분할된 패턴이 십자 형상으로 배치된 패턴이어도 된다. 이상과 같이, 도전성 패턴은, 본더 등에 화상 인식 가능한 패턴이면, 어느 패턴이어도 된다. 화상 인식에 이용하는 광은 일반적으로는 가시광이지만, 적외광 등의 가시광 외의 광이어도 된다.

[0034] <실시예 4>

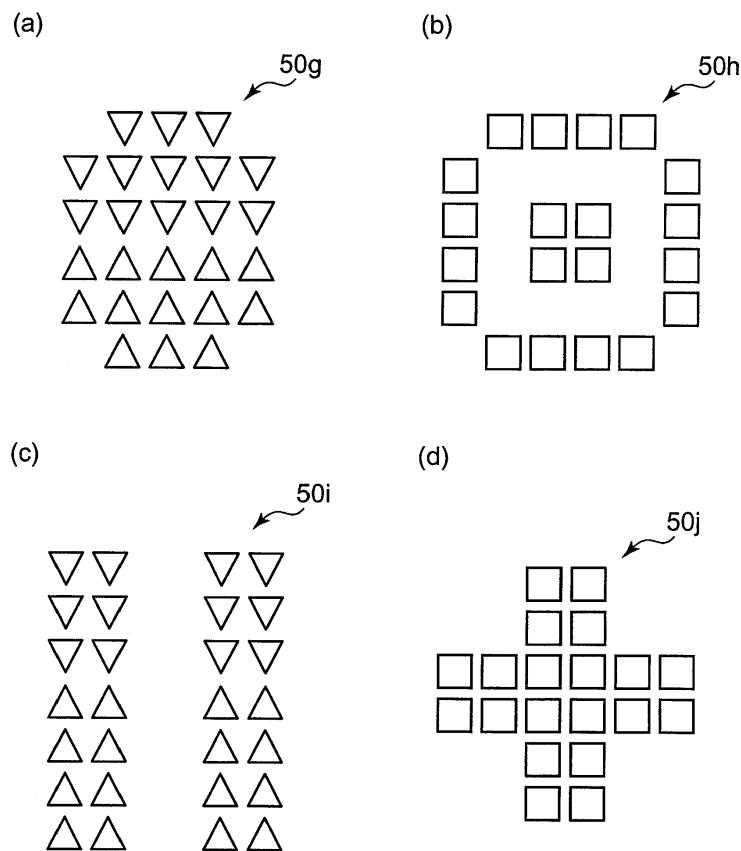

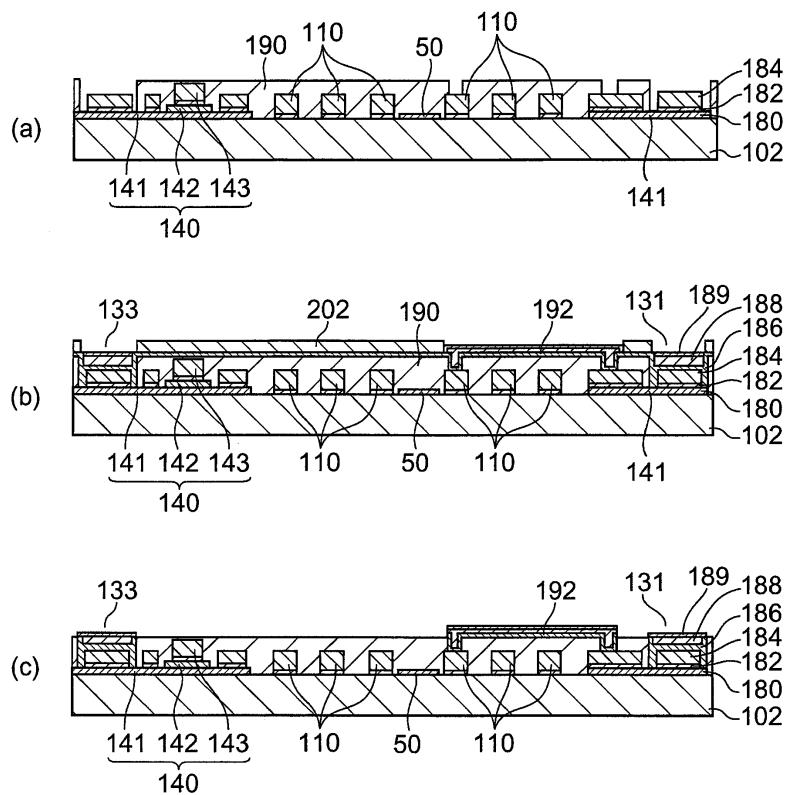

[0035] 실시예 4는, 기판 위에 인덕터 및 캐패시터를 형성하는 제조 방법의 예이다. 도 10의 (a)를 참조하여, 기판(102) 위에, MIM(Metal Insulator Metal) 캐패시터의 하부 전극(141), 도전성 패턴(50) 및 패드의 하부층으로서 금속층(180)을 스퍼터링법 또는 증착법을 이용하여 형성한다. 기판(102)은, 석영(합성 석영을 포함함), 글래스(파이렉스(등록 상표), 텐팩스, 알루미노 실리케이트, 봉규산 글래스 등), 세라믹 기판 등의 절연 기판 또는 고저항 실리콘 기판, LiNbO<sub>3</sub> 기판, LiTaO<sub>3</sub> 기판 등을 이용할 수 있다. 금속층(180)은 비교적 저항이 낮은 Al, Au 또는 Cu를 주재료로서 이용하는 것이 바람직하다. 금속층(180)은 다층 구성이어도 된다. 예를 들면, 기판(102)측으로부터 순서대로 Ti/Au/Ni/Au(20nm/500nm/20nm/500nm)의 4층 구성, 또는 Ti/Au/Ti(20nm/1000nm/20nm) 혹은 Ti/Cu/Ti(20nm/1000nm/20nm)의 3층 구성으로 할 수 있다.

[0036] 도 10의 (b)를 참조하여, 하부 전극(141) 위에 유전체층(142)을 스퍼터링법이나 PECVD(Plasma enhanced chemical vapor deposition)법을 이용하여 형성한다. 유전체층(142)으로서는, SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, Al<sub>2</sub>O<sub>3</sub>, Ta<sub>2</sub>O<sub>5</sub> 등을 이용할 수 있다. 예를 들면, 유전체층(142)은, 두께가 195nm인 PECVD법을 이용하여 형성한 SiO<sub>2</sub>막이다. 도 10의 (c)를 참조하여, 전기 도금용의 종층(182)을 형성한다. 종층(182)의 재료로서, 후에 전기 도금을 행하는 재료와 동일한 것이 바람직하며, 예를 들면 Ti/Cu(20nm/500nm)를 스퍼터링법을 이용하여 형성한다.

[0037] 도 10의 (d)를 참조하여, 종층(182) 위에 도금을 행하는 개구부를 갖는 포토레지스트(200)를 형성한다. 개구부 내에 전해 도금을 행하여, 예를 들면 막 두께가 10μm인 Cu로 이루어지는 도금층(184)을 형성한다.

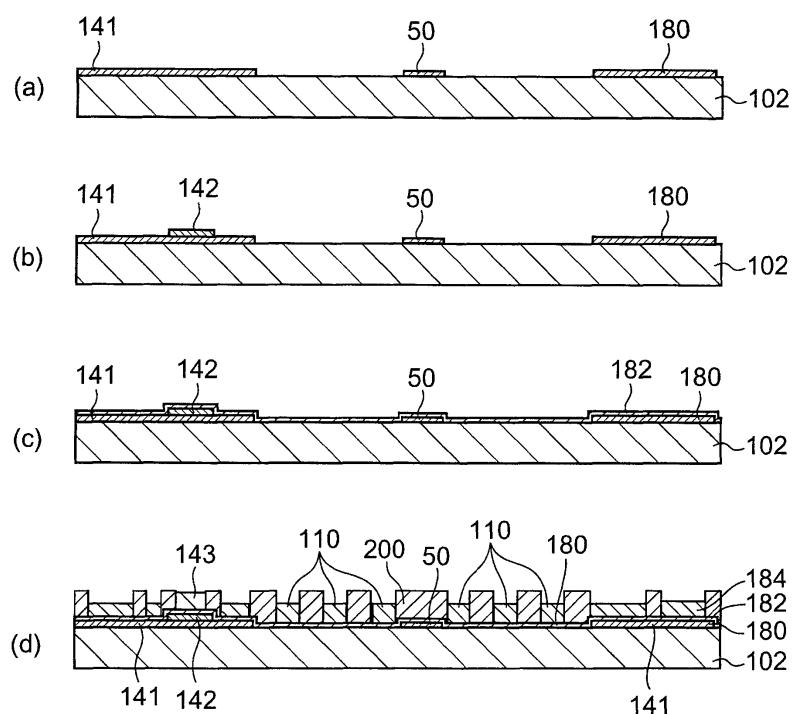

[0038] 도 11의 (a)를 참조하여, 포토레지스트(200)를 제거한다. 도금층(184)을 마스크로 하여 종층(182)을 제거한다. 도금층(184) 및 종층(182)에 의해, 인덕터(110), 캐패시터의 상부 전극(143), 패드부 등이 형성된다. 하부 전극(141), 유전체층(142) 및 상부 전극(143)에 의해 캐패시터(140)가 형성된다. 도금층(184)을 덮도록 상면이 평탄한 후막 유전체층(190)을 형성한다. 후막 유전체층(190)으로서는, 폴리이미드, BCB(Benzocyclobutene) 등을 이용할 수 있다. 후막 유전체층(190)의 패드로 될 영역 등의 소정 영역을 제거한다.

[0039] 도 11의 (b)를 참조하여, 후막 유전체층(190) 위에 종층(182)과 동일한 막 두께의 종층(186)을 형성한다. 종층(186) 위에 개구부를 갖는 포토레지스트(202)를 형성한다. 개구부 내에 전해 도금을 행하여, 예를 들면 막 두께가 10μm인 Cu로 이루어지는 도금층(188)을 형성한다. 도금층(188) 위에 Ni/Au로 이루어지는 표면층(189)을 형성한다.

[0040] 도 11의 (c)를 참조하여, 포토레지스트(202)를 제거한다. 표면층(189)을 마스크로 하여 종층(186)을 제거한다. 종층(186), 도금층(188) 및 표면층(189)에 의해, 패드(13 및 133) 및 상부 배선(192)이 형성된다. 이상에 의해, 실시예 4에 따른 접적화 수동 소자가 완성된다. 실시예 4에 따른 접적화 수동 소자에서, 인덕터(110)는, 특히 문헌 1과 마찬가지로 스파이럴 형상의 코일이 1층으로 형성되어 있다. 이와 같이, 인덕터(110)는 스파이럴 형상의 코일이 1층이어도 된다. 또한, 실시예 1 및 실시예 2와 같이, 인덕터는, 세로 방향으로 이격하여 형성되며 서로 전기적으로 접속된 복수의 코일이어도 된다.

[0041] 실시예 4에 따르면, 도 10의 (a)와 같이, 도전성 패턴(50)은, 기판(102) 위에 형성된 캐패시터(140)의 하부 전극(141)과 동시에 형성되어 있다. 즉, 도전성 패턴(50)은, 하부 전극(141)과 동일한 재료로 이루어진다.

이에 의해, 제조 공정을 간략화할 수 있다. 또한, 도전성 패턴(50)의 광의 반사율을 높이기 위해서는, 도전성 패턴(50)의 상면이 평탄한 것이 바람직하다. 따라서, 도전성 패턴(50)을 스퍼터링법 또는 증착법을 이용하여 형성하는 것이 바람직하다.

[0042] 실시예 1 및 실시예 2에 따른 인덕터 소자의 제조는, 특히 문헌 1에 기재된 방법으로 제조할 수 있다. 이 경 우도 실시예 4와 같이, 캐패시터의 하부 전극과 동시에 도전성 패턴을 형성할 수 있다.

[0043] <실시예 5>

[0044] 실시예 5는 도전성 패턴이 코일의 밖에 있는 예이다. 도 12는 실시예 5에 따른 인덕터 소자의 평면도이다. 도 12를 참조하여, 실시예 1의 도 2와 비교하여, 도전성 패턴(50a)이 인덕터(30)의 외측에 형성되어 있다. 도전성 패턴(50a)은, 인덕터(30)의 외주로부터 인덕터(30)의 반경  $D/2$  외측의 원(11)(직경이  $2D$ 인 원)의 내측에 형성되어 있다. 인덕터(30)의 자장은 인덕터(30)의 외측에도 발생하고 있다. 인덕터(30)의 외측의 자장은 인덕터(30)의 반경 정도의 거리까지 미친다. 따라서, 도전성 패턴(50a)이 인덕터(30)(즉 제1 코일(10) 및 제2 코일(20))의 외주로부터 인덕터(30)의 절반의 거리 이내에 형성되는 경우에도, 도전성 패턴을 분할하는 것이 유효하다. 이에 의해, 인덕터(30)의 Q값 및 인덕턴스값의 저하를 억제할 수 있다.

[0045] 실시예 1 내지 실시예 5에서, 도전성 패턴의 재료는, 기판과의 밀착성이 높은 고용접 재료, 예를 들면 Ti, Cr, Ni, Mo, Ta, W 등과, 고주파 저항이 낮은 Au, Cu, Al, Ag 등을 적층한 막이 바람직하다. 특히, Ti/Au/Ti, Ti/Cu/Ti, Cr 또는 Ni/Au 또는 Cu를 이용하는 것이 바람직하다. 이에 의해, 도전성 패턴의 고주파 저항을 저감할 수 있고, 기판과의 밀착성을 향상시킬 수 있다. 또한, 도전성 패턴과 캐패시터의 하부 전극을 동일한 재료로 형성한 경우, 하부 전극과 캐패시터의 유전체충과의 밀착성을 높일 수 있다.

[0046] 이상, 본 발명의 실시예에 대하여 상술하였지만, 본 발명은 이러한 특정한 실시예에 한정되는 것은 아니며, 특히 청구 범위에 기재된 본 발명의 요지의 범위 내에서, 여러 가지의 변형·변경이 가능하다.

### 도면의 간단한 설명

[0047] 도 1은 비교예 1에 따른 인덕터 소자의 상면도.

[0048] 도 2는 실시예 1에 따른 인덕터 소자의 상면도.

[0049] 도 3은 실시예 1의 변형예에 따른 인덕터 소자의 상면도.

[0050] 도 4는 비교예 2에 따른 인덕터 소자의 상면도.

[0051] 도 5는 각 종류의 인덕터 소자의 Q값을 나타내는 도면.

[0052] 도 6은 각 종류의 인덕터 소자의 인덕턴스값을 나타내는 도면.

[0053] 도 7은 실시예 2에 따른 집적화 수동 소자의 상면도.

[0054] 도 8의 (a) 내지 (c)는 실시예 3의 도전성 패턴을 도시하는 도면(그 1).

[0055] 도 9의 (a) 내지 (d)는 실시예 3의 도전성 패턴을 도시하는 도면(그 2).

[0056] 도 10의 (a) 내지 (d)는 실시예 4에 따른 집적화 수동 소자의 제조 공정을 나타내는 도면(그 1).

[0057] 도 11의 (a) 내지 (c)는 실시예 4에 따른 집적화 수동 소자의 제조 공정을 나타내는 도면(그 2).

[0058] 도 12는 실시예 5에 따른 인덕터 소자의 상면도.

[0059] <도면의 주요 부분에 대한 부호의 설명>

[0060] 10: 제1 코일

[0061] 20: 제2 코일

[0062] 25: 기판

[0063] 30: 인덕터

[0064] 50: 도전성 패턴

[0065]

141: 하부 전극

## 도면

## 도면1

## 도면2

도면3

도면4

도면5

도면6

도면7

도면8

## 도면9

## 도면10

## 도면11

## 도면12