US009203478B2

US 9,203,478 B2

Dec. 1, 2015

# (12) United States Patent

# Saito

### (54) POWER SUPPLY DEVICE AND DRIVING METHOD THEREOF

- (75) Inventor: Toshihiko Saito, Atsugi (JP)

- (73) Assignee: Semiconductor Energy Laboratory Co., Ltd., Atsugi-shi, Kanagawa-ken (JP)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 709 days.

- (21) Appl. No.: 13/070,517

- (22) Filed: Mar. 24, 2011

### (65) **Prior Publication Data**

US 2011/0241435 A1 Oct. 6, 2011

### (30) Foreign Application Priority Data

Mar. 31, 2010 (JP) ..... 2010-083153

(51) Int. Cl.

| H01F 38/14 | (2006.01) |

|------------|-----------|

| H04B 5/00  | (2006.01) |

| H02J 5/00  | (2006.01) |

| H02J 7/02  | (2006.01) |

- (58) Field of Classification SearchCPC combination set(s) only.See application file for complete search history.

### (56) **References Cited**

### U.S. PATENT DOCUMENTS

| 5,731,856 | А | 3/1998  | Kim et al.       |

|-----------|---|---------|------------------|

| 5,744,864 | Α | 4/1998  | Cillessen et al. |

| 5.990.516 | Α | 11/1999 | Momose et al.    |

| 6,229,164 H | 31   | 5/2001 | Momose et al.  |

|-------------|------|--------|----------------|

| 6,294,274 H | 31   | 9/2001 | Kawazoe et al. |

| 6,410,952 H | 32   | 6/2002 | Momose et al.  |

| 6,563,174 H | 32   | 5/2003 | Kawasaki et al |

| 6,642,560 H | 32 1 | 1/2003 | Momose et al.  |

| 6,727,522 H | 31   | 4/2004 | Kawasaki et al |

|             |      |        |                |

(10) **Patent No.:**

(45) Date of Patent:

(Continued)

### FOREIGN PATENT DOCUMENTS

| EP1724048A211/2006EP1737044A12/2006 |

|-------------------------------------|

|-------------------------------------|

(Continued)

### OTHER PUBLICATIONS

International Search Report (Application No. PCT/JP2011/057514) Dated May 10, 2011.

(Continued)

Primary Examiner - Jared Fureman

Assistant Examiner — Aqeel Bukhari

(74) *Attorney, Agent, or Firm* — Eric J. Robinson; Robinson Intellectual Property Law Office, P.C.

### (57) ABSTRACT

An object of the present invention is to provide a highly reliable power supply device which can withstand long-term use. Another object of the present invention is to provide a power supply device with reduced power consumption. The power supply device includes a cell including an antenna and a switch and performing position detection operation and power feeding operation; a high-frequency wave supply circuit; a switch control circuit; and a potential detecting circuit. One electrode of the antenna is connected to the high-frequency wave supply circuit through the switch, and the other thereof is connected to the potential detecting circuit. By the position detection operation, whether there is a power receiving device which gets close to a cell or not is detected. Only when the power receiving device is detected, power is supplied by the power feeding operation.

### 20 Claims, 9 Drawing Sheets

|     |               | 500<br>           |          |                 |

|-----|---------------|-------------------|----------|-----------------|

|     | 506           |                   | 508      |                 |

|     | BS-1 BP-1 BS- | 2 BS-3            | BS-4     |                 |

| 2   |               | BP-2 BS-3         |          | BP-4<br>507 502 |

| 212 |               | ┝╋╦╩┙ᡚ<br>┠┎╼╍╼┑╢ | ┍╫╌╌┨    | ╔╙╩┪            |

|     | ₩S-2          |                   |          | <b>B</b> D      |

|     |               | ÷.                |          | <b>B</b>        |

|     |               |                   |          |                 |

|     | WS-4 TL-4     | <u></u>           | <u> </u> | 501<br>501      |

|     | SL-1          | SL-2<br>510       | SL-3     | SL-4            |

| ĺ   |               |                   |          |                 |

## (56) **References Cited**

## U.S. PATENT DOCUMENTS

| 6,929,990                    | B2       | 8/2005            | Momose et al.                |

|------------------------------|----------|-------------------|------------------------------|

| 7,049,190                    | B2       | 5/2006            | Takeda et al.                |

| 7,061,014                    | B2       | 6/2006            | Hosono et al.                |

| 7,064,346                    | B2       | 6/2006            | Kawasaki et al.              |

| 7,105,868                    | B2       | 9/2006            | Nause et al.                 |

| 7,112,952                    | B2       | 9/2006            | Arai et al.                  |

| 7,211,825                    | B2       | 5/2007            | Shih et al                   |

| 7,233,137                    | B2       | 6/2007            | Nakamura et al.              |

| 7,282,752                    | B2       | 10/2007           | Momose et al.                |

| 7,282,782                    | B2       | 10/2007           | Hoffman et al.               |

| 7,297,977                    | B2       | 11/2007           | Hoffman et al.               |

| 7,323,356                    | B2       | 1/2008            | Hosono et al.                |

| 7,385,224                    |          | 6/2008            | Ishii et al.                 |

| 7,402,506                    | B2       | 7/2008            | Levy et al.<br>Endo et al.   |

| 7,411,209                    | B2<br>B2 | 8/2008<br>11/2008 | Saito et al.                 |

| 7,453,065<br>7,453,087       | B2<br>B2 | 11/2008           | Iwasaki                      |

| 7,462,862                    | B2       | 12/2008           | Hoffman et al.               |

| 7,468,304                    |          | 12/2008           | Kaji et al.                  |

| 7,501,293                    |          | 3/2009            | Ito et al.                   |

| 7,674,650                    |          | 3/2010            | Akimoto et al.               |

| 7,683,429                    |          | 3/2010            | Yamaguchi et al.             |

| 7,732,819                    | B2       | 6/2010            | Akimoto et al.               |

| 7,923,870                    | B2       | 4/2011            | Jin                          |

| 7,948,208                    | B2       | 5/2011            | Partovi et al.               |

| 7,952,322                    | B2       | 5/2011            | Partovi et al.               |

| 8,067,775                    | B2 *     | 11/2011           | Miyairi et al 257/72         |

| 8,115,201                    | B2       | 2/2012            | Yamazaki et al.              |

| 8,169,185                    | B2       | 5/2012            | Partovi et al.               |

| 8,432,502                    | B2       | 4/2013            | Yamazaki et al.              |

| 8,492,760                    | B2       | 7/2013            | Yamazaki et al.              |

| 2001/0046027                 | Al       | 11/2001           | Tai et al.                   |

| 2002/0056838<br>2002/0132454 | Al<br>Al | 5/2002<br>9/2002  | Ogawa<br>Ohtsu et al.        |

| 2003/0189401                 | Al       | 10/2003           | Kido et al.                  |

| 2003/0218222                 | Al       | 11/2003           | Wager et al.                 |

| 2004/0038446                 | Al       | 2/2004            | Takeda et al.                |

| 2004/0127038                 | Al       | 7/2004            | Carcia et al.                |

| 2005/0017302                 | A1       | 1/2005            | Hoffman                      |

| 2005/0199959                 | A1       | 9/2005            | Chiang et al.                |

| 2006/0035452                 | A1       | 2/2006            | Carcia et al.                |

| 2006/0043377                 | A1       | 3/2006            | Hoffman et al.               |

| 2006/0091793                 | A1       | 5/2006            | Baude et al.                 |

| 2006/0108529                 | Al       | 5/2006            | Saito et al.                 |

| 2006/0108636                 | Al       | 5/2006            | Sano et al.                  |

| 2006/0110867                 | Al       | 5/2006            | Yabuta et al.                |

| 2006/0113536                 | Al<br>Al | 6/2006<br>6/2006  | Kumomi et al.<br>Sano et al. |

| 2006/0113539<br>2006/0113549 | A1       | 6/2006            | Den et al.                   |

| 2006/0113565                 | Al       | 6/2006            | Abe et al.                   |

| 2006/0169973                 | Al       | 8/2006            | Isa et al.                   |

| 2006/0170111                 | Al       | 8/2006            | Isa et al.                   |

| 2006/0197092                 | Al       | 9/2006            | Hoffman et al.               |

| 2006/0208977                 | A1       | 9/2006            | Kimura                       |

| 2006/0228974                 | A1       | 10/2006           | Thelss et al.                |

| 2006/0231882                 | A1       | 10/2006           | Kim et al.                   |

| 2006/0238135                 | A1       | 10/2006           | Kimura                       |

| 2006/0244107                 | A1       | 11/2006           | Sugihara et al.              |

| 2006/0284171                 | Al       | 12/2006           | Levy et al.                  |

| 2006/0284172                 | Al       | 12/2006           | Ishii                        |

| 2006/0292777                 | Al<br>Al | 12/2006           | Dunbar<br>Shin at al         |

| 2007/0024187<br>2007/0046191 | A1<br>A1 | 2/2007<br>3/2007  | Shin et al.                  |

|                              |          |                   | Saito                        |

| 2007/0052025 2007/0054507    | Al<br>Al | 3/2007<br>3/2007  | Yabuta<br>Kaji et al.        |

| 2007/0090365                 | Al       | 4/2007            | Hayashi et al.               |

| 2007/0108446                 | Al       | 5/2007            | Akimoto                      |

| 2007/0152217                 | Al       | 7/2007            | Lai et al.                   |

| 2007/0172591                 | Al       | 7/2007            | Seo et al.                   |

| 2007/0187678                 | A1       | 8/2007            | Hirao et al.                 |

| 2007/0187760                 | Al       | 8/2007            | Furuta et al.                |

| 2007/0194379                 | A1       | 8/2007            | Hosono et al.                |

| 2007/0252928                 | A1       | 11/2007           | Ito et al.                   |

| 2007/0272922                 | A1       | 11/2007           | Kim et al.                   |

| 2007/0287296                 | A1       | 12/2007           | Chang                        |

|                              |          |                   | -                            |

| 2008/0006877 | A1  | 1/2008  | Mardilovich et al.     |

|--------------|-----|---------|------------------------|

| 2008/0038882 | A1  | 2/2008  | Takechi et al.         |

| 2008/0038929 | A1  | 2/2008  | Chang                  |

| 2008/0048250 | A1  | 2/2008  | Momose et al.          |

| 2008/0050595 | A1  | 2/2008  | Nakagawara et al.      |

| 2008/0073653 | A1  | 3/2008  | Iwasaki                |

| 2008/0083950 | A1  | 4/2008  | Pan et al.             |

| 2008/0106191 | A1  | 5/2008  | Kawase                 |

| 2008/0128689 | A1  | 6/2008  | Lee et al.             |

| 2008/0129195 | A1  | 6/2008  | Ishizaki et al.        |

| 2008/0166834 | A1  | 7/2008  | Kim et al.             |

| 2008/0182358 | A1  | 7/2008  | Cowdery-Corvan et al.  |

| 2008/0224133 | A1  | 9/2008  | Park et al.            |

| 2008/0231120 | A1  | 9/2008  | Jin                    |

| 2008/0254569 | A1  | 10/2008 | Hoffman et al.         |

| 2008/0258139 | A1  | 10/2008 | Ito et al.             |

| 2008/0258140 | A1  | 10/2008 | Lee et al.             |

| 2008/0258141 | A1  | 10/2008 | Park et al.            |

| 2008/0258143 | A1  | 10/2008 | Kim et al.             |

| 2008/0296568 | A1  | 12/2008 | Ryu et al.             |

| 2009/0068773 | A1  | 3/2009  | Lai et al.             |

| 2009/0073325 | A1  | 3/2009  | Kuwabara et al.        |

| 2009/0114910 | A1  | 5/2009  | Chang                  |

| 2009/0134399 | A1  | 5/2009  | Sakakura et al.        |

| 2009/0152506 | A1  | 6/2009  | Umeda et al.           |

| 2009/0152541 | A1  | 6/2009  | Maekawa et al.         |

| 2009/0278122 | A1  | 11/2009 | Hosono et al.          |

| 2009/0280600 | A1  | 11/2009 | Hosono et al.          |

| 2010/0052430 | A1* | 3/2010  | Takaishi et al 307/104 |

| 2010/0065844 | A1  | 3/2010  | Tokunaga               |

| 2010/0092800 | A1  | 4/2010  | Itagaki et al.         |

| 2010/0109002 | A1  | 5/2010  | Itagaki et al.         |

| 2011/0050164 | A1  | 3/2011  | Partovi et al.         |

| 2011/0089857 | A1  | 4/2011  | Diederiks              |

| 2011/0176263 | A1  | 7/2011  | Yamazaki et al.        |

| 2011/0187688 | A1  | 8/2011  | Yamazaki et al.        |

| 2011/0221385 | A1  | 9/2011  | Partovi et al.         |

| 2012/0126745 | A1  | 5/2012  | Partovi et al.         |

| 2013/0175875 | A1* | 7/2013  | Kurs et al 307/104     |

|              |     |         |                        |

## FOREIGN PATENT DOCUMENTS

| EP          | 2226847 A      | 9/2010  |

|-------------|----------------|---------|

| JP          | 60-198861 A    | 10/1985 |

| $_{\rm JP}$ | 63-210022 A    | 8/1988  |

| $_{\rm JP}$ | 63-210023 A    | 8/1988  |

| JP          | 63-210024 A    | 8/1988  |

| JP          | 63-215519 A    | 9/1988  |

| JP          | 63-239117 A    | 10/1988 |

| JP          | 63-265818 A    | 11/1988 |

| JP          | 05-251705 A    | 9/1993  |

| JP          | 08-264794 A    | 10/1996 |

| JP          | 11-505377      | 5/1999  |

| JP          | 2000-044236 A  | 2/2000  |

| JP          | 2000-150900 A  | 5/2000  |

| JP          | 2000-208430 A  | 7/2000  |

| JP          | 2002-076356 A  | 3/2002  |

| JP          | 2002-289859 A  | 10/2002 |

| JP          | 2003-086000 A  | 3/2003  |

| JP          | 2003-086808 A  | 3/2003  |

| JP          | 2004-103957 A  | 4/2004  |

| JP          | 2004-273614 A  | 9/2004  |

| JP          | 2004-273732 A  | 9/2004  |

| JP          | 2005-110421 A  | 4/2005  |

| JP          | 2005-217436 A  | 8/2005  |

| JP          | 2008-236916 A  | 10/2008 |

| JP          | 2008-252113 A  | 10/2008 |

| JP          | 2009-271846 A  | 11/2009 |

| JP          | 2010-062229 A  | 3/2010  |

| JP          | 2010-062546 A  | 3/2010  |

| $_{\rm JP}$ | 2010-527226    | 8/2010  |

| TW          | 201007529      | 2/2010  |

| WO          | WO-2004/114391 | 12/2004 |

|             |                |         |

### (56) **References Cited**

### FOREIGN PATENT DOCUMENTS

| WO | WO-2008/032746 | 3/2008  |

|----|----------------|---------|

| WO | WO-2009/136619 | 11/2009 |

| WO | WO-2009/150573 | 12/2009 |

### OTHER PUBLICATIONS

Written Opinion (Application No. PCT/JP2011/057514) Dated May 10, 2011.

Fortunato.E et al., "Wide-Bandgap High-Mobility ZnO Thin-Film Transistors Produced at Room Temperature,", Appl. Phys. Lett. (Applied Physics Letters), Sep. 27, 2004, vol. 85, No. 13, pp. 2541-2543.

Dembo.H et al., "RFCPUS on Glass and Plastic Substrates Fabricated by TFT Transfer Technology,". IEDM 05: Technical Digest of International Electron Devices Meeting, Dec. 5, 2005, pp. 1067-1069.

Ikeda.T et al., "Full-Functional System Liquid Crystal Display Using Cg-Silicon Technology,", SID Digest '04 : SID International Symposium Digest of Technical Papers, 2004, vol. 35, pp. 860-863.

Nomura.K et al., "Room-Temperature Fabrication of Transparent Flexible Thin-Film Transistors Using Amorphous Oxide Semiconductors,", Nature, Nov. 25, 2004, vol. 432, pp. 488-492.

Park.J et al., "Improvements in the Device Characteristics of Amorphous Indium Gallium Zinc Oxide Thin-Film Transistors by Ar Plasma Treatment,", Appl. Phys. Lett. (Applied Physics Letters), Jun. 26, 2007, vol. 90, No. 26, pp. 262106-1-262106-3.

Takahashi.M et al., "Theoretical Analysis of IGZO Transparent Amorphous Oxide Semiconductor,", IDW '08 : Proceedings of the 15th International Display Workshops, Dec. 3, 2008, pp. 1637-1640. Hayashi.R et al., "42.1: Invited Paper: Improved Amorphous In—Ga—Zn—O TFTs,", SID Digest '08 : SID International Symposium Digest of Technical Papers, May 20, 2008, vol. 39, pp. 621-624.

Prins.M et al., "A Ferroelectric Transparent Thin-Film Transistor,", Appl. Phys. Lett. (Applied Physics Letters), Jun. 17, 1996, vol. 68, No. 25, pp. 3650-3652.

Nakamura.M et al., "The phase relations in the In2O3—Ga2ZnO4— ZnO system at 1350° C.,", Journal of Solid State Chemistry, Aug. 1, 1991, vol. 93, No. 2, pp. 298-315.

Kimizuka.N et al., "Syntheses and Single-Crystal Data of Homologous Compounds,  $In_2O_3(ZnO)_m$  (m=3, 4, and 5),  $InGaO_3(ZnO)_3$ , and  $Ga_2O_3(ZnO)_m$  (m=7, 8, 9, and 16) in the  $In_2O_3$ —ZnGa $_2O_4$ —ZnO System,", Journal of Solid State Chemistry, Apr. 1, 1995, vol. 116, No. 1, pp. 170-178.

Nomura.K et al., "Thin-Film Transistor Fabricated in Single-Crystalline Transparent Oxide Semicondutor,", Science, May 23, 2003, vol. 300, No. 5623, pp. 1269-1272.

Masuda.S et al., "Transparent thin film transistors using ZnO as an active channel layer and their electrical properties,", J. Appl. Phys. (Journal of Applied Physics), Feb. 1, 2003

Asakuma.N et al., "Crystallization and Reduction of Sol-Gel-Derived Zinc Oxide Films by Irradiation With Ultraviolet Lamp,", Journal of Sol-Gel Science and Technology, 2003, vol. 26, pp. 181-184. Osada.T et al., "15.2: Development of Driver-Integrated Panel using Amorphous In—Ga—Zn—Oxide TFT,", SID Digest '09 : SID International Symposium Digest of Technical Papers, May 31, 2009, pp. 184-187.

Nomura.K et al., "Carrier transport in transparent oxide semiconductor with intrinsic structural randomness probed using single-crystalline  $InGaO_6(ZnO)_5$  films,", Appl. Phys. Lett.(Applied Physics Letters), Sep. 13, 2004, vol. 85, No. 11, pp. 1993-1995.

Li.C et al., "Modulated Structures of Homologous Compounds InMO<sub>3</sub>(ZnO)m (M=In,Ga; m=Integer) Described by Four-Dimensional Superspace Group,", Journal of Solid State Chemistry, 1998, vol. 139, pp. 347-355.

Son.K et al., "42.4L: Late-News Paper: 4 Inch QVGA AMOLED Driven by the Threshold Voltage Controlled Amorphous GIZO  $(Ga_2O_3 - In_2O_3 - ZnO)$  TFT,", SID Digest '08 : SID International Symposium Digest of Technical Papers, May 20, 2008, vol. 39, pp. 633-636.

Lee.J et al., "World's Largest (15-Inch) XGA AMLCD Panel Using IGZO Oxide TFT,", SID Digest '08 : SID International Symposium Digest of Technical Papers, May 20, 2008, vol. 39, pp. 625-628.

Nowatari.H et al., "60.2: Intermediate Connector With Suppressed Voltage Loss for White Tandem OLEDs,", SID Digest '09 : SID International Symposium Digest of Technical Papers, May 31, 2009, vol. 40, pp. 899-902.

Kanno.H et al., "White Stacked Electrophosphorecent Organic Light-Emitting Devices Employing MoO3 as a Charge-Generation Layer,", Adv. Mater. (Advanced Materials), 2006, vol. 18, No. 3, pp. 339-342.

Tsuda.K et al., "Ultra Low Power Consumption Technologies for Mobile TFT-LCDs,", IDW '02 : Proceedings of the 9th International Display Workshops, Dec. 4, 2002, pp. 295-298.

Van de Walle.C, "Hydrogen as a Cause of Doping in Zinc Oxide,", Phys. Rev. Lett. (Physical Review Letters), Jul. 31, 2000, vol. 85, No. 5, pp. 1012-1015.

Fung.T et al., "2-D Numerical Simulation of High Performance Amorphous In—Ga—Zn—O TFTs for Flat Panel Displays,", AM-FPD '08 Digest of Technical Papers, Jul. 2, 2008, pp. 251-252, The Japan Society of Applied Physics.

Jeong J et al., "3.1: Distinguished Paper: 12.1-Inch WXGA AMOLED Display Driven by Indium—Gallium—Zinc Oxide TFTs Array,", SID Digest '08 : SID International Symposium Digest of Technical Papers, May 20, 2008, vol. 39, No. 1, pp. 1-4.

Park.J et al., "High performance amorphous oxide thin film transistors with self-aligned top-gate structure,", IEDM 09: Technical Digest of International Electron Devices Meeting, Dec. 7, 2009, pp. 191-194.

Kurokawa.Y et al., "UHF RFCPUS on Flexible and Glass Substrates for Secure RFID Systems,", Journal of Solid-State Circuits, 2008, vol. 43, No. 1, pp. 292-299.

Ohara.H et al., "Amorphous In—Ga—Zn—Oxide TFTs with Suppressed Variation for 4.0 inch QVGA AMOLED Display,", AM-FPD '09 Digest of Technical Papers, Jul. 1, 2009, pp. 227-230, The Japan Society of Applied Physics.

Coates.D et al., "Optical Studies of the Amorphous Liquid-Cholesteric Liquid Crystal Transition:The "Blue Phase",", Physics Letters, Sep. 10, 1973, vol. 45A, No. 2, pp. 115-116.

Cho.D et al., "21.2:Al and Sn-Doped Zinc Indium Oxide Thin Film Transistors for AMOLED Back Plane,", SID Digest '09 : SID International Symposium Digest of Technical Papers, May 31, 2009, pp. 280-283.

Lee.M et al., "15.4:Excellent Performance of Indium—Oxide-Based Thin-Film Transistors by DC Sputtering,", SID Digest '09 : SID International Symposium Digest of Technical Papers, May 31, 2009, pp. 191-193.

Jin.Det al., "65.2:Distinguished Paper:World-Largest (6.5") Flexible Full Color Top Emission AMOLED Display on Plastic Film and its Bending Properties,", SID Digest '09 : SID International Symposium Digest of Technical Papers, May 31, 2009, pp. 983-985.

Sakata.J et al., "Development of 4.0-In. AMOLED Display With Driver Circuit Using Amorphous In—Ga—Zn—Oxide TFTs,", IDW '09 : Proceedings of the 16th International Display Workshops, 2009, pp. 689-692.

Park.J et al., "Amorphous Indium—Gallium—Zinc Oxide TFTs and Their Application for Large Size AMOLED,", AM-FPD '08 Digest of Technical Papers, Jul. 2, 2008, pp. 275-278.

Park.S et al., "Challenge to Future Displays: Transparent AM-OLED Driven by PEALD Grown ZnO TFT,", IMID '07 Digest, 2007, pp. 1249-1252.

Godo.H et al., "Temperature Dependence of Characteristics and Electronic Structure for Amorphous In—Ga—Zn—Oxide TFT,", AM-FPD '09 Digest of Technical Papers, Jul. 1, 2009, pp. 41-44.

Osada.T et al., "Development of Driver-Integrated Panel Using Amorphous In—Ga—Zn—Oxide TFT,", AM-FPD '09 Digest of Technical Papers, Jul. 1, 2009, pp. 33-36.

Hirao.T et al., "Novel Top-Gate Zinc Oxide Thin-Film Transistors (ZnO TFTs) for AMLCDs,", Journal of the SID, 2007, vol. 15, No. 1, pp. 17-22.

### (56) **References Cited**

### OTHER PUBLICATIONS

Hosono.H, "68.3:Invited Paper:Transparent Amorphous Oxide Semiconductors for High Performance TFT,", SID Digest '07 : SID International Symposium Digest of Technical Papers, 2007, vol. 38, pp. 1830-1833.

Godo.H et al., "P-9:Numerical Analysis on Temperature Dependence of Characteristics of Amorphous In—Ga—Zn—Oxide TFT,", SID Digest '09 : SID International Symposium Digest of Technical Papers, May 31, 2009, pp. 1110-1112.

Ohara.H et al., "21.3:4.0 In. QVGA AMOLED Display Using In—Ga—Zn—Oxide TFTs With a Novel Passivation Layer,", SID Digest '09 : SID International Symposium Digest of Technical Papers, May 31, 2009, pp. 284-287.

Miyasaka.M, "SUFTLA Flexible Microelectronics on Their Way to Business,", SID Digest '07 : SID International Symposium Digest of Technical Papers, 2007, vol. 38, pp. 1673-1676.

Chern.H et al., "An Analytical Model for the Above-Threshold Characteristics of Polysilicon Thin-Film Transistors,", IEEE Transactions on Electron Devices, Jul. 1, 1995, vol. 42, No. 7, pp. 1240-1246.

Kikuchi.H et al., "39.1:Invited Paper:Optically Isotropic Nano-

Structured Liquid Crystal Composites for Display Applications,", SID Digest '09 : SID International Symposium Digest of Technical Papers, May 31, 2009, pp. 578-581.

Asaoka.Y et al., "29.1:Polarizer-Free Reflective LCD Combined With Ultra Low-Power Driving Technology,", SID Digest '09 : SID International Symposium Digest of Technical Papers, May 31, 2009, pp. 395-398.

Lee.H et al., "Current Status of, Challenges to, and Perspective View of AM-OLED,", IDW '06 : Proceedings of the 13th International Display Workshops, Dec. 7, 2006, pp. 663-666.

Kikuchi.H et al., "62.2:Invited Paper:Fast Electro-Optical Switching in Polymer-Stabilized Liquid Crystalline Blue Phases for Display Application,", SID Digest '07 : SID International Symposium Digest of Technical Papers, 2007, vol. 38, pp. 1737-1740.

Nakamura.M, "Synthesis of Homologous Compound with New Long-Period Structure,", NIRIM Newsletter, Mar. 1, 1995, vol. 150, pp. 1-4.

Kikuchi.H et al., "Polymer-Stabilized Liquid Crystal Blue Phases,", Nature Materials, Sep. 2, 2002, vol. 1, pp. 64-68.

Kimizuka.N et al., "Spinel, YbFe<sub>2</sub>O<sub>4</sub>, and Yb<sub>2</sub>Fe<sub>3</sub>O<sub>7</sub> Types of Structures for Compounds in the  $In_2O_3$  and  $Sc_2O_3$ —BO Systems [A; Fe, Ga, or Al; B: Mg, Mn, Fe, Ni, Cu, or Zn] at Temperatures Over 1000° C.,", Journal of Solid State Chemistry, 1985, vol. 60, pp. 382-384.

Kitzerow.H et al., "Observation of Blue Phases in Chiral Networks,", Liquid Crystals, 1993, vol. 14, No. 3, pp. 911-916.

Costello.M et al., "Electron Microscopy of a Cholesteric Liquid Crystal and Its Blue Phase,", Phys. Rev. A (Physical Review. A), May 1, 1984, vol. 29, No. 5, pp. 2957-2959.

Meiboom.S et al., "Theory of the Blue Phase of Cholesteric Liquid Crystals,", Phys. Rev. Lett. (Physical Review Letters), May 4, 1981, vol. 46, No. 18, pp. 1216-1219.

Park.Sang-Hee et al., "42.3: Transparent ZnO Thin Film Transistor for the Application of High Aperture Ratio Bottom Emission AM-OLED Display,", SID Digest '08 : SID International Symposium Digest of Technical Papers, May 20, 2008, vol. 39, pp. 629-632.

Orita.M et al., "Mechanism of Electrical Conductivity of Transparent InGaZnO<sub>4</sub>,", Phys. Rev. B (Physical Review. B), Jan. 15, 2000, vol. 61, No. 3, pp. 1811-1816.

Nomura.K et al., "Amorphous Oxide Semiconductors for High-Performance Flexible Thin-Film Transistors,", Jpn. J. Appl. Phys. (Japanese Journal of Applied Physics), 2006, vol. 45, No. 5B, pp. 4303-4308.

Janotti.A et al., "Native Point Defects in ZnO,", Phys. Rev. B (Physical Review. B), Oct. 4, 2007, vol. 76, No. 16, pp. 165202-1-165202-22.

Park.J et al., "Electronic Transport Properties of Amorphous Indium—Gallium—Zinc Oxide Semiconductor Upon Exposure to Water,", Appl. Phys. Lett. (Applied Physics Letters), 2008, vol. 92, pp. 072104-1-072104-3.

Hsieh.H et al., "P-29: Modeling of Amorphous Oxide Semiconductor Thin Film Transistors and Subgap Density of States,", SID Digest '08: SID International Symposium Digest of Technical Papers, 2008, vol. 39, pp. 1277-1280.

Janotti.A et al., "Oxygen Vacancies in ZnO,", Appl. Phys. Lett. (Applied Physics Letters), 2005, vol. 87, pp. 122102-1-122102-3.

Oba.F et al., "Defect energetics in ZnO: A hybrid Hartree-Fock density functional study,", Phys. Rev. B (Physical Review. B), 2008, vol. 77, pp. 245202-1-245202-6.

Orita.M et al., "Amorphous transparent conductive oxide  $InGaO_3(ZnO)_m$  (m<4):a Zn 4s conductor,", Philosophical Magazine, 2001, vol. 81, No. 5, pp. 501-515.

Hosono.H et al., "Working hypothesis to explore novel wide band gap electrically conducting amorphous oxides and examples,", J. Non-Cryst. Solids (Journal of Non-Crystalline Solids), 1996, vol. 198-200, pp. 165-169.

Mo.Y et al., "Amorphous Oxide TFT Backplanes for Large Size AMOLED Displays,", IDW '08 : Proceedings of the 6th International Display Workshops, Dec. 3, 2008, pp. 581-584.

Kim.S et al., "High-Performance oxide thin film transistors passivated by various gas plasmas,", 214th ECS Meeting, 2008, No. 2317, ECS.

Clark.S et al., "First Principles Methods Using CASTEP,", Zeitschrift fur Kristallographie, 2005, vol. 220, pp. 567-570.

Lany.S et al., "Dopability, Intrinsic Conductivity, and Nonstoichiometry of Transparent Conducting Oxides,", Phys. Rev. Letts. (Physical Review Letters), Jan. 26, 2007, vol. 98, pp. 045501-1-045501-4.

Takamiya.M et al., "Wireless Power Transmission Sheet with Organic FETs and Plastic MEMS Switches,", IDW '07: Proceedings of the 14th International Display Workshops, Dec. 5, 2007, pp. 95-98. Sekitani.T et al., "A large-area flexible wireless power transmission sheet using printed plastic MEMS switches and organic field-effect transistors,", IEDM 06: Technical Digest of International Electron Devices Meeting, 2006, pp. 30-33.

Takamiya.M et al., "20.4 Design Solutions for a Multi-Object Wireless Power Transmission Sheet Based on Plastic Switches,", ISSCC 2007 (Digest of Technical Papers. IEEE International Solid-State Circuits Conference), Feb. 11, 2007, pp. 362-363, 609 (3 pages).

Park.J at al., "Dry etching of ZnO films and plasma-induced damage to optical properties,", J. Vac. Sci. Technol. B (Journal of Vacuum Science & Technology B), Mar. 1, 2003, vol. 21, No. 2, pp. 800-803. Oh.M et al., "Improving the Gate Stability of ZnO Thin-Film Transistors With Aluminum Oxide Dielectric Layers,", J. Electrochem. Soc. (Journal of the Electrochemical Society), 2008, vol. 155, No. 12, pp. H1009-H1014.

Ueno.K et al., "Field-Effect Transistor on SrTiO<sub>3</sub> With Sputtered Al<sub>2</sub>O<sub>3</sub> Gate Insulator,", Appl. Phys. Lett. (Applied Physics Letters), Sep. 1, 2003, vol. 83, No. 9, pp. 1755-1757.

Taiwanese Office Action (Application No. 100110788) Dated Aug. 12, 2015.

\* cited by examiner

# FIG. 2

FIG. 3B

FIG. 4

FIG. 5

FIG. 6A

# FIG. 7

FIG. 8A

FIG. 8C

FIG. 8D

FIG. 8E

15

### POWER SUPPLY DEVICE AND DRIVING METHOD THEREOF

### TECHNICAL FIELD

The present invention relates to a power supply device. In particular, the present invention relates to a power supply device which supplies power by a radio signal.

In this specification, a semiconductor device means all types of devices which can function by utilizing semiconductor characteristics, and an imaging device, a display device, an electro-optical device, a power supply device, a semiconductor circuit, an electronic device, and the like are all semiconductor devices.

### BACKGROUND ART

In recent years, with the development of information communication technology, the realization of a ubiquitous society <sup>20</sup> is proposed in which free communication of information and a variety of services can be achieved by connecting a variety of electronic devices to a computer network. The word "ubiquitous" comes from the Latin meaning "existing or being everywhere" (being omnipresent) and means that the processing of information using computers is naturally widespread throughout a living environment through electronic devices without any awareness of computers at anytime and anywhere.

In order to make an electronic device operate, power needs <sup>30</sup> to be supplied to the electronic device (hereinafter, also referred to as power feeding). Power is supplied to a portable electronic device typified by a mobile phone and the like by a built-in battery. The battery is charged in the following manner: the electronic device is set in a battery charger and power <sup>35</sup> is received from a commercial power supply distributed to each house. In addition, a contact needs to be provided to connect the electronic device and the battery charger; however, a non-contact power supply method utilizing electromagnetic induction phenomenon which does not need a con-<sup>40</sup> tact is known because a malfunction due to a contact defect is prevented, a design to which waterproof function is imparted is easily made, and the like.

If positioned alignment of a power feeding side and a power receiving side is not doned accurately in charging by <sup>45</sup> electromagnetic induction, efficient power supply has been difficult; however, in recent years, a sheet-like power supply device has been known in which the power supply efficiency is improved in such a manner that a plurality of power feeding coils are arranged to have a sheet-like shape and power is <sup>50</sup> supplied from only a power feeding coil over which an electronic device which receives power is placed (Non-Patent Document 1).

By supplying power using a radio signal made by electromagnetic induction, the electronic device can be made to <sup>55</sup> operate without consideration of a power supply cord, a position of an outlet, and the like. A power feeding coil functions as an antenna for supplying power using a radio signal.

### REFERENCE

#### Non-Patent Document

[Non-Patent Document 1] M. Takamiya, T. Sekitani, Y. Miyamoto, Y. Noguchi, H. Kawaguchi, T. Someya, and T. Sakurai, "Wireless Power Transmission Sheet with Organic FETs and Plastic MEMS Switches", IDW, 2007, pp. 95-98

### DISCLOSURE OF INVENTION

The sheet-like power supply device including a plurality of power feeding coils (power feeding antennas) described above includes a power feeding switch for supplying a highfrequency power (hereinafter, also referred to as a high-frequency wave) to a specific power feeding coil; and a position detecting switch for detecting a power feeding coil over which an electronic device which receives power is placed using the high-frequency wave. A mechanical switch manufactured using a micro electro mechanical system (MEMS) technology is used as the power feeding switch because high voltage and a large amount of current need to flow; however, there are problems in that it has a low operation speed and

cannot withstand long-term use because of its poor durability. The position detecting switch requires higher speed operation than the power feeding switch and is easily manufactured by a printing method typified by an ink jet method; therefore, an organic field effect transistor (OFET) is used. However, an OFET has a high drive voltage of several tens of voltage and thus consumes much power in position detection operation. The position detecting switch requires reduction in drive voltage and higher speed operation.

Since the power feeding switch and the position detecting switch satisfy different required specifications, they need to be formed separately; thus, manufacturing steps become complicated.

Since high-frequency waves with different frequencies are used as a high-frequency wave for supplying power and a high-frequency wave for detecting a position, a high-frequency wave supply circuit for supplying power and a highfrequency wave supply circuit for detecting a position need to be provided separately, whereby a circuit configuration becomes complicated. Therefore, the number of components is increased, and improvement in productivity and cost reduction are difficult to achieve.

An object of one embodiment of the present invention is to provide a highly reliable power supply device which can withstand long-term use.

Another object of one embodiment of the present invention is to provide a power supply device with high productivity.

Another object of one embodiment of the present invention is to provide a power supply device with reduced power consumption.

Each embodiment of the invention disclosed in this specification achieves at least one of the above objects.

One embodiment of the present invention is a power supply device which includes an antenna, a switch including an oxide semiconductor, and a high-frequency wave supply circuit. The antenna and the high-frequency wave supply circuit are connected to each other through the switch including an oxide semiconductor.

One embodiment of the present invention is a power supply device which includes a plurality of cells arranged in a matrix, a high-frequency wave supply circuit, a switch control circuit, and a potential detecting circuit. The cell includes an antenna and a transistor including an oxide semiconductor in a channel formation region. One electrode (terminal) of the antenna is connected to the high-frequency wave supply circuit through the transistor including an oxide semiconductor in the channel formation region. The other electrode (terminal) of the antenna is connected to the potential detecting circuit.

By position detection operation, a cell over which a power receiving device is placed is detected from the plurality of cells arranged in a matrix, and by power feeding operation,

60

power is transmitted to only the cell over which the power receiving device is placed, so that efficient power transmission can be realized.

For high-frequency waves used for the position detection operation and the power feeding operation, high-frequency waves with the same frequency can be used. The position detection operation can be performed with power smaller than power used for the power feeding operation.

The position detection operation and the power feeding operation are performed alternately. A power feeding operation period is preferably longer than a position detection operation period.

Another embodiment of the present invention is a power supply device which includes a plurality of power feeding cells arranged in a matrix, a first high-frequency wave supply <sup>15</sup> circuit, a second high-frequency wave supply circuit, a first switch control circuit, a second switch control circuit, and a potential detecting circuit. The power feeding cell includes an antenna, a first switch, and a second switch. One electrode (terminal) of the antenna is connected to the first high-frequency wave supply circuit through the first switch and to the second high-frequency wave supply circuit through the second switch. The other electrode (terminal) of the antenna is connected to the potential detecting circuit.

A transistor including an oxide semiconductor in a channel <sup>25</sup> formation region is used as one or both of the first switch and the second switch.

The first high-frequency wave supply circuit supplies a high-frequency wave for power feeding operation, and the second high-frequency wave supply circuit supplies a high-<sup>30</sup> frequency wave for position detection operation.

When high-frequency waves with different frequencies are used in the power feeding operation and the position detection operation, the power feeding operation and the position detection operation can be performed at the same time. In <sup>35</sup> addition, the frequency of the high-frequency wave for the power feeding operation is preferably higher than the frequency of the high-frequency wave for the position detection operation.

A highly reliable power supply device which can withstand <sup>40</sup> fication and the like. long-term use can be provided. A power supply device with reduced power consumption can be provided.

### BRIEF DESCRIPTION OF DRAWINGS

In the accompanying drawings:

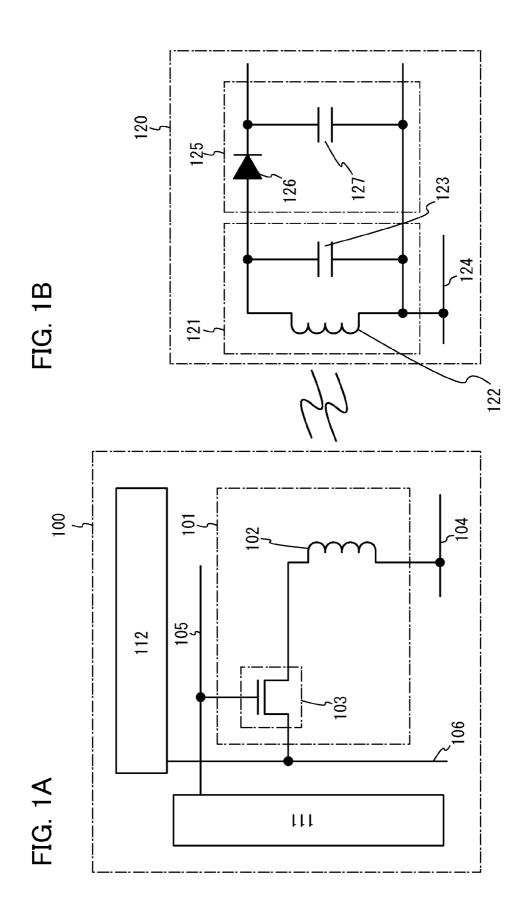

FIGS. 1A and 1B illustrate a power supply device and a power receiving device;

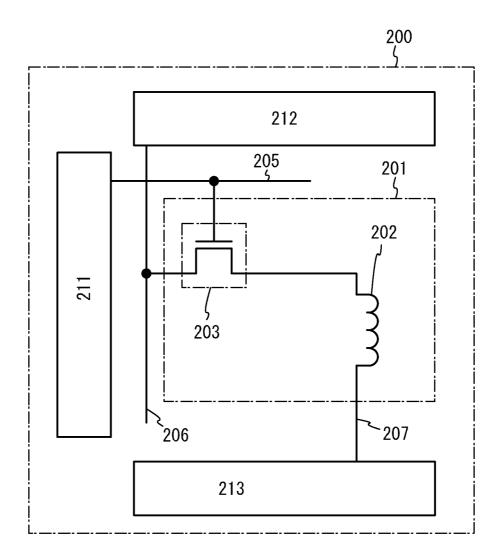

FIG. 2 illustrates a position detecting device;

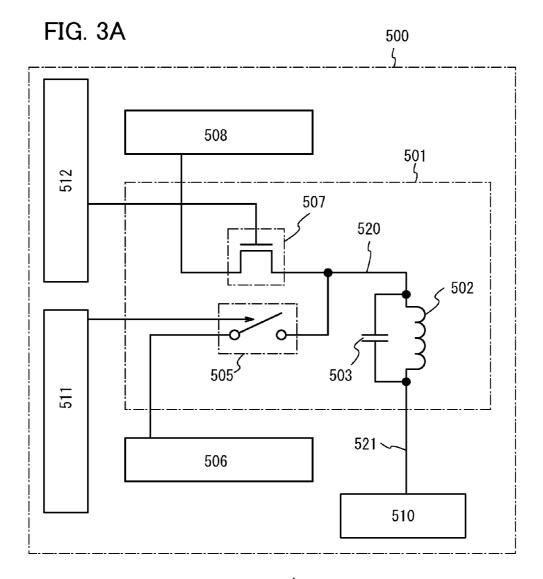

FIGS. **3**A and **3**B illustrate a conventional power supply <sup>50</sup> device;

FIG. 4 illustrates a conventional power supply device;

FIG. **5** illustrates a power supply device;

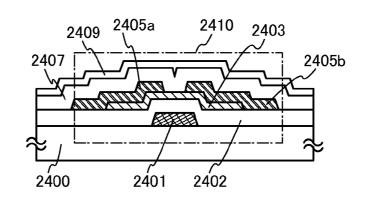

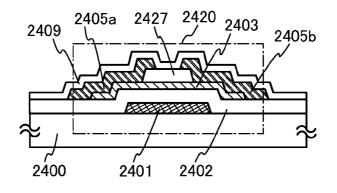

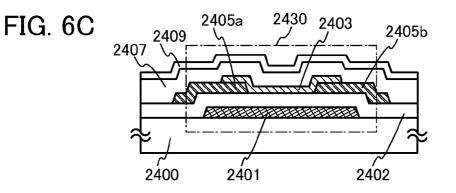

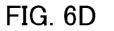

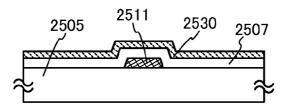

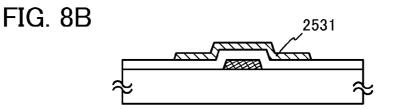

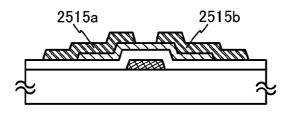

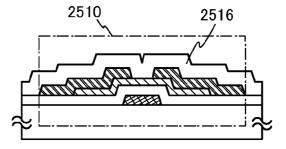

FIGS. **6**A to **6**D each illustrate an example of a structure of a transistor; 55

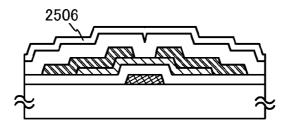

FIG. **7** illustrates an example of a structure of a transistor; FIGS. **8**A to **8**E illustrate a manufacturing process of a transistor; and

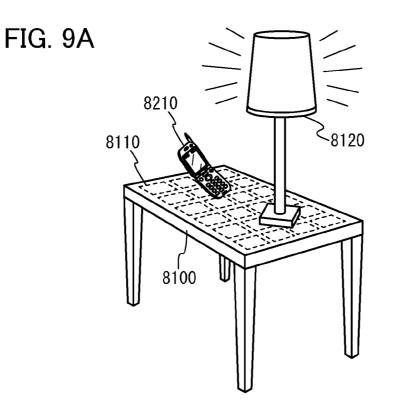

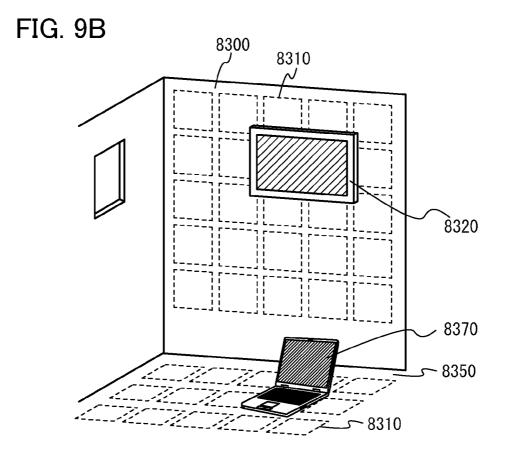

FIGS. 9A and 9B illustrate application examples of a power supply device.

# BEST MODE FOR CARRYING OUT THE INVENTION

Hereinafter, embodiments of the present invention will be 65 described in detail with reference to the accompanying drawings. However, the present invention is not limited to the

description below, and it is easily understood by those skilled in the art that modes and details disclosed herein can be modified in various ways. Therefore, the present invention is not construed as being limited to description of the embodiments.

A transistor is a kind of semiconductor elements and can achieve amplification of current or voltage, switching operation for controlling conduction or non-conduction, or the like. A transistor in this specification includes an insulated-gate field effect transistor (IGFET) and a thin film transistor (TFT).

Note that the position, the size, the range, or the like of each structure illustrated in drawings and the like is not accurately represented in some cases for easy understanding. Therefore, the disclosed invention is not necessarily limited to such a position, size, range, or the like disclosed in the drawings and the like. In the drawings for explaining the embodiments, the same parts or parts having a similar function are denoted by the same reference numerals, and description of such parts is not repeated.

Note that in this specification and the like, the term such as "electrode" or "wiring" does not limit the function of the component. For example, an "electrode" can be used as part of a "wiring", and vice versa. Further, the term "electrode" or "wiring" can also mean a combination of a plurality of "electrodes" and "wirings" formed in an integrated manner.

Note that in this specification and the like, the term "connection" includes not only direct connection but also indirect connection without departing from the purpose and the function.

Note that in this specification and the like, ordinal numbers such as "first", "second", and "third" are used in order to avoid confusion among components, and the terms do not mean limitation of the number of components.

Note that in this specification and the like, since a source and a drain of a transistor may interchange depending on the structure, the operating condition, or the like of the transistor, it is difficult to define which is a source or a drain. Therefore, the terms "source" and "drain" can be switched in this specification and the like.

### Embodiment 1

In this embodiment, an example of a power supply device 45 which is one embodiment of the present invention will be described with reference to FIGS. **1**A and **1**B.

A power supply device 100 illustrated in FIG. 1A includes a power feeding switch control circuit 111, a high-frequency wave supply circuit 112, and at least one power feeding cell 101. The power feeding cell 101 includes a power feeding antenna 102 and a power feeding switch 103. For the power feeding switch 103, a transistor including an oxide semiconductor in a channel formation region is used. The power feeding switch 103 functions as a switch for controlling supply of a high-frequency wave to the power feeding antenna 102. One electrode (terminal) of a source electrode and a drain electrode of the power feeding switch 103 is connected to a wiring 106, and a gate electrode (control terminal) of the power feeding switch 103 is connected to a wiring 105. Further, the other electrode (terminal) of the source electrode and the drain electrode of the power feeding switch 103 is connected to one electrode (terminal) of the power feeding antenna 102, and the other electrode (terminal) of the power feeding antenna 102 is connected to a wiring 104.

The power feeding antenna **102** has a coil shape in this embodiment; however, the shape of the power feeding antenna **102** is not limited thereto, and may be determined as

appropriate in consideration of a frequency of a high-frequency wave used for supplying power. Instead of a coiled antenna, a monopole antenna, a dipole antenna, a patch antenna, or the like can be used.

Although a common potential or a ground potential is 5 applied to the wiring 104, a predetermined potential may be alternatively applied thereto. In addition, the wiring 104 may be connected to another circuit. The wiring 105 is connected to the power feeding switch control circuit 111 and transmits a signal (potential) for turning on/off the power feeding switch 103 from the power feeding switch control circuit 111 to the control terminal of the power feeding switch 103. The high-frequency wave supply circuit 112 includes a high-frequency power supply generating a high-frequency wave and supplies a high-frequency wave to the power feeding antenna 102 through the wiring 106 and the power feeding switch 103.

A power receiving device 120 illustrated in FIG. 1B includes a power receiving circuit 121 and a rectifier circuit 125. The power receiving circuit 121 includes a power receiv- 20 121 is alternating current power; however, it can be converted ing antenna 122 and a resonant capacitor 123 which form an LC parallel resonance circuit. Further, the power receiving antenna 122 is connected to a wiring 124. Although a common potential or a ground potential is applied to the wiring 124, a predetermined potential may be alternatively applied 25 like can be used instead of an electromagnetic coupling thereto. In addition, the wiring 124 may be connected to another circuit. The rectifier circuit 125 includes a rectifier element 126 and a smoothing capacitor 127.

The frequency of the high-frequency wave which the highfrequency wave supply circuit 112 supplies is not limited to a 30 specific frequency, and for example, any of the following frequencies can be used: higher than or equal to 300 GHz and lower than 3 THz, which are frequencies of sub-millimeter waves; higher than or equal to 30 GHz and lower than 300 GHz, which are frequencies of millimeter waves; higher than 35 or equal to 3 GHz and lower than 30 GHz, which are frequencies of microwaves; higher than or equal to 300 MHz and lower than 3 GHz, which are frequencies of ultrashort waves; higher than or equal to 30 MHz and lower than 300 MHz, which are frequencies of very short waves; higher than or 40 equal to 3 MHz and lower than 30 MHz, which are frequencies of shortwaves; higher than or equal to 300 kHz and lower than 3 MHz, which are frequencies of medium waves; higher than or equal to 30 kHz and lower than 300 kHz, which are frequencies of long waves; and higher than or equal to 3 kHz 45 and lower than 30 kHz, which are frequencies of very long waves

Power supply from the power supply device 100 to the power receiving device 120 without a contact therebetween is described here. As a method of power supply from the power 50 supply device 100 to the power receiving device 120, an electromagnetic coupling method or an electromagnetic induction method can be used. In other words, by utilizing an electromagnetic induction phenomenon caused by change in electric field density, power is supplied without an electrical 55 contact. Specifically, first, a high-frequency wave (e.g., 13.56 MHz) is supplied from the high-frequency wave supply circuit 112 to the wiring 106. Next, when the power feeding switch control circuit 111 transmits a signal for turning on the power feeding switch 103 to the control terminal of the power 60 feeding switch 103 through the wiring 105, the power feeding switch 103 is turned on, so that the high-frequency wave is supplied to the power feeding antenna 102. When the highfrequency wave is supplied to the power feeding antenna 102, a magnetic field in which the density is changed in accordance 65 with the frequency of the high-frequency wave is generated from the power feeding antenna 102.

6

The change of the magnetic field generated from the power feeding antenna 102 causes induced current in the power receiving antenna 122 included in the power receiving circuit 121. In this manner, power can be supplied from the power supply device 100 to the power receiving device 120.

Since the power receiving circuit 121 includes an LC parallel resonance circuit in which the power receiving antenna 122 and the resonant capacitor 123 are combined, it can receive only power of a specific frequency. The specific frequency is determined by the inductance of the power receiving antenna 122 and the conductance of the resonant capacitor 123. When the power receiving circuit 121 receives a plurality of magnetic fields having different frequencies at the same time, an electromagnetic induction phenomenon hardly occurs. In contrast, the power receiving circuit 121 receives only power of a specific frequency, it can receive power efficiently.

Note that power received by the power receiving circuit to direct current power by the rectifier circuit 125. In the case where it is not necessary to convert it to direct current power, the rectifier circuit 125 is not necessarily provided.

As the method of power supply, a microwave method or the method and an electromagnetic induction method. The method of power supply may be selected by a practitioner in consideration of an intended use.

In this embodiment, a transistor including an oxide semiconductor in a channel formation region is used for the power feeding switch. Since the band gap of the oxide semiconductor is greater than or equal to 3 eV which is much wider than that of silicon, germanium, or the like, even when a large amount of current flows, hot-carrier degradation is hardly caused and a large amount of power can be supplied. Further, since the transistor including an oxide semiconductor in the channel formation region does not have a mechanical contact, a highly-reliable power supply device which has an excellent withstand property and can withstand long-term use can be provided.

In addition, in the transistor including an oxide semiconductor in the channel formation region, the off-state current per micrometer in channel width at room temperature can be less than or equal to 10 aA/ $\mu$ m (1×10<sup>-17</sup> A/ $\mu$ m), less than or equal to 1 aA/ $\mu$ m (1×10<sup>-18</sup> Å/ $\mu$ m), further less than or equal to 1 zA/um (1×10<sup>-21</sup> A/um), still further less than or equal to 1 vA/ $\mu$ m (1×10<sup>-24</sup> A/ $\mu$ m). Therefore, when the transistor including an oxide semiconductor in the channel formation region is used as the power feeding switch, unnecessary output of a high-frequency wave to the power feeding antenna 102 can be prevented.

For the power feeding switch, a transistor including an inorganic semiconductor such as silicon (Si), germanium (Ge), or silicon carbide (SiC) in a channel formation region can be used; however, the transistor including an oxide semiconductor in the channel formation region, in which degradation is hardly caused and both supply of a large amount of current and a smaller amount of off-state current can be realized, is preferably used.

As described above, the transistor including an oxide semiconductor in the channel formation region is used for the power feeding switch included in the power supply device 100, whereby a highly-reliable low-power-consumption power supply device which can supply a large amount of power and can withstand long-term use can be provided.

This embodiment can be implemented in appropriate combination with any of the other embodiments.

### Embodiment 2

In this embodiment, a position detecting device which can be used for a power supply device of one embodiment of the present invention will be described. By using the position 5 detecting device, whether there is a power receiving device or not can be detected.

A position detecting device 200 illustrated in FIG. 2 includes a position detecting switch control circuit 211, a high-frequency wave supply circuit 212, and at least one 10 position detecting cell 201. The position detecting cell 201 includes a position detecting antenna 202 and a position detecting switch 203. As the position detecting switch 203, a transistor including an oxide semiconductor in a channel formation region is used. The position detecting switch 203 15 functions as a switch for controlling supply of a high-frequency wave to the position detecting antenna 202. One electrode (terminal) of a source electrode and a drain electrode of the position detecting switch 203 is connected to a wiring **206.** and a gate electrode (control terminal) of the position 20 detecting switch 203 is connected to a wiring 205. In addition, the other electrode (terminal) of the source electrode and the drain electrode of the position detecting switch 203 is connected to one electrode (terminal) of the position detecting antenna 202, and the other electrode (terminal) of the position 25 detecting antenna 202 is connected to a potential detecting circuit 213.

The position detecting antenna **202** has a coil shape in this embodiment; however, the shape of the position detecting antenna **202** is not limited thereto, and may be determined as 30 appropriate in consideration of a frequency of a high-frequency wave used for supplying power. Instead of a coiled antenna, a monopole antenna, a dipole antenna, a patch antenna, or the like can be used.

The wiring **205** is connected to the position detecting 35 switch control circuit **211** and transmits a signal (potential) for turning on/off the position detecting switch **203** from the position detecting switch control circuit **211** to the control terminal of the position detecting switch **203**. The high-frequency wave supply circuit **212** includes a high-frequency 40 power supply generating a high-frequency wave and supplies a high-frequency wave to the position detecting antenna **202** through the wiring **206** and the position detecting switch **203**.

The frequency of the high-frequency wave which the highfrequency wave supply circuit 212 supplies is not limited to a 45 specific frequency, and for example, any of the following frequencies can be used: higher than or equal to 300 GHz and lower than 3 THz, which are frequencies of sub-millimeter waves; higher than or equal to 30 GHz and lower than 300 GHz, which are frequencies of millimeter waves; higher than 50 or equal to 3 GHz and lower than 30 GHz, which are frequencies of microwaves; higher than or equal to 300 MHz and lower than 3 GHz, which are frequencies of ultrashort waves; higher than or equal to 30 MHz and lower than 300 MHz, which are frequencies of very short waves; higher than or 55 equal to 3 MHz and lower than 30 MHz, which are frequencies of shortwaves; higher than or equal to 300 kHz and lower than 3 MHz, which are frequencies of medium waves; higher than or equal to 30 kHz and lower than 300 kHz, which are frequencies of long waves; and higher than or equal to 3 kHz 60 and lower than 30 kHz, which are frequencies of very long waves

Next, a method for detecting the power receiving device 120 by the position detecting device 200 is described. Detection of the power receiving device 120 by the position detecting device 200 is performed by detecting a change of the impedance of the position detecting cell 201 which is caused

when the power receiving device **120** gets close to the position detecting device **200**, as a potential change.

Specifically, first, a high-frequency wave (e.g., 3.5 MHz) is supplied from the high-frequency wave supply circuit **212** to the wiring **206** in a state where the power receiving device **120** is not placed over the intended position detecting cell **201** and a signal for turning on the position detecting switch **203** is transmitted from the position detecting switch control circuit **211** to the control terminal of the position detecting switch **203** through the wiring **205**, whereby the position detecting switch **203** is turned on and the high-frequency wave is supplied to the position detecting antenna **202**. The potential of a node **207** at this time is detected and stored by the potential detecting circuit **213**.

When the power receiving device 120 gets close to the intended position detecting cell 201, apparent inductance of the position detecting antenna 202 is changed by the influence of the power receiving antenna 122 included in the power receiving device 120. That is, since impedance of the position detecting cell 201 is changed, the potential of the node 207 is also changed. By comparing the potential of the node 207 with the stored potential, it is possible to determine whether or not the power receiving device 120 is placed over the intended position detecting cell 201.

The impedance of the position detecting cell **201** gets larger as the frequency of a high-frequency wave used for position detection gets higher; thus, the potential change of the node **207** becomes also bigger. In other words, the higher the frequency of the high-frequency wave used for the position detection is, the more sensitively the position detection is performed. The frequency of the high-frequency wave used for the position detection is preferably higher than or equal to 1 MHz, more preferably higher than or equal to 3 MHz, still more preferably higher than or equal to 5 MHz. By using a high-frequency wave with a higher frequency, position detection can be performed quickly and accurately.

An OFET which is conventionally used as a position detecting switch has higher operation speed than a MEMS switch; however, it has been difficult to use a high-frequency wave with a frequency of higher than 5 MHz for position detection. A transistor including an oxide semiconductor in a channel formation region has higher field-effect mobility and higher operation speed than an OFET; therefore, the transistor including an oxide semiconductor in the channel formation region is used as the position detecting switch, so that a high-frequency wave with a higher frequency can be used for position detection.

Since the band gap of the oxide semiconductor is greater than or equal to 3 eV which is much wider than that of silicon, germanium, or the like, hot-carrier degradation is hardly caused; accordingly, a highly reliable position detecting device which can withstand long-term use can be provided.

In addition, in the transistor including an oxide semiconductor in the channel formation region, the off-state current per micrometer in channel width at room temperature can be less than or equal to 10 aA/µm ( $1\times10^{-17}$  A/µm), less than or equal to 1 aA/µm ( $1\times10^{-18}$  A/µm), further less than or equal to 1 zA/µm ( $1\times10^{-21}$  A/µm), still further less than or equal to 1 yA/µm ( $1\times10^{-24}$  A/µm). Therefore, when the transistor including an oxide semiconductor in the channel formation region is used as the position detecting switch, unnecessary output of a high-frequency wave to the position detecting antenna **202** can be prevented.

As the position detecting switch **203**, a transistor including an inorganic semiconductor such as silicon (Si), germanium (Ge), or silicon carbide (SiC) in a channel formation region can be used; however, the transistor including an oxide semiconductor in the channel formation region, in which degradation is hardly caused and both high-speed operation and a smaller amount of off-state current can be realized, is preferably used.

As described above, the transistor including an oxide semiconductor in the channel formation region is used instead of an OFET as the position detecting switch **203** included in the position detecting device **200**, so that the frequency of the high-frequency wave used for the position detection can be higher. As a result, a highly-reliable low-power-consumption power supply device which can realize quick and accurate position detection and can withstand long-term use can be provided.

This embodiment can be implemented in appropriate com-15 bination with any of the other embodiments.

### Embodiment 3

In this embodiment, an example is described in which the 20 power feeding switches and the position detecting switches which are described in Embodiments 1 and 2 are arranged in a matrix. The power feeding cells and/or the position detecting cells are arranged in a matrix to form an antenna sheet.

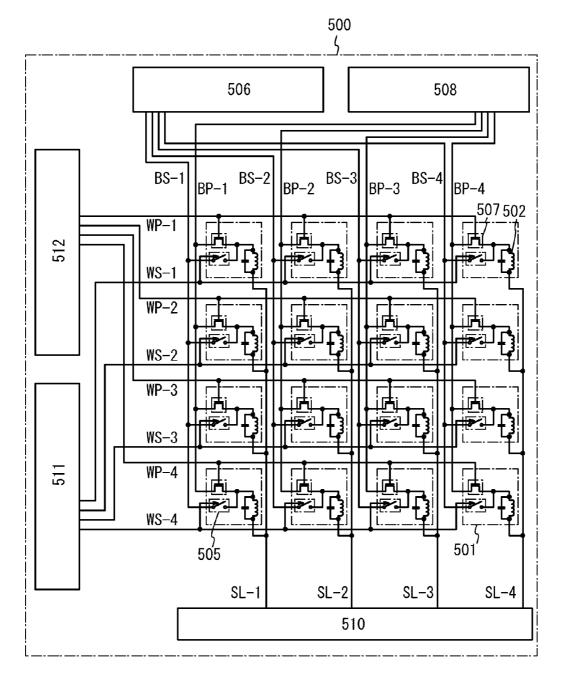

First, a structure of a conventional power supply device **500** 25 and operation thereof are described with reference to FIGS. **3A** and **3B**. The conventional power supply device **500** illustrated in FIG. **3A** includes a power feeding cell **501**, a first high-frequency wave supply circuit **506**, a second high-frequency wave supply circuit **508**, a power feeding switch 30 control circuit **511**, a position detecting switch control circuit **512**, and a potential detecting circuit **510**.

The power feeding cell **501** has a coiled antenna **502** which is used for both power feeding and position detection. One electrode of the antenna **502** is connected to the first high-35 frequency wave supply circuit **506** for the power feeding through a power feeding switch **505** and to the second highfrequency wave supply circuit **508** for the position detection through a position detecting switch **507**. A MEMS switch is used as the power feeding switch **505** and an OFET is used as 40 the position detecting switch **507**. The other electrode of the antenna **502** is connected to the potential detecting circuit **510**. In addition, the antenna **502** and a capacitor **503** are connected in parallel.

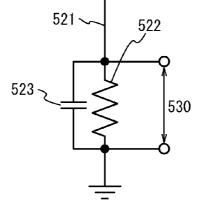

FIG. 3B shows an example of the potential detecting circuit 45 **510**. The potential detecting circuit **510** includes a resistor **522** and a capacitor **523**. An example in which the resistor **522** and the capacitor **523** are connected in parallel is described.

On/off operation of the power feeding switch **505** is controlled by the power feeding switch control circuit **511**. 50 On/off operation of the position detecting switch **507** is controlled by the position detecting switch control circuit **512**.

The first high-frequency wave supply circuit **506** and the second high-frequency wave supply circuit **508** each include a high-frequency power supply generating a high-frequency 55 wave and supply a high-frequency wave to the antenna **502** through the power feeding switch **505** or the position detecting switch **507**.

The frequency of the high-frequency wave supplied from the first high-frequency wave supply circuit **506** and the frequency of the high-frequency wave supplied from the second high-frequency wave supply circuit **508** are different. The first high-frequency wave supply circuit **506** supplies a highfrequency wave with a power feeding frequency (e.g., 13.56 MHz) and the second high-frequency wave supply circuit **508** 65 supplies a high-frequency wave with a position detection frequency (e.g., 3.5 MHz). By using high-frequency waves

with different frequencies, the power feeding and the position detection are performed at the same time.

For example, when position detection is performed during power feeding operation, the power feeding switch **505** and the position detecting switch **507** are turned on simultaneously, and then a high-frequency wave in which a high-frequency wave with a frequency of 13.56 MHz and a high-frequency wave with a frequency of 3.5 MHz are superimposed on each other is applied to a node **520**.

By connecting the capacitor **503** and the antenna **502** in parallel to form an LC parallel resonance circuit, a highfrequency wave with a frequency of 13.56 MHz is taken out from the high-frequency wave in which the two high-frequency waves are superimposed on each other, and used for the power feeding. Further, the capacitor **523** and the resistor **522** included in the potential detecting circuit **510** are connected in parallel and a potential **530** or the potential of a node **521** is detected, so that the potential change of the highfrequency wave with a frequency of 3.5 MHz is detected.

FIG. 4 shows a conventional example in which the power feeding cells **501** illustrated in FIG. **3**A are arranged in a matrix. In FIG. **4**, the power supply device **500** in which 16 power feeding cells **501** are arranged in a matrix with 4 rows and 4 columns is illustrated.

In FIG. 4, gate electrodes of the position detecting switches 507 included in all the power feeding cells 501 in the first row are connected to WP-1; gate electrodes of the power feeding switches 505 included in all the power feeding cells 501 in the first row are connected to WS-1; one of a source electrode and a drain electrode of each of the position detecting switches 507 included in all the power feeding cells 501 in the first column is connected to BP-1; one of a source electrode and a drain electrode of each of the power feeding switches 505 included in all the power feeding cells 501 in the first column is connected to BP-1; one of a source electrode and a drain electrode of each of the power feeding switches 505 included in all the power feeding cells 501 in the first column is connected to BS-1; and an electrode, which is not connected to the position detecting switch 507 and the power feeding switch 505, of each of the antennas 502 included in all the power feeding cells 501 in the first column is connected to SL-1.

In this manner, in FIG. 4, 16 power feeding cells 501 arranged in a matrix with 4 rows and 4 columns are connected to WP-1 to WP-4, WS-1 to WS-4, BP-1 to BP-4, BS-1 to BS-4, and SL-1 to SL-4. WP-1 to WP-4 are connected to the position detecting switch control circuit 512; WS-1 to WS-4 are connected to the power feeding switch control circuit 511; BP-1 to BP-4 are connected to the second high-frequency wave supply circuit 508; BS-1 to BS-4 are connected to the first high-frequency wave supply circuit 506; and SL-1 to SL-4 are connected to the potential detecting circuit 510.

Whether there is the power receiving device **120** which gets close to the power feeding cell **501** or not can be detected by the following operation (position detection operation). First, a potential for turning off the position detecting switches **507** is supplied to WP-2 to WP-4 and a potential for turning on the position detecting switches **507** is supplied to WP-1. A high-frequency wave with a position detection frequency (e.g., 3.5 MHz) is supplied to BS-1 to BS-4. Then, the potentials of SL-1 to SL-4 are detected.

Next, a potential for turning off the position detecting switches **507** is supplied to WP-**1**, WP-**3**, and WP-**4**, and a potential for turning on the position detecting switches **507** is supplied to WP-**2**. A high-frequency wave with a position detection frequency (e.g., 3.5 MHz) is supplied to BS-**1** to BS-**4**. Then, the potentials of SL-**1** to SL-**4** are detected.

As described above, WP-1 to WP-4 are sequentially selected, whereby the position of the power feeding cell **501** to which the power receiving device **120** gets close can be detected (specified).

The power feeding switch **505** of the power feeding cell <sup>5</sup> **501** the position of which is detected (specified) is turned on, and a high-frequency wave with a power feeding frequency (e.g., 13.56 MHz) is supplied from the first high-frequency wave supply circuit **506** (power feeding operation). When it is judged that the power feeding operation by the position detection operation, the power feeding switch **505** is turned off and supply of the power feeding high-frequency wave from the first high-frequency wave supply circuit **506** to the power feeding cell **501** is stopped. In this manner, the position detection operation and the power feeding operation are performed.

The power feeding switch **505** and the position detecting switch **507** each use a transistor including an oxide semicon-<sup>20</sup> ductor in a channel formation region, so that a highly-reliable low-power-consumption power supply device which has excellent sensitivity for the position detection can be provided.

As described in Embodiment 1, the transistor including an 25 oxide semiconductor in the channel formation region has low off-state current, and even when a large amount of current flows, hot-carrier degradation is hardly caused. Further, since there is no mechanical contact, the power feeding switch **505** is replaced with the transistor including an oxide semiconductor in the channel formation region, so that a highlyreliable low-power-consumption power supply device which can supply a large amount of power and can withstand longterm use can be provided.

In addition, as described in Embodiment 2, the transistor 35 including an oxide semiconductor in the channel formation region has higher field-effect mobility and higher operation speed than an OFET; therefore, the position detecting switch **507** is replaced with the transistor including an oxide semiconductor in the channel formation region, so that a high-40 frequency wave with a higher frequency can be used for position detection and quick and accurate position detection can be conducted.

A transistor including an oxide semiconductor in a channel formation region has high operation speed because of its 45 field-effect mobility which is higher than that of an OFET; therefore, even when the number of power feeding cells is large, the power feeding cell **501** over which the power receiving device **120** is placed can be detected (specified) quickly. Further, since a high-frequency wave with a higher 50 frequency can be used for the position detection, more accurate position detection can be conducted.

Note that when the high-frequency wave with the power feeding frequency and the high-frequency wave with the position detection frequency have the same frequency, the 55 power feeding operation and the position detection operation cannot be performed at the same time; therefore, different frequencies need to be used as the power feeding frequency and the position detection frequency. In addition, the frequency of the high-frequency position detection wave is preferably lower than that of the high-frequency power feeding wave.

Next, a structure in which by using the same transistor as a power feeding switch and a position detecting switch, one switch included in a power feeding cell serves as a power 65 feeding one and a position detection one is described with reference to FIG. **5**.

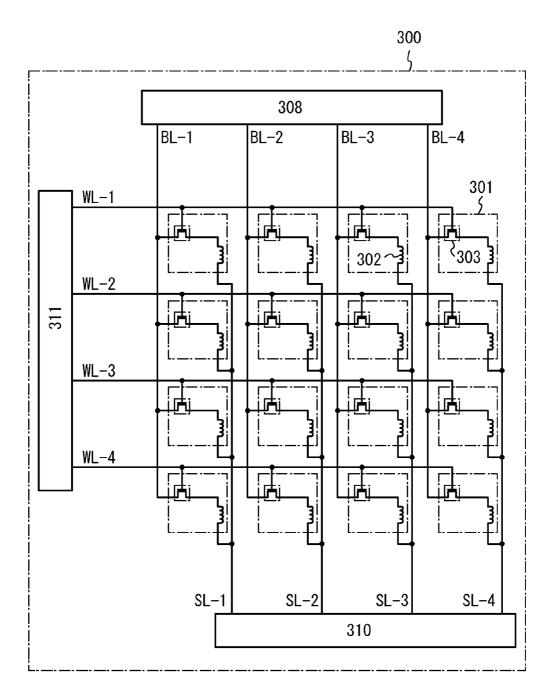

A cell **301** illustrated in FIG. **5** has a structure similar to that of the power feeding cell **101** described in Embodiment 1 and also functions as the position detecting cell described in Embodiment 2. That is, an antenna **302** in FIG. **5** functions as both the power feeding antenna and the position detecting antenna. Further, a switch **303** functions as both the power feeding switch and the position detecting switch.

A power supply device **300** in which 16 cells **301** are arranged in a matrix with 4 rows and 4 columns is illustrated in FIG. **5**; however, the number and arrangement of cells **301** are not limited thereto and can be determined by a practitioner in consideration of an intended use.

In FIG. 5, gate electrodes of the switches 303 included in all the cells 301 in the first row are connected to WL-1; one of a source electrode and a drain electrode of each of the switches 303 included in all the cells 301 in the first column is connected to BL-1; and an electrode, which is not connected to the switch 303, of each of the antennas 302 included in all the cells 301 in the first column is connected to SL-1. Here, WL-1, BL-1, and SL-1 correspond to the wiring 105, the wiring 106, and the wiring 104 which are described in Embodiment 1, respectively (see FIG. 1A).

As described above, in FIG. 5, 16 cells **301** arranged in a matrix with 4 rows and 4 columns are connected to WL-1 to WL-4, BL-1 to BL-4, and SL-1 to SL-4. WL-1 to WL-4 are connected to a switch control circuit **311**; BL-1 to BL-4 are connected to a high-frequency wave supply circuit **308**; and SL-1 to SL-4 are connected to a potential detecting circuit **310**.

The high-frequency wave supply circuit **308** includes a high-frequency power supply generating a high-frequency wave and supplies a high-frequency wave to the antenna **302** through the switch **303**.

Power feeding from the power supply device **300** to the power receiving device **120** in power feeding operation is performed by the cell **301** to which the power receiving device **120** gets close, not by all the cells **301** at the same time. Note that power may be fed from a plurality of cells **301** or all the cells **301** depending on the number or the structure of the power receiving devices **120** which get close.

Since unnecessary power feeding can be reduced by limitation on power feeding from the cell **301** to which the power receiving device **120** does not get close, power consumption of the whole power supply device can be reduced and power feeding can be performed efficiently.

A transistor including an oxide semiconductor in a channel formation region can achieve low power consumption and can supply a large amount of power, and is a highly reliable transistor in which hot-carrier degradation is hardly caused. In addition, the transistor including an oxide semiconductor in the channel formation region has higher field-effect mobility and higher operation speed than an OFET. By using the transistor including an oxide semiconductor in the channel formation region, one transistor can serve as both the power feeding switch and the position detecting switch.

Further, in the transistor including an oxide semiconductor in the channel formation region, a high-frequency wave with a frequency of 5 MHz or higher can be used for position detection. Thus, in addition to low power consumption and high reliability, the high-frequency wave with the power feeding frequency and the high-frequency wave with the position detection frequency have the same frequency. As a result, high-frequency wave supply circuits which have been conventionally needed to be separately provided for the position detection and for the power feeding, can be one high-frequency wave supply circuit. Further, switch control circuits

50

60

which have been needed to be separately provided for the position detection and for the power feeding can be one switch control circuit.

Furthermore, since the position detection and the power feeding can be performed by high-frequency waves with one 5 frequency, a high-frequency wave does not need to be separated using a capacitor. Thus, the capacitor 503 and the capacitor 523 described in FIGS. 3A and 3B do not need to be provided. However, that may not be true if a capacitor is provided to remove noise components or the like.

In the case where the position detection operation and the power feeding operation are performed using high-frequency waves with one frequency, the power feeding operation needs to be stopped during the position detection operation. In the structure illustrated in FIG. 5, for example, the antennas 302 15 included in all the power feeding cells in the second column are all connected to SL-2; therefore, when the power receiving device is placed over any of the power feeding cells in the second column, it is detected that the power receiving device is placed over all the power feeding cells in the second column 20 apparently. Accordingly, in the case where one transistor serves as both the power feeding switch and the position detecting switch, the position detection operation and the power feeding operation need to be alternately performed.

The position detection operation is performed in the fol- 25 lowing manner. First, from the switch control circuit 311, a signal for turning off the switches 303 is supplied to WL-2 to WL-4 and a signal for turning on the switches 303 is supplied to WL-1. A high-frequency wave with a specific frequency (e.g., 13.56 MHz) is supplied from the high-frequency wave 30 supply circuit 308 to BL-1 to BL-4, and the potentials of SL-1 to SL-4 are detected.

Next, from the switch control circuit 311, a signal for turning off the switches 303 is supplied to WL-1, WL-3, and WL-4 and a signal for turning on the switches 303 is supplied 35 to WL-2. A high-frequency wave with a specific frequency (e.g., 13.56 MHz) is supplied from the high-frequency wave supply circuit 308 to BL-1 to BL-4, and the potentials of SL-1 to SL-4 are detected.

In this manner, by scanning WL-1 to WL-4 sequentially, 40 the position of the cell **301** over which the power receiving device 120 is placed can be detected (specified).

Note that the position detection operation is not operation for supplying power like power feeding operation, and by using a transistor including an oxide semiconductor in a chan- 45 nel formation region, the position detection frequency can be higher; therefore, the position detection operation can be performed with power smaller than power used for the power feeding operation. That is, a low-power consumption power supply device can be provided.

Then, the power feeding operation is performed. First, a high-frequency power feeding wave is supplied from the high-frequency wave supply circuit 308 to the cell 301 over which the power receiving device 120 is placed and which is detected by the position detection operation. Next, when a 55 signal for turning on the switch 303 is supplied from the switch control circuit 311 to a control terminal of the switch 303 included in the cell 301, a high-frequency power feeding wave is supplied to the antenna 302 and power can be supplied to the power receiving device 120.

By using a transistor including an oxide semiconductor in a channel formation region as the switch 303, quick and accurate position detection operation can be performed; accordingly, a position detection operation period, namely, a suspension period of the power feeding operation can be 65 shortened. A power feeding operation period is preferably longer than the position detection operation period. Further, it

14

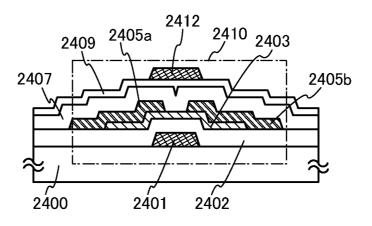

is more preferable that the power feeding operation period be 5 times or more the position detection operation period, preferably 10 times or more the position detection operation period, because the suspension period of the power feeding operation can be substantially regarded as being nonexistent.