(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5090008号

(P5090008)

(45) 発行日 平成24年12月5日(2012.12.5)

(24) 登録日 平成24年9月21日(2012.9.21)

(51) Int.Cl.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO3K 3/356   | (2006.01) | HO3K 3/356 | B    |

| HO1L 29/786  | (2006.01) | HO1L 29/78 | 614  |

| HO1L 21/336  | (2006.01) | HO1L 29/78 | 612Z |

| HO1L 27/08   | (2006.01) | HO1L 29/78 | 618B |

| HO1L 21/8234 | (2006.01) | HO1L 27/08 | 331E |

請求項の数 44 (全 38 頁) 最終頁に続く

(21) 出願番号

特願2007-27595 (P2007-27595)

(22) 出願日

平成19年2月7日(2007.2.7)

(65) 公開番号

特開2008-193545 (P2008-193545A)

(43) 公開日

平成20年8月21日(2008.8.21)

審査請求日

平成22年1月14日(2010.1.14)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100088672

弁理士 吉竹 英俊

(74) 代理人 100088845

弁理士 有田 貴弘

(72) 発明者 宮山 隆

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

(72) 発明者 飛田 洋一

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置およびシフトレジスタ回路

## (57) 【特許請求の範囲】

## 【請求項1】

所定の第1ノードと第2ノードとの間に直列に接続し、制御電極が相互に接続した複数の第1トランジスタを備える半導体装置であって、

前記複数の第1トランジスタ間の接続ノードの各々を第3ノードとし、

前記第1～第3ノードおよび前記制御電極のそれぞれが前記複数の第1トランジスタのしきい値電圧よりも高いH(High)レベルになった状態から、前記第1および第2ノードがHレベルのまま前記制御電極の電位が前記しきい値電圧よりも低いL(Low)レベルに変化すると、それに応じて前記第3ノードのレベルもLレベルに引き下げられるよう構成されており、

前記第3ノードの各々において、

前記制御電極と前記第3ノードとの間の容量成分をC1、当該C1に含まれない前記第3ノードに付随する寄生容量をC2、前記制御電極におけるHレベルとLレベルとの差をVd、前記第1トランジスタのしきい値電圧をVthとすると、

$$C_1 + C_2 \times (V_d - V_{th}) / V_{th}$$

の関係を満たす

ことを特徴とする半導体装置。

## 【請求項2】

請求項1記載の半導体装置であって、

前記第3ノードのレベルを引き下げる手段は、前記制御電極と当該第3ノードとの間の

10

20

寄生容量である

ことを特徴とする半導体装置。

**【請求項 3】**

請求項 2 記載の半導体装置であって、

前記第 3 ノードとなる電極の幅は、前記第 1 および第 2 ノードとなる電極の幅よりも広い

ことを特徴とする半導体装置。

**【請求項 4】**

請求項 1 から請求項 3 のいずれか記載の半導体装置であって、

前記第 3 ノードのレベルを引き下げる手段として、前記制御電極と前記第 3 ノードとの間に接続した容量素子をさらに備える

ことを特徴とする半導体装置。 10

**【請求項 5】**

請求項 1 記載の半導体装置であって、

前記第 3 ノードのレベルを引き下げる手段として、前記制御電極と前記第 3 ノードとの間に接続され、前記制御電極側をカソード、前記第 3 ノード側をアノードとするダイオードをさらに備える

ことを特徴とする半導体装置。

**【請求項 6】**

請求項 1 記載の半導体装置であって、

前記第 3 ノードのレベルを引き下げる手段として、前記第 1 トランジスタの前記制御電極と前記第 3 ノードとの間に接続された第 2 トランジスタをさらに備える

ことを特徴とする半導体装置。 20

**【請求項 7】**

請求項 1 から請求項 6 のいずれか記載の半導体装置であって、

前記複数の第 1 トランジスタは、非晶質シリコン薄膜トランジスタである

ことを特徴とする半導体装置。

**【請求項 8】**

請求項 1 から請求項 6 のいずれか記載の半導体装置であって、

前記複数の第 1 トランジスタは、有機トランジスタである

ことを特徴とする半導体装置。 30

**【請求項 9】**

入力端子、出力端子、第 1 クロック端子およびリセット端子と、

前記第 1 クロック端子に入力される第 1 クロック信号を前記出力端子に供給する第 1 トランジスタと、

前記出力端子を放電する第 2 トランジスタと、

前記入力端子に入力される入力信号に応じて前記第 1 トランジスタの制御電極が接続する第 1 ノードを充電する充電回路と、

前記リセット端子に入力されるリセット信号に応じて前記第 1 ノードを放電する放電回路とを備え、

前記充電回路は、

前記第 1 ノードと電源端子との間に直列に接続し、制御電極が共に前記入力端子に接続した複数の第 3 トランジスタを含み、

前記入力信号が第 3 トランジスタのしきい値電圧よりも高い H (High) レベルになると前記複数の第 3 トランジスタがオンすることで前記第 1 ノードを充電し、その後当該入力信号が前記しきい値電圧よりも低い L (Low) レベルに変化すると前記複数の第 3 トランジスタ間の各接続ノードが L レベルに引き下げられるよう構成されており、 40

前記複数の第 3 トランジスタ間の接続ノードの各々において、

前記入力端子と前記接続ノードとの間の容量成分を C 1、当該 C 1 に含まれない前記接続ノードに付随する寄生容量を C 2、前記入力信号の H レベルと L レベルとの差を V d、

50

前記第3トランジスタのしきい値電圧をV<sub>th</sub>とすると、

$$C_1 C_2 \times (V_d - V_{th}) / V_{th}$$

の関係を満たす

ことを特徴とするシフトレジスタ回路。

**【請求項10】**

請求項9記載のシフトレジスタ回路であって、

前記第2トランジスタの制御電極は、前記リセット端子に接続している

ことを特徴とするシフトレジスタ回路。

**【請求項11】**

請求項9記載のシフトレジスタ回路であって、

前記第1ノードを入力端とし、前記第2トランジスタの制御電極が接続する第2ノードを出力端とするインバータをさらに備える

ことを特徴とするシフトレジスタ回路。

**【請求項12】**

請求項11記載のシフトレジスタ回路であって、

前記第2ノードに接続した制御電極を有し、前記第1ノードを放電する第4トランジスタをさらに備える

ことを特徴とするシフトレジスタ回路。

**【請求項13】**

請求項9記載のシフトレジスタ回路であって、

前記第2トランジスタを2つ有し、

前記2つの第2トランジスタ各々の制御電極が接続するノードをそれぞれ第2および第3ノードとし、

前記2つの第2トランジスタは、所定の制御信号に基づいて交互に駆動される

ことを特徴とするシフトレジスタ回路。

**【請求項14】**

請求項13記載のシフトレジスタ回路であって、

前記制御信号は、

互いに相補な第1および第2制御信号により構成されており、

当該シフトレジスタ回路は、

前記第1および第2制御信号がそれぞれ入力される第1および第2制御端子と、

前記第1制御端子と前記第2ノードとの間に接続する第4トランジスタと、

前記第2制御端子と前記第3ノードとの間に接続する第5トランジスタとをさらに備え

、

前記第4および第5トランジスタは、

その片方の主電極がたすき掛けに互いの制御電極に接続されている

ことを特徴とするシフトレジスタ回路。

**【請求項15】**

請求項13または請求項14記載のシフトレジスタ回路であって、

前記2つの第2トランジスタを交互に駆動する手段は、

前記第1ノードを入力端とするインバータと、

前記制御信号に基づいて、前記インバータの出力端を前記第2および第3ノードへ交互に接続させる切替回路とを含む

ことを特徴とするシフトレジスタ回路。

**【請求項16】**

請求項13から請求項15のいずれか記載のシフトレジスタ回路であって、

前記第2ノードに接続した制御電極を有し、前記第1ノードを放電する第6トランジスタと、

前記第3ノードに接続した制御電極を有し、前記第1ノードを放電する第7トランジスタとをさらに備える

10

20

30

40

50

ことを特徴とするシフトレジスタ回路。

**【請求項 17】**

請求項 9 記載のシフトレジスタ回路であって、

前記第1クロック端子に接続した制御電極を有し、前記第1ノードと前記出力端子との間に接続した第4トランジスタをさらに備える

ことを特徴とするシフトレジスタ回路。

**【請求項 18】**

請求項 17 記載のシフトレジスタ回路であって、

前記第1クロック信号とは位相が異なる第2クロック信号が入力される第2クロック端子と、

前記第1ノードを入力端とし、前記第2クロック信号により活性化されるインバータと、

前記第1クロック端子に接続した制御電極を有し、当該インバータの出力端を放電する第5トランジスタと、

前記インバータの前記出力端に接続した制御電極を有し、前記第1ノードを放電する第6トランジスタとをさらに備える

ことを特徴とするシフトレジスタ回路。

**【請求項 19】**

請求項 18 記載のシフトレジスタ回路であって、

前記第2トランジスタの制御電極は、前記第2クロック端子に接続している

ことを特徴とするシフトレジスタ回路。

**【請求項 20】**

請求項 19 記載のシフトレジスタ回路であって、

前記第2トランジスタは、前記出力端子と前記第1クロック端子との間に接続している

ことを特徴とするシフトレジスタ回路。

**【請求項 21】**

請求項 9 記載のシフトレジスタ回路であって、

前記第1ノードを入力端とし、前記第1クロック信号により活性化されるインバータと、

前記インバータの出力端に接続した制御電極を有し、前記第1ノードを放電する第4トランジスタとをさらに備え、

前記インバータは、

当該インバータの前記出力端と前記第1クロック端子との間に接続した第1容量素子を負荷素子として有している

ことを特徴とするシフトレジスタ回路。

**【請求項 22】**

請求項 21 記載のシフトレジスタ回路であって、

前記第2トランジスタの制御電極は、前記インバータの前記出力端に接続している

ことを特徴とするシフトレジスタ回路。

**【請求項 23】**

請求項 22 記載のシフトレジスタ回路であって、

前記第1クロック信号とは位相が異なる第2クロック信号が入力される第2クロック端子と、

前記第2クロック端子に接続した制御電極を有し、前記出力端子を放電する第5トランジスタとをさらに備える

ことを特徴とするシフトレジスタ回路。

**【請求項 24】**

請求項 9 から請求項 23 のいずれか記載のシフトレジスタ回路であって、

前記複数の第3トランジスタ間の各接続ノードと前記入力端子との間に接続した第2容量素子をさらに備える

ことを特徴とするシフトレジスタ回路。

**【請求項 25】**

請求項 9 から請求項 23 のいずれか記載のシフトレジスタ回路であって、前記複数の第3トランジスタ間の各接続ノードと前記入力端子との間に、前記入力端子側をカソード、前記接続ノード側をアノードとして接続されたダイオードをさらに備えることを特徴とするシフトレジスタ回路。

**【請求項 26】**

請求項 9 から請求項 23 のいずれか記載のシフトレジスタ回路であって、前記複数の第3トランジスタ間の各接続ノードと前記入力端子との間に、制御電極が前記第1クロック端子に接続した第6トランジスタをさらに備えることを特徴とするシフトレジスタ回路。

10

**【請求項 27】**

第1および第2入力端子、出力端子、第1クロック端子並びにリセット端子と、前記第1クロック端子に入力される第1クロック信号を前記出力端子に供給する第1トランジスタと、前記出力端子を放電する第2トランジスタと、前記第1トランジスタの制御電極が接続する第1ノードを充電する第1充電回路と、前記リセット端子に入力されるリセット信号に応じて前記第1ノードを放電する第1放電回路を備え、前記第1充電回路は、

20

前記第1ノードと電源端子との間に直列に接続し、制御電極が共に所定の第2ノードに接続した複数の第3トランジスタと、

前記第1入力端子に入力される第1入力信号に応じて前記第2ノードを充電する第2充電回路と、

前記第2入力信号に入力される第2入力信号に応じて前記第2ノードを昇圧する昇圧回路と、

前記リセット信号に応じて前記第2ノードを放電する第2放電回路を備え、

前記複数の第3トランジスタ間の接続ノードの各々において、

前記第2ノードと前記接続ノードとの間の容量成分をC1、当該C1に含まれない前記接続ノードに付随する寄生容量をC2、前記第2ノードにおけるHレベルとLレベルとの差をVd、前記第3トランジスタのしきい値電圧をVthとすると、

$$C_1 = C_2 \times (V_d - V_{th}) / V_{th}$$

30

の関係を満たす

ことを特徴とするシフトレジスタ回路。

**【請求項 28】**

請求項 27 記載のシフトレジスタ回路であって、前記第1充電回路は、前記第2ノードが前記第3トランジスタのしきい値電圧よりも高いH(High)レベルになると前記複数の第3トランジスタがオンすることで前記第1ノードを充電し、その後当該第2ノードが前記しきい値電圧よりも低いL(Low)レベルに変化すると前記複数の第3トランジスタ間の各接続ノードがLレベルに引き下げられるよう構成されていることを特徴とするシフトレジスタ回路。

40

**【請求項 29】**

請求項 27 または請求項 28 記載のシフトレジスタ回路であって、前記第2ノードを入力端とするインバータをさらに備え、前記第1放電回路は、前記インバータの出力端に接続した制御電極を有し、前記第1ノードを放電する第4トランジスタであることを特徴とするシフトレジスタ回路。

**【請求項 30】**

50

請求項 2 9 記載のシフトレジスタ回路であって、

前記インバータの出力端に接続した制御電極を有し、前記第 2 ノードを放電する第 5 トランジスタをさらに備える

ことを特徴とするシフトレジスタ回路。

【請求項 3 1】

請求項 2 9 または請求項 3 0 記載のシフトレジスタ回路であって、

前記第 2 トランジスタの制御電極は、前記インバータの前記出力端に接続している

ことを特徴とするシフトレジスタ回路。

【請求項 3 2】

請求項 2 7 から請求項 3 1 のいずれか記載のシフトレジスタ回路であって、

前記複数の第 3 トランジスタ間の各接続ノードと前記第 2 ノードとの間に接続した容量素子をさらに備える

ことを特徴とするシフトレジスタ回路。

【請求項 3 3】

請求項 2 7 から請求項 3 1 のいずれか記載のシフトレジスタ回路であって、

前記複数の第 3 トランジスタ間の各接続ノードと前記第 2 ノードとの間に、前記第 2 ノード側をカソード、前記接続ノード側をアノードとして接続されたダイオードをさらに備える

ことを特徴とするシフトレジスタ回路。

【請求項 3 4】

請求項 2 7 から請求項 3 1 のいずれか記載のシフトレジスタ回路であって、

前記複数の第 3 トランジスタ間の各接続ノードと前記第 2 ノードとの間に、制御電極が前記第 1 クロック端子に接続した第 6 トランジスタをさらに備える

ことを特徴とするシフトレジスタ回路。

【請求項 3 5】

請求項 2 7 から請求項 3 4 のいずれか記載のシフトレジスタ回路であって、

前記第 2 充電回路は、

前記第 2 ノードと電源端子との間に直列に接続し、制御電極が共に前記第 1 入力端子に接続した複数の第 7 トランジスタを含む

ことを特徴とするシフトレジスタ回路。

【請求項 3 6】

請求項 3 5 記載のシフトレジスタ回路であって、

前記第 2 充電回路は、

前記第 1 入力端子が前記第 7 トランジスタのしきい値電圧よりも高い H (High) レベルになると前記複数の第 7 トランジスタがオンすることで前記第 2 ノードを充電し、その後当該第 1 入力端子が前記しきい値電圧よりも低い L (Low) レベルに変化すると前記複数の第 7 トランジスタ間の各接続ノードが L レベルに引き下げられるよう構成されている

ことを特徴とするシフトレジスタ回路。

【請求項 3 7】

請求項 3 5 または請求項 3 6 記載のシフトレジスタ回路であって、

前記複数の第 7 トランジスタ間の各接続ノードと前記第 1 入力端子との間に接続した容量素子をさらに備える

ことを特徴とするシフトレジスタ回路。

【請求項 3 8】

請求項 3 5 または請求項 3 6 記載のシフトレジスタ回路であって、

前記複数の第 7 トランジスタ間の各接続ノードと前記第 1 入力端子との間に、前記第 1 入力端子側をカソード、前記接続ノード側をアノードとして接続されたダイオードをさらに備える

ことを特徴とするシフトレジスタ回路。

【請求項 3 9】

10

20

30

40

50

請求項 3 5 または請求項 3 6 記載のシフトレジスタ回路であって、

前記複数の第 7 トランジスタ間の各接続ノードと前記第 1 入力端子との間に接続し、制御電極が前記第 1 クロック信号とは位相が異なる第 2 クロック信号が入力される第 2 クロック端子に接続した第 8 トランジスタをさらに備える

ことを特徴とするシフトレジスタ回路。

## 【請求項 4 0】

第 1 および第 2 入力端子、出力端子並びにクロック端子と、

互いに相補な第 1 および第 2 電圧信号が各々入力される第 1 および第 2 電圧信号端子と

、

前記クロック端子に入力されるクロック信号を出力端子に供給する第 1 トランジスタと

10

前記出力端子を放電する第 2 トランジスタと、

前記第 1 入力端子に入力される第 1 入力信号に基づいて、前記第 1 電圧信号を前記第 1 トランジスタの制御電極が接続する第 1 ノードに供給する第 1 駆動回路と、

前記第 2 入力端子に入力される第 2 入力信号に基づいて、前記第 2 電圧信号を前記第 1 ノードに供給する第 2 駆動回路と、

前記第 1 ノードを入力端とし、前記第 2 トランジスタの制御電極が接続する第 2 ノードを出力端とするインバータとを備え、

前記第 1 駆動回路は、

前記第 1 ノードと前記第 1 電圧信号端子との間に直列に接続し、制御電極が共に前記第 1 入力端子に接続した複数の第 3 トランジスタを含み

20

前記第 2 駆動回路は、

前記第 1 ノードと前記第 2 電圧信号端子との間に直列に接続し、制御電極が共に前記第 2 入力端子に接続した複数の第 4 トランジスタを含み、

前記複数の第 3 トランジスタ間の接続ノードの各々である第 1 接続ノードにおいて、

前記第 1 入力端子と前記第 1 接続ノードとの間の容量成分を C 1 、当該 C 1 に含まれない前記第 1 接続ノードに付随する寄生容量を C 2 、前記第 1 入力信号の H レベルと L レベルとの差を V d 、前記第 3 トランジスタのしきい値電圧を V t h とすると、

$$C_1 = C_2 \times (V_d - V_{th}) / V_{th}$$

の関係を満たし、

30

前記複数の第 4 トランジスタ間の接続ノードの各々である第 2 接続ノードにおいて、

前記第 2 入力端子と前記第 2 接続ノードとの間の容量成分を C 1 a 、当該 C 1 a に含まれない前記第 2 接続ノードに付随する寄生容量を C 2 a 、前記第 2 入力信号の H レベルと L レベルとの差を V d a 、前記第 4 トランジスタのしきい値電圧を V t h a とすると、

$$C_{1a} = C_{2a} \times (V_{da} - V_{tha}) / V_{tha}$$

の関係を満たす

ことを特徴とするシフトレジスタ回路。

## 【請求項 4 1】

請求項 4 0 記載のシフトレジスタ回路であって、

前記第 1 駆動回路は、

40

前記第 1 電圧信号が前記第 3 および第 4 トランジスタのしきい値電圧よりも高い H (High) レベルであり、前記第 2 電圧信号が当該第 3 および第 4 トランジスタのしきい値電圧よりも低い L (Low) レベルである場合に、

前記第 1 入力信号が H レベルになると前記複数の第 3 トランジスタがオンすることで前記第 1 ノードを充電し、その後当該第 1 入力信号が L レベルに変化すると前記複数の第 3 トランジスタ間の各接続ノードが L レベルに引き下げられるよう構成されており、

前記第 2 駆動回路は、

前記第 1 電圧信号が L レベルであり、前記第 2 電圧信号が H レベルである場合に、

前記第 2 入力信号が H レベルになると前記複数の第 4 トランジスタがオンすることで前記第 1 ノードを充電し、その後当該第 2 入力信号が L レベルに変化すると前記複数の第 4

50

トランジスタ間の各接続ノードが L レベルに引き下げられるよう構成されていることを特徴とするシフトレジスタ回路。

**【請求項 4 2】**

請求項 4 0 または請求項 4 1 記載のシフトレジスタ回路であって、前記複数の第 3 トランジスタ間の各接続ノードと前記第 1 入力端子との間に接続した第 1 容量素子と、前記複数の第 4 トランジスタ間の各接続ノードと前記第 2 入力端子との間に接続した第 2 容量素子とをさらに備えることを特徴とするシフトレジスタ回路。

**【請求項 4 3】**

請求項 4 0 または請求項 4 1 記載のシフトレジスタ回路であって、前記複数の第 3 トランジスタ間の各接続ノードと前記第 1 入力端子との間に、前記第 1 入力端子側をカソード、当該複数の第 3 トランジスタ間の接続ノード側をアノードとして接続された第 1 ダイオードと、前記複数の第 4 トランジスタ間の各接続ノードと前記第 2 入力端子との間に、前記第 2 入力端子側をカソード、当該複数の第 4 トランジスタ間の接続ノード側をアノードとして接続された第 2 ダイオードとをさらに備えることを特徴とするシフトレジスタ回路。

**【請求項 4 4】**

請求項 4 0 または請求項 4 1 記載のシフトレジスタ回路であって、前記複数の第 3 トランジスタ間の各接続ノードと前記第 1 入力端子との間に、制御電極が前記クロック端子に接続した第 5 トランジスタをさらに備える前記複数の第 4 トランジスタ間の各接続ノードと前記第 2 入力端子との間に、制御電極が前記クロック端子に接続した第 6 トランジスタをさらに備えることを特徴とするシフトレジスタ回路。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、トランジスタの電気的特性の劣化による誤動作を防止する技術に関するものであり、特に、非晶質シリコン薄膜トランジスタや有機トランジスタ等のしきい値電圧のマイナスシフトを抑制することを可能とする半導体装置に関するものである。 30

**【背景技術】**

**【0002】**

液晶表示装置等の画像表示装置において、表示パネルを走査するためのゲート線駆動回路（走査線駆動回路）としては、表示信号の 1 フレーム期間で一巡するシフト動作を行うシフトレジスタを用いることができる。当該シフトレジスタは、表示装置の製造プロセスにおける工程数を少なくするために、同一導電型の電界効果トランジスタのみで構成されることが望ましい。

**【0003】**

ゲート線駆動回路のシフトレジスタを非晶質シリコン薄膜トランジスタ（以下「a - Si トランジスタ」）で構成した表示装置は、大面積化が容易で且つ生産性が高く、例えばノート型 PC の画面や、大画面ディスプレイ装置などに広く採用されている。 40

**【0004】**

その反面、a - Si トランジスタは、ゲート電極が継続的（直流的）にバイアスされるとそのしきい値電圧がシフトするという特性を有していることが知られている。また、下記の非特許文献 1 で示されているように、一般的に a - Si トランジスタは、進行性の劣化を有する。

**【0005】**

また、トランジスタのしきい値電圧のシフト（V<sub>t h</sub> シフト）は回路の誤動作の原因となるため、その対策が施されたシフトレジスタが種々提案されている（例えば特許文献 1 50

)。このV<sub>t h</sub>シフトの問題は、a-Siトランジスタのみならず有機トランジスタにおいても同様に生じることが分かっている。

### 【0006】

【特許文献1】特開2006-107692号公報

【非特許文献1】R. B. Wehrspohn etc, "Relative importance of the Si-Si bond and Si-H bond for the stability of amorphous silicon thin film transistors" Journal of applied physics vol.87 pp. 144-154

### 【発明の開示】

【発明が解決しようとする課題】

### 【0007】

a-Siトランジスタのしきい値電圧は、ゲートがドレインおよびソースの両方に対しで低い電位状態が続くと、時間の経過と共に負(マイナス)方向へシフトする。a-Siトランジスタのしきい値電圧が負方向にシフトすると、そのゲート・ソース間電位を小さくして当該a-Siトランジスタをオフ(非導通状態)にしようとしても完全なオフ状態にはならなくなる。つまりa-Siトランジスタが電流を完全に遮断することができなくなり、それによって回路の誤動作が生じる。

### 【0008】

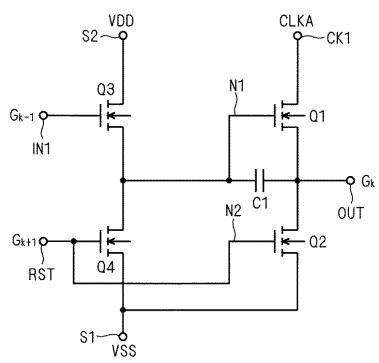

シフトレジスタは、クロック信号を出力端子に供給して当該出力端子の電位をプルアップする出力プルアップトランジスタ(図1のトランジスタQ1)と、当該出力プルアップトランジスタのゲートノード(同図のノードN1)を充電するための充電トランジスタ(同図のトランジスタQ3)とを備えている。詳細は後述するが、シフトレジスタの通常動作においては、その充電トランジスタが、一定の期間、上記の電位状態(トランジスタのゲート電位がドレイン電位およびソース電位の両方に対して低い状態)になるので、しきい値電圧が負方向にシフトして誤動作を引き起こすという問題が生じていた。

### 【0009】

本発明は以上のような課題を解決するためになされたものであり、しきい値電圧の負方向シフト(マイナスシフト)を抑制することが可能なトランジスタを提供し、シフトレジスタをはじめとする半導体装置の誤動作を防止することを目的とする。

### 【課題を解決するための手段】

### 【0010】

本発明に係る半導体装置は、所定の第1ノードと第2ノードとの間に直列に接続し、制御電極が相互に接続した複数のトランジスタを備える半導体装置であって、前記複数のトランジスタ間の接続ノードの各々を第3ノードとし、前記第1～第3ノードおよび前記制御電極のそれぞれが前記複数のトランジスタのしきい値電圧よりも高いH(High)レベルになった状態から、前記第1および第2ノードがHレベルのまま前記制御電極の電位が前記しきい値電圧よりも低いL(Low)レベルに変化すると、それに応じて前記第3ノードのレベルもLレベルに引き下げられるよう構成されており、前記第3ノードの各々において、前記制御電極と前記第3ノードとの間の容量成分をC1、当該C1に含まれない前記第3ノードに付随する寄生容量をC2、前記制御電極におけるHレベルとLレベルとの差をVd、前記第1トランジスタのしきい値電圧をVthとすると、 $C_1 - C_2 \times (V_d - V_{th}) / V_{th}$ の関係を満たすものである。

### 【0011】

本発明に係るシフトレジスタ回路の第1の態様によれば、シフトレジスタ回路は、入力端子、出力端子、第1クロック端子およびリセット端子と、前記第1クロック端子に入力される第1クロック信号を前記出力端子に供給する第1トランジスタと、前記出力端子を放電する第2トランジスタと、前記入力端子に入力される入力信号に応じて前記第1トランジスタの制御電極が接続する第1ノードを充電する充電回路と、前記リセット端子に入力されるリセット信号に応じて前記第1ノードを放電する放電回路とを備え、前記充電回路が、前記第1ノードと電源端子との間に直列に接続し、制御電極が共に前記入力端子に接続した複数の第3トランジスタを含み、前記入力信号が第3トランジスタのしきい値電

10

20

30

40

50

圧よりも高いH (High) レベルになると前記複数の第3トランジスタがオンすることで前記第1ノードを充電し、その後当該入力信号が前記しきい値電圧よりも低いL (Low) レベルに変化すると前記複数の第3トランジスタ間の各接続ノードがLレベルに引き下げられるよう構成されており、前記複数の第3トランジスタ間の接続ノードの各々において、前記入力端子と前記接続ノードとの間の容量成分をC1、当該C1に含まれない前記接続ノードに付随する寄生容量をC2、前記入力信号のHレベルとLレベルとの差をVd、前記第3トランジスタのしきい値電圧をVthとすると、 $C_1 - C_2 \times (V_d - V_{th}) / V_{th}$ の関係を満たすものである。

#### 【発明の効果】

#### 【0012】

10

本発明の第1の態様に係る半導体装置によれば、直列接続した上記トランジスタの各々において、ソースおよびドレインの両方がHレベル、制御電極がLレベルとなる電位状態が防止されるので、当該トランジスタのしきい値電圧が負方向にシフトすることが防止される。それにより、制御電極をLレベルにしたときに、各トランジスタを確実にオフ（遮断状態）にすることができるので、半導体装置の誤動作が防止される。

#### 【0013】

本発明に係るシフトレジスタ回路の第1の態様によれば、第1トランジスタの制御電極の充電回路を構成するトランジスタの各々において、ソースおよびドレインの両方がHレベル、制御電極がLレベルとなる電位状態が防止されるので、当該トランジスタのしきい値電圧が負方向にシフトすることが防止される。それにより、充電回路の制御電極をLレベルにしたときに当該充電回路を確実にオフ（遮断状態）にすることができるので、第1トランジスタが不要にオンするのを防止でき、シフトレジスタ回路の誤動作が防止される。

20

#### 【発明を実施するための最良の形態】

#### 【0014】

以下、本発明の実施の形態を図面を参照しながら説明する。なお、説明が重複して冗長になるのを避けるため、各図において同一または相当する機能を有する要素には同一符号を付してある。

#### 【0015】

30

##### <実施の形態1>

まず、本発明の説明を容易にするために、従来のシフトレジスタについて説明する。通常、シフトレジスタは、複数のシフトレジスタ回路が縦続接続（カスケード接続）して成る多段構造を有している。本明細書では、多段のシフトレジスタを構成する各段のシフトレジスタ回路の各々を「単位シフトレジスタ」と称する。

#### 【0016】

先に述べたように、シフトレジスタは表示装置のゲート線駆動回路として使用することが可能である。シフトレジスタをゲート線駆動回路として用いた表示装置の具体的な構成例は、本発明者らによる特許文献（例えば、特開2006-277860の図1、図2等）に開示されている。以下では、回路の基準電圧である低電位側電源電位（VSS）を0Vとして説明するが、実際の表示装置では、画素に書き込まれるデータの電圧を基準にして基準電位が設定されるため、例えば低電位側電源電位（VSS）は-12V、高電位側電源電位（VDD）は17Vなどと設定される。

40

#### 【0017】

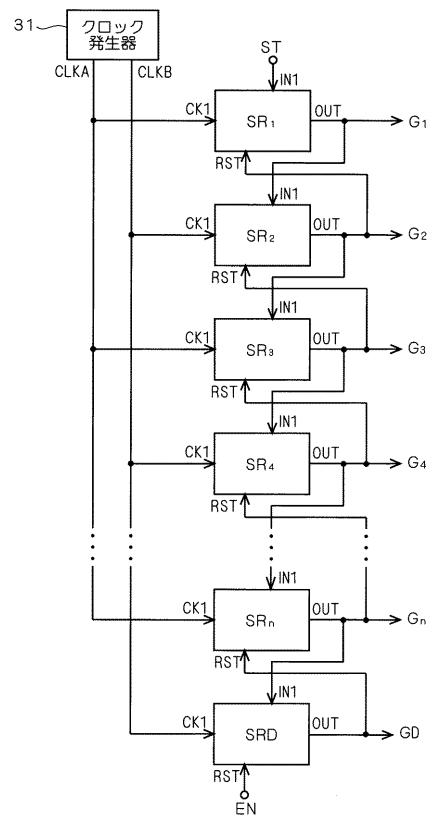

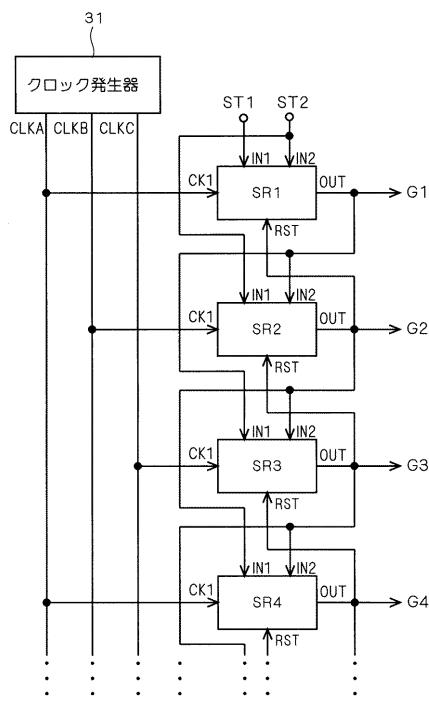

図1は、従来の単位シフトレジスタの構成を示す回路図である。また図2は多段のシフトレジスタの構成を示す図である。図2のシフトレジスタは、縦続接続したn個の単位シフトレジスタSR<sub>1</sub>, SR<sub>2</sub>, SR<sub>3</sub>, ..., SR<sub>n</sub>と、最後段の単位シフトレジスタSR<sub>n</sub>のさらに後段に設けられたダミーの単位シフトレジスタSRDとから成っている（以下、単位シフトレジスタSR<sub>1</sub>, SR<sub>2</sub>, ..., SR<sub>n</sub>, SRDを「単位シフトレジスタSR」と総称する）。従来のシフトレジスタにあっては、単位シフトレジスタSRのそれぞれが図1の回路となる。

50

**【0018】**

また図2に示すクロック発生器31は、互いに逆相の（活性期間が重ならない）2相のクロック信号CLKA, CLKBを複数の単位シフトレジスタSRに供給するものである。ゲート線駆動回路では、これらクロック信号CLKA, CLKBは、表示装置の走査周期に同期したタイミングで順番に活性化するよう制御される。

**【0019】**

図1および図2に示すように、各単位シフトレジスタSRは、入力端子IN1、出力端子OUT、クロック端子CK1およびリセット端子RSTを有している。また各単位シフトレジスタSRには、第1電源端子S1を介して低電位側電源電位VSS（＝0V）が供給され、第2電源端子S2を介して高電位側電源電位VDDがそれぞれ供給される（図2では不図示）。

10

**【0020】**

図1の如く、単位シフトレジスタSRの出力段は、出力端子OUTとクロック端子CK1との間に接続するトランジスタQ1と、出力端子OUTと第1電源端子S1との間に接続するトランジスタQ2により構成されている。即ち、トランジスタQ1は、クロック端子CK1に入力されるクロック信号CLKAを出力端子OUTに供給するトランジスタ（第1トランジスタ）であり、トランジスタQ2は当該出力端子OUTを放電するトランジスタ（第2トランジスタ）である。以下、トランジスタQ1のゲート（制御電極）が接続するノードを「ノードN1」、トランジスタQ2のゲートが接続するノードを「ノードN2」と定義する。

20

**【0021】**

トランジスタQ1のゲート・ソース間（即ちノードN1と出力端子OUTとの間）には容量素子C1が設けられている。この容量素子C1は、出力端子OUTとノードN1との間を容量結合させ、出力端子OUTのレベル上昇に応じてノードN1を昇圧させる素子（ブーストストラップ容量）である。但し、容量素子C1は、トランジスタQ1のゲート・チャネル間容量が充分大きい場合にはそれで置き換えることができるので、そのような場合には省略してもよい。

**【0022】**

ノードN1と第2電源端子S2との間には、ゲートが入力端子IN1に接続したトランジスタQ3が接続する。またノードN1と第1電源端子S1との間には、ゲートがリセット端子RSTに接続したトランジスタQ4が接続する。即ちトランジスタQ3は、入力端子IN1に入力される信号に応じてノードN1を充電する充電回路を構成しており、トランジスタQ4はリセット端子RSTに入力される信号に応じてノードN1を放電する放電回路を構成している。この従来例においては、トランジスタQ2のゲート（ノードN2）もリセット端子RSTに接続されている。

30

**【0023】**

図2の如く、各単位シフトレジスタSRの入力端子IN1には、その前段の単位シフトレジスタSRの出力端子OUTが接続する。但し、第1段目である単位シフトレジスタSR1の入力端子IN1には、所定のスタートパルスSTが入力される。また、各単位シフトレジスタSRのクロック端子CK1には、前後に隣接する単位シフトレジスタSRに互いに異なる位相のクロック信号が入力されるよう、クロック信号CLKA, CLKBの片方が入力される。

40

**【0024】**

そして各単位シフトレジスタSRのリセット端子RSTには、自己の次段の単位シフトレジスタSRの出力端子OUTが接続される。但し、最後段の単位シフトレジスタSRnの次段に設けられたダミーの単位シフトレジスタSRDのリセット端子RSTには、所定のエンドパルスENが入力される。なおゲート線駆動回路では、スタートパルスSTおよびエンドパルスENは、それぞれ画像信号の各フレーム期間の先頭および末尾に対応するタイミングで入力される。

**【0025】**

50

次に図1に示した従来の各単位シフトレジスタSRの動作を説明する。基本的に各段の単位シフトレジスタSRは全て同様に動作するので、ここでは多段のシフトレジスタのうち第k段目の単位シフトレジスタSR<sub>k</sub>の動作を代表的に説明する。当該単位シフトレジスタSR<sub>k</sub>のクロック端子CK1にはクロック信号CLKAが入力されているものとする（例えば、図2における単位シフトレジスタSR<sub>1</sub>, SR<sub>3</sub>などがこれに該当する）。

#### 【0026】

ここで、クロック信号CLKA, CLKBのHレベルの電位はVDD（高電位側電源電位）であり、Lレベルの電位はVSS（低電位側電源電位）であるとする。また単位シフトレジスタSRを構成する各トランジスタQ<sub>x</sub>のしきい値電圧をV<sub>th</sub>(Q<sub>x</sub>)と表すことにとする。

10

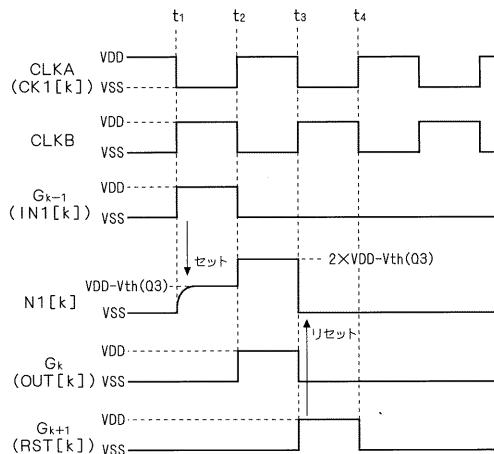

#### 【0027】

図3は、従来の単位シフトレジスタSR<sub>k</sub>（図1）の動作を示すタイミング図である。まず単位シフトレジスタSR<sub>k</sub>の初期状態として、ノードN1がLレベルの状態を仮定する（以下、ノードN1がLレベルの状態を「リセット状態」と称す）。また入力端子IN1（前段の出力信号G<sub>k-1</sub>）、リセット端子RST（次段の出力信号G<sub>k+1</sub>）、クロック端子CK1（クロック信号CLKA）は何れもLレベルであるとする。このときトランジスタQ1, Q2は共にオフであるので出力端子OUTが高インピーダンス状態（フローティング状態）となっているが、当該初期状態では出力端子OUT（出力信号G<sub>k</sub>）もLレベルであるとする。

#### 【0028】

その状態から時刻t<sub>1</sub>において、クロック信号CLKAがLレベル、クロック信号CLKBがHレベルに変化すると共に、前段の出力信号G<sub>k-1</sub>（第1段目の場合はスタートパルスST）がHレベルになると、単位シフトレジスタSR<sub>k</sub>のトランジスタQ3がオンになり、ノードN1は充電されてHレベルになる（以下、ノードN1がHレベルの状態を「セット状態」と称す）。このときノードN1の電位レベル（以下、単に「レベル」と称す）はVDD - V<sub>th</sub>(Q3)まで上昇する。応じて、トランジスタQ1がオンになる。

20

#### 【0029】

そして時刻t<sub>2</sub>において、クロック信号CLKBがLレベル、クロック信号CLKAがHレベルに変化するのと共に、前段の出力信号G<sub>k-1</sub>がLレベルになる。するとトランジスタQ3がオフになりノードN1がHレベルのままフローティング状態になる。またトランジスタQ1がオンしているので、出力端子OUTのレベルがクロック信号CLKAに追随して上昇する。

30

#### 【0030】

クロック端子CK1および出力端子OUTのレベルが上昇すると、容量素子C1およびトランジスタQ1のゲート・チャネル間容量を介する結合により、ノードN1のレベルは図3に示すように昇圧される。このときの昇圧量は、ほぼクロック信号CLKAの振幅（VDD）に相当するので、ノードN1はおよそ2×VDD - V<sub>th</sub>(Q3)まで昇圧される。

#### 【0031】

その結果、出力信号G<sub>k</sub>がHレベルとなる間も、トランジスタQ1のゲート（ノードN1）・ソース（出力端子OUT）間の電圧は大きく保たれる。つまりトランジスタQ1のオン抵抗は低く保たれるので、出力信号G<sub>k</sub>はクロック信号CLKAに追随して高速に立ち上がってHレベルになる。またこのときトランジスタQ1は線形領域（非飽和領域）で動作するので、出力信号G<sub>k</sub>のレベルはクロック信号CLKAの振幅と同じVDDまで上昇する。

40

#### 【0032】

さらに時刻t<sub>3</sub>においてクロック信号CLKBがHレベル、クロック信号CLKAがLレベルに変化するときも、トランジスタQ1のオン抵抗は低く保たれ、出力信号G<sub>k</sub>はクロック信号CLKAに追随して高速に立ち下がって、Lレベルに戻る。

#### 【0033】

50

またこの時刻  $t_3$  では、次段の出力信号  $G_{k+1}$  が H レベルになるので、単位シフトレジスタ  $S R_k$  のトランジスタ  $Q_2, Q_4$  がオンになる。それにより、出力端子  $O U T$  はトランジスタ  $Q_2$  を介して充分に放電され、確実に L レベル ( $V_{SS}$ ) にされる。またノード  $N_1$  は、トランジスタ  $Q_4$  により放電されて L レベルになる。即ち、単位シフトレジスタ  $S R_k$  はリセット状態に戻る。

#### 【0034】

そして時刻  $t_4$  で次段の出力信号  $G_{k+1}$  が L レベルに戻った後は、次に前段の出力信号  $G_{k-1}$  が入力されるまで、単位シフトレジスタ  $S R_k$  はリセット状態に維持され、出力信号  $G_k$  は L レベルに保たれる。

#### 【0035】

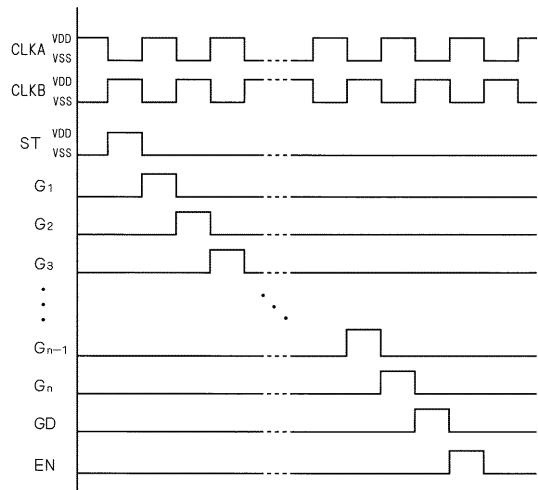

以上の動作をまとめると、単位シフトレジスタ  $S R_k$  は、入力端子  $I N_1$  に信号（スタートパルス  $S P$  または前段の出力信号  $G_{k-1}$ ）が入力されない期間はリセット状態であり、トランジスタ  $Q_1$  がオフを維持するため、出力信号  $G_k$  は L レベル ( $V_{SS}$ ) に維持される。そして入力端子  $I N_1$  に信号が入力されると、単位シフトレジスタ  $S R_k$  はセット状態に切り替わる。セット状態ではトランジスタ  $Q_1$  がオンになるため、クロック端子  $C K_1$  の信号（クロック信号  $C L K A$ ）が H レベルになる間、出力信号  $G_k$  が H レベルになる。そしてその後、リセット端子  $R S T$  に信号（次段の出力信号  $G_{k+1}$  またはエンドパルス  $E N$ ）が入力されると、元のリセット状態に戻る。

#### 【0036】

このように動作する複数の単位シフトレジスタ  $S R$  から成る多段のシフトレジスタによれば、第 1 段目の単位シフトレジスタ  $S R_1$  にスタートパルス  $S T$  が入力されると、それを切っ掛けにして、出力信号  $G$  がクロック信号  $C L K A, C L K B$  に同期したタイミングでシフトされながら、図 4 の如く単位シフトレジスタ  $S R_1, S R_2, S R_3 \dots$  と順番に伝達される。ゲート線駆動回路では、このように順番に出力される出力信号  $G$  が表示パネルの水平（又は垂直）走査信号として用いられる。

#### 【0037】

以下、特定の単位シフトレジスタ  $S R$  が出力信号  $G$  を出力する期間を、その単位シフトレジスタ  $S R$  の「選択期間」と称する。

#### 【0038】

なお、ダミーの単位シフトレジスタ  $S R D$  は、最後段の単位シフトレジスタ  $S R_n$  が出力信号  $G_n$  を出力した直後に、その出力信号  $G_D$  によって単位シフトレジスタ  $S R_n$  をリセット状態にするために設けられている。例えばゲート線駆動回路であれば、最後段の単位シフトレジスタ  $S R_n$  を出力信号  $G_n$  の出力直後にリセット状態にしなければ、それに対応するゲート線（走査線）が不要に活性化され、表示の不具合が生じてしまう。

#### 【0039】

なお、ダミーの単位シフトレジスタ  $S R D$  は、出力信号  $G_D$  を出力した後のタイミングで入力されるエンドパルス  $E N$  によってリセット状態にされる。ゲート線駆動回路のように、信号のシフト動作が繰り返して行われる場合には、エンドパルス  $E N$  に代えて次のフレーム期間のスタートパルス  $S T$  を用いてもよい。

#### 【0040】

また、図 2 のように 2 相クロックを用いた駆動の場合、単位シフトレジスタ  $S R$  のそれぞれは、自己の次段の出力信号  $G$  によってリセット状態にされるので、次段の単位シフトレジスタ  $S R$  が少なくとも一度動作した後でなければ、図 3 および図 4 に示したような通常動作を行うことができない。従って、通常動作に先立って、ダミーの信号を第 1 段目から最終段まで伝達させるダミー動作を行わせる必要がある。あるいは、各単位シフトレジスタ  $S R$  のリセット端子  $R S T$ （ノード  $N_2$ ）と第 2 電源端子  $S_2$ （高電位側電源）との間にリセット用のトランジスタを別途設け、通常動作の前に強制的にノード  $N_2$  を H レベルにするリセット動作を行ってもよい。但し、その場合はリセット用の信号ラインが別途必要になる。

#### 【0041】

10

20

30

40

50

ここで、先に述べた従来の単位シフトレジスタ S R における、a - S i トランジスタのしきい値電圧の負方向シフトの問題を詳細に説明する。

#### 【 0 0 4 2 】

図 3 のタイミング図から分かるように、単位シフトレジスタ S R<sub>k</sub> のノード N 1 は、前段の出力信号 G<sub>k-1</sub> が H レベルになると H レベル ( V D D - V t h ( Q 3 ) ) に充電され ( 時刻 t<sub>1</sub> ) 、その後に前段の出力信号 G<sub>k-1</sub> が L レベルに戻っても ( 時刻 t<sub>2</sub> ) 、フローティング状態で H レベルに維持される。しかも出力信号 G が H レベルである間 ( 選択期間 : 時刻 t<sub>2</sub> ~ 時刻 t<sub>3</sub> ) 、ノード N 1 は  $2 \times V D D - V t h ( Q 3 )$  のレベルにまで昇圧される。

#### 【 0 0 4 3 】

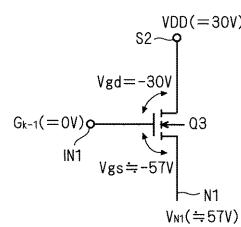

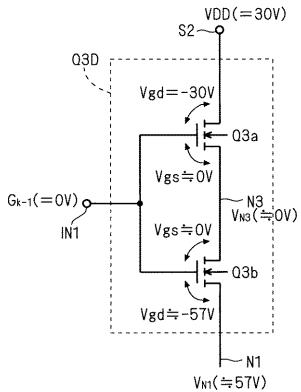

つまり各単位シフトレジスタ S R において、その選択期間ではトランジスタ Q 3 のドレン ( 第 2 電源端子 S 2 ) は V D D 、ソース ( ノード N 1 ) は  $2 \times V D D - V t h ( Q 3 )$  、ゲート ( 入力端子 I N 1 ) は V S S のレベルであり、ゲートがソースおよびドレンの両方に対して負にバイアスされた状態となる。例えば V S S = 0 V 、 V D D = 3 0 V と仮定すると図 5 に示すように、トランジスタ Q 3 のゲート・ドレン間電圧 V g d は - 3 0 V 、ゲート・ソース間電圧 V g s は - 5 7 V 程度となる。

#### 【 0 0 4 4 】

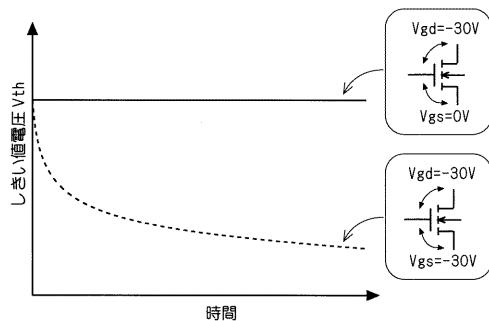

図 6 は、a - S i トランジスタの電位状態としきい値電圧のシフトとの関係を表した実験結果を示す図である。同図に破線で示したように、a - S i トランジスタのゲートがドレンおよびソースの両方に対して低い電位の状態になると、そのしきい値電圧は時間とともに負 ( マイナス ) 方向へシフトする。従って、従来の単位シフトレジスタ S R においては、その選択期間にトランジスタ Q 3 にしきい値電圧の負方向シフトが生じることとなる。

#### 【 0 0 4 5 】

単位シフトレジスタ S R において、トランジスタ Q 3 のしきい値電圧が負方向にシフトすると、入力端子 I N 1 が L レベルのときでもトランジスタ Q 3 に電流が流れようになり、非選択期間にノード N 1 へ電荷が供給され、そのレベルが上昇する。そうなると、非選択期間であるにもかかわらず、単位シフトレジスタ S R のトランジスタ Q 1 がオンし、その出力端子 O U T から誤信号としての出力信号 G が出力されるという誤動作が生じるため問題となる。

#### 【 0 0 4 6 】

それに対し、a - S i トランジスタのゲートがドレンに対して低い電位であっても、ゲートとソースとがほぼ同電位の状態であれば、しきい値電圧のシフトは軽減される。例えば図 6 において実線で示すように、ゲートがドレンに対して低い電位であっても、ゲート・ソース間の電圧を 0 V にすれば、しきい値電圧のシフトは殆ど生じない。

#### 【 0 0 4 7 】

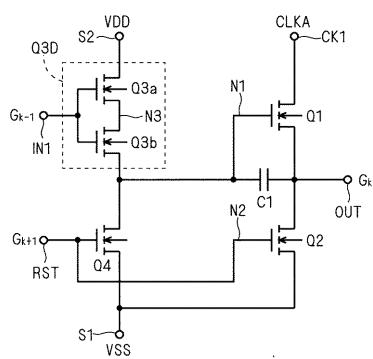

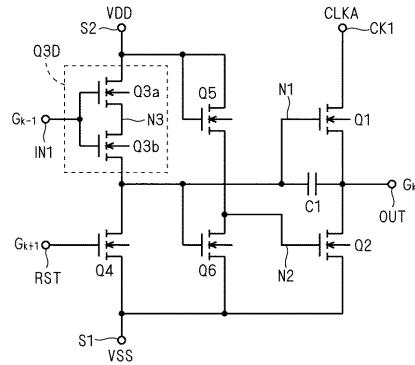

以下、上記の問題を解決することができる、本発明に係るシフトレジスタ回路について説明する。図 7 は、本発明の実施の形態 1 に係る単位シフトレジスタ S R の回路図である。当該単位シフトレジスタ S R は、図 1 の回路に対し、トランジスタ Q 3 をデュアルゲートトランジスタ Q 3 D に置き換えたものである。それ以外の構成は図 1 と同様であるので、ここでの詳細な説明は省略する。

#### 【 0 0 4 8 】

なお本明細書における「デュアルゲートトランジスタ」とは、直列に接続した 2 つのトランジスタであって、両者のゲートが相互に接続したものという。即ち、デュアルゲートトランジスタ Q 3 D は、ノード N 1 と第 2 電源端子 S 2 との間に直列接続したトランジスタ Q 3 a , Q 3 b により構成されており、それらトランジスタ Q 3 a , Q 3 b のゲートは共に入力端子 I N 1 に接続されている。ここで、トランジスタ Q 3 a とトランジスタ Q 3 b との間の接続ノードを「ノード N 3」と定義する。

#### 【 0 0 4 9 】

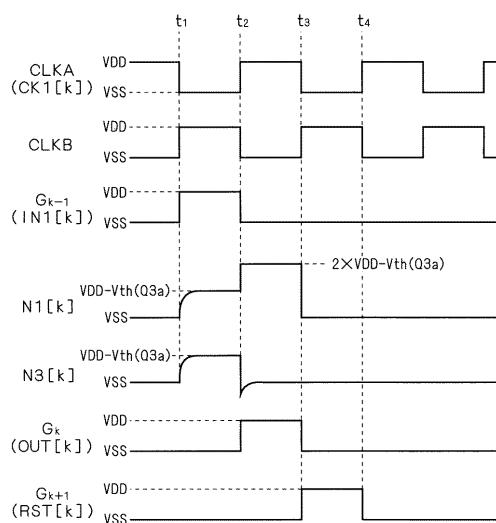

図 8 は、図 7 の単位シフトレジスタ S R の動作を示すタイミング図である。ここでも

10

20

30

40

50

第  $k$  段目の単位シフトレジスタ  $S R_k$  について代表的に説明する。また単位シフトレジスタ  $S R_k$  の初期状態として、ノード  $N 1$  が L レベルのリセット状態を仮定し、またクロック端子  $C K 1$  (クロック信号  $C L K A$ )、リセット端子  $R S T$  (次段の出力信号  $G_{k+1}$ )、入力端子  $I N 1$  (前段の出力信号  $G_{k-1}$ )、出力端子  $O U T$  (出力信号  $G_k$ ) が L レベルであるとする。

#### 【0050】

その状態から時刻  $t_1$ において、クロック信号  $C L K A$  が L レベル、クロック信号  $C L K B$  が H レベルに変化すると共に、前段の出力信号  $G_{k-1}$  (第 1 段目の場合はスタートパルス  $S T$ ) が H レベルになると、単位シフトレジスタ  $S R_k$  のデュアルゲートトランジスタ  $Q 3 D$  を構成するトランジスタ  $Q 3 a$ ,  $Q 3 b$  が共にオンになり、ノード  $N 1$  は充電されて H レベルになる。即ち、単位シフトレジスタ  $S R_k$  はセット状態となる。このときノード  $N 1$ ,  $N 3$  のレベルは、共に  $V D D - V t h (Q 3 a)$  まで上昇する。応じて、トランジスタ  $Q 1$  がオンになる。10

#### 【0051】

そして時刻  $t_2$ においてクロック信号  $C L K B$  が L レベル、クロック信号  $C L K A$  が H レベルに変化すると共に、前段の出力信号  $G_{k-1}$  が L レベルになると、トランジスタ  $Q 3 a$ ,  $Q 3 b$  がオフになりノード  $N 1$  はフローティング状態で H レベルに維持される。そのためトランジスタ  $Q 1$  はオン状態に保たれ、出力信号  $G_k$  がクロック信号  $C L K A$  に追随して H レベルになる。このときノード  $N 1$  のレベルは、およそ  $2 \times V D D - V t h (Q 3 a)$  にまで昇圧される。20

#### 【0052】

本実施の形態においては、デュアルゲートトランジスタ  $Q 3 D$  を構成するトランジスタ  $Q 3 a$ ,  $Q 3 b$  のそれぞれは、大きなゲート・ソースオーバラップ容量を有するものが用いられる (トランジスタ  $Q 3 a$ ,  $Q 3 b$  のゲート・ソースオーバラップ容量を大きくする手法については、実施の形態 9において説明する)。そのため第 1 入力端子  $I N 1$  とノード  $N 3$  との間の寄生容量は大きく、時刻  $t_2$  でクロック信号  $C L K B$  が L レベルになるとには、当該寄生容量を介した結合により、ノード  $N 3$  のレベルは L レベル (即ちトランジスタ  $Q 3 a$ ,  $Q 3 b$  のしきい値電圧よりも低いレベル) に引き下げられる。入力端子  $I N 1$  とノード  $N 3$  との間の容量成分が充分大きければ、時刻  $t_2$  では図 8 の如くノード  $N 3$  のレベルはほぼ  $V S S$  まで引き下げられる。30

#### 【0053】

なお、このとき電位関係から、トランジスタ  $Q 3 a$  においては第 2 電源端子  $S 2$  側がドレイン、ノード  $N 3$  側がソースとなり、トランジスタ  $Q 3 b$  においてはノード  $N 1$  側がドレイン、ノード  $N 3$  側がソースとなる。

#### 【0054】

続いて時刻  $t_3$ においてクロック信号  $C L K B$  が H レベル、クロック信号  $C L K A$  が L レベルに変化すると、出力信号  $G_k$  は L レベルに戻る。それと共に次段の出力信号  $G_{k+1}$  が H レベルになるので、単位シフトレジスタ  $S R_k$  のトランジスタ  $Q 2$ ,  $Q 4$  がオンになり、単位シフトレジスタ  $S R_k$  はリセット状態に戻る。

#### 【0055】

そして時刻  $t_4$ で次段の出力信号  $G_{k+1}$  が L レベルになった後は、次に前段の出力信号  $G_{k-1}$  が入力されるまで、単位シフトレジスタ  $S R_k$  はリセット状態に維持され、出力信号  $G_k$  は L レベルに保たれる。40

#### 【0056】

以上のように本実施の形態に係る単位シフトレジスタ  $S R$  の信号のシフト動作は、ほぼ従来のもの (図 1) と同様であり、それで構成された多段のシフトレジスタは、図 4 で説明したとおりの動作が可能である。

#### 【0057】

本実施の形態においては、上記したように、時刻  $t_2$  にて前段の出力信号  $G_{k-1}$  が立ち下がるのに応じてノード  $N 3$  が L レベルに引き下げられる。そのため時刻  $t_2$  ~ 時刻  $t_3$  の間50

(選択期間)においては、トランジスタQ3aはゲート(入力端子IN1)およびソース(ノードN3)がVSS、ドレイン(第2電源端子S2)がVDDという電位状態となり、トランジスタQ3aはゲート(入力端子IN1)およびソース(ノードN3)がVSS、ドレイン(ノードN1)が $2 \times VDD - V_{th}(Q3a)$ という電位状態となる。

#### 【0058】

つまり本実施の形態に係る単位シフトレジスタSRでは、トランジスタQ3a, Q3bの両方のゲート・ソース間の電圧は、選択期間の間ほぼ0Vとなる。例えばVSS = 0V、VDD = 30Vと仮定すると図9に示すように、トランジスタQ3aのゲート・ドレイン間電圧Vgdは-30V、ゲート・ソース間電圧Vgsは約0Vとなり、またトランジスタQ3bのゲート・ドレイン間電圧Vgdは約-57V、ゲート・ソース間電圧Vgsは約0Vになる。10

#### 【0059】

図6において実線で示したように、a-Siトランジスタは、ゲートがドレインに対して低い電位であっても、ゲートがソースとほぼ同電位(ゲート・ソース間電圧が約0V)の状態であればしきい値電圧のシフトは殆ど生じない。よって本実施の形態の単位シフトレジスタSRにおいては、トランジスタQ3a, Q3bすなわちデュアルゲートトランジスタQ3Dのしきい値電圧の負方向シフトは生じない。従って、非選択期間にデュアルゲートトランジスタQ3Dに電流が流れノードN1のレベルが上昇することを防止でき、それにより誤動作の発生が防止される。20

#### 【0060】

ここで、単位シフトレジスタSRの選択期間において、トランジスタQ3a, Q3bのゲート・ソース間の電圧が0V以下になるための条件(即ち、ノードN3がVSS以下にまで引き下げられる条件)について説明する。ここでもVSS = 0Vとする。即ち、各単位シフトレジスタSRの出力信号Gの振幅(HレベルとLレベルとの差(Vd))はVDDである。20

#### 【0061】

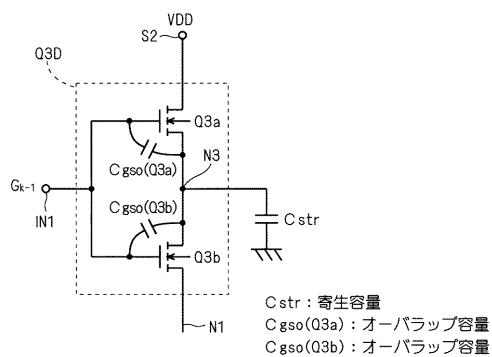

このとき入力端子IN1とノードN3との間の容量成分(C1)をCgsとし、このCgsに含まれないノードN3に付随する寄生容量(C2)をCstrとすると、図8の時刻t<sub>2</sub>に前段の出力信号G<sub>k-1</sub>がHレベル(VDD)からLレベル(VSS = 0V)へと変化したときにおける、単位シフトレジスタSR<sub>k</sub>のノードN3のレベルの変化量は、 $VDD \times Cgs / (Cgs + Cstr)$ で表される。時刻t<sub>2</sub>の直前ではノードN3のレベルはVDD - V<sub>th</sub>(Q3a)となっているので、ノードN3がVSS以下にまで引き下げられるためには、次の式(1)を満たせばよい。30

#### 【0062】

#### 【数1】

$$\frac{Cgs}{Cgs + Cstr} \times VDD \geq VDD - V_{th}$$

$$\therefore Cgs \geq \frac{Cstr \times \{VDD - V_{th}(Q3a)\}}{V_{th}(Q3a)} \dots \text{式(1)} \quad \text{40}$$

#### 【0063】

本実施の形態の単位シフトレジスタSRでは、容量成分Cgsは入力端子IN1とノードN3との間の寄生容量であり、その殆どはトランジスタQ3a, Q3bのゲート・ソースオーバラップ容量である。従って図10に示すように、トランジスタQ3a, Q3bそれぞれのゲート・ソースオーバラップ容量をCgso(Q3a), Cgso(Q3b)とすると、 $Cgs = Cgso(Q3a) + Cgso(Q3b)$ とでき、上記の式(1)は次の式(2)のように変形できる。

#### 【0064】

## 【数2】

$$\frac{C_{gso}(Q3a) + C_{gso}(Q3b)}{C_{gso}(Q3a) + C_{gso}(Q3b) + C_{str}} \times VDD \geq VDD - V_{th}(Q3a)$$

$$\therefore C_{gso}(Q3a) + C_{gso}(Q3b) \geq \frac{C_{str} \times \{VDD - V_{th}(Q3a)\}}{V_{th}(Q3a)} \cdots \text{式(2)}$$

## 【0065】

さらに、トランジスタ Q3a, Q3b それぞれのゲート・ソースオーバラップ容量が互いに等しいと仮定し、その値を  $C_{gso}$  とすると、 $C_{gso} = 2 \times C_{gso}$  であるので、上記の式(1)は次の式(3)のように変形できる。 10

## 【0066】

## 【数3】

$$\frac{2 \times C_{gso}}{2 \times C_{gso} + C_{str}} \times VDD \geq VDD - V_{th}(Q3a)$$

$$\therefore C_{gso} \geq \frac{C_{str} \times \{VDD - V_{th}(Q3a)\}}{2 \times V_{th}(Q3a)} \cdots \text{式(3)} \quad 20$$

## 【0067】

なお本実施の形態においては、ノード N1 と第2電源端子 S2との間に、ゲートが第1入力端子 IN1 に接続したトランジスタを2つ直列接続させた構成を示したが、3つ以上のトランジスタを直列接続させてもよい。その場合、それらのトランジスタ間の各接続ノードにおいて式(1)の条件が満たされれば、非選択期間に各接続ノードは VSS 以下になり、各トランジスタのしきい値電圧の負方向シフトを防止することができる。

## 【0068】

また本実施の形態では、本発明に係るデュアルゲートトランジスタをシフトレジスタ回路に適用した例を示したが、ソースおよびドレインの両方に対してゲートを負バイアスするように動作するトランジスタに広く適用することができる。また本発明は a-Si トランジスタのみならず、有機トランジスタなど、しきい値電圧の負方向シフトの問題を有する各種トランジスタに対しても適用可能である。 30

## 【0069】

## &lt;実施の形態2&gt;

以下の実施の形態においては、本発明に係るデュアルゲートトランジスタを適用可能なシフトレジスタ回路の具体例を示す。

## 【0070】

図11は、実施の形態2に係る単位シフトレジスタ S R の回路図である。当該単位シフトレジスタ S R は、図7の回路に対し、ノード N1 (トランジスタ Q1 のゲート) を入力端とし、ノード N2 (トランジスタ Q2 のゲート) を出力端とするインバータを設けたものである。つまり図7と異なり、トランジスタ Q2 のゲート (ノード N2) はリセット端子 R S T に接続していない。 40

## 【0071】

当該インバータは、ノード N2 と第2電源端子 S2との間にダイオード接続したトランジスタ Q5 と、ノード N2 と第1電源端子 S1との間に接続しゲートがノード N1 に接続したトランジスタ Q6 とから成っている。トランジスタ Q6 は、トランジスタ Q5 よりもオン抵抗が充分に小さく設定されている。

## 【0072】

ノード N1 が L レベルのときは、トランジスタ Q6 がオフするためノード N2 は H レベ 50

ル（VDD - Vth (Q5)）になる。逆にノードN1がHレベルのときは、トランジスタQ5, Q6ともオンするが、ノードN2はトランジスタQ5, Q6のオン抵抗の比により決まる電位（0V）のLレベルになる。つまり、当該インバータはいわゆる「レシオ型インバータ」である。

#### 【0073】

図7の単位シフトレジスタSR<sub>k</sub>においては、次段の出力信号G<sub>k+1</sub>がHレベルになったとき（即ち次段の選択期間）にのみノードN2がHレベルになるので、トランジスタQ2はその期間だけオンして出力端子OUTを低インピーダンスのLレベルにする。そしてそれ以外の非選択期間はトランジスタQ2はオフになっており、出力端子OUTは高インピーダンス（フローティング状態）のLレベルとなる。従って、出力信号G<sub>k</sub>がノイズやリーク電流の影響を受けやすく、動作が不安定になりやすい。10

#### 【0074】

それに対し図11の単位シフトレジスタSR<sub>k</sub>では、ノードN1がLレベルである間、トランジスタQ5, Q6から成るインバータがノードN2をHレベルに維持するので、非選択期間の間じゅう、トランジスタQ2はオン状態に保たれる。つまり、非選択期間における出力端子OUT（出力信号G）が低インピーダンスでLレベルに維持されるので、動作が安定化する。

#### 【0075】

もちろん本実施の形態においても、デュアルゲートトランジスタQ3Dを構成するトランジスタQ3a, Q3bのしきい値電圧の負方向シフトが抑制される効果が得られる。よって、非選択期間にノードN1のレベルが上昇することを防止でき、誤動作の発生を防止することができる。20

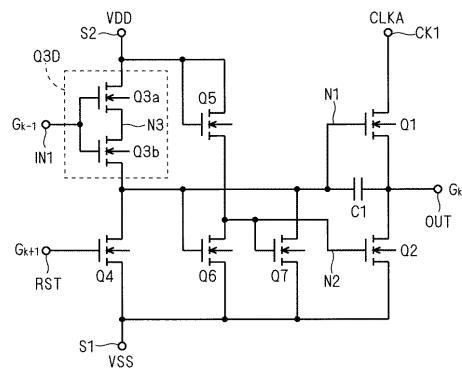

#### 【0076】

##### <実施の形態3>

図12は、実施の形態3に係る単位シフトレジスタSRの回路図である。当該単位シフトレジスタSRは、図11の回路に対し、ノードN1と第1電源端子S1との間に接続し、ゲートがノードN2に接続したトランジスタQ7を設けたものである。即ち、トランジスタQ7は、ノードN2に接続したゲート電極を有し、ノードN1を放電するトランジスタである。

#### 【0077】

図11の単位シフトレジスタSR<sub>k</sub>においては、次段の出力信号G<sub>k+1</sub>がHレベルになったとき（次段の選択期間）に、トランジスタQ4がオンしてノードN1を放電するが、それ以外の非選択期間においてはノードN1は高インピーダンス（フローティング状態）でLレベルとなる。従って、非選択期間にノイズやリーク電流によりノードN1に電荷が供給されると、ノードN1のレベルが上昇する。そうなるとトランジスタQ1がオンし、誤信号として出力信号Gが出力されるという誤動作が生じる。30

#### 【0078】

それに対し図12の単位シフトレジスタSRにおいては、ノードN1がLレベルになると、トランジスタQ5, Q6から成るインバータがノードN2がHレベルにし、応じてトランジスタQ7がオンになるので、ノードN1は非選択期間の間じゅう低インピーダンスでLレベルになる。従って、非選択期間にノードN1のレベルが上昇することが抑制され、上記の誤動作の発生が防止される。40

#### 【0079】

なお、トランジスタQ7は、デュアルゲートトランジスタQ3DがノードN1のレベルを上昇させることができるように、デュアルゲートトランジスタQ3Dよりもオン抵抗が充分大きいものである。

#### 【0080】

本実施の形態においても、デュアルゲートトランジスタQ3Dを構成するトランジスタQ3a, Q3bのしきい値電圧の負方向シフトが抑制される効果が得られる。本実施の形態では、仮に非選択期間にデュアルゲートトランジスタQ3Dに電流がながれてノードN50

1へ電荷が供給されたとしても、その電荷はトランジスタQ7によって第1電源端子S1に放出されるため、それによる誤動作は生じにくくなっている。しかしその電流は、単位シフトレジスタSRの消費電力の増大や、高電位側電源電位VDDの低下を招く。よって、デュアルゲートトランジスタQ3Dのしきい値電圧の負方向シフトを防止することは、本実施の形態においても非常に有効である。

#### 【0081】

##### <実施の形態4>

実施の形態2、3で説明したように、図11および図12の単位シフトレジスタSRにおいては、非選択期間の間トランジスタQ2のゲート（ノードN2）が継続してHレベルになることで、出力端子OUTを低インピーダンスのLレベルにすることができる。しかし、a-Siトランジスタのゲートがソースに対して継続的に正バイアスされると、しきい値電圧が正方向にシフトする。トランジスタQ2でしきい値電圧の正方向シフトが生じると、当該トランジスタQ2のオン抵抗が高くなり、出力端子OUTを充分に低インピーダンスにできなくなるという問題が生じる。

10

#### 【0082】

また図12の単位シフトレジスタSRにおいては、トランジスタQ7のゲートも、非選択期間の間、継続してHレベルになるので、当該トランジスタQ7のしきい値電圧も正方向にシフトし、ノードN1を出力端子OUTを充分に低インピーダンスにできなくなるという問題も生じる。

#### 【0083】

20

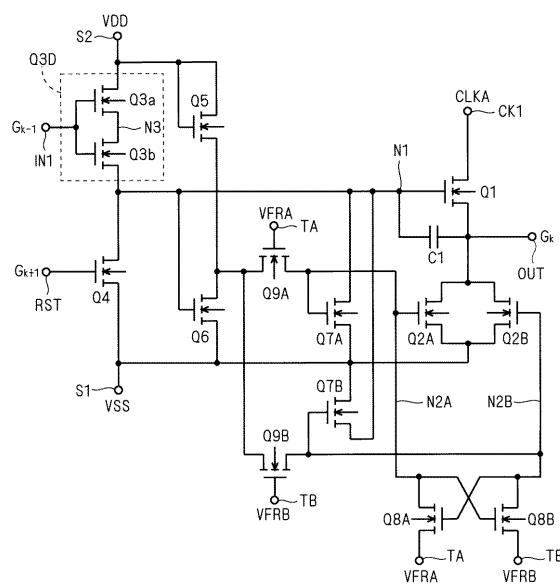

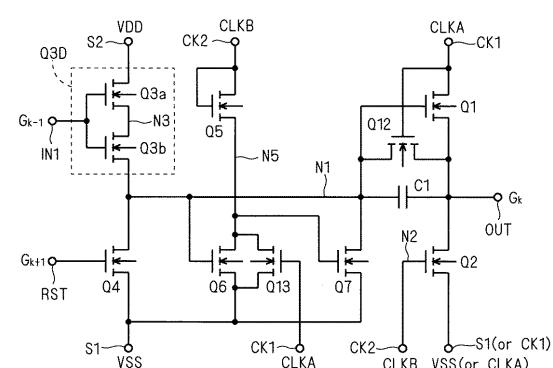

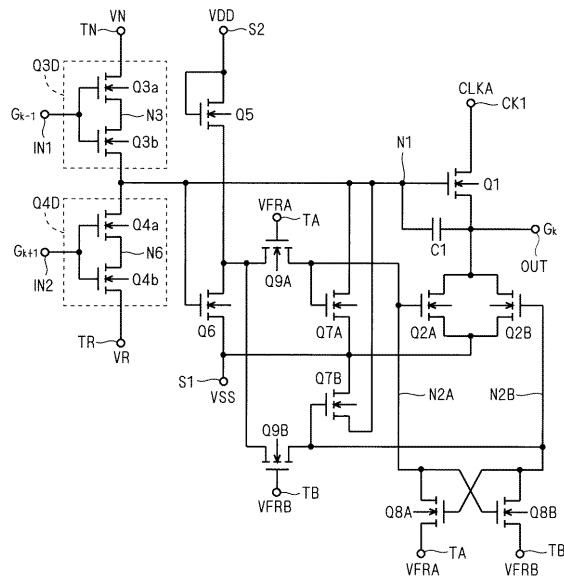

図13は、実施の形態4に係る単位シフトレジスタSRの回路図であり、その問題の対策が施されたものである。図13の単位シフトレジスタSRは、出力端子OUTを放電するトランジスタ（図11および図12のトランジスタQ2に相当する）が並列に2つ設けられている（トランジスタQ2A、Q2B）。ここで、トランジスタQ2A、Q2Bのゲートが接続するノードをそれぞれ「ノードN2A」、「ノードN2B」と定義する。

#### 【0084】

また当該単位シフトレジスタSRには、図12のトランジスタQ7に相当するものが、ノードN2A、N2Bのそれぞれに設けられている（トランジスタQ7A、Q7B）。即ちトランジスタQ7Aは、ノードN2Aに接続したゲート電極を有しノードN1を放電するトランジスタであり、トランジスタQ7Bは、ノードN2Bに接続したゲート電極を有しノードN1を放電するトランジスタである。

30

#### 【0085】

本実施の形態に係る単位シフトレジスタSRは、所定の制御信号VTRAが入力される第1制御端子TAおよび、制御信号VTRBが入力される第2制御端子TBを有している。制御信号VTRA、VTRBは互いに相補な信号であり、シフトレジスタ外部の制御装置（不図示）により生成される。この制御信号VTRA、VTRBは、一定の周期でレベルが切り替わるものである。ゲート線駆動回路では、表示画像のフレーム間のブランкиング期間にレベルが切り替わる（交番する）よう制御されることが望ましく、例えば、表示画像の1フレーム毎にレベルが切り替わるよう制御される。

#### 【0086】

40

また第1制御端子TAとノードN2Aの間にはトランジスタQ8Aが接続し、第2制御端子TBとノードN2Bとの間にはトランジスタQ8Bが接続する。トランジスタQ8AのゲートはノードN2Bに接続し、トランジスタQ8BのゲートはノードN2Aに接続する。即ち、トランジスタQ8AおよびトランジスタQ8Bは、その片方の主電極（ここではドレイン）がたすき掛けに互いの制御電極（ゲート）に接続されており、いわゆるフリップフロップ回路を構成している。

#### 【0087】

さらに当該単位シフトレジスタSRは、トランジスタQ5、Q6から成るインバータの出力端とノードN2Aとの間に接続するトランジスタQ9Aと、当該インバータの出力端とノードN2Bとの間に接続するトランジスタQ9Bとを備えている。トランジスタQ9

50

A のゲートは第 1 制御端子 T A に接続し、トランジスタ Q 9 B のゲートは第 2 制御端子 T B に接続する。

【 0 0 8 8 】

制御信号 V F R A が H レベル、制御信号 V F R B が L レベルの期間は、トランジスタ Q 9 A がオン、トランジスタ Q 9 B がオフになるので、トランジスタ Q 5 , Q 6 から成るインバータの出力端はノード N 2 A に接続される。またこのときトランジスタ Q 8 B がオンし、ノード N 2 A は L レベルになる。つまりその期間には、トランジスタ Q 2 A が駆動され、トランジスタ Q 2 B は休止状態になる。

【 0 0 8 9 】

逆に、制御信号 V F R A が L レベル、制御信号 V F R B が H レベルの期間は、トランジスタ Q 9 A がオフ、トランジスタ Q 9 B がオンになるので、トランジスタ Q 5 , Q 6 から成るインバータの出力端はノード N 2 B に接続される。またこのときトランジスタ Q 8 A がオンし、ノード N 2 B は L レベルになる。つまりその期間には、トランジスタ Q 2 B が駆動され、トランジスタ Q 2 A は休止状態になる。

10

【 0 0 9 0 】

このように、トランジスタ Q 9 A , Q 9 B は、制御信号 V F R A , V F R B に基づいて、トランジスタ Q 5 , Q 6 より成るインバータの出力端を、ノード N 2 A およびノード N 2 B に交互に接続させる切替回路として機能する。

【 0 0 9 1 】

本実施の形態においては、制御信号 V F R A , V F R B が反転する毎に、トランジスタ Q 2 A , Q 5 A のペアとトランジスタ Q 2 B , Q 5 B のペアとが交互に休止状態になるので、それらのゲートが継続的にバイアスされることを防止できる。従って、a - S i トランジスタのしきい値の正方向シフトによる誤動作を防止でき、動作の信頼性が向上する。

20

【 0 0 9 2 】

本実施の形態においても、デュアルゲートトランジスタ Q 3 D を構成するトランジスタ Q 3 a , Q 3 b のしきい値電圧の負方向シフトが抑制される効果が得られる。それにより、単位シフトレジスタ S R の誤動作の発生、消費電力の増大および電源電圧の低下を防止することができる。

【 0 0 9 3 】

< 実施の形態 5 >

30

上記の各実施の形態において、デュアルゲートトランジスタ Q 3 D は、単位シフトレジスタ S R のノード N 1 の充電する際、ソースフォロアモードで動作する。つまり、ノード N 1 の充電が進行するに従い、トランジスタ Q 3 b のゲート（入力端子 I N 1 ）・ソース（ノード N 1 ）間電圧が小さくなつて駆動能力（電流を流す能力）が低下するため、ノード N 1 を充分高いレベルにまで充電するためにある程度の時間を要する。このことはシフトレジスタの動作の高速化の妨げとなる。

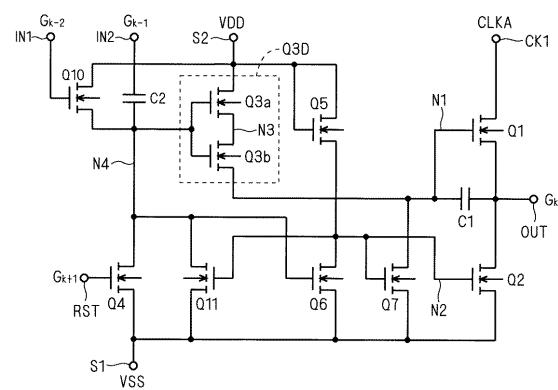

【 0 0 9 4 】

図 1 4 は、実施の形態 5 に係る単位シフトレジスタ S R の回路図であり、その問題の対策が施されたものである。当該単位シフトレジスタ S R は、縦続接続する場合には図 1 5 に示すように互いに位相の異なる 3 相クロック C L K A , C L K B , C L K C を用いて駆動される。

40

【 0 0 9 5 】

また、各単位シフトレジスタ S R は、入力端子として第 1 入力端子 I N 1 および第 2 入力端子 I N 2 の 2 つを有しており、第 1 入力端子 I N 1 には前々段（2 段前）の出力端子 O U T に接続され、第 2 入力端子 I N 2 には前段（1 段前）の出力端子 O U T に接続される。また、第 1 段目の単位シフトレジスタ S R 1 の第 1 入力端子 I N 1 、第 2 入力端子 I N 2 には、それぞれスタートパルス S T 1 , S T 2 が入力される。スタートパルス S T 1 , S T 2 は活性化する（H レベルになる）タイミングが異なつており、スタートパルス S T 2 はスタートパルス S T 1 の後に活性化する。

【 0 0 9 6 】

50

本実施の形態の単位シフトレジスタ S R は、ノード N 1 を充電する手段として、デュアルゲートトランジスタ Q 3 D と、そのゲートノード（「ノード N 4」と定義する）を充電するトランジスタ Q 1 0 と、ノード N 4 を昇圧する容量素子 C 2 と、ノード N 4 を放電するトランジスタ Q 4 とを含んでいる。図 1 4 に示すように、トランジスタ Q 1 0 は、ノード N 4 と第 2 電源端子 S 2 との間に接続し、ゲートが第 1 入力端子 I N 1 に接続する。容量素子 C 2 はノード N 4 と第 2 入力端子 I N 2 との間に接続する。トランジスタ Q 4 は、ノード N 4 と第 1 電源端子 S 1 との間に接続し、ゲートがリセット端子 R S T に接続されている。

#### 【 0 0 9 7 】

当該単位シフトレジスタ S R は、ノード N 4 を入力端とするインバータ（トランジスタ Q 5 , Q 6 ）を備えており、出力端子 O U T およびノード N 1 をそれぞれ放電するトランジスタ Q 2 , Q 7 のゲート（ノード N 2 ）は共に、当該インバータの出力端に接続される。またノード N 4 と第 1 電源端子 S 1 との間には、トランジスタ Q 4 と並列にトランジスタ Q 1 1 が接続しており、そのゲートはノード N 2 に接続されている。

#### 【 0 0 9 8 】

図 1 4 の単位シフトレジスタ S R の基本的な動作理論は、実施の形態 1 で説明したものとほぼ同じであるが、ノード N 1 を充電するデュアルゲートトランジスタ Q 3 D のゲートが、前段および前々段それぞれの出力信号という 2 つの信号を用いて充電・昇圧される点に特徴がある。

#### 【 0 0 9 9 】

つまり単位シフトレジスタ S R<sub>k</sub>において、デュアルゲートトランジスタ Q 3 D のゲート（ノード N 4 ）は、まず前々段の出力信号 G<sub>k-2</sub> が H レベルになると、トランジスタ Q 1 0 によって V D D - V t h ( Q 1 0 ) のレベルにまでプリチャージされる。次いで前段の出力信号 G<sub>k-1</sub> が H レベルになるときには、ノード N 4 は容量素子 C 2 によって 2 × V D D - V t h ( 1 0 ) 程度にまで昇圧される。つまりデュアルゲートトランジスタ Q 3 D のゲート電位は、図 1 の回路の場合よりも V D D 程度高くなり、当該デュアルゲートトランジスタ Q 3 D は、ソースフォロアモードでなく非飽和領域での動作によりノード N 1 を充電することができる。従って、ノード N 1 は高速に充電されて H レベル ( V D D ) になるので、上記の問題が解決される。

#### 【 0 1 0 0 】

なお本実施の形態では、選択期間においてデュアルゲートトランジスタ Q 3 D のゲート（ノード N 4 ）はフローティング状態となるので、次段の出力信号 G<sub>k+1</sub> により制御されるトランジスタ Q 4 は、当該ノード N 4 の放電に用いられている（この点で、図 7 のトランジスタ Q 4 とは異なる）。トランジスタ Q 4 がノード N 4 を L レベルにすると、トランジスタ Q 5 , Q 6 から成るインバータによってノード N 2 が H レベルにされ、応じてトランジスタ Q 7 がオンしてノード N 1 を放電する。つまり本実施の形態では、リセット端子 R S T に入力される信号に応じてノード N 1 を放電する役割（即ち、図 7 におけるトランジスタ Q 4 の役割）は、トランジスタ Q 7 が担っている。

#### 【 0 1 0 1 】

また、トランジスタ Q 1 1 は、ノード N 2 が H レベルになった間（非選択期間）、ノード N 4 を低インピーダンスの L レベルに維持しするように動作しており、それによって当該単位シフトレジスタ S R の誤動作が防止されている。

#### 【 0 1 0 2 】

本実施の形態においても、デュアルゲートトランジスタ Q 3 D を構成するトランジスタ Q 3 a , Q 3 b のしきい値電圧の負方向シフトが抑制される効果が得られる。それにより、単位シフトレジスタ S R の誤動作の発生、消費電力の増大および電源電圧の低下を防止することができる。

#### 【 0 1 0 3 】

また図 1 4 の単位シフトレジスタ S R では、トランジスタ Q 1 0 がノード N 4 を充電した後に、前々段の出力信号 G<sub>k-2</sub> が L レベルになったとき、トランジスタ Q 1 0 のゲート

10

20

30

40

50

がソースおよびドレインよりも低い電位になる。そのためトランジスタQ10においても図1のトランジスタQ3と同様のしきい値電圧の負方向シフトの問題が生じる可能性がある。

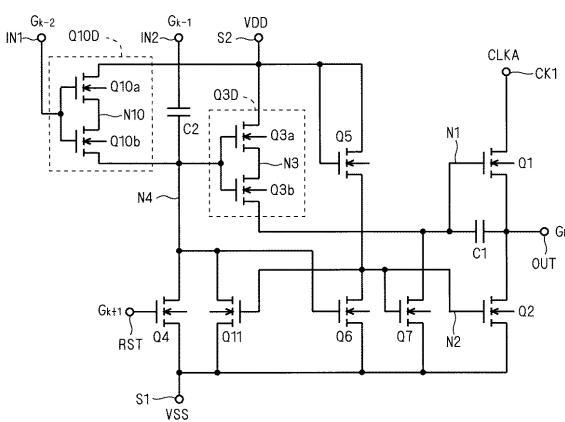

#### 【0104】

そこでその問題を回避するために、図14のトランジスタQ10に対しても本発明のデュアルゲートトランジスタを適用してもよい。即ち当該トランジスタQ10を、図16に示すように、トランジスタQ10a, Q10bから成るデュアルゲートトランジスタQ10Dに置き換えてよい。このデュアルゲートトランジスタQ10Dも、上記のデュアルゲートトランジスタQ3Dと同様に、そのゲート電極がHレベルからLレベルに変化したとき、それに応じてトランジスタQ10a, Q10bの間の接続ノード（「ノードN10」と定義）がLレベルに引き下げられるように、当該ゲートとノードN6との間の寄生容量を大きくしたものである。10

#### 【0105】

この構成によれば、デュアルゲートトランジスタQ10DすなわちトランジスタQ10a, Q10bにおいて、しきい値電圧の負方向シフトを抑制する効果が得られ、本実施の形態に係る単位シフトレジスタSRの誤動作の発生、消費電力の増大および電源電圧の低下を防止することができる。

#### 【0106】

##### <実施の形態6>

実施の形態4においては、非選択期間に出力端子OUTおよびノードN1をそれぞれ低インピーダンスのLレベルにするためのトランジスタQ2, Q7におけるしきい値電圧の正方向シフトの問題を解決する手法の一つを説明した。本実施の形態においても、その問題を解決する手法を示す。20

#### 【0107】

図17は、実施の形態6に係る単位シフトレジスタSRの回路図である。当該単位シフトレジスタSRは、クロック端子を2つ有している。即ち、トランジスタQ1のドレインが接続する第1クロック端子CK1に加え、それに入力されるものとは異なる位相のクロック信号が入力される第2クロック端子CK2を備えている。

#### 【0108】

またノードN1と出力端子OUTとの間に、ゲートが第1クロック端子CK1に接続したトランジスタQ12が設けられると共に、トランジスタQ5, Q6から成るインバータの出力端（「ノードN5」と定義する）と第1電源端子S1との間に、ゲートが第1クロック端子CK1に接続したトランジスタQ13が設けられている。さらに本実施の形態では、出力端子OUTと第1電源端子S1との間に接続したトランジスタQ2のゲートは、第2クロック端子CK2に接続される。30

#### 【0109】

トランジスタQ5, Q6から成るインバータは、実施の形態2, 3と同様にノードN1を入力端としているが、トランジスタQ5のゲートおよびドレインが第2クロック端子CK2に接続される点で異なっている。つまり第2クロック端子CK2に入力されるクロック信号は、当該インバータの電源となる。40

#### 【0110】

図17の単位シフトレジスタSRの基本的な動作理論は、実施の形態1で説明したものとほぼ同じであるが、トランジスタQ5, Q6から成るインバータが、第2クロック端子CK2に入力されるクロック信号によって電力が供給されることで活性化され、またその出力はトランジスタQ13によって強制的にLレベルされる点が特徴的である。

#### 【0111】

ここでも第k段目の単位シフトレジスタSR<sub>k</sub>の動作を代表的に説明する。簡単のため、当該単位シフトレジスタSR<sub>k</sub>においては、第1クロック端子CK1にクロック信号CLKAが入力され、第2クロック端子CK2にクロック信号CLKBが入力されるものとする。50

## 【0112】

まず、単位シフトレジスタ $S R_k$ の非選択期間の動作について説明する。非選択期間では、ノードN1はLレベルであるので、トランジスタQ5, Q6から成るインバータがクロック信号CLKBにより活性化されるとノードN5がHレベルになる。また当該インバータが非活性になるときは、トランジスタQ13がクロック信号CLKAによってオンにされるので、ノードN5はLレベルになる。つまり、非選択期間においては、ノードN5はほぼクロック信号CLKBと同じようにレベルが変化することになる。従ってトランジスタQ7は、クロック信号CLKBがHレベルになるタイミングでノードN1を低インピーダンスのLレベルにする。

## 【0113】

10

トランジスタQ7は、クロック信号CLKBがLレベルのときにはオフになるが、その間はクロック信号CLKAがトランジスタQ12をオンにすることで、ノードN1の電荷はトランジスタQ12によって出力端子OUTに放出される。通常、出力端子OUTには容量性の負荷（ゲート線駆動回路の場合には、表示パネルのゲート線）が接続されるため、このとき出力端子OUTに放出される程度の電荷では、出力端子OUTがHレベルになることはない。

## 【0114】

このように単位シフトレジスタ $S R_k$ の非選択期間においては、トランジスタQ7とトランジスタQ12とが交互にノードN1を放電するように動作することによってノードN1のレベル上昇が防止されている。トランジスタQ7, Q12のゲート電極は継続的に正バイアスされないので、それらのしきい値電圧の正方向シフトは抑制される。

20

## 【0115】

また、トランジスタQ2は、クロック信号CLKBがHレベルになるときにオンして、出力端子OUTを低インピーダンスのLレベルにする。つまりトランジスタQ2のゲートも継続的に正バイアスされないので、そのしきい値電圧の正方向シフトも抑制されている。

## 【0116】

また、前段の出力信号 $G_{k-1}$ がHレベルになり、単位シフトレジスタ $S R_k$ の選択期間になると、ノードN1がHレベルになる。その間は、トランジスタQ5, Q6から成るインバータがクロック信号CLKBにより活性化されてもノードN5はLレベルであるので、トランジスタQ7はオフになりノードN1のHレベルは維持される。そしてクロック信号CLKAがHレベルになると、トランジスタQ12のゲートがHレベルになるが、それと同時に出力端子OUT（出力信号 $G_k$ ）もHレベルになるので、トランジスタQ12はオンせず、ノードN1はフローティング状態でHレベルに維持される（クロック信号CLKAにより昇圧される）。従って、単位シフトレジスタ $S R_k$ は、正常に出力信号 $G_k$ を出力することができる。

30

## 【0117】

以上のように、本実施の形態の単位シフトレジスタ $S R$ においても、実施の形態1と同様にノードN1のレベルが変化する。つまり当該単位シフトレジスタ $S R$ は、非選択期間はリセット状態に維持され、選択期間にセット状態となるように動作する。従って、実施の形態1と同様の信号のシフト動作を行うことができる。

40

## 【0118】

なお上記の説明においては、トランジスタQ2のソースは第1電源端子S1に接続しているものとしたが、第1クロック端子CK1に接続させてもよい。その場合には、トランジスタQ2のゲートに入力されるクロック信号CLKBがLレベルになって当該トランジスタQ2がオフになるとき、ソースに入力されるクロック信号CLKAがHレベルになるため、トランジスタQ2のゲートがソースに対して負にバイアスされるのと等価な状態になる。それにより、正方向へシフトしたしきい値電圧が負方向へ戻って回復するため、トランジスタQ2の駆動能力の低下が軽減され、回路の動作寿命が延びるという効果が得られる。

50

**【0119】**

本実施の形態においても、デュアルゲートトランジスタQ3Dを構成するトランジスタQ3a, Q3bのしきい値電圧の負方向シフトが抑制される効果が得られる。それにより、単位シフトレジスタSRの誤動作の発生、消費電力の増大および電源電圧の低下を防止することができる。

**【0120】**

<実施の形態7>

実施の形態7においても、非選択期間に出力端子OUTおよびノードN1をそれぞれ低インピーダンスのLレベルにするためのトランジスタQ2, Q7におけるしきい値電圧の正方向シフトの問題を解決する手法を示す。

10

**【0121】**

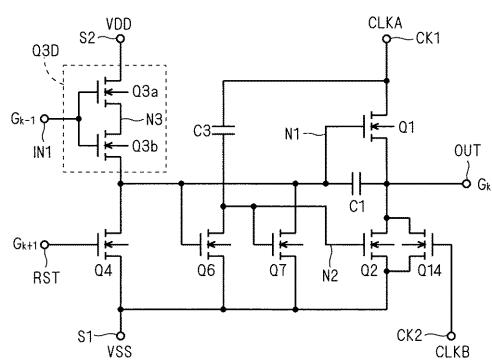

図18は、実施の形態7に係る単位シフトレジスタSRの回路図である。当該単位シフトレジスタSRも、トランジスタQ1のドレインが接続する第1クロック端子CK1に加え、それに入力されるものとは異なる位相のクロック信号が入力される第2クロック端子CK2を備えている。

**【0122】**

図18の回路は、図12に類似した構成を有しているが、トランジスタQ1のゲートノード(ノードN1)を入力端とし、トランジスタQ2のゲートノード(ノードN2)を出力端とするインバータが、容量性負荷型のインバータである点で異なっている。即ち当該インバータは、負荷容量C3を負荷素子としている。また当該インバータは、第1クロック端子CK1に入力されるクロック信号が電源となる点で、通常のインバータとは異なる。つまり負荷容量C3は、当該インバータの出力端であるノードN2と第1クロック端子CK1との間に接続される。負荷容量C3は、当該インバータの負荷素子であると共に、第1クロック端子CK1とノードN2との結合容量としても機能する。

20

**【0123】**

さらに図18の回路では、ゲートが上記インバータの出力端に接続したトランジスタQ2と並列に、トランジスタQ14が接続されている。このトランジスタQ14のゲートは、第2クロック端子CK2に接続している。

**【0124】**

図18の単位シフトレジスタSRの基本的な動作理論は、実施の形態1で説明したものとほぼ同じであるが、負荷容量C3とトランジスタQ6から成るインバータが、第1クロック端子CK1に入力されるクロック信号によって電力が供給されることで活性化される点が特徴的である。

30

**【0125】**

ここでも第k段目の単位シフトレジスタSR<sub>k</sub>の動作を代表的に説明する。簡単のため、当該単位シフトレジスタSR<sub>k</sub>においては、第1クロック端子CK1にクロック信号CLKAが入力され、第2クロック端子CK2にクロック信号CLKBが入力されるものとする。

**【0126】**

まず、単位シフトレジスタSR<sub>k</sub>の非選択期間の動作について説明する。非選択期間では、ノードN1はLレベルであるので、負荷容量C3とトランジスタQ6から成るインバータがクロック信号CLKAにより活性化されるとノードN2がHレベルになる。また当該インバータが非活性になるときは、負荷容量C3を介した結合のため、クロック信号CLKAの立ち下がりに応じてノードN2はLレベルになる。つまり、非選択期間においては、ノードN2はほぼクロック信号CLKAと同じようにレベルが変化することになる。従ってトランジスタQ7はクロック信号CLKAがHレベルになるタイミングでノードN1を低インピーダンスのLレベルにする。

40

**【0127】**

またトランジスタQ2もトランジスタQ7と同様にクロック信号CLKAに同期したタイミングでオンし、それによって出力端子OUTを低インピーダンスのLレベルにする。

50

クロック信号 C L K A が L レベルのときトランジスタ Q 2 はオフになるが、このときトランジスタ Q 1 4 がクロック信号 C L K B によってオンされ、出力端子 O U T を低インピーダンスの L レベルにする。

#### 【 0 1 2 8 】

このように単位シフトレジスタ S R<sub>k</sub> の非選択期間においては、トランジスタ Q 7 がクロック信号 C L K A に同期したタイミングでノード N 1 を放電するように動作することによってノード N 1 のレベル上昇が防止されている。またトランジスタ Q 2 とトランジスタ Q 1 4 とが交互に出力端子 O U T を放電することによって、誤信号としての出力信号 G<sub>k</sub> が発生することを防止している。これらトランジスタ Q 2 , Q 7 , Q 1 4 のゲート電極は継続的に正バイアスされないので、それらのしきい値電圧の正方向シフトは抑制される。

10

#### 【 0 1 2 9 】

また、前段の出力信号 G<sub>k-1</sub> が H レベルになり、単位シフトレジスタ S R<sub>k</sub> の選択期間になると、当該単位シフトレジスタ S R<sub>k</sub> のデュアルゲートトランジスタ Q 3 D がオンするのでノード N 1 が H レベルになる。そのとき負荷容量 C 3 とトランジスタ Q 6 から成るインバータは非活性であり、ノード N 2 は L レベルになっている。そしてクロック信号 C L K A が H レベルになると当該インバータが活性化されるが、トランジスタ Q 6 がオンしているのでノード N 2 は L レベルを維持する。よって選択期間ではトランジスタ Q 7 のオフが維持され、ノード N 1 はフローティング状態で H レベルに保たれる（クロック信号 C L K A により昇圧される）。従って、単位シフトレジスタ S R<sub>k</sub> は、正常に出力信号 G<sub>k</sub> を出力することができる。

20

#### 【 0 1 3 0 】

以上のように、本実施の形態の単位シフトレジスタ S R においても、実施の形態 1 と同様にノード N 1 のレベルが変化する。つまり当該単位シフトレジスタ S R は、非選択期間はリセット状態に維持され、選択期間にセット状態となるように動作する。従って、実施の形態 1 と同様の信号のシフト動作を行うことができる。

#### 【 0 1 3 1 】

本実施の形態においても、デュアルゲートトランジスタ Q 3 D を構成するトランジスタ Q 3 a , Q 3 b のしきい値電圧の負方向シフトが抑制される効果が得られる。それにより、単位シフトレジスタ S R の誤動作の発生、消費電力の増大および電源電圧の低下を防止することができる。

30

#### 【 0 1 3 2 】

##### < 実施の形態 8 >

実施の形態 8 においては、本発明に係るデュアルゲートトランジスタ Q 3 D を、信号のシフト方向を切り替え可能なシフトレジスタ（双方向シフトレジスタ）に適用した例を示す。

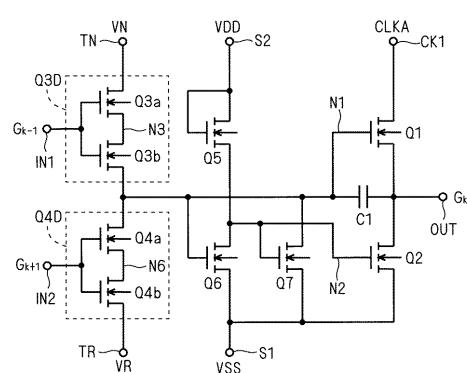

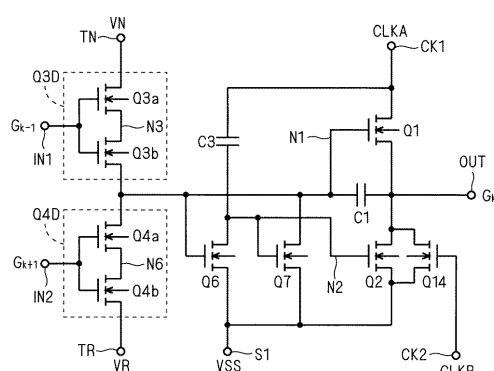

#### 【 0 1 3 3 】

図 1 9 は、実施の形態 8 に係る単位シフトレジスタ S R の回路図である。当該単位シフトレジスタ S R は、双方向シフトレジスタである。当該単位シフトレジスタ S R の回路構成自体はほぼ図 1 1 と同様であるが、トランジスタ Q 4 を本発明に係るデュアルゲートトランジスタ Q 4 D (トランジスタ Q 4 a , Q 4 b ) に置き換えている。上記のデュアルゲートトランジスタ Q 3 D と同様に、このデュアルゲートトランジスタ Q 4 D も、そのゲート電極が H レベルから L レベルに変化したとき、それに応じてトランジスタ Q 4 a , Q 4 b の間の接続ノード（「ノード N 6」と定義）が L レベルに引き下げられるように、当該ゲートとノード N 6 との間の寄生容量を大きくしたものである。

40

#### 【 0 1 3 4 】

一方向のみのシフトを行う単位シフトレジスタは、基本的に入力端子に信号が入力されてセット状態となり、リセット端子に信号が入力されてリセット状態になるが、双方向シフトレジスタでは、信号のシフト方向に応じて入力端子とリセット端子とが機能的に入れ替わるためその区別はない。説明の便宜上、デュアルゲートトランジスタ Q 3 D のゲートが接続する端子を「第 1 入力端子 I N 1」、デュアルゲートトランジスタ Q 4 D のゲート

50

が接続する端子を「第2入力端子IN2」と称する。

**【0135】**

また、双方向シフトレジスタである単位シフトレジスタSRには、信号のシフト方向を決めるための制御信号である第1電圧信号VNおよび第2電圧信号VRが入力される。デュアルゲートトランジスタQ3Dは、第1電圧信号VNが入力される第1電圧信号端子TNとノードN1との間に接続し、デュアルゲートトランジスタQ4Dは、第2電圧信号VRが入力される第2電圧信号端子TRとの間に接続する。第1電圧信号VNと第2電圧信号VRとは、互いに相補な信号である。

**【0136】**

例えば、第1電圧信号VNがHレベル(VDD)、第2電圧信号VRがLレベル(VSS)のときは、図19において第1電圧信号端子TNがVDD、第2電圧信号端子TRがVSSとなるので、デュアルゲートトランジスタQ3DはノードN1の充電回路となり、デュアルゲートトランジスタQ4DはノードN1の放電回路となる。つまりこの状態では、第1入力端子IN1が図11の入力端子IN1として機能し、第2入力端子IN2が図11のリセット端子\_RSTとして機能するようになる。10

**【0137】**

逆に、第1電圧信号VNがLレベル(VSS)、第2電圧信号VRがHレベル(VDD)のときは、デュアルゲートトランジスタQ3DがノードN1の放電回路となり、デュアルゲートトランジスタQ4DがノードN1の充電回路となる。つまりこの状態では、第1入力端子IN1が図11のリセット端子\_RSTとして機能し、第2入力端子IN2が図11の入力端子IN1として機能するようになる。20

**【0138】**

つまり、この単位シフトレジスタSRを図2の如く縦続接続させて成る多段のシフトレジスタによれば、第1電圧信号VNがHレベル、第2電圧信号VRがLレベルの場合には、出力信号G1, G2, G3…の順に活性化される(順方向シフト)。反対に第1電圧信号VNがLレベル、第2電圧信号VRがHレベルの場合には、出力信号Gn, Gn-1, Gn-2…の順に活性化される(逆方向シフト)。

**【0139】**

従って本実施の形態においては、順方向シフトの動作の際にはデュアルゲートトランジスタQ3Dを構成するトランジスタQ3a, Q3bにおいて、しきい値電圧の負方向シフトを抑制する効果が得られる。また逆方向シフトの動作の際にはデュアルゲートトランジスタQ4Dを構成するトランジスタQ4a, Q4bにおいて、しきい値電圧の負方向シフトを抑制する効果が得られる。従って本実施の形態においても、単位シフトレジスタSRの誤動作の発生、消費電力の増大および電源電圧の低下を防止することができる。30

**【0140】**

なお図19においては、実施の形態2(図11)の単位シフトレジスタSRの構成をベースとした双方向シフトレジスタに対し、本発明に係るデュアルゲートトランジスタQ3D, Q4Dを適用した例を示したが、双方向シフトレジスタへの本発明の適用はそれに限定されるものではない。以下、本実施の形態の変形例を示す。

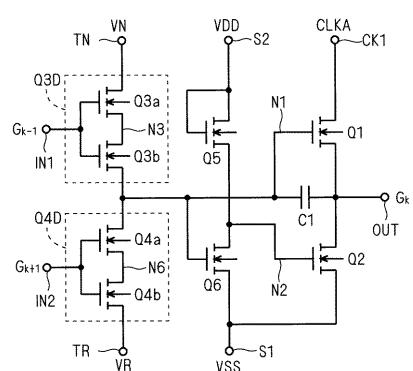

**【0141】**

例えは図20は、実施の形態3(図12)の単位シフトレジスタSRをベースにした双方向シフトレジスタに対して、デュアルゲートトランジスタQ3D, Q4Dを適用した例である。即ち図19の回路に対し、非選択期間にノードN1を放電するトランジスタQ7を設けている。また例えば、図21および図22は、それぞれ実施の形態7(図18)および実施の形態4(図13)の単位シフトレジスタSRをベースにした双方向シフトレジスタに対して、デュアルゲートトランジスタQ3D, Q4Dを適用した例である。これらの変形例においても上記と同様の効果が得られる。40

**【0142】**

<実施の形態9>

上記したように、デュアルゲートトランジスタQ3Dにおいて、トランジスタQ3a,

50

Q 3 b のゲート（単位シフトレジスタ S R の入力端子 I N 1）が H レベル（V D D）から L レベル（V S S = 0 V）へと変化したときにおける、トランジスタ Q 3 a , Q 3 b の間のノード N 3 のレベルの変化量は、入力端子 I N 1 とノード N 3との間の容量成分を C g s 、当該 C g s に含まれないノード N 3 に付随する寄生容量を C s t r とすると、V D D × C g s / ( C g s + C s t r ) で表される。つまり入力端子 I N 1 とノード N 3 との間の容量成分 C g s が、寄生容量 C s t r に比べて大きい程（即ち、ノード N 3 に付随する全寄生容量に占める容量成分 C g s の割合が大きい程）、ノード N 3 をより低いレベルにまで引き下げる事ができる。

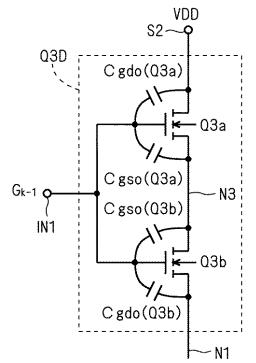

#### 【 0 1 4 3 】

そこで本実施の形態では、デュアルゲートトランジスタ Q 3 D における入力端子 I N 1 とノード N 3 との間の容量成分を大きくするための手法を説明する。一般に、電界効果型トランジスタは、寄生容量としてゲートとソース／ドレインとの間にオーバラップ容量を有している。よって図 2 3 に示すようにデュアルゲートトランジスタ Q 3 D は、寄生容量として、トランジスタ Q 3 a のゲート・ドレンオーバラップ容量 C g d o ( Q 3 a ) およびゲート・ソースオーバラップ容量 C g s o ( Q 3 a ) と、トランジスタ Q 3 b のゲート・ドレンオーバラップ容量 C g d o ( Q 3 b ) およびゲート・ソースオーバラップ容量 C g s o ( Q 3 b ) を有することとなる。

#### 【 0 1 4 4 】

これらのうち入力端子 I N 1 とノード N 3 との間の容量成分 ( C g s ) に寄与するのは、トランジスタ Q 3 a , Q 3 b のゲート・ソースオーバラップ容量 C g s o ( Q 3 a ) , C g s o ( Q 3 b ) であり、本発明においてはそれらの容量値が充分大きいことが望ましい。

#### 【 0 1 4 5 】

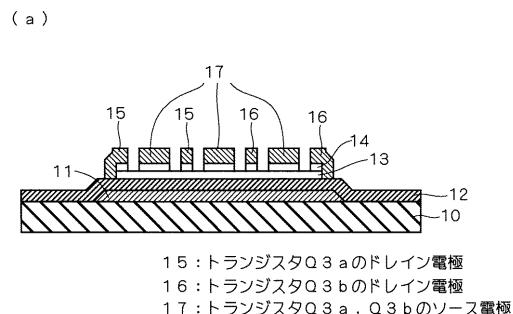

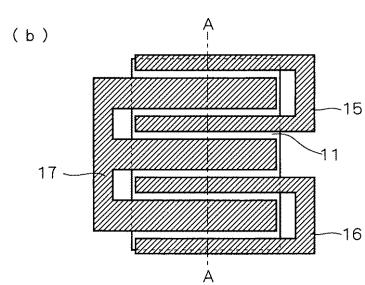

図 2 4 ( a ) , ( b ) は、本実施の形態に係るデュアルゲートトランジスタ Q 3 D の構成を示す図である。図 2 4 ( a ) は、デュアルゲートトランジスタ Q 3 D の断面図であり、図 2 4 ( b ) はその上面図である。なお図 2 4 ( a ) は、図 2 4 ( b ) に示す A - A 線に沿った断面に対応している。

#### 【 0 1 4 6 】

当該デュアルゲートトランジスタ Q 3 D は、ゲート電極上にソース／ドレイン領域が配設された、いわゆる「ボトムゲート型トランジスタ」である。即ち、このデュアルゲートトランジスタ Q 3 D は、ガラス基板 1 0 上に形成されたゲート電極 1 1 、ゲート電極 1 1 上に形成されたゲート絶縁膜 1 2 、ゲート絶縁膜 1 2 上に形成された活性領域 1 3 （イントリニシックシリコン）、活性領域 1 3 上に形成されたコンタクト層 1 4 （N + 型シリコン）により構成される。コンタクト層 1 4 は、トランジスタ Q 3 a , Q 3 b のソース／ドレインとなるものであり、その上にトランジスタ Q 3 a のドレン配線 1 5 、トランジスタ Q 3 b のドレン配線 1 6 、トランジスタ Q 3 a , Q 3 b のソース配線 1 7 がそれぞれ形成される。

#### 【 0 1 4 7 】

例えば図 7 の単位シフトレジスタ S R では、ゲート電極 1 1 は単位シフトレジスタ S R の入力端子 I N 1 に接続され、トランジスタ Q 3 a のドレン配線 1 5 は第 2 電源端子 S 2 に接続され、トランジスタ Q 3 b のドレン配線 1 6 がノード N 1 に接続される。そしてトランジスタ Q 3 a , Q 3 b のソース配線 1 7 がノード N 3 となる。

#### 【 0 1 4 8 】

図 2 4 ( b ) に示すように、本実施の形態においては、ノード N 3 となる配線 1 7 のパターンを、他の配線 1 5 , 1 6 よりも大きくする（幅を広くする）。そうすることにより、ゲート電極 1 1 と配線 1 7 とが対向する面積が大きくなり、オーバラップ容量 C g s o ( Q 3 a ) , C g s o ( Q 3 b ) を大きくすることができる。即ち、入力端子 I N 1 とノード N 3 との間の容量成分 ( C g s + C g s o ( Q 3 a ) + C g s o ( Q 3 b ) ) を大きくすることができる。

#### 【 0 1 4 9 】

10

20

30

40

50

その結果、デュアルゲートトランジスタQ3DのゲートがHレベルからLレベルに変化させたときに、トランジスタQ3a, Q3b間のノードN3のレベルを充分に低いレベルにまで引き下げるようになり、しきい値電圧の負方向シフトを抑制するという本発明の効果が向上される。

#### 【0150】

このときトランジスタQ3aのドレイン配線15およびトランジスタQ3bのドレイン配線16のパターンも大きくしてもよく、上記の効果は得られる。しかしそうするとデュアルゲートトランジスタQ3Dの形成面積が著しく増大するため、図24(b)に示したようにノードN3となるソース配線17のパターンのみを大きくする方が望ましい。つまり、図23において、 $C_{gdo}(Q3a)$ および $C_{gdo}(Q3b)$ の値を維持しつつ、 $C_{gso}(Q3a)$ および $C_{gso}(Q3b)$ の値だけを増加させることが望ましい。結果として、 $C_{gso}(Q3a) > C_{gdo}(Q3a)$ および $C_{gso}(Q3b) > C_{gdo}(Q3b)$ の関係が成り立つようになる。10

#### 【0151】

ところで、本実施の形態のようにノードN3となる配線17の幅を広く形成すると、容量成分 $C_{gs}$ だけでなく、当該 $C_{gs}$ に含まれないノードN3の寄生容量 $C_{str}$ も大きくなるようにも思われるが、寄生容量 $C_{str}$ の増加は殆ど伴わない。

#### 【0152】

寄生容量 $C_{str}$ は、配線17における対接地容量や、例えば液晶表示装置であればガラス基板10の上方に配設される対向電極(コモン電極)と配線17との間の寄生容量など、配線17の「フリンジ容量」である。接地電極やコモン電極は、配線17からの距離が遠いため、配線17の幅が変わっても、上記フリンジ容量の値は殆ど変化しない。本実施の形態において配線17の幅を広く形成しても寄生容量 $C_{str}$ の増加を殆ど伴わないのはそのためである。20

#### 【0153】

それに対し、ゲート・ソースオーバラップ容量 $C_{gso}(Q3a)$ ,  $C_{gso}(Q3b)$ は、配線17とゲート電極11とが対向して成る並行平板型のキャパシタとみなすことができる。そのため、配線17の幅を広げれば、ほぼそれに比例して $C_{gso}(Q3a)$ ,  $C_{gso}(Q3b)$ の値は大きくなる。

#### 【0154】

従って本実施の形態によれば、寄生容量 $C_{str}$ の値を保ちつつ、容量成分 $C_{gs}$ の値を大きくすることができる。言い換えれば、ノードN3に付随する寄生容量に占める容量成分 $C_{gs}$ の割合を大きくすることができます。その結果、トランジスタQ3a, Q3bのゲート(単位シフトレジスタSRの入力端子IN1)がHレベルからLレベルへと変化したときに、ノードN3がより低いレベルにまで引き下げるようになり、上記の効果を得られる。30

#### 【0155】

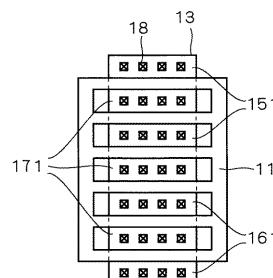

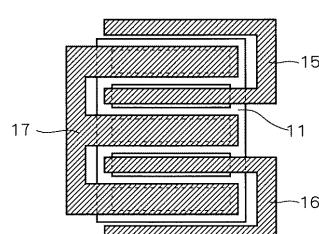

また上記の説明においては、ボトムゲート型トランジスタの例を示したが、本実施の形態は、例えば活性領域13上にゲート電極11が配設される「トップゲート型トランジスタ」に対しても適用可能である。図25(a), (b)は、デュアルゲートトランジスタQ3Dがトップゲート型トランジスタである場合の例を示している。40

#### 【0156】

トップゲート型トランジスタの場合、図25(a)の如く、ゲート電極11は活性領域13上を横切るライン状のパターンで形成される。トランジスタQ3aのドレイン領域151、トランジスタQ3bのドレイン領域161およびトランジスタQ3a, Q3bのソース領域171は、ゲート電極11の下の活性領域13内に形成されるので、それらの上には上層の配線と接続するためのコンタクト18が形成される。図25(b)は、その配線のパターンを示している。

#### 【0157】

この場合も、ノードN3となる配線17のパターンを、他の配線15, 16よりも大き50

くする。それにより、ゲート電極 11 と配線 17 とが対向する面積が大きくなり、オーバラップ容量  $C_{gso}$  ( $Q3a$ ) ,  $C_{gso}$  ( $Q3b$ ) を大きくすることができ、上記と同様の効果を得ることができる。

#### 【0158】

なお本実施の形態は、実施の形態 1 ~ 8 における全てのデュアルゲートトランジスタ  $Q3D$  について適用可能である。また以上では、デュアルゲートトランジスタ  $Q3D$  についてのみ説明したが、図 16 に示した実施の形態 5 の変形例におけるデュアルゲートトランジスタ  $Q10D$ 、並びに実施の形態 8 におけるデュアルゲートトランジスタ  $Q4D$  に対しても適用可能であることは明らかである。

#### 【0159】

10

##### < 実施の形態 10 >

以上の実施の形態においては、デュアルゲートトランジスタ  $Q3D$  のノード  $N3$  のレベルを引き下げる手段は、そのゲート（入力端子  $IN1$ ）とノード  $N3$  との間の寄生容量（トランジスタ  $Q3a$ ,  $Q3b$  のゲート・ソースオーバラップ容量）であった。

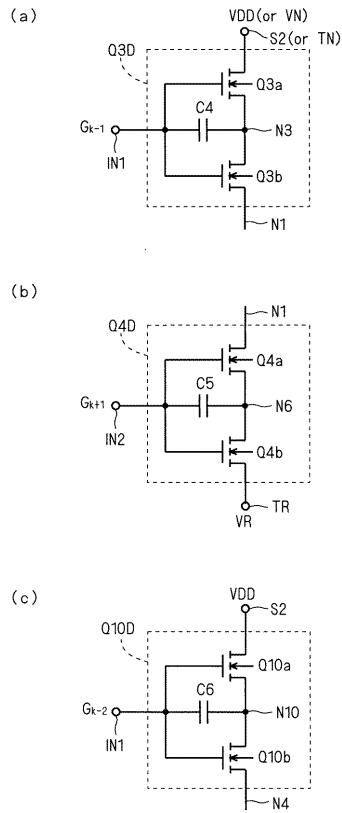

#### 【0160】

上記のように、ノード  $N3$  のレベルをより低いレベルに引き下げるためには、当該ゲートとノード  $N3$  との間の容量成分を大きくすればよい。そこで本実施の形態では、図 26 (a) の如く、デュアルゲートトランジスタ  $Q3D$  のゲートとノード  $N3$  との間に、容量素子  $C4$  を接続させる。それにより、実施の形態 9 のような手法を用いなくても、ゲートとノード  $N3$  との間の容量成分を大きくでき、ノード  $N3$  をより確実に  $L$  レベルにまで引き下げることができる。つまり、デュアルゲートトランジスタ  $Q3D$  のしきい値電圧の負方向シフトをより確実に防止することができる。

20

#### 【0161】

本実施の形態は、実施の形態 1 ~ 8 における全てのデュアルゲートトランジスタ  $Q3D$  について適用可能である。また、実施の形態 8 におけるデュアルゲートトランジスタ  $Q4D$  に対しても適用可能である。その場合には、図 26 (b) の如くデュアルゲートトランジスタ  $Q4D$  のゲートとノード  $N6$  との間に容量素子  $C5$  を接続させればよい。また図 16 に示した実施の形態 5 の変形例におけるデュアルゲートトランジスタ  $Q10D$  に対しても適用可能であり、その場合には図 26 (c) のように、デュアルゲートトランジスタ  $Q10D$  のゲートとノード  $N10$  との間に容量素子  $C6$  を接続させればよい。

30

#### 【0162】

##### < 実施の形態 11 >

以上の実施形態では、デュアルゲートトランジスタ  $Q3D$  のノード  $N3$  のレベルを引き下げる手段は、そのゲート（入力端子  $IN1$ ）とノード  $N3$  との間の容量成分であったが、ダイオードを用いることも可能である。

#### 【0163】

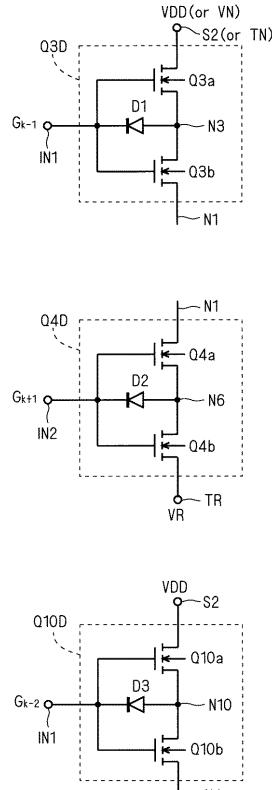

図 27 (a) は、本実施の形態に係るデュアルゲートトランジスタ  $Q3D$  を示す図である。同図の如く、デュアルゲートトランジスタ  $Q3D$  のゲートとノード  $N3$  との間に、ゲート側がカソード、ノード  $N3$  がアノードとなるようにダイオード  $D1$  を接続させる。この場合も、デュアルゲートトランジスタ  $Q3D$  のゲートが  $H$  レベルから  $L$  レベルに変化するとそれに追随してノード  $N3$  は  $L$  レベルに引き下げられる。従って、図 27 (a) のデュアルゲートトランジスタ  $Q3D$  によっても、しきい値電圧の負方向シフトは抑制されるという実施の形態 1 と同様の効果が得られる。

40

#### 【0164】

また上記した各実施形態においては、ノード  $N3$  のレベルが引き下げられたとき、当該ノード  $N3$  はフローティング状態で  $L$  レベルになる。そのため、トランジスタ  $Q3a$ ,  $Q3b$  にリーク電流が生じると、ノード  $N3$  のレベルが上昇し、本発明の効果が低減する問題が生じる。

#### 【0165】

それに対し図 27 (a) のデュアルゲートトランジスタ  $Q3D$  においては、リーク電流

50

によりノードN3のレベルが上昇しようとしても、その電荷はダイオードD1を介して放電される。つまりリーク電流が生じた場合でもノードN3のレベルは、ダイオードD1のしきい値電圧よりも大きくなることはないので、上記の問題を解決できるという効果も得られる。

#### 【0166】

本実施の形態は、実施の形態1～8における全ての単位シフトレジスタSRのデュアルゲートトランジスタQ3Dについて適用可能である。また、実施の形態8における単位シフトレジスタSRのデュアルゲートトランジスタQ4Dに対しても適用可能である。その場合には、図27(b)の如くデュアルゲートトランジスタQ4DのゲートとノードN6との間に、ゲート側がカソード、ノードN6側がアノードとなるようにダイオードD2を接続させる。また図16に示した実施の形態5の変形例におけるデュアルゲートトランジスタQ10Dに対しても適用可能であり、その場合には図27(c)のように、デュアルゲートトランジスタQ10DのゲートとノードN10との間に、ゲート側がカソード、ノードN10側がアノードとなるようにダイオードD3を接続させればよい。10

#### 【0167】

<実施の形態12>

本実施の形態では、デュアルゲートトランジスタQ3DのノードN3のレベルを引き下げる手段として、トランジスタを用いる。

#### 【0168】

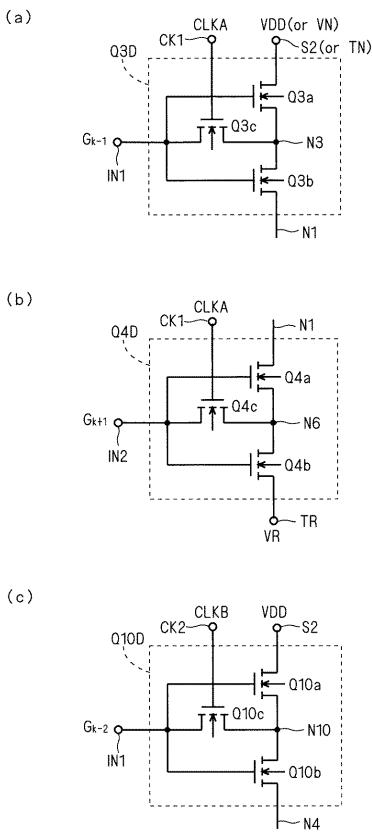

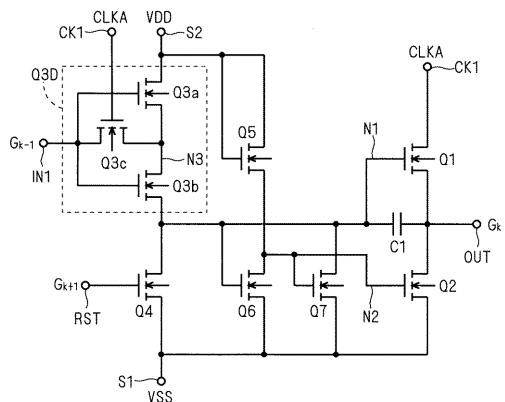

図28(a)は、本実施の形態に係るデュアルゲートトランジスタQ3Dを示す図である。同図の如く、デュアルゲートトランジスタQ3DのゲートとノードN3との間に、当該ゲートに入力される信号(前段の出力信号G<sub>k-1</sub>)がHレベルからLレベルに変化するときにオンするトランジスタQ3cを接続させる。例えば図29は、図28(a)のデュアルゲートトランジスタQ3Dを、図12の単位シフトレジスタSRkに適用した例である。20

#### 【0169】

単位シフトレジスタSRを縦続接続した場合、第k段目の単位シフトレジスタSR<sub>k</sub>の入力端子IN1にはその前段の出力信号G<sub>k-1</sub>が入力されるので、デュアルゲートトランジスタQ3Dのゲートに入力される信号(前段の出力信号G<sub>k-1</sub>)がHレベルからLレベルに変化するときに、トランジスタQ3cをオンさせるためには、トランジスタQ3cのゲートをクロック端子CK1に接続させればよい。30

#### 【0170】

例えば、単位シフトレジスタSR<sub>k</sub>として、クロック端子CK1にクロック信号CLKAが入力されるものと仮定すると、その前段の出力信号G<sub>k-1</sub>はクロック信号CLKBの立ち上がりタイミングでHレベルになる。前段の出力信号G<sub>k-1</sub>がHレベルになるとトランジスタQ3a, Q3bがオンになり、ノードN1, N3がHレベルになる。このときクロック端子CK1に入力されるクロック信号CLKAはLレベルなので、トランジスタQ3cはオフになっている。

#### 【0171】

その後、前段の出力信号G<sub>k-1</sub>がLレベルに変化すると、トランジスタQ3a, Q3bはオフになる。このときクロック信号CLKAがHレベルになるので、トランジスタQ3cがオンになる。その結果、ノードN3はトランジスタQ3cにより放電され、Lレベルに引き下げられる。つまりトランジスタQ3a, Q3bにおいてゲートがソースおよびドレインの両方に対して低電位になることが防止される。従って、デュアルゲートトランジスタQ3Dにおける、しきい値電圧の負方向シフトが抑制されるという実施の形態1と同様の効果が得られる。40

#### 【0172】

本実施の形態は、実施の形態1～8における全ての単位シフトレジスタSRのデュアルゲートトランジスタQ3Dについて適用可能である。また、実施の形態8における単位シフトレジスタSRのデュアルゲートトランジスタQ4Dに対しても適用可能である。その50

場合には、図28(b)の如くデュアルゲートトランジスタQ4DのゲートとノードN6との間に、ゲートがクロック端子CK1に接続したトランジスタQ4cを接続させる。

### 【0173】

また図16に示した実施の形態5の変形例におけるデュアルゲートトランジスタQ10Dに対しても適用可能である。この場合は図28(c)のように、デュアルゲートトランジスタQ10DのゲートとノードN10との間にトランジスタQ10cを接続させる。但し、デュアルゲートトランジスタQ10Dのゲートには、前々段の出力信号G<sub>k-2</sub>が入力されており、それがHレベルからLレベルに変化するときにトランジスタQ10cをオンさせる必要がある。そのため図28(c)に示すように、トランジスタQ10cのゲートは、クロック端子CK2に接続させる。

10

### 【図面の簡単な説明】

#### 【0174】

【図1】従来の単位シフトレジスタの構成を示す回路図である。

【図2】多段のシフトレジスタの構成を示す図である。

【図3】従来の単位シフトレジスタの動作を示すタイミング図である。

【図4】多段のシフトレジスタの動作を示す図である。

【図5】従来の単位シフトレジスタの問題を説明するための図である。

【図6】a-Siトランジスタの電位状態としきい値電圧のシフトとの関係を表した実験結果を示す図である。

【図7】実施の形態1に係る単位シフトレジスタの回路図である。

20

【図8】実施の形態1に係る単位シフトレジスタの動作を示すタイミング図である。

【図9】実施の形態1の効果を説明するための図である。

【図10】実施の形態1の効果を説明するための図である。

【図11】実施の形態2に係る単位シフトレジスタの回路図である。

【図12】実施の形態3に係る単位シフトレジスタの回路図である。

【図13】実施の形態4に係る単位シフトレジスタの回路図である。

【図14】実施の形態5に係る単位シフトレジスタの回路図である。

【図15】実施の形態5に係る単位シフトレジスタから成る多段のシフトレジスタの構成を示す図である。

【図16】実施の形態5の変形例である単位シフトレジスタの回路図である。

30

【図17】実施の形態6に係る単位シフトレジスタの回路図である。

【図18】実施の形態7に係る単位シフトレジスタの回路図である。

【図19】実施の形態8に係る単位シフトレジスタの回路図である。

【図20】実施の形態8の変形例である単位シフトレジスタの回路図である。

【図21】実施の形態8の変形例である単位シフトレジスタの回路図である。

【図22】実施の形態8の変形例である単位シフトレジスタの回路図である。

【図23】デュアルゲートトランジスタにおけるオーバラップ容量の分布を示す図である。

。

【図24】実施の形態9に係るデュアルゲートトランジスタの構成を示す図である。

【図25】実施の形態9に係るデュアルゲートトランジスタの構成を示す図である。

40

【図26】実施の形態10に係るデュアルゲートトランジスタの構成を示す図である。

【図27】実施の形態11に係るデュアルゲートトランジスタの構成を示す図である。

【図28】実施の形態12に係るデュアルゲートトランジスタの構成を示す図である。

【図29】実施の形態12に係る単位シフトレジスタの回路図である。

### 【符号の説明】

#### 【0175】

Q1～Q14 トランジスタ、Q3D, Q4D, Q10D デュアルゲートトランジスタ、CK1, CK2 クロック端子、RST リセット端子、S1 第1電源端子、S2 第2電源端子、IN1, IN2 入力端子、OUT 出力端子、TA 第1制御端子、TB 第2制御端子、TN 第1電圧信号端子、TR 第2電圧信号端子、C1～C6

50

容量素子、D1, D2 ダイオード。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 11】

【図 10】

【図 12】

【図 13】

【図 14】

【図15】

【 図 1 6 】

【 図 17 】

【 図 1 8 】

【 四 20 】

【図19】

〔 図 2-1 〕

【図22】

【図23】

Cstr : 寄生容量

$C_{gso}(Q3a)$ ,  $C_{gdo}(Q3a)$  : オーバラップ容量

$C_{gso}(Q3b)$ ,  $C_{gdo}(Q3b)$  : オーバラップ容量

【図24】

15 : パソコンQ3aのドレイン電極

16 : パソコンQ3bのドレイン電極

17 : パソコンQ3a, Q3bのソース電極

【図25】

151 : パソコンQ3aのドレイン領域

161 : パソコンQ3bのドレイン領域

171 : パソコンQ3a, Q3bのソース領域

(b)

【図26】

【図27】

【図28】

【図29】

## フロントページの続き

| (51)Int.Cl. |        | F I                   |

|-------------|--------|-----------------------|

| H 0 1 L     | 27/088 | (2006.01)             |

| G 0 9 G     | 3/20   | (2006.01)             |

| G 1 1 C     | 19/28  | (2006.01)             |

| G 1 1 C     | 19/00  | (2006.01)             |

| G 0 9 G     | 3/36   | (2006.01)             |

|             |        | H 0 1 L 27/08 1 0 2 A |

|             |        | G 0 9 G 3/20 6 2 3 H  |

|             |        | G 0 9 G 3/20 6 2 2 E  |

|             |        | G 0 9 G 3/20 6 7 0 J  |

|             |        | G 0 9 G 3/20 6 7 0 E  |

|             |        | G 1 1 C 19/28 D       |

|             |        | G 1 1 C 19/00 G       |

|             |        | G 1 1 C 19/00 J       |

|             |        | G 0 9 G 3/36          |

(72)発明者 村井 博之

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

(72)発明者 森 成一郎

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

審査官 石田 勝

(56)参考文献 特開2006-107692(JP,A)

特開昭58-188396(JP,A)

特開2003-101406(JP,A)

特開2005-251335(JP,A)

B.Razavi著、黒田忠広監訳、「アナログCMOS集積回路の設計 基礎編」、日本、丸善株式会社、2006年 3月10日、初版第7刷、52頁、トランジスタの置き換え

## (58)調査した分野(Int.Cl., DB名)

|         |               |

|---------|---------------|

| H 0 3 K | 3 / 3 5 6     |

| G 0 9 G | 3 / 2 0       |

| G 0 9 G | 3 / 3 6       |

| G 1 1 C | 1 9 / 0 0     |

| G 1 1 C | 1 9 / 2 8     |

| H 0 1 L | 2 1 / 3 3 6   |

| H 0 1 L | 2 1 / 8 2 3 4 |

| H 0 1 L | 2 7 / 0 8     |

| H 0 1 L | 2 7 / 0 8 8   |

| H 0 1 L | 2 9 / 7 8 6   |