(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6167646号

(P6167646)

(45) 発行日 平成29年7月26日(2017.7.26)

(24) 登録日 平成29年7月7日(2017.7.7)

(51) Int.Cl.

G06F 12/16 (2006.01)

G11C 16/34 (2006.01)

F 1

G06F 12/16 310A

G11C 16/34 166

請求項の数 9 (全 35 頁)

(21) 出願番号 特願2013-96046 (P2013-96046)

(22) 出願日 平成25年4月30日 (2013.4.30)

(65) 公開番号 特開2014-220021 (P2014-220021A)

(43) 公開日 平成26年11月20日 (2014.11.20)

審査請求日 平成28年1月13日 (2016.1.13)

(73) 特許権者 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

(74) 代理人 100089118

弁理士 酒井 宏明

(72) 発明者 日下田 雅紀

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

(72) 発明者 早坂 和美

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

審査官 堀田 和義

最終頁に続く

(54) 【発明の名称】情報処理装置、制御回路、制御プログラム、および制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

記憶装置と、

前記記憶装置が有する複数の記憶領域の各々に記憶されたデータが移動の対象であるか判定する処理が、前記記憶装置が記憶する全てのデータに対して実行されるとカウント値を更新する計数部と、

前記記憶装置にデータが書き込まれる際に、前記計数部のカウント値を前記データと対応付けて記憶する計数値記憶部と、

前記記憶装置が記憶するデータごとに、前記計数値記憶部が記憶する値と前記計数部のカウント値とを比較して、各データが移動の対象であるか判定する判定部と、

前記記憶装置に対して発行されたデータの読み出し要求、または、前記記憶装置に対して発行されたデータの書き込み要求の数を計数する要求計数部と、

前記要求計数部が計数した前記読み出し要求の数、または、前記書き込み要求の数に応じて、前記データが移動の対象であるか判定するための閾値を設定する設定部と、

を有し、

前記判定部は、前記計数部のカウント値に前記設定部が設定した閾値を加算した値が、前記計数値記憶部が記憶する値以上となる場合は、当該値と対応付けて前記計数値記憶部が記憶するデータが移動の対象であると判定する、

ことを特徴とする情報処理装置。

## 【請求項 2】

10

20

前記計数値記憶部は、前記記憶領域を識別する領域識別子と、前記領域識別子が示す記憶領域にデータが書込まれる際に、前記計数部のカウント値を前記データと対応付けて記憶し、

前記判定部は、前記領域識別子ごとに、前記計数値記憶部が記憶する値と前記計数部のカウント値とを比較して、前記領域識別子が示す記憶領域に書込まれたデータが移動の対象であるか判定することを特徴とする請求項1に記載の情報処理装置。

【請求項3】

前記判定部は、前記記憶装置が記憶する各データが移動の対象であるか判定する処理を開始してから所定の時間が経過した場合は、最後に移動の対象であるか判定したデータが書込まれた記憶領域を示す領域識別子を記憶して前記処理を中断し、前記処理を再開する場合は、記憶した前記領域識別子の次番の領域識別子が示す記憶領域に書込まれたデータから前記処理を再開することを特徴とする請求項1または2に記載の情報処理装置。10

【請求項4】

前記判定部は、前記記憶装置が有する複数の記憶領域を複数のグループに分割し、当該グループごとに、前記グループに含まれる記憶領域に書込まれたデータが移動の対象であるか判定する処理を実行することを特徴とする請求項1または2に記載の情報処理装置。

【請求項5】

前記計数部は、更新の結果、前記カウント値が所定の値となった場合は、カウント値を初期値に戻し、

前記判定部は、前記計数部のカウント値に1を加算した値と、前記計数値記憶部が記憶する値とが一致する場合は、当該値と対応付けられたデータが移動の対象であると判定することを特徴とする請求項1～4のいずれか1つに記載の情報処理装置。20

【請求項6】

前記要求計数部は、前記読み出し要求が発行された数、または、前記書き込み要求が発行された数を、前記記憶領域ごとに計数し、

前記設定部は、前記要求計数部が計数した前記読み出し要求の数、または、前記書き込み要求の数に応じて、前記閾値を前記記憶領域ごとに設定し、

前記判定部は、前記記憶装置が有する記憶領域ごとに、前記設定部が設定した閾値と前記計数部のカウント値とを加算した値が、前記記憶領域に書込まれたデータと対応付けて前記計数値記憶部が記憶する値以上となる場合は、前記記憶領域に書込まれたデータが移動の対象であると判定することを特徴とする請求項1～5のいずれか1つに記載の情報処理装置。30

【請求項7】

記憶装置が有する複数の記憶領域の各々に記憶されたデータが移動の対象であるか判定する処理が、前記記憶装置が記憶する全てのデータに対して実行されるとカウント値を更新する計数部と、

前記記憶装置にデータが書込まれる際に、前記計数部のカウント値を前記データと対応付けて記憶する計数値記憶部と、

前記記憶装置が記憶するデータごとに、前記計数値記憶部が記憶する値と前記計数部のカウント値とを比較して、各データが移動の対象であるか判定する判定部と、40

前記記憶装置に対して発行されたデータの読み出し要求、または、前記記憶装置に対して発行されたデータの書き込み要求の数を計数する要求計数部と、

前記要求計数部が計数した前記読み出し要求の数、または、前記書き込み要求の数に応じて、前記データが移動の対象であるか判定するための閾値を設定する設定部と、

を有し、

前記判定部は、前記計数部のカウント値に前記設定部が設定した閾値を加算した値が、前記計数値記憶部が記憶する値以上となる場合は、当該値と対応付けて前記計数値記憶部が記憶するデータが移動の対象であると判定する、

ことを特徴とする前記記憶装置の制御回路。

【請求項8】

コンピュータに、

記憶装置が有する複数の記憶領域の各々に記憶されたデータが移動の対象であるか判定する処理が、前記記憶装置が記憶する全てのデータに対して実行されるとカウント値を更新し、

前記記憶装置にデータが書き込まれる際に、カウント値と前記データとを対応付けて所定の記憶部に記憶し、

前記記憶装置が記憶するデータごとに、前記所定の記憶部が記憶する値と前記カウント値とを比較して、各データが移動の対象であるか判定し、

前記記憶装置に対して発行されたデータの読み出し要求、または、前記記憶装置に対して発行されたデータの書き込み要求の数を計数し、

計数した前記読み出し要求の数、または、前記書き込み要求の数に応じて、前記データが移動の対象であるか判定するための閾値を設定する、各処理を実行させ、

前記判定する処理は、前記計数する処理のカウント値に前記設定する処理が設定した閾値を加算した値が、前記記憶する処理が記憶する値以上となる場合は、当該値と対応付けて前記記憶する処理が記憶するデータが移動の対象であると判定する、

ことを特徴とする制御プログラム。

#### 【請求項 9】

情報処理装置が、

記憶装置が有する複数の記憶領域の各々に記憶されたデータが移動の対象であるか判定する処理が、前記記憶装置が記憶する全てのデータに対して実行されるとカウント値を更新し、

前記記憶装置にデータが書き込まれる際に、カウント値と前記データとを対応付けて所定の記憶部に記憶し、

前記記憶装置が記憶するデータごとに、前記所定の記憶部が記憶する値と前記カウント値とを比較して、各データが移動の対象であるか判定し、

前記記憶装置に対して発行されたデータの読み出し要求、または、前記記憶装置に対して発行されたデータの書き込み要求の数を計数し、

計数した前記読み出し要求の数、または、前記書き込み要求の数に応じて、前記データが移動の対象であるか判定するための閾値を設定する、各処理を実行し、

前記判定する処理は、前記計数する処理のカウント値に前記設定する処理が設定した閾値を加算した値が、前記記憶する処理が記憶する値以上となる場合は、当該値と対応付けて前記記憶する処理が記憶するデータが移動の対象であると判定する、

ことを特徴とする前記記憶装置の制御方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、情報処理装置、制御回路、制御プログラム、および制御方法に関する。

##### 【背景技術】

##### 【0002】

従来、磁気ディスクよりも高速に動作する不揮発性メモリを用いた情報処理装置が知られている。このような情報処理システムの一例として、NANDフラッシュメモリデバイスをストレージ等の記憶装置として使用する情報処理装置が知られている。なお、以下の説明では、NANDフラッシュメモリデバイスをNANDデバイスと記載する。

##### 【0003】

ここで、NANDデバイスの各記憶領域は、情報を消去する際に劣化する。このため、頻繁に更新される情報が書き込まれた記憶領域と、あまり更新されない情報が書き込まれた記憶領域とでは、劣化する速度にばらつきが存在する。また、NANDデバイスは、情報を書き込んだままにしておくと、データを書き込んだ記憶領域の素子から電荷が抜け、ビット化けを発生させる場合がある。

##### 【0004】

かかる記憶領域の劣化を平準化したり、各記憶領域の素子から電荷が抜けることによるビット化けを防ぐため、情報を書込んだ際の時刻を記憶し、記憶した時刻と現在の時刻との比較結果に応じて情報の再書き込みを行う技術が知られている。例えば、情報処理装置は、記憶領域ごとに、情報を書込んだ際の時刻を記憶する。そして、情報処理装置は、記憶した時刻と現在の時刻とを比較し、情報を書込んでから経過した経過時間を演算する。その後、情報処理装置は、経過時間と所定の閾値との比較結果に応じて、情報の再書き込みを実行するか否か判定する。

【先行技術文献】

【特許文献】

【0005】

10

【特許文献1】特開平08-147988号公報

【特許文献2】特開平05-198198号公報

【特許文献3】特開2006-252695号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、上述した情報の再書き込みを実行する技術では、記憶領域ごとに、情報を書込んだ時刻をそのまま記憶するので、経過時間を演算するために記憶する時刻の総情報量が増大するという問題がある。

【0007】

20

例えば、時刻の総情報量が増大した場合は、時刻を記憶する記憶装置の規模が増大するので、情報処理装置の回路規模が増大する。また、時刻の総情報量が増大すると、判定対象となる記憶領域にデータを書込んだ際の時刻を検索する時間が増大するので、NANDデバイスに対するアクセス性能が低下する。

【0008】

1つの側面では、データを書込んだ時刻を示す情報の情報量を削減する情報処理装置、制御回路、制御プログラム、および制御方法を提供することを目的とする。

【課題を解決するための手段】

【0009】

30

一態様の情報処理装置は、記憶装置を有する。また、情報処理装置は、記憶装置が有する複数の記憶領域の各々に記憶されたデータが移動の対象であるか判定する処理が、記憶装置が記憶する全てのデータに対して実行されるとカウント値を更新する計数部を有する。また、情報処理装置は、記憶装置にデータが書き込まれる際に、計数部のカウント値をデータと対応付けて記憶する計数値記憶部を有する。また、情報処理装置は、記憶装置が記憶するデータごとに、計数値記憶部が記憶する値と計数部のカウント値とを比較して、各データが移動の対象であるか判定する判定部を有する。また、情報処理装置は、記憶装置に対して発行されたデータの読み出し要求、または、記憶装置に対して発行されたデータの書き込み要求の数を計数する要求計数部を有する。また、情報処理装置は、要求計数部が計数した読み出し要求の数、または、書き込み要求の数に応じて、データが移動の対象であるか判定するための閾値を設定する設定部を有する。また、判定部は、計数部のカウント値に設定部が設定した閾値を加算した値が、計数値記憶部が記憶する値以上となる場合は、当該値と対応付けて計数値記憶部が記憶するデータが移動の対象であると判定する。

【発明の効果】

【0010】

一実施形態によれば、データを書込んだ時刻を示す情報の情報量を削減できる。

【図面の簡単な説明】

【0011】

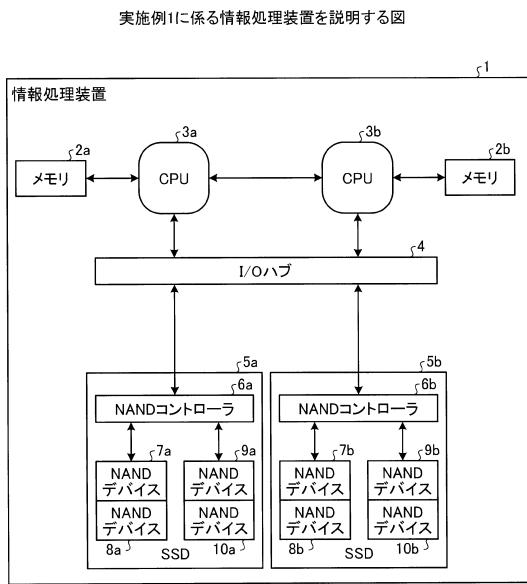

【図1】図1は、実施例1に係る情報処理装置を説明する図である。

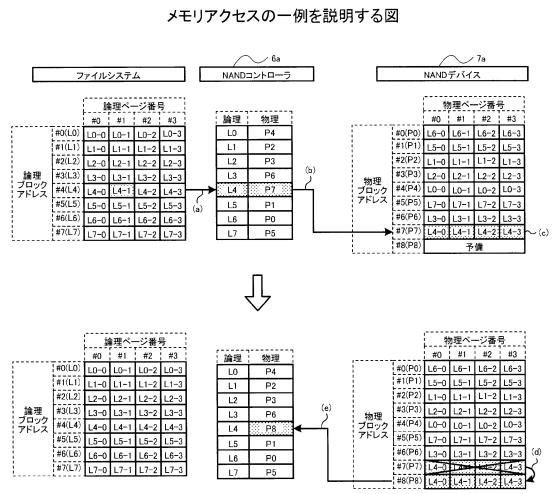

【図2】図2は、メモリアクセスの一例を説明する図である。

【図3】図3は、従来のNANDコントローラが実行する処理の一例を説明する図である

40

50

。

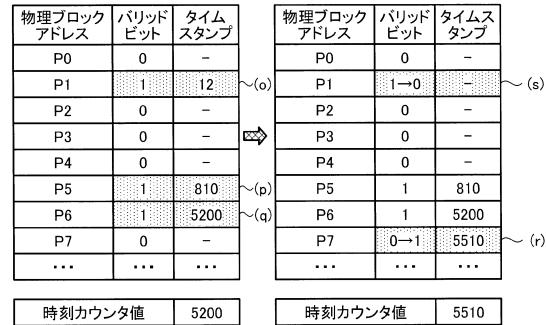

【図4】図4は、従来のタイムスタンプを用いた処理を説明する図である。

【図5】図5は、従来のタイムスタンプを用いた処理の問題を説明する図である。

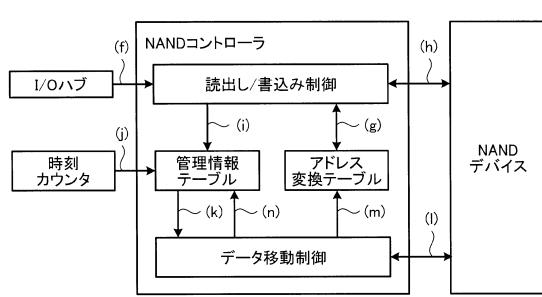

【図6】図6は、実施例1に係るNANDコントローラの機能構成を説明する図である。

【図7】図7は、実施例1に係るアドレス変換テーブルに格納された情報の一例を説明する図である。

【図8】図8は、実施例1に係る管理情報テーブルに格納された情報の一例を説明する図である。

【図9】図9は、NANDコントローラが実行する処理を説明する図である。

【図10】図10は、データ移動制御を説明する図である。

10

【図11】図11は、実施例1に係るNANDコントローラが実行する処理の流れを説明するフローチャートである。

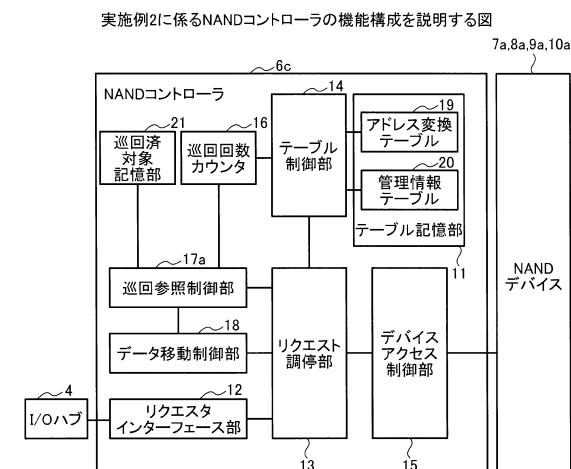

【図12】図12は、実施例2に係るNANDコントローラの機能構成を説明する図である。

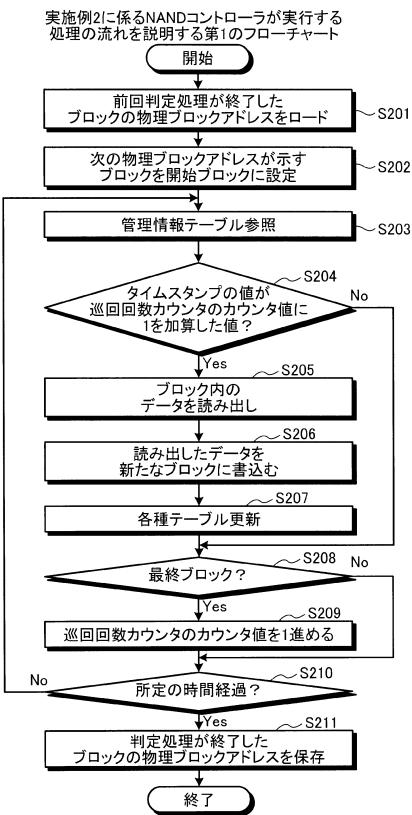

【図13】図13は、実施例2に係るNANDコントローラが実行する処理の流れを説明する第1のフローチャートである。

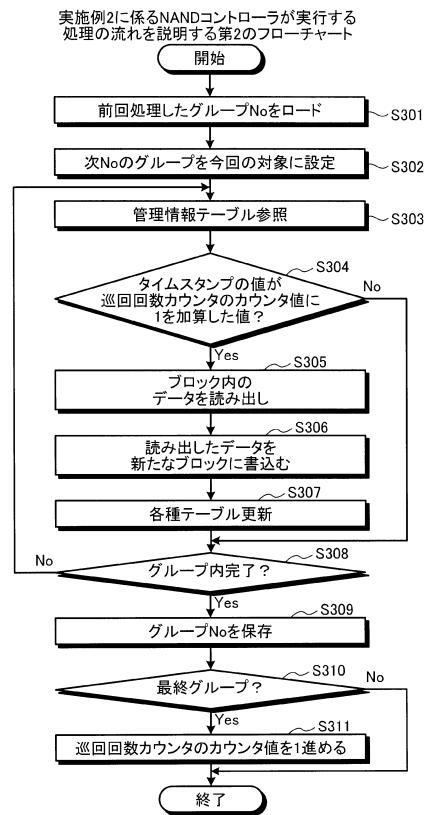

【図14】図14は、実施例2に係るNANDコントローラが実行する処理の流れを説明する第2のフローチャートである。

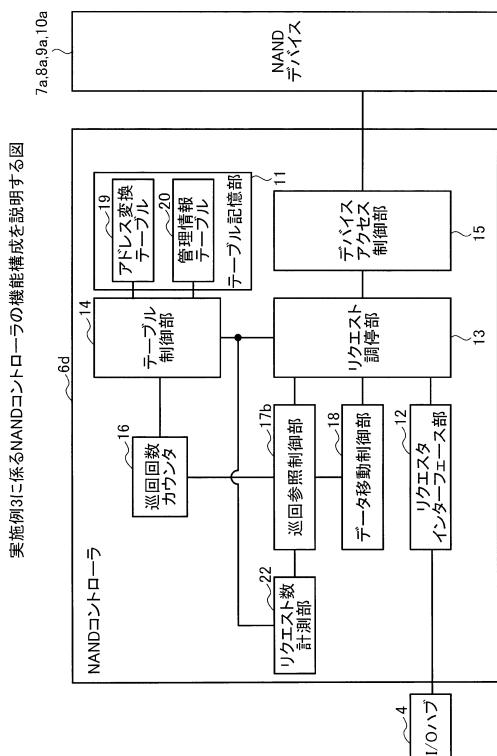

【図15】図15は、実施例3に係るNANDコントローラの機能構成を説明する図である。

20

【図16】図16は、平均要求発行数に応じた閾値の一例を説明する図である。

【図17】図17は、実施例3に係るNANDコントローラが実行する処理の流れを説明するフローチャートである。

【図18】図18は、書きビットを用いた処理の一例を説明する図である。

【図19】図19は、制御プログラムを実行するNANDコントローラの一例を説明する図である。

【発明を実施するための形態】

【0012】

以下に添付図面を参照して本願に係る情報処理装置、制御回路、制御プログラム、および制御方法の実施例を図面に基づいて詳細に説明する。なお、以下の実施例により開示技術が限定されるものではない。また、各実施例は、矛盾しない範囲で適宜組みあわせてよい。

30

【実施例1】

【0013】

以下の実施例1では、図1を用いて、本願に係る情報処理装置の一例を説明する。図1は、実施例1に係る情報処理装置を説明する図である。図1に示す例では、情報処理装置1は、複数のメモリ2a、2b、複数のCPU(Central Processing Unit)3a、3b、I/O(Input Output)ハブ4、複数のSSD(Solid State Drive)5a、5bを有する。また、SSD5aは、NANDコントローラ6a、および複数のNANDデバイス7a～10aを有する。

40

【0014】

また、SSD5bは、NANDコントローラ6b、および複数のNANDデバイス7b～10bを有する。なお、以下の説明では、NANDコントローラ6b、および複数のNANDデバイス7b～10bは、NANDコントローラ6a、および複数のNANDデバイス7a～10aと同様の機能を発揮するものとして、説明を省略する。

【0015】

各メモリ2a、2bは、各CPU3a、3bが演算処理に用いるデータを記憶する記憶装置である。また、各CPU3a、3bは、メモリ2a、2bが記憶するデータを用いて、各種演算処理を行う演算処理装置である。例えば、CPU3a、3bは、NUMA(No n-Uniform Memory Access)の技術を用いて、メモリ2a、2bが記憶するデータを取

50

得し、取得したデータを用いて演算処理を実行する。

【0016】

また、CPU3a、3bは、I/Oハブ4を介して、各SSD5a、5bが記憶するデータを取得し、取得したデータを用いて演算処理を実行する。詳細には、CPU3aは、SSD5aに対し、データの読み出し要求や書き込み要求を発行し、各NANDデバイス7a～10aからデータの読み出しや書き込みを行う。例えば、CPU3aは、SSD5aに対し、読み出し対象となるデータを指定する論理アドレスが格納された読み出し要求を発行する。また、CPU3aは、データの書き込み先を指定する論理アドレスと、書き込み対象となるデータとが格納された書き込み要求を発行する。

【0017】

NANDデバイス7aは、各種データを記憶する不揮発性メモリである。詳細には、NANDデバイス7aは、データの記憶領域であるページを複数有し、ページ単位でデータの書き込みを行う。また、NANDデバイス7aは、複数のページを有するブロックを複数有し、ブロック単位でデータの消去を行う。

【0018】

NANDコントローラ6aは、各NANDデバイス7a～10aに対してアクセスし、データの読み出しや書き込みを行う。例えば、NANDコントローラ6aは、各CPU3a、3bがデータが記憶された記憶領域を指定する際に用いる論理アドレスと、データが格納されたNANDデバイス7a～10aの記憶領域を示す物理アドレスとを対応付けたアドレス変換テーブルを有する。

【0019】

そして、NANDコントローラ6aは、読み出し要求とともに論理アドレスを受信すると、アドレス変換テーブルを用いて、論理アドレスと対応付けられた物理アドレスを識別し、識別した物理アドレスが示す記憶領域からデータの読み出しを行う。その後、NANDコントローラ6aは、I/Oハブ4を介して、読み出したデータをCPU3aに送信する。

【0020】

なお、以下の説明では、理解を容易にするため、各ページの先頭アドレスとなる論理アドレスを単に論理アドレスと記載し、各ページの先頭アドレスとなる物理アドレスを単に物理アドレスと記載する。また、情報処理装置1が実行するシステムは、各ページの先頭アドレスとなる論理アドレスに対する読み出し要求や書き込み要求を発行するものとする。

【0021】

例えば、NANDコントローラ6aは、NANDデバイス7a～10aが、複数のブロックを有し、各ブロックに $2^q$ 個のページが含まれている場合は、以下の処理を行う。まず、NANDコントローラ6aは、論理アドレスの下位qビットを論理的な1つのブロック内において、ページを識別するための論理ページ番号とし、残りの論理アドレスの上位pビットを論理的な1つのブロックを示す論理ブロックアドレスとする。

【0022】

また、NANDコントローラ6aは、物理アドレスの上位pビットを物理的な1つのブロックを示す物理ブロックアドレスとし、物理アドレスの下位qビットを物理的な1つのブロック内において、各ページを識別するための物理ページ番号とする。つまり、NANDコントローラ6aは、論理アドレスを、論理ブロックを示す論理ブロックアドレスと、論理ページを論理ブロックごとに示す論理ページ番号とに分割する。また、NANDコントローラ6aは、物理アドレスを、物理ブロックを示す物理ブロックアドレスと、物理ページを物理ブロックごとに示す物理ページ番号とに分割する。

【0023】

例えば、図2は、メモリアクセスの一例を説明する図である。なお、図2に示す例では、理解を容易にするため、ブロック数を「8」とし、各ブロック内のページ数が「4」のNANDデバイス7aについて記載した。また、図2に示す例では、論理ブロックアドレスと物理ブロックアドレスとを対応付けたアドレス変換テーブルを有するNANDコントローラ6aが実行する処理について記載した。

10

20

30

40

50

## 【0024】

例えば、CPU3aが実行するファイルシステムは、図2中(a)に示すように、論理ロックアドレス「L4」に含まれる論理ページのうち、論理ページ番号「1」が示す論理ページに対する書き込み要求を発行する。すなわち、ファイルシステムは、論理アドレス「L4-1」に対する書き込み要求を発行する。すると、NANDコントローラ6aは、図2中(b)に示すように、論理ロックアドレス「L4」に対応付けられた物理ロックアドレス「P7」を取得し、図2中(c)に示すように、書き込み対象となるページを含むブロックを識別する。

## 【0025】

続いて、NANDコントローラ6aは、図2中(d)に示すように、物理ロックアドレス「P7」が示す物理ロックの全データを予備ブロックにコピーする。この際、NANDコントローラ6aは、書き込み要求の対象となる論理ページ番号「1」と同じ物理ページ番号「1」のデータを書き込み対象となるデータで更新する。その後、NANDコントローラ6aは、図2中(e)に示すように、論理ロックアドレス「L4」と対応付けられていた物理ロックアドレス「P7」を予備ブロックの物理ロックアドレス「P8」に更新する。そして、NANDコントローラ6aは、物理ロックアドレス「P7」が示すブロックのデータを消去する。

## 【0026】

ここで、従来のNANDコントローラは、劣化速度のばらつきを平準化したり、電荷が素子から抜けることで発生するビット化けを防ぐため、NANDデバイスの各ブロックにデータを書き込んだ際の時刻をタイムスタンプとして記憶する。そして、従来のNANDコントローラは、各ブロックについて、記憶したタイムスタンプと現在の時刻との差が所定の閾値よりも大きい場合は、ブロックに格納されたデータを他のブロックに移動することで、データの再書き込みを行う。

## 【0027】

以下、図3を用いて、従来のNANDコントローラが実行する処理の一例を説明する。図3は、従来のNANDコントローラが実行する処理の一例を説明する図である。例えば、NANDコントローラは、図3中(f)に示すように、I/Oハブから読み出し又は書き込み要求を受信する。すると、NANDコントローラは、読み出し/書き込み制御を実行する。例えば、NANDコントローラは、図3中(g)に示すように、アドレス変換テーブルを用いて論理アドレスを物理アドレスに変換する。そして、NANDコントローラは、図3中(h)に示すように、変換後の論理アドレスを用いて、NANDデバイスに対する読み出しや書き込み処理を実行する。

## 【0028】

ここで、NANDコントローラは、NANDデバイスが有する各ブロックの物理アドレスと、データの書き込みを行ったか否かを示すバリッドビットと、データの書き込みを行った時刻を示すタイムスタンプとを対応付けた管理情報テーブルを有する。そして、NANDコントローラは、NANDデバイスに対する書き込み処理を実行した場合は、図3中(i)に示すように、書き込み処理を行った時刻と、データを書き込んだブロックと、バリッドビットとを対応付けて管理情報テーブルに格納する。例えば、NANDコントローラは、図3中(j)に示すように、データの書き込みを行った際に時刻カウンタがカウントしていた時刻と、データの書き込みを行ったブロックの物理ロックアドレスと、バリッドビット「1」とを対応付けて管理情報テーブルに格納する。

## 【0029】

また、NANDコントローラは、データ移動制御を実行する。例えば、NANDコントローラは、図3中(k)に示すように、管理情報テーブルに格納された時刻と、時刻カウンタがカウントする現在の時刻とを比較し、書き込まれてから所定の時間が経過したデータを識別する。そして、NANDコントローラは、図3中(l)に示すように、識別したデータを他のブロックに移動させる。その後、NANDコントローラは、図3中(m)に示すように、データの移動に応じて、アドレス変換テーブルを更新し、図3中(n)に示す

10

20

30

40

50

ように、管理情報テーブルを更新する。

【0030】

次に、図4を用いて、従来のNANDコントローラが、タイムスタンプを用いて移動するデータを識別する処理について説明する。図4は、従来のタイムスタンプを用いた処理を説明する図である。なお、図4には、従来のNANDコントローラが有する管理情報テーブルの内容と、時刻カウンタがカウントする値とを記載した。

【0031】

例えば、NANDコントローラは、時刻カウント値が「12」の際に、物理ブロックアドレス「P1」が示すブロックにデータを書込んだ場合は、以下の処理を実行する。すなわち、NANDコントローラは、図4中(○)に示すように、物理ブロックアドレス「P1」とバリッドビット「1」とタイムスタンプ「12」を対応付けて格納する。 10

【0032】

また、NANDコントローラは、時刻カウント値が「810」の際に物理ブロックアドレス「P5」が示すブロックにデータを書込んだ場合は、以下の処理を実行する。すなわち、NANDコントローラは、図4中(p)に示すように、物理ブロックアドレス「P5」とバリッドビット「1」とタイムスタンプ「810」とを対応付けて管理情報テーブルに格納する。

【0033】

また、NANDコントローラは、時刻カウント値が「5200」の際に物理ブロックアドレス「P6」が示すブロックにデータを書込んだ場合は、以下の処理を実行する。すなわち、NANDコントローラは、図4中(q)に示すように、物理ブロックアドレス「P6」とバリッドビット「1」とタイムスタンプ「5200」とを対応付けて管理情報テーブルに格納する。 20

【0034】

また、NANDコントローラは、所定の時間間隔で、管理情報テーブルに格納された各タイムスタンプの値を参照し、タイムスタンプの値と現在の時刻カウンタの値との差が所定の閾値よりも大きい物理ブロックを識別する。例えば、図4に示す例では、NANDコントローラは、現在の時刻カウンタの値「5510」との差分が大きいタイムスタンプ「12」が対応付けられた物理ブロックアドレス「P1」を識別する。そして、NANDコントローラは、物理ブロックアドレス「P1」が示すブロックのデータを、例えば、物理ブロックアドレス「P7」が示すブロックに移動させる。 30

【0035】

その後、NANDコントローラは、図4中(r)に示すように、物理ブロックアドレス「P7」と対応付けられたバリッドビットを「1」に更新し、タイムスタンプとして現在の時刻の値「5510」を対応付ける。また、NANDコントローラは、図4中(s)に示すように、物理ブロックアドレス「P1」と対応付けられたバリッドビットを「0」に更新し、タイムスタンプの値を削除する。

【0036】

しかしながら、従来のNANDコントローラは、各物理ブロックアドレスごとに、タイムスタンプを記憶するので、管理情報テーブルのデータサイズを増大させてしまう。例えば、NANDコントローラは、1ページの大きさが8キロバイトで、1つのブロックに128ページが含まれる場合は、1メガバイトごとに複数桁のタイムスタンプを管理情報テーブルに格納する。このため、NANDデバイス7a~10aの容量が多くなるほど、管理情報テーブルのサイズが大きくなる。この結果、従来のNANDコントローラは、管理情報テーブルを記憶するために回路規模が増大したり、タイムスタンプを参照する際の時間が増大し、NANDデバイスに対するアクセス性能を低下させてしまう。 40

【0037】

なお、管理情報テーブルのデータサイズを減少させるため、所定の桁数で時刻カウンタの値を初期値に戻す方法が考えられる。しかしながら、所定の桁数で時刻カウンタの値を初期値に戻した場合は、時刻カウンタの値が一巡した際に、誤動作が発生する場合がある 50

。以下、図5を用いて、時刻カウンタの値が一巡した際に発生する誤動作の一例について説明する。

【0038】

図5は、従来のタイムスタンプを用いた処理の問題を説明する図である。なお、図5に示す例では、時刻カウンタの値が「9999」で桁あふれを起こし、初期値「0」に戻る例について説明する。例えば、NANDコントローラは、図5中(t)に示すように、時刻カウンタの値が「12」、「810」、「5200」の際に、物理ブロックアドレス「P1」、「P5」、「P6」が示すブロックにデータを書込んだ旨を管理情報テーブルに格納する。

【0039】

続いて、NANDコントローラは、図5中(u)に示すように、時刻カウンタの値が「8100」の際に、物理ブロックアドレス「P2」が示すブロックにデータを書込んだ旨を管理情報テーブルに格納する。また、NANDコントローラは、時刻カウンタの値が一巡し、「35」となった際に、物理ブロックアドレス「P3」が示すブロックにデータを書込んだ旨を管理情報テーブルに格納する。

【0040】

そして、NANDコントローラは、図5中(v)に示すように、時刻カウンタの値が「50」の際に、各タイムスタンプの値を参照し、時刻カウンタの値が一巡することを考慮して、時刻カウンタの値「50」と差分が大きいタイムスタンプを検索する。ここで、NANDデバイス7a～10aが記憶するデータのうち、最も古いデータは、タイムスタンプ「12」と対応付けられた物理ブロックアドレス「P1」が示すブロックに格納されたデータである。

【0041】

しかしながら、NANDコントローラは、優先度が高い読み出し要求や書き込み要求が集中して発行された際に、データの移動処理が延期された場合や、移動処理の完了が遅れた場合には、時刻カウンタの値がタイムスタンプの値を追い越す場合がある。かかる場合は、NANDコントローラは、タイムスタンプの値が、時刻カウンタの値が一巡する前の値であるか否かを判別できない。

【0042】

この結果、NANDコントローラは、図5中(w)に示すように、物理ブロックアドレス「P5」と対応付けられたタイムスタンプの値「810」が最も古いタイムスタンプの値であると判定する。そして、NANDコントローラは、物理ブロックアドレス「P5」と対応付けられたタイムスタンプの値「810」を削除する。また、NANDコントローラは、図5中(x)に示すように、物理ブロックアドレス「P5」が示すブロックに格納されていたデータを、物理ブロックアドレス「P7」が示すブロックに移動させる。

【0043】

このように、従来のNANDコントローラは、図5中(y)に示すように、物理ブロックアドレス「P1」が示すブロックに格納されたデータが最も古いデータであるにもかかわらず、古いデータであると検出できない。そこで、実施例1に係るNANDコントローラ6aは、以下の処理を実行する。

【0044】

まず、NANDコントローラ6aは、NANDデバイス7a～10aが記憶するデータが移動の対象であるか判定する処理が、全てのデータに対して実行されると、カウント値を更新する巡回回数カウンタを有する。また、NANDコントローラ6aは、NANDデバイス7a～10aにデータを書込む際に、巡回回数カウンタのカウント値を記憶する。詳細には、NANDコントローラ6aは、データの書き込み先となるブロックの物理ブロックアドレスと巡回回数カウンタのカウント値とを対応付けて記憶する。

【0045】

そして、NANDコントローラ6aは、データごとに、データが格納された物理ブロックアドレスと対応付けて記憶するカウント値と、巡回回数カウンタのカウント値とを比較

10

20

30

40

50

して、各ブロックのデータが移動の対象であるか判定する。この結果、NANDコントローラ6aは、巡回回数カウンタが計数するカウント値の桁数を少なくしても、データ書き込み時やデータ移動時に記憶したカウント値を追越す状態を防ぐことができる。

#### 【0046】

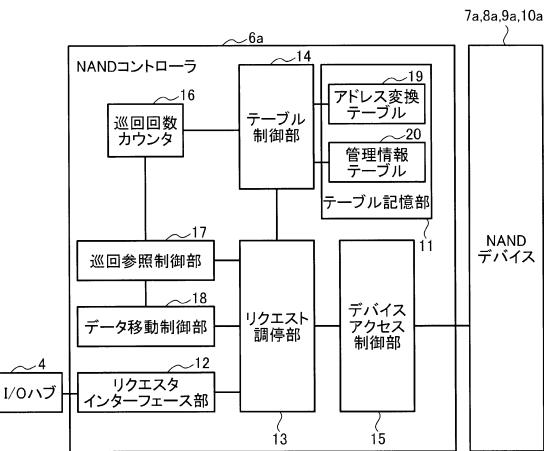

次に、図6を用いて、NANDコントローラ6aが有する機能構成の一例について説明する。図6は、実施例1に係るNANDコントローラの機能構成を説明する図である。図6に示す例では、NANDコントローラ6aは、テーブル記憶部11、リクエスタインターフェース部12、リクエスト調停部13、テーブル制御部14、デバイスアクセス制御部15を有する。また、NANDコントローラ6aは、巡回回数カウンタ16、巡回参照制御部17、データ移動制御部18を有する。また、テーブル記憶部11は、アドレス変換テーブル19、管理情報テーブル20を記憶する。10

#### 【0047】

まず、図7、図8を用いて、テーブル記憶部11が記憶するアドレス変換テーブル19と、管理情報テーブル20に格納された情報について説明する。図7は、実施例1に係るアドレス変換テーブルに格納された情報の一例を説明する図である。図7に示すように、アドレス変換テーブル19には、論理ブロックアドレスと、物理ブロックアドレスとが対応付けて格納されている。

#### 【0048】

例えば、図7に示す例では、アドレス変換テーブル19には、論理ブロックアドレス「L0」と物理ブロックアドレス「P4」とが対応付けて格納されている。すなわち、アドレス変換テーブル19は、物理ブロックアドレス「P4」が示すブロックに論理ブロックアドレス「L0」が指定するデータが格納されている旨を示。20

#### 【0049】

同様に、図7に示す例では、アドレス変換テーブル19には、論理ブロックアドレス「L1」と物理ブロックアドレス「P2」とが対応付けて格納され、論理ブロックアドレス「L2」と物理ブロックアドレス「P3」とが対応付けて格納される。また、アドレス変換テーブル19には、論理ブロックアドレス「L3」と物理ブロックアドレス「P6」とが対応付けて格納され、論理ブロックアドレス「L4」と物理ブロックアドレス「P7」とが対応付けて格納される。

#### 【0050】

また、アドレス変換テーブル19には、論理ブロックアドレス「L5」と物理ブロックアドレス「P1」とが対応付けて格納され、論理ブロックアドレス「L6」と物理ブロックアドレス「P0」とが対応付けて格納される。また、アドレス変換テーブル19には、論理ブロックアドレス「L7」と物理ブロックアドレス「P5」とが対応付けて格納される。30

#### 【0051】

次に、図8を用いて、管理情報テーブル20に格納される情報について説明する。図8は、実施例1に係る管理情報テーブルに格納された情報の一例を説明する図である。図8に示すように、管理情報テーブル20には、物理ブロックアドレスと、バリッドビットと、タイムスタンプとが対応付けて格納される。ここで、バリッドビットとは、対応付けられた物理ブロックアドレスが示すブロックにデータが書き込まれているか否かを示す情報である。また、タイムスタンプとは、対応付けられた物理ブロックアドレスが示すブロックにデータを書き込んだ際に、巡回回数カウンタ16がカウントしていたカウント値である。すなわち、NANDコントローラ6aは、データを書き込んだ際のカウント値を物理ブロックアドレスと対応付けて記憶する。40

#### 【0052】

例えば、図8に示す例では、管理情報テーブル20には、物理ブロックアドレス「P0」と、バリッドビット「1」と、タイムスタンプ「2」とが対応付けて格納される。すなわち、管理情報テーブル20は、物理ブロックアドレス「P0」が示す記憶領域に対し、巡回回数カウンタ16のカウント値が「2」であったことを示す。50

## 【0053】

同様に、図8に示す例では、管理情報テーブル20には、物理ブロックアドレス「P1」と、バリッドビット「1」と、タイムスタンプ「7」とが対応付けて格納される。また、管理情報テーブル20には、物理ブロックアドレス「P5」と、バリッドビット「1」と、タイムスタンプ「7」とが対応付けて格納される。このように、管理情報テーブル20には、データが書込まれた際の巡回回数カウンタ16の値が格納される。なお、管理情報テーブル20を記憶するテーブル記憶部11は、特許請求の範囲に記載の計数値記憶部の一例である。

## 【0054】

図6に戻り、リクエスタインターフェース部12は、CPU3a、3bからNANDデバイス7a～10aに対するリクエストのインターフェースである。例えば、リクエスタインターフェース部12は、CPU3a、3bからI/Oハブ4を介して、論理アドレスを含む読み出し要求を受信する。かかる場合は、リクエスタインターフェース部12は、読み出し要求をリクエスト調停部13に出力する。また、リクエスタインターフェース部12は、NANDデバイス7a～10aから読み出したデータをリクエスト調停部13から受信すると、読み出し要求の発行元となるCPU3a、3bに対して、データを送信する。

10

## 【0055】

また、リクエスタインターフェース部12は、CPU3a、3bから、NANDデバイス7a～10aに対して書込むデータと、書込み対象となるデータの論理アドレスとを含む書込み要求を受信する。かかる場合は、リクエスタインターフェース部12は、受信した書込み要求をリクエスト調停部13に出力する。また、リクエスタインターフェース部12は、リクエスト調停部13から、データ書込みが完了した旨の応答を受信すると、受信した応答を、書込み要求の発行元となるCPU3a、3bに対して、応答を送信する。

20

## 【0056】

リクエスト調停部13は、リクエスタインターフェース部12、データ移動制御部18、巡回参照制御部17が発行する各種リクエストの調停を行う。詳細には、リクエスト調停部13は、リクエスタインターフェース部12から受信する読み出し要求、又は、書込み要求を受信する。また、リクエスト調停部13は、データ移動制御部18から、NANDデバイス7a～10aが記憶するデータを、現在記憶するブロックから他のブロックに移動するよう要求する移動要求を受信する。また、リクエスト調停部13は、巡回参照制御部17から、管理情報テーブル20の参照を要求するテーブル参照要求を受信する。

30

## 【0057】

そして、リクエスト調停部13は、リクエスタインターフェース部12、データ移動制御部18、巡回参照制御部17から受信する読み出し要求、書込み要求、移動要求、テーブル参照要求の調停を行う。例えば、リクエスト調停部13は、CPU3a、3bからNANDデバイス7a～10aに対するデータの読み出しや書込みが阻害されないよう、リクエスタインターフェース部12が発行する読み出し要求、および、書込み要求を最優先で実行する。また、例えば、リクエスト調停部13は、移動要求をテーブル参照要求よりも優先して実行する。なお、リクエスト調停部13が各要求を調停するルールについては、上述した処理に限定されるものではなく、任意のルールを適用してよい。

40

## 【0058】

以下、リクエスト調停部13が読み出し要求、書込み要求、移動要求、テーブル参照要求を受信した際に実行する処理の一例を説明する。例えば、リクエスト調停部13は、読み出し要求を受信すると、読み出し要求に含まれる論理アドレスをテーブル制御部14に出力する。そして、リクエスト調停部13は、テーブル制御部14から、読み出し対象となる物理アドレスを受信すると、受信した物理アドレスを格納した読み出し要求をデバイスアクセス制御部15に発行する。その後、リクエスト調停部13は、読み出し対象となるデータをデバイスアクセス制御部15から受信すると、受信したデータをリクエスタインターフェース部12に出力する。

## 【0059】

50

また、リクエスト調停部13は、書込み要求を受信すると、書込み要求に含まれる論理アドレスをテーブル制御部14に出力する。この結果、リクエスト調停部13は、書込み対象のデータが新たなデータである場合は、データが格納されていない予備ブロックのうち、データの書込み先となるページの物理アドレスをテーブル制御部14から受信する。

#### 【0060】

その後、リクエスト調停部13は、テーブル制御部14から受信した物理アドレスと、書込み対象のデータとを含む書込み要求をデバイスアクセス制御部15に発行する。また、リクエスト調停部13は、データの書込み先となるページの物理アドレスと、書込み要求に含まれる論理アドレスとを含むテーブル更新要求をテーブル制御部14に出力する。

#### 【0061】

また、リクエスト調停部13は、書込みがデータの更新を目的とする場合は、更新元のデータが格納されたページの物理アドレスを更新元物理アドレスとしてテーブル制御部14から受信する。また、リクエスト調停部13は、テーブル制御部14から、予備ブロックに含まれるページの物理アドレス、すなわちデータの書込み先となるページの物理アドレスを更新先物理アドレスとして受信する。

#### 【0062】

そして、リクエスト調停部13は、更新元物理アドレスと、更新先物理アドレスとをテーブル制御部14から受信した場合は、データの更新を要求する更新要求をデバイスアクセス制御部15に発行する。詳細には、リクエスト調停部13は、更新元物理アドレスと、更新先物理アドレスと、書込むデータとを含む更新要求をデバイスアクセス制御部15に発行する。

#### 【0063】

また、リクエスト調停部13は、更新元物理アドレスと、更新先物理アドレスと、書込み要求に含まれる論理アドレスとを含むテーブル更新要求をテーブル制御部14に出力する。その後、リクエスト調停部13は、デバイスアクセス制御部15からデータの書込みが完了した旨の応答を受信すると、受信した応答をリクエスタインターフェース部12に出力する。

#### 【0064】

また、リクエスト調停部13は、移動対象のデータが格納されたブロックの物理ブロックアドレスを含む移動要求を受信する。以下、移動対象のデータが格納されたブロックの物理ブロックアドレスを移動元物理ブロックアドレスと記載する。また、リクエスト調停部13は、テーブル制御部14に問い合わせる等して、予備ブロックの物理ブロックアドレス、すなわちデータの移動先となるブロックの物理ブロックアドレスを移動先物理ブロックアドレスとして取得する。

#### 【0065】

そして、リクエスト調停部13は、移動元物理ブロックアドレスと、移動先物理ブロックアドレスとを含む移動要求をデバイスアクセス制御部15に発行する。また、リクエスト調停部13は、移動元物理ブロックアドレスと、移動先物理ブロックアドレスとを含むテーブル更新要求をテーブル制御部14に出力する。その後、リクエスト調停部13は、デバイスアクセス制御部15からデータの移動が完了した旨の応答を受信すると、データ移動制御部18に対して、データの移動が完了した旨の応答を出力する。

#### 【0066】

また、リクエスト調停部13は、テーブル参照要求を受信した場合は、テーブル制御部14に対し、管理情報テーブル20の参照要求を送信する。そして、リクエスト調停部13は、テーブル制御部14から管理情報テーブル20を受信すると、受信した情報を巡回参照制御部17に出力する。

#### 【0067】

テーブル制御部14は、論理アドレスを物理アドレスに変換する。例えば、テーブル制御部14は、リクエスト調停部13から読み出し要求に格納された論理アドレスを受信すると、受信した論理アドレスに含まれる論理ブロックアドレスを抽出する。また、テーブル

10

20

30

40

50

制御部14は、アドレス変換テーブル19を参照し、抽出した論理プロックアドレスと対応付けられた物理プロックアドレスを取得する。

#### 【0068】

そして、テーブル制御部14は、受信した論理アドレスに含まれる論理ページ番号と、取得した物理プロックアドレスとを組み合わせて物理アドレスを生成する。つまり、テーブル制御部14は、論理アドレスの上位ビットを物理プロックアドレスに変換し、物理プロックアドレスと、論理アドレスの下位ビットとを組み合わせて物理アドレスを生成する。そして、テーブル制御部14は、生成した物理アドレスをリクエスト調停部13に出力する。

#### 【0069】

また、テーブル制御部14は、リクエスト調停部13から書き込み要求に格納された論理アドレスを受信すると、論理プロックアドレスと対応付けられた物理プロックアドレスをアドレス変換テーブル19から検索する。そして、テーブル制御部14は、論理プロックアドレスと対応付けられた物理プロックアドレスがアドレス変換テーブル19に格納されていない場合、すなわち、書き込み対象のデータが新たなデータである場合は、以下の処理を実行する。

#### 【0070】

まず、テーブル制御部14は、管理情報テーブル20を参照し、データが格納されていない物理プロックアドレス、すなわち、予備ブロックの物理プロックアドレスを識別する。例えば、テーブル制御部14は、管理情報テーブル20を参照し、バリッドビット「0」と対応付けられた物理プロックアドレスを検索し、検出した物理プロックアドレスを予備ブロックの物理プロックアドレスとする。そして、テーブル制御部14は、識別した物理プロックアドレスと、受信した論理アドレスの論理ページ番号とを組み合わせた物理アドレスをリクエスト調停部13に出力する。

#### 【0071】

一方、テーブル制御部14は、受信した論理プロックアドレスと対応付けられた物理プロックアドレスがアドレス変換テーブル19に格納されている場合、すなわち、書き込みがデータの更新を目的とする場合は、以下の処理を実行する。まず、テーブル制御部14は、受信した論理プロックアドレスと対応付けられた物理プロックアドレスを取得し、取得した物理プロックアドレスに論理ページ番号を組み合わせた物理アドレスを更新元物理アドレスとしてリクエスト調停部13に出力する。また、テーブル制御部14は、予備ブロックの物理プロックアドレスと、受信した論理アドレスの論理ページ番号とを組み合わせた物理アドレスを更新先物理アドレスとしてリクエスト調停部13に出力する。

#### 【0072】

また、テーブル制御部14は、リクエスト調停部13が移動要求を受信した際には、リクエスト調停部13から予備ブロックの物理プロックアドレスの問い合わせを受ける。かかる場合は、テーブル制御部14は、管理情報テーブル20を参照し、バリッドビット「0」と対応付けられた物理プロックアドレスを識別する。そして、テーブル制御部14は、識別した物理プロックアドレスを移動先物理プロックアドレスとしてリクエスト調停部13に出力する。

#### 【0073】

また、テーブル制御部14は、データの書き込みや移動に応じて、アドレス変換テーブル19、および、管理情報テーブル20の更新を行う。例えば、テーブル制御部14は、リクエスト調停部13が新たなデータの書き込みを行う場合は、データの書き込み先となるページの物理アドレスと、書き込み要求に含まれる論理アドレスとを含むテーブル更新要求を受信する。

#### 【0074】

かかる場合は、テーブル制御部14は、書き込み要求に含まれる論理アドレスから論理プロックアドレスを抽出し、書き込み要求に含まれる物理アドレスから物理プロックアドレスを抽出する。そして、テーブル制御部14は、抽出した論理プロックアドレスと抽出した

10

20

30

40

50

物理ロックアドレスとを対応付けてアドレス変換テーブル19に格納する。

#### 【0075】

また、テーブル制御部14は、管理情報テーブル20のエントリのうち、抽出した物理ロックアドレスが格納されたエントリを抽出し、抽出したエントリに格納されたバリッドビットを「1」に更新する。また、テーブル制御部14は、巡回回数カウンタ16の値を取得し、取得した値をタイムスタンプとして、抽出したエントリに格納する。

#### 【0076】

例えば、テーブル制御部14は、巡回回数カウンタ16のカウント値が「7」である際に、物理ロックアドレス「P1」を含む物理アドレスが格納されたテーブル更新要求を受信する。かかる例では、テーブル制御部14は、物理ロックアドレス「P1」が格納されたエントリを管理情報テーブル20から抽出する。10

#### 【0077】

そして、テーブル制御部14は、抽出したエントリの、バリッドビットを「1」に更新し、タイムスタンプ「7」を格納する。この結果、管理情報テーブル20は、物理ロックアドレス「P1」と、バリッドビット「1」と、タイムスタンプ「7」とを対応付けて記憶する。

#### 【0078】

また、テーブル制御部14は、リクエスト調停部13がデータの更新を行う場合は、更新元物理アドレスと、更新先物理アドレスと、書き込み要求に含まれる論理アドレスとを含むテーブル更新要求を受信する。かかる場合は、テーブル制御部14は、更新元物理アドレスに含まれる物理ロックアドレスを更新元物理ロックアドレスとして抽出し、更新先物理アドレスに含まれる物理ロックアドレスを更新先物理ロックアドレスとして抽出する。また、テーブル制御部14は、テーブル更新要求に含まれる論理アドレスから論理ロックアドレスを抽出する。20

#### 【0079】

また、テーブル制御部14は、論理ロックアドレスが格納されたエントリをアドレス変換テーブル19から抽出する。そして、テーブル制御部14は、抽出したエントリに格納された物理ロックアドレスを、更新先物理ロックアドレスに更新する。

#### 【0080】

また、テーブル制御部14は、管理情報テーブル20から、更新元物理ロックアドレスが格納されたエントリを抽出し、抽出したエントリに格納されたバリッドビットを「0」に更新し、タイムスタンプの値を削除する。また、テーブル制御部14は、管理情報テーブル20から、更新先物理ロックアドレスが格納されたエントリを抽出し、抽出したエントリに格納されたバリッドビットを「1」に更新する。そして、テーブル制御部14は、巡回回数カウンタ16の値を取得し、取得した値をタイムスタンプとして、抽出したエントリに格納する。30

#### 【0081】

また、テーブル制御部14は、リクエスト調停部13がデータの移動を行う場合は、移動元物理ロックアドレスと、移動先物理ロックアドレスとを含むテーブル更新要求を受信する。かかる場合は、テーブル制御部14は、移動元物理ロックアドレスが格納されたエントリをアドレス変換テーブル19から抽出する。そして、テーブル制御部14は、抽出したエントリに格納された移動元物理ロックアドレスを、移動先物理ロックアドレスに更新する。40

#### 【0082】

また、テーブル制御部14は、管理情報テーブル20から、移動元物理ロックアドレスが格納されたエントリを抽出し、抽出したエントリに格納されたバリッドビットを「0」に更新し、タイムスタンプの値を削除する。そして、テーブル制御部14は、管理情報テーブル20から、移動先物理ロックアドレスが格納されたエントリを抽出し、抽出したエントリに格納されたバリッドビットを「1」に更新する。また、テーブル制御部14は、巡回回数カウンタ16の値を取得し、取得した値をタイムスタンプとして、抽出した50

エントリに格納する。

#### 【0083】

例えば、テーブル制御部14は、巡回回数カウンタ16のカウント値が「7」である際に、移動元物理ブロックアドレス「P0」、移動先物理ブロックアドレス「P4」が格納されたテーブル更新要求を受信する。かかる例では、テーブル制御部14は、論理アドレスブロック「P0」が格納されたエントリをアドレス変換テーブル19から抽出し、抽出したエントリの物理ブロックアドレス「P0」を移動先物理ブロックアドレス「P4」に更新する。

#### 【0084】

また、テーブル制御部14は、移動元物理ブロックアドレス「P0」が格納されたエントリを管理情報テーブル20から抽出する。そして、テーブル制御部14は、抽出したエントリのバリッドビット「1」を「0」に更新し、タイムスタンプの値を削除する。また、テーブル制御部14は、移動先物理ブロックアドレス「P4」が格納されたエントリを管理情報テーブル20から抽出し、抽出したエントリのバリッドビットを「1」に更新する。そして、テーブル制御部14は、抽出したエントリに、巡回回数カウンタ16の値「7」をタイムスタンプとして格納する。

#### 【0085】

また、テーブル制御部14は、テーブル参照要求を受信した場合は、テーブル記憶部11から管理情報テーブル20を取得する。そして、テーブル制御部14は、取得した管理情報テーブル20をリクエスト調停部13に出力する。

10

20

#### 【0086】

デバイスアクセス制御部15は、リクエスト調停部13からの各種リクエストに従って、NANDデバイス7a～10aに対するデバイスアクセスを実行する。例えば、デバイスアクセス制御部15は、リクエスト調停部13から、物理アドレスを含む読み出し要求を受信する。かかる場合は、デバイスアクセス制御部15は、NANDデバイス7a～10aが有するページのうち、読み出し要求に格納されていた物理アドレスが示すページに格納されたデータの読み出しを実行する。そして、デバイスアクセス制御部15は、読み出したデータをリクエスト調停部13に出力する。

#### 【0087】

また、例えば、デバイスアクセス制御部15は、リクエスト調停部13から、物理アドレスと、書込み対象のデータとを含む書込み要求を受信する。かかる場合は、デバイスアクセス制御部15は、書込み要求に含まれる物理アドレスが示すページに書込み対象のデータを格納する。その後、デバイスアクセス制御部15は、データの書込みを終了した旨の応答をリクエスト調停部13に出力する。

30

#### 【0088】

また、例えば、デバイスアクセス制御部15は、更新元物理アドレスと、更新先物理アドレスと、書込むデータとを含む更新要求をリクエスト調停部13から受信する。かかる場合は、デバイスアクセス制御部15は、更新元物理アドレスが示すページを含むブロックのデータを読み出す。続いて、デバイスアクセス制御部15は、読み出したデータのうち、更新元物理アドレスが示すページに格納されたデータを更新要求に含まれるデータに更新する。

40

#### 【0089】

そして、デバイスアクセス制御部15は、更新したデータを含む各データを、更新先物理アドレスが示すページを含むブロックに格納する。なお、デバイスアクセス制御部15は、データ更新元に各データが格納されたページのページ番号と、データ更新先に各データが格納されるページのページ番号とが同一となるように、データを格納する。その後、デバイスアクセス制御部15は、データの書込みを終了した旨の応答をリクエスト調停部13に出力する。

#### 【0090】

また、デバイスアクセス制御部15は、移動元物理ブロックアドレスと、移動先物理ブ

50

ロックアドレスとを含む移動要求をリクエスト調停部13から受信する。かかる場合は、デバイスアクセス制御部15は、移動元物理ブロックアドレスが示すブロックからデータの読み出しを行う。そして、デバイスアクセス制御部15は、移動先物理ブロックアドレスが示すブロックに、読み出したデータを格納する。なお、デバイスアクセス制御部15は、移動元と移動先とで、各データが格納されたページのページ番号が同一となるように、データを格納する。その後、デバイスアクセス制御部15は、データの移動を終了した旨の応答をリクエスト調停部13に出力する。

#### 【0091】

巡回回数カウンタ16は、NANDデバイス7a～10aの全ブロックについて、データが書き込まれてから所定の期間が経過したか否かを判定する巡回参照処理をNANDコントローラ6aが実行した回数をカウントする。つまり、巡回回数カウンタ16は、時間等の独立したタイミングでカウントを行うカウンタではなく、NANDコントローラ6aが実行する巡回参照処理が終了した際にカウント値を更新するカウンタである。また、巡回回数カウンタ16は、所定の桁数、例えば1桁のみのカウンタであり、桁あふれが発生した場合には、カウント値が初期値「0」に戻るカウンタである。なお、巡回回数カウンタ16は、特許請求の範囲に記載の計数部の一例である。

#### 【0092】

巡回参照制御部17は、所定のタイミングで、巡回参照制御を実行する。例えば、巡回参照制御部17は、所定の時間間隔、所定の時刻、情報処理装置1が実行するアプリケーションプログラムの指示等を契機として、巡回参照制御を実行する。

#### 【0093】

以下、巡回参照制御部17が実行する巡回参照制御の処理内容について説明する。例えば、巡回参照制御部17は、管理情報テーブル20の参照要求をリクエスト調停部13に出力する。また、巡回参照制御部17は、巡回回数カウンタ16のカウント値を取得する。また、巡回参照制御部17は、リクエスト調停部13から管理情報テーブル20を受信すると、管理情報テーブル20から先頭のエントリを抽出し、以下の判定処理を実行する。

#### 【0094】

まず、巡回参照制御部17は、抽出したエントリのバリッドビットが「1」であるか否かを判定する。また、巡回参照制御部17は、抽出したエントリのバリッドビットが「1」ではない場合は、管理情報テーブル20から、次のエントリを抽出する。一方、巡回参照制御部17は、抽出したエントリのバリッドビットが「1」である場合は、抽出したエントリに格納されたタイムスタンプの値と、巡回回数カウンタ16のカウント値とを比較する。

#### 【0095】

そして、巡回参照制御部17は、比較結果に応じて、データの移動を行うか否かを判定する。例えば、巡回参照制御部17は、データが書き込まれてから所定の期間が経過するまでの間、データが更新されていない場合は、データの移動を行うと判定する。その後、巡回参照制御部17は、データの移動を行うと判定した場合は、抽出したエントリの物理ブロックアドレスをデータ移動制御部18に出力する。そして、巡回参照制御部17は、データの移動が終了した旨の応答をデータ移動制御部18から受信した場合は、管理情報テーブル20から次のエントリを抽出し、抽出したエントリに対して、判定処理を実行する。

#### 【0096】

例えば、巡回参照制御部17は、巡回回数カウンタ16の値に1を加算した値と抽出したエントリに格納されたタイムスタンプの値とが一致した場合は、抽出したエントリに格納された物理ブロックアドレスをデータ移動制御部18に出力する。すなわち、巡回参照制御部17は、抽出したエントリに格納された物理ブロックアドレスが示すブロックにデータを書き込んでから、巡回回数カウンタ16が一巡するまでの間、移動や更新が行われなかつた場合は、データの移動をデータ移動制御部18に依頼する。

10

20

30

40

50

## 【0097】

また、巡回参照制御部17は、移動すると判定した全てのデータについて、データ移動制御部18から移動が終了した旨の応答を受信した場合は、巡回回数カウンタ16の値を1つインクリメントする。つまり、巡回回数カウンタ16の値は、管理情報テーブル20の全てのエントリについて、判定処理を実行した場合には、巡回回数カウンタ16の値を1インクリメントする。このため、NANDコントローラ6aは、移動対象のデータを確実に移動させるので、巡回回数カウンタ16のカウント値が管理情報テーブル20に格納されるタイムスタンプの値を追い越すことが無い。この結果、情報処理装置1は、巡回回数カウンタ16の桁数を削減することができる。

## 【0098】

10

詳細な例を挙げると、巡回参照制御部17は、図8に示す管理情報テーブル20から、物理ブロックアドレス「P0」が格納されたエントリを抽出し、抽出したエントリのタイムスタンプの値と、巡回回数カウンタ16のカウント値、例えば「1」とを比較する。この結果、巡回参照制御部17は、巡回回数カウンタ16のカウント値「1」に1を加算した値「2」と、物理ブロックアドレス「P0」が格納されたエントリのタイムスタンプ「2」とが一致するので、物理ブロック「P0」をデータ移動制御部18に出力する。

## 【0099】

その後、巡回参照制御部17は、データ移動制御部18から応答を受信すると、管理情報テーブル20から物理ブロックアドレス「P1」が格納されたエントリを抽出し、抽出したエントリについて、判定処理を実行する。また、巡回参照制御部17は、管理情報テーブル20の最後のエントリについて判定処理を行い、データの移動を行わないと判定した場合や、データの移動が完了した旨の応答を受信した場合は、巡回回数カウンタ16のカウント値「1」を「2」に更新する。

20

## 【0100】

なお、巡回参照制御部17は、設定に応じて、書き込まれてから任意の期間が経過したデータが格納されているブロックの物理ブロックアドレスをデータ移動制御部18に出力することができる。例えば、巡回参照制御部17は、任意の閾値「N」を巡回回数カウンタ16のカウント値に加算した値よりも、管理情報テーブル20に格納されたタイムスタンプの値が小さい場合は、データを移動すると判定してよい。なお、巡回参照制御部17は、特許請求の範囲に記載の判定部の一例である。

30

## 【0101】

データ移動制御部18は、書き込まれてから所定の期間が経過したデータを他のブロックに移動させる。すなわち、データ移動制御部18は、書き込まれてから所定の期間が経過したデータの移動を行う。例えば、データ移動制御部18は、巡回参照制御部17から物理ブロックアドレスを受信した場合は、受信した物理ブロックアドレスを含む移動要求をリクエスト調停部13に出力する。

## 【0102】

また、データ移動制御部18は、データの移動が終了した場合は、リクエスト調停部13から、データの移動が終了した旨の応答を受信する。かかる場合は、データ移動制御部18は、巡回参照制御部17に対し、データの移動が終了した旨の応答を出力する。

40

## 【0103】

なお、例えば、リクエスタインターフェース部12、リクエスト調停部13、テーブル制御部14、デバイスアクセス制御部15、巡回回数カウンタ16、巡回参照制御部17、データ移動制御部18とは、電子回路である。ここで、電子回路の例として、ASIC(Application Specific Integrated Circuit)やFPGA(Field Programmable Gate Array)などの集積回路、またはCPU(Central Processing Unit)やMPU(Micro Processing Unit)などを適用する。

## 【0104】

また、テーブル記憶部11とは、RAM(Random Access Memory)、フラッシュメモリ(flash memory)などの半導体メモリ素子などの記憶装置である。

50

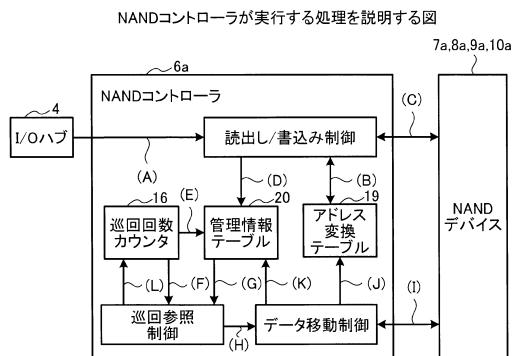

## 【0105】

次に、図9を用いて、NANDコントローラ6aが実行する処理の流れについて説明する。図9は、NANDコントローラが実行する処理を説明する図である。例えば、NANDコントローラ6aは、図9中(A)に示すように、I/Oハブ4を介して、読み出し要求や書き込み要求を受信すると、読み出し/書き込み制御を実行する。詳細には、NANDコントローラ6aは、図9中(B)に示すように、アドレス変換テーブル19を参照して、論理アドレスと物理アドレスとのアドレス変換を実行する。

## 【0106】

そして、NANDコントローラ6aは、図9中(C)に示すように、アドレス変換した物理アドレスを用いて、NANDデバイス7a～10aに対する読み出しや書き込みを実行する。また、NANDコントローラ6aは、データの書き込みを実行した場合は、図9中(D)に示すように、管理情報テーブル20の更新を行う。詳細には、NANDコントローラ6aは、図6中(E)に示すように、データ書き込みの際に巡回回数カウンタ16がカウントしていたカウント値を管理情報テーブル20に格納する。

10

## 【0107】

また、NANDコントローラ6aは、所定の時間間隔等で、巡回参照制御を実行する。詳細には、NANDコントローラ6aは、図9中(F)に示すように、巡回回数カウンタ16の値を取得する。そして、NANDコントローラ6aは、図9中(G)に示すように、管理情報テーブル20の各エントリごとに、タイムスタンプの値と巡回回数カウンタ16の値とを比較し、データが書き込まれてから所定の期間が経過したブロックを識別する。

20

## 【0108】

そして、NANDコントローラ6aは、図9中(H)に示すように、識別したブロックのデータ移動制御を実行する。例えば、NANDコントローラ6aは、図9中(I)に示すように、識別したブロックから他のブロックにデータを移動させる。そして、NANDコントローラ6aは、データの移動に従って、図9中(J)に示すように、アドレス変換テーブル19を更新し、図9中(K)に示すように、管理情報テーブル20を更新する。

## 【0109】

また、NANDコントローラ6aは、管理情報テーブル20の全エントリについて、タイムスタンプの値と巡回回数カウンタ16の値との比較が終了した場合は、図9中(L)に示すように、巡回回数カウンタ16の値をインクリメントする。この結果、NANDコントローラ6aは、カウンタの桁数を少ない桁数とした場合にも、カウント値が管理情報テーブル20に格納されたタイムスタンプの値を追越さないので、書き込まれてから所定の期間が経過したデータの移動を行うことができる。

30

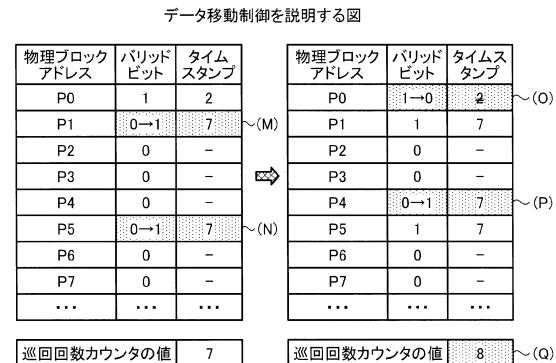

## 【0110】

次に、図10を用いて、NANDコントローラ6aが管理情報テーブル20を用いてデータ移動制御の対象となるデータを識別し、データ移動後に管理情報テーブル20を更新する例について説明する。図10は、データ移動制御を説明する図である。なお、図10に示す例では、巡回回数カウンタ16のカウント値は1桁であるものとする。

## 【0111】

また、図10に示す例では、NANDコントローラ6aは、タイムスタンプの値と、巡回回数カウンタ16のカウント値に「5」を加算した値とが一致する場合は、データの移動を行うものとする。また、図10に示す例では、物理ブロックアドレス「P0」が示すブロックのデータを物理ブロックアドレス「P4」が示すブロックに移動する例について説明する。

40

## 【0112】

例えば、NANDコントローラ6aは、巡回回数カウンタ16のカウント値が「7」の際に、物理ブロックアドレス「P1」、「P5」が示すブロックにデータを格納する。この結果、NANDコントローラ6aは、図10中(M)に示すように、物理ブロックアドレス「P1」が格納されたエントリのバリッドビットを「1」に更新し、タイムスタンプとして、巡回回数カウンタ16のカウント値「7」を格納する。また、NANDコントローラ

50

ーラ 6 a は、図 10 中 (N) に示すように、物理ブロックアドレス「P5」が格納されたエントリのバリッドビットを「1」に更新し、タイムスタンプとして、巡回回数カウンタ 16 のカウント値「7」を格納する。

【0113】

ここで、巡回回数カウンタ 16 のカウント値「7」に「5」を加算した値は「12」であるが、桁あふれを考慮すると、加算した値は「2」となる。この結果、NANDコントローラ 6 a は、図 10 中 (O) に示すように、物理ブロックアドレス「P0」が格納されたエントリのタイムスタンプが「2」であるので、物理ブロックアドレス「P0」が示すブロックのデータを移動する。また、NANDコントローラ 6 a は、物理ブロックアドレス「P0」が格納されたエントリのバリッドビットを「0」に更新し、タイムスタンプの値を削除する。

10

【0114】

また、NANDコントローラ 6 a は、図 10 中 (P) に示すように、データの移動先ブロックを示す物理ブロックアドレス「P4」のエントリを抽出する。そして、NANDコントローラ 6 a は、抽出したエントリのバリッドビットを「1」に更新し、タイムスタンプとして、巡回回数カウンタ 16 のカウント値「7」を格納する。その後、NANDコントローラ 6 a は、図 10 中 (Q) に示すように、巡回回数カウンタ 16 のカウント値を「8」にインクリメントする。

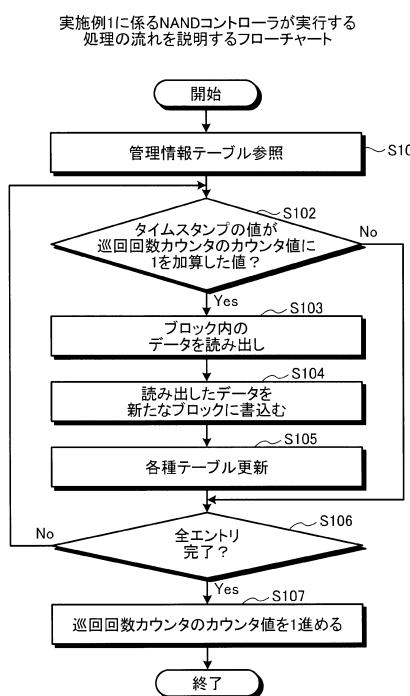

【0115】

次に、図 11 を用いて、NANDコントローラ 6 a が実行する処理の流れについて説明する。図 11 は、実施例 1 に係る NANDコントローラが実行する処理の流れを説明するフローチャートである。例えば、NANDコントローラ 6 a は、管理情報テーブル 20 を参照する (ステップ S101)。そして、NANDコントローラ 6 a は、参照した管理情報テーブル 20 からエントリを 1 つ抽出し、抽出したエントリのタイムスタンプの値が巡回回数カウンタ 16 のカウント値に 1 を加算した値か否かを判定する (ステップ S102)。

20

【0116】

また、NANDコントローラ 6 a は、タイムスタンプの値が巡回回数カウンタ 16 のカウント値に 1 を加算した値であると判定した場合は (ステップ S102 肯定)、以下のステップ S103 ~ S105 に示すデータ移動制御を実行する。詳細には、NANDコントローラ 6 a は、抽出したエントリに格納された物理ブロックアドレスが示すブロック内のデータを読み出す (ステップ S103)。次に、NANDコントローラ 6 a は、読み出したデータを新たなブロックに書込む (ステップ S104)。

30

【0117】

そして、NANDコントローラ 6 a は、データの移動に応じて、アドレス変換テーブル 19、および、管理情報テーブル 20 の更新を行う (ステップ S105)。なお、ステップ S103 ~ ステップ S105 の処理は、リクエスト調停部 13、テーブル制御部 14 によってアトミックに実行される。一方、NANDコントローラ 6 a は、タイムスタンプの値が巡回回数カウンタ 16 のカウント値に 1 を加算した値ではないと判定した場合は (ステップ S102 否定)、ステップ S103 ~ S105 に示すデータ移動制御をスキップする。

40

【0118】

また、NANDコントローラ 6 a は、管理情報テーブル 20 の全てのエントリについて、ステップ S102 ~ S105 の処理を実行したか否かを判定する (ステップ S106)。そして、NANDコントローラ 6 a は、管理情報テーブル 20 の全てのエントリについて、ステップ S102 ~ S105 の処理を実行していないと判定した場合は (ステップ S106 否定)、以下の処理を実行する。すなわち、NANDコントローラ 6 a は、管理情報テーブル 20 の各エントリのうち、ステップ S102 の処理を実行していない他のエントリについてステップ S102 を再度実行する。

【0119】

また、NANDコントローラ6aは、管理情報テーブル20の全てのエントリについて、ステップS102～S105の処理を実行したと判定した場合は（ステップS106肯定）、以下の処理を実行する。すなわち、NANDコントローラ6aは、巡回回数カウンタ16の値を1進め（ステップS107）、処理を終了する。

【0120】

【情報処理装置1の効果】

上述したように、情報処理装置1は、NANDデバイス7a～10aが記憶するデータが移動の対象であるか判定する処理が、全てのデータに対して実行された場合は、巡回回数カウンタ16のカウント値を更新する。また、情報処理装置1は、NANDデバイス7a～10aにデータが書き込まれる際に、巡回回数カウンタ16のカウント値をデータの書き込み先となるブロックの物理ブロックアドレスと対応付けて記憶する。そして、情報処理装置1は、データごとに、データが書き込まれた物理ブロックアドレスと対応付けて記憶するカウント値と、巡回回数カウンタ16のカウント値とを比較して、各ブロックのデータが移動の対象であるか判定する。

【0121】

このため、情報処理装置1は、巡回回数カウンタ16のカウント値が少ない桁数であっても、管理情報テーブル20が記憶するタイムスタンプの値の追い越しを防げる。この結果、情報処理装置1は、タイムスタンプの桁数を削減することができる。また、テーブル記憶部11の記憶容量を削減できるので、NANDコントローラ6aの回路規模を小さくすることができる。また、情報処理装置1は、管理情報テーブル20のサイズを削減する結果、検索処理の時間を短縮し、NANDデバイス7a～10aに対するアクセス性能を向上させることができる。

【0122】

また、情報処理装置1は、物理ブロックアドレスと、物理ブロックアドレスが示すブロックにデータを書き込んだ際のカウント値であるタイムスタンプとを対応付けて管理情報テーブル20に格納する。そして、情報処理装置1は、物理ブロックアドレスごとに、巡回回数カウンタ16のカウント値と管理情報テーブル20に格納された各タイムスタンプの値とを比較して、各データを再度NANDデバイス7a～10aに書き込むか否か判定する。

【0123】

このため、情報処理装置1は、各ブロックごとに、データが書き込まれてから所定の期間が経過したデータを判定できる。この結果、情報処理装置1は、NANDデバイス7a～10aが有する各ブロックごとに、素子の劣化を平準化し、電荷が抜けることによるビット化けを防げる。

【0124】

また、情報処理装置1は、巡回回数カウンタ16のカウント値を所定の値で初期値に戻す。そして、情報処理装置1は、カウント値に1を加算した値と、あるデータについて管理情報テーブル20に格納されたタイムスタンプの値とが一致する場合は、データが移動の対象であると判定する。この結果、情報処理装置1は、NANDデバイス7a～10aに格納されたデータのうち、最も古いデータの移動を行うことができる。

【実施例2】

【0125】

上述したNANDコントローラ6aは、1回の巡回参照制御で、全ての物理ブロックアドレスについて、データの移動を行うか否か判定した。しかし、実施例はこれに限定されるものではない。例えば、実施例2に係るNANDコントローラ6cは、1回の巡回参照処理で、全ての物理ブロックアドレスのうち、一部の物理ブロックアドレスのみについて判定処理を行ってもよい。

【0126】

以下、NANDコントローラ6cが実行する処理について説明する。まず、図12を用いて、NANDコントローラ6cの機能構成について説明する。図12は、実施例2に係

10

20

30

40

50

るNANDコントローラの機能構成を説明する図である。なお、図12に示すNANDコントローラ6cの機能構成のうち、図6に示すNANDコントローラ6aの機能構成と同様の機能構成については、同一の符号を付し、説明を省略する。

#### 【0127】

図12に示す例では、NANDコントローラ6cは、巡回参照制御部17aと巡回済対象記憶部21とを有する。巡回済対象記憶部21は、巡回参照制御部17aが判定処理を行った対象を記憶するためのメモリである。巡回参照制御部17aは、図6に示す巡回参照制御部17と同様の機能を有し、所定の時間間隔で巡回参照制御を実行する。

#### 【0128】

ここで、巡回参照制御部17aは、管理情報テーブル20の各エントリのうち、物理ブロックアドレスが「P0」のエントリから順番に判定処理を実行する。例えば、巡回参照制御部17aは、物理ブロックアドレスが「P0」のエントリを抽出し、抽出したエントリのタイムスタンプの値と巡回回数カウンタ16のカウント値とを比較し、判定処理を実行する。次に、巡回参照制御部17aは、物理ブロックアドレスが「P1」のエントリを抽出し、抽出したエントリについて判定処理を実行する。

10

#### 【0129】

ここで、巡回参照制御部17aは、巡回参照制御を開始してから所定の時間が経過した場合は、最後に判定処理を実行したエントリに格納された物理ブロックアドレスを巡回済対象記憶部21に格納する。その後、巡回参照制御部17aは、巡回参照処理を再開した場合は、巡回済対象記憶部21に格納した物理ブロックアドレスの次の物理ブロックアドレスが格納されたエントリから、順番に判定処理を実行する。その後、巡回参照制御部17aは、管理情報テーブル20の全てのエントリについて判定処理を実行した場合は、巡回回数カウンタ16の値を1つインクリメントする。

20

#### 【0130】

例えば、巡回参照制御部17aは、物理ブロックアドレス「P7」のエントリについて判定処理を終了した際に、所定の時間が経過した場合は、物理ブロックアドレス「P7」を巡回済対象記憶部21に格納する。かかる場合は、巡回参照制御部17aは、巡回参照制御を再開した際に、巡回済対象記憶部21から物理ブロックアドレス「P7」を取得する。そして、巡回参照制御部17aは、管理情報テーブル20から、物理ブロックアドレス「P7」の次の物理ブロックアドレス「P8」が格納されたエントリを抽出し、抽出したエントリに対して判定処理を実行する。

30

#### 【0131】

なお、巡回参照制御部17aは、所定の時間内で判別対象を区切るのではなく、他の方法で判別対象を区切ってもよい。例えば、巡回参照制御部17aは、物理ブロックアドレスを所定の数ごとにグループ分けする。そして、巡回参照制御部17aは、一回の巡回参照制御で、1つのグループに含まれる物理ブロックアドレスに対して判定処理を実行してもよい。

#### 【0132】

例えば、巡回参照制御部17aは、物理ブロックアドレス「P0」～「P7」をグループ「No1」とし、物理ブロックアドレス「P8」～「P15」をグループ「No2」とする。すなわち、巡回参照制御部17aは、物理ブロックアドレスの上位ビットの値ごとに、8個の連続する物理ブロックアドレスを1つのグループとする。そして、巡回参照制御部17aは、管理情報テーブル20の各エントリのうち、グループ「No1」に含まれる物理ブロックアドレスが格納された各エントリについて判定処理を実行する。

40

#### 【0133】

また、巡回参照制御部17aは、グループ「No1」に含まれる物理ブロックアドレスが格納された各エントリについて判定処理を実行した場合は、判定処理を実行したグループを示す情報として、「No1」を巡回済対象記憶部21に格納する。そして、巡回参照制御部17aは、巡回参照制御の再開時には、巡回済対象記憶部21からグループを示す情報「No1」を取得する。かかる場合は、巡回参照制御部17aは、管理情報テーブル

50

20から、グループ「No 1」の次のグループ「No 2」に含まれる物理ブロックアドレスが格納された各エントリについて判定処理を実行する。

【0134】

なお、巡回参照制御部17aは、グループを示す情報として、任意の情報を用いることができる。例えば、巡回参照制御部17aは、物理ブロックアドレスの上位ビットでグループ分けを行う場合は、判定処理を終了したグループの物理ブロックアドレスの上位ビットを巡回済対象記憶部21に格納してもよい。

【0135】

次に、図13を用いて、NANDコントローラ6cが実行する処理の流れについて説明する。図13は、実施例2に係るNANDコントローラが実行する処理の流れを説明する第1のフローチャートである。なお、図13に示す例では、NANDコントローラ6cが、所定の時間内で判別対象となるブロックを区切る例について記載した。また、図13に示す処理のうち、ステップS203～ステップS207の処理については、図11に示すステップS101～ステップS105と同様の処理であるものとして、説明を省略する。

10

【0136】

まず、NANDコントローラ6cは、巡回済対象記憶部21から、前回、判定処理が終了したブロックの物理ブロックアドレスを読み出す(ステップS201)。次に、NANDコントローラ6cは、読み出した物理ブロックアドレスの次の物理ブロックアドレスが示すブロックを開始ブロックに設定する(ステップS202)。そして、NANDコントローラ6cは、ステップS203～ステップS207の処理を実行する。

20

【0137】

また、NANDコントローラ6cは、ステップS207を実行すると、判定対象とした物理ブロックアドレスが示すブロックが、最終ブロックであるか否かを判定する(ステップS208)。そして、NANDコントローラ6cは、判定対象とした物理ブロックアドレスが示すブロックが、最終ブロックであると判定した場合は(ステップS208肯定)、巡回回数カウンタ16のカウント値を1進める(ステップS209)。一方、NANDコントローラ6cは、判定対象とした物理ブロックアドレスが示すブロックが、最終ブロックではないと判定した場合は(ステップS208否定)、ステップS209をスキップする。

【0138】

30

次に、NANDコントローラ6cは、巡回参照処理を開始してから所定の時間が経過したか否かを判定する(ステップS210)。そして、NANDコントローラ6cは、巡回参照処理を開始してから所定の時間が経過したと判定した場合は(ステップS210肯定)、判定処理が終了したブロックの物理ブロックアドレスを巡回済対象記憶部21に保存し(ステップS211)、処理を終了する。一方、NANDコントローラ6cは、巡回参照処理を開始してから所定の時間が経過していないと判定した場合は(ステップS210否定)、ステップS203の処理を実行する。

【0139】

次に、図14を用いて、NANDコントローラ6cが実行する処理の他の例について説明する。図14は、実施例2に係るNANDコントローラが実行する処理の流れを説明する第2のフローチャートである。なお、図14に示す例では、NANDコントローラ6cが、物理ブロックアドレスを所定の数ごとにグループ分けし、1回の巡回参照制御で1つのグループに含まれるブロックを判定処理の対象となる例について記載した。また、図14に示す処理のうち、ステップS303～ステップS307の処理については、図11に示すステップS101～ステップS105と同様の判定処理であるものとして、説明を省略する。

40

【0140】

まず、NANDコントローラ6cは、巡回済対象記憶部21から、前回、判定処理が終了したグループのグループNoを読み出す(ステップS301)。次に、NANDコントローラ6cは、読み出したグループNoの次のグループNoが示すグループを巡回参照処

50

理の対象に設定する(ステップS302)。そして、NANDコントローラ6cは、巡回参照処理の対象となるグループに含まれる各ブロックについて、ステップS303～ステップS307の処理を実行する。

#### 【0141】

また、NANDコントローラ6cは、ステップS307を実行すると、判定対象とした物理ブロックアドレスが示すブロックが、巡回参照処理の対象となるグループの最終ブロックであるか判定する(ステップS308)。そして、NANDコントローラ6cは、判定対象とした物理ブロックアドレスが示すブロックが、巡回参照処理の対象となるグループの最終ブロックであると判定した場合は(ステップS308肯定)、以下の処理を実行する。すなわち、NANDコントローラ6cは、巡回参照処理の対象となるグループのグループNoを巡回済対象記憶部21に格納する(ステップS309)。

10

#### 【0142】

また、NANDコントローラ6cは、巡回参照処理を実行したグループが最終グループであるか否かを判定する(ステップS310)。すなわち、NANDコントローラ6cは、管理情報テーブル20の全てのエントリについて判定処理を実行したか否かを判定する。そして、NANDコントローラ6cは、巡回参照処理を実行したグループが最終グループであると判定した場合は(ステップS310肯定)、巡回回数カウンタ16のカウント値を1進め(ステップS311)、処理を終了する。

#### 【0143】

一方、NANDコントローラ6cは、巡回参照処理を実行したグループが最終グループではないと判定した場合は(ステップS310否定)、ステップS311をスキップして処理を終了する。また、NANDコントローラ6cは、判定対象とした物理ブロックアドレスが示すブロックが、巡回参照処理の対象となるグループの最終ブロックではないと判定した場合は(ステップS308否定)、ステップS303の処理を実行する。

20

#### 【0144】

##### 【NANDコントローラ6cの効果】

上述したように、NANDコントローラ6cは、巡回参照制御を開始してから所定の時間が経過した場合は、最後に判定処理の対象となったブロックの物理ブロックアドレスを記憶する。その後、NANDコントローラ6cは、巡回参照処理の再開時には、記憶した物理ブロックアドレスの次の物理ブロックアドレスが示すブロックから、物理ブロックアドレスの順で、巡回参照処理を実行する。

30

#### 【0145】

このため、NANDコントローラ6cは、巡回参照処理を1回実行する際の処理時間を短縮することができる。この結果、NANDコントローラ6cは、例えば、情報処理装置1が処理を実行していない夜間等に、巡回参照処理を実行する等、柔軟なスケジューリングを実現することができる。また、NANDコントローラ6cは、巡回参照処理によってNANDデバイス7a～10aにアクセスできない時間を短縮化するので、NANDデバイス7a～10aに対するアクセス性能を向上させることができる。

#### 【0146】

また、NANDコントローラ6cは、NANDデバイス7a～10aの記憶領域を複数のグループに分割し、グループごとに、巡回参照処理を実行する。このため、NANDコントローラ6cは、巡回参照処理を1回実行する際の処理時間を短縮し、柔軟なスケジューリングを実現できる。また、NANDコントローラ6cは、NANDデバイス7a～10aに対するアクセス性能を向上させることができる。

40

#### 【実施例3】

#### 【0147】

上述したNANDコントローラ6a～6cは、巡回回数カウンタ16のカウント値に所定の閾値を加算した値と、タイムスタンプの値とが一致した場合は、データの移動処理を実行した。しかし、実施例は、これに限定されるものではない。例えば、NANDコントローラ6a～6cは、各ブロックに対するリクエストの数に応じて、閾値を動的に設定し

50

てもよい。

【0148】

以下、実施例3に係るNANDコントローラとして、各ブロックに対するリクエストの数に応じて、異なる閾値を設定するNANDコントローラ6dについて説明する。まず、図15を用いて、NANDコントローラ6dの機能構成について説明する。図15は、実施例3に係るNANDコントローラの機能構成を説明する図である。なお、図15に示すNANDコントローラ6dの機能構成のうち、図6に示すNANDコントローラ6aの機能構成と同様の機能構成については、同一の符号を付し、説明を省略する。

【0149】

例えば、NANDコントローラ6dは、巡回参照制御部17bと、リクエスト数計測部22とを有する。リクエスト数計測部22は、NANDデバイス7a～10aが有するブロックごとに、以下の処理を実行する。まず、リクエスト数計測部22は、リクエスト調停部13とテーブル制御部14とを接続する信号線やバスを監視し、各ブロックに対して発行されたリクエストの数を計数する。詳細には、リクエスト数計測部22は、所定の時間間隔で、各ブロックに対して発行されたリクエストの数、例えば、読み出し要求や書き込み要求の数をブロックごとに計測する。

【0150】

なお、リクエスト数計測部22は、読み出し要求、又は、書き込み要求のいずれか一方の数を計数してもよい。また、リクエスト数計測部22は、リクエスト調停部13とデバイスアクセス制御部15とを接続する信号線やバスを監視することで、各ブロックに対するリクエストの数を計数しても良い。

【0151】

また、リクエスト数計測部22は、計測結果から、10秒間に発行されたリクエストの平均値である平均要求発行数をブロックごとに算出する。そして、リクエスト数計測部22は、算出した平均要求発行数に応じた閾値をブロックごとに設定する。その後、リクエスト数計測部22は、ブロックごとに設定した閾値を巡回参照制御部17bに出力する。なお、リクエスト数計測部22は、特許請求の範囲に記載の要求計数部、および、設定部の一例である。

【0152】

ここで、図16を用いて、リクエスト数計測部22が、平均要求発行数に応じて設定する閾値の一例について説明する。図16は、平均要求発行数に応じた閾値の一例を説明する図である。例えば、図16に示すように、リクエスト数計測部22は、平均要求発行数が「0」から「9」の間であるブロックの閾値を「4」とし、平均要求発行数が「10」から「49」の間であるブロックの閾値を「3」とする。

【0153】

また、リクエスト数計測部22は、平均要求発行数が「50」から「99」の間であるブロックの閾値を「2」とし、平均要求発行数が「100」以上であるブロックの閾値を「1」とする。なお、図16に示す平均要求発行数と閾値との対応は、あくまで一例であり、NANDコントローラ6dは、平均要求発行数の数に応じた閾値を設定するのであれば、任意の閾値を設定できる。

【0154】

図15に戻り、巡回参照制御部17bは、図6に示す巡回参照制御部17と同様の機能を発揮する。また、巡回参照制御部17bは、管理情報テーブル20の各エントリについて、判定処理を実行する場合は、以下の処理を実行する。まず、巡回参照制御部17bは、管理情報テーブル20から判定処理の対象となるエントリを抽出する。

【0155】

また、巡回参照制御部17bは、抽出したエントリに格納された物理ブロックアドレスが示すブロックに対してリクエスト数計測部22が設定した閾値と、現在の巡回回数カウンタ16のカウント値との和の値を算出する。そして、巡回参照制御部17bは、抽出したエントリに格納されたタイムスタンプの値が算出した和の値以下となるか否かを判定す

10

20

30

40

50

る。

【0156】

また、巡回参照制御部17bは、抽出したエントリに格納されたタイムスタンプの値が算出した和の値以下となる場合は、抽出したエントリに格納された物理ブロックアドレスをデータ移動制御部18に出力し、データを移動させる。一方、巡回参照制御部17bは、抽出したエントリに格納されたタイムスタンプの値が算出した和の値より大きい場合は、データを移動させずに、管理情報テーブル20の次のエントリについて判定処理を実行する。

【0157】

この結果、NANDコントローラ6dは、読み出し要求や書き込み要求が頻繁に発行されるブロックについては、データの移動を先延ばしするので、読み出し要求や書き込み要求が阻害されずに実行される結果、アクセス性能の悪化を防ぐことができる。一方、NANDコントローラ6dは、読み出し要求や書き込み要求があまり発行されていないブロックについては、データの移動を前倒しで実行するので、アクセス性能の悪化を防ぎつつ、ビット化けを防ぐことができる。

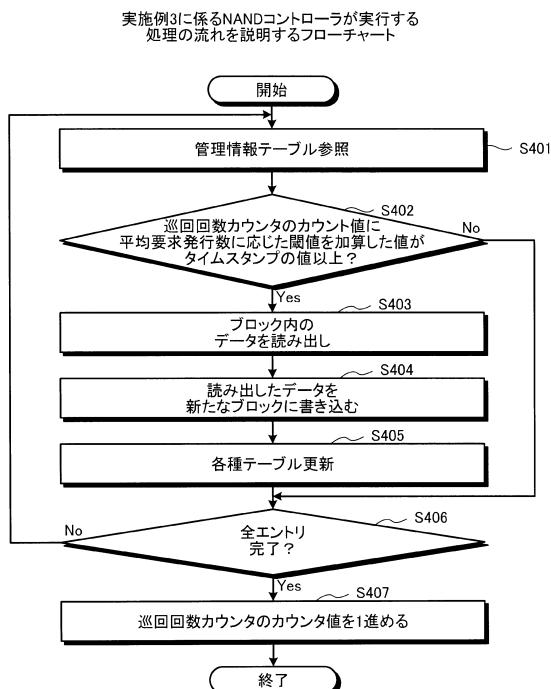

【0158】

次に、図17を用いて、NANDコントローラ6dが実行する処理の他の例について説明する。図17は、実施例3に係るNANDコントローラが実行する処理の流れを説明するフローチャートである。また、図17に示す処理のうち、ステップS401、ステップS403～ステップS407の処理については、図11に示すステップS101、ステップS103～ステップS107と同様の判定処理であるものとして、説明を省略する。

【0159】

例えば、NANDコントローラ6dは、判定処理の対象となるエントリについて、巡回回数カウンタ16のカウント値に平均要求発行数に応じた閾値を加算した値がタイムスタンプの値以上か否かを判定する（ステップS402）。そして、NANDコントローラ6dは、巡回回数カウンタ16のカウント値に平均要求発行数に応じた閾値を加算した値がタイムスタンプの値以上である場合は（ステップS402肯定）、ステップS403の処理を実行する。一方、NANDコントローラ6dは、巡回回数カウンタ16のカウント値に平均要求発行数に応じた閾値を加算した値がタイムスタンプの値より少ない場合は（ステップS402否定）、ステップS406を実行する。

【0160】

【NANDコントローラ6dの効果】

上述したように、NANDコントローラ6dは、ブロックごとに、発行された読み出し要求、および、書き込み要求の数を計数する。また、NANDコントローラ6dは、計数した数に応じて、各ブロックのデータを移動させるか否かを判定するための閾値、すなわち、各ブロックのデータが移動の対象であるか判定するための閾値をブロックごとに設定する。

【0161】

そして、NANDコントローラ6dは、ブロックごとに、巡回回数カウンタ16のカウント値と設定した閾値との和を算出し、算出した値が管理情報テーブル20に格納されたタイムスタンプの値以上となるか否かを判定する。その後、NANDコントローラ6dは、算出した値が管理情報テーブル20に格納されたタイムスタンプの値以上となる場合は、判断対象のブロックに格納されたデータが移動の対象であると判定する。

【0162】

このため、NANDコントローラ6dは、CPU3a、3bが発行するリクエストの数に応じて、データの移動のを行ふことができる。例えば、NANDコントローラ6dは、読み出し要求や書き込み要求が頻繁に発行されるブロックについては、データの移動を先延ばし、読み出し要求や書き込み要求があまり発行されていないブロックについては、データの移動を前倒しして実行する。この結果、NANDコントローラ6dは、アクセス性能の悪化や、ビット化けを防ぐことができる。

10

20

30

40

50

**【実施例 4】****【0163】**

これまで本発明の実施例について説明したが実施例は、上述した実施例以外にも様々な異なる形態にて実施されてよいものである。そこで、以下では実施例 4 として本発明に含まれる他の実施例を説明する。

**【0164】****(1) データ移動の粒度について**

上述した NAND コントローラ 6 a ~ 6 d は、NAND デバイス 7 a ~ 10 a が有するブロックごとに、データを移動させるか否かを判定した。しかしながら、実施例はこれに限定されるものではない。すなわち、NAND コントローラ 6 a ~ 6 d は、任意の単位でデータの移動を行うか否かを判定することができる。例えば、NAND コントローラ 6 a ~ 6 d は、複数のブロックごとにデータの移動を行うか否かを判定してもよい。また、NAND コントローラ 6 a ~ 6 d は、管理情報テーブル 20 がタイムスタンプを管理する単位と、データ書き込みの単位とに異なる粒度を採用してもよい。

10

**【0165】****(2) NAND コントローラ 6 a ~ 6 d の機能構成について**

上述した NAND コントローラ 6 a ~ 6 d の機能構成は、あくまで一例であり、NAND コントローラ 6 a ~ 6 d として同様の処理を実行できるのであれば、任意の構成を採用することができる。例えば、NAND コントローラ 6 a は、巡回参照制御部 17 とデータ移動制御部 18 との機能を有する移動制御部を有してもよい。

20

**【0166】**

なお、上述した例では、NAND コントローラ 6 a ~ 6 d が NAND デバイス 7 a ~ 10 a に格納されたデータの移動を判定する処理について記載した。しかしながら、実施例はこれに限定されるものではない。すなわち、NAND コントローラ 6 a ~ 6 d は、データの移動のを行うのであれば、任意の技術が適用された記憶媒体、例えばメモリ等のメモリコントローラとして動作してもよい。

**【0167】****(3) リクエストの調停について**

上述した NAND コントローラ 6 a ~ 6 d は、リクエストインターフェース部 12 から受信する読み出し要求や書き込み要求を優先して実行した。しかし、実施例はこれに限定されるものではなく、NAND コントローラ 6 a ~ 6 d は、NAND デバイス 7 a ~ 10 a の各セルの寿命が平準化するように、各リクエストの調停を行ってもよい。

30

**【0168】****(4) 予備ブロックについて**

上述したテーブル制御部 14 は、データが格納されていない予備ブロックをデータの移動先とした。しかしながら、実施例はこれに限定されるものではない。例えば、テーブル制御部 14 は、データが格納されていないブロックのうち、最も余命が長いブロックを識別する。そして、テーブル制御部 14 は、識別したブロックを示す物理ブロックアドレスをリクエスト調停部 13 に通知してもよい。かかる処理を実行した場合は、NAND コントローラ 6 a ~ 6 d は、NAND デバイス 7 a ~ 10 a が有する各ブロックのセルの劣化を平準化し、寿命を使いきることができる。

40

**【0169】****(5) 巡回回数カウンタについて**

上述した NAND コントローラ 6 a ~ 6 d は、「0」から「9」までカウントする巡回回数カウンタ 16 を有する。しかしながら、実施例はこれに限定されるものではない。すなわち、巡回回数カウンタ 16 がカウントする値は、任意の範囲や桁数を設定することができる。例えば、NAND コントローラ 6 a ~ 6 d は、「0」または「1」をカウントする巡回回数カウンタ 16 を有し、2 回の巡回参照制御で全てのデータを移動させてもよい。

**【0170】**

50

また、NANDコントローラ6a～6dは、カウンタ巡回回数カウンタ16として有する必要はない。例えば、NANDコントローラ6a～6dは、所定の桁数の数値を記憶可能なメモリを有し、メモリ上にカウント値を格納する。そして、NANDコントローラ6a～6dは、管理情報テーブル20の全てのエントリについて判定処理を完了した場合は、メモリ上のカウント値を読み出し、読み出した値に1を加算した値を再度メモリに書き込むことで、巡回回数カウンタ16を再現してもよい。

#### 【0171】

なお、NANDコントローラ6a～6dは、任意の記憶装置に巡回参照制御を実行した回数を格納し、巡回参照制御を実行後に、記憶装置に格納した回数を更新することで、巡回回数カウンタ16の機能を実現してもよい。

10

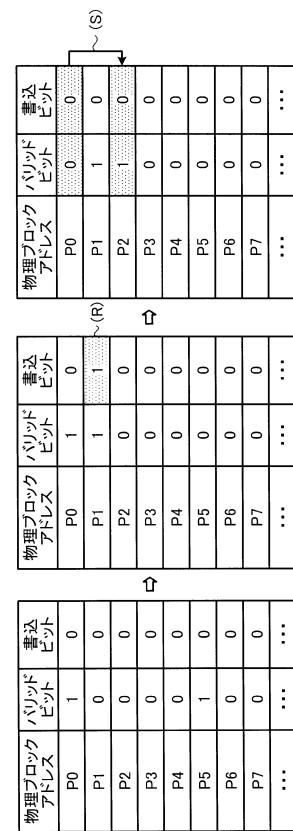

#### 【0172】

また、NANDコントローラ6a～6dは、各ブロックごとに、巡回参照制御を行った後でデータの書き込みが行われたか否かを示す書きビットを管理情報テーブル20に格納する。そして、NANDコントローラ6a～6dは、管理情報テーブル20の書きビットを参照し、巡回参照制御を行った後でデータの書き込みが行われなかったブロックを識別する。その後、NANDコントローラ6a～6dは、識別したブロックのデータを移動させ、管理情報テーブル20のフラグをリセットしてもよい。

#### 【0173】

すなわち、NANDコントローラ6a～6dは、前回巡回参照処理を行ってから書き込みが行われなかったブロックについて、データの再書き込みを行う場合は、巡回回数カウンタ16を有さず、書きビットを用いて処理を行っても良い。以下、図18を用いて、NANDコントローラ6aが巡回回数カウンタ16を用いずに、巡回参照処理を実行する処理の一例について説明する。

20

#### 【0174】

図18は、書きビットを用いた処理の一例を説明する図である。なお、図18に示す例では、NANDコントローラ6aが、巡回回数カウンタ16を用いずに巡回参照処理を実行する際に、管理情報テーブル20に格納する情報について記載した。図18に示すように、NANDコントローラ6aは、管理情報テーブル20に、タイムスタンプに変えて書きビットを格納する。ここで、書きビットとは、前回巡回参照処理が実行されてから、データの書き込みや移動が行われたか否かを示す情報である。

30

#### 【0175】

例えば、図18に示す例では、管理情報テーブル20は、物理ブロックアドレス「P0」、「P5」が示すブロックにデータが格納されている旨を示す。ここで、NANDコントローラ6aは、データの更新や移動を行った結果、物理ブロックアドレス「P5」が示すブロックに格納されたデータを物理ブロックアドレス「P1」が示すブロックに移動する。

#### 【0176】

そして、NANDコントローラ6aは、管理情報テーブル20の各エントリのうち、物理ブロックアドレス「P5」のバリッドビットを「0」に更新し、物理ブロックアドレス「P1」のバリッドビットを「1」に更新する。また、NANDコントローラ6aは、図18中(R)に示すように、物理ブロックアドレス「P1」の書きビットを「1」に更新する。

40

#### 【0177】

ここで、NANDコントローラ6aは、巡回参照処理を実行する場合は、以下の処理を実行する。まず、NANDコントローラ6aは、管理情報テーブル20の各エントリのうち、バリッドビットが「1」で書きビットが「0」のエントリを識別する。すなわち、NANDコントローラ6aは、前回巡回参照処理が実行された後で書き込みや移動が行われたブロックの物理ブロックアドレスを識別する。そして、NANDコントローラ6aは、識別した物理ブロックアドレスが示すブロックのデータを他のブロックに移動する。

#### 【0178】

50

例えば、NANDコントローラ6aは、図18に示す管理情報テーブル20から、バリッドビットが「1」で書き込みビットが「0」のエントリに格納された物理ブロックアドレス「P0」を識別する。そして、NANDコントローラ6aは、図18中(S)に示すように、物理ブロックアドレス「P0」が示すブロックのデータを物理ブロックアドレス「P2」が示すブロックに移動させ、管理情報テーブル20を更新する。また、NANDコントローラ6aは、管理情報テーブル20の全エントリについて、上述した処理を実行し、全エントリについて処理が終了した場合は、管理情報テーブル20に格納された全ての書き込みビットを「0」にリセットする。

#### 【0179】

この結果、NANDコントローラ6aは、カウンタを用いずとも、書き込みから所定の期間が経過したデータを移動させることができるので、管理情報テーブル20のデータ量を削減できる。なお、NANDコントローラ6aは、データの移動を行った際に書き込みビットの値を「1」に更新し、全エントリについて処理が終了した場合は、管理情報テーブル20に格納された全ての書き込みビットを「0」にリセットしなくともよい。かかる場合は、NANDコントローラ6aは、任意のタイミングで、書き込みビットのリセットを行えばよい。

#### 【0180】

##### (6) リクエスト数計測の粒度について

上述したNANDコントローラ6dは、各ブロックに対して発行されたリクエストの数をリクエスト数計測部22がブロックごとに計測し、ブロックごとに閾値を設定した。しかし、実施例はこれに限定されるものではなく、NANDコントローラ6dは、異なる粒度でリクエスト数の計測と閾値の設定を行ってもよい。例えば、NANDコントローラ6dは、すべてのブロックに対して発行されたリクエストを共通のカウンタで計測し、NANDコントローラ6d全体で共通の閾値を1つ設定してもよい。また、NANDコントローラ6dは、複数のブロックを含むグループごとに、リクエストが発行された数に応じた閾値を設定してもよい。

#### 【0181】

このように、NANDコントローラ6dは、すべてのブロックに対して発行されたリクエストの数に応じて、データの移動を判定する閾値を設定した場合は、例えば、読み出しや書き込みが頻繁に発行される場合は、データの移動を先延ばしできる。また、NANDコントローラ6dは、読み出し要求や書き込み要求があまり発行されていない場合は、データの移動を前倒しして実行できる。この結果、NANDコントローラ6dは、アクセス性能の悪化や、ビット化けを防ぐことができる。

#### 【0182】

##### (7) プログラム

上記の実施例で説明したNANDコントローラ6a～6dが発揮する機能は、予め用意された制御プログラムをNANDコントローラ内の演算処理装置が実行することで実現してもよい。そこで、以下では、図19を用いて、上記のNANDコントローラ6aと同様の機能を有する制御プログラムを実行するコンピュータの一例について説明する。

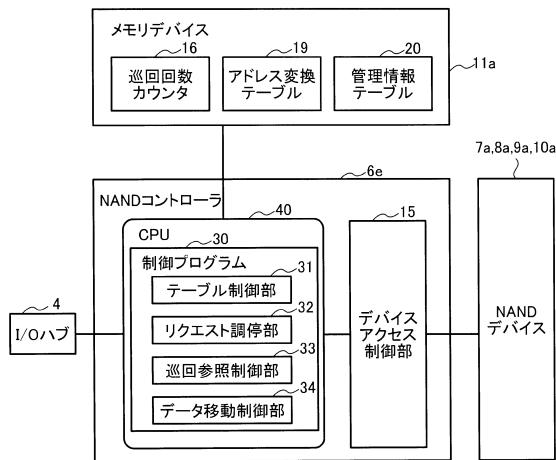

#### 【0183】

図19は、制御プログラムを実行するNANDコントローラの一例を説明する図である。図19に示すように、NANDコントローラ6eは、CPU40、デバイスアクセス制御部15を有する。また、CPU40は、メモリデバイス11aと接続される。なお、メモリデバイス11aは、NANDコントローラ6eに内蔵されるメモリであってもよい。

#### 【0184】

メモリデバイス11aには、巡回回数カウンタ16、アドレス変換テーブル19、管理情報テーブル20があらかじめ記憶される。ここで、CPU40が制御プログラム30を読み出して展開して実行することにより、制御プログラム30は、以下の様に機能する。すなわち、制御プログラム30は、CPU40をテーブル制御部31、リクエスト調停部32、巡回参照制御部33、データ移動制御部34として動作させる。ここで、テーブル制御部31、リクエスト調停部32、巡回参照制御部33、データ移動制御部34は、図6

10

20

30

40

50

に示すテーブル制御部 14、リクエスト調停部 13、巡回参照制御部 17、データ移動制御部 18 と同様の機能を発揮する。

【0185】

なお、上記の制御プログラム 30 は、CPU40 に、巡回参照制御の実行回数を巡回回数カウンタ 16 としてメモリデバイス 11a 上に格納させる。そして、制御プログラム 30 は、CPU40 に、全てのブロックに対して巡回参照制御を実行させた場合は、巡回回数カウンタ 16 の値を更新させる。また、NANDコントローラ 6e は、CPU ではなく、例えば MPU や FPGA 等の演算装置を用いて制御プログラム 30 を実行しても良い。

【0186】

また、上記の制御プログラム 30 については、例えば、メモリデバイス 11a や、NAND デバイス 7a ~ 10a に記憶させてもよいし、他の方法で CPU40 に実行させてもよい。例えば、フレキシブルディスク、いわゆる FD (Flexible Disk)、CD (Compact Disk) - ROM、DVD (Digital Versatile Disk)、光磁気ディスク、IC カードなどの「可搬用の物理媒体」に各プログラムを記憶させる。

【0187】

そして、NANDコントローラ 6e が各 CPU3a、3b を介して、これらの可搬用の物理媒体から各プログラムを取得して実行するようにしてもよい。また、公衆回線、インターネット、LAN、WAN (Wide Area Network) などを介して他のコンピュータまたはサーバ装置などに記憶させた各プログラムを取得して実行するようにしてもよい。

【符号の説明】

【0188】

- 1 情報処理装置

- 2a、2b メモリ

- 3a、3b、40 CPU

- 4 I/O ハブ

- 5a、5b SSD

- 6a ~ 6e NANDコントローラ

- 7a ~ 10a、7b ~ 10b NANDデバイス

- 11 テーブル記憶部

- 12 リクエスタインターフェース部

- 13、32 リクエスト調停部

- 14、31 テーブル制御部

- 15 デバイスアクセス制御部

- 16 巡回回数カウンタ

- 17、33 巡回参照制御部

- 18、34 データ移動制御部

- 19 アドレス変換テーブル

- 20 管理情報テーブル

- 21 巡回済対象記憶部

- 22 リクエスト数計測部

- 30 制御プログラム

10

20

30

40

【図1】

【図2】

【図3】

従来のNANDコントローラが実行する処理の一例を説明する図

【図4】

従来のタイムスタンプを用いた処理を説明する図

【 図 5 】

【図7】

### 実施例1に係るアドレス変換テーブルに格納された情報の一例を説明する図

| 論理ブロックアドレス | 物理ブロックアドレス |

|------------|------------|

| L0         | P4         |

| L1         | P2         |

| L2         | P3         |

| L3         | P6         |

| L4         | P7         |

| L5         | P1         |

| L6         | P0         |

| L7         | P5         |

【 図 6 】

## 実施例1に係るNANDコントローラの機能構成を説明する図

【図8】

## 実施例1に係る管理情報テーブルに格納された情報の一例を説明する図

| 物理ブロックアドレス | パリッドビット | タイムスタンプ |

|------------|---------|---------|

| P0         | 1       | 2       |

| P1         | 1       | 7       |

| P2         | 0       | -       |

| P3         | 0       | -       |

| P4         | 0       | -       |

| P5         | 1       | 7       |

| P6         | 0       | -       |

| P7         | 0       | -       |

| ⋮          | ⋮       | ⋮       |

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

平均要求発行数に応じた閾値の一例を説明する図

| 10秒間の平均要求発行数 | 閾値 |

|--------------|----|

| 0~9          | 4  |

| 10~49        | 3  |

| 50~99        | 2  |

| 100~         | 1  |

【図17】

【 図 1 8 】

【図19】

### 制御プログラムを実行するNANDコントローラの一例を説明する図

---

フロントページの続き

(56)参考文献 特開2009-110314(JP,A)

特開2010-146512(JP,A)

特開2010-146515(JP,A)

特開2010-250413(JP,A)

特表2007-507804(JP,A)

特表2009-512119(JP,A)

特開平6-19778(JP,A)

特開2012-33047(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 12 / 16

G 11 C 16 / 34