(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6140965号

(P6140965)

(45) 発行日 平成29年6月7日(2017.6.7)

(24) 登録日 平成29年5月12日(2017.5.12)

|                |           |        |           |

|----------------|-----------|--------|-----------|

| (51) Int.Cl.   | F 1       |        |           |

| HO 1 L 23/522  | (2006.01) | HO 1 L | 21/88 J   |

| HO 1 L 21/768  | (2006.01) | HO 1 L | 27/14 A   |

| HO 1 L 21/3205 | (2006.01) | HO 1 L | 27/14 D   |

| HO 1 L 27/146  | (2006.01) | HO 1 L | 21/90 B   |

| HO 1 L 27/14   | (2006.01) | HO 4 N | 5/335 690 |

請求項の数 18 (全 21 頁) 最終頁に続く

|           |                              |           |                                            |

|-----------|------------------------------|-----------|--------------------------------------------|

| (21) 出願番号 | 特願2012-215971 (P2012-215971) | (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (22) 出願日  | 平成24年9月28日(2012.9.28)        | (74) 代理人  | 100126240<br>弁理士 阿部 琢磨                     |

| (65) 公開番号 | 特開2014-72297 (P2014-72297A)  | (74) 代理人  | 100124442<br>弁理士 黒岩 創吾                     |

| (43) 公開日  | 平成26年4月21日(2014.4.21)        | (72) 発明者  | 古田 真梨子<br>東京都大田区下丸子3丁目30番2号キヤ<br>ノン株式会社内   |

| 審査請求日     | 平成27年9月28日(2015.9.28)        | 審査官       | 佐藤 靖史                                      |

最終頁に続く

(54) 【発明の名称】半導体装置およびその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

光電変換素子が設けられた第1半導体層を含む第1素子部と、前記第1素子部に電気的に接続された第1配線を含む第1配線部と、を有する第1部品と、

第2半導体層を含む第2素子部と、前記第2素子部に電気的に接続された第2配線を含む第2配線部と、を有する第2部品とを、

前記第1素子部と前記第2素子部との間に前記第1配線部および前記第2配線部が位置するように接合する接合工程と、

前記第1配線を構成する第1配線パターンおよび前記第2配線を構成する第2配線パターンの両方に接触する導電部材を形成して前記第1配線と前記第2配線とを電気的に接続する接続工程と、

前記接続工程の後に、前記第1素子部に対して前記第1配線部側とは反対側に光学部材を形成する工程と、を備え、

前記接続工程は、前記第1部品を貫通し、前記第2配線パターンを露出する貫通孔を、前記貫通孔が前記第1配線パターンを露出し、かつ、前記貫通孔が前記第1配線パターンの複数の部分の間に位置するように形成する第1段階と、前記貫通孔に露出した前記第1配線パターンおよび前記第2配線パターンの両方に接触する前記導電部材を前記貫通孔内に形成する第2段階と、を有し、

前記第2段階では、前記貫通孔の内面にチタン層、チタン化合物層、タンタル層およびタンタル化合物層の少なくともいずれかを形成した後に、銅を前記貫通孔に埋め込むこと

10

20

を特徴とする半導体装置の製造方法。

【請求項 2】

光電変換素子が設けられた第1半導体層を含む第1素子部と、前記第1素子部に電気的に接続された第1配線を含む第1配線部と、を有する第1部品と、

第2半導体層を含む第2素子部と、前記第2素子部に電気的に接続された第2配線を含む第2配線部と、を有する第2部品とを、

前記第1素子部と前記第2素子部との間に前記第1配線部および前記第2配線部が位置するように接合する接合工程と、

前記第1配線を構成する第1配線パターンおよび前記第2配線を構成する第2配線パターンの両方に接触する導電部材を形成して前記第1配線と前記第2配線とを電気的に接続する接続工程と、

前記接続工程の後に、前記第1素子部に対して前記第1配線部側とは反対側に光学部材を形成する工程と、を備え、

前記接合工程は、前記第1配線パターンと前記第2配線パターンが重なり合うように行われ、

前記接続工程は、前記第1部品を貫通し、前記接合工程において前記第2配線パターンの前記第1配線パターンに重なる部分を露出する貫通孔を、前記貫通孔が前記第1配線パターンを露出し、かつ、前記接合工程において前記第1配線パターンの前記第2配線パターンに重なる部分を除去するように形成する第1段階と、前記貫通孔に露出した前記第1配線パターンおよび前記第2配線パターンの両方に接触する前記導電部材を前記貫通孔内に形成する第2段階と、を有し、

前記第2段階では、前記貫通孔の内面にチタン層、チタン化合物層、タンタル層およびタンタル化合物層の少なくともいずれかを形成した後に、銅を前記貫通孔に埋め込むことを特徴とする半導体装置の製造方法。

【請求項 3】

前記貫通孔の幅は、前記接合工程において前記第1配線パターンの前記第2配線パターンに重なる前記部分の幅よりも小さい請求項2に記載の半導体装置の製造方法。

【請求項 4】

前記貫通孔は前記第1配線パターンに囲まれるように形成される請求項1乃至3のいずれか1項に記載の半導体装置の製造方法。

【請求項 5】

前記貫通孔は、前記第1配線パターンと前記第1半導体層との間に位置する第1絶縁体層を貫通し、前記第1配線パターンと前記第2配線パターンとの間に位置する第2絶縁体層を貫通し、

前記貫通孔の前記第1絶縁体層を貫通する部分の幅が、前記貫通孔の前記第2絶縁体層を貫通する部分の幅よりも大きい請求項1乃至4のいずれか1項に記載の半導体装置の製造方法。

【請求項 6】

前記第1段階では、前記第1配線パターンと前記第1半導体層との間に位置する第1絶縁体層のエッチングと、前記第1配線パターンと前記第2配線パターンとの間に位置する第2絶縁体層のエッチングを行い、前記第1絶縁体層のエッチングと前記第2絶縁体層のエッチングとで、同じマスクパターンを用いる請求項1乃至5のいずれか1項に記載の半導体装置の製造方法。

【請求項 7】

前記貫通孔を設ける前に、前記第1配線パターンは前記貫通孔が設けられる位置に開口を有する請求項1乃至6のいずれか1項に記載の半導体装置の製造方法。

【請求項 8】

前記導電部材は、前記第1配線パターンの側面および前記第1配線パターンの前記第1半導体層側の面に接触する請求項1乃至7のいずれか1項に記載の半導体装置の製造方法。

。

10

20

30

40

50

## 【請求項 9】

前記第1段階では、前記第1配線パターンのエッチングを行う請求項1乃至8のいずれか1項に記載の半導体装置の製造方法。

## 【請求項 10】

前記第1配線パターンは銅層、タンゲステン層またはアルミニウム層である第1導電層と、タンタル層、窒化タンタル層、チタン層または窒化チタン層である第2導電層と、を有し、前記導電部材は前記第2導電層に接触する請求項1乃至9のいずれか1項に記載の半導体装置の製造方法。

## 【請求項 11】

光電変換素子が設けられた第1半導体層を含む第1素子部と、

前記第1素子部に電気的に接続された第1配線を含む第1配線部と、

第2半導体層を含む第2素子部と、

前記第2素子部に電気的に接続された第2配線を含む第2配線部と、

前記第1素子部に対して前記第1配線部側とは反対側に配された光学部材と、を備える半導体装置であって、

前記第1素子部と前記第2素子部との間に前記第1配線部および前記第2配線部が位置し、前記第1素子部と前記第2配線部との間に前記第1配線部が位置し、

前記第1素子部および前記第1配線部を貫通し、前記第1配線の第1配線パターンと前記第2配線の第2配線パターンに接触する導電部材が設けられており、

前記導電部材の前記第1配線部を貫通する部分は、前記第1配線パターンの複数の部分の間に位置し、

前記導電部材は、銅層と前記銅層と前記第1配線パターンの前記複数の部分との間に位置し、チタン層、チタン化合物層、タンタル層およびタンタル化合物層の少なくともいずれかを含む膜と、を有することを特徴とする半導体装置。

## 【請求項 12】

前記導電部材は前記第1配線パターンに囲まれる請求項11に記載の半導体装置。

## 【請求項 13】

前記導電部材は、前記第1配線パターンと前記第1半導体層との間に位置する第1絶縁体層を貫通し、前記第1配線パターンと前記第2配線パターンとの間に位置する第2絶縁体層を貫通し、

前記導電部材の前記第1絶縁体層を貫通する部分の幅が、前記導電部材の前記第2絶縁体層を貫通する部分の幅よりも大きい請求項11または12に記載の半導体装置。

## 【請求項 14】

前記第1配線パターンは銅層、タンゲステン層またはアルミニウム層である第1導電層と、タンタル層、窒化タンタル層、チタン層または窒化チタン層である第2導電層と、を有し、前記導電部材は前記第2導電層に接触する請求項11乃至13のいずれか1項に記載の半導体装置。

## 【請求項 15】

前記複数の部分は、前記第2配線パターンに重なる請求項11乃至14のいずれか1項に記載の半導体装置。

## 【請求項 16】

前記導電部材は、前記第1配線パターンの側面および前記第1配線パターンの前記第1半導体層側の面に接触する請求項11乃至15のいずれか1項に記載の半導体装置。

## 【請求項 17】

前記光学部材に含まれる層が前記導電部材を覆う請求項11乃至16のいずれか1項に記載の半導体装置。

## 【請求項 18】

端子を有するパッケージを更に備え、

前記第1半導体層には前記端子との接続のための開口が設けられている請求項11乃至17のいずれか1項に記載の半導体装置。

10

20

30

40

50

**【発明の詳細な説明】****【技術分野】****【0001】**

複数の素子部を有する半導体装置に関する。

**【背景技術】****【0002】**

半導体装置の一種であるC M O Sイメージセンサなどの光電変換装置では、複数の光電変換素子を有する光電変換ユニットと、光電変換ユニットからの電気信号を処理する信号処理ユニットとを1つの半導体基板にモノリシックに作り込んでいた。光電変換ユニットと信号処理ユニットとを別々の部品(チップ)に分けて形成し、これらの部品を重ね合せ、部品同士を導電部材で電気的に接続することが検討されている。このようにすることで、光電変換装置が搭載される電子機器における光電変換装置の占有面積(フットプリント)を効率的に活用することができる。このような構造は、いわゆるシステムインパッケージを実現する種々の半導体装置に応用が可能である。10

**【0003】**

特許文献1には、部品に相当する半導体基板(3445)同士の電気的接続を得るための導電部材として、貫通接続導体(64)、接続導体(65)、および接続用配線(72)を設けることが記載されている(特許文献1の図3参照)。あるいは導電部材として、1つの貫通接続導体(84)を設けることが記載されている(特許文献1の図15参照)20

。

**【先行技術文献】****【特許文献】****【0004】****【特許文献1】特開2010-245506号公報****【発明の概要】****【発明が解決しようとする課題】****【0005】**

特許文献1の技術では、電気的接続についての検討が十分でない。貫通接続導体(64)と接続導体(65)を設けて、これらを接続用配線(72)で接続する場合、半導体層を2回貫通することにより配線容量や配線抵抗が大きくなり、配線遅延により半導体装置性能が低下し得るという問題がある。また、貫通接続導体(84)を用いると、製造時のアライメントずれおよび/または使用時のクラックに起因して、貫通接続孔(85)と配線(40)と配線(53)の接続不良が生じやすいという問題がある。30

そこで本発明は、導電部材による電気的接続の性能および信頼性の高い半導体装置を提供することを目的とする。

**【課題を解決するための手段】****【0006】**

課題を解決するための手段は、半導体装置の製造方法であって、第1半導体層を含む第1素子部と、前記第1素子部に電気的に接続された第1配線を含む第1配線部と、を有する第1部品と、第2半導体層を含む第2素子部と、前記第2素子部に電気的に接続された第2配線を含む第2配線部と、を有する第2部品とを、前記第1素子部と前記第2素子部との間に前記第1配線部および前記第2配線部が位置するように接合する接合工程と、前記第1配線を構成する第1配線パターンおよび前記第2配線を構成する第2配線パターンの両方に接触する導電部材を形成して前記第1配線と前記第2配線とを電気的に接続する接続工程と、を備え、前記接続工程は、前記第1部品を貫通し、前記第2配線パターンを露出する貫通孔を、前記貫通孔が前記第1配線パターンを露出し、かつ、前記貫通孔が前記第1配線パターンの複数の部分の間に位置するように形成する第1段階と、前記貫通孔に露出した前記第1配線パターンおよび前記第2配線パターンの両方に接触する前記導電部材を前記貫通孔内に形成する第2段階と、を有することを特徴とする。40

50

## 【0007】

また、課題を解決するための手段は、半導体装置の製造方法であって、第1半導体層を含む第1素子部と、前記第1素子部に電気的に接続された第1配線を含む第1配線部と、を有する第1部品と、第2半導体層を含む第2素子部と、前記第2素子部に電気的に接続された第2配線を含む第2配線部と、を有する第2部品とを、前記第1素子部と前記第2素子部との間に前記第1配線部および前記第2配線部が位置するように接合する接合工程と、前記第1配線を構成する第1配線パターンおよび前記第2配線を構成する第2配線パターンの両方に接触する導電部材を形成して前記第1配線と前記第2配線とを電気的に接続する接続工程と、を備え、前記接合工程は、前記第1配線パターンと前記第2配線パターンが重なり合うように行われ、前記接続工程は、前記第1部品を貫通し、前記接合工程において前記第2配線パターンの前記第1配線パターンに重なる部分を露出する貫通孔を、前記貫通孔が前記第1配線パターンを露出し、かつ、前記接合工程において前記第1配線パターンの前記第2配線パターンに重なる部分を除去するように形成する第1段階と、前記貫通孔に露出した前記第1配線パターンおよび前記第2配線パターンの両方に接触する前記導電部材を前記貫通孔内に形成する第2段階と、を有することを特徴とする。

10

## 【0008】

また、課題を解決するための手段は、半導体装置であって、第1半導体層を含む第1素子部と、前記第1素子部に電気的に接続された第1配線を含む第1配線部と、第2半導体層を含む第2素子部と、前記第2素子部に電気的に接続された第2配線を含む第2配線部と、を備える半導体装置であって、前記第1素子部と前記第2素子部との間に前記第1配線部および前記第2配線部が位置し、前記第1素子部と前記第2配線部との間に前記第1配線部が位置し、前記第1素子部および前記第1配線部を貫通し、前記第1配線の第1配線パターンと前記第2配線の第2配線パターンに接触する導電部材が設けられており、前記導電部材の前記第1配線部を貫通する部分は、前記第1配線パターンの複数の部分の間に位置することを特徴とする。

20

## 【発明の効果】

## 【0009】

本発明によれば、導電部材による電気的接続の性能および信頼性が高い半導体装置を提供することができる。

30

## 【図面の簡単な説明】

## 【0010】

【図1】半導体装置の一例の模式図。

【図2】半導体装置の一例の模式図。

【図3】半導体装置の製造方法の一例の模式図。

【図4】半導体装置の製造方法の一例の模式図。

【図5】半導体装置の製造方法の別の例の模式図。

【図6】半導体装置の製造方法を説明する模式図。

## 【発明を実施するための形態】

## 【0011】

以下、本発明を実施するための形態を、図面を参照しながら説明する。なお、以下の説明において、複数の図面を相互に参照する場合がある。また、同一あるいは類似の構成について共通の符号を付しており、共通の符号を付した構成については適宜説明を省略する。

40

## 【0012】

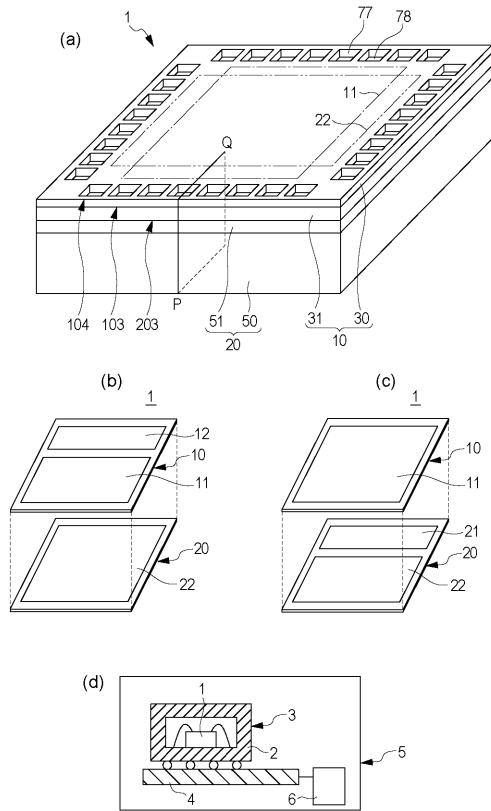

本実施形態の半導体装置の一例としての光電変換装置を、図1を用いて説明する。図1(a)は半導体装置の主要部である半導体デバイス1の斜視図である。図1(b)、(c)は半導体デバイス1の一例の分解斜視図である。図1(d)は半導体デバイス1を含む半導体装置3および電子機器5の模式図である。

## 【0013】

図1(a)に示した半導体デバイス1においては、図1(b)または図1(c)に示し

50

たように、第1部分10と第2部分20が重なっている。本実施形態は、主に、第1部分10と第2部分20との電気的接続を得るための導電部材に関する。第1部分10は、第1素子部30と第1配線部31によりなる。第2部分20は第2素子部50と第2配線部51よりなる。第2配線部51が第1部分10と第2素子部50との間に位置する。本実施形態では、第1部分10の第1配線部31が第1素子部30と第2素子部との間に位置するが、第1部分10の第1素子部30が第1配線部31と第2素子部50との間に位置してもよい。

【0014】

本実施形態では、第1部分10は入射光に応じて信号電荷が発生する光電変換ユニット11を有する。光電変換ユニット11は光電変換素子を含む。光電変換ユニット11は光電変換素子で発生した信号電荷に基づく電気信号を生成する信号生成回路を含み得る。信号生成回路は、例えば、増幅トランジスタや転送トランジスタ、リセットトランジスタ、選択トランジスタを含む。他の例の光電変換ユニット11は、光電変換素子と信号電荷を転送するためのCCD(Charge Coupled Device:電荷結合素子)を含み得る。

【0015】

本実施形態では、第2部分20は、信号処理ユニット22を有する。信号処理ユニット22は、光電変換ユニット11で発生した信号電荷に基づく電気信号を処理する。信号処理ユニット22は、ノイズ除去回路、増幅回路、変換回路、画像処理回路を含むことができる。ノイズ除去回路は、例えばCDS(Correlated Double Sampling:相関二重サンプリング)回路である。増幅回路は、例えば列アンプ回路である。変換回路は、例えばコンパレータとカウンタで構成されたADC(Analog Digital Converter:アナログデジタル変換)回路である。画像信号処理回路は、例えばメモリとプロセッサを含み、アナログデジタル変換されたデジタル信号から画像データを生成したり、画像データに画像処理を施したりする。

【0016】

図1(a)では、光電変換ユニット11の位置を一点鎖線で囲んで示し、信号処理ユニット22の位置を二点鎖線で囲んで示している。ここでは光電変換ユニット11の、第2部分20への正射影領域の一部に信号処理ユニット22の一部が位置している。しかし、光電変換ユニット11の第2部分20への正射影領域の全部に信号処理ユニット22の全部または一部が位置していてもよい。あるいは、第2部分20における光電変換ユニット11の正射影領域の一部に、信号処理ユニット22の全部または一部が位置していてもよい。なお、信号処理ユニット22の一部が第1部分10に設けられていてもよい。例えば、ノイズ除去回路や増幅回路などアナログ信号用の信号処理ユニットを第1部分10に設け、変換回路や画像処理回路などデジタル信号用の信号処理ユニットを第2部分20に設けることもできる。

【0017】

図1(b)、(c)に示す様に、半導体デバイス1は、光電変換ユニット11を制御する制御ユニット12、および/または、信号処理ユニット22を制御する制御ユニット21を更に備えることができる。これら制御ユニットは、第1部分10と第2部分20の少なくとも一方に設けることができる。図1(b)に示した例では制御ユニット12が第1部分10に設けられており、図1(c)に示した例では制御ユニット21が第2部分20に設けられている。光電変換ユニット11用の制御ユニットを第1部分10に、信号処理ユニット22用の制御ユニットを第2部分20に分けて設けることもできる。制御ユニット12は垂直走査線を介して画素回路に駆動信号を供給する垂直駆動回路や、電源回路を含み得る。制御ユニット21は信号処理ユニット22を駆動するためのタイミング発生回路や、変換回路へ参照信号を供給する参照信号供給回路、増幅回路あるいは変換回路から信号を順次読み出すための水平走査回路を含み得る。

【0018】

図1(d)に示す様に、半導体装置3は、半導体デバイス1の1次実装用の実装部材と

10

20

30

40

50

して、パッケージ 2 を含むことができる。半導体デバイス 1 はこのパッケージにダイボンドされ、収容されうる。パッケージ 2 は PGA (Pin Grid Array) や LGA (Land Grid Array)、BGA (Ball Grid Array) 、リードフレーム等の外部端子を含み得る。図 1 (d) に示す様に、半導体装置 3 は、2 次実装用の実装部材として、回路基板 4 を含むことができる。パッケージ 2 はこの回路基板 4 に実装されうる。回路基板 4 は、リジッド基板、フレキシブル基板あるいはリジッドフレキシブル基板等のプリント基板でありうる。光電変換装置としての半導体装置 3 は半導体デバイス 1 に光を導くための光学系を含みうる。

## 【0019】

半導体装置 3 は、種々の電子機器に搭載が可能である。電子機器 5 は半導体装置 3 に加えて、演算装置、記憶装置、記録装置、通信装置あるいは表示装置などの周辺装置 6 を備える。これら周辺装置は、半導体装置 3 と接続されて、直接的にあるいは間接的に信号のやり取りをおこなう。電子機器 5 としては、携帯電話やパーソナルコンピュータなどの情報端末、カメラやディスプレイなどの映像機器などが挙げられる。勿論、カメラ付きの情報端末なども含まれる。

## 【0020】

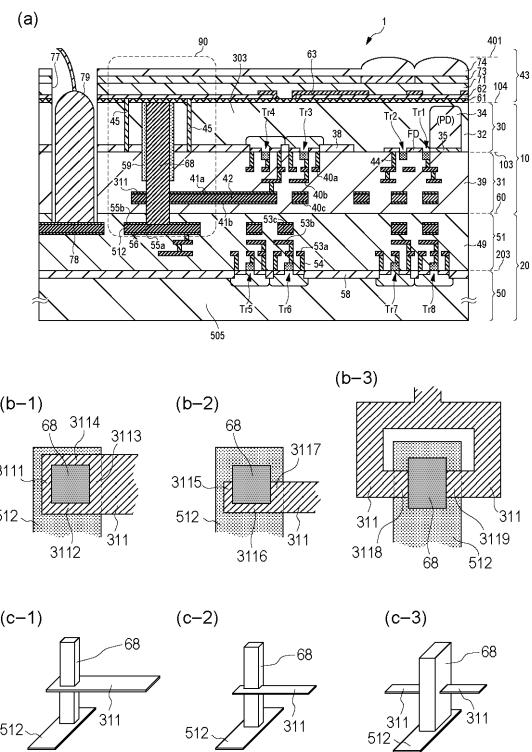

半導体デバイス 1 の一例の詳細を、図 2 を用いて説明する。図 2 は、図 1 (a) に示した点 P と点 Q を含む面における半導体デバイス 1 の断面図である。なお、図 2 は図 1 (b) の様に、制御ユニット 12 を有する例である。

## 【0021】

以下の説明において、導電体層は半導体層よりも導電率の高い材料からなるものとし、絶縁体層は半導体層よりも導電率の低い材料からなるものとする。

## 【0022】

また、以下の半導体化合物や金属化合物の説明において、炭化窒化物および酸化窒化物は窒化物に含める。窒化炭化物および酸化炭化物は炭化物に含める。

## 【0023】

まず、第 1 部分 10 について、第 1 素子部 30 と第 1 配線部 31 のそれぞれの構成を説明する。

## 【0024】

第 1 素子部 30 は第 1 半導体層 303 を含む。第 1 半導体層 303 は例えばシリコン層である。第 1 素子部 30 は、図 1 (b) における光電変換ユニット 11 を構成する半導体素子（光電変換素子）として第 1 半導体層 303 に設けられたフォトダイオード PD を有する。フォトダイオード PD は、第 1 半導体層 303 の p 型半導体領域 32 と n 型半導体領域 34 と p 型半導体領域 35 を含む。光電変換素子はフォトゲートでもよい。光電変換ユニット 11 は光電変換素子で発生した信号電荷に基づく電気信号を生成する信号生成回路を含み得る。信号生成回路は、MOS トランジスタ等の半導体素子で構成することができる。図 2 には、第 1 部分 10 の光電変換ユニット 11 の転送トランジスタ Tr 1 と、リセットトランジスタ Tr 2 とを示している。また、図 1 (b) における第 1 部分 10 の制御ユニット 12 の半導体素子として、トランジスタ Tr 3 、Tr 4 とを示している。

## 【0025】

本例では、第 1 素子部 30 を構成する第 1 半導体層 303 の表面 103 の一部は MOS トランジスタ Tr 1 、Tr 2 、Tr 3 、Tr 4 のゲート絶縁膜と界面を成している。第 1 素子部 30 には STI (Shallow Trench Isolation) や LOCOS (Local Oxidation of Silicon) などの素子分離 38 が設けられている。第 1 半導体層 303 の上には、第 1 半導体層 303 の表面 103 を保護する、窒化シリコンや酸化シリコンなどの絶縁体層からなる第 1 保護膜（不図示）が設けられている。このように、第 1 素子部 30 は第 1 半導体層 303 に加えて、素子分離 38 やゲート絶縁膜、ゲート電極、第 1 保護膜を含み得る。

## 【0026】

第 1 配線部 31 は、導電体層および絶縁体層を含む。第 1 配線部 31 は複数の配線レベ

10

20

30

40

50

ルを有しうる。1つの配線レベルは、配線パターンとプラグを有しうる。典型的な導電体層は配線パターンを構成する。さらに典型的な導電体層は配線パターンの内で電流密度の大きい主導電層を構成するが、導電体層は配線パターンの内で主導電層よりも電流密度の小さい副導電層を構成する場合もある。導電体層は下の配線レベルとの導通を得るためのビアプラグ、あるいは第1素子部30との導通を得るためのコンタクトプラグを構成する場合もある。

【0027】

ビアプラグやコンタクトプラグもまた、主導電層と副導電層で構成され得る。これら副導電層は典型的にはバリアメタルでありうる。バリアメタルのバリア機能としては、主導電層と絶縁体層との間での拡散に対するバリア、或いは主導電層と絶縁体層との間の反応に対するバリアが挙げられる。しかし、「バリアメタル」は、副導電層に与えられる便宜的な呼称であって何らかのバリア機能を有しているとは限らない。バリアメタルは、これらのバリア機能を必要としない場合であっても、単に主導電層を形成する際の下地としてや、エレクトロマイグレーションやストレスマイグレーションの緩和などを目的として用いられる。

【0028】

絶縁体層は同じ配線レベルの配線パターン同士を絶縁する配線間絶縁層および/または異なる配線レベルの配線パターン同士を絶縁する層間絶縁層として機能し得る。第1配線部31は1層以上の導電体層で構成された、多数の電気経路(配線)を有する。一つの配線は、コンタクトプラグ、ビアプラグおよび配線パターンで構成されうる。

【0029】

第1配線部31の詳細な構成を説明する。第1配線部31には、コンタクトプラグ44と、配線パターン40a、40b、40cおよびビアプラグが設けられている。導電体層で構成されたこれらコンタクトプラグ、配線パターン、ビアプラグが多数の電気経路を構成する。コンタクトプラグ44は主にタングステン層からなり、タングステン層に加えて、チタン層および/または窒化チタン層を含むバリアメタルを有する。配線パターン40a、40b、40cおよびビアプラグは主に銅層からなり、銅層に加えて、窒化タンタル層および/またはタンタル層を含むバリアメタルを有する。配線パターン40aは1つの銅層で構成され、配線パターン40bとビアプラグ、および配線パターン40cとビアプラグは、それぞれ1つの銅層で一体的に構成される。本例の第1配線311は、配線パターン40cを含んでおり、半導体素子とは、不図示の部分で、コンタクトプラグ44と、配線パターン40a、40bおよびビアプラグを介して接続されている。

【0030】

第1配線部31には、層間絶縁層あるいは配線間絶縁層としての、主に酸化シリコンからなる絶縁体層を含む絶縁体膜39が設けられている。典型的な絶縁体膜39は複数の絶縁体層を有する多層膜である。第1配線部31の絶縁体膜39は、窒化シリコン、炭化シリコンなどからなる不図示の絶縁体層を、配線パターン40a、40b、40cに含有される銅の拡散防止層としてさらに有することができる。これらは、層間絶縁層と配線パターンの間に配され得る。

【0031】

次に、第2部分20について、第2素子部50と第2配線部51のそれぞれの構成を説明する。

【0032】

第2素子部50は第2半導体層505を含み、信号処理ユニット22を構成する半導体素子としてのMOSトランジスタTr5、Tr6、Tr7、Tr8を有する。本例では、第2半導体層505の表面203の一部は、MOSトランジスタTr5、Tr6、Tr7、Tr8のゲート絶縁膜と界面を成している。第2素子部50にはSTIやLOCOSなどの素子分離58が設けられている。第2半導体層505の上には、第2半導体層505の表面203を保護する窒化シリコンや酸化シリコンなどの絶縁体からなる第2保護膜(不図示)が設けられている。第2素子部50は第2半導体層505に加えて、素子分離5

10

20

30

40

50

8 やゲート絶縁膜、ゲート電極、第2保護膜を含み得る。

【0033】

第2配線部51は、導電体層および絶縁体層を含む。第2配線部51の導電体層および絶縁体層も、第1配線部31の導電体層および絶縁体層と同様の機能を有する。

【0034】

第2配線部51の詳細な構成を説明する。第2配線部51には、コンタクトプラグ54aと、複数の配線パターン53a、53b、53cおよびビアプラグ54b、54cが設けられている。導電体層で構成されたこれらコンタクトプラグ、配線パターン、ビアプラグが多数の電気経路を構成する。コンタクトプラグ54aとビアプラグ54cは主にタンゲステン層からなり、タンゲステン層に加えて、チタン層および/または窒化チタン層を含むバリアメタルを有する。配線パターン53a、53bおよびビアプラグ54bは主に銅層からなり、銅層に加えて、窒化タンタル層および/またはタンタル層を含むバリアメタルを有する。配線パターン53aは1つの銅層を含み構成される。配線パターン53bとビアプラグ54bは、1つの銅層で一体的に構成される。配線パターン53cは主にアルミニウム層からなり、アルミニウム層に加えて、チタン層および/または窒化チタン層を含むバリアメタルを有する。本例の第2配線512は、配線パターン53cを含んでおり、半導体素子とは、不図示のコンタクトプラグ54aと、配線パターン53a、53bおよびビアプラグ54b、54cを介して接続されている。

【0035】

第2配線部51には、層間絶縁層あるいは配線間絶縁層として、主に酸化シリコンからなる絶縁体層を含む絶縁体膜49が設けられている。典型的な絶縁体膜49は複数の絶縁体層を有する多層膜である。第2配線部51の絶縁体膜49は窒化シリコンや炭化シリコンからなる不図示の絶縁体層を、配線パターン53a、53bに含有される銅の拡散防止層としてさらに有することができる。これらは、層間絶縁層と配線パターンの間に配され得る。

【0036】

第1配線部31と第2配線部51の配線パターン40a、40b、40c、53a、53bやプラグにおいて、銅層やタンゲステン層、アルミニウム層は、配線における導電率の高い主導電層として機能する。主導電層は、バリアメタルに用いられるタンタル層や窒化タンタル層、チタン層、窒化チタン層などの副導電層よりも導電率の高い材料からなり、また、電流が流れる方向における断面積が小さく、低抵抗である。

【0037】

配線パターン40a、40b、40c、53a、53bが主に銅層からなる例を示したが、これらには、配線パターン53cの様に、主にアルミニウム層からなる配線パターンを採用することもできる。なお、銅層やアルミニウム層は単体の銅のみならず、他の金属が添加された合金であってもよい。例えば、銅層は銅よりも少ないアルミニウムやシリコンなどを添加物として含み得るし、アルミニウム層はアルミニウムより少ない銅やシリコンなどを添加物として含み得る。絶縁体膜39の主たる絶縁体層が酸化シリコンからなる例を挙げたが、BSGやPSG、BPSGなどのケイ酸塩ガラスを用いることもできる。また、酸化シリコンよりも低誘電率の低い材料(LOW-k材料)を用いることもできる。

【0038】

第1配線部31の配線パターンを配線パターン40a、40b、40cの3レベル、第2配線部51の配線パターンは53a、53b、53cの3レベルとする例を示した。しかし、配線パターンのレベル数は適宜設定可能であり、第1配線部31と第2配線部51とで異なっていてもよい。例えば、第2配線部51の配線パターンのレベル数を第1配線部31の配線パターンのレベル数よりも多くしてもよい。

【0039】

続いて、電子デバイス1の他の構造について説明する。

【0040】

10

20

30

40

50

第1部分10と第2部分20は、第1配線部31と第2配線部51とで接合されている。第1配線部31の絶縁体膜39と第2配線部51の絶縁体膜49が、接合面60を介して接合されている。

【0041】

本例の半導体デバイス1は、第1半導体層303のトランジスタTr1～4が設けられた面(表面103)とは反対側の面(裏面104)が受光面となる裏面照射型の光電変換装置を構成する。裏面照射型の光電変換装置において、第1部分10の第1半導体層303の厚みは10μm未満であり、例えば2～5μmである。第2半導体層505の厚みは第1半導体層303よりも厚く、第2半導体層505は第1半導体層303の支持体として機能する。第2半導体層505の厚みは10μm以上であり、例えば20～500μmである。

【0042】

第1半導体層303の裏面104側には、光学部材41が設けられている。

【0043】

光学部材41は、反射防止層61、絶縁体層62、遮光層63、絶縁体層69、平坦化層71、カラーフィルタアレイ73およびマイクロレンズアレイ74を含みうる。光学部材41は第1素子部30の受光面(裏面104)を構成するp型半導体領域32に接触している。光学部材41は第1素子部30側とは反対側に光入射面401を有する。本例では光入射面401はマイクロレンズアレイ74で構成されている。

【0044】

電極パッド78は配線パターン53cと同レベルの層に配されている。電極パッド78の上には、複数の絶縁体層、第1半導体層303、光学部材41を貫通する開口77が設けられている。開口77には、電極パッド78に接続するボンディングワイヤ79が設けられている。ワイヤボンディングはパッケージの内部端子に接続される。なお、半導体デバイス1とパッケージの接続には、ワイヤボンディング接続に限らず、フリップチップ接続を用いることもできる。

【0045】

半導体デバイス1には、第1配線311と第2配線512を相互に接続する導電部材68が設けられている。導電部材68を構成する導電材料は、金、銀、銅、アルミニウム、タンゲステン、タンタル、チタン、マンガン、或いはこれらの窒化物や炭化物などの化合物である。

【0046】

導電部材68は、第1素子部30の第1半導体層303を貫通して第1配線部31の第1配線311に接続し、さらに、第1配線部31を貫通して第2配線部51の第2配線512に接続する。本例では、導電部材68は第1配線311の配線パターン40cに接触し、第2配線512の配線パターン53cに接触する。本実施形態では、導電部材68は第1配線311の配線パターン40cの複数の部分の間に位置しうる。換言すれば、配線パターン40cの複数の部分が導電部材68を挟む。配線パターン40cの導電部材68を挟む複数の部分は、導電部材68に対向する部分(対向部分)である。導電部材68の配線パターン40cの複数の部分の間に位置する部分は、第1配線部31を貫通する部分である。導電部材68を挟む、配線パターン40cの複数の部分(対向部分)は、第2配線512の配線パターン53cに重なっていることが好ましいが、重なっていなくてもよい。2つの配線パターン40c、53cの重なり合う部分は、一方の配線パターンの、他方の配線パターンに重なる部分である。ここで、配線パターンが重なり合うことは、第1半導体層303から第2半導体層505に向かう方向(第1半導体層303と第2半導体層505の法線方向)において、複数の配線パターンが位置することを意味する。

【0047】

図2(b-1)は導電部材68が第1配線311に囲まれている場合の平面図であり、図2(c-1)はその斜視図である。配線パターン40cは、部分3111、3112、3113、3114を有している。導電部材68は、部分3111と部分3113の間に

10

20

30

40

50

位置し、部分 3112 と部分 3114 との間に位置する。また、導電部材 68 は、部分 3111 と部分 3112 の間に位置し、部分 3113 と部分 3114 との間に位置する。これらの部分 3111、3112、3113、3114 は、第 2 配線 512 を構成する配線パターン 53c に重なっていることが望ましいが、重なっていなくてもよい。また、これらの部分 3111、3112、3113、3114 は、導電部材 68 に接触している。本例では、導電部材 68 は第 1 配線 311 の側面に接触している。この側面は、部分 3111、3112、3113、3114 で構成される。ここでは、導電部材 68 は第 1 配線 311 の側面に接触している例を挙げたが、導電部材 68 が第 1 配線 311 の側面ではなく第 1 配線 311 の上面に接触していてもよい。導電部材 68 が第 1 配線 311 の側面および上面に接していてもよい。

10

#### 【0048】

図 2 (b - 2) は導電部材 68 が第 1 配線 311 に挟まれている場合の平面図であり、図 2 (c - 2) はその斜視図である。配線パターン 40c は、部分 3115、3116、3117 を有している。導電部材 68 は、部分 3115 と部分 3117 の間に位置する。また、導電部材 68 は第 1 配線 311 の部分 3115 と部分 3116 との間に位置し、部分 3116 と部分 3117 との間に位置している。図 2 (b - 2) の例では、導電部材 68 は、第 1 配線 311 の連続な 3 つの部分 3115、3116、3117 の側面に面している。そして、3 つの部分のうちの 2 組の 2 部分 (部分 3115 と部分 3115、部分 3116 と部分 3117) の側面が成す角度が 90° である。また、3 つの部分のうちの 1 組の 2 部分 (部分 3115 と部分 3117) の側面が成す角度が 0° (平行) である。図 2 (b - 1) の例と同様に、部分 3115、3116、3117 は第 2 配線 512 を構成する配線パターン 53c に重なっている。

20

#### 【0049】

図 2 (b - 3) は導電部材 68 が第 1 配線 311 に挟まれている場合の平面図であり、図 2 (c - 3) はその斜視図である。配線パターン 40c は、部分 3118、3119 を有している。2 つの部分 3118、3119 は第 1 配線 311 の配線パターン 40c の不連続な部分である。図 2 (b - 3) の例では、部分 3118、3119 は第 2 配線 512 の配線パターン 53c に重なっている。導電部材 68 は部分 3118、3119 の側面に挟まれている。図 2 (b - 3) の例では、導電部材 68 は、そして、2 つの部分 3118 と部分 3119 の成す角度が 0° (平行) である。図 2 (b - 3)、(c - 3) において、導電部材 68 を挟む第 1 配線 311 の 2 つの部分 3114、3115 の双方は、仮に導電部材 68 を絶縁部材に置き換えたとしても、第 1 配線 311 の一部であり得る。ここでは、2 つの部分 3118、3119 が配線パターン 40c 内で電気的に連続している例を示している。しかし、配線パターン 40b、40a など、他の配線レベルを介して 2 つの部分が電気的に連続して一つの電気経路たる第 1 配線 311 を構成していてもよい。

30

#### 【0050】

導電部材 68 が第 1 配線 311 の配線パターンの複数の部分の間に位置することは、複数の部分の、導電部材 68 に向かう面 (対向面) 同士が成す、導電部材 68 側の角度が 180° 未満であることを意味する。つまり、対向面が 1 つの平面のみで構成されなければよい。ここでは、複数の平面を組み合わせて対向面を構成した例を示したが、滑らかな曲面等、明確な境界の無い側面に導電部材 68 が面していてもよい。複数の部分の、導電部材 68 に向かう面 (対向面) が成す、導電部材 68 側の角度は、90° 以下であることが好ましい。例えば、導電部材 68 が円柱形状で、配線パターン 40c の側面が平面視して円弧状であれば、この円弧の中心角が 90° 以上であることが好ましい。円弧の一端における接線と他端における接線の成す角が 90° 以上になるためである。

40

#### 【0051】

導電部材 68 は配線パターン 40a、40b、40c の何れか、もしくは複数に接触しても良く、導電部材 68 は配線パターン 53a、53b、53c の何れか 1 つ、もしくは複数に接触しても良い。また、導電部材 68 は、配線パターンの主導電層に接触する場合もあるし、配線パターンのバリアメタルなどの副導電層に接触する場合もある。また、配

50

線パターンのバリアメタルの副導電層を貫通して、主導電層に接触する場合もある。本例では、配線パターン 40c の主導電層 42 であるアルミニウム層の側面、副導電層 41a、41b である窒化チタン層（およびチタン層）の側面に接触している。そして、導電部材 68 は主導電層 42 の側面に囲まれているか挟まれている。また、配線パターン 53c の主導電層 56 であるアルミニウム層の上面、副導電層 55a、55b である窒化チタン層（およびチタン層）の側面に接触している。

#### 【0052】

本実施形態では、第 1 配線 311 と第 2 配線 512 の電気経路が第 1 配線部 31 と第 2 配線部 51 の外を経由することなく、第 1 配線部 31 および第 2 配線部 51 内に形成されている。これにより、第 1 配線 311 と第 2 配線 512 との間の配線容量および／または配線抵抗の増大を抑制し、半導体装置を高速に動作させることが可能となる。

10

#### 【0053】

また、第 1 配線 311 と導電部材 68 との電気的接続を、導電部材 68 の両側に位置する複数の部分で確保することが可能である。そのため、第 1 配線 311 と導電部材 68 との接続不良が生じにくい構造が得られる。接続不良の一因は、使用時の熱サイクルに起因するクラックや、導電部材 68 や配線パターン 40c の腐食や拡散などの化学変化である。また、接続不良の一因は、後述する製造時のアライメントずれでありうる。

#### 【0054】

導電部材 68 は第 1 半導体層 303 に設けられた絶縁領域 45 に囲まれている。本例の絶縁領域 45 は固体の領域であるが、気体あるいは真空の領域であってもよい。導電部材 68 により、光電変換ユニット 11 と信号処理ユニット 22、光電変換ユニット 11 と制御ユニット 21 あるいは制御ユニット 12 と信号処理ユニット 22 とが電気的に接続されている。あるいは、第 1 部分 10 に設けられた信号処理ユニットの一部と第 2 部分 20 に設けられた信号処理ユニットの一部とが電気的に接続されている。

20

#### 【0055】

図 2 に示したブロック 90 は部分間の接続に関わる導電部材 68、第 1 配線 311、第 2 配線 512、絶縁領域 42 を含む領域を示している。このブロック 90 は、複数個が並列に配されることが好ましい。ブロック 90 が複数に並列に配されることにより、光電変換ユニット 11 の列毎または行毎の信号を信号処理ユニット 22 に受け渡し、信号処理ユニット 22 は光電変換ユニット 11 で発生した信号電荷に基づく電気信号を処理することが可能となる。またブロック 90 は縦列に配されてもよいし、縦列と並列を併用してもよい。

30

#### 【0056】

以上が、半導体デバイス 1 の構成の一例である。これらの構成は、適宜変更することができる。

#### 【0057】

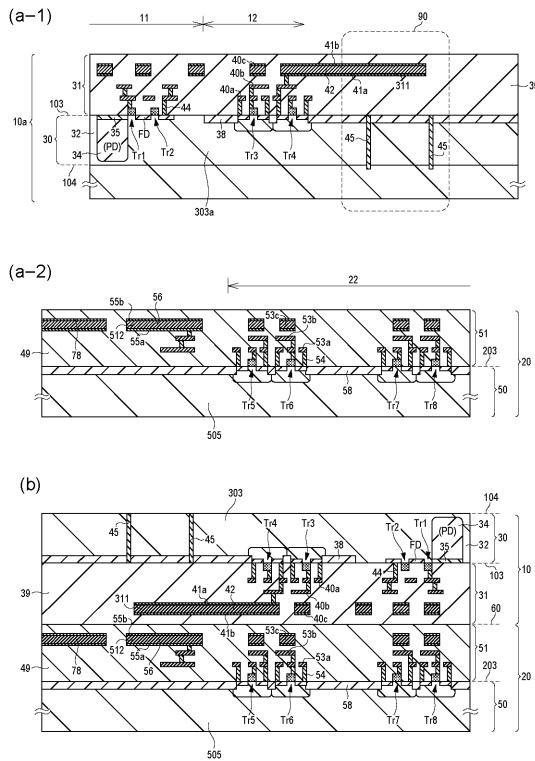

次に、図 3、図 4 を参照しながら本実施形態の半導体装置の製造方法を説明する。図 3、図 4 は、図 2 と同様の部分（図 1 の点 P と点 Q を含む面）を示す断面図である。

#### 【0058】

図 3 (a - 1) を参照して説明する。第 1 半導体基板 303a を準備する。第 1 半導体基板 303a は例えばシリコン基板である。第 1 半導体基板 303a の第 1 面（表面）103 に STI などの素子分離 38 を形成する。次いで第 1 半導体基板 303a にフォトダイオード PD およびトランジスタ Tr1、Tr2、Tr3、Tr4 を形成する。このようにして、第 1 素子部 30 を形成する。

40

#### 【0059】

次いで、第 1 素子部 30 の上に層間絶縁層を形成し、層間絶縁層にコンタクトプラグ 44 を形成する。コンタクトプラグ 44 に接続するように、シングルダマシン法を用いて配線パターン 40a を形成する。さらに層間絶縁層を形成した後、デュアルダマシン法を用いて配線パターン 40b およびビアプラグ、配線パターン 40c およびビアプラグを形成する。その後、配線パターン 40c の上に絶縁体膜 39 の表層となる絶縁体層を形成し、

50

これを平坦化する。このようにして、第1配線部31を形成する。第1配線部31には第1配線311が形成されている。

【0060】

以上の様にして、第1部分10となる第1部品10aを作成する。

【0061】

図3(a-2)を参照して説明する。第2半導体基板505aを準備する。第2半導体基板505aは例えればシリコン基板である。第2半導体基板505aの第1面(表面)203にSTIなどの素子分離38を形成する。次いで第2半導体基板505aにTr5、Tr6、Tr7、Tr8を形成する。このようにして、第2素子部50を形成する。

【0062】

次いで、第2素子部50の上に層間絶縁層を形成し、層間絶縁層にコンタクトプラグ54aを形成する。コンタクトプラグ54aに接続するように、シングルダマシン法を用いて配線パターン53aを形成する。さらに層間絶縁層を形成した後、デュアルダマシン法を用いて配線パターン53bおよびビアプラグ54b、配線パターン53cおよびビアップラグ54cを形成する。その後、絶縁体膜49の表層となる絶縁体層を形成し、これを平坦化する。このようにして、第2配線部51を形成する。第2配線部51には第2配線512が形成されている。

【0063】

以上の様にして、第2部分20となる第2部品20aを作成する。

【0064】

図3(b)を参照して説明する。上述のようにして第1部品10aと第2部品20aを用意し、第1部品10aと第2部品20aとを、第1部品10aと第2部品20aとを、第1素子部30と第2素子部50との間に第1配線部31および第2配線部51が位置するように接合する。この接合は、平坦化された絶縁体膜39の表層および絶縁体膜49の表層とのプラズマ接合の他、第1配線部31と第2配線部51の各々の表面に露出した金属層同士の金属接合、或いは接着剤層を介した接着で実現できる。この時、第1配線311の配線パターン40cと第2配線512の配線パターン53cとが重なり合うように接合することが好ましい。第1部品10aと第2部品20aの作製時点で、第1配線311と第2配線512の位置関係を設定しておく。第1配線311の配線パターン40cと第2配線512の配線パターン53cの一方の全部が、他方に重なっていてもよいし、一方の一部が他方に重なっていてもよい。第1配線311の配線パターン40cと第2配線512の配線パターン53cとの間には、平坦化された絶縁体膜39の表層を成す絶縁体層と平坦化された絶縁体膜49の表層を成す絶縁体層とが位置することになる。なお、第1配線部31と第2配線部51の絶縁体膜の少なくとも一方の表層をなす絶縁体層を省略してもよく、配線部の表面に配線パターンが露出していてもよい。

【0065】

次いで、第1半導体基板303aを、第1素子部30の第1配線部31側とは反対側(裏面側)から、位置104まで薄化することにより、第1半導体層303を得る。この薄化は、CMPなどの研磨やグラインドなどの研削、エッティングなどの周知の方法で行われる。この薄化は、当初の第1半導体基板303aが700μm以上の厚みを有するのに対して、第1半導体基板303aの薄化後における第1半導体層303の厚みが500μm以下、さらには10μm以下となるように行うことが出来る。この時点で、第1半導体層303の厚みは第2半導体層505の厚みよりも小さくされうる。フリップチップ接続を用いる場合などには第2半導体基板505aは薄化することが好ましいが、そのまま第2半導体層505として用いることも可能である。

【0066】

このようにして接合工程が行われ、積層体が得られる。次に、積層体に導電部材を形成することにより、第1配線311と第2配線512とを接続する接続工程が行われる。接続工程は複数の段階を経て行われる。

【0067】

10

20

30

40

50

図4(c)を参照して説明する。第1段階として、絶縁領域45の内側に、第1半導体層303側から接続孔を形成する。この接続孔は、第1半導体層303を貫通し、配線パターン40cに達する直前の深さまで開口する。この接続孔の形成は、絶縁体膜39の絶縁体層の内、配線パターン40cと第1半導体層303との間に位置する絶縁体層のエッチングによって行われる。上述のように第1半導体基板303aを薄化することで、接続孔のアスペクト比を小さくすることが可能となり、微細化が可能である。次に、接続孔の側壁及び底部を含む領域に、例えば酸化シリコンなどの絶縁膜を成膜する。この絶縁膜をエッチバックすることにより、接続孔の側壁のみに絶縁領域59を残す。

#### 【0068】

さらに接続孔と配線パターン40cの間に位置する残りの絶縁体層をエッチングして接続孔を深くする。接続孔が配線パターン40cに達し、さらに配線パターン40cの一部を、エッチングなどを用いて除去する。詳細には、副導電層41a、主導電層42、副導電層41bの順でエッチングする。配線パターン40cのエッチング条件は、絶縁体層のエッチング条件と異なるものを採用することができる。ここで、配線パターン40cの除去される一部とは、第1配線311を構成する配線パターン40cの、第2配線512の配線パターン53cに重なる部分の一部または全部でありうる。本例では、配線パターン40cの配線パターン53cに重なる部分の一部を除去しており、除去後には、配線パターン53cに重なる部分の残りの一部が残留している。

#### 【0069】

さらに絶縁体膜39をエッチングすることにより、接続孔が第1配線部31と第2配線部51の接合面60を通過して、第1部品10aを貫通する。さらに、第2配線部51に形成された配線パターン53cに達するまで絶縁体膜49をエッチングする。この接続孔の形成は、絶縁体膜39の絶縁体層および絶縁体膜49の絶縁体層の内、配線パターン40cと配線パターン53cとの間に位置する絶縁体層のエッチングによって行われる。これらの絶縁体層には絶縁体膜39や絶縁体膜49の表層の絶縁体層が含まれうる。このようにして、第2配線512の配線パターン53cに達する貫通孔67を形成する。これにより、貫通孔67には配線パターン40cの側面が露出し、配線パターン53cの上面が露出する。そして、配線パターン40cの複数の部分の間に貫通孔67が位置する。換言すれば、配線パターン40cの複数の部分は、貫通孔67を介して向かい合う。配線パターン53cの露出される部分とは、接合工程の後の時点で、第2配線512を構成する配線パターン53cの、第1配線311の配線パターン40cに重なっていた部分の一部または全部でありうる。貫通孔67の形成位置を配線パターン40cの輪郭よりも内側に設定することができる。これにより、第1部品10aと第2部品20aとの接合工程あるいは貫通孔67の形成時にアライメントズレが生じていたとしても、配線パターン40cと配線パターン53cの一方に貫通孔67が達しないリスクが軽減される。次いで、薬液によるウェットエッチングにより、露出した配線パターン40c上の堆積物を除去する。ウェットエッチングとしたが、デポ物を除去できる手段であれば、ドライエッチングも可能である。

#### 【0070】

図4(d)を参照して説明する。第2段階として、貫通孔67に、例えば、銅などの導電材料を埋め込むことにより、導電部材68が形成される。本例では、配線パターン40cの側面と、配線パターン53cの上面とに導電部材68が接触する。なお、貫通孔67の側面および底面に沿って導電材料を薄く堆積して、導電部材68を導電膜としても第1配線311と第2配線512の導通を取ることも可能である。導電部材68と第1半導体層303との間には絶縁領域59が形成されている。このため、導電部材68と第1半導体層303とが電気的に接続されることがない。また、第1半導体層303に形成された絶縁領域45の内側に形成されるので、これによっても、導電部材68と第1素子部30の半導体素子が電気的に接続されることが防止される。なお、絶縁領域59及び絶縁領域45の一方を省略することもできる。絶縁領域45を形成しない場合には、導電部材68の配置密度を高めたり、ブロック90の占有面積を低減したりすることが可能となる。本

10

20

30

40

50

例では、貫通孔 6 7 に埋め込まれる導電材料として銅を挙げたが、アルミニウムやタンゲステンであってもよい。

【 0 0 7 1 】

第 1 素子部 3 0 の第 1 配線部 3 1 とは反対側に光学部材 4 1 を形成する。まず、第 1 半導体層 3 0 3 の裏面 1 0 4 の上に反射防止層 6 1 、絶縁体層 6 2 を形成する。その後、遮光層 6 3 を形成する。反射防止層 6 1 はシリコンと酸化シリコンとの間の屈折率を有する材料、例えば窒化シリコンや酸化ハフニウム等で形成することが好ましい。反射防止層 6 1 は複数の膜を積層する構成でも良い。絶縁体層 6 2 は例えば酸化シリコン層である。遮光層 6 3 はアルミニウムやタンゲステンを堆積し、パターニングすることで形成できる。遮光層 6 3 は各画素間、オブティカルブラック画素上、および光の入射による影響を受ける素子の上に配するのが好ましい。遮光層 6 3 を堆積する前に反射防止層 6 1 、絶縁体層 6 2 をパターニングしてから、遮光層 6 3 を堆積することで遮光層 6 3 と第 1 半導体層 3 0 3 とを接続させることも可能である。

【 0 0 7 2 】

さらに、遮光層 6 3 の上に平坦化層 7 1 を形成する。平坦化層 7 1 は無機絶縁体膜や有機絶縁体膜であり、複数の層で構成することも可能である。また平坦化層 7 1 は適宜 C M P などで平坦化することも可能である。平坦化層 7 1 の上に樹脂からなるカラーフィルタアレイ 7 3 、マイクロレンズアレイ 7 4 をこの順で適宜形成する。この時、樹脂材料はスピンドルコートなどの塗布法を用いて成膜されるが、先に貫通孔 6 7 が導電材料で埋めかれているため、樹脂膜の成膜時にストリエーション等の膜ムラが生じることを抑制することができる。

【 0 0 7 3 】

その後電極パッド 7 8 に開口 7 7 を形成する。これにより図 2 に示す構成が得られる。本実施形態では開口 7 7 の形成工程はカラーフィルタ 7 3 、オンチップレンズ 7 4 の形成の後とした例を示したが、カラーフィルタ 7 3 、オンチップレンズ 7 4 の形成前に行うこととも可能である。カラーフィルタ 7 3 、オンチップレンズ 7 4 を形成した後では、樹脂であるカラーフィルタ 7 3 、オンチップレンズ 7 4 の保護のため、高温 ( 4 0 0 度 ) の熱処理はできない。開口 7 7 の処理により半導体デバイス 1 にダメージが入ると、ダメージ回復のための熱処理が必要になる場合があり、工程順は適宜変更可能である。

【 0 0 7 4 】

その後、半導体デバイス 1 をパッケージにダイボンドを用いて接着する。そして、開口 7 7 に、電極パッド 7 8 に接続するボンディングワイヤ 7 9 を形成する。パッケージを透明板で封止する。パッケージの外部端子である L G A ( L a n d G r i d A r r a y ) をリフローはんだ付けにより、回路基板に固着する。以上の様にして、半導体装置 3 を製造することができる。

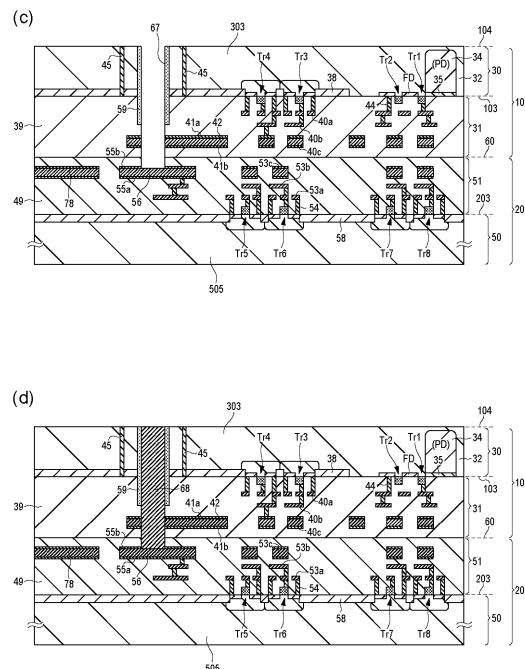

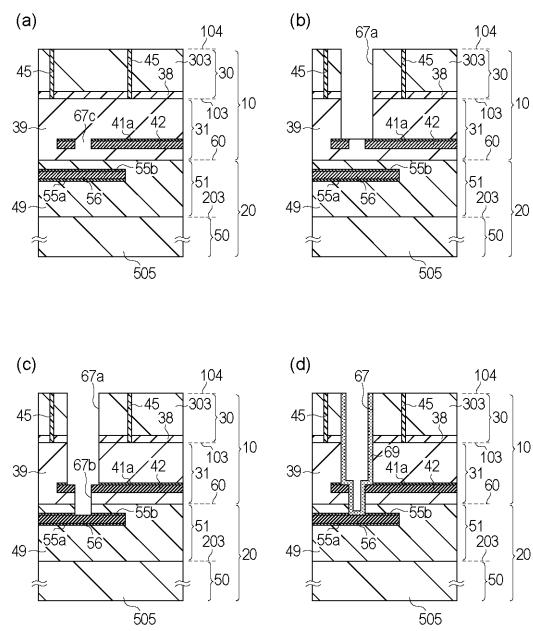

【 0 0 7 5 】

図 5 ( a ) ~ 図 5 ( d ) を参照して半導体装置の製造方法の他の例を説明する。

【 0 0 7 6 】

図 5 ( a ) は第 1 部品 1 0 a と第 2 部品 2 0 a とを接合した後の状態である。第 1 部品 1 0 a の配線パターン 4 0 c は、貫通孔 6 7 が設けられる位置に開口 6 7 c を有する。この開口 6 7 c は接合工程の前に、第 1 部品 1 0 a に予め設けられている。開口 6 7 c は配線パターン 4 0 c のパターニング時に形成できる。

【 0 0 7 7 】

図 5 ( b ) を参照して説明する。第 1 半導体層 3 0 3 の裏面 1 0 4 側からパターニングを行い、大口径の接続孔 6 7 a を形成する。接続孔 6 7 a は配線パターン 4 0 c に達するように形成される。接続孔 6 7 a が配線パターン 4 0 c の上面である副導電層 4 1 a を露出させている。接続孔 6 7 a の形成に当たっては、副導電層 4 1 a が絶縁体膜 3 9 のエッティングストップとなるようなエッティング条件を採用することにより、配線パターン 4 0 c の損傷を抑制できる。

【 0 0 7 8 】

10

20

30

40

50

図5(c)を参照して説明する。続いて、接続孔67aよりも径(幅)の小さい小口径の接続孔67bを形成する。接続孔67bは配線パターン53cに達するように形成される。接続孔67bが配線パターン53cの上面である副導電層55bを露出させている。また、本例では接続孔67bに配線パターン40c(主導電層42)の側面が露出している。しかし、接続孔67aに配線パターン40cの上面が露出していれば、接続孔67bに配線パターン40c(主導電層42)の側面が露出する必要はない。

#### 【0079】

接続孔67bの形成に当たっては、副導電層55bが絶縁体膜49のエッチングストップとなるようなエッチング条件を採用することにより、配線パターン53cの損傷を抑制できる。

10

#### 【0080】

接続孔67bの一部は予め配線パターン40cに形成された開口67cに形成されるため、接続孔67bの形成に伴って配線パターン40cの損傷を最小限に抑えるか、無くすことが可能となる。本例では、配線パターン40cの主導電層42はアルミニウム層であるが、主導電層42が銅層である場合には、予め開口67cを設けておくことは特に効果的である。銅はドライエッチングが難しいため、予め開口67cを設けておくことで、接続孔67bの開口を銅層のエッチングを伴わずに行うことが可能となる。なお、本例の様に、大口径の接続孔67aと小口径の接続孔67bを形成する形態においては、予め開口67cを設けておかずに、アルミニウム層などの主導電層42のエッチングを行うことにより接続孔67bを形成してもよい。

20

#### 【0081】

また、小口径の接続孔67bの形成においては、配線パターン40cと絶縁体膜39との選択比の大きいエッチング方法を採用することで、配線パターン40cをエッチングマスクとして、セルファアラインで、接続孔67aより小さな径の接続孔67bを形成することができる。つまり、同じマスクパターンを用いることが出来る。なお、接続孔67bの幅は開口67cの幅より大きくてもよいし、開口67cの幅より小さくてもよい。接続孔67bの幅が開口67の幅より大きい場合には、接続孔67bの形成には配線パターン40cの除去が伴い、配線パターン40cの側面が露出しうる。接続孔67bの幅が開口67cの幅より小さい場合には、接続孔67bの形成には配線パターン40cの除去が生じず、配線パターン40cの側面が露出しないことが考えられる。

30

#### 【0082】

図5(d)を参照して説明する。次いで、接続孔67a、67bの底部にあたる、配線パターン40cの副導電層41a及び、配線パターン53cの副導電層55bをエッチングにより除去する。これにより、貫通孔67に、第1配線311の主導電層42と第2配線512の主導電層56が露出する。なお、副導電層41aおよび/または配線パターン53cの副導電層55bの露出部分の除去は必須ではなく副導電層55bが露出したままにしてもよい。

#### 【0083】

その後は、導電材料を貫通孔67に埋め込む。導電材料に銅を用いる場合には、アルミニウム層である主導電層42、56の露出面から銅が拡散する場合があり、この銅の拡散が第1配線311と第2配線512の接続の信頼性を低下させる可能性がある。特にアルミニウム層の主導電層42、56の側面や上面が露出面となると、アルミニウム層の側面から銅が拡散する可能性がある。そこで、導電材料(銅)の埋め込みに先立って貫通孔67の内面に沿って拡散防止膜69を形成することが好ましい。この拡散防止膜69の貫通孔67からはみ出した部分は、導電材料を埋め込んだ後のCMPによる平坦化時、導電材料と合せて除去が可能である。拡散防止膜69の材料としては、チタン、窒化チタン、炭化チタン、タンタル、窒化タンタル、炭化タンタルなどの金属、金属化合物が利用可能である。拡散防止膜69は、チタン層、チタン化合物層、タンタル層およびタンタル化合物層の単層、または、これらから選ばれた2つ以上の層を含む複層膜であってもよい。これにより、導電部材68は、導電材料(銅)からなる埋め込み層と、配線パターンへの埋め

40

50

込み材料の拡散に対する拡散防止層と、を有する構造となる。

【0084】

図6を参照しながら貫通孔67と第1配線311と第2配線512の位置関係について説明する。図6は図2の貫通孔67形成時の状態を模式的に示す平面図である。

【0085】

図6(a-1)、(a-2)、(a-3)を参照して説明する。貫通孔67の一部が第2配線に接しているところを上面から示した模式図である。ここで貫通孔67の幅をaとする。

【0086】

図6(a-2)は、フォトマスクの設計通りに貫通孔67が形成された場合を示している。図6(a-1)は、図6(a-2)の状態に対して、貫通孔67が左方向に距離bだけシフトした状態である。図6(a-3)は、図6(a-2)の状態に対して、貫通孔67が右方向に距離bだけシフトした状態である。右方向を正として左方向へのシフト量を負で示している。図6(a-1)と図6(a-3)の状態では、貫通孔67に導電材料を埋め込んでも、導電部材68は第2配線512と第1配線311の一方のみに接触するため、配線間接続が行えない。

【0087】

図6(b-2)は、図6(a-2)で説明したフォトマスクとは別のフォトマスクの設計通りに貫通孔67が形成された場合を示している。図6(b-1)は、図6(b-2)の状態に対して、貫通孔67が左方向に距離bだけシフトした状態である。図6(b-3)は、図6(b-2)の状態に対して、貫通孔67が右方向に距離bだけシフトした状態である。右方向を正として左方向へのシフト量を負で示している。図6(b-1)と図6(b-2)と図6(b-3)のいずれの状態でも、貫通孔67に導電材料を埋め込むことで、導電部材68は第2配線512と第1配線311の両方に接触するため、配線間接続を行うことが出来る。

【0088】

このためには、仮に距離bのアライメントズレが生じたとしても、接合工程において第1配線311と第2配線512とが重なる領域(以下、接続領域と呼ぶ)から貫通孔67がはみ出さないように、貫通孔67を形成するためのフォトマスクを設計すればよい。つまり、貫通孔67の理想的な形成位置を意味するフォトマスク上のマスクパターンにおいて、接続領域の端部から貫通孔67の形成位置を距離cだけ離しておく。つまり、接続領域の幅を貫通孔の幅aよりも大きくしておけばよい。距離cは想定されるアライメントズレの距離b以上とすると良い。距離bは貫通孔67の形成のためのフォトレジストのパターンングに用いる露光装置の性能に依存するが、例えば1μm未満でありうる。したがって距離cを1μm以上とすると良い。貫通孔67の径との関連では、距離bはa/10未満である。したがって、距離cをa/10以上とすると良い。当然、接続領域の輪郭は、少なくとも第1配線311の輪郭で決定されるため、第1配線311の端部から距離c以上はなして、貫通孔67を形成するように、フォトマスクを設計すると良い。なお、理想的な形成位置を意味するフォトマスク上のマスクパターンを用いて貫通孔を形成する限りにおいては、貫通孔がマスクパターン通りの位置に形成されなくてもよい。例えば、マスクパターン上で貫通孔が第1配線311に囲まれるように設計されていることは、このマスクを用いる限り、貫通孔が第1配線311に囲まれるように形成することと実質的に同じである。

【0089】

本実施形態で説明した接合工程と接続工程とを備える半導体装置の製造方法をまとめます。

【0090】

接続工程では、第1部品10aと第2部品20aとを接合する。第1部品10aは、第1半導体層303を含む第1素子部30と、第1素子部30に電気的に接続された第1配線311を含む第1配線部31と、を有する。第2部品20aは、第2半導体層505を含

10

20

30

40

50

む第2素子部50と、第2素子部50に電気的に接続された第2配線512を含む第2配線部51と、を有する。

【0091】

接合工程は、第1素子部30と第2素子部50との間に第1配線部31および第2配線部51が位置するように行われる。接合工程では、配線パターン40c配線パターン53cが重なり合うように行うことが出来る。

【0092】

接続工程では、第1配線311を構成する配線パターン40cおよび第2配線512を構成する配線パターン53cの両方に接触する導電部材68を形成して第1配線311と第2配線512とを電気的に接続する。

10

【0093】

接続工程は、第1部品10aを貫通し、配線パターン53cを露出する貫通孔67を形成する第1段階を有する。また、この貫通孔67は、接合工程の時点で配線パターン53cの配線パターン40cに重なる部分を、露出しうる。この貫通孔67は、貫通孔67が配線パターン40cを露出するように形成されうる。この貫通孔67は、配線パターン40cの複数の部分の間に位置するように形成されうる。また、この貫通孔67は、接合工程の時点で配線パターン40cの配線パターン53に重なる部分を、除去することで形成されうる。また、接続工程は、貫通孔67に露出した配線パターン40cおよび配線パターン53cの両方に接触する導電部材68を貫通孔67内に形成する第2段階と、を有する。

20

【0094】

このようにすることで、導電部材68による第1配線311と第2配線512の電気的接続の性能および信頼性が高い半導体装置を提供することができる。

【符号の説明】

【0095】

303 第1半導体層

30 第1素子部

40c 配線パターン

31 第1配線部

311 第1配線

505 第2半導体層

50 第2素子部

53c 配線パターン

51 第2配線部

512 第2配線

67 貫通孔

68 導電部材

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(51)Int.Cl. F I

H 04N 5/369 (2011.01)

(56)参考文献 特表2009-505401 (JP, A)

特開2011-096851 (JP, A)

国際公開第2014/002852 (WO, A1)

(58)調査した分野(Int.Cl., DB名)

H 01L 21/3205

H 01L 21/768

H 01L 23/522

H 01L 27/14

H 01L 27/146

H 04N 5/369