(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2012-0114372

(43) 공개일자 2012년10월16일

(51) 국제특허분류(Int. Cl.)

*H01L 29/78* (2006.01) *H01L 21/336* (2006.01)

(21) 출원번호 10-2012-7022265

(22) 출원일자(국제) 2011년02월10일

심사청구일자 空

(85) 번역문제출일자 2012년08월24일

(86) 국제출원번호 PCT/US2011/024310

(87) 국제공개번호 WO 2011/106165

국제공개일자 2011년09월01일

(30) 우선권주장

12/713,264 2010년02월26일 미국(US)

(71) 출원인

이스트맨 코닥 캄파니

미합중국 뉴욕 로체스터 스테이트 스트리트 343

(72) 발명자

터트, 리, 윌리암

미국 14650-2201 뉴욕주 로체스터 스테이트 스트리트 343

넬슨, 셸비, 포레스터

미국 14650-2201 뉴욕주 로체스터 스테이트 스트리트 343

(74) 대리인

장수길, 양영준

전체 청구항 수 : 총 8 항

(54) 발명의 명칭 **요각 프로파일을 포함하는 수직 트랜지스터**

### (57) 요 약

트랜지스터는 기판, 전기적 도전 재료층, 및 전기적 절연 재료층을 포함한다. 기판, 전기적 도전 재료층 및 전기적 절연 재료층 중 하나 이상의 적어도 일부분은 요각 프로파일을 정의한다.

### 대 표 도

## 특허청구의 범위

### 청구항 1

트랜지스터로서,

기판;

전기적 도전 재료층; 및

전기적 절연 재료층

을 포함하고, 상기 기판, 상기 전기적 도전 재료층 및 상기 전기적 절연 재료층 중 하나 이상의 적어도 일부분은 요각(reentrant) 프로파일을 정의하는 트랜지스터.

### 청구항 2

제1항에 있어서,

상기 전기적 절연 재료층은 제1 전기적 절연 재료층이고, 상기 요각 프로파일에 정합하는 제2 전기적 절연 재료층을 더 포함하는 트랜지스터.

### 청구항 3

제2항에 있어서,

상기 제2 전기적 절연 재료층과 접촉하여 상기 요각 프로파일에 정합하는 반도체 재료층을 더 포함하는 트랜지스터.

### 청구항 4

제1항에 있어서,

상기 요각 프로파일에 정합하는 반도체 재료층을 더 포함하는 트랜지스터.

### 청구항 5

제4항에 있어서,

상기 반도체 재료층과 접촉하는 전기적 도전 재료층을 더 포함하는 트랜지스터.

### 청구항 6

제1항에 있어서,

상기 기판은 플렉시블한 트랜지스터.

### 청구항 7

제1항에 있어서,

상기 전기적 절연 재료층 및 상기 전기적 도전 재료층은 상기 요각 프로파일을 정의하는 트랜지스터.

### 청구항 8

반도체 디바이스를 활성화시키는 방법으로서,

기판;

제1 전기적 도전 재료층;

전기적 절연 재료층 - 상기 전기적 절연 재료층은 상기 전기적 도전 재료층에 대한 요각 프로파일을 포함함 - ;

상기 전기적 절연 재료층 위에 위치된 제2 전기적 도전 재료층; 및

상기 기판 위에 위치된 제3 전기적 도전 재료층

을 포함하는 트랜지스터를 제공하는 단계;

상기 제2 전기적 도전 재료층과 상기 제3 전기적 도전 재료층 사이에 전압을 인가하는 단계; 및

상기 제1 전기적 도전 재료층에 전압을 인가하여, 상기 제2 전기적 도전 재료층 및 상기 제3 전기적 도전 재료층을 전기적으로 접속시키는 단계

를 포함하는 방법.

## 명세서

### 기술분야

[0001]

본 발명은 일반적으로 반도체 디바이스들에 관한 것이고, 특히 트랜지스터 디바이스들에 관한 것이다.

### 배경기술

[0002]

반도체 공정 기술에서, 웨이퍼 표면에 대해 수평인 평면 기판 표면들은 선택적 에칭 공정들과 함께 포토리소그래프 방법들에 의해 패터닝된다. 집적 회로들의 공정 동안, 뚜렷한 표면형태를 가지는 부조(relief)들이 웨이퍼 또는 기판 표면 상에 형성된다. 통상적으로, 이러한 타입의 부조는 기판 표면에 대해 수직이거나 기울어진 표면들을 포함한다. 집적 회로들의 사이즈들이 계속 감소함에 따라, 패턴 정렬을 여전히 유지하면서 자신의 수직 연장에 대해 이들 디바이스들을 기능적으로 차별화하기 위해 수직 또는 기울어진 디바이스 표면들을 패터닝 하는 것이 더더욱 필요해진다. 이러한 타입들의 반도체 디바이스들의 예들은 깊은 트랜치 커패시터들, 스태킹된(stacked) 커패시터들, 및 수직 트랜지스터들을 포함한다.

[0003]

현재, 통상적인 포토리소그래프 기법들을 사용하여 기판 표면에 대해 수직인 벽들 상에 직접 패턴들을 두는 것이 가능하지 않다. 일반적으로, 이러한 속성의 수직 벽 패터닝은, 트랜치 내에 부분적으로 채울 시에 아래에 위치된 벽의 일부분들에 대한 마스크로서 작용하는 적절한 충진 재료를 사용하여 달성되는 동시에 충진 재료 위의 벽들의 공정을 허용한다. 예를 들어, 산화물이 충진 재료 아래의 수직 벽에 대해 독점적으로 증착될 경우, 산화물을 먼저 부조의 전체 표면 위에 증착되거나 생성된다. 부조 또는 트렌치는 초기에 적절한 충진 재료로 완전히 채워진다. 이후, 충진 재료는 원하는 산화물만을 커버하는 깊이로 다시 우뚝하게 들어간다(recess). 산화물의 커버되지 않은 섹션들이 제거된 후, 나머지 충진 재료가 제거된다.

[0004]

대안적으로, 산화물이 수직 벽의 상위 영역들에만 증착 또는 생성될 경우, 에칭 중단층, 예를 들어, 질화물층은 먼저 전체 부조 패턴의 전체 표면 위에 제공된다. 지향성 에칭에 영향을 받기 쉬운 다른 재료, 예를 들어, 다결정질 실리콘 부조를 채우기 위해 사용되고, 최종 수직 산화물의 원하는 커버리지 깊이만큼 다시 에칭된다. 에칭 중단 층이 벽들의 채워지지 않은 섹션들로부터 제거된 이후, 산화물은 커버되지 않은 영역들에서 열 기법을 사용하여 증착되거나 생성된다. 다음으로, 산화물은 이방성으로 에칭되며, 이는 증착된 산화물을 수평으로 부터 제거한다. 이에 후속하여 충진 재료가 제거되고, 그후 에칭 중단층이 제거된다.

[0005]

기판 부조의 수직 또는 기울어진 표면들 상에 박막들을 증착하기 위해 사용될 수 있는 증착 공정들이 존재한다. 그러나, 증착된 층의 두께를 제어하는 것이 어렵다. 통상적으로, 코팅의 두께는 부조의 깊이가 증가함에 따라, 예를 들어, 수직 또는 기울어진 벽의 길이가 증가함에 따라 감소한다. 그러한 것으로서, 증착 공정들의 이러한 타입들을 사용하여 증착된 층들은 부조의 길이에 대해 두께에 있어 상당한 차이를 가진다. 이러한 타입들의 증착 공정들은 테트라에틸 오소실리케이트(TEOS)를 사용하는 플라즈마-강화 화학 기상 증착(PECVD) 및 실리콘 산화물의 확산-제한 증착을 포함한다.

[0006]

따라서, 패터닝된 수직 또는 기울어진 디바이스 표면들을 포함하는 반도체 디바이스 아키텍처들을 제공하는 것이 계속 필요하다. 또한, 높은 분해능 정렬 허용오차들을 요구하지 않고 반도체 디바이스들의 작은 디바이스 특징들을 공정할 수 있는 제조 기법들을 제공하는 것이 계속 필요하다.

### 발명의 내용

[0007]

본 발명의 일 양상에 따라, 트랜지스터는 기판, 전기적 도전 재료층, 및 전기적 절연 재료층을 포함한다.

기판, 전기적 도전 재료층, 및 전기적 절연 재료층 중 하나 이상의 적어도 일부분이 요각 프로파일을 정의한다.

[0008] 본 발명의 또 다른 양상에 따라, 전기적 절연 재료층은 제1 전기적 절연 재료층이고, 트랜지스터는 요각 프로파일에 정합하는 제2 전기적 절연 재료층을 포함한다. 본 발명의 또 다른 양상에서, 반도체 재료층은 제2 전기적 절연 재료층과 접촉하여 요각 프로파일에 부합하다.

[0009] 본 발명의 또 다른 양상에 따라, 전기적 절연 재료층 및 전기적 도전 재료층이 요각 프로파일을 정의한다.

[0010] 본 발명의 또 다른 양상에 따라, 반도체 디바이스를 활성화시키는 방법은 기판, 제1 전기적 도전 재료층, 전기적 절연 재료층 - 전기적 절연 재료층은 전기적 도전 재료층에 대한 요각 프로파일을 포함함 - ; 전기적 절연 재료층 위에 위치된 제2 전기적 도전 재료층; 및 기판 위에 위치된 제3 전기적 도전 재료층을 포함하는 트랜지스터를 제공하는 단계; 제2 전기적 도전 재료층 및 제3 전기적 도전 재료층 사이에 전압을 인가하는 단계; 및 제1 전기적 도전 재료층에 전압을 인가하여, 제2 전기적 도전 재료층 및 제3 전기적 도전 재료층을 전기적으로 접속시키는 단계를 포함한다.

### 도면의 간단한 설명

[0011] 하기에 제시된 본 발명의 바람직한 실시예들의 상세한 설명에서 첨부 도면들에 대한 참조가 이루어진다.

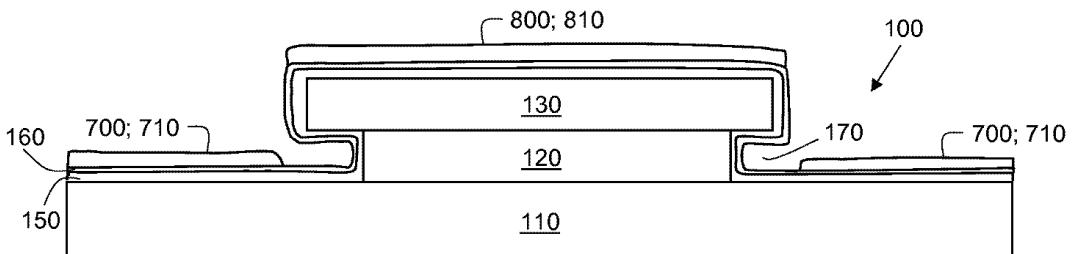

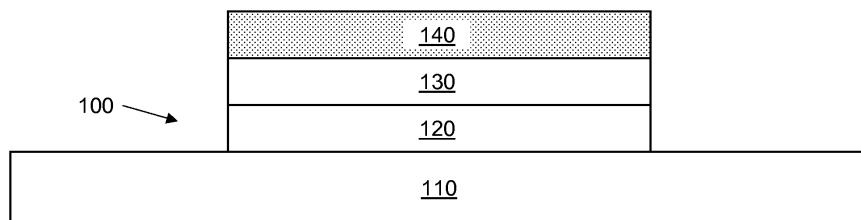

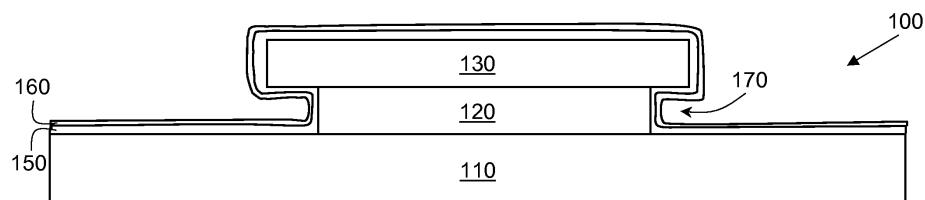

도 1은 수직 트랜지스터의 개략적인 횡단면도이다.

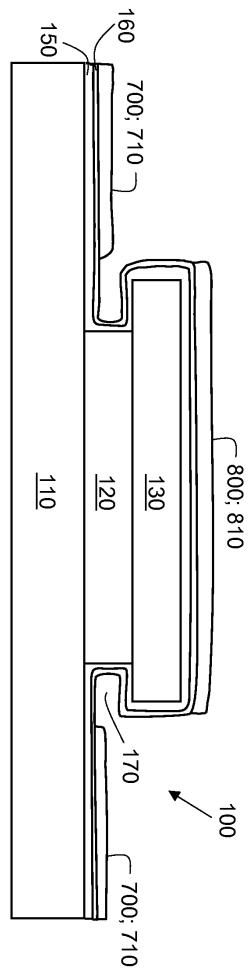

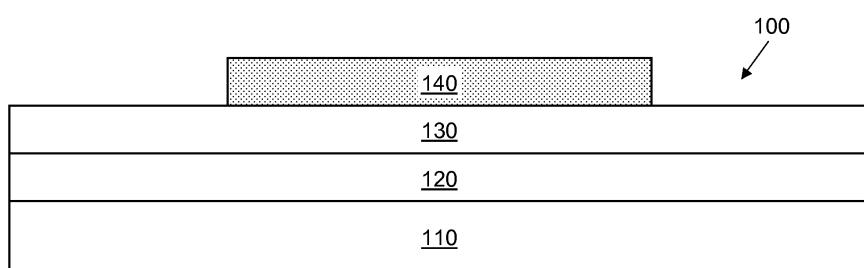

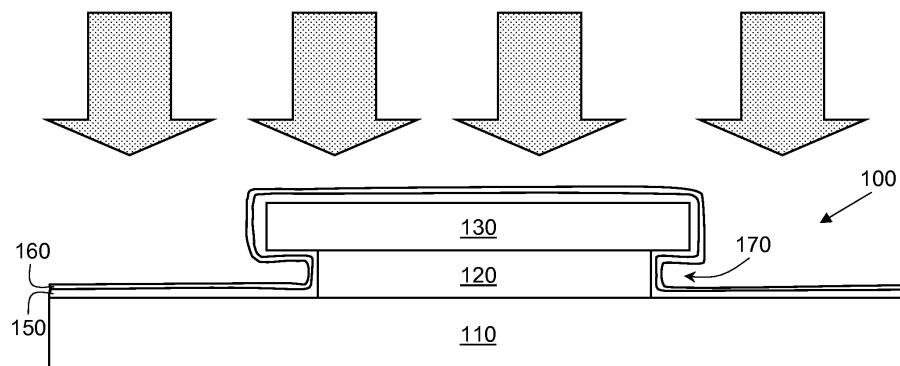

도 2 내지 8은 도 1에 도시된 수직 트랜지스터의 제조 방법의 예시적인 실시예와 연관된 공정 단계들의 개략적인 횡단면도이다.

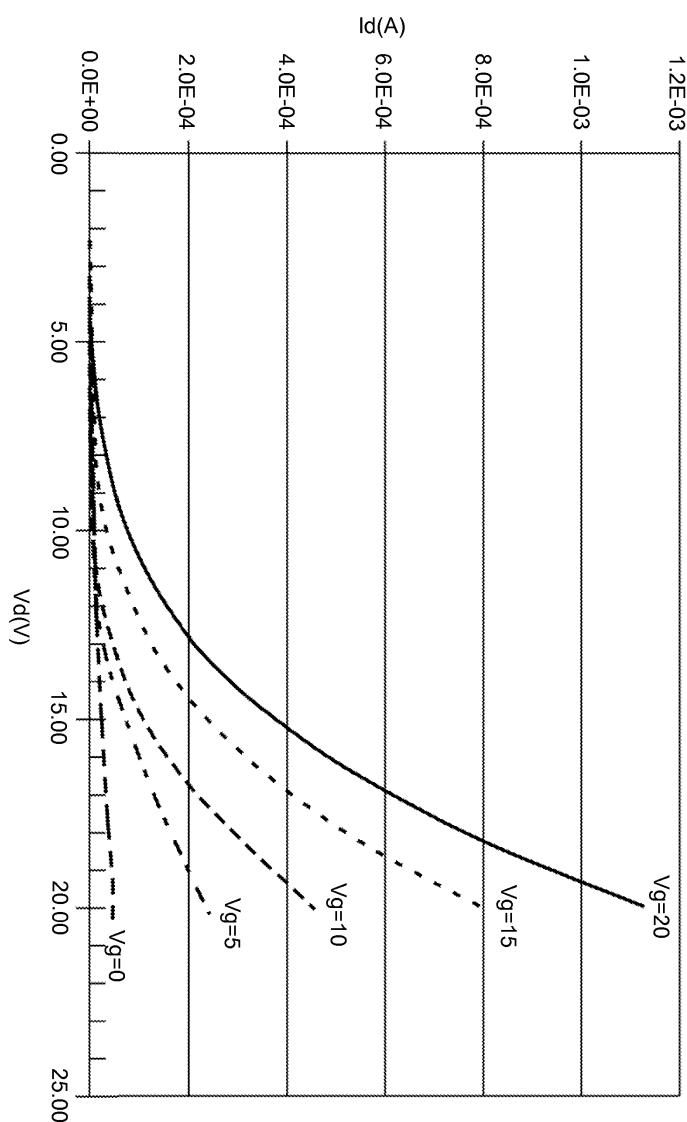

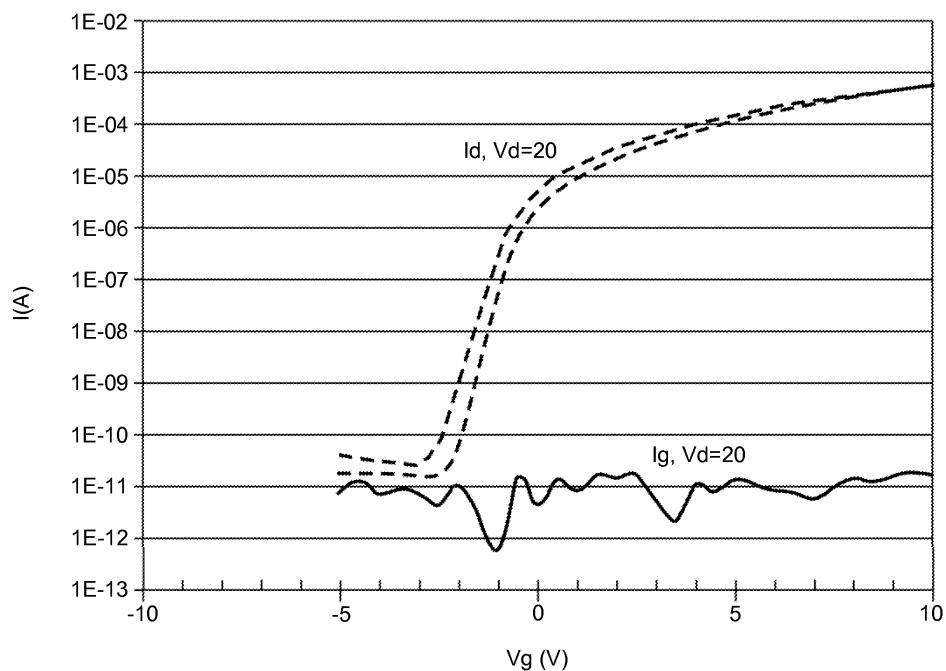

도 9는 도 1에 도시된 수직 트랜지스터에 대한 성능 전달 특성들을 도시하는 그래프이다.

도 10은 도 1에 도시된 수직 트랜지스터에 대한 성능  $I_d-V_d$  커브 특성들을 도시하는 그래프이다.

### 발명을 실시하기 위한 구체적인 내용

[0012] 본 기재는 특히 본 발명에 따른 장치의 일부분을 형성하거나 장치와 더 직접적으로 협력하는 엘리먼트들에 관련될 것이다. 구체적으로 도시되거나 기술되지 않은 엘리먼트들이 당업자에게 공지된 다양한 형태들을 취할 수 있다는 점이 이해되어야 한다.

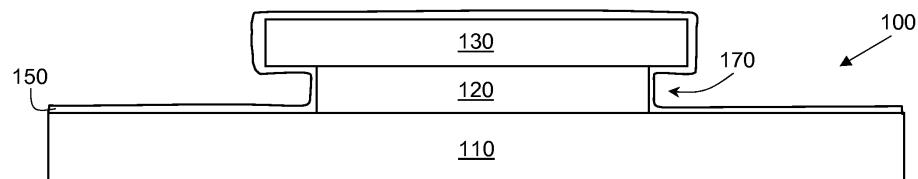

[0013] 도 1을 참조하면, 수직 트랜지스터(100)의 개략적 횡단면도가 도시된다. 트랜지스터(100)는 기판(110), (제1) 전기적 도전 재료층(120), 및 (제1) 전기적 절연 재료층(130)을 포함한다. 트랜지스터(100)는 또한 또 다른(제2) 전기적 절연 재료층(150), 반도체 재료층(160), 전극(들)(700) 및 전극(800)을 포함한다.

[0014] 도전층(120)은 기판(110) 및 절연층(130) 사이에 위치된다. 도전층(120)의 제1 표면은 기판(110)의 제1 표면에 접촉하는 반면, 도전층(120)의 제2 표면은 절연층(130)의 제1 표면에 접촉한다. 절연 재료층(130)은 종종 유전 재료층으로서 참조된다. 종종 지지대로서 참조되는 기판(110)은 딱딱하거나 플렉시블할 수 있다.

[0015] 절연층(130), 도전층(120), 기판(100) 또는 이들의 조합들은 트랜지스터(100) 내의 요각 프로파일(170)을 생성하기 위해 적어도 하나의 다른 층 또는 기판에 대해 적절하게 디멘셔닝되거나(또는 크기가 정해지거나), 위치지정되거나, 또는 디멘셔닝 및 위치지정된다. 따라서, 절연층(130), 도전층(120), 기판(100) 중 하나 이상의 적어도 일부분이 트랜지스터(100)의 요각 프로파일(170)을 정의한다고 할 수 있다. 요각 프로파일(170)은 지향성(또는 라인 오브 사이트) 증착(또는 코팅) 공정을 사용하여 증착되는(또는 코팅되는) 재료로부터 도전층(120)의 적어도 일부분을 차폐한다. 요각 프로파일(170)은 도전층(120)의 적어도 일부가 등각 증착(또는 코팅) 공정을 사용하여 증착된 재료에 접근 가능하게 한다. 예를 들어, 전기적 절연 재료층(130) 및 전기적 도전 재료층(120)이 요각 프로파일(170)을 정의할 수 있다.

[0016] 도 1에 도시된 바와 같이, 요각 프로파일(170)은 전기적 절연 재료층(130) 및 전기적 도전 재료층(120) 중 하나 또는 둘 모두의 일부분들에 의해 정의된다. 절연층(130)은, 절연층(130)이 도전층(120)에 대해 요각 프로파일(170)을 생성하도록 도전층(120)을 넘어 확장하도록 크기가 정해지고 위치지정된다. 다르게 언급하자면, 도전층(120)은, 도전층(120)이 절연층(130)에 대해 요각 프로파일(170)을 생성하도록 (도 1에 도시된 바와 같이 좌우 방향들 모두에서) 절연층(130)이 끝나기 이전에 끝나도록 크기가 정해지고 위치지정된다.

[0017] 절연 재료층(150)은 트랜지스터(100)의 요각 프로파일(170)에 정합하다. 절연 재료층(150)은 제1 및 제2 표면들을 포함하고, 제1 표면은 절연층(130), 도전층(120) 및 기판(110)의 표면들의 일부분들과 접촉한다. 반도체

재료층(160)은 트랜지스터(100)의 요각 프로파일(170)에 정합하다. 반도체층(160)은 제1 및 제2 표면들을 포함하고, 제1 표면은 절연층(150)의 제2 표면과 접촉한다. 반도체층(160)의 제2 표면의 별개의(또는 분리된, 상이한) 부분들은 전극(들)(700) 및 전극(800)과 접촉한다.

[0018] 전극(들)(700)은 또다른(제2) 전기적 도전 재료층(710)을 포함한다. 전극(800)은 또다른(제3) 전기적 도전 재료층(810)을 포함한다. 전극(들)(700) 및 전극(800)은 트랜지스터(100)의 상이한 위치들에 서로 이격되어 위치지정된다. 제2 및 제3 전기적 도전 재료층들(710, 810)은 동일한 재료층일 수 있다. 이것이 이루어지는 경우, 전극(들)(700) 및 전극(800)은 재료층(710) 또는 재료층(810)인, 동일한 전기적 도전 재료층의 별개의 부분들에 포함된다. 대안적으로, 제2 및 제3 전기적 도전 재료층들(710, 810)은 별개의(상이한) 재료층들일 수 있다.

[0019] 도전층(120)은 트랜지스터(100)의 게이트로서 동작한다. 트랜지스터(100)의 일부 실시예들에서, 전극(들)(700)은 트랜지스터(100)의 드레인으로서 기능하고, 전극(800)은 트랜지스터(100)의 소스로서 기능한다. 트랜지스터(100)의 다른 예시적인 실시예들에서, 전극(들)(700)은 소스로서 기능하고, 전극(800)은 드레인으로서 기능한다.

[0020] 반도체 디바이스는 후속하는 방식으로 작동된다. 트랜지스터(100)가 제공된 이후, 제2 전기적 도전 재료층(710) 및 제3 전기적 도전 재료층(810) 사이에 전압이 인가된다. 전압은 또한 제1 전기적 도전 재료층(120)에 인가되어 제2 전기적 도전 재료층(710) 및 제3 전기적 도전 재료층(810)을 전기적으로 접속시킨다.

[0021] 트랜지스터(100)의 요각 프로파일(170)은 트랜지스터의 반도체 재료 채널의 디멘전이 트랜지스터(100)의 게이트로서 기능하는 도전층(120)의 두께와 연관되도록 한다. 유리하게는, 본 발명의 이러한 아키텍처는 작은 채널들을 포함하는 트랜지스터들의 제조 동안 매우 정밀한 정렬 특징들 또는 높은 분해능에 대한 의존성을 감소시킨다.

[0022] 도 2 내지 8을 참조하면, 트랜지스터(100)의 제조 방법의 예시적인 실시예와 연관된 공정 단계들의 개략적인 단면도들이 도시된다.

[0023] 일반적으로 설명하면, 트랜지스터(100)는 후속하는 방식으로 제조된다. 기판(110)이 전기적 도전 재료층(120) 및 전기적 절연 재료층(130)을 차례로 포함하여 제공된다. 레지스트 재료층(140)은 전기적 절연 재료층(130) 위에 있다. 레지스트 재료층(140)은 전기적 절연 재료층(130)의 일부분을 노출하도록 패터닝된다. 전기적 절연 재료층(130)의 노출된 부분을 제거하여, 전기적 도전 재료층(120)의 일부분을 노출한다. 전기적 도전 재료층(120)의 노출된 부분이 제거된다. 도전 재료층(120)의 제거는 요각 프로파일(170)을 생성하기 위해 계속된다. 도 1에 도시된 바와 같이, 전기적 도전 재료층(120)의 일부가 제거되는 한편, 전기적 절연 재료층(130)의 일부는 남아 있음으로써 요각 프로파일(170)이 생성된다. 이러한 견지에서, 전기적 절연 재료층(130)에 대해 도전 재료층(120) 내에서 요각 프로파일(170)이 생성된다고 할 수 있다. 포토레지스트층(140)의 제거 이후, 만약 이러한 사항이 필요하다면, 기판(110) 및 나머지 노출된 재료층들(120, 130)은 제2 전기적 절연 재료층(150)으로 등각으로(conformally) 코팅된다. 제2 전기적 절연 재료층(150)은 반도체 재료층(160)으로 등각으로 코팅된다. 전기적 도전 재료층(710 또는 810) 또는 전기적 도전 재료층들(710, 810)은 반도체 재료층(160) 위에 지향성으로 증착된다.

[0024] 레지스트 재료층(140)은 전기적 절연 재료층(130) 위에 증착되고 동일한 공정 단계에서 패터닝될 수 있다. 전기적 절연 재료층(130)의 노출된 부분을 제거하여 전기적 도전 재료층(120)의 일부분을 노출시키기 위해 액체 에칠프로판트가 사용될 수 있다. 전기적 절연 재료층(130)의 노출된 부분을 제거하기 위해 사용되는 동일한 액체 에칠프로판트가 전기적 도전 재료층(120)의 노출된 부분을 제거하여 전기적 도전 재료층(120)의 요각 프로파일(170)을 생성하기 위해 사용될 수 있다.

[0025] 일부 예시적인 실시예들에서, 기판(110)은 하나 초과의 재료층을 포함할 수 있다. 추가적인 재료층(들)은 제조 공정 동안 기판(110)의 구조적 무결성을 개선하거나 유지하기 위해 일부 경우들에서 포함된다. 기판(110)이 하나 초과의 재료층, 예를 들어, 제1층 및 제2층을 포함하는 경우, 제조 방법은 기판(110)의 제2층을 제거하는 것을 포함할 수 있다.

[0026] 도 2를 참조하면, 재료 공정 이전의 트랜지스터(100) 재료층들의 개략적인 단면도가 도시된다. 수직 트랜지스터 디바이스를 형성하기 위한 제조 공정은 도전층(120)에 인접한 기판의 적어도 일부분(도 2에 도시된 바와 같은 기판(110)의 최상부)에 대해 전체적으로 또는 부분적으로 비도전성인 기판(110)으로 시작하며, 따라서, 트랜지스터(100)의 전기적 단락이 발생하지 않는다. 도전층(120)은 기판(110) 상에 도포되거나 증착되지 않는다. 도전층(200)은 트랜지스터(100)의 게이트로서 기능하고 (도 2에 도시된 바와 같이 수직 방향인) 그 두께에 의해

자신의 두께만큼 게이트의 길이를 정의한다. 유전 비도전층(130)이 도전층(120)에 도포되거나 코팅된다. 비도전층(130)은 패턴이 없는 균일한 층이다. 레지스트층(140)이 유전 비도전층(130)에 도포된다. 레지스트(400)가 패터닝된다.

[0027] 기판(110)은 공정 방법들 또는 층들 중 어느 것과도 두드러지게 상호작용하지 않는다. 종종 지지대라고도 참조되는 기판(110)은 제조, 테스트 및/또는 사용 동안 박막 트랜지스터(또한 TFT라고 참조됨)를 지지하기 위해 사용될 수 있다. 당업자는 상업적 실시예를 위해 선택된 지지대가 테스트 또는 스크린 실시예들을 위해 선택된 것과는 상이할 수 있다는 점을 이해할 것이다. 일부 실시예들에서, 기판(110)은 TFT에 대한 어떠한 필수적인 전기적 기능도 제공하지 않는다. 이러한 타입의 기판(110)은 여기서 "비-참여 지지대"로 명명된다. 유용한 기판 재료는 유기 또는 무기 재료들을 포함한다. 예를 들어, 기판(110)은 무기 유리, 세라믹 포일, 폴리머 재료, 충진 폴리머 재료, 코팅된 금속 포일, 아크릴, 에폭시, 폴리아미드, 폴리카보네이트, 폴리이미드, 폴리케톤, 폴리(옥시-1, 4-페닐린옥시-1, 4-페닐린카보닐-1, 4-페닐린)(때때로, 폴리(에테르 에테르 케톤) 또는 PEEK라고 참조됨), 폴리노보넨, 폴리페닐린옥사이드, 폴리(에틸렌 나프탈렌다이카복실레이트)(PEN), 폴리(에틸렌 테레프탈레이트)(PET), 폴리(에테르 술폰)(PES), 폴리(페닐렌 설파이드)(PPS), 및 섬유 강화 플라스틱(FRP)을 포함할 수 있다. 기판(110)의 두께는 통상적으로 약 100 $\mu\text{m}$ 에서 약 1cm까지 달라질 수 있다.

[0028] 플렉시블한 지지대 또는 기판(110)이 본 발명의 일부 예시적인 실시예들에서 사용된다. 플렉시블한 기판(110)을 사용하는 것은, 지속적일 수 있는 률 공정을 허용하여, 평평하거나 딱딱한 지지대에 비해 제조 절감 및 스케일링 절감을 제공한다. 선택된 플렉시블한 지지대는, 실제 손으로 적은 힘을 사용하여, 왜곡 또는 파손 없이, 바람직하게는 직경 약 50 cm 미만의, 더 바람직하게는 직경 25 cm 미만의, 가장 바람직하게는 직경 10 cm 미만의 원통 원주 주위를 둘러쌀 수 있다. 바람직한 플렉시블한 지지대는 그 자체가 말릴 수 있다. 플렉시블한 기판들의 추가적인 예들은, 포일들이 박막 트랜지스터를 전기적으로 절연시키기 위해 절연층으로 코팅되는 경우, 스테인리스 강철과 같은 얇은 금속 포일들을 포함한다. 유연성이 고려사항이 아닌 경우, 기판은 유리 및 실리콘을 포함하는 재료들로 이루어진 웨이퍼 또는 시트일 수 있다.

[0029] 일부 예시적인 실시예들에서, 기판(110)은, 예를 들어, 추가적인 구조적 지지대가 임시 목적, 예를 들어, 제조, 전송, 테스트 또는 저장을 위해 요구되는 경우, 임시 지지대 또는 지지층을 포함할 수 있다. 이러한 예시적인 실시예들에서, 기판(110)은 임시 지지대에 분리가능하게 부착되거나 기계적으로 붙을 수 있다. 예를 들어, 플렉시블 폴리머 지지대는 트랜지스터 제조 공정 동안 추가된 구조적 강성을 제공하기 위해 단단한 유리 지지대에 일시적으로 부착될 수 있다. 유리 지지대는 제조 공정의 완료 이후 플렉시블한 폴리머 지지대로부터 제거될 수 있다.

[0030] 일반적으로 도전체라고 참조되는 도전층(120)은 도전층(120)이 게이트로서 기능하도록 허용하는 임의의 적절한 도전 재료일 수 있다. 금속, 축퇴식으로(degenerately) 도핑된 반도체들, 도전성 폴리머들, 및 카본 잉크, 실버-에폭시 또는 침전가능 금속 나노입자 서스펜션들과 같은 프린팅가능 재료들을 포함하는 당해 기술분야에 공지된 다양한 게이트 재료들이 또한 적절할 수 있다. 예를 들어, 게이트 전극은 도핑된 실리콘, 또는 알루미늄, 크롬, 금, 은, 니켈, 구리, 텅스텐, 팔라듐, 플래티늄, 탄탈륨 및 티타늄과 같은 금속을 포함할 수 있다. 게이트 전극 재료들은 또한 인듐-틴 옥사이드(ITO), ZnO, SnO<sub>2</sub>, 또는 In<sub>2</sub>O<sub>3</sub>와 같은 투명한 도전체들을 포함할 수 있다. 또한, 도전성 폴리머들, 예를 들어, 폴리아닐린, 폴리(3,4-에틸린다이옥시티오펜)/폴리(스티렌설포네이트)(PEDOT:PSS)가 사용될 수 있다. 추가로, 이들 재료들의 합금들, 혼합물들 및 다층들이 사용될 수 있다.

[0031] 게이트 전극은 화학 기상 증착, 스퍼터링, 이베포레이션(evaporation), 도핑 또는 용해 공정을 사용하여 기판(110) 상에 증착될 수 있다. 본 발명의 일부 실시예들에서, 동일한 재료가 게이트 전극 기능을 제공하고, 또한 기판(110)이 트랜지스터(100)를 전기적으로 절연시키기 위한 절연층을 포함하는 경우 기판(110)의 지지 기능을 제공할 수 있다. 예를 들어, 도핑된 실리콘은 게이트 전극으로서 기능하고 TFT를 지지할 수 있다.

[0032] 게이트 전극의 두께(도 2에 도시된 바와 같은 수직 방향)는 통상적으로 약 100에서 약 10000 nm까지 달라질 수 있다. 두께가 게이트 길이를 정의함에 따라, 두께는 일반적으로 전기적 단락 가능성을 감소시키기 위해 등각으로 코팅된 재료들의 두께의 두배보다 더 두껍다.

[0033] 도 2에 도시된 바와 같이, 비도전층(130)은 도전층(120) 위에 균일하게 코팅된다. 비도전층(130)에서 사용하기에 적합한 예시적인 재료들은 스트론티에이트(strontiates), 탄탈산염, 티탄산염, 지르콘산염, 알루미늄 산화물, 실리콘 산화물, 탄탈륨 산화물, 티타늄 산화물, 실리콘 질화물, 바륨 티탄산염, 바륨 스트론튬 티탄산염, 바륨 지르콘산염 티탄산염, 아연 셀렌화물 및 아연 황화물을 포함한다. 추가로, 이들 예들의 합금들, 혼합

물들 및 다층들이, 일반적으로 게이트 유전체라고 참조되는 비도전층(130)에 대해 사용될 수 있다. 이들 재료들 중에서, 알루미늄 산화물, 실리콘 산화물, 및 아연 셀렌화물이 바람직하다. 추가로, 폴리아미드, 폴리비닐 알콜, 폴리(4-비닐페놀), 폴리아미드 및 폴리(비닐리텐 플루오르화물), 폴리스티렌 및 그 치환된 파생물, 폴리(비닐 나프탈렌) 및 치환된 파생물, 및 폴리(메틸 메타크릴레이트)와 같은 고분자 재료가 사용될 수 있다.

[0034] 비도전층(130)은 레지스트(400)로 코팅된다. 레지스트(400)는 패터닝된다. 레지스트(400)는 폴리머 포지티브 동작 레지스트 또는 네거티브 레지스트와 같은 당해 기술분야에 공지된 종래의 포토레지스트일 수 있다. 레지스트(400)는 기판(110)에 대해 낮은 분해능(> 1 mm) 정렬을 가지는 마스크를 통해 노출되고 레지스트의 패턴을 얻기 위해 현상된다. 또다른 예시적인 실시예에서, 레지스트(400)의 패턴은 마스크를 사용하지 않고 패터닝된 방식으로 직접 레지스트를 프린트하는 플렉소그래피 또는 잉크젯 프린팅과 같은 프린팅 공정을 사용하여 달성된다.

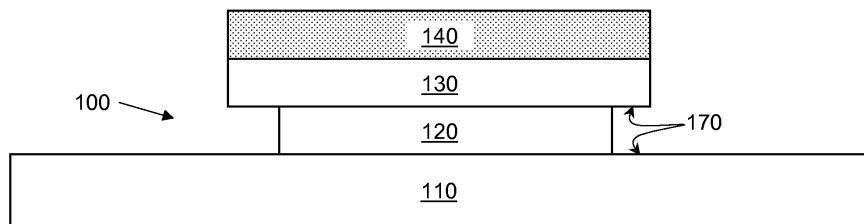

[0035] 도 3 내지 5를 다시 참조하면, 재료 공정 동안 그리고 재료 공정 이후 트랜지스터(100) 재료의 개략적 횡단면도가 도시된다. 도 3에서, 공통적으로 비도전체라고 참조되는 비도전층(130)이 패터닝된 레지스트(400)를 통해 에칭된다. 에칠프로필트리트는 기저의 도전층(120) 또는 레지스트(400)의 실질적 침해(attacking) 없이 비도전 재료를 제거하는 임의의 유기 또는 무기 재료일 수 있다. 도전체(120)는 이후, 도전체(120)를 제거하지만 기판(110) 또는 위에 놓인(overlying) 비도전체(130)에 대한 영향을 거의 가지지 않는 적절한 에칠프로필트리를 사용하여 제거된다. 따라서, 선택된 에칠프로필트리는 종종 기판(110), 도전체(120), 또는 비도전체(130)에 의존한다. 레지스트(140)와의 에칠프로필트리트 상호작용 및 이때의 레지스트(140)의 손실은 일반적으로 크게 중요하지 않은데, 왜냐하면, 비도전체(130)가 이제 마스크로서 작용하기 때문이다. 도 3에 도시된 바와 같이, 에칭 공정 또는 공정들은, 도전체(120) 및 비도전체(130)가 동일한 패턴을 가지도록, 도전체(120) 및 비도전체(130)의 일부분들을 에칭하는데 사용되었다.

[0036] 도 4에 도시된 바와 같이, 도전체(120)의 선택적 에칭은 도 4에 도시된 요각 프로파일(170)이 형성될 때까지 계속된다. 도전체(120)의 에칭이 완료되는 경우, 비도전체(130)는 도전체(120) 위로 돌출하며, 이는 (도 4에 도시된 바와 같이) 기판(110) 위에 위치지정된 (도전체(120) 또는 기판(110)의) 기저 표면의 적어도 일부를 지향성(또는 라인-오브-사이트) 코팅 소스에 의한 코팅으로부터 차폐하기에 충분한 요각 프로파일(170)을 생성한다. 다르게 언급하자면, 도전체(120)는 비도전체(130) 아래에 매달려있다(underhang). 나머지 도전체(120)는 반도체 디바이스가 완료될 때 게이트 도전체로서 작용한다.

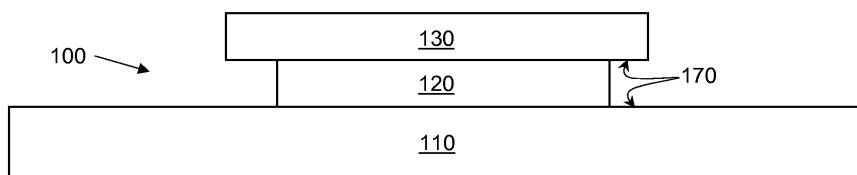

[0037] 이 시점에서, 필요한 경우, 레지스트(140)가 제거된다. 세정 공정이 요각 프로파일(170)을 제거하지 못하는 경우, 필요하다면, 부드러운 세정이 재료층 스택 상에서 수행될 수 있다. 도 5는 요각 프로파일(170)이 생성된 이후 그리고 레지스트가 제거된 이후 반도체 디바이스의 횡단면도를 도시한다.

[0038] 도 6 및 도 7을 다시 참조하면, 종종 절연체라고 참조되는 유전성 비도전 재료, 및 반도체 재료를 각각 등각 코팅한 이후의 반도체 디바이스의 개략적 횡단면도들이 도시된다. 도 6에서, 유전성 비도전 재료(150)는 이후 기판(110) 및 재료층들(120 및 130)에 의해 형성된 표면형태 특징 위의 등각 코팅 증착 공정을 사용하여 등각으로 코팅된다. 등각 코팅 공정을 사용하여 비도전 재료(150)를 도포하는 것은 요각 프로파일(170)을 유지하는 것을 보조한다. 비도전 재료(150)는 종종 게이트 유전체라고 참조된다. 적절한 비도전 재료는 스트론티에이트, 탄탈산염, 티탄산염, 지르콘산염, 알루미늄 산화물, 실리콘 산화물, 탄탈륨 산화물, 티타늄 산화물, 실리콘 질화물, 바륨 티탄산염, 바륨 스트론튬 티탄산염, 바륨 지르콘산염 티탄산염을 포함한다. 유전 재료가 도포될 반도체 재료로부터 게이트 도전체를 분리시킴에 따라, 등각으로 코팅된 재료에 적어도 요각 프로파일(170) 및 게이트가 위치되는 영역 내에 일정하거나 균일한 두께가 제공되는 것이 중요하다.

[0039] 등각 코팅을 달성하기 위한 바람직한 공정들은 원자층 증착(ALD) 또는 그 파생물들 중 하나, 예를 들어, 공간 ALD (S-ALD) 또는 플라즈마 강화 ALD(PEALD)를 포함하는데, 왜냐하면, 이들 공정들이 매우 가변적인 토폴로지에 대해 또는 그 위에서 균일한 두께 코팅을 획득하기 때문이다. ALD 및 S-ALD가 하기에 더욱 상세하게 논의된다.

[0040] 도 7에서, 반도체 재료(160)는 이후 요각 프로파일(170)을 유지하는 것을 보조하는 등각 코팅 증착 공정을 사용하여 코팅된다. 이러한 등각 코팅 공정은 유전 재료를 코팅하기 위해 이전에 사용된 동일한 공정일 수 있다. 대안적으로, 등각 코팅 공정은 상이할 수 있다. 게이트(120)가 활성화될 때 반도체 재료(160)가 전극(700 및 800) 사이에서 채널로서 작용함에 따라, 적어도 요각 프로파일(170) 및 게이트가 위치되는 영역 내에서, 더 바람직하게는 요각 프로파일(170) 및 게이트가 위치되는 영역을 포함하는 전극(들)(700) 및 전극(800) 사이의 영역을 내에서 등각으로 코팅된 재료에 일정한 또는 균일한 두께가 제공되는 것이 중요하다. 등각 코팅을 위한 바람직한 공정은 원자층 증착(ALD) 또는 그 다양한 파생물들 중 하나, 예를 들어, 공간 ALD (S-ALD)이다. 이러한

한 공정은 고도로 가변적인 토폴로지에 대해 균일한 두께를 획득한다. ALD 및 S-ALD가 하기에 더욱 상세하게 논의된다.

- [0041] 종종 반도체라고 참조되는 반도체 재료층(160)은 반도체 재료가 ALD와 같은 등각 코팅 공정을 사용하여 증착 또는 코팅될 수 있는 경우 임의의 타입의 반도체일 수 있다. 적절한 반도체 재료들의 예들은 아연 산화물, 아연 칼코겐화물, 카드뮴 칼코겐화물, 갈륨 낙타이드, 알루미늄 낙타이드 또는 실리콘을 포함한다.

- [0042] 반도체는 도전성을 증가 또는 감소시키기 위해 다른 재료들로 선택적으로 도핑될 수 있다. 일부 예시적인 실시 예들에서, 공핍 모드 디바이스가 바람직하며, 따라서, 캐리어들은 도편트들의 사용을 통해 추가될 수 있다. 반도체가 아연 산화물인 경우, 알루미늄 도편트의 사용은, 예를 들어, 전자 캐리어 밀도를 증가시킨다. 이러한 구성에서, 게이트는 통상적으로, 게이트를 드레인 및 소스에 대해 네거티브로 만듦으로써 디바이스를 턴오프하기 위해 사용된다.

- [0043] 보상 도편트는 또한 진성 캐리어 농도를 공핍시키기 위해 사용될 수 있다. 반도체가 아연 산화물인 경우, 질소의 사용은 전자 캐리어 밀도를 감소시키며 반도체를 더 약한 n-타입으로 만드는 것으로 발견되었다. 이러한 구성에서, 반도체는 양의 게이트 전압이 인가되는 경우 트랜지스터를 턴온시키기 위해 누적 모드에서 동작하도록 만들어질 수 있다. 이를 도편트들은 종종 성장 동안 화합물들로서 추가되지만, 또한 반도체층이 이온 주입 또는 열 확산과 같은 공정을 사용하여 도포된 이후에 추가될 수도 있다.

- [0044] 도 8을 다시 참조하면, 전기적 도전 재료의 지향성 코팅 동안 반도체 디바이스의 개략적 횡단면도가 도시된다. 반도체층(160)이 증착된 이후, 소스 및 드레인 전극(들)(700) 및 전극(800)은 요각 프로파일(170) 내로 재료를 증착 또는 코팅시키지 않는 지향성(또는 라인-오브-사이트) 증착 공정을 사용하여 증착된다. 적절한 지향성 증착 공정의 예들은 열 증착, 전자 빔 증착, 스퍼터링, 또는 레이저 삭마를 포함한다. 전극(들)(700) 및 전극(800) 사이의 활성 채널 캡은 도전 재료층(120)에 대한 비도전층(130)의 돌출에 의해 생기는 그림자에 의해 유지된다.

- [0045] 도 1을 다시 참조하면, 전극(들)(700) 및 전극(800)이 증착된 이후 트랜지스터(100)가 도시된다. 트랜지스터(100)의 드레인 및 소스는 전극(700) 및 전극(800) 중에서 선택될 수 있으며, 상기 선택은 통상적으로 참작되는 디바이스들의 특성을 및 응용예에 기초한다. 도 1에 도시된 바와 같이, 전극(800)은 비도전체(130) 및 도전체(120)에 의해 형성되는 메사의 최상부 상에 존재하지만, 전극(들)(700)은 그러하지 않다. 그러한 것으로서, 전극(700) 및 전극(800)은 상이한 면들 상에 존재한다. 임의의 필요한 상호접속들은 당해 기술분야에 공지된 종래의 기법들, 예를 들어, 레이어 레벨링 및 비아 피드 스루(via feed through)를 사용하여 달성될 수 있다.

- [0046] 기판(110), 도전층(120), 비도전층(130), 비도전층(150), 반도체층(160), 또는 이들의 조합은 층의 기능적 양상들이 변경되지 않고 유지되는 경우 하나 이상의 층들을 포함할 수 있다. 추가적인 층들, 예를 들어, 레벨링 층들, 장벽층들, 접착층은 전술된 층들의 기능이 보존되는 한 반도체 디바이스 내에 포함될 수 있다.

- [0047] 원자층 증착(ALD)은 일정한, 균일한, 또는 심지어 정확한 것으로 간주될 수 있는 두께들을 가지는 코팅들을 생성하기 위해 사용되는 공정이다. ALD는 등각이거나 또는 훨씬 더 등각인 재료 층들로 간주될 수 있는 코팅들을 생성한다. 일반적으로 설명하자면, ALD 공정은 진공 챔버 내에서 일반적으로 전구체들이라고 참조되는 둘 이상의 반응성 재료들 사이에서 변경시킴으로써 기판 코팅을 달성한다. 제1 전구체가 기판과 반응하기 위해 도포된다. 제1 전구체의 초과분은 진공 챔버로부터 제거된다. 제2 전구체는 이후 기판과 반응하기 위해 도포된다. 제2 전구체의 초과분은 진공 챔버로부터 제거되고 공정이 반복된다.

- [0048] 최근에, 진공 챔버에 대한 필요성을 무효화시키는 새로운 ALD 공정이 개발되었다. 일반적으로 S-ALD라고 참조되는 이러한 공정은 미국 특허 제7,413,982호, 미국 특허 제7,456,429호, 미국 특허 공보 제2008/0166884호, 및 미국 특허 공보 제2009/0130858호 중 적어도 하나에 기재되며, 이 개시내용들은 여기에 참조로 통합된다. S-ALD는 일정하고, 균일하거나, 또는 심지어 정확한 것으로 간주될 수 있는 두께들을 가지는 코팅들을 생성한다. S-ALD는 등각이거나, 훨씬 더 등각 재료층인 것으로 간주될 수 있는 코팅들을 생성한다. S-ALD는 저온 코팅 환경에서 호환가능하고, 다른 코팅 기법들에 비해 더 높은 이동도 재료들을 사용하기 위한 능력을 제공한다. 추가로, S-ALD는 웹 코팅과 호환가능하여, 이를 대규모 생산 공정에 대해 흥미롭게 한다. 일부 웹 코팅 동작들이 예를 들어, 웹 트래킹 또는 스트레칭 이슈들과 같은 정렬 이슈들을 경험할 수 있지만, 본 발명의 아키텍처는 제조 공정 동안 높은 분해능 또는 매우 미세한 정렬 특징들에 대한 의존성을 감소시킨다. 그러한 것으로서, S-ALD는 본 발명의 제조에 대해 매우 적합하다.

- [0049] 실험 결과들

[0050] 600 nm 크롬층이 열 산화물층에 의해 코팅된 62.5 제곱 밀리미터( $\text{mm}^2$ ) 실리콘 기판 상에서의 스퍼터링을 통해 증착되었다. 이것의 최상부 상에, 120 nm 알루미늄 산화물층이 미국 특허 제7,413,982호에서 기술된 S-ALD 공정, 및 미국 특허 제7,456,429호에서 기술된 S-ALD 장치를 사용하여 질소의 불활성 캐리어 가스를 가진 워터 및 유기-금속 전구체 트리메틸 알루미늄으로 섭씨 200도에서 코팅되었다.

[0051] 패터닝된 포토레지스트층은 낮은 분해능 또는 조제(crude) 정렬로서 실리콘 기판의 에지들만을 사용하여, 섭씨 115도에서 60초동안 뜨거운 플레이트 상에 배치된 Microposit S1805 레지스트(MA주, Marlborough, Rohm and Haas Electronic Materials LLC)를 1000 rpm에서 스핀 코팅함으로써 형성되고, 이후, Cobalt 마스크 정렬기(CA 주, Sunnyvale, Computervision 사로부터의 Cobalt 모델 CA-419) 상에서 70초 동안 라인들을 포함하는 유리/크롬 접촉 마스크를 통해 노출되었다. 샘플이 이후 Microposit MF-319 현상기(MA주, Marlborough, Rohm and Haas Electronic Materials LLC)에서 60초 동안 현상되고 DI 워터에서 5분 동안 린싱되었다.

[0052] 비도전성 알루미늄 산화물이 6.5분 동안 농축 인산을 이용하여 섭씨 60도에서 에칭되었다. 크롬은 8% 아세트산을 이용하여 세륨 암모늄 염화물의 0.6M 용액을 포함하는 크로뮴 에칭을 사용하여 에칭되었다. 노출된 크롬은 13.3분에서 가시적으로 에칭되었다. 언더컷 에칭은 2분 동안의 계속된 에칭을 통해 달성되었다. 기판은 이후 5분동안 DI 워터에서 린싱되고, 포토 레지스트를 제거하기 위해 아세톤으로 린싱되고, 이후 HPLC 그레이드 이소프로페놀에서 린싱되고, 이후 건조하도록 허용되었다.

[0053] 기판은 이후 S-ALD 장치 및 공정을 사용하여 등각으로 알루미늄 산화물의 추가층 120nm 두께를 가지고 전술된 바와 같이 코팅되었다. 기판은 이후 전구체들, 다이에틸 아연 및 농축 암모니아 용액 및 캐리어 가스로서의 질소를 사용하여 25 nm 아연 산화물층으로 코팅되었다.

[0054] 전극들은 증발에 의해 도포되었다. 알루미늄은 기판 상에서 각각의 라인에 완전하게 교차하고 직교로 진행하는 사각홀들을 포함하는 쉐도우 마스크를 통해 증발되었다. 알루미늄은 70 nm 두께였다.

[0055] 트랜지스터의 테스트는 라인의 최상부 상의 알루미늄, 라인의 한 측면 상의 알루미늄 및 게이트로서 작용하는 크롬 게이트 금속을 접촉시키기 위한 프로브 스테이션을 사용함으로써 달성되었다. 도 9를 참조하면, 트랜지스터에 대한 성능 전송 특성들을 도시하는 그래프가 도시된다. 도 9에서 알 수 있는 바와 같이, 드레인 전류 대 게이트 전압은 20 볼트의 드레인 전압에서 일정하다. 모든 게이트 전압들에서 매우 적은 누설을 가지는 게이트 전류가 또한 도시된다. 또한, 드레인 전류는, 2볼트의 게이트에서의 약  $10^{-11}$  암페어의 소전류 내지 10볼트의 게이트에서의 거의 1밀리암페어까지를 범위로 하는, 게이트 전압에 적절히 응답하는 것 역시 알 수 있다. 도 10을 참조하면, 트랜지스터에 대한 성능  $I_d$ - $V_d$  커브 특성들을 도시하는 그래프가 도시된다. 도 10에서 알 수 있는 바와 같이, 드레인 전류 대 드레인 전압은 게이트 전압에 대해 매우 응답한다. 디바이스의 테스트 결과들은 또한 10V 게이트 전압 및 20V 드레인 전압에 대해  $10^7$ 보다 더 큰 양호한(respectable) 온/오프를 도시한다.

## 부호의 설명

[0056] 100 트랜지스터

110 기판

120 도전체

130 비도전체

140 레지스트

150 게이트 유전체

160 반도체

170 요각 프로파일

700 전극

710 제2 전기적 도전 재료층

800 전극

810 제3 전기적 도전 재료층

도면

도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10