(19) (KR)

(12) (B1)

(51) 。 Int. Cl. <sup>7</sup>

H03K 3/037 (45) 2003 03 15

(11) 10 - 0375907

(24) 2003 02 28

---

(21) 10 - 2001 - 0017989 (65) 2001 - 0095330

(22) 2001 04 04 (43) 2001 11 03

---

(30) 0008080.4 2000 04 04 (GB)

(73) 가 가

가 22 22

(72) 28 22

44 124

(74)

(54)

---

|     |                |               |           |                   |                   |                 |

|-----|----------------|---------------|-----------|-------------------|-------------------|-----------------|

| (3) | D<br>G가<br>. . | (4)<br>가<br>R | (3)<br>CK | (4)<br>!CK<br>(3) | (1,2)<br>Q<br>. . | (4)<br>(3)<br>D |

|-----|----------------|---------------|-----------|-------------------|-------------------|-----------------|

1                   2

2

3                   2

4     3

5     3     4

6                   2

7     6

8     6     7

9                   2

10    9

11    8     9

12                   2

13    12

14    12     13

15                   2

16    15

17                   1

18                   1

19    18

20                   1

21                   1

22                   1

23

&lt;

3:

1 , N , i (i+a)

, , D - a 1 - ; (i-1)

D (gating circuit) - 1 < i (N-a) -

D D .

D 가

$$i \quad D \quad (i+a)$$

i D (i+a) D

D

(cascade)

+1) D

D

(switching arrangement)

i D (i - 1) D

$$D_i \quad D_{(i+1)} \\ 1-(1+a) \quad D_{(i+1)};$$

1 1 D

$$N \quad , \quad D \\ ; \quad (N - 1) \quad D \quad D$$

D , D , D , D

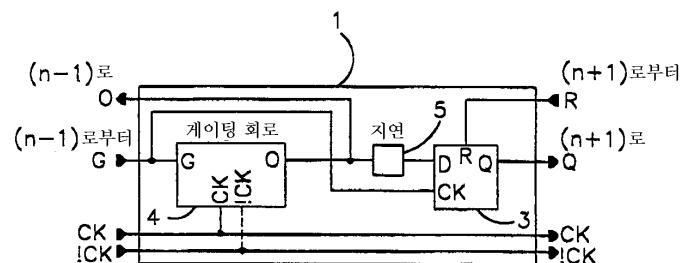

1 , D . , 1 , 1 , 4 , 3 , 4 , 1 , 1 , 4 , 1 , , ,

The diagram shows a logic circuit with four inputs labeled D<sub>1</sub>, D<sub>2</sub>, D<sub>3</sub>, and D<sub>4</sub>. The outputs are labeled 1, 2, 5, and 2. The first three outputs (1, 2, 5) are connected to the inputs of a 4-to-16 decoder. The fourth output (2) is connected to one input of a NOT gate (inverter). The other input of the NOT gate is connected to the fourth input D<sub>4</sub>. The output of the NOT gate is connected to the fourth input of the decoder. The decoder has four outputs: 1, 2, 3, and 4. The output 2 is connected to the inputs of two AND gates. The other inputs of these AND gates are connected to the outputs of the decoder. The outputs of the AND gates are labeled 2 and (gated inverter).

1 , 가

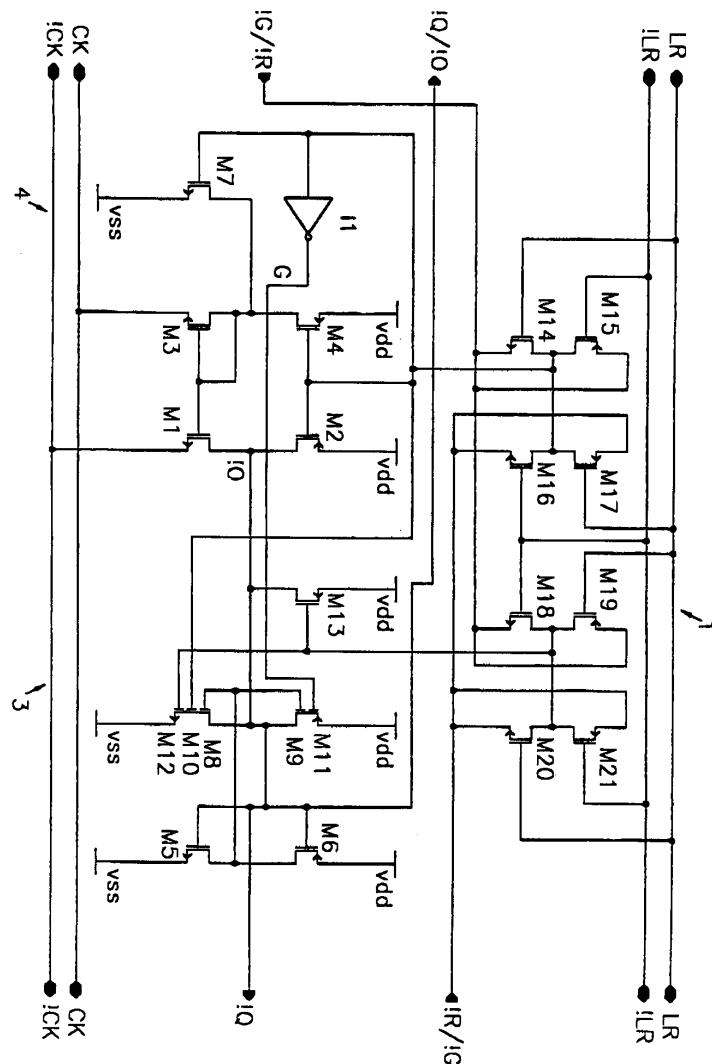

CMOS

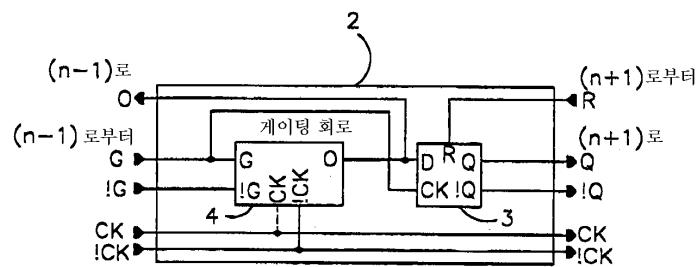

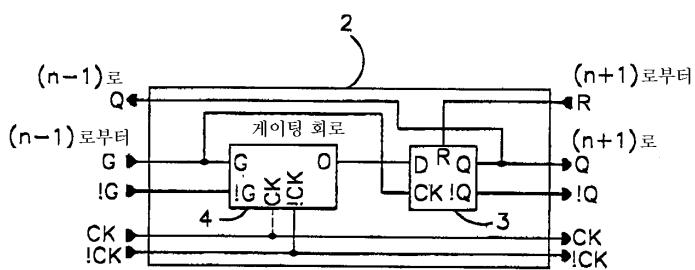

2 , 1

3 , 2 가

4 , 1 가

가 가

10 20

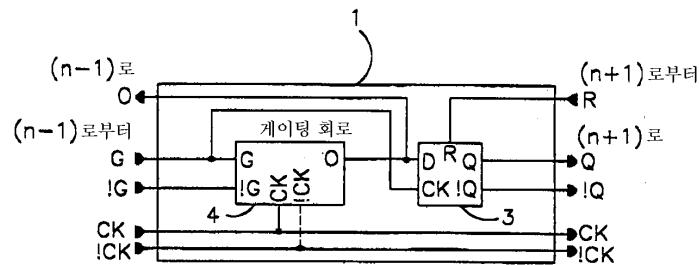

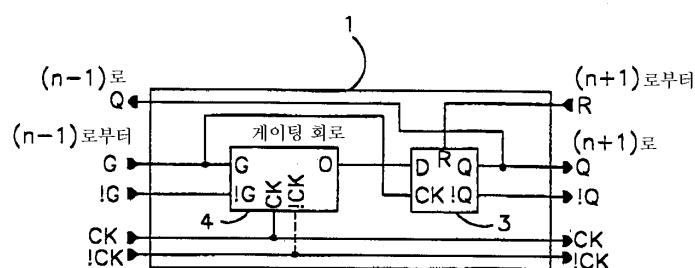

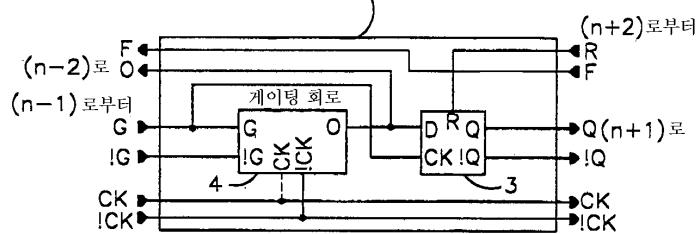

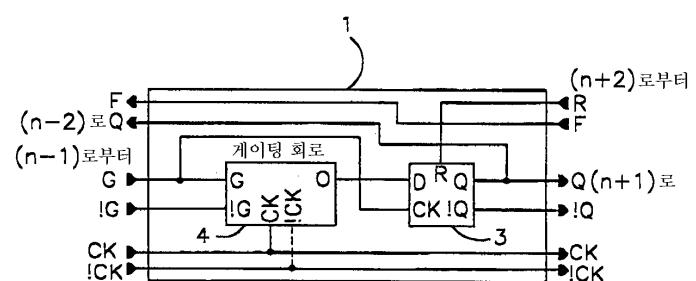

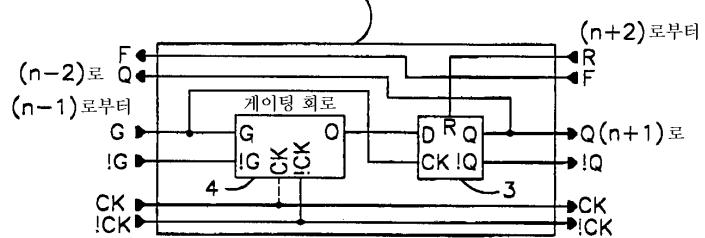

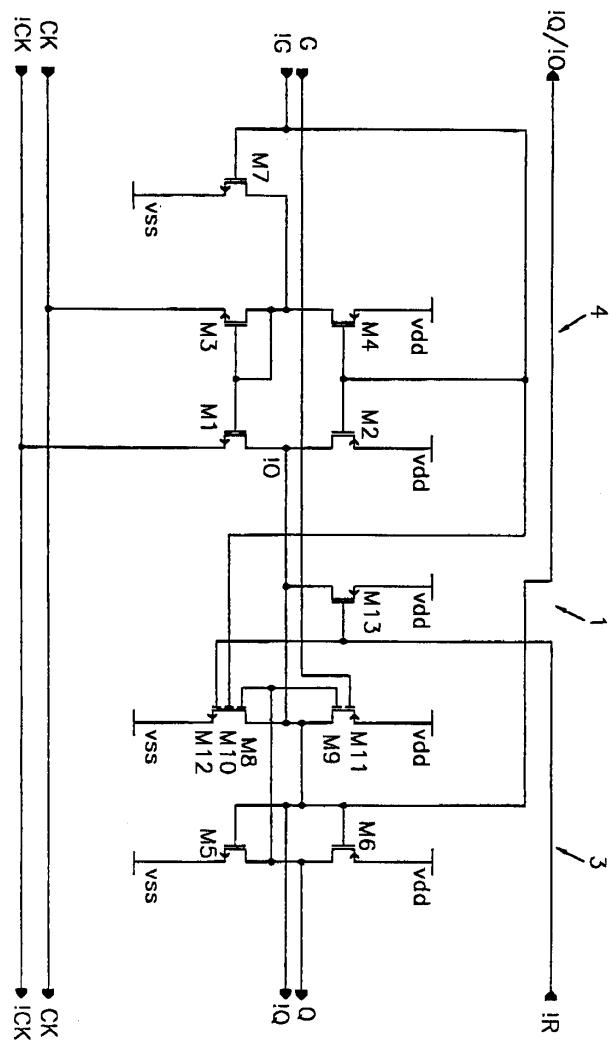

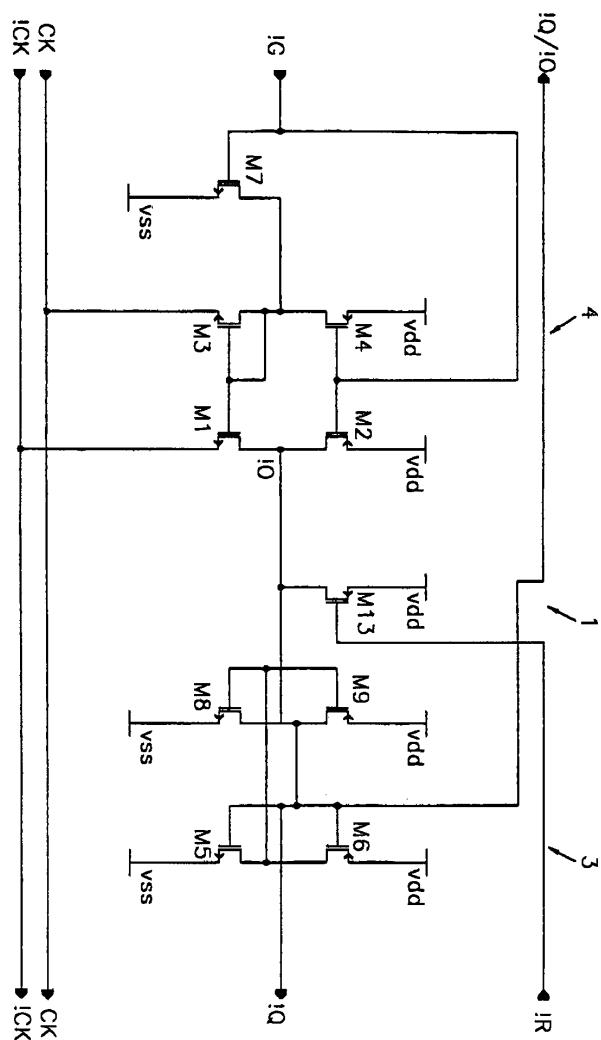

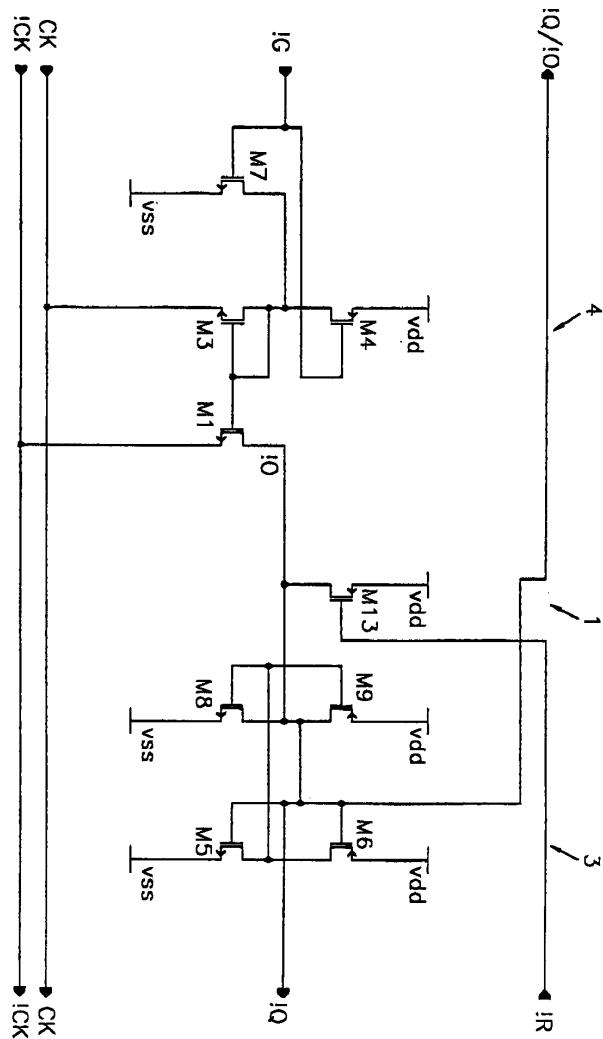

3 2 (1 2) (3) Q, !Q , (1) D (3) (4)

, Q

R

(4) (1) (4) CK CK !CK CK, !CK 3

,

(4) (4) (3) (G) G, !G (3) CK

(D) O

(1) CK , (2) !CK ( ) (4) !

CK ,

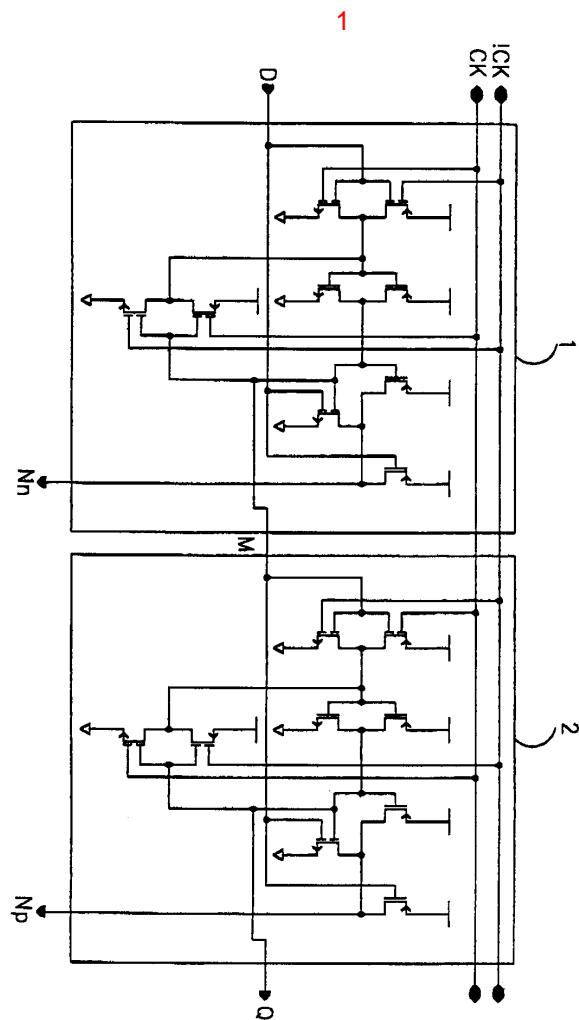

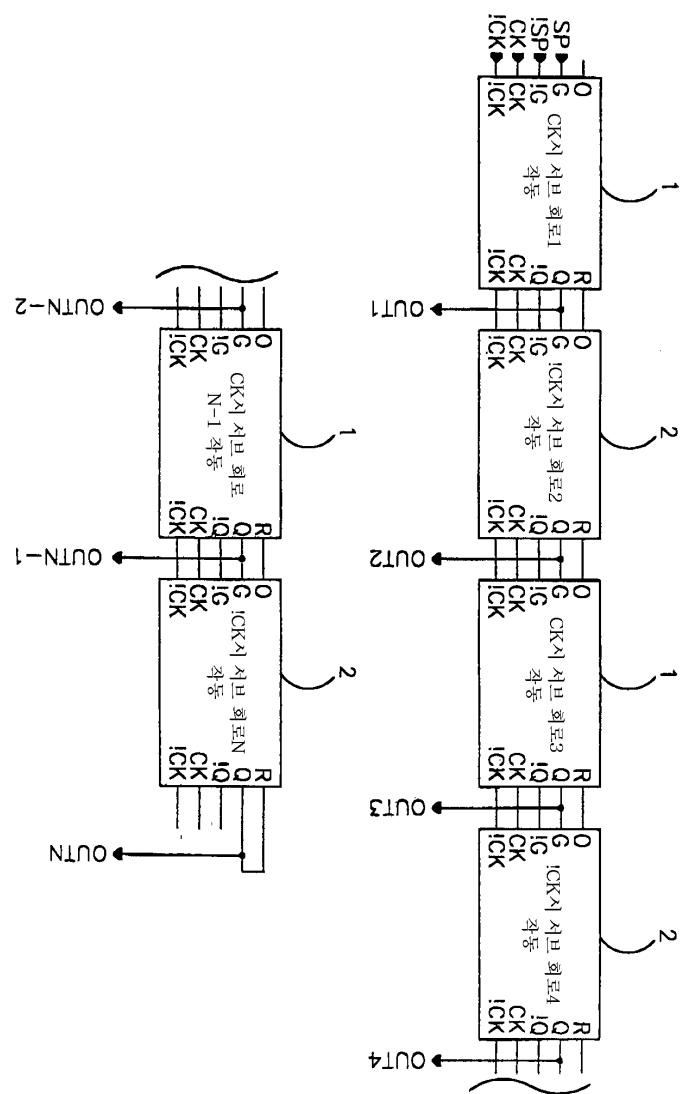

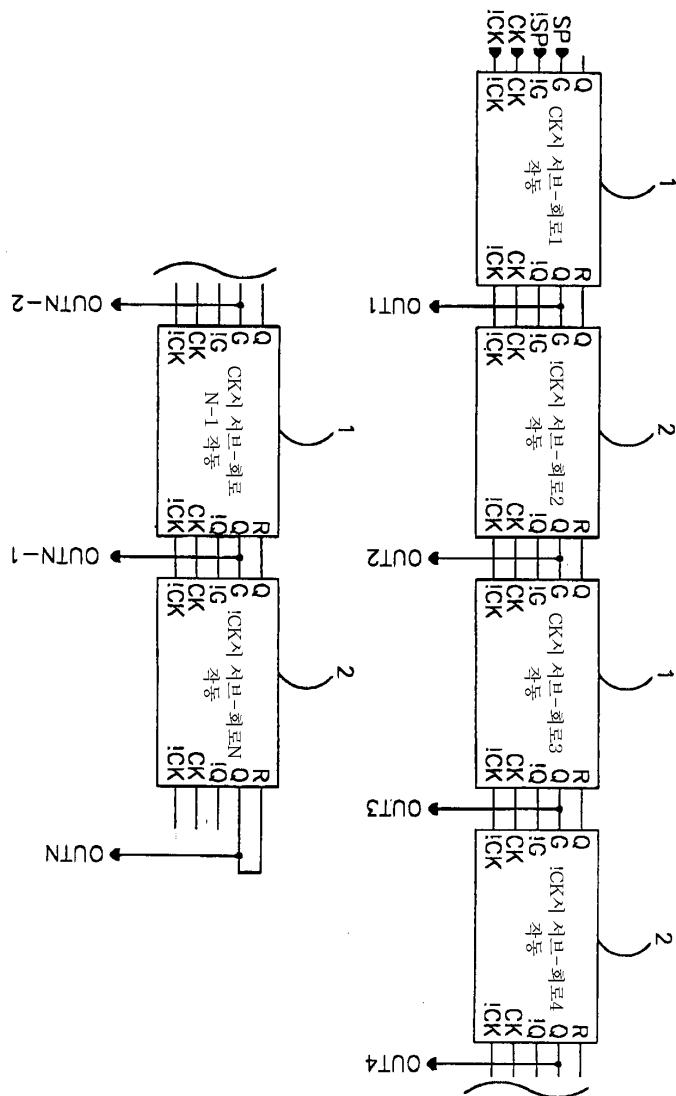

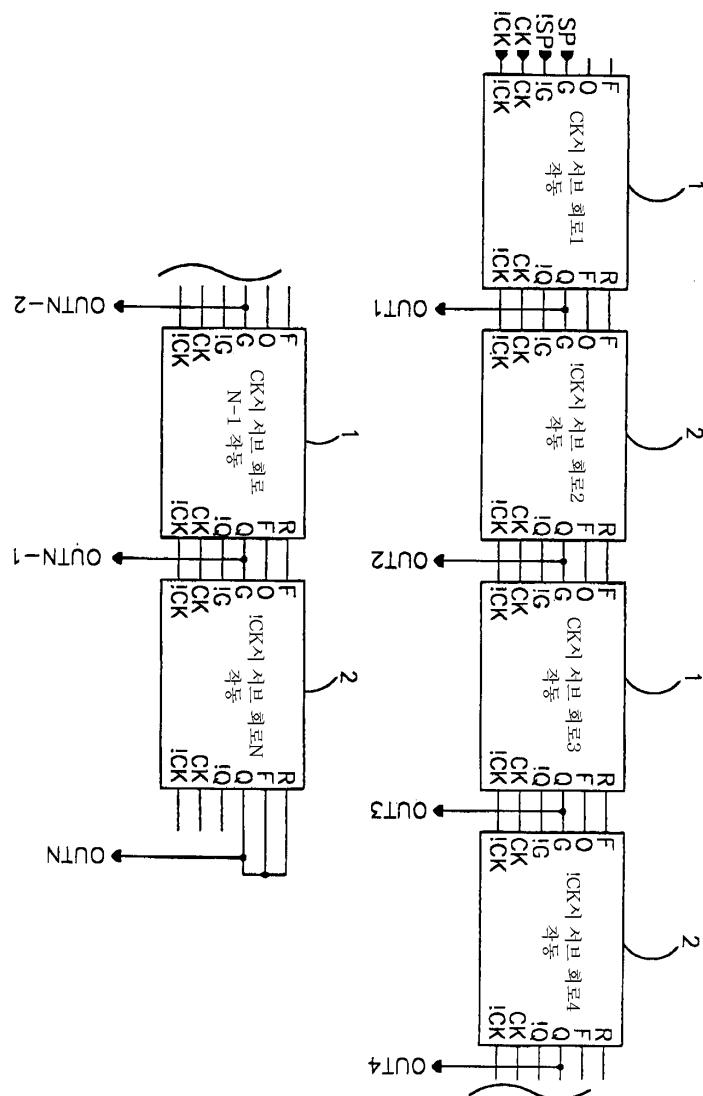

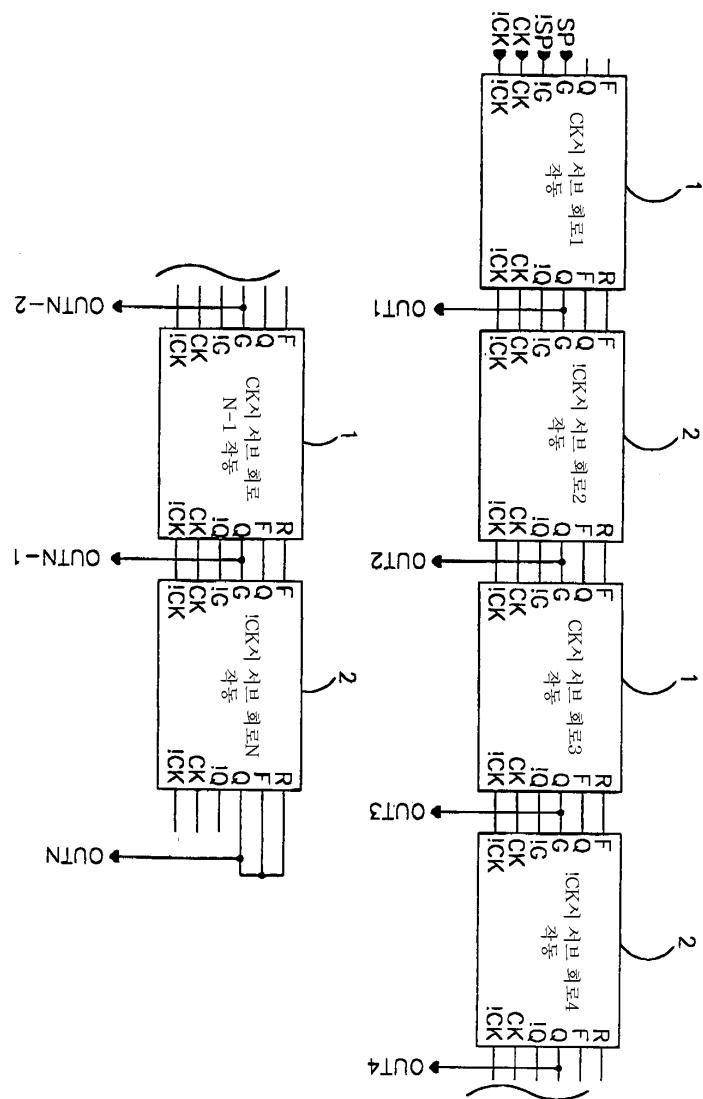

4 (2) 1 (1) N (1, 2) G, !G SP, !SP (1) (1)

2 R N CK, !CK (1, 2) R Q O

, (1, 2) 4 (3) 4 , O 5

(1, 2) (4) O

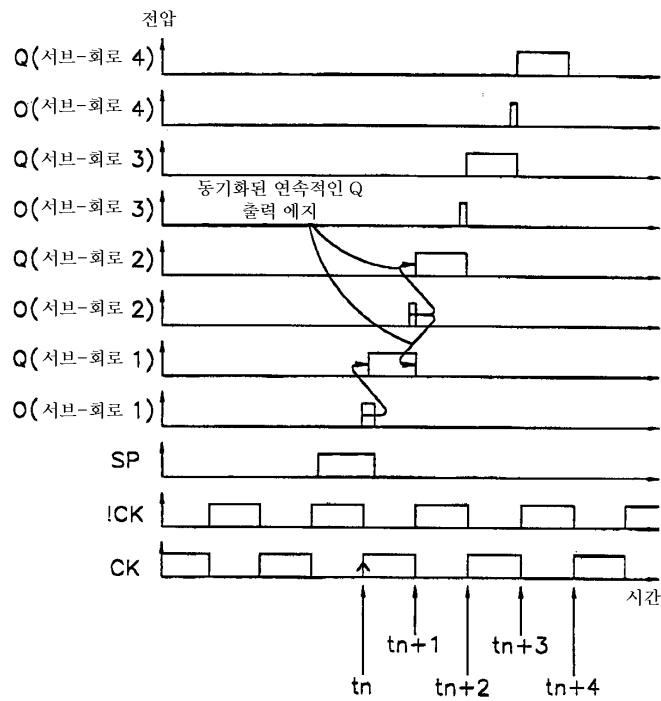

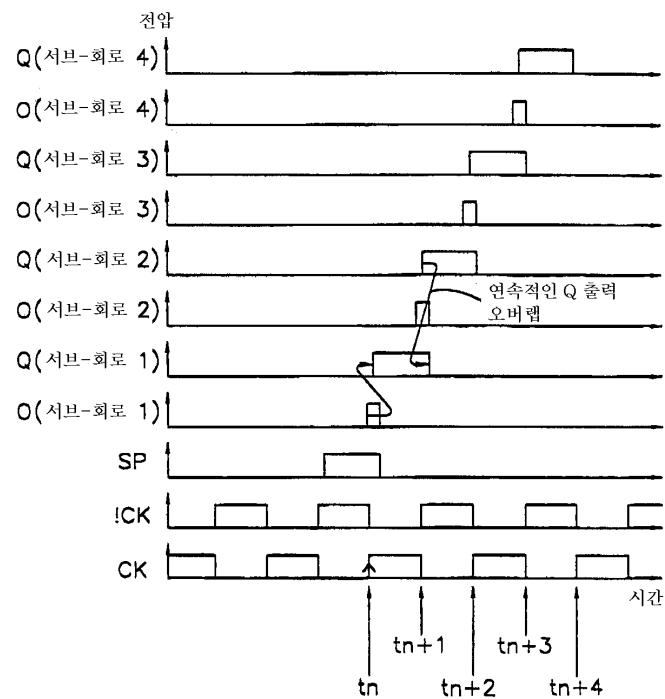

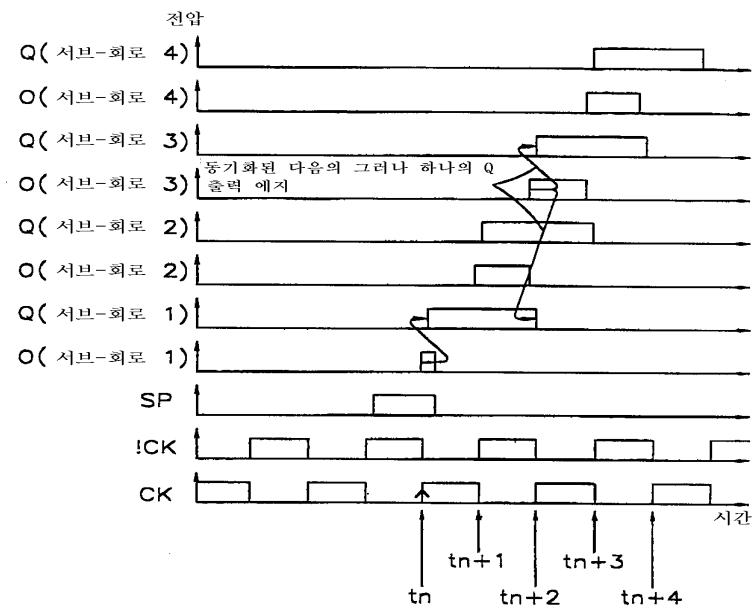

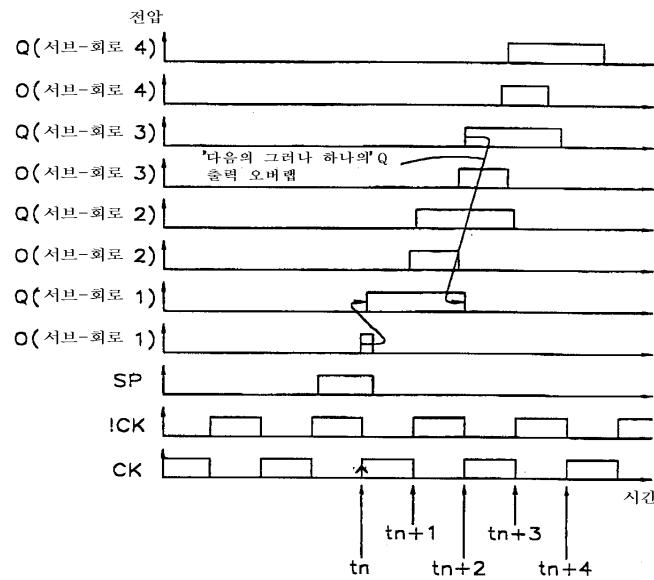

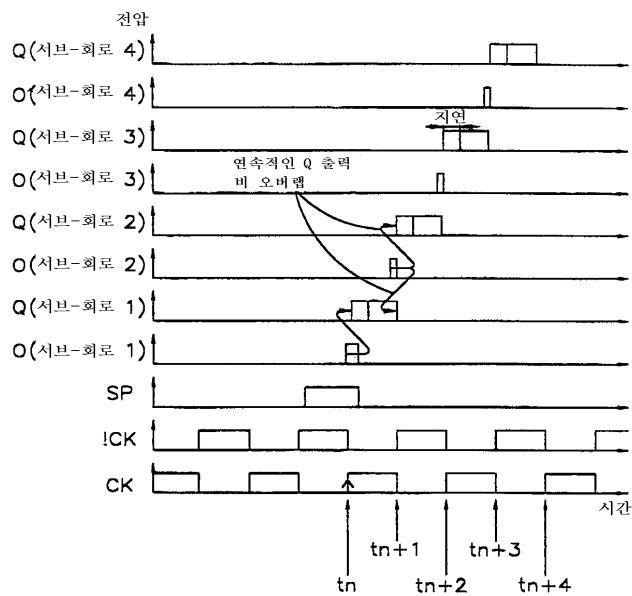

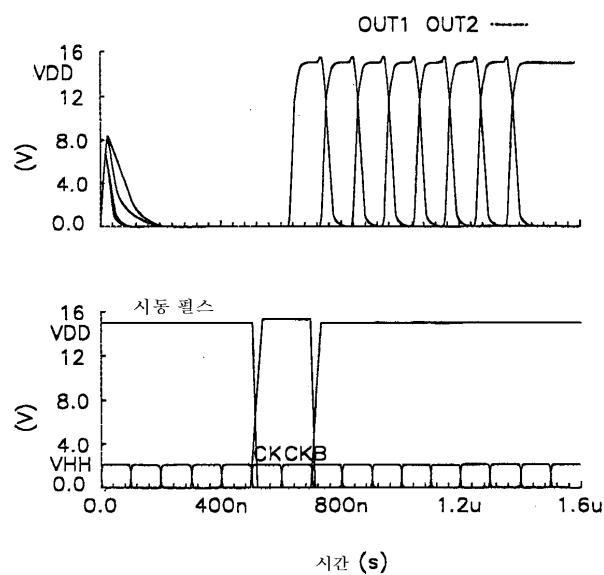

t<sub>n</sub>, 1 SP가 , (4) CK , (4) , , ,

(4) O

Q t<sub>n</sub>, 가 , (4) O CK , 가 , , (3)

CK t<sub>n</sub>, SP 가 , 1 (1) Q가

t<sub>n</sub>+1 2 (2) (4) O !CK 2 , 2

2 (4) O 1 Q 3 R (4) Q , 2

5

Q t<sub>n</sub>+2 3 (4) O CK 2 (3) 3

가 4 (4) 1

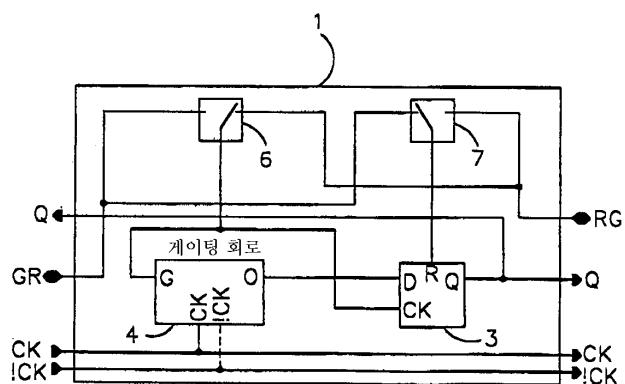

6 (1) (2) 가 7 (4) Q (3) Q

4 3 . . . (1 2)

8 , Q 8 (3) (3) 가 ,

,

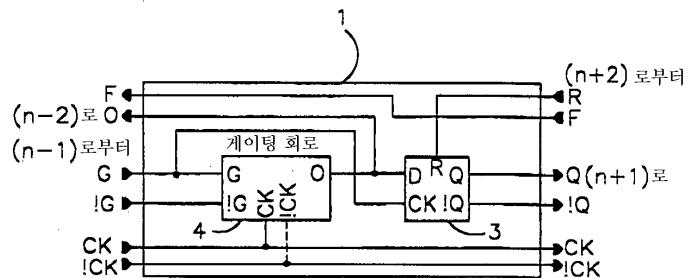

9 (1, 2) 가 (next - but - one following s

stage) , n , (1, 2) 가 (n+2)

3 , (feed - through line) F R F 10

. N Q . .

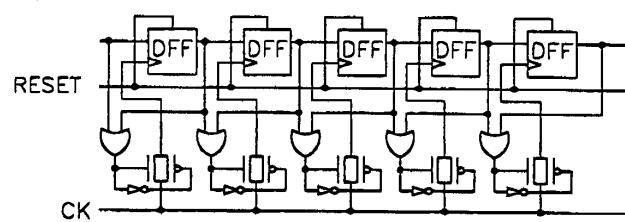

11 , Q CK, !CK Q

,

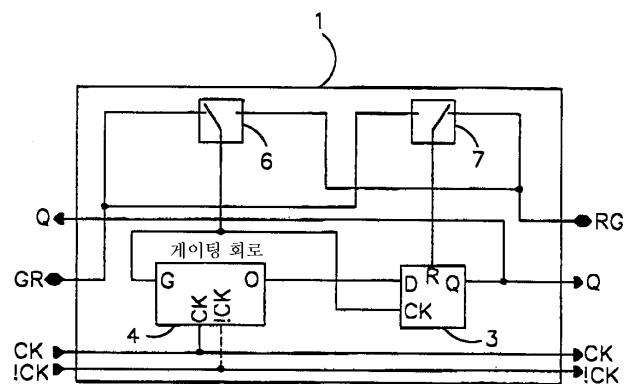

12 (1) (2) 6 , Q 가 ,

9 10 (3) (3) 가 13 (3)

, (next - but - one stage) Q 가 , 14

,

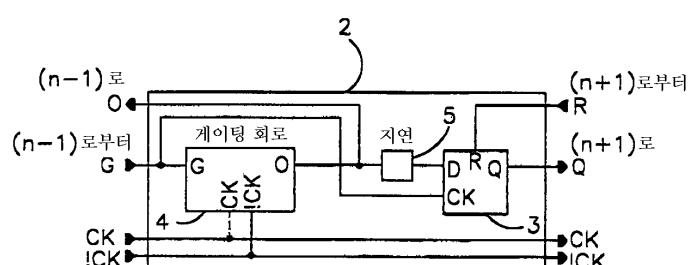

15 (1, 2) (4) 0 (3) 0 D 3

(5) 가 (4) . . (5)

. 4 (3) 가 ,

,

16 , (5) Q 가 (3) 가 (non - overlapping)

,

17 (1) 17 !CK (2) 6

,

(1) 1 2 (6,7) (6,7)

( ) 17

17 , 가 , (6)

G (3) CK Q GR . (7)

Q RG (3) R . ,

$$(6,7) \quad 2 \qquad \qquad \qquad 1 \qquad \qquad \qquad . \qquad \qquad \qquad 2$$

18 CMOS . (2) 1 , CK !CK ,

D (3) N M5, P M6 M13, M8, M10,

M12 N , 2 M9, M11

P . M5 M6 (4) (10)

(1) Q M8 - M12

M5 M6 .

M11 G M10 !G

, 가 , , ,

|     |     |     |     |     |    |

|-----|-----|-----|-----|-----|----|

| M13 |     | 1   | vdd | (4) | !O |

| .   | M13 | M12 | (3) |     | !R |

21 20 M2가

!O M9 . , (4)가 , M9

M1 CK 가 !O 1/2

M1 M13 !O .

.

22 M14 - M21 18

. , LR !LR , LR !LR , / , (11)

LR !LR . , G .

!G .

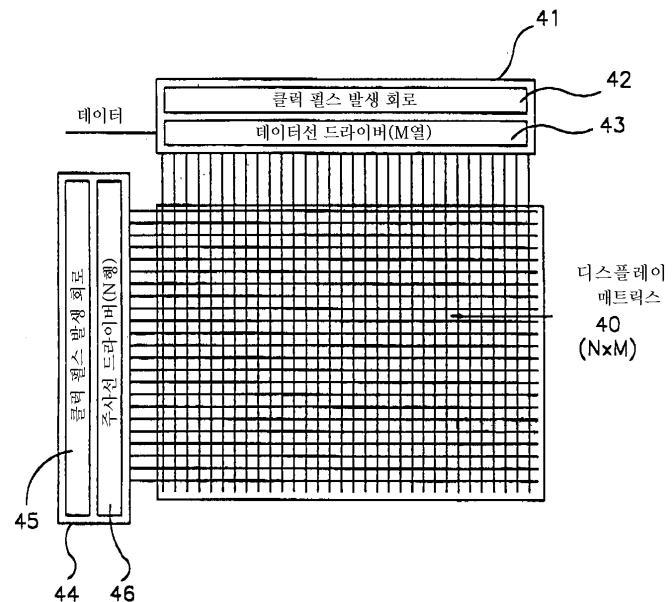

23 N M (40) , (42)

(43) (41) 0 (42) 3 22

(45) (46) (44) (45) 3 22

. (42) . (42) .

45)

, 가 가 . 가 .

(57)

1.

N (stages) ,

i

(i+a) , D - a 1

- ;

(i-1) D (gating circuit) - 1 < i (N-a) -

2.

1 , D D .

3.

1 , D .

4.

1 , i D (i+a)

5.

1 , i D (i+a) D

6.

1 , D

7.

6 , (cascade)

8.

1 ,

(i-a) D

↗ (i+1) D

$(1+a) < i \leq N$  (switching arrangement)

9.

8 ,

10.

1 , i D (i-1) D

11.

8 , i D

$(i+1)$

12.

1 , 1

$(1+a)$  , D ;

D

13.

8 , 1 1 D

14.

1 , N , D D ;

(N - 1) D

15.

1 , , (consecutive pairs of stages)

16.

1 , , , D , 1 D

17.

16 , , , 1 , , 1

2

18.

17 , , 2 , , D

19.

16 , , 1 , , D

20.

19 , , , ,

1 , , 3

21.

20 , 1 , 1

4 .

22.

21 , 4 , D

23.

16 , 1 , 2 , .

5 . D

24.

2 , , D 1 2

25.

24 , 2 , D

(gated inverter) .

26.

24 , 1 , .

27.

1 , CMOS

28.

1 , .

29.

1 .

30.

29 , .

31.

30 , .

32.

30 ,

33.

32 ,

34.

29

35.

1

36.

35 ,

37.

35 ,

2

3

4

5

6

7

9

2

10

11

12

2

13

14

15

17

18

19

20

21

22

23