#### INSTITUT NATIONAL DE LA PROPRIÉTÉ INDUSTRIELLE

**PARIS**

11) N° de publication :

(à n'utiliser que pour les commandes de reproduction)

21) N° d'enregistrement national :

92 02652

2 683 371

(51) Int CI<sup>5</sup> : G 11 C 11/34

(12)

## **DEMANDE DE BREVET D'INVENTION**

**A1**

- 22 Date de dépôt : 05.03.92.

- (30) Priorité : 31.10.91 KR 9119331.

71 Demandeur(s): SAMSUNG ELECTRONICS CO., LTD. — KR.

- 43 Date de la mise à disposition du public de la demande : 07.05.93 Bulletin 93/18.

- 66 Liste des documents cités dans le rapport de recherche : Se reporter à la fin du présent fascicule.

- Références à d'autres documents nationaux apparentés :

- 73) Titulaire(s) :

- 74 Mandataire : Cabinet Nony & Cie.

**(**72**) Inventeur(s) :** Choi Do-chan.

- (54) Mémoire-tampon d'entrée d'adresse d'un dispositif de mémoire à semiconducteurs.

- 67) Mémoire-tampon d'entrée d'adresse d'un dispositif de memoire à semiconducteurs comportant une borne d'entrée d'adresse (1), un commutateur d'adresse de colonne (9), un commutateur de rangée (4), une bascule d'adresse de colonne (9), une bascule d'adresse de rangée (5) reliée au commutateur d'adresse de rangée (5) reliée au commutateur d'adresse de rangée (4), et une mémoire-tampon d'entrée (12) reliée à la borne d'entrée d'adresse (1), au nœud commun du commutateur d'adresse de colonne (9) et au commutateur d'adresse de rangée (4), et commandée par un signal de commande de mémoire-tampon d'entrée. Ainsi, la surface d'implantation peut être réduite en tamponnant les signaux d'entrée d'adresse de rangée et de colonne à l'aide d'une seule mémoire-tampon d'entrée sans séparer les mémoires-tampons d'adresse de colonne et de rangée.

FR 2 683 371 - A1

# <u>Mémoire-tampon d'entrée d'adresse d'un dispositif de mémoire</u> à semiconducteurs.

La présente invention a trait à un dispositif de mémoire à semiconducteurs, et en particulier à une mémoire-tampon d'entrée d'adresse d'un dispositif de mémoire à semiconducteurs.

5

10

15

20

25

30

D'une manière générale, dans un dispositif de mémoire à semiconducteurs, une mémoire-tampon d'entrée d'adresse est utilisée pour convertir une donnée d'entrée d'adresse d'un niveau logique transistor-transistor (TTL) en une donnée d'entrée d'adresse d'un niveau d'un semiconducteurs métal-oxyde complémentaire (CMOS), et accroître la marge de bruit. Cependant, dans un dispositif de mémoire à semiconducteurs, lorsque la capacité du dispositif de mémoire augmente, le nombre d'adresses augmente et deux fois plus de mémoires-tampons d'entrée d'adresse que d'adresses sont nécessaires. Ainsi, le nombre de mémoirestampons d'entrée d'adresse est ordinairement le double du nombre d'adresses ; la moitié est utilisée en tant que mémoires-tampons d'adresse de colonne et le reste en tant que mémoires-tampons d'adresse de rangée. Par conséquent, le nombre d'adresses est augmenté selon l'accroissement de la capacité du dispositif de mémoire à semiconducteurs, et avec plus d'adresses le nombre des mémoires-tampons d'entrée d'adresse s'élève, qui nécessite une surface d'implantation accrue.

Le but de la présente invention est de proposer une nouvelle mémoire-tampon d'entrée d'adresse simplifiée apte à réduire la surface d'implantation occupée par la mémoire-tampon d'entrée d'adresse.

Un autre but de la présente invention est de proposer une mémoire-tampon d'entrée d'adresse apte à améliorer une caractéristique d'entrée.

Afin d'atteindre les buts précités, la mémoiretampon d'entrée d'adresse de la présente invention comporte

une borne d'entrée d'adresse, un moyen de commutation

d'adresse de rangée, un moyen de commutation d'adresse

de colonne, une bascule d'adresse de rangée reliée au

moyen de commutation d'adresse de rangée, une bascule

d'adresse de colonne reliée au moyen de commutation d'adresse de colonne, et une mémoire-tampon d'entrée reliée

à la borne d'entrée d'adresse, au nœud commun du moyen

de commutation d'adresse de rangée et au moyen de commutation d'adresse de colonne, et commandée par un signal de

commande de mémoire-tampon d'entrée.

5

10

15

30

La présente invention sera mieux comprise en se référant à la description détaillée qui va suivre de modes de réalisation particuliers, en référence aux dessins annexés sur lesquels :

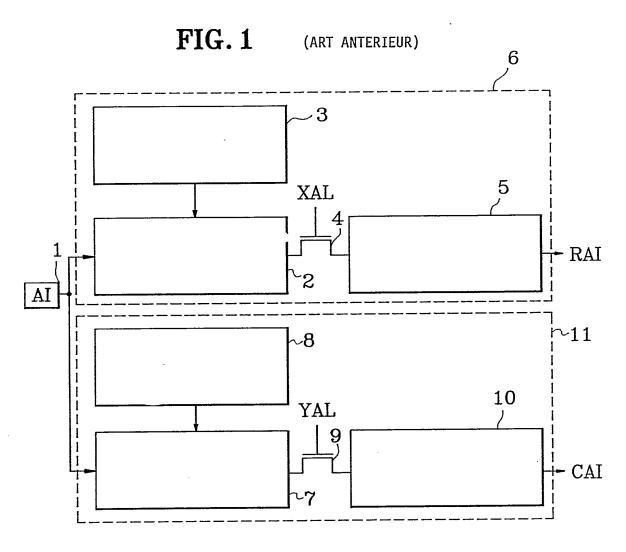

la Figure l représente un schéma synoptique d'une mémoire-tampon d'entrée d'adresse classique.

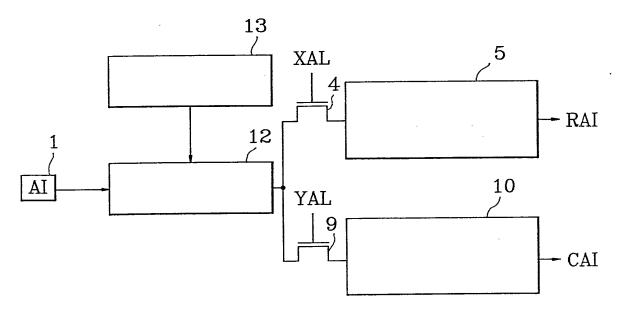

La Figure 2 représente un schéma synoptique d'une 20 mémoire-tampon d'entrée d'adresse selon la présente invention.

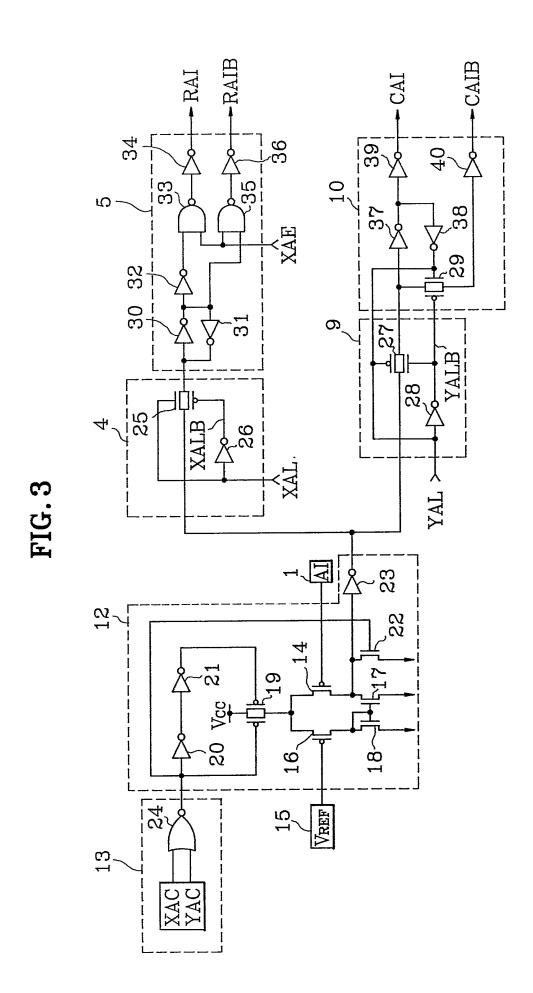

La Figure 3 est un schéma de circuit illustrant un mode de réalisation de la mémoire-tampon d'entrée d'adresse représentée sur la Figure 2.

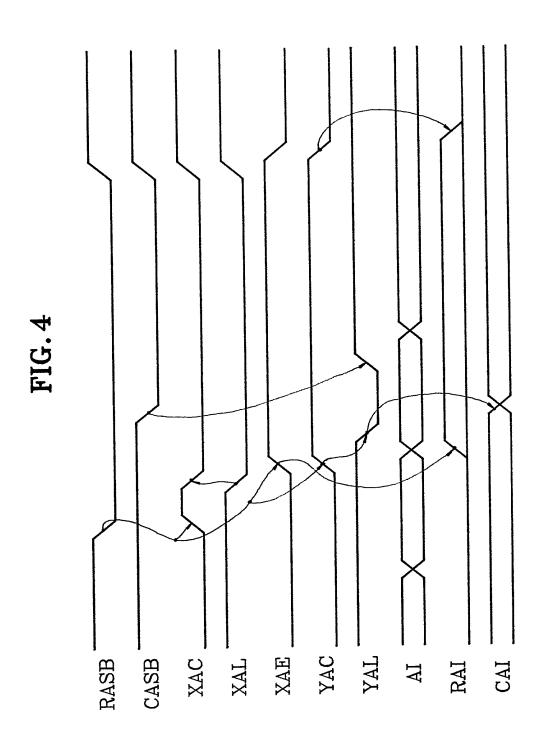

25 La Figure 4 représente un diagramme temporel expliquant le fonctionnement du circuit de la Figure 2.

Avant de décrire une mémoire-tampon d'entrée d'adresse de la présente invention, une mémoire-tampon d'entrée d'adresse classique sera décrite ci-après en référence aux dessins annexés.

5

1.0

15

20

25

La Figure 1 représente un schéma synoptique d'une mémoire-tampon d'entrée d'adresse classique.

En référence à la Figure 1, la mémoire-tampon d'entrée d'adresse classique d'un dispositif de mémoire à semiconducteurs comporte des moyens de génération d'adresse de rangée 6 et des moyens de génération d'adresse de colonne 11. Les moyens de génération d'adresse de rangée 6 comporte une mémoire-tampon d'entrée d'adresse de rangée 2 reliée à une borne d'entrée d'adresse 1, des moyens de génération de signal de commande de mémoiretampon d'entrée d'adresse de rangée 3 commandant la mémoire-tampon d'entrée d'adresse de rangée 2, un transistor du commutation d'adresse de rangée 4 commuté par un signal de bascule d'adresse de rangée XAL, et une bascule d'adresse de rangée 5 reliée au transistor de commutation d'adresse de rangée 4, de manière à générer un signal d'entrée d'adresse de rangée RAI. Par ailleurs, des moyens de génération d'adresse de colonne 11 comportent une mémoiretampon d'entrée d'adresse de colonne 7 reliée à une borne d'entrée d'adresse 1, des moyens de génération de signal de commande de mémoire-tampon d'entrée d'adresse de colonne 8 pour commander la mémoire-tampon d'entrée d'adresse de colonne 7, un transistor de commutation d'adresse de colonne 9 commuté par un signal de bascule d'adresse de colonne YAL, et une bascule d'adresse de colonne 10 reliée au transistor de commutation d'adresse de colonne 9, de manière à générer un signal d'entrée d'adresse de colonne CAI.

Par conséquent, la mémoire-tampon d'entrée d'a-30 dresse de rangée 2 et la mémoire-tampon d'entrée d'adresse de colonne 7 sont séparées, ce qui accroîtra la surface d'implantation durant une intégration. La Figure 2 représente un schéma synoptique d'une mémoire-tampon d'entrée d'adresse selon la présente invention.

En référence à la Figure 2, cette mémoire-tampon d'entrée d'adresse comporte une borne d'entrée d'adresse 5 1, un moyen de génération de signal de commande de mémoiretampon d'entrée 13 commandant une mémoire-tampon d'entrée 12 reliée à la borne d'entrée d'adresse l, un transistor de commutation d'adresse de rangée 4 commandé par un signal de bascule d'adresse de rangée XAL et relié à la mémoire-10 tampon d'entrée 12, à une bascule d'adresse de rangée 5 reliée au transistor de commutation d'adresse de rangée 4 pour délivrer un signal d'entrée d'adresse de rangée RAI, un transistor de commutation d'adresse de colonne 9 commandé par un signal de bascule d'adresse de colonne 15 YAL et relié à la mémoire-tampon d'entrée 12, et une bascule d'adresse de colonne 10 reliée à un transistor de commutation d'adresse de colonne 9 pour délivrer un signal d'entrée d'adresse de colonne CAI.

20 Le fonctionnement selon la structure précitée est le suivant.

25

La mémoire-tampon d'entrée 12 fonctionne en réponse à un signal de commande provenant du moyen de génération de signal de commande de mémoire-tampon d'entrée 13. Des données d'adresse de niveau TTL introduites depuis la borne d'entrée d'adresse l sont converties en données d'adresse de niveau CMOS par l'intermédiaire de la mémoire-tampon d'entrée.

Avec le signal XAL actif, la bascule d'adresse 30 de rangée 5 reçoit le signal de sortie de la mémoire-tampon d'entrée 12 par l'intermédiaire du transistor de commutation d'adresse de rangée 4 et délivre un signal d'entrée d'adresse RAI. Avec le signal YAL actif, la bascule d'adresse de colonne 10 reçoit le signal de sortie de la mémoire-tampon d'entrée 12 par l'intermédiaire du transistor de commutation d'adresse de colonne 9 et ensuite délivre un signal d'entrée d'adresse de colonne CAI. Ici, lorsque le signal de bascule d'adresse de rangée XAL se trouve dans l'état actif, le signal de bascule d'adresse de colonne YAL est inactif, tandis que lorsque le signal de bascule d'adresse de colonne YAL est inactif, le signal de bascule d'adresse de colonne YAL est actif, le signal de bascule d'adresse de colonne YAL est actif, le signal de bascule de rangée XAL est inactif.

5

10

15

20

25

30

La Figure 3 représente un mode de réalisation de la mémoire-tampon d'entrée d'adresse de la Figure 2 selon la présente invention.

Sur la Figure 3, la mémoire-tampon d'entrée 12 comporte un transistor PMOS 14 ayant son électrode de commande reliée à la borne d'entrée d'adresse 1, le transistor PMOS 16 ayant son électrode de source reliée en commun à l'électrode de source du transistor PMOS 14 et son électrode de grille est alimentée par une tension constante (Vref) 15, le transistor NMOS 17 ayant son électrode de drain reliée à l'électrode de drain du transistor PMOS 14 et son électrode de source reliée au potentiel de masse, le transistor NMOS 18 ayant son électrode de drain reliée à l'électrode de drain du transistor PMOS 16, son électrode de source reliée au potentiel de la masse et son électrode de grille reliée en commun à son électrode de drain et à l'électrode de grille du transistor NMOS 17, deux transistors PMOS 19 ayant leurs électrodes de drain reliées aux électrodes de source des transistors PMOS 14 et 16 et leurs électrodes de source reliées à une tension d'alimentation Vcc, et un inverseur 20 ayant sa borne d'entrée reliée à une électrode de grille des

transistors PMOS 19, un inverseur 21 ayant sa borne de sortie reliée à l'autre électrode de grille destransistors PMOS 19, sa borne d'entrée reliée à la sortie du premier inverseur 20, un transistor NMOS 22 ayant son électrode de grille également reliée à la borne d'entrée de l'inverseur 20, son électrode de drain reliée à l'électrode de drain du transistor NMOS 17 et son électrode de source est reliée au potentiel de la masse, et un inverseur 23 ayant sa borne d'entrée reliée au drain du transistor NMOS 22.

5

10

15

20

25

30

Le moyen de génération d'un signal de commande de mémoire-tampon d'entrée 13 est constitué d'une porte NON OU 24 recevant un signal de commande d'adresse de rangée XAC et un signal de commande de colonne YAC, et ayant sa borne de sortie reliée à la borne d'entrée de l'inverseur 20 de la mémoire-tampon d'entrée 12.

Le transistor de commutation d'adresse de rangée 4 est constitué d'un inverseur 26 et d'une porte de transfert CMOS 25 comprenant un transistor NMOS appliquant un signal de bascule d'adresse de rangée XAL à son électrode de grille, et un transistor PMOS appliquant un signal de bascule d'adresse de rangée inversé XALB inversé par l'inverseur 26 à son électrode de grille, et ayant son côté d'entrée relié à la sortie de l'inverseur 23.

Le transistor de commutation d'adresse de colonne 9 est constitué d'un inverseur 28 et d'une porte de transfert CMOS 24 comprenant un transistor PMOS appliquant un signal de bascule d'adresse de colonne YAL à son électrode de grille et un transistor NMOS appliquant un signal de bascule d'adresse de colonne inversé YALB inversé par l'inverseur 28 à son électrode de grille et ayant son côté d'entrée également relié à la sortie de l'inverseur 23.

5

10

15

20

25

30

Le circuit de bascule d'adresse de rangée 5 comporte un inverseur 30 ayant sa borne d'entrée reliée au côté de sortie de la porte de transfert 25 du transistor de commutation d'adresse de rangée 4, un inverseur 31 ayant sa borne d'entrée reliée à la borne de sortie de l'inverseur 30 et sa borne de sortie reliée à l'entrée de l'inverseur 30, un inverseur 32 ayant sa borne d'entrée reliée à la borne de sortie de l'inverseur 30, une porte NON ET 33 recevant un signal de sortie de l'inverseur 32 et un signal de validation d'adresse de rangée XAE, un inverseur 34 connecté en série à la porte NON ET 33 et délivrant ensuite un signal d'entrée d'adresse de rangée RAI, une porte NON ET 35 recevant un signal de sortie de l'inverseur 30 et un signal de validation d'adresse de rangée XAE, et un inverseur 36 connecté en série à la porte NON ET 35 et délivrant ensuite un signal d'entrée d'adresse de rangée inversé RAIB.

Le circuit de bascule d'adresse de colonne 10 comporte une porte de transfert CMOS 29 ayant son côté d'entrée relié au côté de sortie de la porte de transfert CMOS 27 et constituée d'un transistor NMOS ayant son électrode de grille reliée au signal de bascule d'adresse de colonne YAL, d'un transistor PMOS ayant son électrode de grille reliée au signal de bascule d'adresse de colonne inversé YALB inversé par un inverseur 28 ; un inverseur 37 ayant sa borne d'entrée reliée au côté de sortie de la porte de transfert CMOS 27 du transistor de commutation adresse de colonne 9 ; un inverseur 38 ayant sa borne d'entrée reliée à la borne de sortie de l'inverseur 37 et sa borne de sortie reliée à une électrode de grille du transistor NMOS de la porte de transfert CMOS 29 ; un inverseur 39 ayant sa borne d'entrée reliée à la borne de sortie de l'inverseur 37 et délivrant un signal d'entrée d'adresse de colonne CAI, et un inverseur 40 ayant

sa borne d'entrée reliée au côté de sortie de la porte de transfert CMOS et délivrant un signal d'entrée d'adresse de colonne inversé CAIB.

En référence à la Figure 4, le fonctionnement de la mémoire-tampon d'entrée d'adresse réalisée comme ci-5 dessus sera expliqué ci-après. Lorsqu'un signal d'échantillonnage d'adresse de rangée inversé RASB est généré, le signal de commande d'adresse de colonne XAC devient haut durant la transition descendante du signal d'échantillonnage d'adresse de rangée inversé RASB. Le signal de 10 commande d'adresse de colonne YAC devient haut plus tard que le signal de commande d'adresse de rangée XAC. Lorsque le signal de commande d'adresse de colonne YAC devient haut, le signal de sortie de la porte NON ET 24 devient bas. La porte de transfert 19 constituée des deux tran-15 sistors PMOS devient passante. Simultanément, le transistor NMOS 22 est rendu non conducteur. Ici, les inverseurs 20 et 21 génèrent un retard pour réduire le courant de crête généré lorsque les deux transistors PMOS deviennent conducteurs. 20

Recevant une tension constante (Vref) 15 sur son électrode de grille, le transistor PMOS 16 devient conducteur et son électrode de drain devient haute. Lorsque cette tension logique "haute" est appliquée aux électrodes de grille des transistors NMOS 17 et 18, les transistors NMOS 17 et 18 conduisent.

25

30

Lorsqu'une entrée d'adresse logique "haute" provenant de la borne d'entrée d'adresse l'est reçue, le transistor PMOS 14 est rendu non conducteur et l'électrode de drain du transistor NMOS 17 devient basse. Si une entrée d'adresse logique "basse" est reçue, le transistor PMOS 14 est rendu conducteur et l'électrode de drain du

transistor NMOS 17 devient haute.

5

10

L'inverseur 23 inverse le signal de l'électrode de drain du transistor NMOS 17 pour générer des signaux d'entrée d'adresse tamponnés. Ainsi, lorsqu'elle reçoit un signal d'entrée d'adresse de niveau TTL, la mémoiretampon d'entrée 12 génère un signal d'entrée d'adresse de niveau CMOS.

Dans le transistor de commutation d'adresse de rangée 4, lorsque le signal d'adresse de rangée XAL tombe à un niveau logique "bas", le signal de commande d'adresse de rangée XAC tombe également à un niveau loqique "bas". Lorsqu'un signal de bascule d'adresse de rangée "haut" XAL est reçu, la porte de transfert CMOS 25 signal de sortie de l'inverseur 23 à transfère le un circuit bascule constitué des inverseurs 30 et 31. Le 15 signal transféré est ensuite inversé par l'inverseur 32. Le signal de validation d'adresse de rangée XAE devient haut plus tard que le signal de commande d'adresse de rangée XAC par un signal d'échantillonnage d'adresse de rangée inversé RASB. Si le signal de sortie de l'inverseur 20 32 se trouve à un état logique "haut" lorsque le signal de validation d'adresse de rangée XAE est haut, le signal de sortie RAI de l'inverseur 34 par l'intermédiaire de la porte NON ET 33 devient haut, et le signal de sortie RAIB de l'inverseur 36 par l'intermédiaire de la porte 25 NON ET 35 devient bas. Le signal de commande d'adresse de colonne YAC devient haut plus tard que le signal de validation d'adresse de rangée XAE lorsque le signal d'échantillonnage d'adresse de rangée inversé RASB devient 30 bas.

La mémoire-tampon d'entrée 12 fonctionne lorsque le signal de commande d'adresse de colonne YAC est

haut. Lorsqu'un signal logique d'entrée d'adresse de colonne "haut" provenant de la borne d'entrée d'adresse l est reçu, l'inverseur 23 de la mémoire-tampon d'entrée 12 délivre un signal logique "haut". Durant une transition 5 ascendante du signal de commande d'adresse de colonne YAC, le signal de bascule d'adresse de colonne YAL est retardé d'un niveau haut à un niveau bas. Les portes de transfert NMOS 27 et 29 sont rendues conductrices lorsque le signal de bascule d'adresse de colonne YAL est bas, de sorte que les inverseurs 37 et 39 délivrent un signal 10 d'entrée d'adresse de colonne CAI sous la forme d'un signal logique "haut" et l'inverseur 40 délivre un signal d'entrée d'adresse de colonne inversé CAIB sous la forme d'un signal logique de niveau "bas". Le signal de bascule d'adresse de colonne YAL devient haut lorsque le signal 15 d'échantillonnage d'adresse de colonne inversé CASB tombe à un niveau logique "bas". Le signal d'entrée d'adresse de rangée RAI et le signal d'entrée d'adresse de rangée inversé RAIB demeurent inchangés jusqu'à ce que le signal de validation d'adresse de rangée XAE tombe à 20 un niveau logique "bas".

Selon l'art antérieur, dans une mémoire-tampon d'entrée d'adresse, lorsque le nombre d'adresses est N, N mémoires-tampons d'entrée d'adresse de colonne et N mémoires-tampons d'entrée d'adresse de rangée sont nécessaires, ce qui veut dire que 2N mémoires-tampons d'entrée d'adresse sont nécessaires. Si une mémoire-tampon d'entrée est implantée selon la largeur du trait dans une DRAM à 64 Mbits,  $180000~\mu\text{m}^2$  sont nécessaires, du fait que 26 mémoires-tampons d'entrée d'adresse sont nécessaires si l'on suppose que la surface occupée par une mémoire-tampon d'entrée d'adresse est  $120~x~60~\mu\text{m}^2$ .

25

30

Cependant, la mémoire-tampon d'entrée d'adresse

selon la présente invention utilise seulement N mémoires-tampons d'entrée d'adresse en réunissant une mémoire-tampon d'entrée d'adresse de colonne et une mémoire-tampon d'entrée d'adresse de colonne en une mémoire-tampon d'entrée d'adresse, réduisant ainsi la surface d'implantation occupée par une mémoire-tampon d'adresse de moitié. C'est-à-dire que dans le cas de DRAM de 64 Mbits, la surface peut être réduite à environ 90000  $\mu\text{m}^2$ . Egalement, en commandant une adresse de colonne et une adresse de rangée avec une seule mémoire-tampon d'entrée, un signal d'entrée d'adresse de colonne ayant les mêmes caractéristiques sont obtenus, améliorant ainsi la caractéristique du circuit intégré global.

### REVENDICATIONS

1. Mémoire-tampon d'entrée d'adresse dans un dispositif de mémoire à semiconducteurs, caractérisée en ce qu'elle comporte :

une borne d'entrée d'adresse (1),

5

10

15

20

25

30

des moyens formant mémoire-tampon d'entrée (12) reliés à ladite borne d'entrée d'adresse (1) pour recevoir un signal d'adresse de colonne en réponse à un premier état d'un premier signal de commande, recevoir un signal d'adresse de rangée en réponse à un second état d'un second signal de commande et tamponner lesdits signaux d'adresse de colonne et de rangée,

des moyens de commutation d'adresse de rangée (4) reliés à la borne de sortie desdits moyens formant mémoire-tampon d'entrée (12) pour transférer ledit signal d'adresse tamponné en réponse à un premier signal passant au second état avant que ledit premier signal de commande passe au second état,

des moyens formant bascule d'adresse de rangée (5) reliés auxdits moyens de commutation d'adresse de colonne (9) en réponse à un second signal passant au premier état après que ledit premier signal est passé au second état,

des moyens de commutation d'adresse de colonne (9) reliés à la borne de sortie desdits moyens formant mémoire-tampon d'entrée (12) en réponse à un troisième signal passant au second état après que ledit second signal de commande est passé au premier état, et

des moyens formant bascule d'adresse de colonne (10) reliés auxdits moyens de commutation d'adresse de colonne (9), ladite mémoire-tampon d'entrée d'adresse (12) recevant, par l'intermédiaire desdits moyens de commutation d'adresse de rangée (4), le premier signal passant au second état avant qu'un signal d'entrée d'adresse

soit tamponné, recevant, par lesdits moyens formant bascule d'adresse de rangée (5), le second signal passant au premier état après que ledit premier signal est passé au second état, et recevant, par l'intermédiaire desdits moyens de commutation d'adresse de colonne (9), le troisième signal passant au second état après que ledit second signal de commande est passé au premier état.

5

10

20

25

30

2. Mémoire-tampon d'entrée d'adresse selon la revendication l, caractérisée en ce que lesdits moyens formant mémoire-tampon d'entrée (12) comportent :

un premier transistor PMOS (14) ayant une électrode de grille reliée à ladite borne d'entrée d'adresse (1),

un second transistor PMOS (16) ayant une électrode de source reliée en commun à l'électrode de source dudit premier transistor PMOS (14) et son électrode de grille alimentée par une tension constante,

un premier transistor NMOS (17) ayant une électrode de drain reliée à l'électrode de drain dudit premier transistor PMOS (14) et une électrode de source reliée à un potentiel de masse,

un second transistor NMOS (18) ayant une électrode de drain reliée à l'électrode de drain dudit second transistor PMOS (16), une électrode de source reliée à un potentiel de masse et une électrode de grille reliée en commun à son électrode de drain et à l'électrode de grille dudit premier transistor NMOS (17),

deux troisièmes transistors PMOS (19) ayant des électrodes de drain reliées aux électrodes de source desdits premier et second transistors PMOS (14) et (19) et des électrodes de source reliées à une tension d'alimentation.

un cinquième inverseur (20) ayant une borne d'entrée reliée à l'électrode de grille d'un desdits

troisièmes transistors PMOS (19), un second inverseur (21) ayant une borne de sortie reliée à l'électrode de grille de l'autre desdits troisièmes transistors PMOS (19), et une borne d'entrée reliée à la borne de sortie dudit premier inverseur (20),

5

10

30

un troisième transistor NMOS (22) ayant une électrode de grille reliée à la borne d'entrée dudit premier inverseur (20), une électrode de drain reliée à l'électrode de drain dudit premier transistor NMOS (17) et une électrode de source reliée à un potentiel de masse et

un troisième inverseur (23) ayant une borne d'entrée reliée à l'électrode de drain dudit troisième transistor NMOS (22).

- 3. Mémoire-tampon d'entrée d'adresse selon la revendication 2, caractérisée en ce que lesdits moyens formant

mémoire-tampon d'entrée (12) comportent en outre un moyen

logique (24) qui reçoit le premier signal de commande et

le second signal de commande, délivre ledit premier état

lorsqu'un des deux signaux se trouve dans le premier état,

et dont la borne de sortie est reliée à la borne d'entrée

dudit premier inverseur (20).

- 4. Mémoire-tampon d'entrée d'adresse selon la revendication 3, caractérisée en ce que lesdits moyens de commutation d'adresse de rangée (4) comportent :

- un quatrième inverseur (26) pour inverser ledit premier signal,

une première porte de transfert CMOS (25) comprenant un quatrième transistor NMOS appliquant le premier signal à son électrode de grille et un quatrième transistor PMOS reliant son électrode de grille audit premier signal inversé par un quatrième inverseur (26), et dans laquelle sa borne d'entrée est reliée à la borne de sortie dudit troisième inverseur (23). 5. Mémoire-tampon d'entrée d'adresse selon la revendication 4, caractérisée en ce que lesdits moyens formant bascule d'adresse de rangée (5) comportent :

un cinquième inverseur (30) relié à la borne de sortie de ladite première porte de transfert (25),

5

20

un sixième inverseur (31) ayant une borne d'entrée reliée à la borne de sortie dudit cinquième inverseur (30) et une borne de sortie reliée à la borne d'entrée dudit cinquième inverseur (30),

10 un septième inverseur (32) ayant une borne d'entrée reliée audit cinquième inverseur (30),

une première porte NON ET (33) recevant le signal de sortie dudit septième inverseur (32) et le troisième signal,

un huitième inverseur (34) relié à la borne de sortie de ladite première porte NON ET (33) pour délivrer un signal d'entrée d'adresse de rangée,

une seconde porte NON ET (35) recevant le signal de sortie dudit cinquième inverseur (30) et ledit troisième signal, et

un neuvième inverseur (36) relié à la borne de sortie de ladite seconde porte NON ET (35) pour délivrer un signal d'entrée d'adresse de rangée inversé.

Mémoire-tampon d'entrée d'adresse selon la reven dication 5, caractérisée en ce que lesdits moyens de commutation d'adresse de colonne (9) comportent :

un dixième inverseur (28) pour inverser ledit second signal, et

une seconde porte de transfert CMOS (27) compre-30 nant un cinquième transistor PMOS ayant une électrode de grille recevant ledit second signal et un cinquième transistor NMOS ayant une électrode de grille recevant ledit second signal inversé par ledit dixième inverseur (28). 7. Mémoire-tampon d'entrée d'adresse selon la revendication 6, caractérisée en ce que lesdits moyens formant bascule d'adresse de colonne (10) comportent :

une troisième porte de transfert CMOS (29) comprenant un sixième transistor NMOS (27) ayant une électrode de grille recevant ledit second signal et un sixième transistor PMOS ayant une électrode de grille recevant ledit second signal inversé par ledit dixième inverseur (28), et ladite troisième porte de transfert CMOS (29) ayant une borne d'entrée reliée à la borne de sortie de ladite seconde porte de transfert CMOS (27),

5

10

15

20

un onzième inverseur (37) ayant sa borne d'entrée reliée au côté sortie de ladite seconde porte de transfert CMOS (27) du transistor de commutation d'adresse de colonne (9).

un douzième inverseur (38) ayant une borne d'entrée reliée à la sortie dudit onzième inverseur (37) et une borne de sortie reliée à une électrode de grille du sixième transistor NMOS de ladite troisième porte de transfert CMOS (29),

un treizième inverseur (39) ayant une borne d'entrée reliée à la borne de sortie dudit onzième inverseur (37) et délivrant un signal d'entrée d'adresse de colonne, et

un quatorzième inverseur (40) ayant sa borne d'entrée reliée à la borne de sortie de ladite troisième porte de transfert CMOS (29) et délivrant un signal d'entrée d'adresse de colonne inversé.

8. Mémoire-tampon d'entrée d'adresse d'un dispositif 30 de mémoire à semiconducteurs, caractérisée en ce qu'elle comporte :

une borne d'entrée d'adresse (1), des moyens de commutation d'adresse de colonne (9), des moyens de commutation d'adresse de rangée (4),

des moyens formant bascule d'adresse de colonne (10) reliés auxdits moyens de commutation d'adresse de colonne (9),

5

10

20

25

30

des moyens formant bascule d'adresse de rangée (5) reliés auxdits moyens de commutation d'adresse de rangée (4), et

une mémoire-tampon d'entrée (12) reliée à ladite borne d'entrée d'adresse (1), au au nœud commun desdits moyens de commutation d'adresse de colonne (9) et auxdits moyens de commutation d'adresse de rangée (4), et commandée par un signal de commande de mémoire-tampon d'entrée.

9. Mémoire-tampon d'entrée d'adresse selon la reven-15 dication 8, caractérisée en ce que ladite mémoire-tampon d'entrée (12) comporte :

des moyens de génération de signaux de commande (13) recevant des signaux de commande d'adresse de colonne et de rangée et délivrant un signal au-dessous du premier état lorsqu'un des deux signaux présente le premier état,

un premier transistor PMOS (14) ayant une électrode de grille reliée à ladite borne d'entrée,

un second transistor PMOS (16) ayant une électrode de source reliée en commun à l'électrode de source dudit premier transistor PMOS (14) et délivrant une tension constante à son électrode de grille,

un premier transistor NMOS (17) ayant une électrode de drain reliée à l'électrode de drain dudit transistor PMOS (14) et une électrode de source reliée à un potentiel de masse,

un second transistor NMOS (18) ayant une électrode de drain reliée à l'électrode de drain dudit second transistor PMOS (16), une électrode de source reliée au potentiel de la masse, et une électrode de grille reliée en commun à son électrode de drain et à l'électrode de grille dudit premier transistor NMOS (17),

deux troisièmes transistors PMOS (19) ayant des électrodes de drain reliées aux électrodes de source desdits premier et second transistors PMOS (14) et (16) et des électrodes de source reliées à une tension d'alimentation,

5

10

20

25

un premier inverseur (20) ayant une borne d'entrée reliée à l'électrode de grille de l'un desdits troisièmes transistors PMOS (19),

un second inverseur (21) ayant une borne d'entrée reliée à la borne de sortie dudit premier inverseur (20) et une borne de sortie reliée à l'électrode de grille de l'autre desdits troisièmes transistors PMOS (19),

un troisième transistor NMOS (22) ayant une 15 électrode de grille reliée à la borne d'entrée dudit premier inverseur (20) et une électrode de drain reliée à l'électrode de drain dudit premier transistor NMOS (17), et

un troisième inverseur (23) ayant une borne d'entrée reliée au drain dudit troisième transistor NMOS (22).

- Mémoire-tampon d'entrée d'adresse, caractérisée en ce qu'elle comporte une mémoire-tampon d'entrée (12) pour entrer une adresse de rangée et une adresse de colonne provenant d'une borne d'entrée d'adresse (1) en réunissant une mémoire-tampon d'entrée d'adresse de ranqée (2) pour entrer ladite adresse de rangée provenant de ladite borne d'entrée d'adresse (1) et une mémoiretampon d'entrée d'adresse de colonne (7) pour entrer ladite adresse de colonne provenant de ladite borne 30 d'entrée d'adresse (1).

- Mémoire-tampon d'entrée d'adresse selon la reven-11. dication 10, caractérisée en ce que ladite mémoire-tampon

d'entrée comporte :

5

10

15

20

25

30

35

des moyens de génération de signaux de commande (13) recevant un signal de commande d'adresse de colonne et un signal de commande d'adresse de rangée et délivrant un signal au-dessous du premier état lorsque l'un des deux signaux présente le premier état,

un premier transistor PMOS (14) ayant une électrode de grille reliée à ladite borne d'entrée d'adresse,

un second transistor PMOS (16) ayant une électrode de source reliée en commun à l'électrode de source dudit premier transistor PMOS (14) et délivrant une tension constante à son électrode de grille,

un premier transistor NMOS (17) ayant une électrode de drain reliée à l'électrode de drain dudit transistor PMOS (14) et une électrode de source reliée à un potentiel de masse,

un second transistor NMOS (18) ayant une électrode de drain reliée à l'électrode de drain dudit second transistor PMOS (16), une électrode de source reliée au potentiel de masse, et une électrode de grille reliée en commun à son électrode de drain et à l'électrode de grille dudit premier transistor NMOS (17),

deux troisièmes transistors PMOS (19) ayant des électrodes de drain reliées aux électrodes de source desdits premier et second transistors PMOS (14) et (16) et des électrodes de source reliées à une tension d'alimentation.

un premier inverseur (20) ayant une borne d'entrée reliée à l'électrode de grille de l'un desdits troisièmes transistors PMOS (19),

un second inverseur (21) ayant une borne d'entrée reliée à la borne de sortie dudit premier inverseur (20) et une borne de sortie reliée à l'électrode de grille de l'autre desdits troisièmes transistors PMOS (19),

un troisième transistor NMOS (22) ayant une élec-

trode de grille reliée à la borne d'entrée dudit premier inverseur (20) et une électrode de drain reliée à l'électrode de drain dudit premier transistor NMOS (17), et un troisième inverseur (23) ayant une borne d'entrée reliée au drain dudit troisième transistor NMOS (22).

FIG. 2

INSTITUT NATIONAL

PROPRIETE INDUSTRIELLE

### RAPPORT DE RECHERCHE

Nº d'enregistrement national

de la

1

établi sur la base des dernières revendications déposées avant le commencement de la recherche

FR 9202652 468621 FA

| atégorie                                                                                                                                                                                                                                                                                                                     | Citation du document avec indication, en cas de des parties pertinentes                                                                     | besoin,            | de la demande<br>examinée                                                                                                                                |                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| (                                                                                                                                                                                                                                                                                                                            | US-A-4 104 733 (SATOH)  * colonne 4, ligne 5 - colonne 48; revendication 1; figures 1-                                                      | 8, ligne<br>-3 *   | 1,8,10                                                                                                                                                   |                                            |

|                                                                                                                                                                                                                                                                                                                              | US-A-4 879 681 (MIWA ET AL) * colonne 8, ligne 12 - ligne 4                                                                                 | 6; figure 1        | 2,9,11                                                                                                                                                   |                                            |

|                                                                                                                                                                                                                                                                                                                              | EP-A-0 206 928 (THOMSON COMPONE CORPORATION) * figure 1 *                                                                                   | ENTS-MOSTEK        | 4-7                                                                                                                                                      |                                            |

|                                                                                                                                                                                                                                                                                                                              | WESTE N H E & ESHRAGHIAN K 'Pri<br>CMOS VLSI design'<br>Octobre 1985 , ADDISON-WESLEY ,<br>US<br>* page 212, ligne 1 - page 214,            | READING,           | 4-7                                                                                                                                                      |                                            |

| <b>\</b>                                                                                                                                                                                                                                                                                                                     | figure 5.50A *  IEEE INTERNATIONAL SOLID STATE CONFERENCE. 15 Février 1979, NE pages 142 - 143 LEE ET AL 'A 80ns 5V-only Dynam * figure 2 * | W YORK US          | 2,9,11                                                                                                                                                   | DOMAINES TECHNIQUES RECHERCHES (Int. Cl.5) |

|                                                                                                                                                                                                                                                                                                                              | <b></b>                                                                                                                                     |                    |                                                                                                                                                          |                                            |

|                                                                                                                                                                                                                                                                                                                              |                                                                                                                                             |                    |                                                                                                                                                          |                                            |

|                                                                                                                                                                                                                                                                                                                              | Date d'achiveme                                                                                                                             | nt de la recherche |                                                                                                                                                          | Examinateur                                |

| 04 JANVIER 1993                                                                                                                                                                                                                                                                                                              |                                                                                                                                             |                    |                                                                                                                                                          | CUMMINGS A.                                |

| CATEGORIE DES DOCUMENTS CITES  X: particulièrement pertinent à lui seul Y: particulièrement pertinent en combinaison avec un autre document de la même catégorie A: pertinent à l'encontre d'au moins une revendication  T: théorie ou prin E: document de la det de dé de dépôt ou qu D: cité dans la de L: cité pour d'aut |                                                                                                                                             |                    | cipe à la base de l'invention<br>evet bénéficiant d'une date antérieure<br>sôt et qui n'a été publié qu'à cette date<br>à une date postérieure.<br>nande |                                            |