## (12) NACH DEM VERTRAG ÜBER DIE INTERNATIONALE ZUSAMMENARBEIT AUF DEM GEBIET DES PATENTWESENS (PCT) VERÖFFENTLICHTE INTERNATIONALE ANMELDUNG

(19) Weltorganisation für geistiges Eigentum

Internationales Büro

(43) Internationales Veröffentlichungsdatum

26. März 2015 (26.03.2015)

(10) Internationale Veröffentlichungsnummer

WO 2015/039733 A1

## (51) Internationale Patentklassifikation:

*H03K 17/16 (2006.01) H03K 17/0812 (2006.01)*

## (21) Internationales Aktenzeichen: PCT/EP2014/002413

## (22) Internationales Anmeldedatum:

5. September 2014 (05.09.2014)

## (25) Einreichungssprache: Deutsch

## (26) Veröffentlichungssprache: Deutsch

(30) Angaben zur Priorität:

10 2013 015 723.4

20. September 2013 (20.09.2013) DE

## (71) Anmelder: HOCHSCHULE REUTLINGEN [DE/DE]; Alteburgstr. 150, 72762 Reutlingen (DE).

## (72) Erfinder: PFOST, Martin; Lüftestr. 33, 72762 Reutlingen (DE). CENUSA, Marius; Kirrlestr. 17, 72768 Reutlingen (DE). RETTU, Gabriel; Rossnagelweg 9, 72762 Reutlingen (DE).

## (74) Anwälte: HUBER, Michael et al.; MÜLLER-BORE &amp; PARTNER PATENTANWÄLTE PARTG MBB, Friedenheimer Brücke 21, 80639 München (DE).

## (81) Bestimmungsstaaten (soweit nicht anders angegeben, für jede verfügbare nationale Schutzrechtsart): AE, AG, AL,

AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Bestimmungsstaaten (soweit nicht anders angegeben, für jede verfügbare regionale Schutzrechtsart): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), eurasisches (AM, AZ, BY, KG, KZ, RU, TJ, TM), europäisches (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

## Veröffentlicht:

— mit internationalem Recherchenbericht (Artikel 21 Absatz 3)

## (54) Title: IMPROVED ACTUATION FOR SWITCHING ON IGBT

## (54) Bezeichnung : VERBESSERTE ANSTEUERUNG ZUM EINSCHALTEN VON IGBT

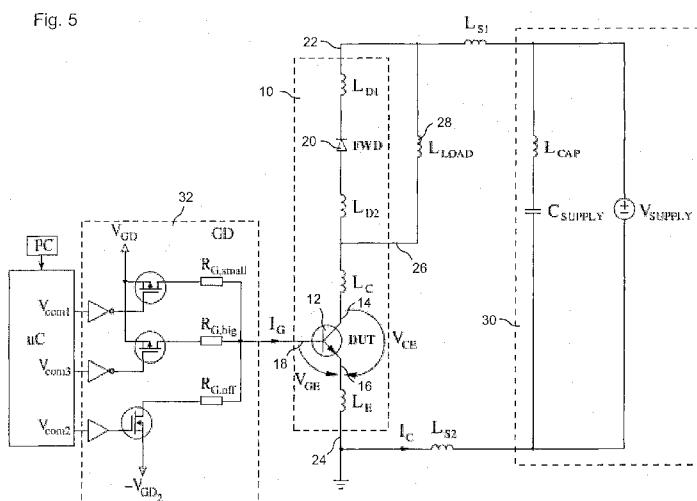

Fig. 5

(57) Abstract: The present invention relates to an improved method and an improved gate driver for actuating a power switching section that comprises at least one isolated gate bipolar transistor having a gate (18) and a collector/emitter path (14, 16) that can be switched by means of the gate and a protective diode (20) connected in series with the collector/emitter path, wherein the method comprises the following steps: from a non-conductive state of the collector/emitter path, the gate (18) is charged by means of a gate current (via  $R_{G, \text{small}}$ ) having a first polarity in order to partially enable the collector/emitter path; the gate (18) is partially discharged by means of a gate current (via  $R_{G, \text{off}}$ ) having a second polarity, opposite to the first; and the gate is charged further by means of a gate current (via  $R_{G, \text{big}}$ ) having the first polarity in order to completely enable the collector/emitter path.

(57) Zusammenfassung:

[Fortsetzung auf der nächsten Seite]

---

Die vorliegende Erfindung betrifft ein verbessertes Verfahren und einen verbesserten Gate-Treiber zur Ansteuerung eines Leistungsschaltteils, welches zumindest einen Isolated-Gate-Bipolartransistor mit einem Gate (18) und einer mittels des Gates schaltbaren Kollektor-Emitter-Strecke (14, 16) und eine zur Kollektor-Emitter-Strecke in Serie geschaltete Schutzdioden (20) umfasst, wobei das Verfahren folgende Schritte umfasst: ausgehend von einem nicht-leitenden Zustand der Kollektor-Emitter-Strecke Laden des Gates (18) mittels eines Gate-Stroms (via  $R_{G, \text{small}}$ ) einer ersten Polarität zum teilweisen Freischalten der Kollektor-Emitter-Strecke; teilweises Entladen des Gates (18) mittels eines Gate-Stroms (via  $R_{G, \text{off}}$ ) einer zweiten, zur ersten entgegengesetzten Polarität; und weiteres Laden des Gates mittels eines Gate-Stroms (via  $R_{G, \text{big}}$ ) der ersten Polarität zum vollständigen Freischalten der Kollektor-Emitter-Strecke.

**VERBESSERTE ANSTEUERUNG ZUM EINSCHALTEN VON IGBT****Beschreibung**

Die vorliegende Erfindung betrifft ein Verfahren und eine Treiberschaltung zur Ansteuerung eines Bipolartransistors mit isoliertem Steueranschluss (Gate), auch als Isolated-Gate-Bipolartransistor (IGBT) bekannt. Insbesondere wird damit ein 5 verbesserter Einschaltvorgang beim Schalten einer induktiven Last mit einer antiparallelen Schutzdiode (FWD) erreicht.

Bipolartransistoren mit isolierter Gate-Elektrode (IGBT) werden häufig zusammen mit antiparallelen Schutzdioden (FWD) in Schaltelementen der Leistungselektronik verwendet. 10 IGBTs sind heutzutage von großer Bedeutung beim Schalten mittlerer und hoher elektrischer Leistungen mit Spannungen, die von wenigen hundert bis mehrere tausend Volt mit Strömen im Bereich von einigen zehn bis mehreren hundert Ampere reichen. Damit können also elektrische Leistungen von bis zu mehreren Megawatt (MW) geschaltet werden. Eine große Herausforderung beim Schalten solcher 15 Leistungen ist die mit dem Schaltvorgang verbundene Verlustleistung und die damit im IGBT selbst dissipierte Energie aber auch eine Begrenzung der Belastung des IGBT durch Überschwingverhalten im Schaltkreis.

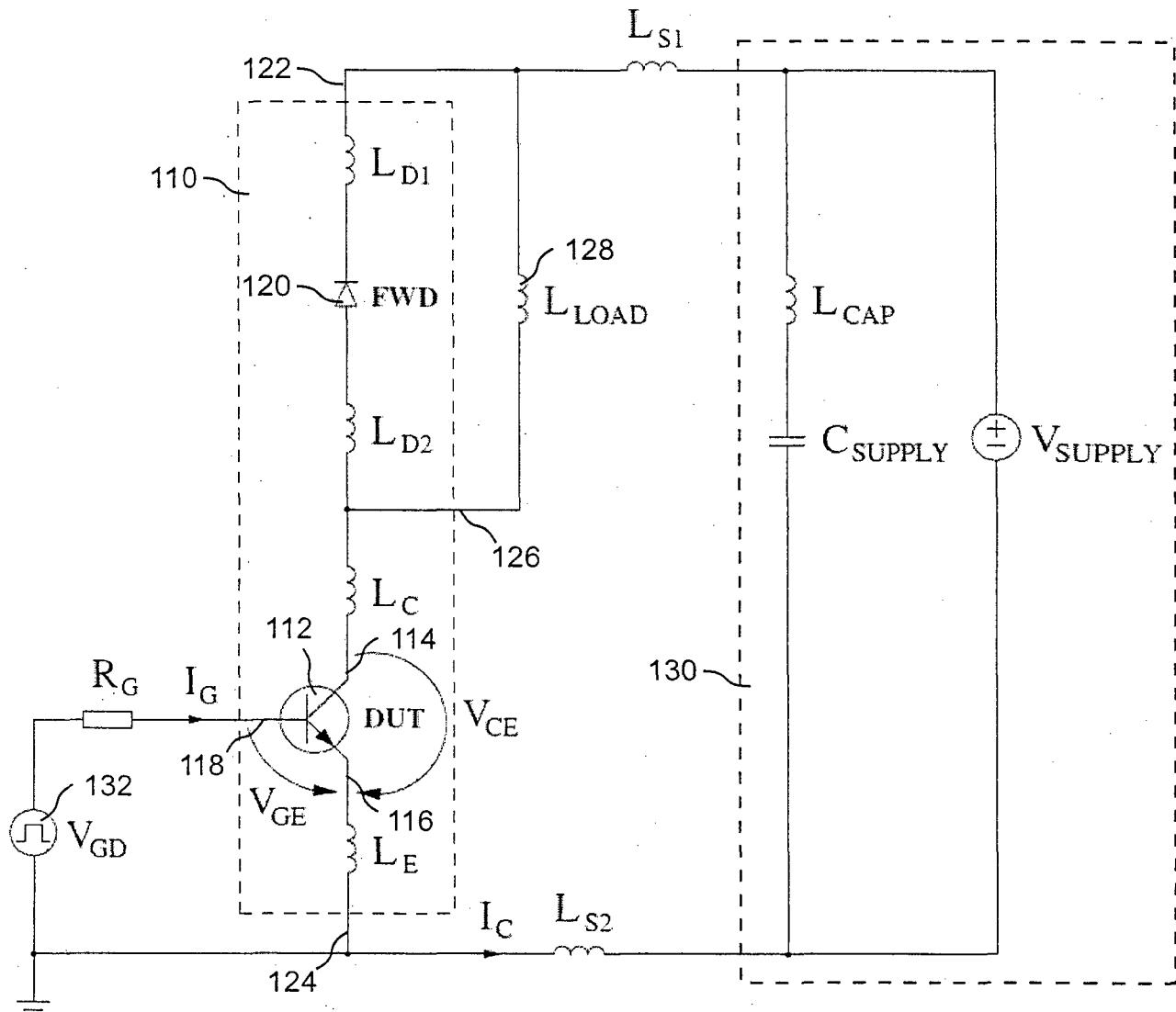

In einem Großteil der typischen Anwendungen von IGBTs werden induktive Lasten 20 mittels eines IGBT geschaltet, wie dies beispielhaft in Fig. 1 dargestellt ist. Dabei umfasst ein IGBT Modul 110 einen IGBT 112 mit einem Kollektoranschluss 114, einem Emitteranschluss 116 und einem Steueranschluss (Gate) 118 sowie eine zur Kollektor-Emitter-Strecke des IGBT in Serie geschaltete Schutzdiode (FWD, freewheeling diode) 120, welche in Sperrrichtung zu der zu schaltenden 25 Stromrichtung liegt. Die Anode der Schutzdiode 120 ist dabei zum Kollektoranschluss 114 des IGBT 112 hin verbunden während die Kathode der Schutzdiode 120 zu einem ersten Versorgungsanschluss 122 des IGBT-Moduls 110 verbunden ist. Ein

zweiter Versorgungsanschluss 124 des IGBT-Moduls 110 ist zum Emitteranschluss 116 hin verbunden. Ein Schaltausgang 126 des IGBT-Moduls 110 ist dabei zum Kollektoranschluss 114 und zur Anode der Schutzdiode hin verbunden. Damit kann eine an den ersten Versorgungsanschluss 122 und Schaltausgang 126 angeschlossene Last 128 geschaltet und mit einer elektrischen Versorgungseinrichtung 130 verbunden werden. Der Schaltvorgang wird dabei über das Gate 118 gesteuert. Dazu liefert ein Gate-Treiber 132 ein entsprechendes Steuersignal. Fig. 1 veranschaulicht außerdem schematisch einige intrinsische, parasitäre Induktivitäten  $L_{D1}$ ,  $L_{D1}$ ,  $L_C$  und  $L_E$  des IGBT-Moduls 110.

10

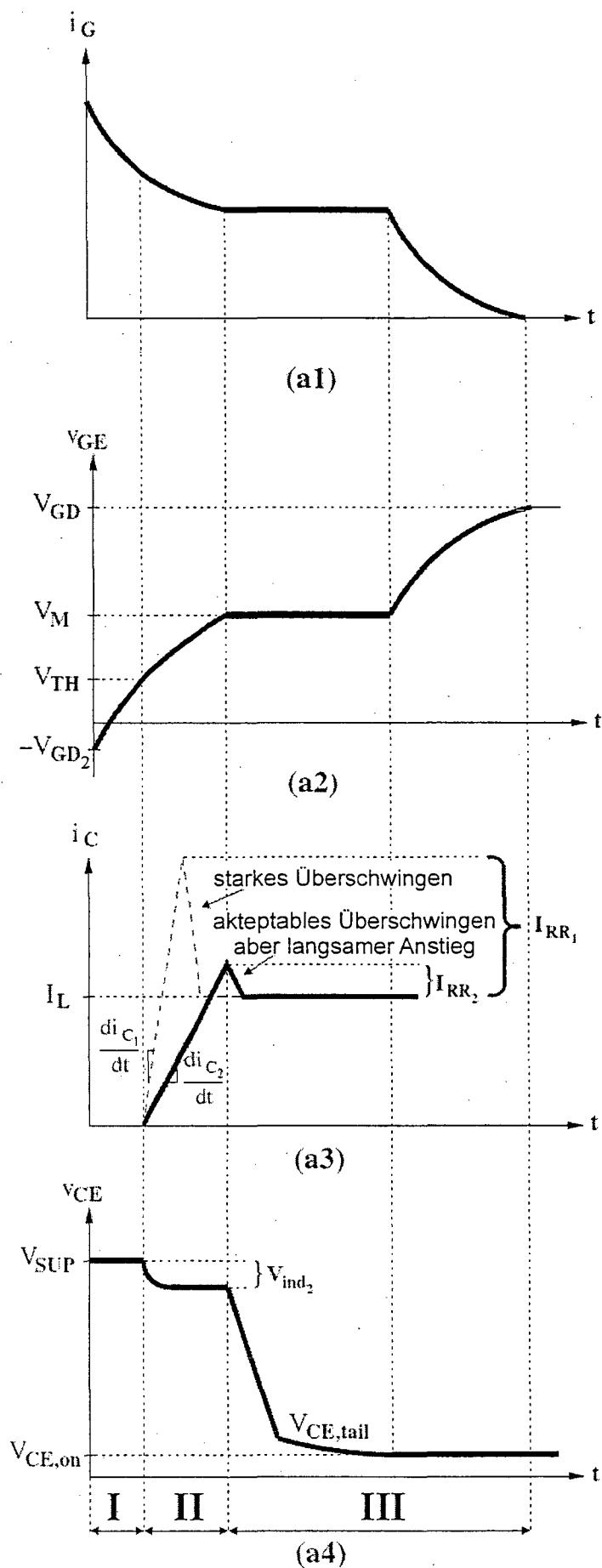

Ein beispielhafter Einschaltvorgang des IGBT-Moduls 110 ist in Fig. 2A schematisch dargestellt. Darin sind übereinander der zeitliche Verlauf des Gate-Stromes  $i_G$  (Kurve a1), der Gate-Emitter-Spannung  $v_{GE}$  (Kurve a2), des Kollektor-Stromes  $i_C$  (Kurve a3) und der Kollektor-Emitter-Spannung  $v_{CE}$  (Kurve a4) dargestellt. Im Aus-Zustand der IGBT-Moduls liefert der Gate-Treiber eine „Off“-Spannung  $-V_{GD_2}$ , bei der die Kollektor-Emitter-Strecke des IGBT stromlos ist. Um das IGBT-Modul einzuschalten liefert der Gate-Treiber eine „On“-Spannung  $V_{GD}$ , welche zumindest über der Schwellspannung  $V_{TH}$  des IGBT liegt. Der Zeitpunkt dieses Umschaltens des Gate-Treibers zur Spannung  $V_{GD}$  bildet den linken Rand der Kurven in Fig. 2A.

20

Mit dem Einschalten des Gate-Treibers setzt ein hoher Gate-Strom  $i_G$  ein, der durch die vom Gate-Treiber erzeugte Spannung und durch einen Gate-Widerstand oder Gate-Treiber-Widerstand  $R_G$  bestimmt wird und zu einer Beladung des Gates führt (Kurve a1). Die Gate-Emitter-Spannung  $v_{GE}$  steigt damit von dem Wert  $-V_{GD_2}$  ausgehend an (Kurve a2) bis es vorübergehend das sogenannte Miller-Plateau  $V_M$  erreicht um schließlich bis zum vollständigen Durchschalten des IGBT auf den Wert  $V_{GD}$  anzusteigen. Sobald die Gate-Emitter-Spannung den Wert der Schwellspannung  $V_{TH}$  erreicht, beginnt die Kollektor-Emitter-Strecke zu leiten, d.h. der Kollektorstrom beginnt zu fließen (Kurve a3). Aufgrund parasitärer Induktivitäten

der Zuleitungen sinkt die Kollektor-Emitter-Spannung  $V_{CE}$  um einen Wert  $V_{ind}$  sobald der Kollektorstrom  $i_C$  anfängt zu steigen:

$$V_{ind} = L_\sigma \frac{di_C}{dt}, \quad (1)$$

5

wobei  $L_\sigma$  die gesamte, parasitäre Induktivität (Streuinduktivität) der Leitungen ist.

$$L_\sigma = L_{S1} + L_{D1} + L_{D2} + L_C + L_E + L_{S2} + L_{CAP} \quad (2)$$

- 10 Gleichung (1) zeigt, dass der Abfall der Kollektor-Emitter-Spannung proportional zum Anstieg des Kollektor-Stroms ist. Außerdem wirkt sich der positive Wert von  $\frac{di_C}{dt}$  des Anstiegs des Kollektor-Stroms bei Verwendung eines herkömmlichen Gate-Treibers auf den Maximalwert des Sperr-Erholstroms (engl. reverse recovery current) der Schutzdiode aus. Dabei handelt es sich um den Strom in Sperrrichtung

15 der Diode, der bis zum (Wieder-)Aufbau des Sperreffekts der Diode fließt.

$$I_{RR} \approx \sqrt{Q_{rr} \frac{di_C}{dt}} \quad (3)$$

- 20 wobei  $Q_{rr}$  die Sperr-Erholladung der Diode bezeichnet, also insbesondere diejenige Ladung, die fließen muss, um den pn-Übergang der Diode zu verarmen.

- L. Chen und F.Z. Peng haben in „Switching loss analysis of closed-loop gate drive“, Proc. Of the 25<sup>th</sup> Annual IEEE Applied Power Electronics Conf. and Exposition (APEC), Palm Springs, CA, USA, Feb. 2010, pp. 1119-1123 gezeigt, dass durch schnellere Schalttransienten die Verlustleistung des IGBT reduziert werden kann.

25 Allerdings führt ein schneller Anstieg des Kollektorstroms auch zu einem stärkeren Überschwingen des Sperr-Erholstroms. Zu hohe Sperr-Erholstrom-Überschwingungen können aber zu einem dynamischen Lawinendurchbruch und damit zu einer Schädigung oder Zerstörung der Schaltung führen. Es wird daher ein Kompromiss

gesucht zwischen den Einschalt-Verlusten einerseits und der Spitze des Sperr-Erholstroms andererseits. Diese grundsätzliche Idee bleibt im Prinzip bei allen herkömmlichen Ansätzen die gleiche.

- 5 Aufgabe der vorliegenden Erfindung ist es, den Einschaltvorgang im Hinblick auf möglichst geringe Verlustleistungen und möglichst geringe Belastung oder Gefährdung der Schaltung durch Überspannungen zu verbessern. Diese Aufgabe wird durch ein Verfahren mit den in Anspruch 1 und eine Treiberschaltung mit den in Anspruch 9 angegebenen Merkmalen gelöst. Bevorzugte Ausführungsformen sind

10 Gegenstand der abhängigen Ansprüche.

Somit bietet die Erfindung in einem Aspekt ein Verfahren zur Ansteuerung eines Leistungsschaltteils, welches zumindest einen Isolated-Gate-Bipolartransistor (IGBT, Bipolartransistor mit isoliertem Gate IGBT) mit einem Gate und einer mittels des

15 Gates schaltbaren Kollektor-Emitter-Strecke und eine zur Kollektor-Emitter-Strecke in Serie geschaltete Schutzdiode umfasst. In einer solchen Schaltung können auch noch weitere Schaltungskomponenten enthalten sein, die in der in Fig. 1 beschriebenen herkömmlichen Schaltung nicht ausdrücklich gezeigt sind. Beispielsweise ist die vorliegende Erfindung auch anwendbar, wenn parallel zur

20 Schutzdiode ein weiterer IGBT geschaltet ist.

Ausgehend von einem nicht-leitenden Zustand der Kollektor-Emitter-Strecke also von einem „Aus“ bzw. „Off“-Zustand des IGBT umfasst das Verfahren ein Laden des Gates mittels eines Gate-Stroms einer ersten Polarität zum teilweisen Freischalten

25 der Kollektor-Emitter-Strecke. Es kommt dabei im Allgemeinen nicht unbedingt auf den absoluten Ladezustand des Gates vor und nach dem (teilweisen) Laden an. Entscheidend ist lediglich, dass mittels eines ersten Gate-Stroms in Freischaltrichtung (also „Ein“-Richtung des IGBT) die Ladung am Gate und damit das Potential am Gate geändert wird, um den IGBT von einem „Aus“- in Richtung eines

30 „Ein“-Zustandes zu versetzen.

Außerdem umfasst das Verfahren insbesondere anschließend ein teilweises

- Entladen des Gates mittels eines Gate-Stroms einer zweiten, zur ersten entgegengesetzten Polarität. Der Einschaltvorgang wird also erfindungsgemäß nicht mit einer durchgehend gleichbleibenden Gate-Strom-Richtung bewerkstelligt. Stattdessen schlägt die Erfindung vor, vorübergehend den Gate-Strom umzukehren.

- 5 Schließlich umfasst das Verfahren außerdem ein weiteres Laden des Gates mittels eines Gate-Stroms der ersten Polarität zum vollständigen Freischalten der Kollektor-Emitter-Strecke. Mit dieser Folge von Gate-Strömen bietet die Erfindung eine unerwartet deutliche Verbesserung des Einschaltvorgangs von Leistungsschaltbeuteilen auf Basis von IGBT, sowohl hinsichtlich der

- 10 Betriebssicherheit unter Vermeidung zu hoher Überschwingströme als auch hinsichtlich überraschenderweise deutlich reduzierter elektrischer Schaltungsverluste. So kann durch das erfindungsgemäße Verfahren insbesondere ein anfangs deutlich höherer Gate-Strom verwendet werden als in herkömmlichen Verfahren, da im Rahmen der Erfindung erkannt wurde, dass durch eine nachfolgende kurze

- 15 Umkehrung des Gate-Stromes dennoch die ansonsten zu erwartenden Überschwingungströme sehr effizient unterdrückt und das Sperrverhalten der Schutzdiode dabei dennoch aufgebaut werden kann, allerdings „sanfter“ als in herkömmlichen Schaltvorgängen und mittels herkömmlicher Gate-Treiber.

- 20 Vorzugsweise wird das Gate ausgehend vom nicht-leitenden Zustand der Kollektor-Emitter-Strecke so lange mittels des Gate-Stroms der ersten Polarität geladen, bis der Kollektor-Strom im IGBT einen bestimmten Wert erreicht. Dies kann beispielsweise ein Referenzwert im Bereich des im „Ein“-Zustand des IGBT zu erwartenden Last-Stromes in der jeweiligen Schaltung sein. Damit wird erreicht, dass

- 25 der Kollektor-Strom nicht sehr viel höher ansteigt, als der gewünschte Referenzwert. In einer bevorzugten Ausführungsform wird beispielsweise der Kollektor-Strom während des Einschaltvorgangs direkt oder indirekt erfasst oder gemessen und mit dem vorgegebenen Referenzwert verglichen, um dann in Abhängigkeit von dem erfassten Kollektor-Strom den Gate-Strom zu steuern, insbesondere umzukehren.

- 30 In einer anderen Ausführungsform kann empirisch für eine vorgegebenen Schaltung und bei einer Vorgabe für die Höhe des anfänglichen Gate-Stroms, und damit

vorzugsweise einem vorgegebenen anfänglichen Anstieg des Kollektor-Stroms, die Zeit ermittelt werden, die vergeht, bis der Kollektor-Strom auf den Referenzwert angestiegen ist. Diese Zeit kann dann zur Steuerung des Gate-Stromes herangezogen werden. Diese Implementierung reagiert zwar weniger flexibel auf Änderungen in der gesamten Schaltung (z.B. evtl. Änderungen von Streuinduktivitäten), kann aber ohne eine ständige Messung und Auswertung des Kollektorstromes in Echtzeit auskommen und für viele Anwendungen ausreichen.

In einer bevorzugten Ausführungsform beginnt das teilweise Entladen des Gates mittels des Gate-Stroms der zweiten Polarisation zu einem Zeitpunkt, bei dem der Kollektorstrom des IGBT einen bestimmten (vorgegebenen) Wert (Umschaltreferenzwert) überschritten hat. Insbesondere kann in einer bevorzugten Ausführungsform das Verfahren ein Messen bzw. Erfassen des momentanen Kollektorstroms umfassen, wobei in Abhängigkeit davon, wann der Umschaltreferenzwert erreicht bzw. überschritten ist, ein Umschalten des Gate-Stroms erfolgt.

In einer weiteren bevorzugten Ausführungsform umfasst das Verfahren außerdem zwischen dem teilweisen Entladen des Gates mittels eines Gate-Stroms der zweiten Polarität und dem weiteren Laden des Gates mittels eines Gate-Stroms der ersten Polarität ein Setzen des Gate-Stroms auf Null für eine Gate-Verweilzeit. Besonders bevorzugt liegt die Gate-Verweilzeit in einem Bereich des etwa 0,1-fachen bis etwa 10-fachen, vorzugsweise im Bereich des etwa 0,2 bis etwa 5-fachen der Zeit, während der das Gate zuvor teilweise mittels des Gate-Stroms der zweiten Polarität entladen wurde.

In einer weiteren bevorzugten Ausführungsform weicht der Kollektorstrom zwischen dem Beginn des teilweisen Entladens des Gates und dem vollständigen Freischalten der Kollektor-Emitter-Strecke um weniger als etwa 20%, vorzugsweise weniger als etwa 15%, noch mehr bevorzugt weniger als etwa 10%, am meisten bevorzugt sogar weniger als etwa 5% von dessen Mittelwert während dieser Zeit abweicht.

Vorzugsweise umfasst das teilweise Entladen des Gates durch Anlegen einer Gate-Entladespannung an das Gate über einen Gate-Entladewiderstand, wobei die Gate-Entladespannung kleiner ist als die Schwellspannung des IGBT.

- 5 Vorzugsweise umfasst das Laden des Gates mittels eines Gate-Stroms einer ersten Polarität ausgehend von einem nicht-leitenden Zustand der Kollektor-Emitter-Strecke ein Anlegen einer Gate-Ladespannung an das Gate über einen ersten Gate-Ladewiderstand, wobei das weitere Laden des Gates mittels eines Gate-Stroms der ersten Polarität nach dem teilweisen Entladen ein Anlegen der

10 Gate-Ladespannung an das Gate über einen zweiten Gate-Ladewiderstand umfasst, der größer ist als der erste Gate-Ladewiderstand.

In einem weiteren Aspekt betrifft die Erfindung einen Gate-Treiber zur Ansteuerung eines Leistungsschaltteils, welches zumindest einen Isolated-Gate-Bipolartransistor

15 mit einem Gate und einer mittels des Gates schaltbaren Kollektor-Emitter-Strecke und eine zur Kollektor-Emitter-Strecke in Serie geschaltete Schutzdiode umfasst, wobei der Gate-Treiber ausgelegt ist, folgende Schritte auszuführen:

- ausgehend von einem nicht-leitenden Zustand der Kollektor-Emitter-Strecke Laden des Gates mittels eines Gate-Stroms einer ersten Polarität zum teilweisen

20 Freischalten der Kollektor-Emitter-Strecke;

- teilweises Entladen des Gates mittels eines Gate-Stroms einer zweiten, zur ersten entgegengesetzten Polarität; und

- weiteres Laden des Gates mittels eines Gate-Stroms der ersten Polarität zum vollständigen Freischalten der Kollektor-Emitter-Strecke.

25

Vorzugsweise ist der Gate-Treiber ausgelegt ein erfindungsgemäßes Verfahren insbesondere in einer der hier beschriebenen bevorzugten Ausführungsformen auszuführen bzw. (insbesondere automatisch) zu steuern bzw. zu regeln.

- 30 In einem weiteren Aspekt betrifft die Erfindung ein Leistungsschaltteil umfassend:

- einen Isolated-Gate-Bipolartransistor mit einem Gate und einer mittels des Gates schaltbaren Kollektor-Emitter-Strecke;

- eine zur Kollektor-Emitter-Strecke in Serie geschaltete Schutzdiode und

- einen Gate-Treiber gemäß der vorliegenden Erfindung insbesondere in einer der hier beschriebenen bevorzugten Ausführungsformen.

- 5 Die Erfindung wird nachfolgend anhand bevorzugter Ausführungsformen mit Verweis auf die beigefügten Zeichnungen beschrieben, dabei zeigen:

- 10 Fig. 1: ein Beispielhaftes Schaltungsdiagramm einer herkömmlichen Leistungsschaltung auf Basis eines IGBT;

- Fig. 2A: schematische Strom- und Spannungsverläufe bei einem herkömmlichen Einschaltvorgang;

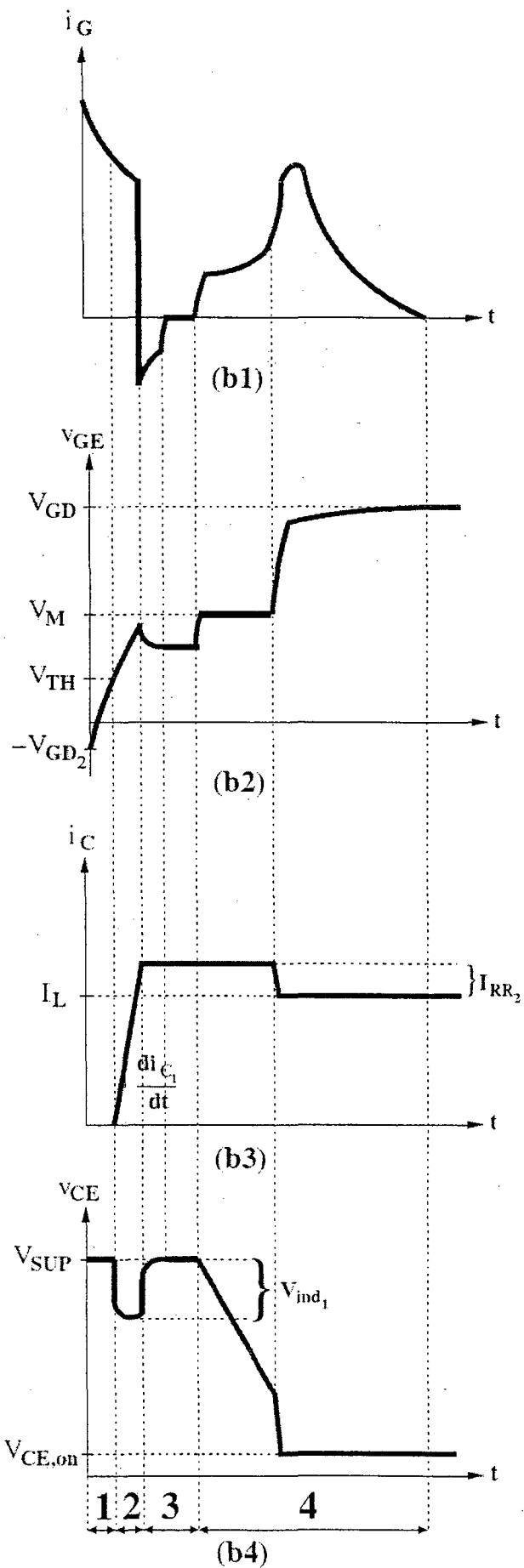

- 15 Fig. 2B: beispielhafte schematische Strom- und Spannungsverläufe bei einem Einschaltvorgang gemäß einer bevorzugten Ausführungsform der Erfindung;

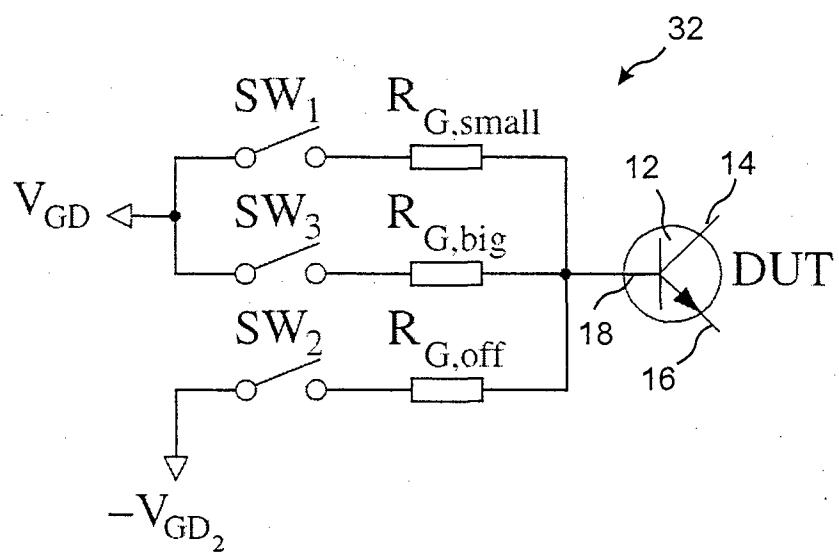

- Fig. 3: ein Schaltungsdiagramm eines Gate-Treibers gemäß einer bevorzugten Ausführungsform der vorliegenden Erfindung;

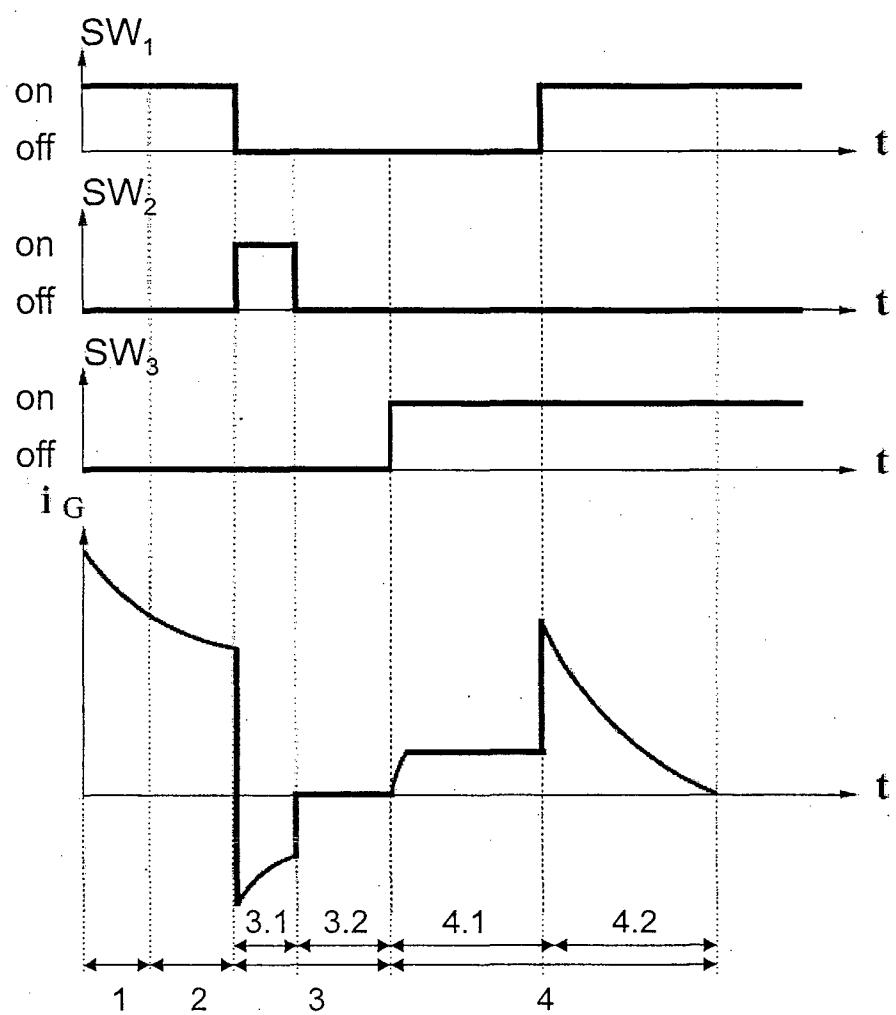

- 20 Fig. 4: eine schematische Darstellung des zeitlichen Verlaufs eines Steuersignals (Gate-Stromes) bei Anwendung eines Gate-Treibers gemäß Fig. 3;

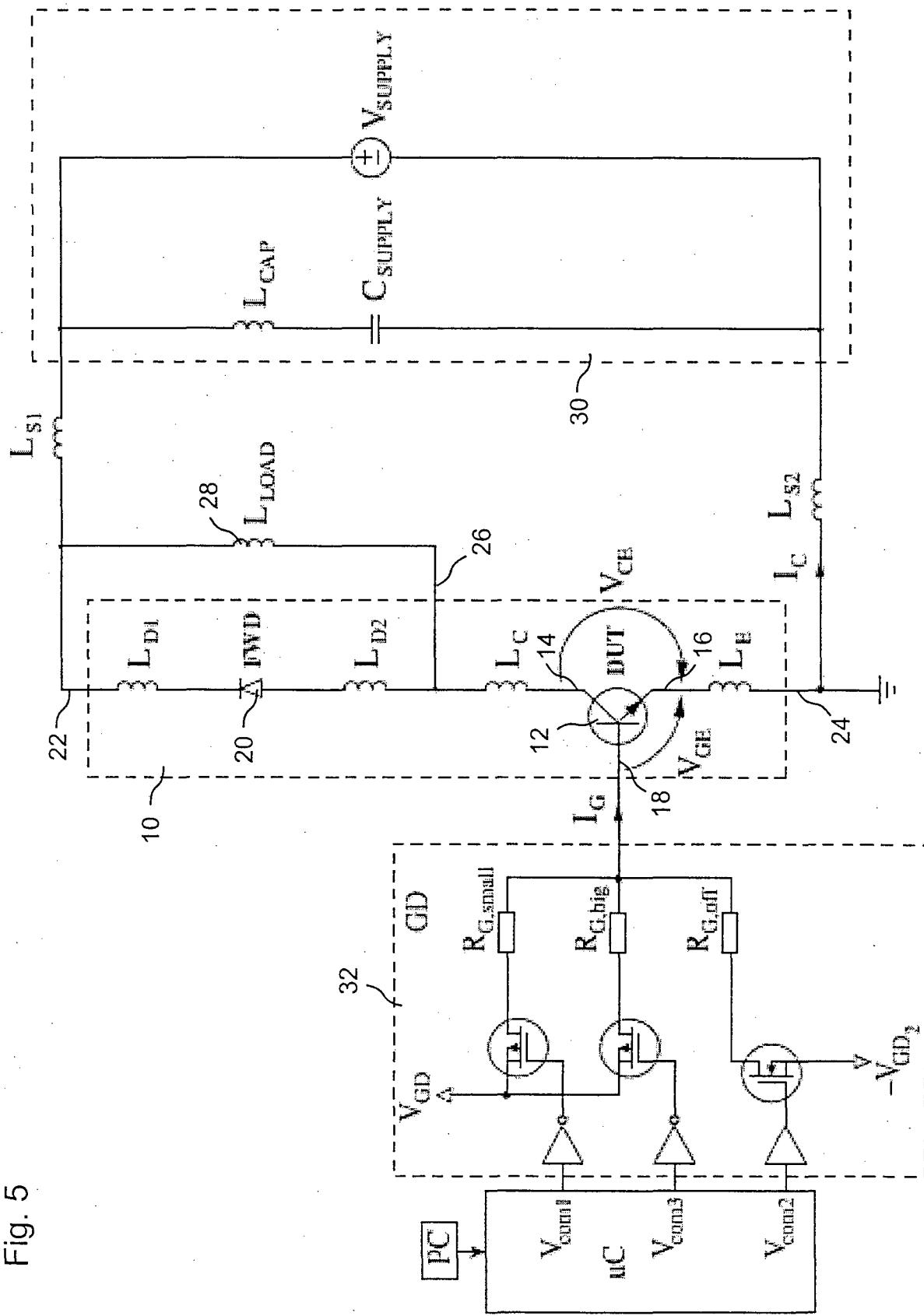

- Fig. 5: ein Beispielhaftes Schaltungsdiagramm eines Leistungsschaltkreises auf Basis eines IGBT zusammen mit einem Gate-Treiber gemäß einer bevorzugten Ausführungsform der vorliegenden Erfindung;

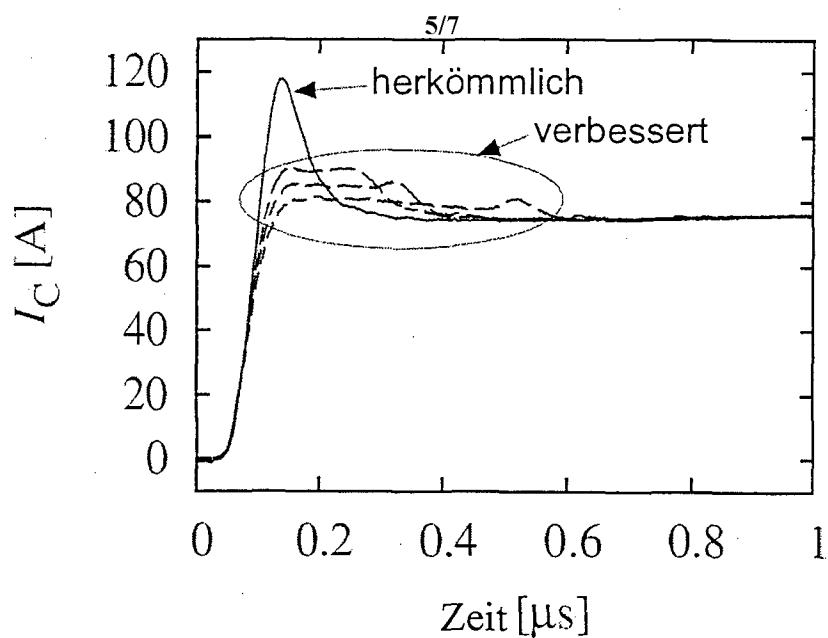

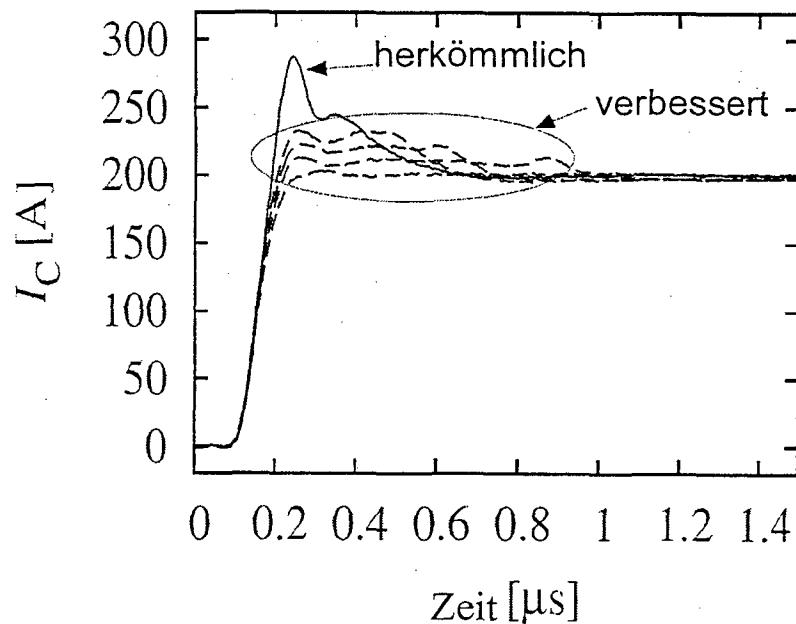

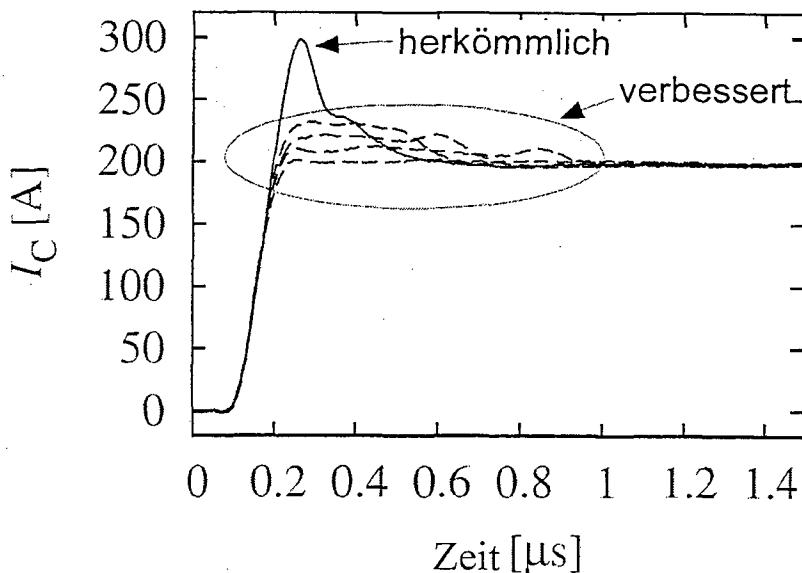

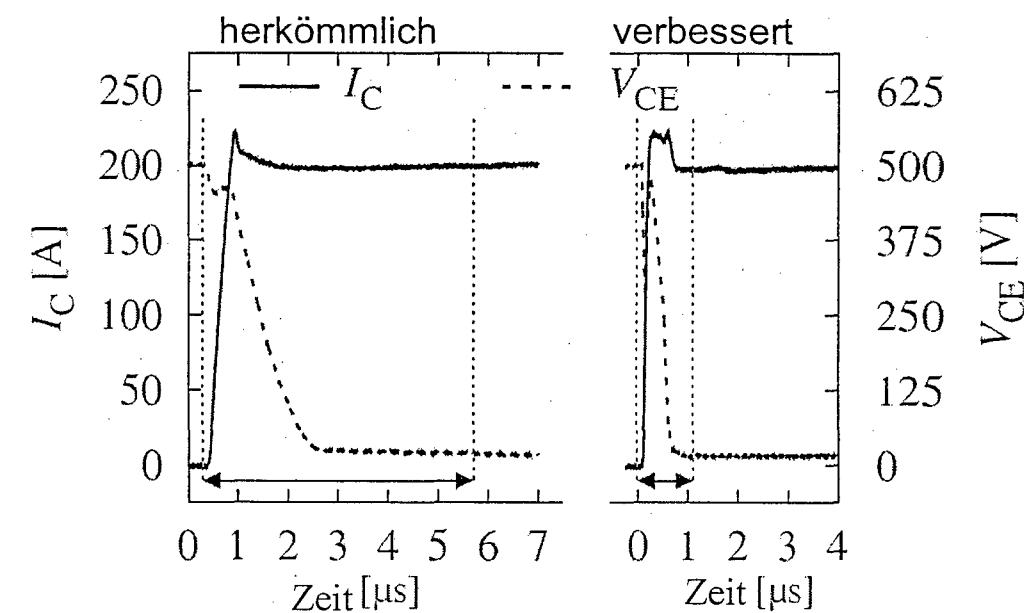

- 25 Fig. 6A – 6C: Vergleiche von Messungen des zeitlichen Verlaufs des Kollektorstroms bei einem herkömmlichen Einschaltvorgang und erfindungsgemäßen Ansteuerverfahren für drei verschiedene IGBT-Module;

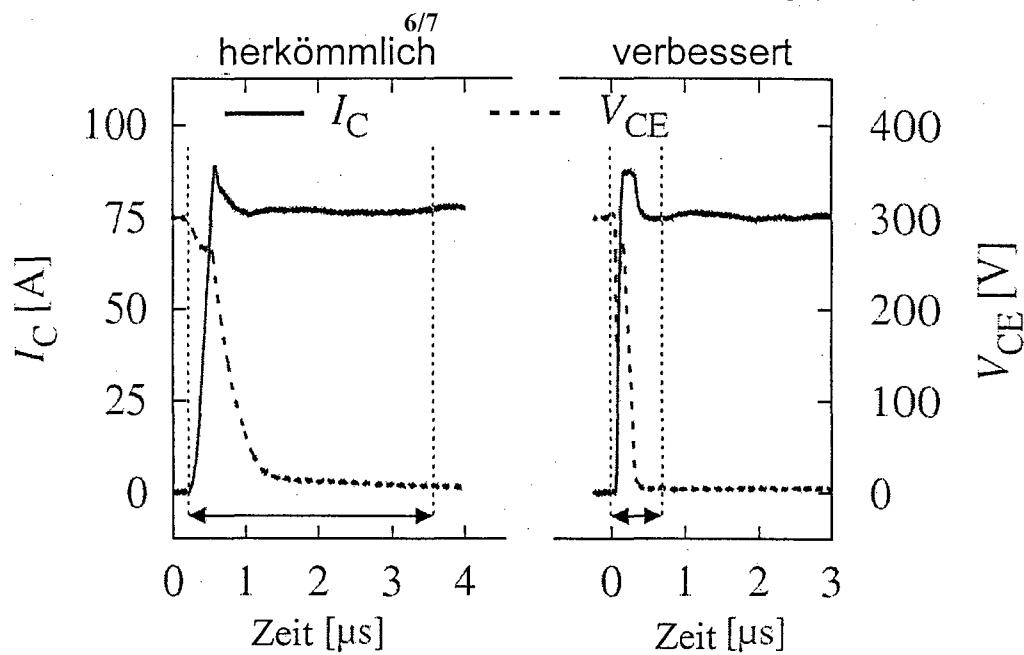

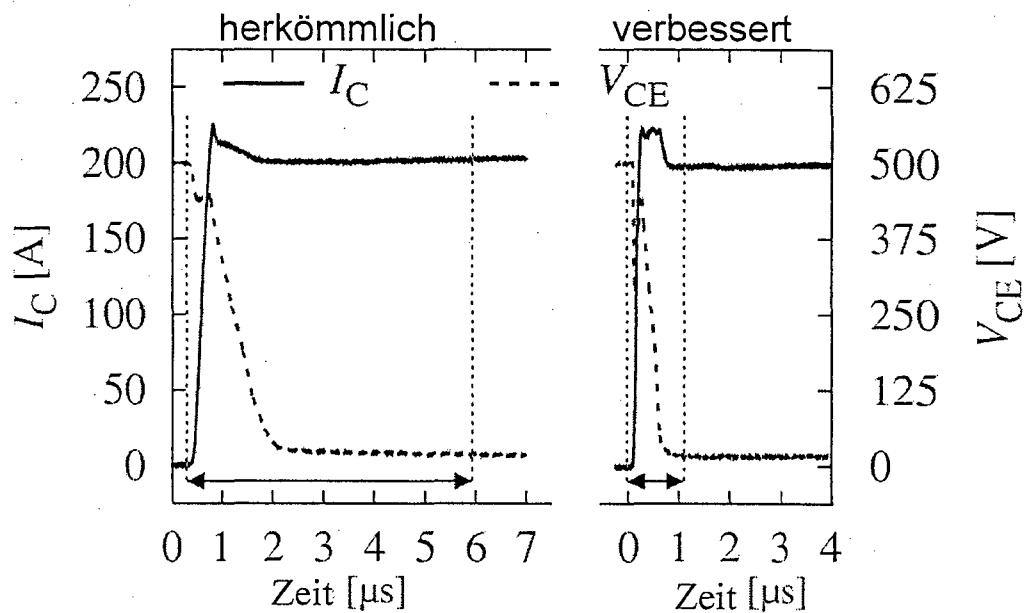

- 30 Fig. 7A – 7C: Vergleiche von Messungen des zeitlichen Verlaufs des Kollektorstroms

und der Kollektor-Emitter-Spannung bei einem herkömmlichen Einschaltvorgang und jeweils einem erfindungsgemäßen Ansteuerverfahren für drei verschiedene IGBT-Module; und

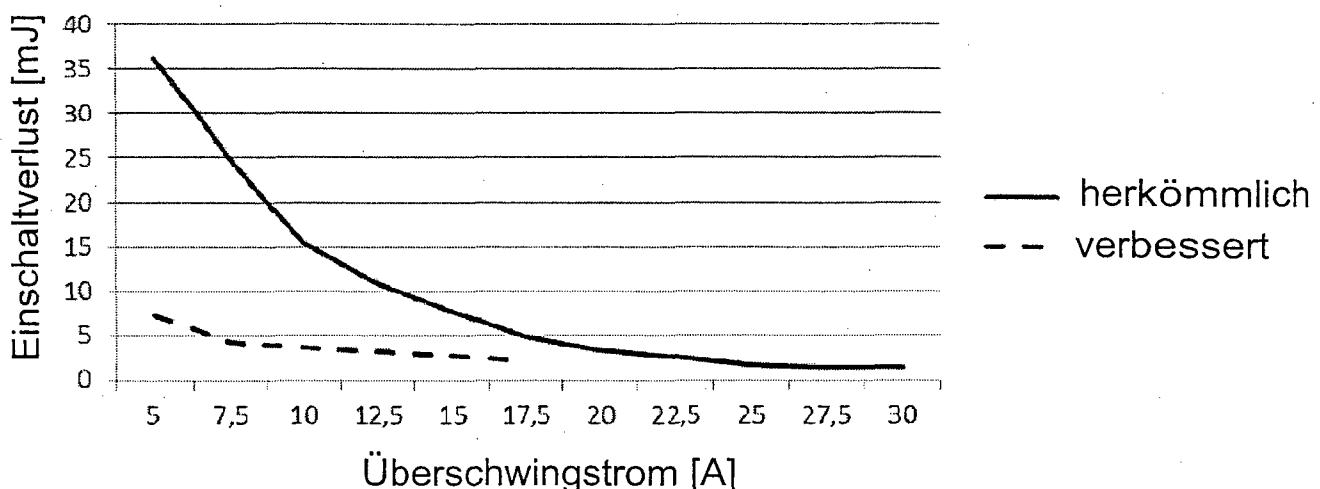

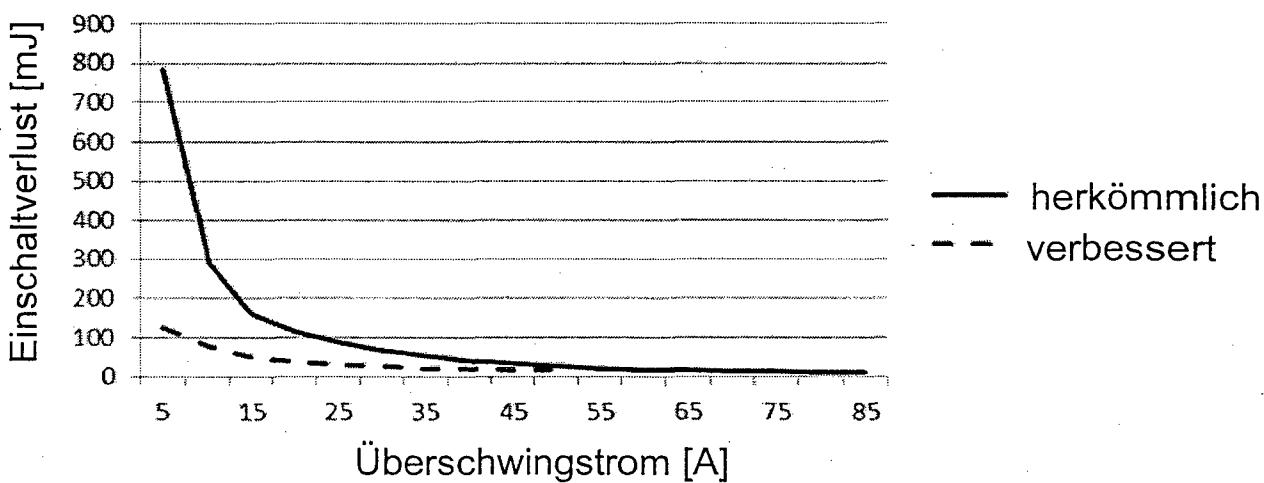

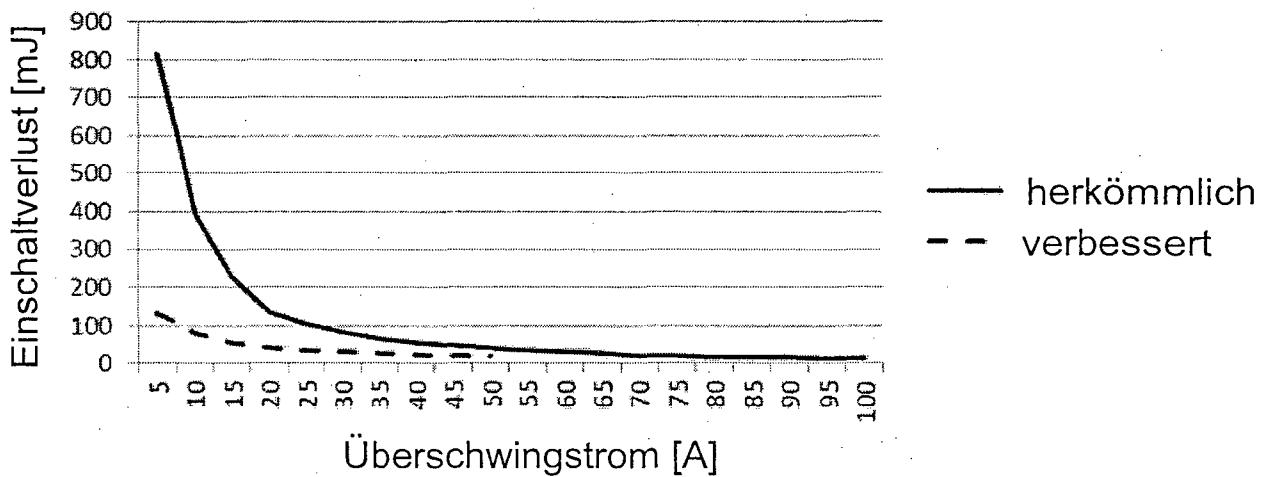

- 5 Fig. 8A – 8C: Vergleiche von Messungen der Überschwingströme und elektrischen Schaltungsverluste bei herkömmlichen Einschaltvorgängen und erfindungsgemäßen Ansteuerverfahren für drei verschiedene IGBT-Module.

- 10 Der Einschaltvorgang wird bei der herkömmlichen Steuerung oft als in drei Phasen unterteilt angesehen, wie dies in Fig. 2A veranschaulicht ist: Phase I repräsentiert die Verzögerungszeit bis die Gate-Spannung des IGBT die Schwellspannung erreicht und die Kollektor-Emitter-Strecke anfängt zu leiten; Phase II bezeichnet die Zeit, in der der Kollektor-Strom bis zu dessen Maximum ansteigt, welches durch die Summe 15 aus dem Laststrom und dem Sperr-Erholstrom bestimmt ist; Phase III schließlich beschreibt das anschließende Abfallen der Kollektor-Emitter-Spannung bis zur Sättigungsspannung des IGBT kombiniert mit dem abschließenden Anstieg der Gate-Spannung kurz nachdem das Miller-Plateau abgeschlossen ist.

- 20 Der eingangs erwähnte Kompromiss zwischen möglichst geringen Verlustleistungen und der Vermeidung zu hoher Überspannungen in herkömmlichen Einschaltsequenzen betrifft dabei die Wahl eines ausreichend langsamem Anstiegs des Kollektorstroms während der Phase II, um das Sperr-Erholstrom-Überschwingen gering zu halten, und einen genügend schnellen Abfall der 25 Kollektor-Emitter-Spannung während der Phase III, um die Schaltverluste beim Einschalten zu minimieren.

- Eine erfindungsgemäße Lösung gemäß einer bevorzugten Ausführungsform lässt sich anhand von Fig. 2B gut nachvollziehen, wobei zur leichteren Nachvollziehbarkeit 30 einzelne Phasen mit „1“ bis „4“ durchnumeriert sind.

Phase 1 stellt die Einschalt-Verzögerungszeit dar, die nach dem Einschalten eines

Gate-Treiber-Signals zum Öffnen der Kollektor-Emitter-Strecke auftritt bis die Gate-Emitter-Spannung auf die Schwellspannung des IGBT angestiegen ist. Diese Verzögerungszeit ist insbesondere gegeben durch:

$$5 \quad t_{delayON} \approx \frac{Q_{delayON}}{i_G} \quad (4)$$

Durch die Möglichkeit, diese Verzögerungszeit zu minimieren, kann die Schaltfrequenz erhöht werden. Dies ist bei erfindungsgemäßen Verfahren mittels eines anfänglich vergleichsweise hohen Gate-Stromes möglich, ohne dass damit gleichzeitig ein starkes Überschwingen des Kollektor-Stroms riskiert wird. Es wird also zunächst ein Gate-Strom einer ersten Polarität angelegt, welcher das Gate in Richtung eines „Ein“-Zustandes des IGBT lädt. Im Falle eines n-Kanal-IGBT entspricht dies einem Gate-Strom durch eine positive Gate-Emitter-Spannung, d.h. das Gate ist auf höherem Potential als der Emitter-Anschluss. Beim p-Kanal-IGBT wäre die erste Polarität sinngemäß umgekehrt, um zu einem „Ein“-Zustand des IGBT zu führen.

In Phase 2 steigt der Kollektor-Strom bis auf einen Maximal-Sollwert, insbesondere oberhalb des endgültigen Laststroms, an. Dabei wird vorzugsweise der hohe Gate-Strom der vorangegangenen Phase zumindest annähernd beibehalten, was gemäß

$$25 \quad \frac{di_C}{dt} \approx \frac{g_{fs} \cdot i_G}{C_{GE}} \quad (5)$$

zu einem schnellen Anstieg des Kollektor-Stromes führt, wobei  $g_{fs}$  die Transkonduktanz des IGBT bezeichnet.

In Phase 3 wird vorzugsweise der Kollektor-Strom und damit auch der Sperr-Erholstrom insbesondere oberhalb des Laststromes  $I_L$ , der sich nach 30 Abschluss des Einschaltvorganges einstellt, im Wesentlichen konstant, insbesondere

- bei oder unter dem Maximal-Sollwert, gehalten. Bei Betrachtung von Gleichung (5) könnte man davon ausgehen, dass dies erreicht wird, indem der Gate-Strom auf Null gesetzt wird. Allerdings lässt diese Betrachtung die Streuinduktivitäten außer Acht. So fällt während des Anstiegs des Kollektor-Stromes ein Teil der 5 Versorgungsspannung über diesen Streuinduktivitäten (siehe Gleichung (2)) ab. Die Kollektor-Spannung wird um diesen Betrag erniedrigt. Wenn allerdings der Gate-Strom auf Null gesetzt wird, sinkt die zeitliche Änderung des Kollektorstroms, wodurch die Kollektor-Emitter-Spannung wieder etwas ansteigt. Da aber der Kollektor-Strom auch von der Kollektor-Emitter-Spannung abhängt, steigt der 10 Kollektor-Strom mit steigender Kollektor-Emitter-Spannung ebenfalls weiter an, auch wenn der Gate-Strom auf Null gesetzt wird, die Ladung am Gate also konstant bleibt. Ein Absenken des Gate-Stroms auf Null führt also zu einem weiteren Anstieg des Kollektor-Stroms, wenn auch mit kleiner werdender Steigung.

- 15 Um diesen Effekt der Streuinduktivitäten zu kompensieren, wird daher der Gate-Strom kurzzeitig umgekehrt, wie dies in Kurve (b1) der Fig. 2B gezeigt ist, d.h. das Gate wird wieder ein wenig entladen. Es wird also kurzzeitig ein Gate-Strom einer zweiten Polarität angelegt, die entgegengesetzt zur ersten Polarität ist. Damit kann erreicht werden, dass der Kollektor-Strom bei oder unter einem bestimmten 20 Maximal-Sollwert gehalten wird, (Kurve (b3) in Fig. 2B), während die Kollektor-Emitter-Spannung wieder etwas ansteigt (Kurve (b4) in Fig. 2B). Insbesondere sobald die Kollektor-Emitter-Spannung wieder einen im Wesentlichen konstanten Wert, insbesondere den Wert der Versorgungsspannung, erreicht hat, wird der Gate-Strom vorzugsweise auf Null gesetzt.

- 25 In Phase 4 wird vorzugsweise weiterhin der Kollektor-Strom im Wesentlichen konstant gehalten während die Kollektor-Emitter-Spannung abfällt. Hierzu wird der Gate-Strom wieder in der ersten Polarität angelegt, also in Richtung des „Ein“-Zustandes des IGBT, aber vorzugsweise für eine kurze Zeit vom Betrag her 30 unterhalb eines Wertes des Gate-Stromes in der ersten Phase. Besonders bevorzugt wird der Gate-Strom in Phase 4 konstant gehalten oder kontinuierlich oder stufenweise wieder erhöht, insbesondere bis die Gate-Emitter-Spannung über das

Miller-Plateau ansteigt und/oder der Kollektor-Strom wieder zurückgeht, um sich auf den Wert des Laststromes einzustellen. In dieser Zeit fällt insbesondere auch die Kollektor-Emitter-Spannung auf ihren Sättigungswert ab und der IGBT ist eingeschaltet.

5

Eine bevorzugte Ausführungsform eines erfindungsgemäßen Gate-Treibers 32, der eine entsprechende Ansteuerung eines IGBTs 12 in sehr einfacher und zuverlässiger Weise bewerkstelligen kann, ist in Fig. 3 schematisch dargestellt. In dieser Ausführungsform ist der Gate-Treiber 32 ausgelegt, wahlweise unterschiedliche elektrische Potentiale  $-V_{GD_2}$ ,  $V_{GD}$  (Gate-Treiber-Potentiale) über unterschiedliche elektrische Widerstände  $R_{G,off}$ ,  $R_{G,big}$ ,  $R_{G,small}$  (Gate-Treiber-Widerstände) mit einem Gate 18 des IGBT 32 zu verbinden. Die Gate-Treiber-Potentiale werden dabei im Betrieb des Gate-Treibers 32 mit einem IGBT 12 so gewählt, dass zumindest eines der Gate-Treiber-Potentiale  $-V_{GD_2}$  in Bezug auf ein elektrisches Potential eines Emitteranschlusses 16 des IGBT 12 unterhalb der Schwellspannung  $V_{TH}$  des IGBT 12 und zumindest eines der Gate-Treiber-Potentiale  $V_{GD}$  in Bezug auf das elektrische Potential des Emitteranschlusses 16 oberhalb der Schwellspannung  $V_{TH}$  des IGBT liegt, um damit den IGBT aus- und einschalten zu können.

20 Besonders bevorzugt ist ein erstes Gate-Treiber-Potential  $V_{GD}$  zum Einschalten des IGBT wahlweise mittels einer Vielzahl parallel zueinander geschalteter elektrischer Widerstände einzeln mit dem Gate verbindbar. Der Gate-Treiber stellt somit vorzugsweise an einem Gate-Treiber-Ausgang das erste Gate-Treiber-Potential  $V_{GD}$  mit einer Vielzahl unterschiedlicher Ausgangswiderstände wahlweise zur Verfügung. Besonders bevorzugt ist der Gate-Treiber ausgelegt, die unterschiedlichen Gate-Treiber-Potentiale mit den unterschiedlichen Ausgangswiderständen automatisch in einer vorher festgelegten Sequenz auszugeben und damit eine entsprechende Sequenz von Gate-Strömen zu erzeugen.

25

30 Eine solche Folge von Gate-Strömen und die dafür genutzte Folge von

Schalterstellungen von Schaltelementen  $SW_1$ ,  $SW_2$  und  $SW_3$  gemäß eines Gate-Treiber nach Fig. 3 ist in Fig. 4 veranschaulicht. Dabei wird zunächst ein relativ hoher Gate-Strom mit einer ersten Polarisation erzeugt, indem der Schalter  $SW_1$  geschlossen und damit der Gate-Treiber-Ausgang über einen niedrigen Ausgangswiderstand mit der Gate-Treiber-Spannung  $V_{GD}$  verbunden wird. Falls also ausgehend von einem nicht-leitenden Zustand der Kollektor-Emitter-Strecke des IGBT das Gate mit diesem Treibersignal versorgt wird, fließt ein relativ hoher Gate-Strom. Dieser kann damit die beiden oben anhand von Fig. 2B beispielhaft beschriebenen Phasen 1 und 2 recht gut verwirklichen.

10

Entweder nach einer vorgegebenen Zeit, welche dem Ablauf der beiden oben beschriebenen Phasen 1 und 2 entspricht, und/oder nach Erreichen eines vorgegebenen Zustandes des IGBT, welcher durch direktes oder indirektes Ermitteln insbesondere eines Wertes des Kollektorstroms in Echtzeit erfolgen kann, wird in einer weiteren Phase der Gate-Strom kurzzeitig umgekehrt, d.h. das Gate wird durch einen Gate-Strom in eine entgegengesetzte Richtung kurzzeitig wieder etwas entladen. In der Schaltung gemäß der bevorzugten Ausführungsform von Fig. 3 kann dies erfolgen, indem der Schalter  $SW_1$  wieder geöffnet und der Schalter  $SW_2$  geschlossen wird. Die Höhe der einzelnen Gate-Treiber-Widerstände beeinflussen dabei die Höhe des Gate-Stroms, während über die Dauer der Schalterstellungen die gesamte Beladung des Gates gesteuert werden kann. Die Phase des kurzzeitigen Entladens des Gates ist in Fig. 4 als Phase 3.1 dargestellt. Sie stellt insbesondere eine beispielhafte Umsetzung eines ersten Teils der im Zusammenhang mit Fig. 2B beschriebenen Phase 3 dar.

25

In einer besonders bevorzugten Ausführungsform, wie sie insbesondere sowohl in Fig. 2B bereits diskutiert wurde und in Fig. 3 und 4 in einer konkreten Implementierung nochmals demonstriert wird, schließt sich der Phase des Gate-Stroms mit umgekehrter Polarität eine kontinuierliche oder Stückweise Erhöhung des Gate-Stroms an, bevor das Gate-Treiber-Potential  $V_{GD}$  wieder mit niedrigem Ausgangswiderstand an das Gate des IGBT gekoppelt wird. In Fig. 4 ist dieser Übergangsbereich mit den Phasen 3.2, 4.1 und 4.2 bezeichnet. Dabei ist die

Phase 3.2 vorzugsweise dadurch geprägt, dass der Gate-Strom im Wesentlichen auf Null gesetzt wird, indem alle Schaltelemente SW<sub>1</sub>, SW<sub>2</sub> und SW<sub>3</sub> geöffnet werden. Durch Schließen des Schaltelements SW<sub>3</sub> wird anschließend in Phase 4.1 das Gate-Treiber-Potential  $V_{GD}$  über einen höheren Ausgangswiderstand als in den

- 5 Phasen 1 und 2 an das Gate gekoppelt. Dadurch ergibt sich ein deutlich niedrigerer Gate-Strom der ersten Polarität, wodurch das Gate wieder langsam in Richtung einer Freischaltung der Kollektor-Emitter-Strecke des IGBT geladen wird.

Insbesondere mit dieser Folge von Gate-Strömen in den Phasen 3.1, 3.2 und 4.1 mit

10 einer kurzen Phase eines rückwärts gerichteten Gate-Stroms (d.h. zweite Polarität) einer Phase ohne Gate-Strom und einer Phase mit niedrigem vorwärts gerichteten Gate-Strom (d.h. erste Polarität) kann auf sehr einfache und effiziente Weise der Kollektorstrom während des Einschaltvorgangs des IGBT annähernd konstant zwischen dem endgültigen Laststrom und einem kritisch hohen Wert des

15 Sperr-Erholstrom-Überswingens herkömmlicher Schaltungen gehalten werden, wie dies beispielhaft in Fig. 2B gezeigt und weiter oben bereits erklärt wurde. Die Vermeidung eines zu starken Überswingens kann sogar für sehr schnelle Anstiege des Kollektorstroms in der Anfangsphase noch sichergestellt werden, weshalb die Erfindung auf sehr wirkungsvolle Weise einen schnellen Schaltvorgang mit einem

20 sicheren Betrieb der Schaltung vereint.

Nachdem das Überschwingen des Kollektorstromes aufgrund des Sperr-Erholstromes abklingt und der Kollektorstrom sich dem endgültigen Laststrom nähert, kann in einer weiteren Phase 4.2 auch das Schaltelement SW<sub>1</sub> wieder

25 geschlossen und das Gate wieder über einen niedrigen Ausgangswiderstand des Gate-Treibers an die Gate-Treiber-Potential  $V_{GD}$  gekoppelt werden. Damit kann das Gate vollständig geladen und die Kollektor-Emitter-Spannung auf den Sättigungswert gesenkt werden.

30 Nicht zuletzt durch die Möglichkeit des Einsatzes eines sehr schnellen Anstiegs des Kollektorstroms in der Anfangsphase des Einschaltvorgangs wird nicht nur der Schaltvorgang zeitsparender erzielt, sondern es kann auch eine deutliche Reduktion

der Verlustleistung durch den gesamten Schaltvorgang beobachtet werden.

Um die wesentlichen Verbesserungen durch die Erfindung an realen IGBTs und IGBT-Modulen zu demonstrieren, wurde eine Reihe von Tests durchgeführt, von

5 denen einige Tests insbesondere auf Basis von Einschalt-Sequenzen ähnlich den hier bereits beschriebenen Gate-Strom-Folgen im Folgenden kurz dargestellt werden. Dazu wurde ein Standard-Prüfstand aufgebaut, dessen Prinzip in Fig. 5 schematisch dargestellt ist. Dabei entspricht das Prinzip dieses Prüfstandes eigentlich auch genau einer möglichen Implementierung einer Leistungsschaltvorrichtung auf Basis eines

10 erfindungsgemäßen Gate-Treibers bzw. dessen erfindungsgemäßer Funktionsweise in einer bevorzugten Ausführungsform. Fig. 5 kann somit auch für eine mögliche schaltungstechnische Umsetzung der Erfindung verstanden werden.

Insbesondere wurden in dem Test kommerzielle IGBT-Module von Infineon in

15 unterschiedlichen Leistungsklassen getestet: ein 600 V/75 A Modul und zwei 1200 V/200 A Module. Wie in Fig. 5 dargestellt ist, umfasst ein IGBT Modul 10 einen IGBT 12 mit einem Kollektoranschluss 14, einem Emitteranschluss 16 und einem Steueranschluss (Gate) 18 sowie eine zur Kollektor-Emitter-Strecke des IGBT in Serie geschaltete Schutzdiode (FWD, freewheeling diode) 20, welche in

20 Sperrrichtung zu der zu schaltenden Stromrichtung liegt. Die Anode der Schutzdiode 20 ist dabei zum Kollektoranschluss 14 des IGBT 12 hin verbunden während die Kathode der Schutzdiode 20 zu einem ersten Versorgungsanschluss 22 des IGBT-Moduls 10 verbunden ist. Ein zweiter Versorgungsanschluss 24 des IGBT-Moduls 10 ist zum Emitteranschluss 16 hin verbunden. Ein Schaltausgang 26

25 des IGBT-Moduls 10 ist dabei zum Kollektoranschluss 14 und zur Anode der Schutzdiode hin verbunden. Damit kann eine an den ersten Versorgungsanschluss 22 und Schaltausgang 26 angeschlossene Last 28 geschaltet und mit einer elektrischen Versorgungseinrichtung 30 verbunden werden. Der Schaltvorgang wird dabei über das Gate 18 gesteuert. Dazu liefert ein Gate-Treiber 32, insbesondere der

30 bereits beschriebenen Art, ein entsprechendes Steuersignal.

Als Last 28 wurde für die nun vorgestellten Untersuchungen eine Induktivität von

etwa 800  $\mu$ H verwendet. Die Kapazität  $C_{SUPPLY}$  parallel zur Versorgungsspannung  $V_{SUPPLY}$  liegt bei etwa 3.3 mF. Der Gesamtwert der Streukapazität liegt für das untersuchte 600 V/75 A Modul bei etwa 110 nH und für die untersuchten 1200 V/200 A Module bei etwa 90 nH. Im Prüfstand von Fig. 5 werden die Schaltelemente  $SW_1$ ,  $SW_2$  und  $SW_3$ , welche als MOSFETs realisiert werden können, mittels eines Mikrocontrollers 34 gesteuert. Dabei sind die DRAIN-Kontakte der MOSFETs vorzugsweise mit den jeweiligen Gate-Treiber-Widerstand verbunden, welche dann wiederum zusammen mit dem Gate des IGBT verbunden sind. Die SOURCE-Kontakte der MOSFETs sind mit dem jeweiligen Gate-Treiber-Potential verbunden.

Die experimentellen Ergebnisse für die drei beispielhaften IGBT-Module sind in den Figuren 6 bis 8 dargestellt, wobei jeweils die Figuren 6A, 7A und 8A das 600 V/75 A Modul, die Figuren 6B, 7B und 8B eines der 1200 V/200 A Module (Generation 3) und die Figuren 6C, 7C und 8C das andere der 1200 V/200 A Module (Generation 4) betrifft. Dabei sind in jeder Figur einige erfindungsgemäße Verfahren zur Ansteuerung des IGBT-Moduls mit einem herkömmlichen Einschaltvorgang verglichen. Für alle drei gezeigten Module ist dabei eine sehr deutliche Verbesserung hinsichtlich des unerwünschten Überschwingverhaltens einerseits und hinsichtlich der Reduktion der Verlustleistung andererseits zu erkennen.

Fig. 6A bis 6C zeigt jeweils die Kollektorströme bei einer vorgegebenen, anfänglichen Steigung des Kollektorstroms. Während für das 600 V/75 A Modul eine Steigung von 1500 A/ $\mu$ s gewählt wurde, lag die Steigung für die 1200 V/200 A Module bei 2400 A/ $\mu$ s. Dabei wurde jeweils für die herkömmliche und die erfindungsgemäß verbesserte Einschaltsequenz dieselbe Steigung verwendet. Dabei ist erkennbar, wie deutlich das unerwünschte Überschwingen im Kollektorstrom mittels der Erfindung reduziert werden kann. Die unterschiedlichen Kurven für die verbesserten, erfindungsgemäßen Sequenzen entstanden durch Variationen der Längen der einzelnen Phasen während des Einschaltvorgangs.

In Fig. 7A bis 7C sind nun Messungen der Kollektorströme und der

Kollektor-Emitter-Spannungen bei einem herkömmlichen Einschaltvorgang und einem erfindungsgemäßen gegenübergestellt, wobei für den Vergleich jeweils Stromverläufe mit vergleichbar hohem Überschwingen aufgrund des Sperr-Erholstroms einander gegenüber gestellt wurden. Um im herkömmlichen

5 Einschaltvorgang das Überschwingen durch den Sperr-Erholstrom gering genug zu halten, muss ein wesentlich langsamerer anfänglicher Anstieg des Kollektorstroms gewählt werden. Bei diesen Messungen zeigte sich, um wie viel schneller durch das erfindungsgemäße Ansteuerverfahren der Einschaltvorgang für den IGBT abgeschlossen ist und die Kollektor-Emitter-Spannung auf den Sättigungswert

10 abgesunken ist. Insbesondere wird damit eine ganz beträchtliche und überraschend deutliche Reduktion der elektrischen Schaltungsverluste erreicht.

Diese Schaltungsverluste sind gegenüber dem Überschwingstrom für verschiedene anfängliche Anstiegsraten des Kollektorstroms in den Figuren 8A bis 8C gegenüber

15 gestellt. Wie bereits eingangs erwähnt, kann mit einer höheren anfänglichen Anstiegsrate des Kollektorstroms der Gesamtverlust beim Einschalten tendenziell reduziert werden. Vor allem bei herkömmlichen Einschaltvorgängen nimmt damit aber das Überschwingen des Kollektorstroms sehr stark zu. Durch das erfindungsgemäße Ansteuerverfahren hingegen kann eine sehr deutlich erkennbare

20 Reduktion des Überschwingstroms und der Schaltungsverluste erreicht werden.

### Bezugszeichenliste

- |            |                                        |

|------------|----------------------------------------|

| 10, 110    | IGBT-Modul                             |

| 25 12, 112 | Isolated-Gate-Bipolartransistor (IGBT) |

| 14, 114    | Kollektoranschluss                     |

| 16, 116    | Emitteranschluss                       |

| 18, 118    | Steueranschluss (Gate)                 |

| 20, 120    | Schutzdiode (FWD)                      |

| 30 22, 122 | erster Versorgungsanschluss            |

| 24, 124    | zweiter Versorgungsanschluss           |

| 26, 126    | Schaltausgang                          |

- 28, 128      Last

30, 130      elektrische Versorgungseinrichtung

32, 132      Gate-Treiber

34            Mikrocontroller

## Patentansprüche

1. Verfahren zur Ansteuerung eines Leistungsschaltteils, welches zumindest einen Isolated-Gate-Bipolartransistor mit einem Gate (18) und einer mittels des Gates schaltbaren Kollektor-Emitter-Strecke und eine zur Kollektor-Emitter-Strecke in Serie geschaltete Schutzdiode (20) umfasst, wobei

5 das Verfahren folgende Schritte umfasst:

- ausgehend von einem nicht-leitenden Zustand der Kollektor-Emitter-Strecke Laden des Gates (18) mittels eines Gate-Stroms einer ersten Polarität zum teilweisen Freischalten der Kollektor-Emitter-Strecke;

- teilweises Entladen des Gates (18) mittels eines Gate-Stroms einer zweiten, 10 zur ersten entgegengesetzten Polarität; und

- weiteres Laden des Gates mittels eines Gate-Stroms der ersten Polarität zum vollständigen Freischalten der Kollektor-Emitter-Strecke.

2. Verfahren nach Anspruch 1, wobei das Gate ausgehend vom

15 nicht-leitenden Zustand der Kollektor-Emitter-Strecke so lange mittels des Gate-Stroms der ersten Polarität geladen wird, bis der Kollektor-Strom im IGBT einen bestimmten Wert erreicht.

3. Verfahren nach Anspruch 1 oder 2, wobei das teilweise Entladen des Gates

20 (18) mittels des Gate-Stroms der zweiten Polarisation zu einem Zeitpunkt beginnt, bei dem der Kollektorstrom des IGBT einen bestimmten Wert überschritten hat.

4. Verfahren nach einem der vorangegangenen Ansprüche, welches

außerdem zwischen dem teilweisen Entladen des Gates mittels eines 25 Gate-Stroms der zweiten Polarität und dem weiteren Laden des Gates mittels eines Gate-Stroms der ersten Polarität ein Setzen des Gate-Stroms auf Null für eine Gate-Verweilzeit umfasst.

5. Verfahren nach Anspruch 4, wobei die Gate-Verweilzeit in einem Bereich des etwa 0,1-fachen bis etwa 10-fachen, vorzugsweise im Bereich des etwa 0,2 bis etwa 5-fachen der Zeit liegt, während der das Gate zuvor teilweise mittels des Gate-Stromes der zweiten Polarität entladen wurde.

5

6. Verfahren nach einem der vorangegangenen Ansprüche, wobei zwischen dem Beginn des teilweisen Entladens des Gates und dem vollständigen Freischalten der Kollektor-Emitter-Strecke der Kollektorstrom um weniger als etwa 20%, vorzugsweise weniger als etwa 15%, noch mehr bevorzugt weniger als etwa 10%, am meisten bevorzugt sogar weniger als etwa 5% von dessen Mittelwert während dieser Zeit abweicht.

7. Verfahren nach einem der vorangegangenen Ansprüche, wobei das teilweise Entladen des Gates durch Anlegen einer Gate-Entladespannung an das Gate über einen Gate-Entladewiderstand umfasst, wobei die Gate-Entladespannung kleiner ist als die Schwellspannung des IGBT.

8. Verfahren nach einem der vorangegangenen Ansprüche, wobei das Laden des Gates (18) mittels eines Gate-Stroms einer ersten Polarität ausgehend von einem nicht-leitenden Zustand der Kollektor-Emitter-Strecke ein Anlegen einer Gate-Ladespannung an das Gate über einen ersten Gate-Ladewiderstand umfasst, und wobei das weitere Laden des Gates mittels eines Gate-Stroms der ersten Polarität nach dem teilweisen Entladen ein Anlegen der Gate-Ladespannung an das Gate über einen zweiten Gate-Ladewiderstand umfasst, der größer ist als der erste Gate-Ladewiderstand.

9. Gate-Treiber zur Ansteuerung eines Leistungsschaltteils, welches zumindest einen Isolated-Gate-Bipolartransistor mit einem Gate (18) und einer mittels des Gates schaltbaren Kollektor-Emitter-Strecke und eine zur Kollektor-Emitter-Strecke in Serie geschaltete Schutzdiode (20) umfasst, wobei der Gate-Treiber ausgelegt ist, folgende Schritte auszuführen:

- ausgehend von einem nicht-leitenden Zustand der Kollektor-Emitter-Strecke Laden des Gates (18) mittels eines Gate-Stroms einer ersten Polarität zum teilweisen Freischalten der Kollektor-Emitter-Strecke;

<sup>21</sup>

- teilweises Entladen des Gates (18) mittels eines Gate-Stroms einer zweiten, zur ersten entgegengesetzten Polarität; und

- weiteres Laden des Gates mittels eines Gate-Stroms der ersten Polarität zum vollständigen Freischalten der Kollektor-Emitter-Strecke.

5

## 10. Leistungsschaltteil umfassend:

- einen Isolated-Gate-Bipolartransistor mit einem Gate (18) und einer mittels des Gates schaltbaren Kollektor-Emitter-Strecke;

- eine zur Kollektor-Emitter-Strecke in Serie geschaltete Schutzdiode (20)

- 10 und

- einen Gate-Treiber gemäß Anspruch 9 zur Ansteuerung des Gates (18) des IGBT.

Fig. 1

(Stand der Technik)

Fig. 2A

2/7

(Stand der Technik)

Fig. 2B

Fig. 3

Fig. 4

Fig. 5

Fig. 6A

Fig. 6B

Fig. 6C

Fig. 7A

Fig. 7B

Fig. 7C

Fig. 8A

Fig. 8B

Fig. 8C

# INTERNATIONAL SEARCH REPORT

International application No

PCT/EP2014/002413

**A. CLASSIFICATION OF SUBJECT MATTER**

INV. H03K17/16 H03K17/0812

ADD.

According to International Patent Classification (IPC) or to both national classification and IPC

**B. FIELDS SEARCHED**

Minimum documentation searched (classification system followed by classification symbols)

H03K

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

EPO-Internal, WPI Data

**C. DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                  | Relevant to claim No. |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X         | DE 10 2011 076516 A1 (BOSCH GMBH ROBERT [DE]) 29 November 2012 (2012-11-29)<br>figure 1<br>abstract<br>paragraph [0006] - paragraph [0013]<br>----- | 1-10                  |

| X         | WO 02/07315 A1 (CT CONCEPT TECHNOLOGIE AG [CH]; THALHEIM JAN [CH])<br>24 January 2002 (2002-01-24)<br>figure 9<br>-----                             | 1,9                   |

Further documents are listed in the continuation of Box C.

See patent family annex.

\* Special categories of cited documents :

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier application or patent but published on or after the international filing date

- "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

"&" document member of the same patent family

|                                                                                                                                                                      |                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Date of the actual completion of the international search                                                                                                            | Date of mailing of the international search report |

| 9 December 2014                                                                                                                                                      | 18/12/2014                                         |

| Name and mailing address of the ISA/<br>European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040,<br>Fax: (+31-70) 340-3016 | Authorized officer<br><br>Simon, Volker            |

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/EP2014/002413

| Patent document cited in search report | Publication date | Patent family member(s) |                 | Publication date |

|----------------------------------------|------------------|-------------------------|-----------------|------------------|

| DE 102011076516 A1                     | 29-11-2012       | CN 103548266 A          |                 | 29-01-2014       |

|                                        |                  | DE 102011076516 A1      |                 | 29-11-2012       |

|                                        |                  | EP 2715939 A1           |                 | 09-04-2014       |

|                                        |                  | US 2014084827 A1        |                 | 27-03-2014       |

|                                        |                  | WO 2012159812 A1        |                 | 29-11-2012       |

| <hr/>                                  |                  |                         |                 |                  |

| WO 0207315                             | A1               | 24-01-2002              | AT 396539 T     | 15-06-2008       |

|                                        |                  |                         | AU 5559200 A    | 30-01-2002       |

|                                        |                  |                         | EP 1299950 A1   | 09-04-2003       |

|                                        |                  |                         | ES 2302695 T3   | 01-08-2008       |

|                                        |                  |                         | JP 4823470 B2   | 24-11-2011       |

|                                        |                  |                         | JP 2004504799 A | 12-02-2004       |

|                                        |                  |                         | US 6972611 B1   | 06-12-2005       |

|                                        |                  |                         | WO 0207315 A1   | 24-01-2002       |

| <hr/>                                  |                  |                         |                 |                  |

# INTERNATIONALER RECHERCHENBERICHT

Internationales Aktenzeichen

PCT/EP2014/002413

**A. KLASIFIZIERUNG DES ANMELDUNGSGEGENSTANDES**

INV. H03K17/16 H03K17/0812

ADD.

Nach der Internationalen Patentklassifikation (IPC) oder nach der nationalen Klassifikation und der IPC

**B. RECHERCHIERTE GEBIETE**

Recherchierter Mindestprüfstoff (Klassifikationssystem und Klassifikationssymbole)

**H03K**

Recherchierte, aber nicht zum Mindestprüfstoff gehörende Veröffentlichungen, soweit diese unter die recherchierten Gebiete fallen

Während der internationalen Recherche konsultierte elektronische Datenbank (Name der Datenbank und evtl. verwendete Suchbegriffe)

**EPO-Internal, WPI Data**

**C. ALS WESENTLICH ANGESEHENE UNTERLAGEN**

| Kategorie* | Bezeichnung der Veröffentlichung, soweit erforderlich unter Angabe der in Betracht kommenden Teile                                                       | Betr. Anspruch Nr. |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| X          | DE 10 2011 076516 A1 (BOSCH GMBH ROBERT [DE]) 29. November 2012 (2012-11-29)<br>Abbildung 1<br>Zusammenfassung<br>Absatz [0006] - Absatz [0013]<br>----- | 1-10               |

| X          | WO 02/07315 A1 (CT CONCEPT TECHNOLOGIE AG [CH]; THALHEIM JAN [CH])<br>24. Januar 2002 (2002-01-24)<br>Abbildung 9<br>-----                               | 1,9                |

Weitere Veröffentlichungen sind der Fortsetzung von Feld C zu entnehmen  Siehe Anhang Patentfamilie

\* Besondere Kategorien von angegebenen Veröffentlichungen :

"A" Veröffentlichung, die den allgemeinen Stand der Technik definiert, aber nicht als besonders bedeutsam anzusehen ist

"E" frühere Anmeldung oder Patent, die bzw. das jedoch erst am oder nach dem internationalen Anmeldedatum veröffentlicht worden ist

"L" Veröffentlichung, die geeignet ist, einen Prioritätsanspruch zweifelhaft erscheinen zu lassen, oder durch die das Veröffentlichungsdatum einer anderen im Recherchenbericht genannten Veröffentlichung belegt werden soll oder die aus einem anderen besonderen Grund angegeben ist (wie ausgeführt)

"O" Veröffentlichung, die sich auf eine mündliche Offenbarung, eine Benutzung, eine Ausstellung oder andere Maßnahmen bezieht

"P" Veröffentlichung, die vor dem internationalen Anmeldedatum, aber nach dem beanspruchten Prioritätsdatum veröffentlicht worden ist

"T" Spätere Veröffentlichung, die nach dem internationalen Anmeldedatum oder dem Prioritätsdatum veröffentlicht worden ist und mit der Anmeldung nicht kollidiert, sondern nur zum Verständnis des der Erfindung zugrundeliegenden Prinzips oder der ihr zugrundeliegenden Theorie angegeben ist

"X" Veröffentlichung von besonderer Bedeutung; die beanspruchte Erfindung kann allein aufgrund dieser Veröffentlichung nicht als neu oder auf erforderlicher Tätigkeit beruhend betrachtet werden

"Y" Veröffentlichung von besonderer Bedeutung; die beanspruchte Erfindung kann nicht als auf erforderlicher Tätigkeit beruhend betrachtet werden, wenn die Veröffentlichung mit einer oder mehreren Veröffentlichungen dieser Kategorie in Verbindung gebracht wird und diese Verbindung für einen Fachmann naheliegend ist

"&" Veröffentlichung, die Mitglied derselben Patentfamilie ist

Datum des Abschlusses der internationalen Recherche

Absendedatum des internationalen Recherchenberichts

**9. Dezember 2014**

**18/12/2014**

Name und Postanschrift der Internationalen Recherchenbehörde

Europäisches Patentamt, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040,

Fax: (+31-70) 340-3016

Bevollmächtigter Bediensteter

**Simon, Volker**

**INTERNATIONALER RECHERCHENBERICHT**

Angaben zu Veröffentlichungen, die zur selben Patentfamilie gehören

Internationales Aktenzeichen

PCT/EP2014/002413

| Im Recherchenbericht<br>angeführtes Patentdokument | Datum der<br>Veröffentlichung | Mitglied(er) der<br>Patentfamilie                                                                                                   | Datum der<br>Veröffentlichung                                                                                |

|----------------------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| DE 102011076516 A1                                 | 29-11-2012                    | CN 103548266 A<br>DE 102011076516 A1<br>EP 2715939 A1<br>US 2014084827 A1<br>WO 2012159812 A1                                       | 29-01-2014<br>29-11-2012<br>09-04-2014<br>27-03-2014<br>29-11-2012                                           |

| -----                                              |                               |                                                                                                                                     |                                                                                                              |

| WO 0207315                                         | A1 24-01-2002                 | AT 396539 T<br>AU 5559200 A<br>EP 1299950 A1<br>ES 2302695 T3<br>JP 4823470 B2<br>JP 2004504799 A<br>US 6972611 B1<br>WO 0207315 A1 | 15-06-2008<br>30-01-2002<br>09-04-2003<br>01-08-2008<br>24-11-2011<br>12-02-2004<br>06-12-2005<br>24-01-2002 |

| -----                                              |                               |                                                                                                                                     |                                                                                                              |