(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2014년04월23일

(11) 등록번호 10-1388369

(24) 등록일자 2014년04월16일

- (51) 국제특허분류(Int. Cl.)

*H01L 33/02* (2010.01) *H01L 33/04* (2010.01)

*H01L 33/32* (2010.01)

- (21) 출원번호 10-2011-7021897(분할)

- (22) 출원일자(국제) 2005년06월24일

심사청구일자 2011년09월19일

- (85) 번역문제출일자 2011년09월19일

- (65) 공개번호 10-2011-0110868

- (43) 공개일자 2011년10월07일

- (62) 원출원 특허 10-2007-7001904

원출원일자(국제) 2005년06월24일

심사청구일자 2010년06월16일

- (86) 국제출원번호 PCT/US2005/022597

- (87) 국제공개번호 WO 2006/023060

국제공개일자 2006년03월02일

(30) 우선권주장

10/899,791 2004년07월27일 미국(US)

(56) 선행기술조사문헌

JP10065271 A

JP2003218454 A

KR1020030097817 A\*

US20020195606 A1\*

\*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 19 항

심사관 : 김태연

(54) 발명의 명칭 III 족 나이트라이드계 발광 다이오드

**(57) 요 약**

III 족 나이트라이드계 발광소자 및 III 족 나이트라이드계 발광소자를 제조하는 방법이 제공된다. 발광 소자는 n 형 III 족 나이트라이드 층, 적어도 하나의 양자 우물 구조를 포함하며, 상기 n 형 III 족 나이트라이드 층 위에 있는 III 족 나이트라이드계 활성 영역, 상기 활성 영역 위의 인듐을 포함하는 III 족 나이트라이드 층, 상기 인듐을 포함하는 III 족 나이트라이드 층 위의 알루미늄을 포함하는 p 형 III 족 나이트라이드 층, 상기 n 형 III 족 나이트라이드 층 위의 제1 콘택 및 상기 p 형 III 족 나이트라이드 층 위의 제2 콘택을 포함한다. 인듐을 포함하는 III 족 나이트라이드 층은 알루미늄을 더 포함할 수 있다.

**대 표 도 - 도1**

## 특허청구의 범위

### 청구항 1

n 형 III 족 나이트라이드 층;

상기 n 형 III 족 나이트라이드 층 위의 인듐을 포함하는 복수의 양자 우물을 포함하는 III 족 나이트라이드 활성 영역;

상기 n 형 III 족 나이트라이드 층의 반대편의, 상기 활성 영역 위의, 인듐을 포함하는 비도핑(undoped) 4원 (quaternary) III 족 나이트라이드 캐핑층 - 상기 비도핑 4원 III 족 나이트라이드 캐핑층은 상기 활성 영역과 분리됨 - ; 및

상기 비도핑 4원 III 족 나이트라이드 캐핑층 상의 인듐을 포함하지 않는 p 형 III 족 나이트라이드 층을 포함하고,

상기 비도핑 4원 III 족 나이트라이드 캐핑층은 상기 활성 영역의 격자 구조로부터 그 위의 상기 p 형 III 족 나이트라이드 층의 격자 구조로의 전이를 제공하고, 인듐을 포함하지 않는 2원 III 족 나이트라이드 층 바로 위에 있고, 상기 2원 III 족 나이트라이드 층은 상기 활성 영역과 상기 캐핑층 사이의 층 또는 상기 활성 영역의 장벽 층을 포함하는, III 족 나이트라이드계 발광 다이오드.

### 청구항 2

삭제

### 청구항 3

제1항에 있어서,

상기 활성 영역은, 교변하는(alternating) 인듐 갈륨 나이트라이드(InGaN) 양자 우물 층들 및 갈륨 나이트라이드(GaN) 장벽 층들을 포함하고, 상기 비도핑 4원 III 족 나이트라이드 캐핑층은 상기 활성 영역의 GaN 장벽 층 위에 있는 III 족 나이트라이드계 발광 다이오드.

### 청구항 4

제1항에 있어서,

비도핑 갈륨 나이트라이드(GaN) 층은 상기 활성 영역과 상기 비도핑 4원 III 족 나이트라이드 캐핑층 사이에 위치하는 III 족 나이트라이드계 발광 다이오드.

### 청구항 5

제1항에 있어서, 상기 p형 III 족 나이트라이드층은 비도핑 갈륨 나이트라이드(GaN) 층 반대편의 상기 비도핑 4원 III 족 나이트라이드 캐핑층 위의 3원(ternary) p 형 III 족 나이트라이드 층을 포함하는, III 족 나이트라이드 계 발광 다이오드.

### 청구항 6

삭제

### 청구항 7

제5항에 있어서,

상기 비도핑 4원 III 족 나이트라이드 캐핑층은 알루미늄을 포함하는 III 족 나이트라이드계 발광 다이오드.

### 청구항 8

제7항에 있어서,

상기 비도핑 4원 III 층 나이트라이드 캐핑층의 알루미늄(Al) 조성은 구배된(graded) III 층 나이트라이드계 발광 다이오드.

### 청구항 9

제8항에 있어서,

상기 비도핑 4원 III 층 나이트라이드 캐핑층의 상기 알루미늄 조성은 계단식으로 구배된 III 층 나이트라이드계 발광 다이오드.

### 청구항 10

제8항에 있어서,

상기 비도핑 4원 III 층 나이트라이드 캐핑층의 상기 알루미늄 조성은 연속적인 방식으로 구배된 III 층 나이트라이드계 발광 다이오드.

### 청구항 11

제8항에 있어서,

상기 비도핑 4원 III 층 나이트라이드 캐핑층은 비도핑 인듐 알루미늄 갈륨 나이트라이드(InAlGaN)를 포함하는 III 층 나이트라이드계 발광 다이오드.

### 청구항 12

제5항에 있어서,

상기 3원 p 형 III 층 나이트라이드 층은 상기 비도핑 4원 III 층 나이트라이드 캐핑층 바로 위에 있는 III 층 나이트라이드계 발광 다이오드.

### 청구항 13

제12항에 있어서,

상기 3원 p 형 III 층 나이트라이드 층은 알루미늄을 포함하는 III 층 나이트라이드계 발광 다이오드.

### 청구항 14

제13항에 있어서,

상기 3원 p 형 III 층 나이트라이드 층의 알루미늄 조성은 상기 비도핑 4원 III 층 나이트라이드 캐핑층의 알루미늄 조성보다 낮은 III 층 나이트라이드계 발광 다이오드.

### 청구항 15

제12항에 있어서,

상기 비도핑 4원 III 층 나이트라이드 캐핑층은 그 내부의 캐리어 재결합(carrier recombination)으로 인한 광자 방출(photon emission)을 제공하지 않는 III 층 나이트라이드계 발광 다이오드.

### 청구항 16

제12항에 있어서,

상기 비도핑 4원 III 층 나이트라이드 캐핑층 반대편의 상기 3원 p 형 III 층 나이트라이드 층 위의 2원 p 형 III 층 나이트라이드 층; 및

상기 3원 p 형 III 층 나이트라이드 층 반대편의 상기 2원 p 형 III 층 나이트라이드 층 위의 제2 콘택트을 더 포함하는 III 층 나이트라이드계 발광 다이오드.

### 청구항 17

제1항에 있어서,

상기 비도핑 4원 III 족 나이트라이드 캐핑층은 복수의 비도핑 인듐 알루미늄 갈륨 나이트라이드(InAlGaN) 층을 포함하는 III 족 나이트라이드계 발광 다이오드.

### 청구항 18

제1항에 있어서,

상기 비도핑 4원 III 족 나이트라이드 캐핑층은 0 웅스트롬(Å)보다 크고 120 Å 이하의 두께를 갖는 III 족 나이트라이드계 발광 다이오드.

### 청구항 19

제1항에 있어서,

상기 비도핑 4원 III 족 나이트라이드 캐핑층은 상기 활성 영역의 상기 양자 우물들보다 고온에서 성장되는 III 족 나이트라이드계 발광 다이오드.

### 청구항 20

제1항에 있어서,

상기 n 형 III 족 나이트라이드 층 위의 III 족 나이트라이드계 초격자(superlattice) - 상기 초격자는 적어도 2 주기로 교번하는 층들을 가짐 -

를 더 포함하고,

상기 활성 영역은 상기 n 형 III 족 나이트라이드 층 반대면의 상기 초격자 위에 있는 III 족 나이트라이드계 발광 다이오드.

### 청구항 21

제1항에 있어서,

상기 비도핑 4원 III 족 나이트라이드 캐핑층은 상기 활성 영역에 대하여 개선된 결정 품질을 갖는 III 족 나이트라이드계 발광 다이오드.

### 청구항 22

삭제

### 청구항 23

삭제

### 청구항 24

삭제

### 청구항 25

삭제

### 청구항 26

삭제

### 청구항 27

삭제

### 청구항 28

삭제

청구항 29

삭제

청구항 30

삭제

청구항 31

삭제

청구항 32

삭제

청구항 33

삭제

청구항 34

삭제

청구항 35

삭제

청구항 36

삭제

청구항 37

삭제

청구항 38

삭제

청구항 39

삭제

청구항 40

삭제

## 명세서

### 기술분야

[0001] 본 발명은 마이크로전자 소자 및 그 제조방법에 관한 것으로, 특히 발광 다이오드(LED)와 같은 III 족 나이트라이드 반도체 소자에 사용될 수 있는 구조에 관한 것이다.

[0002] 이 출원은, "GROUP III MULTI-QUANTUM WELL LIGHT EMITTING DIODE STRUCTURE"라는 제목의 2001년 5월 30일 출원된 예비 출원 번호 60/294,445, "LIGHT EMITTING DIODE STRUCTURE WITH SUPERLATTICE STRUCTURE"라는 제목의 2001년 5월 30일 출원된 예비 출원 번호 60/294,308 및 "LIGHT EMITTING DIODE STRUCTURE WITH MULTI-QUANTUM WELL AND SUPERLATTICE STRUCTURE"라는 제목의 2001년 5월 30일 출원된 예비 출원 번호 60/294,378으로부터의 우선권의 이익을 주장하는, "GROUP III NITRIDE BASED LIGHT EMITTING DIODE STRUCTURE WITH A QUANTUM WELL AND SUPERLATTICE, GROUP III NITRIDE BASED QUANTUM WELL STRUCTURES AND GROUP III NITRIDE

"BASED SUPERLATTICE STRUCTURES"라는 제목의 2002년 5월 7일 출원된 미국 특허 출원 번호 10/140,796의 일부 계속출원이며, 상기 출원들의 개시내용은 여기에서 완전히 설명된 것처럼 참조에 의하여 여기에 통합된다.

## 배경 기술

[0003]

발광 다이오드는 소비, 상업적 응용에 널리 사용된다. 기술분야에 숙련된 자에게 잘 알려진 바와 같이, 발광 다이오드는 일반적으로 마이크로전자 기판 위의 다이오드 영역을 포함한다. 마이크로전자 기판은 예를 들면, 갈륨 아세나이드, 갈륨 포스파이드, 이들의 합금, 실리콘 카바이드 및/또는 사파이어를 포함할 수 있다. LED에서의 계속된 발전은 가시영역의 스펙트럼과 가시영역을 넘는 영역을 커버할 수 있는 매우 효율적이고 기계적으로 강한 광원을 얻었다. 이 성질은 고체 소자의 잠재적으로 긴 수명과 결합하여 다양한 새로운 디스플레이 응용을 가능하게 하고, LED를 잘 확립되어 있는 백열 램프와 경쟁할 수 있는 지위에 올려놓을 수 있다.

[0004]

갈륨 나이트라이드계(gallium nitride based) LED와 같은 III 족 나이트라이드계 LED를 제조하는데 있어서 한 가지 어려움은, 고품질의 갈륨 나이트라이드를 제조하는데 있었다. 통상, 갈륨 나이트라이드 LED는 사파이어 또는 실리콘 카바이드 기판 위에 제조되어 왔다. 그러한 기판은 기판과 갈륨 나이트라이드 사이의 결정 격자(crystal lattice) 사이의 부정합(mismatch)이 있을 수 있다. 사파이어 및/또는 실리콘 카바이드 위의 갈륨 나이트라이드 성장에 관련된 잠재적인 문제들을 극복하기 위하여 여러가지 기술들이 채용되어 왔다. 예를 들면, 알루미늄 나이트라이드(AlN)가 실리콘 카바이드 기판과 III 족 활성층(active layer), 특히 갈륨 나이트라이드 활성층 사이의 베퍼로서 사용될 수 있다. 전형적으로, 그러나, 알루미늄 나이트라이드는 도전성이라기보다는 절연성이다. 그러므로, 알루미늄 나이트라이드 베퍼층을 갖는 구조는 통상 도전성의 실리콘 카바이드 기판을 III 족 나이트라이드 활성층으로 전기적으로 연결시키기 위하여 알루미늄 나이트라이드 베퍼를 우회하는 연결 콘택을 필요로 한다.

[0005]

다르게는, 갈륨 나이트라이드(GaN), 알루미늄 갈륨 나이트라이드(AlGaN) 또는 갈륨 나이트라이드와 알루미늄 갈륨 나이트라이드의 조합과 같은 도전성의 베퍼층 물질이 알루미늄 나이트라이드(AlN) 베퍼층과 함께 통상 사용되는 연결 콘택을 제거할 수 있도록 한다. 통상, 연결 콘택을 제거하는 것은 에피택셜층 두께를 줄이고, 소자를 제조하는데 필요한 제조 단계의 수를 감소시키고, 전체 칩 크기를 줄이고/또는 소자 효율을 증가시킨다. 따라서 III 족 나이트라이드 소자는 저비용으로 고성능을 갖도록 생산될 수 있다. 그러나, 이러한 도전성의 베퍼 물질들이 이러한 장점들을 제공함에도 불구하고, 이들의 실리콘 카바이드와의 결정 격자 정합은 알루미늄 나이트라이드보다 덜 만족스럽다.

[0006]

고품질의 갈륨 나이트라이트를 제공하는데 있어서의 위에서 기술한 어려움들은 소자의 효율을 감소시킬 수 있다. III 족 나이트라이드계 소자의 출력(output)을 향상시키기 위한 시도는 소자의 활성 영역의 형태(configuration)를 변화시키는 것을 포함한다. 그러한 시도는 예를 들면, 단일 및/또는 이중 혜테로구조의 활성 영역의 사용을 포함하였다. 유사하게, 하나 또는 그 이상의 III 족 나이트라이드 양자 우물(quantum well)을 갖는 양자 우물 소자가 또한 기술되었다. 그러한 시도는 III 족에 기반을 둔 소자의 효율을 향상시켰지만, 여전히 효율을 더 향상시킬 여지가 있다.

## 발명의 내용

### 과제의 해결 수단

[0007]

본 발명의 일부 실시예는 n 형 III 족 나이트라이드 층, 적어도 하나의 양자 우물 구조를 포함하며, 상기 n 형 III 족 나이트라이드 층 위에 있는 III 족 나이트라이드계 활성 영역, 상기 활성영역 위의 인듐을 포함하는 III 족 나이트라이드 층, 상기 인듐을 포함하는 III 족 나이트라이드 층 위의 알루미늄을 포함하는 p 형 III 족 나이트라이드 층, 상기 n 형 III 족 나이트라이드 층 위의 제1 콘택 및 상기 p 형 III 족 나이트라이드 층 위의 제2 콘택을 포함하는 III 족 나이트라이드계 발광소자 및 III 족 나이트라이드계 발광소자를 제조하는 방법을 제공한다.

[0008]

본 발명의 다른 실시예에서, 인듐을 포함하는 III 족 나이트라이드 층은 알루미늄을 더 포함한다. 예를 들면, 상기 인듐을 포함하는 III 족 나이트라이드 층은 InAlGaN을 포함할 수 있다. 상기 인듐을 포함하는 III 족 나이트라이드 층은 또한 InGaN을 포함할 수 있다. 상기 인듐을 포함하는 III 족 나이트라이드 층은 약 20 내지 약 320 Å의 두께일 수 있다.

[0009]

본 발명의 특정 실시예들에서, 상기 인듐을 포함하는 III 족 나이트라이드 층은 상기 활성영역에서 먼 영역에서 상기 활성영역에 인접한 영역보다 더 높은 Al 조성을 갖는 InAlGaN을 포함한다. 일부 실시예들에서, 상기 InAlGaN 층은 연속적으로 구배될 수 있다. 다른 실시예들에서, 상기 InAlGaN 층은 다른 Al 조성을 갖는 복수의

InAlGaN 층을 포함할 수 있다.

[0010] 본 발명의 또 다른 실시예들에서, 상기 인듐을 포함하는 III 족 나이트라이드 층은  $\text{In}_x\text{Al}_y\text{Ga}_{1-x-y}\text{N}$ ,  $0 < x \leq 0.2$ ,  $0 \leq y \leq 0.4$  의 제1 층 및  $\text{In}_w\text{Al}_z\text{Ga}_{1-w-z}\text{N}$ ,  $0 < w \leq 0.2$ ,  $y \leq z \leq 1$  의 제2 층; 을 포함할 수 있다. 상기 제1 층은 약 10 내지 200 Å의 두께를 갖고, 상기 제2 층은 약 10 내지 120 Å의 두께를 가질 수 있다. 본 발명의 특정 실시예들에서, 상기 제1 층은 약 80 Å의 두께를 갖고,  $x=0.1$  및  $y=0.25$  이고, 상기 제2 층은 약 30 Å의 두께를 갖고,  $w=0.05$  및  $z=0.55$  이다.

[0011] 본 발명의 부가적인 실시예들에서, 발광 소자는 상기 제2 콘택과 상기 알루미늄을 포함하는 p 형 III 족 나이트라이드 층 사이에 배치된 p 형 III 족 나이트라이드 층을 더 포함한다. 상기 제2 콘택과 알루미늄을 포함하는 상기 p 형 III 족 나이트라이드 층 사이에 배치된 p 형 III 족 나이트라이드 층은 또한 인듐을 포함할 수 있다. 상기 알루미늄을 포함하는 p 형 III 족 나이트라이드 층은 또한 인듐을 포함할 수 있다.

[0012] 본 발명의 일부 실시예들에서, 상기 제1 콘택과 상기 n 형 III 족 나이트라이드 층 사이에 배치된 실리콘 카바이드 기판을 더 포함한다.

[0013] 본 발명의 일부 실시예들은 기판 위의 n 형 갈륨 나이트라이드계 층, 적어도 하나의 양자 우물 구조를 포함하며, 상기 n 형 갈륨 나이트라이드계 층 위에 있는 갈륨 나이트라이드계 활성 영역, 상기 활성영역 위의 인듐을 포함하는 갈륨 나이트라이드계 층, 인듐을 포함하는 상기 갈륨 나이트라이드계 층 위의 알루미늄을 포함하는 p 형 갈륨 나이트라이드계 층, 상기 n 형 갈륨 나이트라이드계 층 위의 제1 콘택 및 상기 p 형 갈륨 나이트라이드계 층 위의 제2 콘택을 포함하는 발광 소자 및 발광 소자의 제조방법을 제공한다.

[0014] 본 발명의 특정 실시예들에서, 상기 n 형 갈륨 나이트라이드 층은 상기 기판 위의 n 형 AlGaN 층 및 상기 n 형 AlGaN 층 위의 n 형 GaN 층을 포함한다. 상기 갈륨 나이트라이드계 활성 영역은 복수의 InGaN/GaN 양자 우물을 포함할 수 있다.

[0015] 본 발명의 다른 실시예들에서, 상기 p 형 갈륨 나이트라이드계 층은 상기 인듐을 포함하는 갈륨 나이트라이드계 층 위의 p 형 AlGaN 층 및 상기 p 형 AlGaN 층 위의 p 형 GaN 층;을 포함한다. 상기 제2 콘택은 상기 p 형 GaN 층 위에 있다. 상기 인듐을 포함하는 갈륨 나이트라이드계 층은  $\text{In}_x\text{Al}_y\text{Ga}_{1-x-y}\text{N}$ ,  $0 < x \leq 0.2$ ,  $0 \leq y \leq 0.4$  의 제1 층 및  $\text{In}_w\text{Al}_z\text{Ga}_{1-w-z}\text{N}$ ,  $0 < w \leq 0.2$ ,  $y \leq z \leq 1$  의 제2 층을 포함할 수 있다. 상기 제1 층은 약 10 내지 200 Å의 두께를 갖고, 상기 제2 층은 약 10 내지 120 Å의 두께를 가질 수 있다. 본 발명의 특정 실시예들에서, 상기 제1 층은 약 80 Å의 두께를 갖고,  $x=0.1$  및  $y=0.25$  이고, 상기 제2 층은 약 30 Å의 두께를 갖고,  $w=0.05$  및  $z=0.55$  이다.

[0016] 본 발명의 또 다른 실시예들에서, 상기 기판은 실리콘 카바이드이고, 상기 제1 콘택은 상기 n 형 AlGaN 층의 반대편의 상기 실리콘 카바이드 기판 위에 있다.

### 도면의 간단한 설명

[0017] 본 발명의 다른 특징들은 첨부된 도면과 함께 읽힐 때 특정 실시예의 상세한 기술로부터 더욱 잘 이해될 것이다.

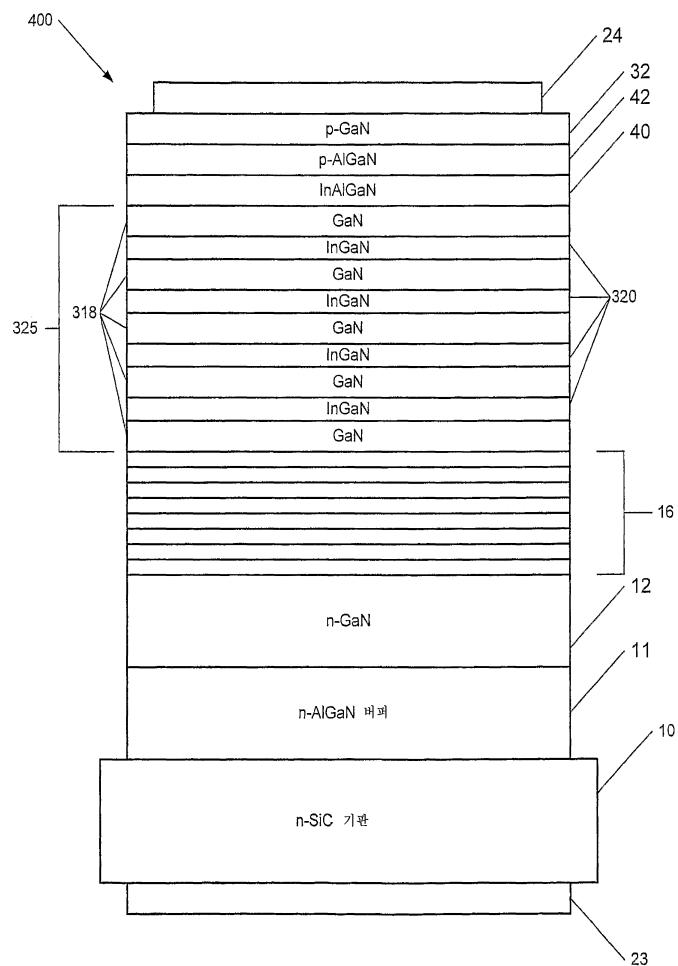

도 1은 본 발명의 실시예들을 통합하는 III 족 나이트라이드 발광 다이오드의 개략적인 도면이다.

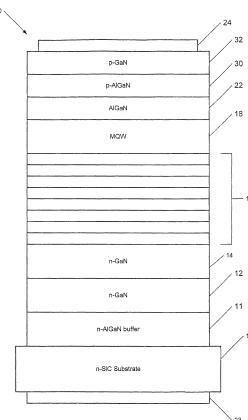

도 2는 본 발명의 다른 실시예들을 통합하는 III 족 나이트라이드 발광 다이오드의 개략적인 도면이다.

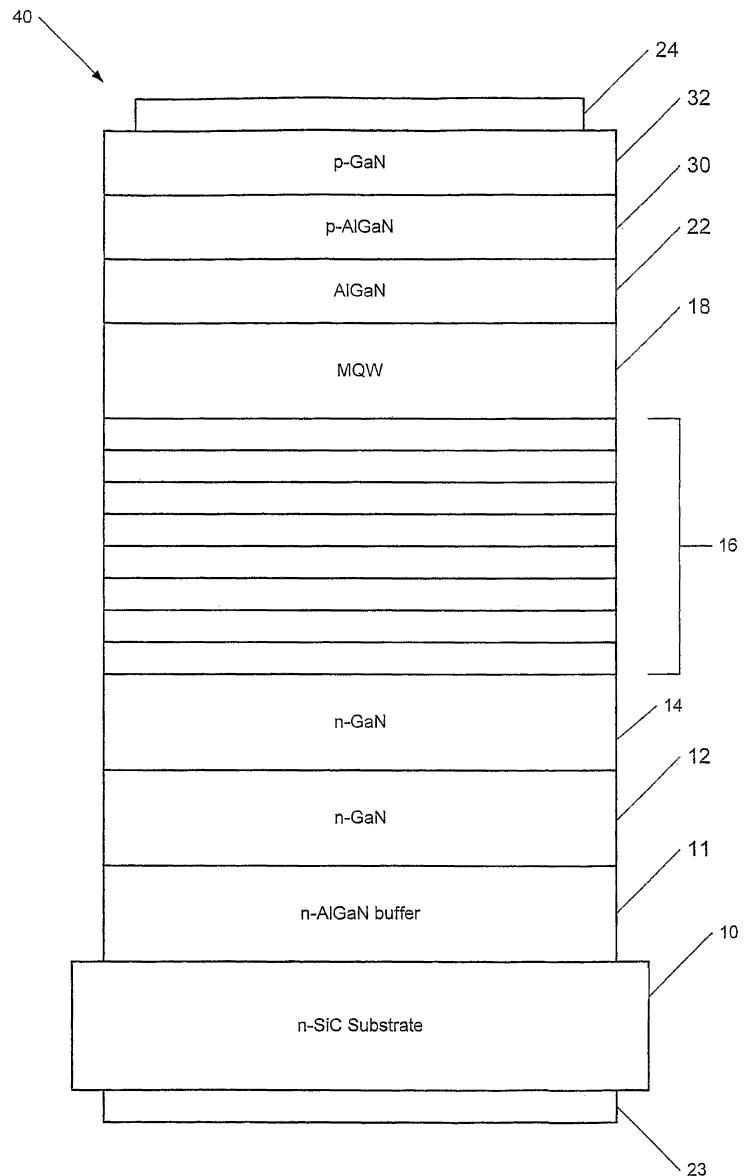

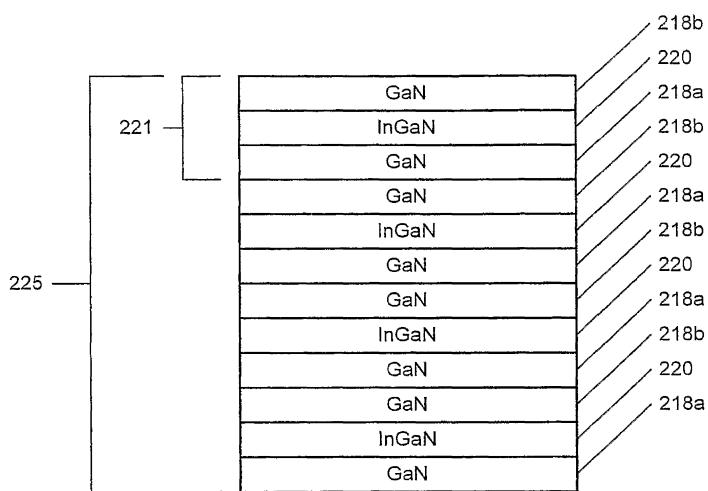

도 3은 본 발명의 부가적인 실시예들에 따른 양자 우물 구조 및 다중 양자 우물 구조의 개략적인 구조이다.

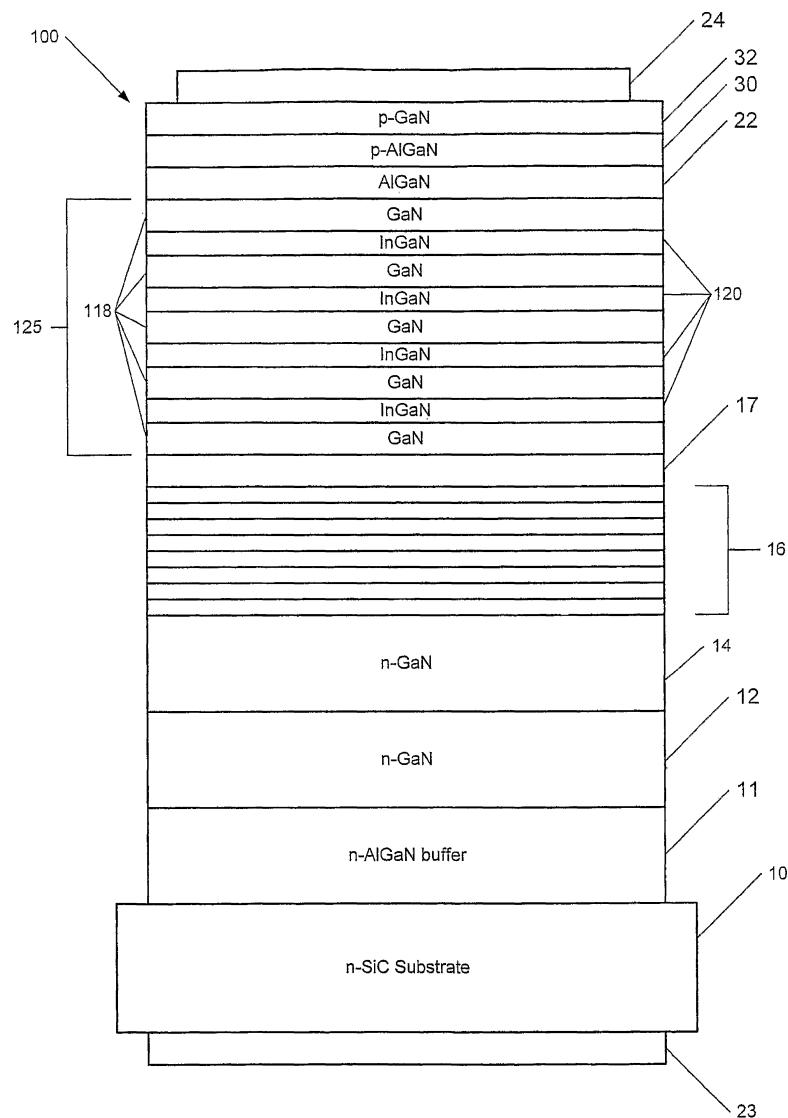

도 4는 본 발명의 다른 실시예들을 통합하는 III 족 나이트라이드 발광 다이오드의 개략적인 도면이다.

### 발명을 실시하기 위한 구체적인 내용

[0018] 본 발명은 본 발명의 실시예들이 보여지는 관련 도면을 참조하여 여기에서 더욱 상세하게 기술될 것이다. 그러나 본 발명은 여기에 설명된 실시예들로만 한정되는 것으로 해석되서는 안된다. 오히려, 이 실시예들은 그 개시가 당업자에게 철저하고 완전하며 발명의 범위를 완전히 전달하기 위하여 제공된다. 도면에서, 층들의 두께 및 영역들은 명확성을 위하여 과장된다. 동일한 숫자는 끝까지 동일한 요소를 지칭한다. 여기에서 사용되는 바와 같이 "및/또는"의 용어는 관련되어 열거된 항목들의 하나 또는 그 이상의 임의의 또는 모든 조합을 포함한

다.

[0019] 여기에 사용된 용어들은 특정 실시예들만을 기술하려는 목적으로, 본 발명을 제한하려는 의도는 아니다. 여기에서 사용된 바와 같이 단수의 형태는 본문에서 명확하게 다르게 지시하지 않으면 복수의 형태도 포함하는 것으로 의도된다. 더 나아가 "포함한다(comprises)" 및/또는 "포함하는(comprising)"의 용어가 본 상세한 설명에서 사용되는 경우에는 상술된 형태, 복합체(integer), 단계, 작용, 요소, 및/또는 구성요소의 존재를 특정하지만, 하나 또는 그 이상의 다른 형태, 복합체, 단계, 작용, 요소, 구성요소, 및/또는 이들의 그룹의 존재 또는 부가를 제외하지 않는다.

[0020] 충, 영역 또는 기판과 같은 요소가 다른 요소 "위(on)"에 존재하는 것으로 또는 "위로(onto)" 확장되는 것으로 기술되는 경우, 그 요소는 다른 요소의 직접 위에 있거나 직접 위로 확장될 수 있고, 또는 중간의 요소가 존재할 수도 있다. 반면에, 하나의 요소가 다른 요소 "바로 위(directly on)"에 있거나 "바로 위로(directly onto)" 확장된다고 언급되는 경우, 다른 중간 요소들은 존재하지 않는다. 또한, 하나의 요소가 다른 요소에 "연결(connected)"되거나 "결합(coupled)"된다고 기술되는 경우, 그 요소는 다른 요소에 직접 연결되거나 직접 결합될 수 있고, 또는 중간 요소가 존재할 수도 있다. 반면에, 하나의 요소가 다른 요소에 "직접 연결(directly connected)"되거나 "직접 결합(directly coupled)"된다고 기술되는 경우에는 다른 중간 요소가 존재하지 않는다. 같은 숫자는 발명의 상세한 설명의 처음부터 끝까지 같은 요소를 지칭한다.

[0021] 비록 제1, 제2, 기타의 용어가 여기에서 여러가지 요소, 구성요소, 영역, 충 및/또는 구간을 기술하는데 사용되더라도 이 요소, 구성요소, 영역, 충 및/또는 구간은 이 용어에 의하여 제한되어서는 안된다. 이 용어들은 단지 하나의 요소, 구성요소, 영역, 충 또는 구간을 다른 영역, 충 또는 구간과 구별하기 위하여 사용된다. 따라서, 이하에서 논의되는 제1 요소, 구성요소, 영역, 충 또는 구간은 본 발명의 가르침으로부터 벗어나지 않고 제2 요소, 구성요소, 영역, 충 또는 구간을 지칭할 수 있다.

[0022] 더욱이, "하부의(lower)" 또는 "바닥(bottom)" 및 "상부의(upper)" 또는 "상부(top)"와 같은 상대적인 용어들은 여기에서 도면에 도시된 바와 같이 하나의 요소의 다른 요소에 대한 관계를 기술하는데 사용될 수 있다. 상대적인 용어들은 도면에 묘사된 방향(orientation)에 부가하여 장치의 다른 방향을 포함하기 위한 의도를 갖는 것으로 이해될 것이다. 예를 들면, 도면에서 장치가 뒤집혔으면, 다른 요소들의 "하부의(lower)" 면에 존재하는 것으로 기술된 요소들은 그 다른 요소들의 "상부의(upper)" 면에 향하는 것이 될 수 있다. 따라서 예시된 용어 "하부의(lower)"는 형태의 특정한 방향에 따라 "하부의(lower)" 및 "상부의(upper)"의 모든 방향을 포함할 수 있다. 비슷하게, 도면 중 하나에서 장치가 뒤집혔으면, 다른 요소들의 "아래(below)" 또는 "바로 밑(beneath)"에 있는 것으로 기술된 요소들은 그 다른 요소들의 "위(above)"로 향할 수 있다. 예시된 용어 "아래(below)" 또는 "바로 밑(beneath)"은 따라서 위와 아래의 양 방향을 포함할 수 있다.

[0023] 본 발명의 실시예들은 본 발명의 이상화된 실시예들의 개략적인 도시인 단면도에 관련하여 여기에서 기술된다. 그러므로, 예를 들면, 제조 기술 및/또는 허용한도의 결과로서 도면의 형태로부터의 변형이 예상될 수 있다. 그러므로, 본 발명의 실시예들은 여기에 도시된 영역의 특정 형태로 제한되는 것이 아니라 예를 들면, 제조로부터 기인하는 형태의 변형을 포함하는 것으로 해석되어야 할 것이다. 예를 들면, 직사각형으로 도시되거나 기술된 식각된 영역은, 통상, 라운드되거나 곡면의(curved) 형태를 가질 수 있다. 그러므로, 도면에 도시된 영역들은 사실은 개략적인 것이고, 이들의 형태는 소자의 영역의 정확한 형태를 도시하기 위한 의도를 갖지 않고, 본 발명의 범위를 제한하려는 의도를 갖지 않는다.

[0024] 다르게 정의되지 않으면, (기술적이고 과학적인 용어들을 포함하여) 여기에 사용된 모든 용어들은 이 발명이 속하는 분야에서 통상적인 기술을 갖는 사람에 의해 일반적으로 이해되는 것과 동일한 의미를 갖는다. 더 나아가 일반적으로 사용되는 사전에 정의된 것과 같은 용어들은 관련 분야의 상황에서의 의미와 일관되는 의미를 갖는 것으로 해석되어야 하며, 여기에서 그렇게 정의되지 않는 한 이상적이거나 지나치게 형식적인 의미로 해석되어서는 안된다.

[0025] 다른 형태에 "인접하게(adjacent)" 배치된 구조 또는 형태에 대한 참조는 인접한 형태와 오버랩하거나 인접한 형태의 아래에 있는 부분을 갖는 것으로 관련 분야의 기술자들에게 또한 이해될 것이다.

[0026] 비록 여기에 기술된 LED 들의 다양한 실시예들이 기판을 포함하지만, 기술분야의 숙련된 자들은 LED 를 포함하는 독립(free standing) 에피택설층이 그 위에 자라는 결정질의 에피택설 성장 기판은 제거될 수 있고, 본래의 기판보다 더 나은 열적, 전기적, 구조적 및/또는 광학적 특성을 갖을 수 있는 대용의 운반 기판 또는 서브마운트(submount)에 독립 에피택설층이 마운트될 수 있음을 이해할 것이다. 여기에 기술된 발명은 결정질의 에피택

설 성장 기판을 갖는 구조에 한정되지 않고 에피택셜층이 본래의 성장 기판으로부터 제거되어 대용의 운반 기판에 본딩된 구조와 연관되어 사용될 수 있다.

[0027] 본 발명의 실시예들이 발광 다이오드(LED) 구조(40)을 도시하는 도 1과 관련하여 기술될 것이다. 도 1의 LED 구조(40)는 기판(10)을 포함하며, 이것은 바람직하게는 4H 또는 6H의 n 형 실리콘 카바이드이다. 기판(10)은 또한 사파이어, 벌크 갈륨 나이트라이드 또는 다른 적절한 기판을 포함할 수 있다. 도 1의 LED 구조(40)에는 기판(10) 위의 갈륨 나이트라이드계의 반도체층들을 포함하는, 층으로 된(layered) 반도체 구조가 포함되어 있다. 즉, 도시된 LED 구조(40)는 다음의 층들을 포함한다: 도전성의 베퍼층(11), 제1 실리콘-도핑 GaN 층(12), 제2 실리콘-도핑 GaN 층(14), 실리콘-도핑 GaN 및/또는 InGaN 의 교대층들을 포함하는 초격자(superlattice) 구조(16), 다중-양자 우물 구조(multi-quantum well structure)에 의해 제공될 수 있는 활성 영역(18), 도핑되지 않은 GaN 및/또는 AlGaN 층(22), p 형 불순물로 도핑된 AlGaN 층(30) 및 역시 p 형 불순물로 도핑된 GaN 콘택층(32). 구조는 또한 기판(10) 위의 n 형 오믹 콘택(23) 및 콘택층(32) 위의 p 형 오믹 콘택(24)을 포함한다.

[0028] 베퍼층(11)은 바람직하게는 n 형 AlGaN이다. 실리콘 카바이드와 III 족-나이트라이드 물질 사이의 베퍼층은 본 발명의 양수인에게 양도된 "Vertical Geometry InGaN Light Emitting Diode" 란 제목의 미국 특허 5,393,993, 5,523,589 및 미국 출원 번호 09/154,363에 제공되어 있으며, 그 개시 내용은 여기에 완전히 개시되어 있는 것처럼 참조에 의해 통합된다. 유사하게, 본 발명의 실시예들은 또한 "Group III Nitride Photonic Devices on Silicon Carbide Substrates With Conductive Buffer Interlayer Structure" 란 제목의 미국 특허 번호 6,201,262에 기술된 것과 같은 구조를 포함할 수 있으며, 그 기술 내용은 여기에 완전히 개시되어 있는 것처럼 참조에 의해 통합된다.

[0029] GaN 층(12)은 바람직하게 약 500 과 4000 nm 사이의 두께이고, 가장 바람직하게는 약 1500 nm 두께이다. GaN 층(12)은 약  $5 \times 10^{17}$  에서  $5 \times 10^{18} \text{ cm}^{-3}$  의 레벨로 실리콘으로 도핑될 수 있다. GaN 층(14)은 바람직하게 약 10 과 500 nm 사이의 두께이고, 가장 바람직하게는 약 80 Å 두께이다. GaN 층(14)은 약  $5 \times 10^{19}$  보다 적은 레벨로 실리콘으로 도핑될 수 있다.

[0030] 도 1에 도시된 바와 같이, 본 발명의 일 실시예에 따른 초격자 구조(16)는  $\text{In}_x\text{Ga}_{1-x}\text{N}$  과  $\text{In}_y\text{Ga}_{1-y}\text{N}$  의 교대층들을 포함하며, 여기서 X는 0 과 1 사이이고, X는 Y와 같지 않다. 바람직하게는, X=0 이고 InGaN 의 교대층들의 각각의 두께는 약 5-40 Å이고, GaN의 교대층들의 각각의 두께는 약 5-100 Å이다. 일부 실시예들에서, GaN 층들은 약 30 Å 두께이고, InGaN 층들은 약 15 Å 두께이다. 초격자 구조(16)는 약 5 에서부터 50 주기를 포함할 수 있다. (여기서 한 주기는 초격자를 포함하는  $\text{In}_x\text{Ga}_{1-x}\text{N}$  과  $\text{In}_y\text{Ga}_{1-y}\text{N}$  층들의 각각의 한 반복과 같다) 일 실시예에서, 초격자 구조(16)는 25 주기를 포함한다. 다른 실시예에서, 초격자 구조(16)는 10 주기를 포함한다. 주기의 수는, 그러나, 예를 들면, 각 층들의 두께를 증가시킴으로써 감소될 수 있다. 그러므로, 예를 들면, 층들의 두께를 두배로 하고 주기의 수를 반으로 할 수 있다. 다르게는, 주기의 수와 두께가 서로 독립적일 수 있다.

[0031] 바람직하게는, 초격자 구조(16)는 약  $1 \times 10^{17} \text{ cm}^{-3}$  로부터 약  $5 \times 10^{19} \text{ cm}^{-3}$  의 레벨로 실리콘과 같은 n 형 불순물로 도핑된다. 그러한 도핑 레벨은 초격자 구조(16)의 층의 실질적인 도핑 또는 평균 도핑일 수 있다. 그러한 도핑 레벨이 평균 도핑이라면, 초격자 구조(16)에 인접한 인접한 층들의 도핑이 초격자 구조(16)에 인접한 층들과 초격자 구조(16)에 걸쳐서 평균이 되는, 원하는 평균 도핑을 제공하는 초격자 구조(16)에 인접한 도핑된 층들을 제공하는 것이 유리할 것이다. 기판(10)과 활성영역(18) 사이에 초격자 구조(16)를 제공함으로써, InGaN 계의 활성영역(18)을 그 위에 성장시킬 더 나은 표면이 제공될 수 있다. 어떤 작용 원리에 구속되는 것을 바라는 것은 아니지만, 초격자 구조(16)의 스트레인 효과(strain effect)가 고품질의 InGaN을 포함하는 활성영역의 성장을 이끄는 성장 표면을 제공한다고 여겨진다. 더욱이, 초격자는 소자의 동작 전압에 영향을 끼치는 것으로 알려져 있다. 초격자의 두께 및 조성 변수의 적절한 선택은 동작 전압을 감소시키고 광학적 효율을 증가시킬 수 있다.

[0032] 초격자 구조(16)는 구조에서 고품질의 InGaN 층들을 성장시킬 수 있는 질소 또는 다른 가스의 분위기에서 성장될 수 있다. 질소 분위기에서 실리콘-도핑된 GaN 층 위에 실리콘-도핑된 InGaN/GaN 초격자를 성장함에 의하여, 최적화된 스트레인으로 향상된 결정성과 도전성을 갖는 구조가 실현될 수 있다.

[0033] 본 발명의 일부 실시예들에서, 활성영역(18)은 단일 또는 이중 헤테로정션 활성영역 뿐만 아니라 단일 또는 다

중-양자 우물 구조를 포함할 수 있다. 본 발명의 특정 실시예들에서, 활성영역(18)은 (도 1에 도시되지 않은) 장벽층들에 의해 분리된 다중의 InGaN 양자 우물층들을 포함하는 다중-양자 우물 구조를 포함할 수 있다.

[0034] 층(22)은 활성영역(18) 위에 제공되며 바람직하게는 약 0 과 120 Å 사이의 두께인 도핑되지 않은 GaN 또는 AlGaN 이다. 여기에 사용된 바와 같이, 도핑되지 않은 것은 의도적으로 도핑되지 않은 것을 지칭한다. 층(22)은 바람직하게는 약 35 Å의 두께이다. 층(22)이 AlGaN 을 포함한다면, 그러한 층에서 알루미늄의 퍼센트는 바람직하게는 약 10-30% 이고, 가장 바람직하게는 약 24% 이다. 층(22)의 알루미늄의 레벨은 계단형으로 또는 연속적으로 감소하는 형태로 점차 변화될 수 있다. 층(22)의 결정 품질을 향상시키기 위하여 층(22)은 양자 우물 영역(25)에서의 성장 온도보다 더 높은 온도에서 성장될 수 있다. 도핑되지 않은 GaN 또는 AlGaN 의 부가적인 층들이 층(22)의 주위에 포함될 수 있다. 예를 들면, LED 1은 활성영역(18)과 층(22) 사이에 약 6-9 Å 두께의 도핑되지 않은 AlGaN의 부가층을 포함할 수 있다.

[0035] 마그네슘과 같은 p 형 불순물로 도핑된 AlGaN 층(30)이 층(22) 위에 제공된다. AlGaN 층(30)은 약 0 과 300 Å 사이의 두께일 수 있고(inclusively) 바람직하게는 약 130 Å 두께이다. P 형의 GaN의 콘택층(32)이 층(30)위에 제공되며 바람직하게 약 1800 Å 두께이다. 오믹 콘택(24, 25)이 p-GaN 콘택층(32)과 기판(10) 위에 각각 제공된다.

[0036] 도 2는 다중-양자 우물 활성영역을 포함하는 본 발명의 다른 실시예들을 도시한다. 도 2에 도시된 본 발명의 실시예들은 기판(10) 위에 성장된 갈륨 나이트라이드-계 반도체층들을 포함하는 층으로 된 반도체 구조(100)를 포함한다. 위에서 기술된 바와 같이, 기판(10)은 SiC, 사파이어 또는 벌크 갈륨 나이트라이드일 수 있다. 도 2에 도시된 바와 같이, 본 발명의 특정한 실시예들에 따른 LED는 도전성의 베퍼층(11), 제1 실리콘-도핑 GaN 층(12), 제2 실리콘-도핑 GaN 층(14), 실리콘-도핑 GaN 및/또는 InGaN의 교대층들을 포함하는 초격자(superlattice) 구조(16), 다중-양자 우물 구조를 포함하는 활성 영역(125), 도핑되지 않은 GaN 또는 AlGaN 층(22), p 형 불순물로 도핑된 AlGaN 층(30) 및 역시 p 형 불순물로 도핑된 GaN 콘택층(32)을 포함할 수 있다. LED는 또한 기판(10) 위의 n 형 오믹 콘택(23) 및 콘택층(32) 위의 p 형 오믹 콘택(24)을 포함한다. 기판(10)이 사파이어인 본 발명의 실시예들에서, n 형 오믹 콘택(23)은 n 형 GaN 층(12) 및/또는 n 형 GaN 층(14)위에 제공될 수 있다.

[0037] 도 1에 관련하여 위에서 기술된 바와 같이, 베퍼층(11)은 바람직하게는 n 형 AlGaN이다. 유사하게, GaN 층(12)은 바람직하게 약 500 과 4000 nm 사이의 두께이고(inclusively), 가장 바람직하게는 약 1500 nm 두께이다. GaN 층(12)은 약  $5 \times 10^{17}$  에서  $5 \times 10^{18} \text{ cm}^{-3}$  의 레벨로 실리콘으로 도핑될 수 있다. GaN 층(14)은 바람직하게 약 10 과 500 nm 사이의 두께이고(inclusively), 가장 바람직하게는 약 80 Å 두께이다. GaN 층(14)은 약  $5 \times 10^{19}$  보다 적은 레벨로 실리콘으로 도핑될 수 있다. 초격자 구조(16)가 도 1과 관련하여 위에서 기술된 바와 같이 또한 제공될 수 있다.

[0038] 활성영역(125)은 장벽층(118)에 의해 분리된 다중 InGaN 양자 우물층(120)을 포함하는 다중-양자 우물 구조를 포함하여 구성된다. 장벽층(118)은  $0 \leq X < 1$  인  $\text{In}_x\text{Ga}_{1-x}\text{N}$  을 포함한다. 바람직하게 장벽층(118)의 인듐 조성은 양자 우물층(120)의 것보다 적으며, 그리하여 장벽층(118)은 양자 우물층(120)보다 더 큰 밴드갭을 갖는다. 장벽층(118)과 양자 우물층(120)은 도핑되지 않을 수 있다(즉, 실리콘이나 마그네슘과 같은 불순물 원자로 고의적으로 도핑되지 않을 수 있다). 그러나 특히 자외선 발광을 희망하는 경우, 장벽층(118)을 실리콘으로  $5 \times 10^{19} \text{ cm}^{-3}$  보다 적은 레벨로 도핑하는 것이 바람직할 수 있다.

[0039] 본 발명의 다른 실시예들에서, 장벽층(118)은  $0 < X < 1$ ,  $0 \leq Y < 1$  및  $X+Y \leq 1$  인  $\text{Al}_x\text{In}_y\text{Ga}_{1-x-y}\text{N}$  을 포함하여 구성된다. 장벽층(118)의 결정에 알루미늄을 포함함으로써, 장벽층(118)은 양자 우물층(120)에 격자-정합될 수 있고, 그에 의하여 양자 우물층(120)에 향상된 결정 품질을 제공하여, 소자의 발광 효율을 증가시킬 수 있다.

[0040] 도 3을 참조하면, 갈륨 나이트라이드계 소자의 다중-양자 우물 구조를 제공하는 본 발명의 실시예들이 도시되어 있다. 도 3에 도시된 다중-양자 우물 구조는 도 1 및/또는 도 2에 도시된 LED 의 활성 영역을 제공할 수 있다. 도 3에 보이는 바와 같이, 활성영역(225)은 높은 결정 품질을 갖는 우물 지지층(well support layer)(218a), 양자 우물층(quantum well layer)(220) 및 양자 우물층(220)을 위한 보호 캐핑층으로서 역할을 하는 캐핑층(218b)을 포함하는 주기적으로 반복되는 구조(221)을 포함하여 구성된다. 구조(221)가 성장되면, 캐핑층(218b)과 우물 지지층(218a)이 함께 인접한 양자 우물들(220) 사이의 장벽층을 형성한다. 바람직하게는, 고품질의 우물 지지층(218a)이 InGaN 양자 우물층(220)을 성장시키는데 사용되는 온도보다 더 높은 온도에서 성장된다.

본 발명의 일부 실시예들에서, 우물 지지층(218a)이 캐핑층(218b)보다 더 느린 성장속도로 성장된다. 다른 실시예들에서, 더 낮은 성장속도는 더 져온의 성장 공정 동안 사용될 수 있고, 더 높은 성장속도는 더 고온의 성장 공정 동안 사용될 수 있다. 예를 들면, InGaN 양자 우물층(220)을 성장시키기 위한 고품질의 표면을 얻기 위하여, 우물 지지층(218a)은 약 700 과 900 °C 사이의 성장 온도에서 성장될 수 있다. 그 후, 고품질의 InGaN 양자 우물층(220)의 성장을 허용하도록 성장 챔버의 온도는 약 0 에서 200°C 만큼 낮아진다. 그 후, 온도는 낮은 InGaN 성장 온도에서 유지되면서, 캐핑층(218b)이 성장된다. 이와 같은 방법으로, 고품질의 InGaN 층들을 포함하는 다중-양자 우물 영역이 제조될 수 있다.

[0041] 도 2 및 도 3의 활성영역(125, 225)은 바람직하게는 질소 분위기에서 성장되어, 향상된 InGaN 결정 품질을 제공할 수 있다. 장벽층(118), 우물 지지층(218a) 및/또는 캐핑층(218b)은 약 50-400 Å 사이의 두께일 수 있다. 대응되는 우물 지지층(218a) 및 캐핑층(218b)의 결합된 두께는 약 50-400 Å 의 두께일 수 있다. 바람직하게는, 장벽층(118), 우물 지지층(218a) 및/또는 캐핑층(218b)은 약 90 Å 두께보다 크고, 가장 바람직하게는 약 225 Å의 두께이다. 또한, 우물 지지층(218a)이 캐핑층(218b)보다 더 두꺼운 것이 바람직하다. 그러므로, 캐핑층(218b)은 양자 우물층(220)으로부터의 인듐(In)의 이탈 또는 양자 우물층(220)의 열화를 감소시키면서 가능한 얇은 것이 바람직하다. 양자 우물층(120, 220)은 약 10-50 Å 사이의 두께일 수 있다. 바람직하게는, 양자 우물층(120, 220)은 20 Å 두께보다 두꺼운 것이 바람직하고, 가장 바람직하게는 25 Å의 두께이다. 양자 우물층(120, 220)의 두께 및 인듐의 퍼센트는 원하는 파장을 갖는 빛을 생성하기 위하여 변화될 수 있다. 통상, 양자 우물층(120, 220)의 인듐의 퍼센트는 약 25 ~ 30 % 이지만, 원하는 파장에 따라, 인듐의 퍼센트는 약 5%에서 약 50 %까지 변화된다.

[0042] 본 발명의 바람직한 실시예들에서, 초격자구조(16)의 밴드캡은 양자 우물층(120)의 밴드캡을 초과한다. 이것은 초격자구조(16)에서 인듐의 평균 퍼센트를 조절함으로써 얻어질 수 있다. 초격자구조의 두께 (또는 주기) 및 층들의 평균 인듐 퍼센트는 초격자구조(16)의 밴드캡이 양자우물(120)의 밴드캡보다 크도록 선택되어야 한다. 초격자구조(16)의 밴드캡을 양자 우물층(120)의 밴드캡보다 높게 유지함으로써, 소자에서 원하지 않는 흡수가 최소화될 수 있고, 발광은 최대화될 수 있다. 초격자구조(16)의 밴드캡은 약 2.95 eV에서 약 3.35 eV 될 수 있다. 더 바람직한 실시예에서, 초격자구조(16)의 밴드캡은 약 3.15 eV이다.

[0043] 본 발명의 부가적인 실시예들에서, 도 2에 도시된 LED 구조는 초격자구조(16)와 활성영역(125) 사이에 배치된 스페이서층(17)을 포함한다. 스페이서층(17)은 바람직하게는 도핑되지 않은 GaN을 포함하여 구성된다. 도핑된 초격자구조(16)와 활성영역(125) 사이의 선택적인 스페이서층(17)의 존재는 실리콘 불순물이 활성영역(125)으로 섞이는 것을 막을 수 있다. 이것은, 즉, 활성영역(125)의 재료 품질을 향상시켜서 더 일관된 소자 성능과 더 나은 균일도를 제공할 수 있다. 유사하게, 스페이서층은 또한 도 1에 도시된 LED 구조에서 초격자구조(16)와 활성영역(125) 사이에 제공될 수 있다.

[0044] 다시 도 2를 참조하면, 층(22)은 활성영역(125) 위에 제공될 수 있으며, 바람직하게는 약 0 과 120 Å 사이의 두께인 도핑되지 않은 GaN 또는 AlGaN이다. 층(22)은 바람직하게는 약 35 Å의 두께이다. 층(22)이 AlGaN을 포함한다면, 그러한 층에서 알루미늄의 퍼센트는 바람직하게는 약 10-30 %이고, 가장 바람직하게는 약 24 %이다. 층(22)에서 알루미늄의 레벨은 계단형으로 또는 연속적으로 감소하는 형태로 점차 변화될 수 있다. 층(22)의 결정 품질을 향상시키기 위하여 층(22)은 활성영역(125)에서의 성장 온도보다 더 높은 온도에서 성장될 수 있다. 도핑되지 않은 GaN 또는 AlGaN의 부가적인 층들이 층(22)의 주위에 포함될 수 있다. 예를 들면, 도 2에 도시된 LED는 활성영역(18)과 층(22) 사이에 약 6-9 Å 두께의 도핑되지 않은 AlGaN의 부가층을 포함할 수 있다.

[0045] 마그네슘과 같은 p 형 불순물로 도핑된 AlGaN 층(30)이 층(22) 위에 제공된다. AlGaN 층(30)은 약 0 과 300 Å 사이의 두께일 수 있고(inclusively) 바람직하게는 약 130 Å 두께이다. P 형의 GaN 의 콘택층(32)이 층(30)위에 제공되며 바람직하게 약 1800 Å 두께이다. 오믹 콘택(24, 25)이 p-GaN 콘택층(32)과 기판(10) 위에 각각 제공된다.

[0046] 도 4는 소자의 활성영역 위에 인듐을 포함하는 III 족 나이트라이드층을 포함하는 본 발명의 다른 실시예들을 도시한다. 예를 들면, InAlGaN 캡 구조가 제공될 수 있다. 도 4에 도시된 본 발명의 실시예들은 기판(10) 위에 성장된 갈륨 나이트라이드-계 반도체층들을 포함하는 층으로 된 반도체 구조(400)를 포함한다. 위에서 기술된 바와 같이, 기판(10)은 SiC, 사파이어 또는 벌크 갈륨 나이트라이드일 수 있다. 본 발명의 특정 실시예들에서, 기판(10)은 약 50 에서 약 800  $\mu\text{m}$  의 두께, 일부 실시예들에서, 약 100  $\mu\text{m}$  의 두께를 갖는 SiC 기판이다.

[0047] 도 4에 도시된 바와 같이, 본 발명의 특정한 실시예들에 따른 LED는 도전성의 베퍼층(11), 제1 실리콘-도핑 GaN

층(12), 제2 실리콘-도핑 GaN 층(14), 실리콘-도핑 GaN 및/또는 InGaN 의 교대층들을 포함하는 초격자구조(16), 다중-양자 우물 구조를 포함하는 활성 영역(125), 도핑되지 않은 AlInGaN 층(40), p 형 불순물로 도핑된 AlGaN 층(30) 및 역시 p 형 불순물로 도핑된 GaN 콘택층(32)을 포함할 수 있다. LED는 또한 기판(10) 위의 n 형 오믹 콘택(23) 및 콘택층(32) 위의 p 형 오믹 콘택(24)을 포함할 수 있다. 기판(10)이 사파이어인 본 발명의 실시예들에서, n 형 오믹 콘택(23)은 n 형 GaN 층(12) 및/또는 n 형 GaN 층(14)위에 제공될 수 있다.

[0048] 도 1 및 도 2에 관련하여 위에서 기술된 바와 같이, 베피층(11)은 바람직하게는 n 형 AlGaN일 수 있다. 예를 들면, 베피층(11)은 Si 으로 도핑되고, 약 100 에서 약 10,000 Å의 두께를 갖는 AlGaN일 수 있다. 일부 실시예들에서 두께는 약 1500 Å이다. GaN 층(12)은 Si 으로 도핑될 수 있고, 약 5000 내지 50,000 Å의 두께를 가질 수 있고(inclusively), 특정 실시예들에서 약 1,8000 Å 두께이다. GaN 층(12)은 약  $5 \times 10^{17}$  에서  $5 \times 10^{18} \text{ cm}^{-3}$  의 레벨로 실리콘으로 도핑될 수 있다. 초격자 구조(16)가 도 1과 관련하여 위에서 기술된 바와 같이 또한 제공될 수 있다. 예를 들면, 초격자구조(16)는 약 3 내지 35 주기의 InGaN/GaN를 포함할 수 있다. 주기의 두께는 약 30 으로부터 100 Å 일 수 있다. 본 발명의 특정 실시예들에서, 25 주기의 InGaN/GaN 가 한 주기의 층의 두께가 약 70 Å으로 제공되며, GaN 또는 InGaN 층은 약 15Å의 두께이고 다른 층이 그 나머지를 구성한다.

[0049] 활성영역(325)은 장벽층들(318)에 의해 분리된 다중 InGaN 양자 우물층들(320)을 포함하는 다중-양자 우물 구조를 포함하여 구성될 수 있다. 장벽층(318)은  $0 \leq X < 1$  인  $\text{In}_x\text{Ga}_{1-x}\text{N}$  을 포함한다. 바람직하게는, 장벽층(318)의 인듐 조성은 양자 우물층(320)의 것보다 적으며, 그리하여 장벽층(318)은 양자 우물층(320)보다 더 큰 밴드갭을 갖는다. 장벽층(318)과 양자 우물층(320)은 도핑되지 않을 수 있다 (즉, 실리콘이나 마그네슘과 같은 불순물 원자로 고의적으로 도핑되지 않을 수 있다). 그러나 특히 자외선 발광을 희망하는 경우, 장벽층(318)을 실리콘으로  $5 \times 10^{19} \text{ cm}^{-3}$  보다 적은 레벨로 도핑하는 것이 바람직할 수 있다.

[0050] 본 발명의 다른 실시예들에서, 장벽층(318)은  $0 < X < 1$ ,  $0 \leq Y < 1$  및  $X+Y \leq 1$  인  $\text{Al}_x\text{In}_y\text{Ga}_{1-x-y}\text{N}$ 을 포함하여 구성된다. 장벽층(318)의 결정에 알루미늄을 포함함으로써, 장벽층(318)은 양자 우물층(320)에 격자-정합될 수 있고, 그에 의하여 양자 우물층(320)에 향상된 결정 품질을 제공하여, 소자의 발광 효율을 증가시킬 수 있다.

[0051] 활성영역(325)이 또한 도 3에 도시되고 도 1 내지 도 3에 관련되어 위에서 기술된 대로 제공될 수 있다. 본 발명의 특정 실시예들에서, 활성영역(325)은 3개 또는 그 이상의 양자 우물을 포함하고, 다른 실시예들에서 8개의 양자 우물이 제공된다. 양자 우물 구조의 두께는 약 30 내지 250 Å 일 수 있다. 본 발명의 특정 실시예들에서, 양자 우물 구조의 두께는 약 120 Å 이고, 우물(well) 층의 두께는 약 25Å 일 수 있다.

[0052] 도 4에 도시된 LED 구조는 또한 위에서 기술된 바와 같이 초격자구조(16)와 활성영역(325) 사이에 배치된 스페이서층을 포함할 수 있다.

[0053] 다시 도 4를 참조하면, 인듐을 포함하는 III 측 나이트라이드 캐핑층(40)이 활성영역(325)위에, 더욱 특징하자면, 활성영역(325)의 양자우물(320) 위에 제공될 수 있다. III 측 나이트라이드 캐핑층(40)은 약 10 과 320 Å 사이의 두께인 InAlGaN을 포함할 수 있다. 캐핑층(40)은 균일한 조성, 다층의 다른 조성 및/또는 구배(graded) 조성일 수 있다. 본 발명의 특정 실시예들에서, 캐핑층(40)은  $\text{In}_x\text{Al}_y\text{Ga}_{1-x-y}\text{N}$ ,  $0 < X < 0.2$  이고  $0 \leq Y < 0.4$  인 조성과 약 10 내지 약 200 Å의 두께를 갖는 제1 캐핑층 및  $\text{In}_w\text{Al}_z\text{Ga}_{1-w-z}\text{N}$ ,  $0 < W < 0.2$  이고  $Y \leq Z < 1$  인 조성과 약 10 내지 약 120 Å의 두께를 갖는 제2 캐핑층을 포함한다. 본 발명의 일부 실시예들에서, 제1 캐핑층은 두께가 약 80 Å,  $x=0.1$  이고  $y=0.25$  이고, 제2 캐핑층은 두께가 약 30 Å,  $w=0.05$  이고  $z=0.55$  이다. 캐핑층(40)의 결정 품질을 향상시키기 위하여 캐핑층(40)은 활성영역(325)의 성장 온도보다 더 높은 온도에서 성장될 수 있다. 캐핑층(40) 가까이에 도핑되지 않은 GaN 또는 AlGaN 의 부가층들이 포함될 수 있다. 예를 들면, GaN 의 얇은 층이 마지막 양자 우물층과 캐핑층(40) 사이에 제공될 수 있다. 인듐을 포함하는 캐핑층(40)은 양자 우물의 활성영역(325)에 더욱 가깝게 격자 정합될 수 있고, 활성영역(325)의 격자 구조로부터 p 형 층들의 격자 구조로의 전이를 제공할 수 있다. 그러한 구조는 소자의 밝기를 증가시키는 결과를 낳을 수 있다.

[0054] 마그네슘과 같은 p 형 불순물로 도핑된 AlGaN 정공 주입층(hole infection layer)(42)이 캐핑층(40) 위에 제공될 수 있다. AlGaN 층(42)은 약 50 과 2500 Å 사이의 두께일 수 있고(inclusively), 특정 실시예들에서 약 150 Å 두께이다. AlGaN 층(42)은  $\text{AlG}_{1-x}\text{N}$ ,  $0 \leq x \leq 0.4$ 의 조성일 수 있다. 본 발명의 특정 실시예들에서, AlGaN 층(42)에 대하여  $x=0.23$  일 수 있다. AlGaN 층(42)은 Mg로 도핑될 수 있다. 본 발명의 일부 실시예들에서, AlGaN 층(42)은 또한 인듐을 포함할 수 있다.

- [0055] p 형의 GaN의 콘택층(32)가 AlGaN 층(42) 위에 제공될 수 있고, 약 250 내지 약 10,000 Å 두께이거나 일부 실시예들에서, 약 1500 Å의 두께이다. 일부 실시예들에서, 콘택층(32)은 또한 인듐을 포함할 수 있다. 오믹 콘택(24, 25)는 p-GaN 콘택층(32) 및 기판(10) 위에 각각 제공될 수 있다.

- [0056] 본 발명의 일부 실시예들에서, 인듐을 포함하는 캐핑층(40)은 예를 들면, 그 개시 내용이 전부 여기에 설명되어 있는 것처럼 여기에 통합된, 이것과 동시에 출원된 "ULTRA-THIN OHMIC CONTACTS FOR P-TYPE NITRIDE LIGHT EMITTING DEVICES"라는 제목의 미국 예비 특허출원 번호 \_\_\_\_\_ (대리인 참조 번호 5308-463PR), 이것과 동시에 출원된 "LIGHT EMITTING DEVICES HAVING A REFLECTIVE BOND PAD AND METHODS OF FABRICATING LIGHT EMITTING DEVICES HAVING REFLECTIVE BOND PADS"라는 제목의 미국 특허 출원 번호 \_\_\_\_\_ (대리인 참조 번호 5308-468), 2004년 6월 30일에 출원된 "LIGHT EMITTING DEVICES HAVING CURRENT BLOCKING STRUCTURES AND METHODS OF FABRICATING LIGHT EMITTING DEVICES HAVING CURRENT BLOCKING STRUCTURES,"라는 제목의 미국 특허 번호 6,664,560, 미국 특허 출원 번호 \_\_\_\_\_ (대리인 참조 번호 5308-457), "LIGHT EMITTING DIODES INCLUDING SUBSTRATE MODIFICATIONS FOR LIGHT EXTRACTION AND MANUFACTURING METHODS THEREFOR" 제목의 미국 특허 공개 번호 2003/0123164 및/또는 "REFLECTIVE OHMIC CONTACTS FOR SILICON CARBIDE INCLUDING A LAYER CONSISTING ESSENTIALLY OF NICKEL, METHODS OF FABRICATING SAME, AND LIGHT EMITTING DEVICES INCLUDING THE SAME,"라는 제목의 미국 특허 공개 번호 2003/0168663에 기술된 바와 같은 발광 소자에서 제공될 수 있다.

- [0057] 전자발광(EM: electroluminescence) 테스트가 도 4에 도시된 바와 같은, 인듐을 포함하는 캐핑층, 특히, InAlGaN 캐핑층이 있거나 또는 없는 소자를 가진 LED 웨이퍼에 대하여 수행되었다. EL 테스트는 LED 에피택셜 구조의 밝기를 측정하는 온-웨이퍼 테스트이다. 이 테스트는 LED 제조방법, 침의 형상화 또는 패키지 방법에 의해 영향을 받지 않는다. 인듐을 포함하는 층을 포함하는 구조를 갖는 약 176개의 웨이퍼와 인듐을 포함하는 층을 갖지 않는 615 웨이퍼가 테스트되었다. 두 구조가 모두 몇 개의 반응기에서 연속적으로 성장되었다. 모든 반응기들은 실질적으로 동일했다. (즉, 어떤 것도 밝기의 증가를 위한 임의의 특별한 변화를 갖지 않으며, 모두 제조용으로 계속 적절하였다) 웨이퍼들로부터의 데이터가 저장되었고, 인듐을 포함하는 층을 갖는 구조가 인듐을 포함하는 층을 갖지 않는 구조보다 약 1.15 내지 1.25 배 더 밝았다.

- [0058] 본 발명의 실시예들이 다중 양자 우물을 갖는 것에 대하여 기술되었으나, 본 발명의 가르침으로부터의 이익은 단일 양자 우물 구조에서도 역시 얻어질 수 있다. 그러므로, 예를 들면, 소자의 활성 영역으로서 도 3의 구조(221)의 단일 존재를 갖고 발광 소자가 제공될 수 있다. 따라서, 다른 수의 양자우물이 본 발명의 실시예들에 따라 사용될 수 있지만, 양자 우물의 수는 통상 1 내지 10 양자 우물의 범위가 될 것이다.

- [0059] 본 발명의 실시예들이 갈륨 나이트라이드계 소자에 관하여 기술되었으나, 본 발명의 가르침으로부터의 이익은 다른 III 족 나이트라이드에서도 역시 얻어질 수 있다. 그러므로, 본 발명의 실시예들은 III 족 나이트라이드계 초격자구조, 양자 우물 구조 및/또는 초격자 및/또는 양자 우물을 갖는 III 족 나이트라이드계 발광 다이오드를 제공한다.

- [0060] 도면과 상세한 설명에서, 전형적인 본 발명의 바람직한 실시예들이 기술되었고, 비록 특정한 용어들이 채용되었지만, 이들은 일반적이고 기술적인 의미에서만 사용된 것이고, 다음의 청구항들에 나타낸 본 발명의 범위를 제한하기 위한 목적으로 사용된 것이 아니다.

### 산업상 이용가능성

- [0061] 본 발명에 의한 발광 다이오드 및 그 제조방법은 발광 다이오드의 효율을 더욱 높일 수 있다.

## 도면

## 도면1

도면2

도면3

## 도면4