# (12) UK Patent Application (19) GB (11) 2 318 955 (13) A

(43) Date of A Publication 06.05.1998

(21) Application No 9722863.9 (51) INT CL6 H04N 7/01 (22) Date of Filing 29.10.1997 (52) UK CL (Edition P) (30) Priority Data H4P PT (31) 08286816 (32) 29.10.1996 (33) JP (56) Documents Cited GB 2203616 A EP 0524715 A2 US 5452235 A (71) Applicant(s) US 5325179 A US 5134702 A **NEC Corporation** (58) Field of Search (Incorporated in Japan) UK CL (Edition P) H4F FEP, H4P PF PT INT CL6 H04N 7/01 7-1 Shiba 5-chome, Minato-ku, Tokyo 108-01, Japan Online:WPI, JAPIO (72) Inventor(s) Eiichi Kobayashi (74) Agent and/or Address for Service Reddie & Grose 16 Theobalds Road, LONDON, WC1X 8PL, **United Kingdom**

#### (54) Frame format converter with FIFO buffer

(57) A transmission frame format converter circuit has a first-in-first-out(FIFO) memory 201 where the inputting and outputting of a data signal are conducted at different clock rates, A write control means 203 writes write-in data and a frame pulse which is extracted from a transmission line and indicates a head position of the write-in data in the FIFO memory. A read control means 205 judges that read-out data are valid only when the frame pulse to be read out from the read control means is active and then reads out the read-out data from the FIFO memory, and judges that the read-out data are invalid and then conducts the resetting of the write control means and the FIFO memory.

F16.4

١

This invention relates to a transmission frame format converter circuit with a first-in-first-out(FIFO) memory, and more particularly to, a transmission frame format converter circuit where the inputting and outputting of a data signal are conducted at different clock rates.

10

15

20

25

5

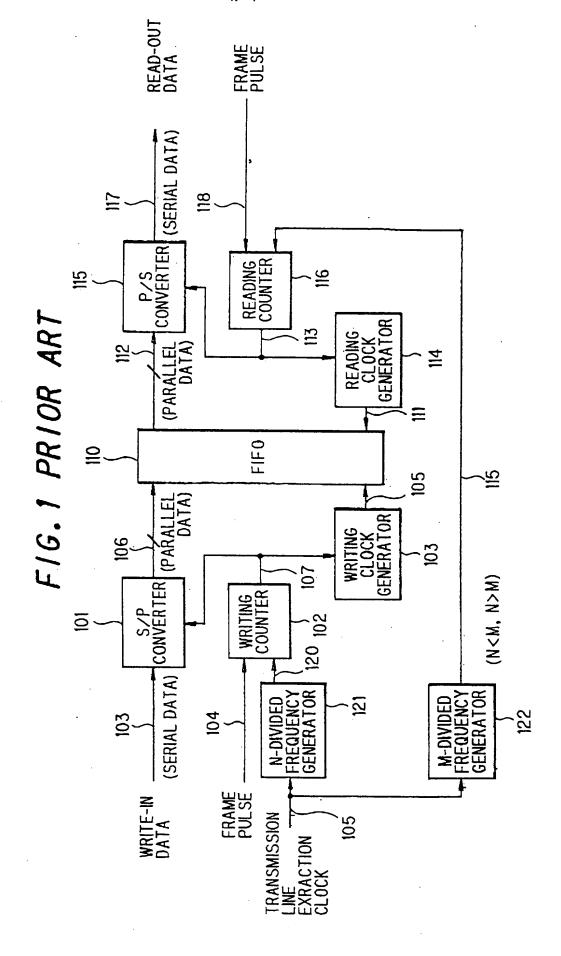

An example of a known transmission frame format converter circuit with a FIFO memory is shown in FIG.1.

As shown in FIG.1, the data-writing side of FIFO 110 in the transmission frame format converter circuit comprises a serial-to-parallel(S/P) converter 101, a N-divided frequency generator 121, a writing counter 102, and a writing clock generator 108.

The S/P converter 101 converts write-in data which is input in the form of serial data 103 into parallel data 106, according to a divided frequency clock, which is explained later, to be output from the writing counter 102, and then outputs it to FIFO 110. The N-divided frequency generator 121, to which an extraction clock 105 from a transmission line is input, outputs a N-divided clock 120. The writing counter 102, to which a frame pulse 104 and the N-divided frequency clock 120 from the N-divided frequency generator 121 are input, outputs a write-side divided frequency clock 107. The divided frequency clock 107 output from the writing counter 102 is supplied to the S/P converter 101 and the writing clock

generator 108. The writing clock generator 108, to which the divided frequency clock 107 is input, outputs a write clock 109 for writing in FIFO 110.

The parallel data 106 which are converted by and output from the S/P converter 101 are written in FIFO 110 according to the writing clock 109 output from the writing clock generator 108.

5

10

15

20

25

The data-reading side of FIFO 110 in the transmission frame format converter circuit comprises a M-divided frequency generator 122, a reading counter 116, a reading clock generator 114, and a parallel-to-serial(P/S) converter 115.

The M-divided frequency generator 122, to which the extraction clock 105 from the transmission line is input, outputs a M-divided frequency clock 119, where M is not the same value as N and satisfies the relation of M>N or M<N. The reading counter 116, to which the M-divided frequency clock 119 and a frame pulse 118 are input, outputs a read-side divided frequency clock 113, which is supplied to the reading clock generator 114 and the P/S converter 115. The reading clock generator 114 outputs a read clock 111 for reading data from FIFO 110 according to the divided frequency clock 113 to be input.

Data to be read out from FIFO 110 according to the read clock 111 are converted into serial data 117, which are output as read-out data.

However, in the conventional transmission frame format converter circuit, the read clock forces data to be read out regardless of the state that the data is not yet written in FIFO since the writing and reading operations are conducted independently of each other. Thus, data to be forcibly read out from FIFO must

be acknowledged as effective data and transmitted even if the data are meaningless or useless.

Accordingly, it is an object of particular preferred embodiments of the invention to provide a transmission frame format converter circuit where the writing of unnecessary data can be canceled and only valid data are read out even when invalid data are written in so as to efficiently conduct the data transmission.

According to particular embodiments of the invention, a transmission frame format converter circuit with a first-in-first-out (FIFO) memory where the inputting and outputting of a data signal are conducted at different clock rates, comprises:

a write control means which writes write-in data and a frame pulse which is extracted from a transmission line and indicates a head position of the write-in data in the FIFO memory; and

a read control means which judges that read-out data are valid only when the frame pulse to be read out from the read control means is active and then reads out the read-out data from the FIFO memory, and which judges that the read-out data are invalid and then conducts the resetting of the write control means and the FIFO memory.

In this embodiment of the invention, on the write side of the FIFO memory, a write clock for writing in the FIFO memory is generated. The write clock is generated only when a frame pulse from the transmission line is active, so as to write only valid data in the FIFO memory. At this time, a frame pulse indicating the head position of valid data is also written therein.

On the other hand, on the read side of the FIFO memory, a read clock for reading data from the FIFO memory is generated. The read clock is generated only when a frame pulse from the FIFO memory is active, therefore data from the FIFO memory are not read out until an active frame pulse appears. When a frame pulse read out from the FIFO memory by a constant period read clock is active, data are in due order read out according to the read clock. If not active, the data are judged to be invalid and cleared by resetting.

10

5

The invention will be explained in more detail in conjunction with the appended drawings, wherein:

FIG.1 is a block diagram showing a conventional transmission frame format converter circuit.

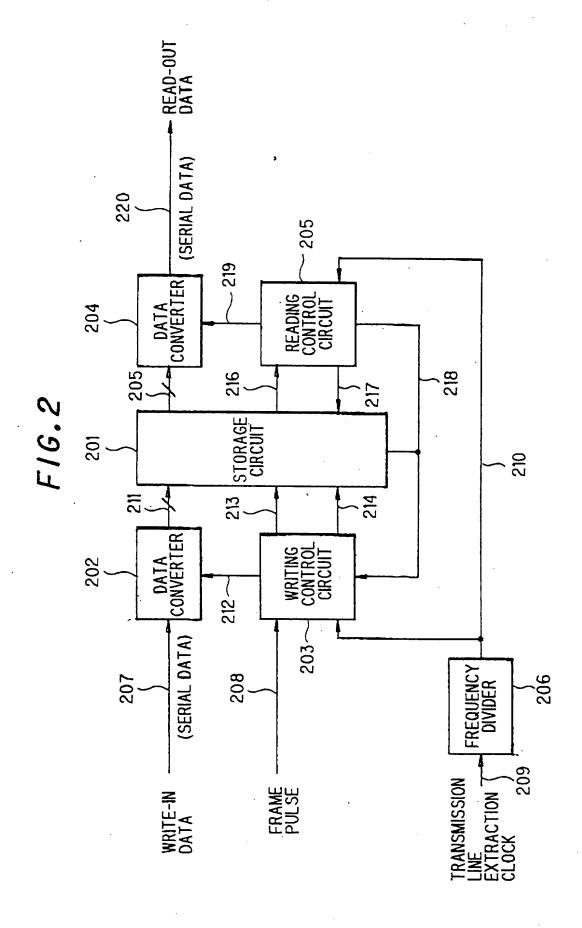

15 FIG.2 is a block diagram showing a transmission frame format converter circuit in a preferred embodiment according to the invention,

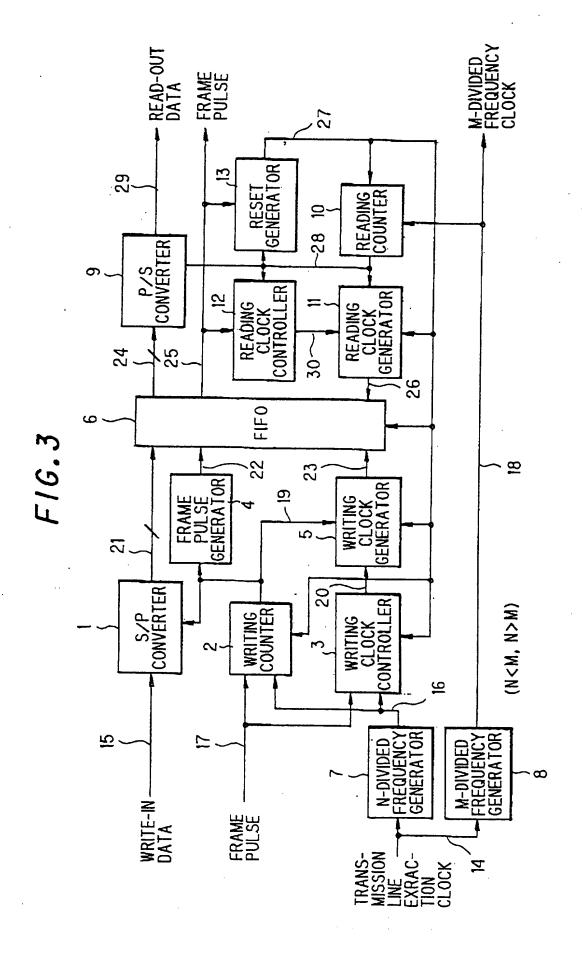

FIG.3 is a block diagram showing the details of the transmission frame format converter circuit in FIG.2, and

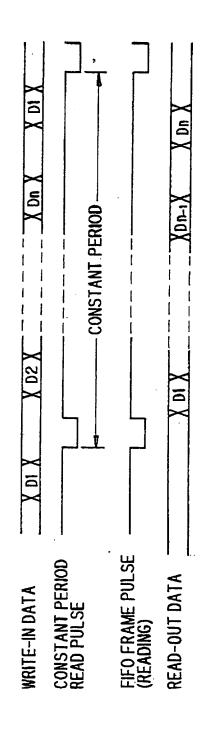

20 FIG.4 is a timing chart showing a phase relation between data to be written in FIFO and data to be read out from FIFO.

A transmission frame format converter circuit in the preferred embodiment will be explained in FIGS.2 to 4.

As shown in FIG.2, the transmission frame format converter circuit in the embodiment comprises a writing control circuit 203

5

10

15

20

on the write side of a storage circuit 201 and a reading control circuit 205 on the read side of the storage circuit 201.

Namely, provided on the write side are a frequency divider 206 to which an extraction clock 209 from a transmission line is input and from which a divided frequency clock 210 is output, a data converter(S/P converter) 202 which converts serial write-in data 207 to be input there into parallel data 211, and a writing control circuit 203 to which a frame pulse 208 is input, the divided frequency clock 210 output from the frequency divider 206 and a reset signal 218, which is explained later, output from the reading control circuit 205, and outputs a write clock 214 and a frame pulse 213 for indicating the head position of write data to the storage circuit 201 and outputs a divided frequency clock 212 necessary for the data converter(S/P) 202.

On the other hand, provided on the read side are a reading control circuit 205 to which a divided frequency clock 210 output from the frequency divider 206 and a frame pulse 216 for indicating the head position of data output from the storage circuit 201 are input and from which a read clock 217 is output to the storage circuit 201, and a data converter(P/S converter) 204 which converts parallel data to be read out from the storage circuit 201 into serial data 220. Also, a divided frequency clock 219 necessary for the data converter(P/S) 204 is output from the reading control circuit 205.

In this composition, the parallel data 211 output from the data converter(S/P) 202 and the frame pulse 213, which indicates the write data position, output from the writing control circuit 203 are written in the storage circuit 201 according to the write

clock 214 output from the writing control circuit 203, and the parallel data 215 and frame pulse 216 are read out from the storage circuit 201 according to the read clock 217 output from the reading control circuit 205. Also, when the reset signal to be output from the reading control circuit 205 becomes active, the reset operations of the storage circuit 201 and writing control circuit 203 are conducted.

5

10

15

20

25

Referring to FIGS.3 and 4, the transmission frame format converter circuit in the embodiment will be further detailed.

With reference to FIG.3, FIFO 6 corresponds to the storage circuit 201 in FIG.2, a S/P converter 1 corresponds to the data converter 202 in FIG.2, a P/S converter 9 corresponds to the data converter 204 in FIG.2, and a N-divided frequency generator 7 and a M-divided frequency generator 8 correspond to the frequency divider 206 in FIG.2. Also, the writing control circuit 203 in FIG.2 is composed of a writing clock controller 3, a writing counter 2, a writing clock generator 5 and a frame pulse generator 4 in FIG.3. The reading control circuit 205 in FIG.2 is composed of a reading counter 10, a reading clock controller 12, a reading clock generator 11 and a reset generator 13 in FIG.3.

FIG.4 is a timing chart showing the operation of the transmission frame format converter circuit in the embodiment.

First, on the write side, an extraction clock 14 from a transmission is input to the N-divided frequency generator 7, where a N-divided frequency clock 16 synchronizing with the clock 14 is generated and output. The writing counter 2, to which the N-divided frequency clock 16 and a frame pulse 17 are input, generates a divided

frequency clock 19 which is the source of a write clock 23 for FIFO 6. Also, the writing clock controller 3 monitors the states of the N-divided frequency clock 16 and the frame pulse 17 to be input and outputs a write clock control signal 20. The write clock control signal 20 serves to mask the write clock 23 from the turning-on and resetting through the inputting of the first frame pulse 17. To the writing clock generator 5, the divided frequency clock 19 generated by the writing counter 2 and the write clock control signal 20 are input, and then the writing clock generator 5 generates the write clock 23 to FIFO 6. The frame pulse generator 4 generates a frame pulse 22 for indicating the head position of data written in FIFO 6 according to a divided frequency clock 19 output from the writing counter 2. The S/P converter 1 converts serial write-in data 15 into parallel data 21. The parallel data 21 and the frame pulse 22 are written in FIFO 6 according to the write clock 23.

On the other hand, on the read side, the clock 14 extracted from the transmission line is input to the M-divided frequency generator 8, which outputs a M-divided frequency clock 18 synchronized with the input clock 14. Here, the M-divided frequency clock 16 is not the same value as the N-divided frequency clock and satisfies the relation of M>N or M<N. The reading counter 10 to which the M-divided frequency clock 18 is input generates a divided frequency clock 28 which is the source of a read clock 26 for FIFO 6. The reading clock controller 12 monitors the divided frequency clock 28 output from the reading counter and the state of a frame pulse 25 read from FIFO 6, and outputs a clock control signal 30. The clock control signal 30 serves to mask the read clock 26 from

the turning-on and resetting through the inputting of the first frame pulse 15. To the reading clock generator 11, the divided frequency clock 28 generated by the reading counter 10 and the read clock control signal 30 are input, and then the reading clock generator 11 generates the read clock 26 to FIFO 6. By the read clock 26, parallel data 24 and the frame pulse 25 are read out from FIFO 6.

5

20

25

The parallel data 24 are input to the P/S converter 9, converted into serial data 29, then output as read-out data.

Here, the frame pulse 25 read out from FIFO 6 is input to the reset generator 13. The reset generator 13, to which the divided frequency clock 28 output from the reading counter 10 is also input, compares the divided frequency clock 28 with the frame pulse 25 to judge the validity/invalidity of read-out data. When the frame pulse 25 read out from FIFO 6 is not active at the position of a constant period read pulse, data at the position is judged to be invalid. Then, a reset signal is output to reset the writing counter 2, writing clock controller 3 and writing clock generator 5 on the write side, the reading counter 10 and reading clock generator 11 on the reading side, and FIFO 6.

FIG. 4 is a timing chart showing phase relation between write-in data and read-out data. According to the constant period read pulse, write-in data written in FIFO 6 and a frame pulse to indicate the head position of valid data are read out. As the result of comparing the frame pulse read out from FIFO 6 with the constant period read pulse, when the frame pulse is not active, the resetting is conducted to initialize the control circuit including FIFO 6. Therefore, valid data to be read out are surely read after they are written

in FIFO 6. Also, when data to be read out are judged to be invalid, they are not read out since the resetting is conducted. Thus, only valid data can be always read out.

5

10

### CLAIMS:

1. A transmission frame format converter circuit with a first-in-first-out(FIFO) memory where the inputting and outputting of a data signal are conducted at different clock rates, comprising:

a write control means which writes write-in data and a frame pulse which is extracted from a transmission line and indicates a head position of said write-in data in said FIFO memory; and

a read control means which judges that read-out data are valid only when said frame pulse to be read out from said read control means is active and then reads out said read-out data from said FIFO memory, and which judges that said read-out data are invalid and then conducts the resetting of said write control means and said FIFO memory.

15

20

10

5

2. A transmission frame format converter circuit, according to claim 1, wherein:

said write control means comprises a writing clock generator which outputs a data write clock to said FIFO memory only when said frame pulse is active.

3. A transmission frame format converter circuit, according to claim 1, wherein:

said read control means comprises a reading clock generator

25 which outputs a read clock only when a frame pulse read out from

said FIFO memory is active.

4. A transmission frame format converter circuit as hereinbefore described, with reference to Figures 2 to 4.

,

**Application No:**

GB 9722863.9

Claims searched: 1

Examiner:

B.J.SPEAR

Date of search:

10 February 1998

# Patents Act 1977 Search Report under Section 17

### Databases searched:

UK Patent Office collections, including GB, EP, WO & US patent specifications, in:

UK Cl (Ed.P): H4F (FEP): H4P (PF,PT)

Int Cl (Ed.6): H04N 7/01

Other: Online: WPI, JAPIO

## Documents considered to be relevant:

| Category | Identity of document and relevant passage |                                                                                          | Relevant<br>to claims |

|----------|-------------------------------------------|------------------------------------------------------------------------------------------|-----------------------|

| X        | GB2203616A                                | (Digital Equipment) Whole document, eg Fig. 4 and p 5 1 4 to p 10 1 5.                   | 1-3                   |

| Х        | EP0524715A2                               | (Tektronix) Whole document, eg Fig. 1 and p 5 l 39 to p 8 l 38.                          | 1-3                   |

| Х        | US5452235                                 | (Intel) Whole document, eg Fig. 2 and col. 3 1 25 to col. 4 1 23                         | 1-3                   |

| Х        | US5325179                                 | (Instant Replay) Whole document, eg Fig. 1 and col. 2 1 10-43, col. 4 1 55 to col. 5 1 2 | 1-3                   |

| X        | US5134702                                 | (NCR) Whole document, eg abstract, Figs. 1, 10, and col. 3 1 17 to col. 4 1 65.          | 1-3                   |

|          |                                           |                                                                                          |                       |

X Document indicating lack of novelty or inventive step

Document indicating lack of inventive step if combined with one or more other documents of same category.

<sup>&</sup>amp; Member of the same patent family

A Document indicating technological background and/or state of the art.

P Document published on or after the declared priority date but before the filing date of this invention.

E Patent document published on or after, but with priority date earlier than, the filing date of this application.