**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

|                                            |                                       |

|--------------------------------------------|---------------------------------------|

| (51) Int. Cl. <sup>6</sup><br>H01L 21/66   | (45) 공고일자<br>2001년01월15일              |

| (21) 출원번호<br>10-1992-0000267               | (11) 등록번호<br>10-0274558               |

| (22) 출원일자<br>1992년01월10일                   | (24) 등록일자<br>2000년09월14일              |

| (30) 우선권주장<br>640,198 1991년01월11일 미국(US)   | (65) 공개번호<br>특 1992-0015499           |

| (73) 특허권자<br>텍사스 인스트루먼츠 인코포레이티드 월리엄 비. 캠플러 | (43) 공개일자<br>1992년08월27일              |

| (72) 발명자<br>안소니 엠. 췌                       | 미국 텍사스주 75265 달拉斯 노스센트럴 익스프레스웨이 13500 |

| (74) 대리인<br>주성민                            | 미합중국 75082 텍사스주 리차드슨 버터컴 드라이브 2563    |

**심사관 : 박준영**

---

**(54) 웨이퍼 번인 및 검사 시스템**

---

**요약**

디바이스가 형성되는 반도체 웨이퍼로부터 분리시키기 전에 반도체 디바이스(12)를 번인하고 검사하는 상호접속 시스템 및 방법이 디바이스 위에 도체(16 및 17)의 상호접속층을 형성한 후 디바이스를 검사하고 번인하는 것을 포함한다. 결함이 있는 디바이스는 부수적인 검사 및 번인을 실행하기 전에 상기 도체로부터 절단된다. 상호접속부는 웨이퍼 상의 디바이스를 분리하고 다른 가능한 검사 및 팩킹 전에 제거된다.

**대표도**

**도1**

**명세서**

[발명의 명칭]

웨이퍼 번인 및 검사 시스템

[도면의 간단한 설명]

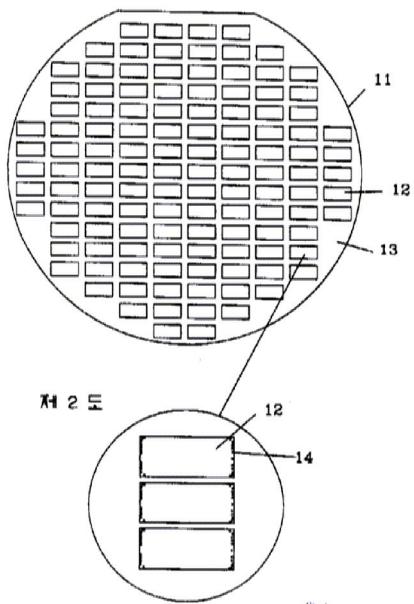

제1도는 반도체 웨이퍼 상에 형성되는 다수의 디바이스를 갖는 반도체 웨이퍼를 나타낸 도면.

제2도는 웨이퍼 상의 3개 디바이스의 확대도.

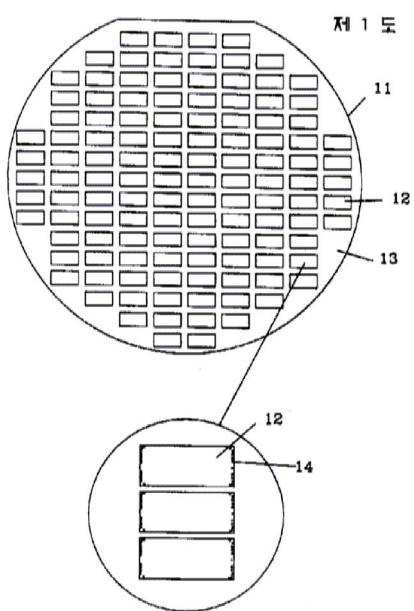

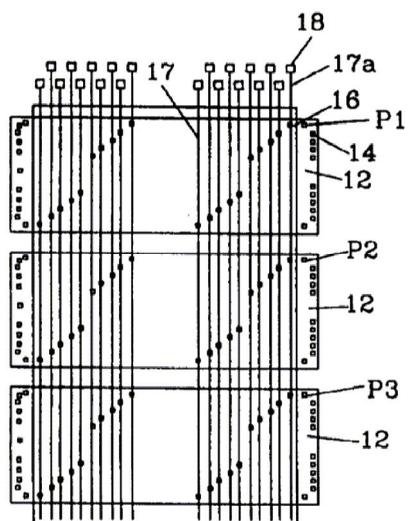

제3도는 제1 도체층을 갖는 3개의 디바이스를 나타낸 도면.

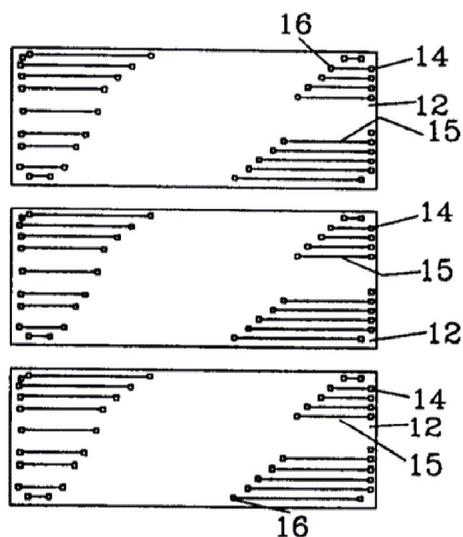

제4도는 제2 도체층을 갖는 제3도의 3개의 디바이스를 나타낸 도면.

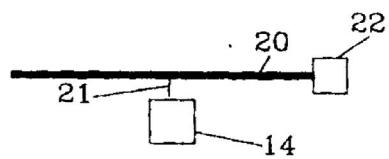

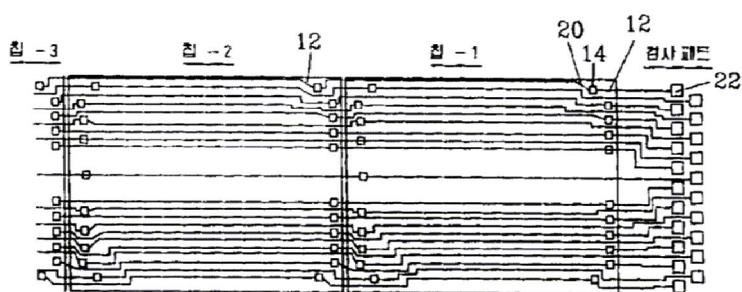

제5도는 상호접속부의 단일층을 나타낸 도면.

제6도는 반도체 디바이스 상의 도체로부터 본드 패드로의 휴즈 링크 접속부를 나타낸 도면.

\* 도면의 주요부분에 대한 부호의 설명

|            |                |

|------------|----------------|

| 11 : 웨이퍼   | 12 : 반도체 디바이스  |

| 14 : 본드 패드 | 15 : 휴즈 링크 도체  |

| 16 : 비아 패드 | 17 : 상호 접속 도체  |

| 18 : 검사점   | 20 : 상호 접속부    |

| 21 : 휴즈 링크 | 22 : 검사 패드 접촉부 |

[발명의 상세한 설명]

본 발명은 반도체 디바이스의 검사 및 번인(burn-in)에 관한 것으로, 특히 웨이퍼를 다이싱하기 전에 웨이퍼 전체를 검사하고 번인하는 시스템 및 방법에 관한 것이다.

대부분의 MOS 반도체 제품은 제조시 결함이 있는 디바이스로 인한 실제고장(field failure)을 피하기 위

해 번인 및 검사를 필요로 한다 소정의 방법에서는 팩킹 및 번인 전에 결함이 있는 칩을 검출하고 분류하기 위해 높은 전압을 가하여 탐색 한다.

종래의 웨이퍼 시험 시스템에 사용되는 것과 유사한 다핀 카운트 접촉 어셈블리(hight pin Count Contact assembly)가 번인 기간 동안, 3000 내지 6000개의 모든 본드 패드와 양호한 접촉을 유지하는 것이 어렵기 때문에 실용적이지 못하다. 이 기간은 20시간 내지 120시간 범위이다. 이러한 다핀 카운트 번인 탐침의 구조물은 제조가 불가능하지 않더라도 고가이다.

도금 기술을 사용하여 제조되는, 융통성있고 재생 가능한 접촉 어셈블리는 개개의 핀 탐침보다는 저렴하지만, 이런 유형의 접촉부는 알루미늄 본드 패드 상의 천연산화물 때문에 나(bare) 알루미늄 본드 패드와 함께 사용될 수는 없다 이런 유형의 접촉 어셈블리를 사용하기 전에 일반적으로 본드 패드에 범핑 또는 산화물 제거 단계가 요구되는 것이 일반적이다. 그러나, 이러한 것은 접촉 압력에 매우 민감하므로 비실용적이다.

본 발명에 있어서, 웨이퍼의 각 반도체 상의 본드 패드마다 정 접촉(positive contact)이 이루어진다. 단일 또는 단일 층 구조물 중 하나가 사용될 수 있다.

도체(conductors)층 구조물에 있어서, 접촉부는 웨이퍼의 연부 주위에 형성된다. 다수의 반도체층 중의 제1층은 웨이퍼의 표면 상의 절연층 상에 형성된다 각 디바이스 상의 각 본드 패드에 대해 검사되어야 할 1개의 도체가 있다. 제2 금속 도체층은 제1 도체층 위에 형성된다. 제2 리드 층은 공통 본드 패드(예를 들면, 각 디바이스핀 1)를 함께 상호접속하고 웨이퍼의 연부 상의 접촉부에 상호 접속시킨다.

이러한 방법에 있어서, 웨이퍼 상에 단일 열로 구성된 반도체 디바이스는 별별로 접속되는 것이 효과적이다. 이러한 번인 방법은, 모든 어드레스 라인 및 입력 라인이 동시에 활성화 될 수 있는 메모리 디바이스에 대해 매우 유용하다 제1 도체층은 휴즈 링크를 통해 제2 도체층에 접속된다. 그다음, 이들 링크는 후에 동작불능 또는 단락된 디바이스를 절단하기 위해 레이저를 사용함으로써 절단될 수 있다.

단일층 구조물은 디바이스 행 내의 디바이스의 공통 본드 패드를 접속시키기 위해 단일 도체를 사용한다. 각 본드 패드는 휴즈 링크에 의해 도체에 접속된다.

디바이스가 웨이퍼 상에 계속해서 유지되는 동안, 그들은 번인 전압에 연결된다. 번인된 후, 번인된 금속 상호접속부의 구조물이 제거된다. 결함이 있는 디바이스를 식별하기 위한 검사가 행해지고, 이 결함이 있는 디바이스는 폐기 처분용으로 표시된다. 그 후 디바이스는 팩킹 및 최종 검사를 위해 분리된다.

본 발명의 목적 및 기술적인 장점은 첨부된 도면 및 첨부된 특허 청구의 범위에서 설명되는 새로운 장점과 관련하여 생각할 때 다음의 본 발명의 양호한 실시예에 대한 설명으로부터 명백하다.

#### [실시예]

제1도는 반도체 웨이퍼 상에 형성된 다수의 반도체 디바이스(12)를 갖고 있는 반도체 웨이퍼(11)를 도시하고 있다. 웨이퍼(11)는 디바이스가 없는 웨이퍼의 연부 둘레에 마진 영역(13)을 갖는다. 반도체 디바이스에 콘택 액세스를 제공하기 위해 검사점이 마진 영역(13)에 형성되어 후술하는 바와 같이, 검사 및 번인이 행해진다.

제2도는 본드 패드(14)를 갖고 있는 3개의 반도체 디바이스(12)를 나타낸 일부 웨이퍼(11)의 확대도이다. 본드 패드(14)는 디바이스(12)의 접촉부이다.

제3도는 각각의 반도체 디바이스(12)에 접속 계면을 제공하는 제1 단계를 도시한다. 상호 접속부의 제1 층은 웨이퍼 표면의 각각의 반도체 디바이스 상에 개별적으로 형성된다. 그 절차는 다음과 같다. 열연화성 플라스틱과 같은 접착제가 웨이퍼 상에 가해진 다음, 폴리이미드와 같은 유전 물질이 접착제에 가해진다. 그다음 유전체는 각 본드 패드(14)상에 개구를 제공하기 위해 패턴화된다. TiW와 같은 제1 금속 층이 유전체 상에 도포된 다음 구리와 같은 제2 금속이 도포된다. 그 다음 단락된 디바이스를 절연시키기 위해 후에 절단 개방될 수 있는 노출된 도체, 즉 휴즈링크 도체(15)를 형성하기 위해 금속층이 패턴화되고 에칭된다. 각 도체(15)는 한 단부에서 디바이스 본드 패드(14)에 접속된다. 디바이스 본드 패드에 접속된 단부에 대향하는 각 도체(15)의 다른 단부 상에 비아 패드(16)가 형성된다.

제4도는 웨이퍼(11) 상의 각 반도체 디바이스에 접속 계면을 제공하는 제2 단계를 도시한다. 프로세스를 계속 행하면, 유전체가 웨이퍼 상에 가해져서 도체(15) 및 비아 패드(16)를 덮는다. 비아 패턴은 폴리이미드 상에서 에칭된다. 제2 금속층은, 예를 들면 구리층이 수반되는 TiW층과 같은 유전체 위에 도포된다. 제2 금속층은 상호 접속 도체(17)를 형성하기 위해 패턴화되고 에칭된다. 또한, 폴리이미드는 이 마스킹 단계 중에 도체(15)의 일부를 노출하기 위해 에칭된다(도시되지 않음). 이들 도체 각각은 각각의 디바이스 상의 비아 패드를 특정한 열 형태로 접속시킨다.

예를 들어, 비아 패드에 접속하는 도체는 도체(15)에 의해 각 디바이스 상의 각각의 본드 패드에 접속된다. 예를 들어, 도체(17a)는 각각의 도체(15) 및 비아 패드(16)에 의해 본드 패드 P1, P2 및 P3에 접속된다. 각 도체(17)는 웨이퍼(11)의 비패턴화 영역(13) 내에 위치한 검사점(18)에 접속된다.

웨이퍼 상의 디바이스의 예비 검사는 동작불능 디바이스를 찾아낸다. 동작불능 디바이스는, 예를 들어 레이저 빔에 의해 디바이스의 도체(15)를 절단함으로써 전기적으로 절연된다. 예비 검사 후에, 개방 및 단락을 위해, 잔여 디바이스는 부수적인 결함 디바이스가 존재하는지를 결정하기 위해 번인되어야 한다. 번인 및 예비검사 후에, 2개의 도체층(15 및 17)이 제거되고, 웨이퍼는 다른 어셈블리를 위해 개별적인 디바이스로 분할된다.

제5도는 상호접속부의 단일층이 사용되는 본 발명의 제2 실시예를 도시하고 있다. 절연 물질이 웨이퍼 및 웨이퍼 상의 각 디바이스 위에 도포된다. 다수의 상호 접속부(20)가 디바이스 상에 형성되고, 각각의 상호 접속부(20)는 행 방향 디바이스상의 동일한 각각의 본드 패드(14)에 각각 접속된다. 웨이퍼 상의 어떤 디바이스도 단락되어 있지 않으면 이 상호접속 시스템은 실용적이다. 단락되어 있고 이 단락된 디

바이스를 절연시키는 것이 요구된다면, 휴즈 링크 구조물이 필요하게 된다. 휴즈 링크(21, 제6도)가 상호 접속부(20)와 디바이스 상의 본드 패드(14) 사이에 존재한다. 각 상호 접속부는 웨이퍼(11)의 연부(13, 제1도) 주위에 배치된 검사 패드 접촉부(22)를 갖는다.

제5도의 실시예에 대한 검사 및 번인 절차는 제4도 및 제5도의 실시예에 대한 절차와 동일하다. 예비 검사는 결함이 있는 디바이스에 대해 행해진다. 결함이 있는 디바이스는 휴즈 링크(21)를 개방함으로써 전기적으로 절연된다. 번인 및 검사 절차가 진행되고, 웨이퍼는 다음 어셈블리를 위해 개개의 디바이스로 분할된다.

본 발명의 상호접속 시스템의 한 장점은 웨이퍼를 개개의 디바이스로 분할시키기 전에 병렬로 예비검사가 행해지고 최종 개별 디바이스 어셈블리 및 검사를 위해 상호접속부가 제거된다는 것이다. 웨이퍼 상태에서 디바이스를 검사하는 것은 각 디바이스의 “출력” 핀을 접촉시킬 필요가 있다. 이것은 출력 핀을 웨이퍼 상의 더 편리한 위치에 접속시키는 탐침 카드 또는 부수적인 금속층을 사용함으로써 달성된다.

## (57) 청구의 범위

### 청구항 1

반도체 웨이퍼로부터 분리시키기 전에 반도체 디바이스를 번인(burn-in)하고 검사하기 위한 상호 접속 시스템에 있어서, 다수의 본드 패드를 각각 가지고 웨이퍼 상에 행과 열로 배열된 다수의 반도체 디바이스를 갖고 있는 반도체 웨이퍼, 상기 디바이스 및 상기 본드 패드로부터 절연된 상기 웨이퍼 상의 다수의 전기적으로 절연된 도체들 중 적어도 1개의 층, 열 내의 각각의 상기 디바이스 상의 상기 다수의 전기적으로 분리된 각각의 도체와 대응 본드 패드 사이의 전기 접속부, 및 상기 다수의 전기적으로 분리된 도체의 각각에 접속된 상기 웨이퍼 상의 다수의 검사점을 포함하는 것을 특징으로 하는 상호 접속 시스템.

### 청구항 2

제1항에 있어서, 상기 열 내의 각 디바이스 상의 상기 다수의 분리된 각각의 도체와 대응 본드 패드 사이의 접속부가 휴즈 링크(fuse link)인 것을 특징으로 하는 상호 접속 시스템.

### 청구항 3

제1항에 있어서, 다수의 전기적으로 분리된 도체들의 상기 최소한 1개의 층으로부터 절연된 다수의 접속 층들의 제2 층을 포함하고, 상기 제2 상호 접속부 레벨의 각각의 도체가 비아에 의해 상기 제1 층의 상기 다수의 전기적으로 분리된 접속기들 중의 1개에 접속되는 것을 특징으로 하는 상호 접속 시스템.

### 청구항 4

제3항에 있어서, 다수의 상기 상호 접속층들의 상기 제2 층의 각 도체가 휴즈 링크에 의해 상기 웨이퍼 상의 본드 패드에 접속되는 것을 특징으로 하는 상호 접속 시스템.

### 청구항 5

반도체 웨이퍼로부터 분리시키기 전에 반도체 디바이스를 번인하고 검사하기 위한 상호 접속 시스템에 있어서, 다수의 본드 패드를 각각 가지고 웨이퍼 상에 행과 열로 배열된 다수의 반도체 디바이스를 갖고 있는 반도체 웨이퍼, 상기 디바이스 및 상기 본드 패드로부터 절연된 상기 웨이퍼 상의 다수의 전기적으로 분리된 도체들의 제1 층, 상기 다수의 전기적으로 분리된 도체들의 제1 층으로부터 절연된 웨이퍼 상의 다수의 전기적으로 분리된 도체들의 제2 층, 각각의 상기 전기적으로 분리된 도체들의 제1 층과 상기 다수의 전기적으로 분리된 도체들의 제2 층, 각각의 상기 전기적으로 분리된 도체들의 제1 층과 상기 다수의 전기적으로 분리된 도체들의 제2 층 중 1개의 도체 사이의 상호 접속부, 및 상기 다수의 전기적으로 분리된 도체들의 제2 층 내의 상기 각각의 도체에 접속된 상기 웨이퍼 상의 다수의 접촉 검사점을 포함하는 것을 특징으로 하는 상호 접속 시스템.

### 청구항 6

제5항에 있어서, 상기 다수의 검사점 각각과 본드 패드 사이의 상호 접속부가 휴즈 링크인 것을 특징으로 하는 시스템.

### 청구항 7

제5항에 있어서, 상기 디바이스로부터 절연되고 상기 디바이스 상의 상기 본드 패트 및 상기 웨이퍼 상의 상기 접촉 검사점에 접속된 상기 웨이퍼 상에 다수의 전기적으로 분리된 도체들의 1개의 층만이 형성되어 있는 것을 특징으로 하는 상호 접속 시스템.

### 청구항 8

반도체 웨이퍼로부터 분리시키기 전에 반도체 디바이스를 번인하고 2검사하기 위한 상호 접속 시스템을 형성하기 위한 방법에 있어서, 상기 반도체 웨이퍼의 표면 및 그 상부에 형성된 반도체 디바이스 상에 절연층을 형성하는 단계를 포함하되, 상기 반도체 디바이스 각각이 다수의 본드 패드를 갖고 있고, 상기 절연층이 상기 본드 패드 상에 개구를 가지며, 상기 절연층 상에 제1 금속층을 피착하고 개구 내의 절연층을 통해 연장시키며 상기 반도체 디바이스 상의 상기 본드 패드를 접촉시키는 단계, 다수의 도체를 형성하기 위해 상기 제1 금속층을 에칭하는 단계, 상기 반도체 디바이스를 포함하지 않는 위치에서 상기 반도체 웨이퍼 외변상에 검사점 접촉부를 형성하는 단계, 및 상기 본드 패드에 접속된 다수의 도체들 중의 하나에 검사점 접촉부를 각각 하나씩 상호 접속하는 단계를 포함하는 것을 특징으로 하는 상호 접속 시스템의 형성 방법.

**청구항 9**

제8항에 있어서, 상기 반도체 디바이스 상의 상기 본드 패드를 상기 다수의 도체들에 접속시키기 위해 휴즈 링크를 형성하는 단계를 포함하는 것을 특징으로 하는 상호 접속 시스템의 형성 방법.

**청구항 10**

제8항에 있어서, 금속층이 에칭된 후에 상기 금속층 위에 제2 절연 물질층을 형성하는 단계, 비아를 형성한 후 상기 제2 절연 물질층 위에 제2 금속층을 피착하는 단계, 다수의 제2 도체를 형성하기 위해 상기 제2 금속층을 에칭하는 단계, 및 상기 제2 금속층의 도체에 상기 제1 금속층의 상기 도체를 접속하는 단계를 포함하는 것을 특징으로 하는 상호 접속 시스템의 형성 방법.

**청구항 11**

제10항에 있어서, 상기 제1 금속층으로 형성된 상기 도체가 비아를 통해 상기 제2 금속층으로 형성된 상기 도체에 접속되는 것을 특징으로 하는 상호 접속 시스템의 형성 방법.

**청구항 12**

제8항에 있어서, 상기 절연 물질을 피착하기 전에 접착 물질층을 도포하는 단계를 포함하는 것을 특징으로 하는 상호 접속 시스템의 형성 방법.

**청구항 13**

제9항에 있어서, 상기 휴즈 링크가 번인 중 과부하가 발생할 때 개방하는 저전력 반송 도체인 것을 특징으로 하는 상호 접속 시스템의 형성 방법.

**청구항 14**

제8항에 있어서, 상기 반도체 디바이스가 상기 반도체 웨이퍼의 양단에 열로 배열되며, 열의 각 반도체 디바이스 상에 다수의 대응하는 본드 패드를 병렬로 접속시키는 단계를 포함하는 것을 특징으로 하는 상호 접속 시스템의 형성 방법.

**청구항 15**

반도체가 반도체 웨이퍼 표면의 양단에 다수의 열로 형성되고, 반도체 디바이스가 형성되는 반도체 웨이퍼로부터 상기 반도체 디바이스를 분리하기 전에, 각 반도체 상에 다수의 본드 패드를 갖고 있는 다수의 반도체 디바이스를 검사하고 번인하는 방법에 있어서, 반도체 디바이스의 각 열에 대해 상기 반도체 디바이스 상에 대응하는 본드 패드를 병렬로 상호 접속하는 단계, 상기 반도체 디바이스 행의 병렬 접속된 본드 패드의 각 셋트를 상기 반도체 웨이퍼 상의 검사점 접촉부에 접속시키는 단계, 및 상기 각 반도체 디바이스를 검사하고 번인하는 방식으로 각 검사점 접촉부에 검사 및 번인 전압을 인가하는 단계를 포함하는 것을 특징으로 하는 다수의 반도체 디바이스를 검사하고 번인하는 방법.

**청구항 16**

제15항에 있어서, 상기 병렬 접속부로부터 결함으로 검사된 각 반도체를 절단하는 단계를 포함하는 것을 특징으로 하는 다수의 반도체 디바이스를 검사하고 번인하는 방법.

**청구항 17**

제16항에 있어서, 각 반도체 입력 신호 본드 패드는 휴즈 링크에 의해 상기 병렬 접속부에 접속되며, 번인 전에 결함이 있는 디바이스를 절단하기 위해 레이저 빔으로써 휴즈 링크를 개방하는 단계를 포함하는 것을 특징으로 하는 다수의 반도체 디바이스를 검사하고 번인하는 방법.

**청구항 18**

제15항에 있어서, 웨이퍼로부터 상기 디바이스를 분리시키기 전에 상기 웨이퍼로부터 상기 상호 접속 회로를 제거하는 단계를 포함하는 것을 특징으로 하는 다수의 반도체 디바이스를 검사하고 번인하는 방법.

**청구항 19**

제2항에 있어서, 상기 휴즈 링크가 번인 중 과부하가 발생할 때 개방되는 저전압 반송 물질인 것을 특징으로 하는 상호 접속 시스템.

**도면**

도면1

도면2

도면3

도면4

도면5

도면6