(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第6203935号

(P6203935)

(45) 発行日 平成29年9月27日(2017.9.27)

(24) 登録日 平成29年9月8日(2017.9.8)

|                      |                |

|----------------------|----------------|

| (51) Int.Cl.         | F 1            |

| G06F 17/16 (2006.01) | G06F 17/16 K   |

| G06F 9/30 (2006.01)  | G06F 9/30 350A |

| G06F 9/32 (2006.01)  | G06F 9/32 320F |

| H03M 13/41 (2006.01) | H03M 13/41     |

| G06F 9/305 (2006.01) | G06F 9/30 340C |

請求項の数 25 (全 17 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2016-501437 (P2016-501437)  |

| (86) (22) 出願日 | 平成26年3月12日 (2014.3.12)        |

| (65) 公表番号     | 特表2016-517577 (P2016-517577A) |

| (43) 公表日      | 平成28年6月16日 (2016.6.16)        |

| (86) 國際出願番号   | PCT/US2014/024203             |

| (87) 國際公開番号   | W02014/150778                 |

| (87) 國際公開日    | 平成26年9月25日 (2014.9.25)        |

| 審査請求日         | 平成28年11月16日 (2016.11.16)      |

| (31) 優先権主張番号  | 13/841,878                    |

| (32) 優先日      | 平成25年3月15日 (2013.3.15)        |

| (33) 優先権主張国   | 米国(US)                        |

早期審査対象出願

|           |                                                                                        |

|-----------|----------------------------------------------------------------------------------------|

| (73) 特許権者 | 507364838<br>クアルコム、インコーポレイテッド<br>アメリカ合衆国 カリフォルニア 921<br>21 サン・ディエゴ モアハウス ドラ<br>イブ 5775 |

| (74) 代理人  | 100108453<br>弁理士 村山 靖彦                                                                 |

| (74) 代理人  | 100163522<br>弁理士 黒田 晋平                                                                 |

| (72) 発明者  | ニコ・デ・ローレンティス<br>アメリカ合衆国・カリフォルニア・921<br>21-1714・サン・ディエゴ・モアハ<br>ウス・ドライブ・5775             |

審査官 田中 幸雄

最終頁に続く

(54) 【発明の名称】加算比較選択命令

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のレジスタ、第2のレジスタ、および第3のレジスタを特定する命令を記憶するメモリを備える装置であって、プロセッサによって前記命令が実行されると、

前記プロセッサによって、前記第1のレジスタからの第1の値を、前記第2のレジスタからの第2の値に加算するようにベクトル加算演算が行われ、

前記第3のレジスタからの第3の値から、前記第2の値を減算するようにベクトル減算演算が行われ、

前記ベクトル加算演算の結果を、前記ベクトル減算演算の結果と比較するようにベクトル比較演算が行われる、

装置。

## 【請求項 2】

前記プロセッサによって前記命令が実行されると、ベクトル選択演算が行われて、

前記ベクトル比較演算に基づいて、前記ベクトル加算演算の前記結果、または前記ベクトル減算演算の前記結果を選択し、

前記選択結果を用いて前記第1のレジスタを更新する、

請求項1に記載の装置。

## 【請求項 3】

前記ベクトル加算演算の前記結果が、前記ベクトル減算演算の前記結果より大きいときは、前記ベクトル加算演算の前記結果が選択され、前記ベクトル減算演算の前記結果が、

前記ベクトル加算演算の前記結果より大きいときは、前記ベクトル減算演算の前記結果が選択される、請求項2に記載の装置。

**【請求項4】**

前記選択結果が前記ベクトル加算演算の前記結果であるときは、デコーダは偶数状態に対応する先行状態への遷移を決定し、前記選択結果が前記ベクトル減算演算の前記結果であるときは、前記デコーダは奇数状態に対応する先行状態への遷移を決定する、請求項3に記載の装置。

**【請求項5】**

前記ベクトル加算演算、前記ベクトル減算演算、前記ベクトル比較演算、および前記ベクトル選択演算が、同じ実行サイクルの間に行われる、請求項2に記載の装置。 10

**【請求項6】**

前記命令が記憶位置をさらに特定し、前記ベクトル比較演算の結果は前記記憶位置に記憶される、請求項1に記載の装置。

**【請求項7】**

前記記憶位置が前記第1のレジスタに対応する、請求項6に記載の装置。

**【請求項8】**

前記第1の値がデコーダのパスメトリック値の第1の組であり、前記第2の値がプランチメトリック値であり、前記第3の値がパスメトリック値の第2の組である、請求項1に記載の装置。

**【請求項9】**

前記デコーダがビタビデコーダである、請求項8に記載の装置。 20

**【請求項10】**

前記命令および第2の命令を含む超長命令語(VLIW)パケットが前記メモリからの取り出しのために使用される、請求項1に記載の装置。

**【請求項11】**

命令を実行する方法であって、前記方法が

第1のレジスタ、第2のレジスタ、および第3のレジスタを特定する前記命令を受け取るステップと、

プロセッサによって前記命令を実行するステップであって、

前記第1のレジスタからの第1の値を、前記第2のレジスタからの第2の値に加算して、第1の結果を生成するステップと、 30

前記第3のレジスタからの第3の値から、第2の値を減算して、第2の結果を生成するステップと、

前記第1の結果を前記第2の結果と比較するステップと

を含む、前記命令を実行するステップと

を含む命令を実行する方法。

**【請求項12】**

前記命令を実行するステップが、

前記第1の結果を前記第2の結果と比較するステップに基づいて、前記第1の結果または前記第2の結果を選択するステップと、 40

前記選択結果を用いて前記第1のレジスタを更新するステップと

をさらに含む、請求項11に記載の命令を実行する方法。

**【請求項13】**

前記第1の結果が前記第2の結果より大きいときは、前記第1の結果が選択され、前記第2の結果が前記第1の結果より大きいときは、前記第2の結果が選択される、請求項12に記載の命令を実行する方法。

**【請求項14】**

前記第1の値を前記第2の値に加算するステップ、前記第3の値から前記第2の値を減算するステップ、前記第1の結果を前記第2の結果と比較するステップ、および前記第1の結果または前記第2の結果を選択するステップが、同じ実行サイクルの間に行われる、請求項1 50

3に記載の命令を実行する方法。

**【請求項 15】**

前記命令が記憶位置をさらに特定し、前記命令を実行するステップが、前記第1の結果を前記第2の結果と比較するステップの結果を前記記憶位置に記憶するステップをさらに含む、請求項11に記載の命令を実行する方法。

**【請求項 16】**

前記第1の値がデコーダのバスメトリック値の第1の組であり、前記第2の値がプランチメトリック値であり、前記第3の値がバスメトリック値の第2の組である、請求項11に記載の命令を実行する方法。

**【請求項 17】**

前記デコーダがビタビデコーダである、請求項16に記載の命令を実行する方法。

**【請求項 18】**

前記命令および第2の命令を含む、超長命令語(VLIW)パケットを受け取るステップをさらに含む、請求項11に記載の命令を実行する方法。

**【請求項 19】**

第1のレジスタ、第2のレジスタ、および第3のレジスタを特定する命令を記憶するための手段と、

前記命令を実行するための手段であって、

前記第1のレジスタからの第1の値を、前記第2のレジスタからの第2の値に加算して、第1の結果を生成するための手段と、

前記第3のレジスタからの第3の値から、第2の値を減算して、第2の結果を生成するための手段と、

前記第1の結果を、前記第2の結果と比較するための手段と

を備える、前記命令を実行するための手段と

を備える装置。

**【請求項 20】**

前記加算するための手段がベクトル加算器を含み、前記減算するための手段がベクトル減算器を含み、前記比較するための手段が比較器を含む、請求項19に記載の装置。

**【請求項 21】**

前記命令を実行するための手段が、同じ実行サイクルの間に、前記第1の値を前記第2の値に加算し、前記第3の値から前記第2の値を減算し、前記第1の結果を前記第2の結果と比較するように構成される、請求項19に記載の装置。

**【請求項 22】**

プロセッサによって実行されたときに、前記プロセッサに、

第1のレジスタ、第2のレジスタ、および第3のレジスタを特定する单一命令を受け取らせ、

前記单一命令を実行させる、

プログラムコードを含む、コンピュータ可読記憶媒体であって、

前記单一命令を実行することは、

前記第1のレジスタからの第1の値を、前記第2のレジスタからの第2の値に加算して、第1の結果を生成し、

前記第3のレジスタからの第3の値から、第2の値を減算して、第2の結果を生成し、

前記第1の結果を前記第2の結果と比較すること

を含む、コンピュータ可読記憶媒体。

**【請求項 23】**

前記单一命令を実行することが、

前記第1の結果を前記第2の結果と比較することに基づいて、前記第1の結果または前記第2の結果の1つを選択すること、および

前記選択結果を用いて前記第1のレジスタを更新すること

をさらに含む、請求項22に記載のコンピュータ可読記憶媒体。

10

20

30

40

50

**【請求項 2 4】**

前記第1の値を前記第2の値に加算すること、前記第3の値から前記第2の値を減算すること、前記第1の結果を前記第2の結果と比較すること、および前記第1のレジスタを更新することが、同じ実行サイクルの間に行われる、請求項23に記載のコンピュータ可読記憶媒体。

**【請求項 2 5】**

前記单一命令を実行することが、前記第1の結果を前記第2の結果と比較することの結果を記憶位置に記憶することをさらに含む、請求項22に記載のコンピュータ可読記憶媒体。

**【発明の詳細な説明】****【技術分野】**

10

**【0 0 0 1】****関連出願の相互参照**

本出願は、参照によりその全体が本明細書に明白に組み込まれている、本出願の譲受人が所有する2013年3月15日に出願した米国仮出願第13/841,878号の優先権を主張するものである。

**【0 0 0 2】**

本開示は、一般に加算比較選択命令に関する。

**【背景技術】****【0 0 0 3】**

20

技術の進歩は、結果としてより小さく、より強力なコンピューティングデバイスをもたらしている。たとえば現在は、小型、軽量でユーザによって容易に持ち運ばれる、ポータブルワイヤレス電話、携帯情報端末(PDA)、およびページングデバイスなどのワイヤレスコンピューティングデバイスを含む、多様なポータブルパーソナルコンピューティングデバイスが存在する。より具体的には、セルラー電話およびインターネットプロトコル(IP)電話などのポータブルワイヤレス電話は、音声およびデータパケットを、ワイヤレスネットワークを通して通信することができる。さらに、多くのこのようなワイヤレス電話は、それらに組み込まれた他のタイプのデバイスを含む。たとえばワイヤレス電話はまた、デジタルスチルカメラ、デジタルビデオカメラ、デジタルレコーダ、およびオーディオファイルプレーヤを含むことができる。またこのようなワイヤレス電話は、インターネットにアクセスするために用いることができるウェブブラウザアプリケーションなどの、ソフトウェアアプリケーションを含む実行可能命令を処理することができる。したがってこれらのワイヤレス電話は、かなりのコンピューティング能力を含むことができる。

**【0 0 0 4】**

30

オーディオまたはビデオ復号などのマルチメディア処理を行うワイヤレス電話は、符号化された信号を復号するために、しばしばビタビアルゴリズムなどのアルゴリズムを用いることができる。たとえば、符号化された2値信号を生成するために、2値信号は、複数の符号化段階(たとえば畳み込み符号化)において符号化され得る。各符号化段階において符号化演算は、2値信号の状態(S)を変化させ得る。2値信号の状態は、特定の時点(k)における(たとえば特定の符号化段階における)、ワイヤレス電話内のエンコーダの状態に対応し得る。たとえば、第1の符号化段階の間に第1の状態を生成するように、2値信号に対して第1の符号化演算を行ってもよいし、第2の符号化段階の間に第2の状態を生成するように、第1の状態に対して第2の符号化演算を行ってもよい。符号化された2値信号は、符号化演算が完了した後に生成される。連続する状態の順序は、符号化された2値信号に対応する独特なパス(すなわちビタビパス)を生成することができる。

40

**【0 0 0 5】**

ワイヤレス電話は、連続する状態を2値信号まで辿ることによって、パスを回復して符号化された2値信号を復号することができる。たとえばワイヤレス電話は、符号化された2値信号(たとえば符号化された2値信号に関連する状態)から、符号化時に生成された先行状態(たとえば前の状態)を2値信号まで遡って、パスを復元することができる。パスの先行状態は、各到着状態(arrival state)(すなわち「現在の」状態)において決定すること

50

ができ、プロセスは2値信号が回復される(たとえば2値信号までバスを遡る)まで繰り返すことができる。このプロセスは疊み込み復号と呼ぶことができる。符号化された2値信号を復号するために、ビタビアルゴリズムを用いることができる。たとえばワイヤレス電話はデコーダにおいて、ビタビアルゴリズムを用いて、バスの到着状態からバスの先行状態を決定し、2値信号が回復されるまでプロセスを繰り返すことができる。先行状態は、到着状態を回復するために用いられるバスメトリックに基づいて決定することができる。しかし復号段階において先行状態を決定することは、複数の命令を利用し得る。復号段階の間に複数の命令を用いて先行状態を決定することは、処理時間を増加させ得る。

#### 【発明の概要】

#### 【課題を解決するための手段】

10

#### 【0006】

ビタビアルゴリズムを用いた復号段階の間に、先行状態を決定する単一命令を開示している。たとえば最も可能性の高い状態のシーケンス(すなわちビタビパス)は、ビタビアルゴリズムを用いて見出すことができる。ビタビパスは、各状態に至る複数のバスを有する複数の状態が存在する、状態のトレリスとすることができる。状態間のどの遷移が最も可能性が高いかを判断する(たとえば「生き残り」バスを決定する)ために、状態間の異なる遷移の尤度が決定される。命令は、電子デバイス(たとえばモバイルデバイス)において疊み込み復号を行うために、他の実行可能命令に関連して、加算、比較、および選択演算を行うために用いることができる。たとえば命令は、第1の状態(2S)(たとえば偶数状態)から到着状態(S)に達するために用いられるメトリックの和、および第2の状態(2S+1)(たとえば奇数状態)から同じ到着状態(S)に達するために用いられるメトリックの差を決定することができる。命令はまた、和を差と比較して、どちらの計算がより大きい値に対応するかを判定することができる。より大きな値に対応する計算は、先行状態を予測(たとえば生き残りバスを予測)するために選択することができる。命令がプロセッサによって実行されるときは、選択されたメトリックの計算はレジスタにロードされ、次の復号段階の間に用いることができる。加算演算、比較演算、および選択演算は、命令の同じ実行サイクルにおいて行われ得る。さらに命令は、超長命令語(VLIW)アーキテクチャの命令レベル並列処理をうまく利用することができる。たとえば単一のVLIWパケットは、このような並列に実行可能な命令を複数含むことができる。

20

#### 【0007】

30

特定の実施形態では、装置は、第1のレジスタ、第2のレジスタ、および第3のレジスタを特定する命令を記憶するメモリを含む。プロセッサによって命令が実行されると、プロセッサによって、第1のレジスタからの第1の値を、第2のレジスタからの第2の値に加算するように、ベクトル加算演算が行われる。また命令が実行されると、第3のレジスタからの第3の値から、第2の値を減算するように、ベクトル減算演算が行われる。また、命令が実行されると、ベクトル加算演算の結果を、ベクトル減算演算の結果と比較するように、ベクトル比較演算が行われる。

#### 【0008】

40

他の特定の実施形態では、方法は、第1のレジスタ、第2のレジスタ、および第3のレジスタを特定する命令を受け取るステップを含む。方法はまた、プロセッサによって命令を実行するステップを含む。命令を実行するステップは、第1のレジスタからの第1の値を、第2のレジスタからの第2の値に加算して、第1の結果を生成するステップを含む。命令を実行するステップはまた、第3のレジスタからの第3の値から、第2の値を減算して、第2の結果を生成するステップを含む。命令を実行するステップはまた、第1の結果を、第2の結果と比較するステップを含む。

#### 【0009】

他の特定の実施形態では、装置は、第1のレジスタ、第2のレジスタ、および第3のレジスタを特定する命令を記憶するための手段を含む。装置はまた、命令を実行するための手段を含む。命令を実行するための手段は、第1のレジスタからの第1の値を、第2のレジスタからの第2の値に加算して、第1の結果を生成するための手段を含む。命令を実行するた

50

めの手段はさらに、第3のレジスタからの第3の値から、第2の値を減算して、第2の結果を生成するための手段を含む。実行するための手段はさらに、第1の結果を、第2の結果と比較するための手段を含む。

#### 【0010】

他の特定の実施形態では、非一時的コンピュータ可読媒体は、プロセッサによって実行されたときに、プロセッサに、第1のレジスタ、第2のレジスタ、および第3のレジスタを特定する单一命令を受け取らせる、プログラムコードを含む。プログラムコードはまた、プロセッサに单一命令を実行させる。单一命令を実行することは、第1のレジスタからの第1の値を、第2のレジスタからの第2の値に加算して、第1の結果を生成することを含む。单一命令を実行することはまた、第3のレジスタからの第3の値から、第2の値を減算して、第2の結果を生成することを含む。单一命令を実行することはさらに、第1の結果を、第2の結果と比較することを含む。

10

#### 【0011】

開示した実施形態の少なくとも1つによってもたらされる、1つの特定の利点は、加算、比較、および選択機能を行うための单一命令の使用により、復号段階のためのコードサイズが縮小され、実行サイクルが減少されることである。本開示の他の態様、利点、および特徴は、以下の「図面の簡単な説明」、「発明を実施するための形態」、および「特許請求の範囲」のセクションを含む明細書全体を読んだ後に明らかになるであろう。

#### 【図面の簡単な説明】

##### 【0012】

20

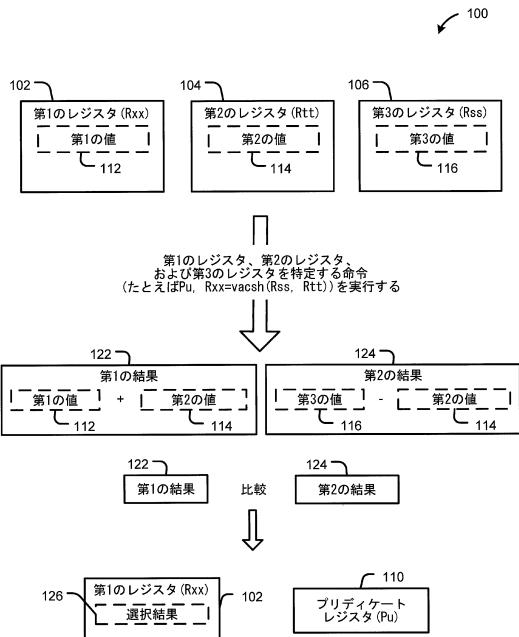

【図1】第1のレジスタ、第2のレジスタ、および第3のレジスタを特定する命令の実行を示す図である。

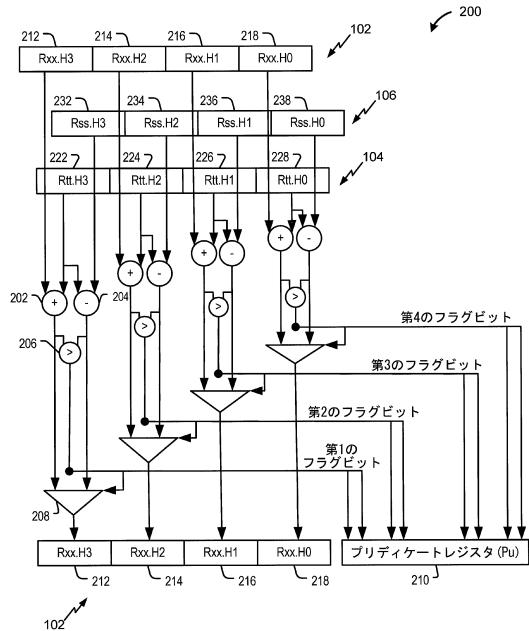

【図2】第1のレジスタ、第2のレジスタ、および第3のレジスタを特定する命令の実行を示す別の図である。

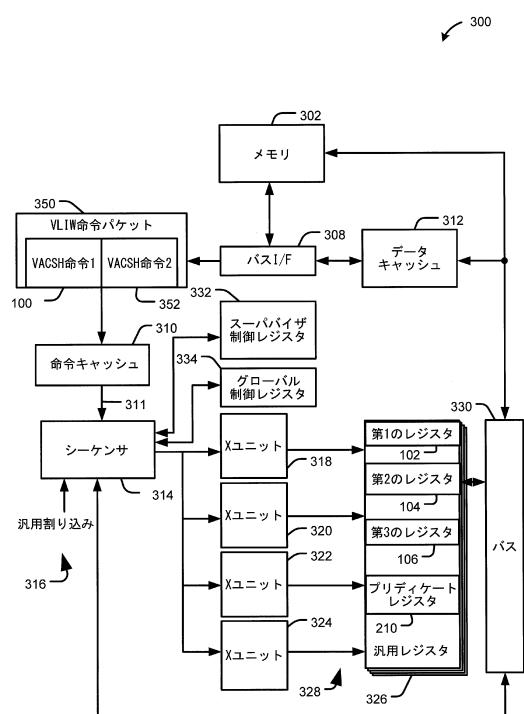

【図3】第1のレジスタ、第2のレジスタ、および第3のレジスタを特定する命令を記憶し処理するように動作可能なシステムの特定の例示的実施形態を示す図である。

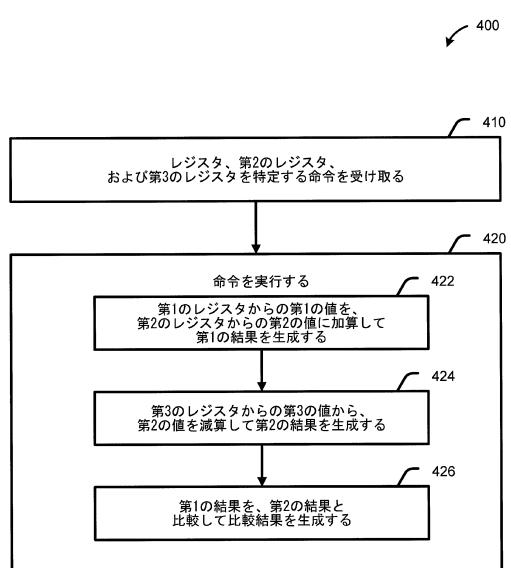

【図4】第1のレジスタ、第2のレジスタ、および第3のレジスタを特定する命令を処理する方法の特定の例示的実施形態のフローチャートである。

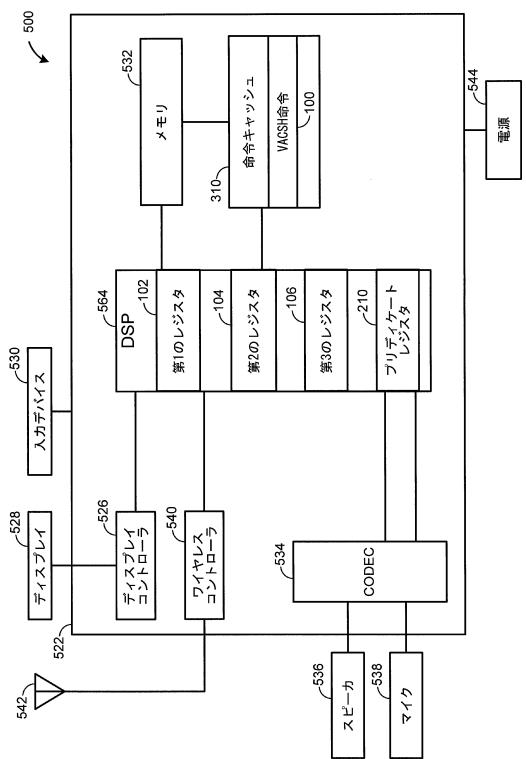

【図5】第1のレジスタ、第2のレジスタ、および第3のレジスタを特定する命令を記憶するメモリを含むワイヤレスデバイスの特定の実施形態のブロック図である。

30

#### 【発明を実施するための形態】

##### 【0013】

復号演算を行うための命令は、第1の値(たとえばデコーダのバスメトリック値の第1の組)、第2の値(たとえばプランチメトリック値)、および第3の値(たとえばデコーダのバスメトリック値の第2の組)を含むことができる。デコーダは、復号演算の間に第1、第2、および第3の値を用いて、先行状態を決定する(たとえば生き残りバスを決定する)ことができる。たとえば第1の値は、到着状態(S)に達するために用いられる偶数状態(2S)のバスメトリックに対応することができ、第3の値は、到着状態(S)に達するために用いられる奇数状態(2S+1)のバスメトリックに対応することができる。第2の値は、復調されたシンボルから取得されるプランチメトリックに対応することができ、符号多項式の関数とすることができます。オプションとして命令は、宛先レジスタを特定することができる。命令が実行されたときは、第1の結果および第2の結果が生成され得る。第1の結果は、ベクトル加算演算に応答して生成され得る。たとえばプロセッサは、第1の値を第2の値に加算して、第1の結果を生成することができる。第2の結果は、ベクトル減算演算に応答して生成され得る。たとえばプロセッサは、第3の値から第2の値を減算して、第2の結果を生成することができる。特定の実施形態では、第1の値および第3の値は、補数ビットを含むことができる。

40

##### 【0014】

ベクトル比較演算は、第1の結果(たとえば偶数状態(2S)に関連する結果)を、第2の結果(たとえば奇数状態(2S+1)に関連する結果)と比較するために行われる。第1の結果が第2の

50

結果より大きいときは、偶数状態(2S)に対応する先行状態を選択することができる。第2の結果が第1の結果より大きいときは、奇数状態(2S+1)に対応する先行状態を選択することができる。

#### 【0015】

図1を参照すると、第1のレジスタ、第2のレジスタ、および第3のレジスタを特定する命令100の実行の、第1の例示的な例を示している。特定の実施形態では命令100は、第1のレジスタ102、第2のレジスタ104、第3のレジスタ106、およびプリディケートレジスタ110を特定することができる。第1のレジスタ102は第1の値112を記憶することができ、第2のレジスタ104は第2の値114を記憶することができ、第3のレジスタ106は第3の値116を記憶することができる。命令100は「Pu, Rxx=vacsh(Rss, Rtt)」とすることができます、「vacsh」は命令100の演算コード、「Rxx」は第1のレジスタ102、「Rtt」は第2のレジスタ104、「Rss」は第3のレジスタ106、および「Pu」は、回復された遷移(たとえば符号化された遷移)が、偶数状態(2S)に対応するか、奇数状態(2S+1)に対応するかに基づいて、生き残り状態(すなわち先行状態)を予測するプリディケートレジスタ110である。10

#### 【0016】

ベクトル比較演算の結果は、先行状態(たとえば生き残りパス)が、偶数状態(2S)に対応するか、奇数状態(2S+1)に対応するかを予測するために、プリディケートレジスタ110に記憶され得る。生き残り状態は、到着状態(S)に達するために用いられるメトリックの関数とすることができます。たとえば第1の値112は、偶数状態(2S)から到着状態(S)に達するために用いられるパスメトリック値の第1の組に対応することができる。パスメトリック値は、到着状態(S)に達するために最も可能性が高いパスにわたる距離に関連する値に対応することができます。第2の値114は、プランチメトリック値に対応することができる。プランチメトリック値は、状態間の正規化距離を測る値に対応することができます。第3の値116は、奇数状態(2S+1)から到着状態(S)に達するために用いられるパスメトリック値の第2の組に対応することができます。到着状態(S)において、ビタビデコーダなどのデコーダは、到着状態(S)に達するために用いられるパスメトリック値112、116に基づいて、偶数先行状態(2S)と奇数先行状態(2S+1)から選択することができる。20

#### 【0017】

演算時には、プロセッサ内のベクトル加算器は、ベクトル加算演算を行って、第1のレジスタ102からの第1の値112を、第2のレジスタ104からの第2の値114に加算することができる。たとえばパスメトリック値の第1の組を、プランチメトリック値に加算して、第1の結果122を生成することができる。プロセッサ内のベクトル減算器は、ベクトル減算演算を行って、第3のレジスタ106の第3の値116から、第2の値114を減算することができる。たとえばパスメトリック値の第2の組を、プランチメトリック値から減算して、第2の結果124を生成することができる。プロセッサ内の比較器は、ベクトル比較演算を行って、第1の結果122を第2の結果124と比較して、結果122、124のどちらがより大きな値に対応するかを判定することができる。30

#### 【0018】

プロセッサは、ベクトル選択演算を行って、より大きな値に対応する結果122または124を選択することができ、第1のレジスタ102は、選択結果126を用いて更新され得る。たとえば第1の結果122が第2の結果124より大きいときは、第1の結果122が、選択結果126として第1のレジスタ102に記憶され、先行状態は偶数状態(2S)に対応すると予測される。第2の結果124が第1の結果122より大きいときは、第2の結果124が、選択結果126として第1のレジスタ102に記憶され、先行状態は奇数状態(2S+1)に対応すると予測される。40

#### 【0019】

述べられた单一命令100は、同じ実行サイクルの間に、ベクトル加算演算、ベクトル減算演算、ベクトル比較演算、およびベクトル選択演算が行われることを可能にし得ることが理解されるであろう。ベクトル加算演算、ベクトル減算演算、ベクトル比較演算、およびベクトル選択演算を、4つの個別の命令ではなく、1つの命令(たとえば「vacsh」命令)として実装することにより、およそ40パーセントの処理速度の増加を生じることができる50

。たとえば单一命令は、5パイプラインサイクル(4つの命令に対して)と比べて、3パイプラインサイクルを用いて実行することができる。また命令100が発行されたときは、スループットは、およそサイクル当たり2バタフライに等しくなり得ることが理解されるであろう。たとえば各バタフライは、状態から状態への可能な遷移の数に対応することができる。特定の実施形態では、命令100が単一サイクルの間に2回発行されたときは、スループットはおよそサイクル当たり4バタフライに等しくなり得る。

#### 【0020】

図2を参照すると、第1のレジスタ、第2のレジスタ、および第3のレジスタを特定する命令の実行の、第2の例示的な例を示しており、全体的に200として示している。

#### 【0021】

特定の実施形態では、第1のレジスタ102は、4つの部分を含む64ビットレジスタとすることができる。たとえば第1のレジスタ102は、第1の部分(Rxx.H3)212、第2の部分(Rxx.H2)214、第3の部分(Rxx.H1)216、および第4の部分(Rxx.H0)218を含むことができる。各部分212～218は、第1のパスメトリック値に対応する16ビット値を記憶することができる。たとえば第1の部分212は第1の16ビット値(x1)を記憶することができ、第2の部分214は第2の16ビット値(x2)を記憶することができ、第3の部分216は第3の16ビット値(x3)を記憶することができ、第4の部分218は第4の16ビット値(x4)を記憶することができる。第1のパスメトリック値は、図1の第1の値112に対応することができる。たとえば第1のパスメトリック値は、偶数状態(2S)から到着状態(S)に達するために用いられるパスメトリック値の第1の組に対応することができる。

#### 【0022】

特定の実施形態では、第2のレジスタ104は、4つの部分を含む64ビットレジスタとすることができる。たとえば第2のレジスタ104は、第1の部分(Rtt.H3)222、第2の部分(Rtt.H2)224、第3の部分(Rtt.H1)226、および第4の部分(Rtt.H0)228を含むことができる。各部分222～228は、プランチメトリック値に対応する16ビット値を記憶することができる。たとえば第1の部分222は第1の16ビット値(y1)を記憶することができ、第2の部分224は第2の16ビット値(y2)を記憶することができ、第3の部分226は第3の16ビット値(y3)を記憶することができ、第4の部分228は第4の16ビット値(y4)を記憶することができる。

#### 【0023】

特定の実施形態では、第3のレジスタ106は、4つの部分を含む64ビットレジスタとすることができる。たとえば第3のレジスタ106は、第1の部分(Rss.H3)232、第2の部分(Rss.H2)234、第3の部分(Rss.H1)236、および第4の部分(Rss.H0)238を含むことができる。各部分232～238は、第2のパスメトリック値に対応する16ビット値を記憶することができる。たとえば第1の部分232は第1の16ビット値(z1)を記憶することができ、第2の部分234は第2の16ビット値(z2)を記憶することができ、第3の部分236は第3の16ビット値(z3)を記憶することができ、第4の部分238は第4の16ビット値(z4)を記憶することができる。第2のパスメトリック値は、図1の第3の値116に対応することができる。たとえば第2のパスメトリック値は、偶数状態(2S)から到着状態(S)に達するために用いられるパスメトリック値の第2の組に対応することができる。

#### 【0024】

第1のベクトル加算器202は、第1のレジスタ102の第1の部分212からの第1の16ビット値(x1)を、第2のレジスタ104の第1の部分222からの第1の16ビット値(y1)に加算して、第1の16ビット結果を生成するように構成される。第1のベクトル減算器204は、第3のレジスタ106の第1の部分232からの第1の16ビット値(z1)から、第1の16ビット値(y1)を減算して、第2の16ビット結果を生成するように構成される。第1の比較器206は、第1の16ビット結果を第2の16ビット結果と比較するように構成される。比較に基づいて第1の比較器206は、第1の16ビット結果が第2の16ビット結果より大きいかどうか、または第2の16ビット結果が第1の16ビット結果より大きいかどうかを特定する、第1のフラグビット(たとえば1ビット信号)を生成することができる。第1のフラグビットは、プリディケートレジスタ(Pu)210の第1の部分に供給することができ、先行状態が偶数状態(2S)である、または奇数状態(2S+1)

10

20

30

40

50

)である可能性が最も高いかどうかを予測するために用いられる。

**【0025】**

第1のフラグビットはまた、選択デバイス208に供給され得る。特定の実施形態では、選択デバイス208はマルチブレクサとすることができます。選択デバイス208は、第1のフラグビットに基づいて第1の16ビット結果または第2の16ビット結果のいずれかを選択し、選択結果を第1のレジスタ102の第1の部分212に供給するように構成される。たとえば選択デバイス208は、第1の16ビット結果が第2の16ビット結果より大きいことを第1のフラグビットが示すときは、第1の16ビット結果を第1のレジスタ102の第1の部分212に供給することができる。あるいは選択デバイス208は、第2の16ビット結果が第1の16ビット結果より大きいことを第1のフラグビットが示すときは、第2の16ビット結果を第1のレジスタ102の第1の部分212に供給することができる。10

**【0026】**

さらなるベクトル加算器、ベクトル減算器、および比較器は並列に、かつ第1のベクトル加算器202、第1のベクトル減算器204、および第1の比較器206と実質的に同様に動作することができる。たとえばさらなるベクトル加算器、ベクトル減算器、および比較器は、第1のレジスタ102、第2のレジスタ104、および第3のレジスタ106の対応する部分における16ビット値に基づいて、第2のフラグビット、第3のフラグビット、および第4のフラグビットを生成することができる。第1のレジスタ102の第2、第3、および第4の部分214～218は、それぞれ第2、第3、および第4のフラグビットに基づいて、16ビット結果を用いて更新することができる。したがって単一実行サイクルの間に、4つの状態を処理することができる。20

**【0027】**

図3を参照すると、命令100(たとえば「VACSH」命令)を記憶し処理するように動作可能なシステムの特定の例示的実施形態を開示しており、全体的に300として示している。システム300は、バスインターフェース308を通じて命令キャッシュ310に結合された、メモリ302を含むことができる。特定の実施形態では、システム300のすべてまたは一部分は、プロセッサ内に一体化され得る。

**【0028】**

命令100(たとえば加算比較選択命令)、および第2の命令352(たとえば第2の加算比較選択命令)は、超長命令語(VLIW)パケット350内に含まれ得る。命令100は、図1～図2に示されるような第1のレジスタ102、第2のレジスタ104、および第3のレジスタ106を特定することができる。第1のレジスタ102、第2のレジスタ104、および第3のレジスタ106は、汎用レジスタファイル326内に含まれ得る。第1のレジスタ102は、偶数状態(2S)から到着状態(S)に達するために用いられるパスマトリック値の第1の組を記憶することができ、第2のレジスタ104は、プランチメトリック値を記憶することができ、第3のレジスタ106は、奇数状態(2S+1)から到着状態(S)に達するために用いられるパスマトリック値の第2の組を記憶することができる。命令100はまた、プリディケートレジスタ210を特定することができる。図1～図2に関連して述べられたように、ベクトル比較演算の結果は、先行状態(たとえば生き残りパス)が、偶数状態(2S)に対応するか、奇数状態(2S+1)に対応するかを予測するために、プリディケートレジスタ210に記憶することができる。プリディケートレジスタ210はまた、汎用レジスタファイル326内に含まれ得る。40

**【0029】**

メモリ302は、命令100を、バスインターフェース308を通じて命令キャッシュ310に送信することができる。データキャッシュ312はまた、バスインターフェース308を通じてメモリ302に結合され得る。特定の実施形態ではメモリ302は、図1～図2に関連して述べられたように、命令100を用いてベクトル加算演算、ベクトル減算演算、ベクトル比較演算、ベクトル選択演算、またはそれらの任意の組合せを行うデコーダによってアクセス可能とすることができる。たとえばデコーダは、図5を参照してさらに述べられるように、コーダ/デコーダ(CODEC)の一部とすることができます。

**【0030】**

50

命令キャッシュ310は、バス311を通じてシーケンサ314に結合され得る。シーケンサ314は、割り込みレジスタ(図示せず)から取り出すことができる汎用割り込み316を受け取ることができる。特定の実施形態では、命令キャッシュ310は、複数の現行命令レジスタ(図示せず)を通じて、シーケンサ314に結合することができ、これらはバス311に結合され、システム300の特定のスレッド(たとえばハードウェアスレッド)に関連付けられ得る。特定の実施形態では、プロセッサ300は、6つのスレッドを含むインターリーブされたマルチスレッドプロセッサとすることができる。他の特定の実施形態では、プロセッサ300は、3つまたは4つのスレッドを含むことができる。

#### 【0031】

特定の実施形態ではバス311は、128ビットバスとすることができ、シーケンサ314は、命令パケット(たとえば命令100および第2の命令352を含む、超長命令語(VLIW)命令パケット350)を通じて、メモリ302から命令を取り出すように構成することができる。シーケンサ314は、第1の命令実行ユニット318、第2の命令実行ユニット320、第3の命令実行ユニット322、および第4の命令実行ユニット324に結合され得る。より少ないまたはより多い命令実行ユニットが存在し得ることに留意されるべきである。各命令実行ユニット318～324は、第1のバス328を通じて汎用レジスタファイル326に結合され得る。汎用レジスタファイル326はまた、第2のバス330を通じて、シーケンサ314、データキャッシュ312、およびメモリ302に結合され得る。

#### 【0032】

システム300はまた、割り込み(たとえば汎用割り込み316)を受け入れるかどうかを判断するため、および命令の実行を制御するために、シーケンサ314内の制御ロジックによってアクセスされ得る、ビットを記憶するためのスーパバイザ制御レジスタ332、およびグローバル制御レジスタ334を含むことができる。

#### 【0033】

特定の実施形態では、実行ユニット318～324のいずれも、図1の命令100を実行して第1の結果122および第2の結果124を生成することができる。別の実施形態では、実行ユニット318～324のすべてではないがいくつかは、命令100を実行することができる。たとえば実行ユニット318～324は、図2に関連して述べられたようなベクトル加算器、ベクトル減算器、比較器、および選択デバイスを含む演算論理ユニット(ALU)を含むことができる。実行ユニット318～324は、図2に関連して述べられたベクトル加算器202などのベクトル加算器を用いて、第1のレジスタ102に記憶されたバスメトリック値の第1の組を、第2のレジスタ104に記憶されたプランチメトリック値に加算することによって、第1の結果を生成することができる。実行ユニット318～324は、図2に関連して述べられたベクトル減算器204などのベクトル減算器を用いて、第3のレジスタ106に記憶されたバスメトリック値の第2の組から、第2のレジスタ104に記憶されたプランチメトリック値を減算することによって、第2の結果を生成することができる。実行ユニット318～324は、第1の結果を第2の結果と比較して、どちらの結果が大きいかを判定し、比較の結果を知らせる信号をプリディケートレジスタ210に供給することができる。プリディケートレジスタ210に記憶された情報は、先行状態が偶数状態(2S)に対応するか、奇数状態(2S+1)に対応するかを予測するために用いることができる。

#### 【0034】

したがって、符号化されたデータストリームの復号時に、符号化されたデータ信号の先行状態は、単一命令を用いて、到着状態を回復するために用いられたバスメトリックから予測することができる。さらに比較に応じて、第1の結果または第2の結果のいずれかを、後続の状態プレディケーションにおいて用いられるように第1のレジスタに記憶することができる。命令100は、コードサイズの全体的な低減を達成し、先行状態を予測するために単一命令を使用することにより、プロセッサが行う実行サイクルをより少なくすることができます。命令100および第2の命令352を同時に実行することは、システム300が複数のビタビバスに対応する複数の先行状態を同時に予測することを可能にすることによって、効率を向上し得ることが理解されるであろう。

10

20

30

40

50

**【 0 0 3 5 】**

図3に示されるシステム300は、例示のみであることが留意されるべきである。開示した命令および技法は、他のアーキテクチャ(たとえばマイクロアーキテクチャ、およびデジタル信号プロセッサ(DSP)アーキテクチャ)によってサポートされ、その中で実行され得る。たとえば代替のDSPアーキテクチャは、図3のシステム300より多い、少ない、および/または異なる構成要素を含むことができる。例示として、代替のDSPアーキテクチャは、図3に示されるような4つの実行ユニットの代わりに、2つの実行ユニット、および2つのロード/記憶ユニットを含むことができる。

**【 0 0 3 6 】**

図4を参照すると、第1のレジスタ、第2のレジスタ、および第3のレジスタを特定する命令を処理する方法の特定の例示的実施形態のフローチャートを示しており、全体的に400として示している。例示的実施形態では方法400は、図3のシステム300において行うことができ、図1～図2を参照して示され得る。10

**【 0 0 3 7 】**

方法400は、410で、第1のレジスタ、第2のレジスタ、および第3のレジスタを特定する命令を受け取るステップを含むことができる。たとえば図3において、命令100は、実行ユニット318～324の1つによって受け取られ得る。命令100は、第1のレジスタ102、第2のレジスタ104、および第3のレジスタ106を特定することができる。

**【 0 0 3 8 】**

方法400はまた、420で、命令を実行するステップを含むことができる。たとえば図3において命令100は、実行ユニット318～324の1つによって実行され得る。命令を実行するステップ420は、422で、第1のレジスタからの第1の値を、第2のレジスタからの第2の値に加算して、第1の結果を生成するステップを含むことができる。たとえば図3において、実行ユニット318～324の1つのALU内のベクトル加算器は、第1のレジスタ102に記憶されたパスマトリック値の第1の組を、第2のレジスタ104に記憶されたプランチメトリック値に加算することによって、第1の結果を生成することができる。命令を実行するステップ420はまた、424で、第3のレジスタからの第3の値から、第2の値を減算して、第2の結果を生成するステップを含むことができる。たとえば図3において、実行ユニット318～324の1つのALU内のベクトル減算器は、第3のレジスタ106に記憶されたパスマトリック値の第2の組から、第2のレジスタ104に記憶されたプランチメトリック値を減算することによって、第2の結果を生成することができる。命令を実行するステップ420はまた、426で、第1の結果を第2の結果と比較して、比較結果を生成するステップを含むことができる。たとえば図3において、実行ユニット318～324の1つのALU内の比較器は、第1の結果を第2の結果と比較して、結果のどちらが大きいかを判定し、大きい方の結果を知らせる信号を、プリディケートレジスタ210に供給することができる。プリディケートレジスタ210に記憶された情報は、先行状態が偶数状態(2S)に対応するか、奇数状態(2S+1)に対応するかを予測するために用いることができる。2030

**【 0 0 3 9 】**

図4の方法400は、フィールドプログラマブルゲートアレイ(FPGA)デバイス、特定用途向け集積回路(ASIC)、中央処理装置(CPU)などの処理装置、デジタル信号プロセッサ(DSP)、コントローラ、他のハードウェアデバイス、ファームウェア、またはそれらの任意の組合せによって実施してもよい。例として、図4の方法400は、図3および図5に関連して述べたように、プログラムコードまたは命令を実行するプロセッサ、またはその構成要素によって行われ得る。40

**【 0 0 4 0 】**

図5を参照すると、第1のレジスタ102、第2のレジスタ104、および第3のレジスタ106を特定する命令100(たとえば加算比較選択命令)を記憶するメモリ532を含む、ワイヤレスデバイスの特定の例示的実施形態のブロック図を示しており、全体的に500として示している。デバイス500は、メモリ532に結合された、デジタル信号プロセッサ(DSP)などのプロセッサ564を含む。命令キャッシュ(たとえば例示の命令キャッシュ310)はまた、メモリ5350

2およびプロセッサ564に結合され得る。特定の実施形態ではメモリ532は、命令100などのプロセッサ564によって実行可能な命令を記憶し、命令キャッシュ310に送信する。

#### 【0041】

図5はまた、プロセッサ564およびディスプレイ528に結合された、ディスプレイコントローラ526を示す。コーダ/デコーダ(CODEC)534はまた、プロセッサ564に結合され得る。スピーカ536およびマイク538は、CODEC534に結合され得る。図5はまたワイヤレスコントローラ540は、プロセッサ564およびワイヤレスアンテナ542に結合され得ることを示す。特定の実施形態では、プロセッサ564、ディスプレイコントローラ526、メモリ532、CODEC534、およびワイヤレスコントローラ540は、システムインパッケージまたはシステムオンチップデバイス522に含まれる。特定の実施形態では、命令100を含んだメモリ532または命令キャッシュ310は、電子デバイス(たとえばワイヤレスデバイス500)におけるオーディオまたはビデオ復号時に、命令100を用いて畳み込み復号を行う、CODEC534によってアクセス可能とすることができる。特定の実施形態では、CODEC534はビタビデコーダを含む。

#### 【0042】

処理されると、命令100は、プロセッサ564に、第1のレジスタ102に記憶されたパスメトリック値の第1の組を、第2のレジスタ104に記憶されたプランチメトリック値に加算することによって、第1の結果を生成させる。命令100はまた、プロセッサ564に、第3のレジスタ106に記憶されたパスメトリック値の第2の組から、第2のレジスタ104に記憶されたプランチメトリック値を減算することによって、第2の結果を生成させる。第1および第2の結果を生成すると、命令100はプロセッサ564に、どちらの結果が大きいかを判定するために、第1の結果を第2の結果と比較させ、大きい方の結果を知らせる信号を、プリディケートレジスタ210に供給させることができる。比較に基づいて第1のレジスタ102は、第1の結果または第2の結果のいずれかを用いて更新することができる。たとえば第1の結果が第2の結果より大きかった場合は、第1の結果を第1のレジスタ102に記憶することができる。あるいは第2の結果が第1の結果より大きかった場合は、第2の結果を第1のレジスタ102に記憶することができる。

#### 【0043】

特定の実施形態では、入力デバイス530および電源544は、システムオンチップデバイス522に結合される。さらに特定の実施形態では、図5に示されるように、ディスプレイ528、入力デバイス530、スピーカ536、マイク538、ワイヤレスアンテナ542、および電源544は、システムオンチップデバイス522の外部となる。しかしディスプレイ528、入力デバイス530、スピーカ536、マイク538、ワイヤレスアンテナ542、および電源544のそれぞれは、インターフェースまたはコントローラなどの、システムオンチップデバイス522の構成要素に結合され得る。

#### 【0044】

図5は、ワイヤレス通信デバイスを示すが、プロセッサ564などの加算比較選択命令を実行するためのプロセッサ、メモリ532、および加算比較選択命令を記憶する命令キャッシュ310は、代替としてセットトップボックス、音楽プレーヤ、ビデオプレーヤ、娯楽ユニット、ナビゲーションデバイス、携帯情報端末(PDA)、固定ロケーションデータユニット、またはコンピュータ内に一体化され得ることが留意されるべきである。

#### 【0045】

述べられた実施形態に関連して、第1のレジスタ、第2のレジスタ、および第3のレジスタを特定する命令を記憶するための手段を含む、装置を開示している。たとえば記憶するための手段は、図3のメモリ302、図5のメモリ532、図3および図5の命令キャッシュ310、命令を記憶するように構成された1つまたは複数の他のデバイス、またはそれらの任意の組合せとすることができます。

#### 【0046】

装置はまた、命令を実行するための手段を含むことができる。たとえば命令を実行するための手段は、図2のベクトル加算器、図2のベクトル減算器、図2の比較器、図2の選択デバイス、図3の実行ユニット318、320、322、および324の1つまたは複数、図5のプロセッ

10

20

30

40

50

サ564、命令を実行するように構成された1つまたは複数の他のデバイス、またはそれらの任意の組合せを含むことができる。

#### 【0047】

装置はまた、第1のレジスタからの第1の値を、第2のレジスタからの第2の値に加算して、第1の結果を生成するための手段を含むことができる。たとえば加算するための手段は、図2のベクトル加算器、図3の実行ユニット318、320、322、および324の1つまたは複数、図5のプロセッサ564、値を加算するように構成された1つまたは複数の他のデバイス、またはそれらの任意の組合せを含むことができる。

#### 【0048】

装置はまた、第3のレジスタからの第3の値から、第2の値を減算して、第2の結果を生成するための手段を含むことができる。たとえば減算するための手段は、図2のベクトル減算器、図3の実行ユニット318、320、322、および324の1つまたは複数、図5のプロセッサ564、値を減算するように構成された1つまたは複数の他のデバイス、またはそれらの任意の組合せを含むことができる。

10

#### 【0049】

装置はまた、第1の結果を第2の結果と比較するための手段を含むことができる。たとえば比較するための手段は、図2の比較器、図3の実行ユニット318、320、322、および324の1つまたは複数、図5のプロセッサ564、結果を比較するように構成された1つまたは複数の他のデバイス、またはそれらの任意の組合せを含むことができる。

#### 【0050】

20

当業者ならさらに、様々な例示の論理ブロック、構成、モジュール、回路、および本明細書で開示した実施形態に関連して述べられたアルゴリズムステップは、電子ハードウェア、コンピュータソフトウェア、またはそれらの両方の組合せとして実施できることが理解されよう。様々な例示の構成要素、ブロック、構成、モジュール、回路、およびステップについて、一般にそれらの機能の観点から述べてきた。このような機能がハードウェアとして実施されるか、ソフトウェアとして実施されるかは、特定の用途、および全体のシステムに課される設計上の制約による。当業者は、述べられた機能を、それぞれの特定の用途に対して様々な方法において実施することができるが、このような実施の決定は、本開示の範囲からの逸脱を生じるものと解釈されるべきではない。

#### 【0051】

30

本明細書で開示した実施形態に関連して述べられた方法またはアルゴリズムのステップは、直接ハードウェアにおいて、プロセッサによって実行されるソフトウェアモジュールにおいて、または両者の組合せにおいて具体化され得る。ソフトウェアモジュールは、ランダムアクセスメモリ(RAM)、フラッシュメモリ、リードオンリメモリ(ROM)、プログラマブルリードオンリメモリ(PROM)、消去可能プログラマブルリードオンリメモリ(EPROM)、電気的消去可能プログラマブルリードオンリメモリ(EEPROM)、レジスタ、ハードディスク、リムーバブルディスク、コンパクトディスククリードオンリメモリ(CD-ROM)、または当技術分野で知られている任意の他の形の記憶媒体内に存在することができる。例示の非一時的(たとえば有形の)記憶媒体は、プロセッサが記憶媒体から情報を読み出し、それに情報を書き込むことができるよう、プロセッサに結合される。代替として記憶媒体は、プロセッサと一体とすることができる。プロセッサおよび記憶媒体は、特定用途向け集積回路(ASIC)内に存在することができる。ASICは、コンピューティングデバイスまたはユーザ端末内に存在することができる。代替としてプロセッサおよび記憶媒体は、コンピューティングデバイスまたはユーザ端末内に個別構成要素として存在することができる。

40

#### 【0052】

開示した実施形態の上記の説明は、当業者が開示した実施形態を作製または使用することを可能にするように示された。これらの実施形態に対する様々な変更は当業者には容易に明らかとなり、本明細書で定義される原理は、本開示の範囲から逸脱せずに他の実施形態に応用され得る。したがって本開示は、本明細書に示される実施形態に限定されるものではなく、添付の「特許請求の範囲」によって定義される原理および新規な特徴と一貫し

50

たできる限り広い範囲が与えられるべきである。

【符号の説明】

【0053】

|     |                 |    |

|-----|-----------------|----|

| 100 | 命令              |    |

| 102 | 第1のレジスタ         |    |

| 104 | 第2のレジスタ         |    |

| 106 | 第3のレジスタ         |    |

| 110 | プリディケートレジスタ     |    |

| 112 | 第1の値            | 10 |

| 114 | 第2の値            |    |

| 116 | 第3の値            |    |

| 122 | 第1の結果           |    |

| 124 | 第2の結果           |    |

| 126 | 選択結果            |    |

| 210 | プリディケートレジスタ     |    |

| 302 | メモリ             |    |

| 308 | バスインターフェース      |    |

| 310 | 命令キャッシュ         |    |

| 311 | バス              |    |

| 312 | データキャッシュ        | 20 |

| 314 | シーケンサ           |    |

| 316 | 汎用割り込み          |    |

| 318 | 命令実行ユニット        |    |

| 320 | 命令実行ユニット        |    |

| 322 | 命令実行ユニット        |    |

| 324 | 命令実行ユニット        |    |

| 326 | 汎用レジスタファイル      |    |

| 330 | バス              |    |

| 332 | スーパバイザ制御レジスタ    |    |

| 334 | グローバル制御レジスタ     |    |

| 350 | 超長命令語(VLIW)パケット | 30 |

| 352 | 第2の命令           |    |

| 528 | ディスプレイ          |    |

| 530 | 入力デバイス          |    |

| 526 | ディスプレイコントローラ    |    |

| 532 | メモリ             |    |

| 536 | スピーカ            |    |

| 538 | マイク             |    |

| 540 | ワイヤレスコントローラ     |    |

| 544 | 電源              | 40 |

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(56)参考文献 特開2012-39849(JP,A)

特開平5-282601(JP,A)

特開平5-206873(JP,A)

特開平11-261426(JP,A)

米国特許出願公開第2003/0028844(US,A1)

(58)調査した分野(Int.Cl., DB名)

G 06 F 17 / 16

G 06 F 9 / 30

G 06 F 9 / 305

G 06 F 9 / 32

H 03 M 13 / 41